(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0052296

(43) 공개일자 2012년05월23일

(51) 국제특허분류(Int. C1.)

*H01L 31/073* (2012.01) *H01L 31/042*

(2006.01)

*H01L 31/18* (2006.01)

(21) 출원번호 10-2012-7003509

(22) 출원일자(국제) 2010년07월09일

심사청구일자 없음

(85) 번역문제출일자 2012년02월09일

(86) 국제출원번호 PCT/US2010/041500

(87) 국제공개번호 WO 2011/006050

국제공개일자 2011년01월13일

(30) 우선권주장

61/224,658 2009년07월10일 미국(US)

61/225,013 2009년07월13일 미국(US)

(71) 출원인

퍼스트 솔라, 인코포레이티드

미국 오하이오 43551 페리스버그 세다 파크 블러

바드 28101

(72) 발명자

파월, 릭, 씨.

미국, 미시간주 48108, 앤 아버, 볼더 폰드 드라

이브 4497

글록클러, 마커스

미국, 오하이오주 43551, 페리스버그, 바스우드

드라이브 26652

(뒷면에 계속)

(74) 대리인

김영철, 김순영

전체 청구항 수 : 총 66 항

(54) 발명의 명칭 **아연을 포함하는 광전지 소자**

### (57) 요 약

광전지 제조 방법은 투명 전도성 산화물 스택 상에 카드뮴 설파이드 층을 증착하는 단계; 상기 카드뮴 설파이드 층 상에 아연 포함 층을 증착하는 단계; 및 상기 아연 포함 층 상에 카드뮴 텔루라이드 층을 증착하는 단계를 포함할 수 있다.

**대 표 도** - 도1

(72) 발명자

불러, 벤야민

미국, 오하이오주 43560, 실바니아, 노스 스톤 밀

로드 8733

샤오, 류이

미국, 오하이오주 43560, 실바니아, 스토니브룩

블러바드 9048

---

## 특허청구의 범위

### 청구항 1

투명 전도성 산화물 스택에 카드뮴 설파이드 층을 증착(depositing)하는 단계;

상기 카드뮴 설파이드 층에 아연 포함 층을 증착(depositing)하는 단계; 및

상기 아연 포함 층에 카드뮴 텔루라이드 층을 증착(depositing)하는 단계를 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 2

제 1 항에 있어서,

상기 방법은 카드뮴 아연 설파이드를 형성하는 단계를 더 포함하고, 상기 형성 단계는 하나 이상의 층을 어닐링 하는 것을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 3

제 1 항에 있어서,

하나 이상의 상기 증착 단계는 400°C 내지 800°C 범위의 온도에서 수행되는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 4

제 3 항에 있어서,

하나 이상의 상기 증착 단계는 500°C 내지 700°C 범위의 온도에서 수행되는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 5

제 4 항에 있어서,

하나 이상의 상기 증착 단계는 550°C 내지 650°C 범위의 온도에서 수행되는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 6

제 5 항에 있어서,

하나 이상의 상기 증착 단계는 550°C의 온도에서 수행되는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 7

제 5 항에 있어서,

하나 이상의 상기 증착 단계는 600°C의 온도에서 수행되는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 8

제 1 항에 있어서,

하나 이상의 상기 증착 단계는 증기 수송(transporting a vapor)을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 9

제 1 항에 있어서,

상기 방법은 카드뮴 설파이드 층 및 아연 포함 층을 어닐링 하는 것을 더 포함하는 것을 특징으로 하는 광전

지 제조 방법.

### 청구항 10

제 9 항에 있어서,

카드뮴 텔루라이드 층을 어닐링 하는 것을 더 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 11

제 9 항에 있어서,

상기 어닐링은 카드뮴 설파이드 층 및 아연 포함 층을 400°C 내지 800°C 범위의 온도에서 가열하는 것을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 12

제 11 항에 있어서,

상기 어닐링은 카드뮴 설파이드 층 및 아연 포함 층을 500°C 내지 700°C 범위의 온도에서 가열하는 것을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 13

제 12 항에 있어서,

상기 어닐링은 카드뮴 설파이드 층 및 아연 포함 층을 550°C 내지 650°C 범위의 온도에서 가열하는 것을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 14

제 13 항에 있어서,

상기 어닐링은 카드뮴 설파이드 층 및 아연 포함 층을 550°C 온도에서 가열하는 것을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 15

제 13 항에 있어서,

상기 어닐링은 카드뮴 설파이드 층 및 아연 포함 층을 650°C 온도에서 가열하는 것을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 16

제 1 항에 있어서,

상기 아연 포함 층은 아연 텔루라이드를 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 17

제 1 항에 있어서,

상기 아연 포함 층은 카드뮴 아연 텔루라이드를 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 18

제 17 항에 있어서,

상기 카드뮴 아연 텔루라이드는 2% 내지 10%의 아연 함량을 가지는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 19

제 18 항에 있어서,

상기 카드뮴 아연 텔루라이드는 4% 내지 8%의 아연 함량을 가지는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 20

제 19 항에 있어서,

상기 카드뮴 아연 텔루라이드는 5% 내지 6%의 아연 함량을 가지는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 21

제 17 항에 있어서,

하나 이상의 상기 중착 단계는 카드뮴 설파이드 층 및 카드뮴 아연 텔루라이드 사이의 교환 반응(exchange reaction)을 조절하는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 22

제 1 항에 있어서,

상기 아연 포함 층은 아연 설파이드를 포함하는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 23

제 1 항에 있어서,

상기 아연 포함 층은 아연 텔루라이드 층 위에 카드뮴 아연 텔루라이드 층을 포함하는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 24

제 23 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 아연 텔루라이드 층의 아연 농도보다 낮은 아연 농도를 포함하는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 25

제 23 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 2% 내지 10%의 아연 함량을 가지는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 26

제 25 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 4% 내지 8%의 아연 함량을 가지는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 27

제 26 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 5% 내지 6% 범위의 아연 함량을 가지는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 28

제 23 항에 있어서,

하나 이상의 상기 중착 단계는 카드뮴 설파이드 층 및 카드뮴 아연 텔루라이드 층 사이의 교환 반응(exchange reaction)을 조절하는 것을 특징으로 하는 광전지 제조 방법.

## 청구항 29

제 1 항에 있어서,

상기 투명 전도성 산화물 스택은 투명 전도성 산화물 층 상의 완충층(buffer layer)을 포함하는 것이고, 상기 투명 전도성 산화물 층은 하나 이상의 장벽층(barrier layer) 상에 위치하는 것을 특징으로 하는 광전지 제조

방법.

### 청구항 30

제 29 항에 있어서,

상기 방법은 제 1 기관상에 투명 전도성 산화물 스택을 증착(depositing)하는 것을 더 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 31

제 30 항에 있어서,

상기 제 1 기판은 유리를 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 32

제 31 항에 있어서,

상기 유리는 소다석회유리를 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 33

제 29 항에 있어서,

하나 이상의 장벽층 각각은 실리콘 질화물, 알루미늄 도핑 된 실리콘 질화물, 실리콘 산화물, 알루미늄 도핑 된 실리콘 산화물, 붕소 도핑 된 실리콘 질화물, 인 도핑 된 실리콘 질화물, 실리콘 산화물-질화물(silicon oxide-nitride) 및 주석 산화물로 이루어진 그룹에서 선택된 물질을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 34

제 29 항에 있어서,

상기 투명 전도성 산화물 층은 카드뮴 및 주석 층을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 35

제 29 항에 있어서,

상기 투명 전도성 산화물 층은 주석 산화물을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 36

제 29 항에 있어서,

상기 투명 전도성 산화물 층은 아연 산화물을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 37

제 29 항에 있어서,

상기 완충층은 아연 주석 산화물, 주석 산화물, 아연 산화물 및 아연 마그네슘 산화물로 이루어진 그룹에서 선택된 물질을 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 38

제 29 항에 있어서,

상기 방법은 투명 전도성 산화물 스택을 어닐링 하는 것을 더 포함하는 것을 특징으로 하는 광전지 제조 방법.

### 청구항 39

제 29 항에 있어서,

상기 방법은 카드뮴 텔루라이드 층 상에 후면 컨택트(back contact)를 증착(depositing)하는 것을 더 포함하는 것을 특징으로 하는 광전지 제조 방법.

#### 청구항 40

제 39 항에 있어서,

상기 방법은 후면 컨택트 상에 후면 서포트(back support)를 증착(depositing)하는 것을 더 포함하는 것을 특징으로 하는 광전지 제조 방법.

#### 청구항 41

카드뮴 아연 설파이드 층; 및

상기 카드뮴 아연 설파이드 층 상의 카드뮴 텔루라이드 층을 포함하고, 상기 카드뮴 아연 설파이드 층은 증가된 효율을 가지는 것을 특징으로 하는 광전지.

#### 청구항 42

제 41 항에 있어서,

상기 카드뮴 아연 설파이드 층은 고 결정도를 가지는 것을 특징으로 하는 광전지.

#### 청구항 43

제 41 항에 있어서,

상기 카드뮴 아연 설파이드 층은 결정도가 근사적으로 비결정질인 것을 특징으로 하는 광전지.

#### 청구항 44

제 41 항에 있어서,

상기 카드뮴 아연 설파이드 층은 20% 내지 40%의 아연을 가지는 것을 특징으로 하는 광전지.

#### 청구항 45

제 41 항에 있어서,

상기 광전지는 카드뮴 아연 설파이드 층 및 카드뮴 텔루라이드 층 사이에 카드뮴 아연 테루라이드 층을 더 포함하는 것을 특징으로 하는 광전지.

#### 청구항 46

제 45 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 2% 내지 10%의 아연 함량을 가지는 것을 특징으로 하는 광전지.

#### 청구항 47

제 46 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 4% 내지 8%의 아연 함량을 가지는 것을 특징으로 하는 광전지.

#### 청구항 48

제 47 항에 있어서,

상기 카드뮴 아연 텔루라이드 층은 5% 내지 6% 범위의 아연 함량을 가지는 것을 특징으로 하는 광전지.

#### 청구항 49

제 41 항에 있어서,

상기 광전지는 투명 전도성 산화물 스택을 더 포함하고, 카드뮴 아연 설파이드 층이 상기 투명 전도성 산화물

스택 상에 위치하는 것을 특징으로 하는 광전지.

### 청구항 50

제 49 항에 있어서,

상기 광전지는 제 1 기판을 더 포함하고, 투명 전도성 산화물 스택이 제 1 기판상에 위치하는 것을 특징으로 하는 광전지.

### 청구항 51

제 50 항에 있어서,

상기 제 1 기판은 유리를 포함하는 것을 특징으로 하는 광전지.

### 청구항 52

제 51 항에 있어서,

상기 유리는 소다석회유리를 포함하는 것을 특징으로 하는 광전지.

### 청구항 53

제 49 항에 있어서,

상기 투명 전도성 산화물 스택은 투명 전도성 산화물 층 상에 완충층(buffer layer)을 포함하고, 상기 투명 전도성 산화물 층은 하나 이상의 장벽층(barrier layer) 상에 위치하는 것을 특징으로 하는 광전지.

### 청구항 54

제 53 항에 있어서,

상기 투명 전도성 산화물 층은 카드뮴 스테네이트를 포함하는 것을 특징으로 하는 광전지.

### 청구항 55

제 53 항에 있어서,

상기 투명 전도성 산화물 층은 주석 산화물을 포함하는 것을 특징으로 하는 광전지.

### 청구항 56

제 53 항에 있어서,

상기 투명 전도성 산화물 층은 아연 산화물을 포함하는 것을 특징으로 하는 광전지.

### 청구항 57

제 53 항에 있어서,

상기 완충층은 아연 주석 산화물, 주석 산화물, 아연 산화물 및 아연 마그네슘 산화물로 이루어진 그룹에서 선택된 물질을 포함하는 것을 특징으로 하는 광전지.

### 청구항 58

제 53 항에 있어서,

하나 이상의 장벽층 각각은 실리콘 질화물, 알루미늄 도핑 된 실리콘 질화물, 실리콘 산화물, 알루미늄 도핑 된 실리콘 산화물, 봉소 도핑 된 실리콘 질화물, 인 도핑 된 실리콘 질화물, 실리콘 산화물-질화물(silicon oxide-nitride) 및 주석 산화물로 이루어진 그룹에서 선택된 물질을 포함하는 것을 특징으로 하는 광전지.

### 청구항 59

제 53 항에 있어서,

상기 광전지는 카드뮴 텔루라이드 층 상에 후면 컨택트(back contact)를 더 포함하는 것을 특징으로 하는 광

전지.

### 청구항 60

제 59 항에 있어서,

상기 광전지는 후면 컨택트 상에 후면 서포트(back support)를 더 포함하는 것을 특징으로 하는 광전지.

### 청구항 61

카드뮴 설파이드 층;

상기 카드뮴 설파이드 층 상의 아연 포함 층;

상기 아연 포함 층 상의 카드뮴 텔루라이드 층을 포함하는 것을 특징으로 하는 광전지.

### 청구항 62

제 61 항에 있어서,

상기 아연 포함 층은 아연 텔루라이드를 포함하는 것을 특징으로 하는 광전지.

### 청구항 63

제 61 항에 있어서,

상기 아연 포함 층은 아연 설파이드를 포함하는 것을 특징으로 하는 광전지.

### 청구항 64

제 61 항에 있어서,

상기 아연 포함 층은 카드뮴 아연 텔루라이드를 포함하는 것을 특징으로 하는 광전지.

### 청구항 65

제 61 항에 있어서,

상기 아연 포함 층은 아연 텔루라이드 층 상에 카드뮴 아연 텔루라이드 층을 포함하는 것을 특징으로 하는 광전지.

### 청구항 66

제 61 항에 있어서,

상기 광전지는 기판상에 투명 전도성 산화물 스택을 더 포함하고, 상기 투명 전도성 산화물 스택은 하나 이상의 장벽층(barrier layer) 상에 투명 전도성 산화물 층 및 상기 투명 전도성 산화물 층 상에 완충층(buffer layer)을 포함하며, 카드뮴 설파이드 층이 투명 전도성 산화물 스택 상에 위치하는 것을 특징으로 하는 광전지.

## 명세서

### 기술 분야

[0001]

본 발명은 아연을 포함하는 광전지 소자 및 반도체 층에 관한 것이다.

### 배경 기술

[0002]

광전지 소자를 제작하는 동안, 반도체 물질 층은 원도우 층 역할을 하는 하나의 층 및 흡수층 역할을 하는 두 번째 층을 가진 기판(substrate)에 적용될 수 있다. 상기 원도우 층은 흡수층에 태양 복사(solar radiation) 침투를 허용할 수 있으며, 광출력(optical power)이 전력으로 변환된다. 일부 광전지 소자는 또한 전하 전도체인 투명 박막을 사용할 수 있다.

[0003]

전도성 박막은 카드뮴 스테네이트(stannate) 산화물과 같은 투명 전도성 산화물을 포함하는 투명 전도성 층을

포함할 수 있다. 상기 투명 전도성 층은 빛이 반도체 윈도우 층을 통과하여 활성 광 흡수 물질에 이르도록 할 수 있고, 또한 광 생성 전하 운반체를 광 흡수 물질로부터 떨어지도록 운반하는 저항 접촉(ohmic contact)의 역할을 할 수도 있다. 후면 전극(back electrode)은 반도체 층의 후면(back surface)에서 형성될 수 있다.

### 도면의 간단한 설명

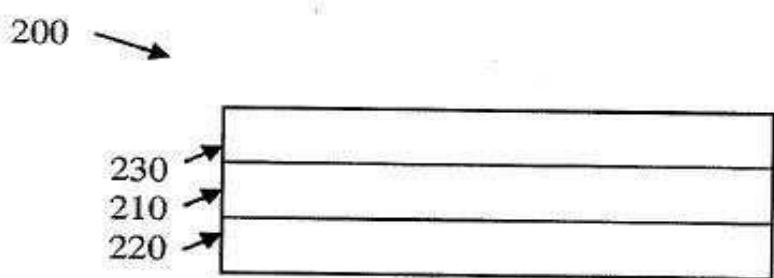

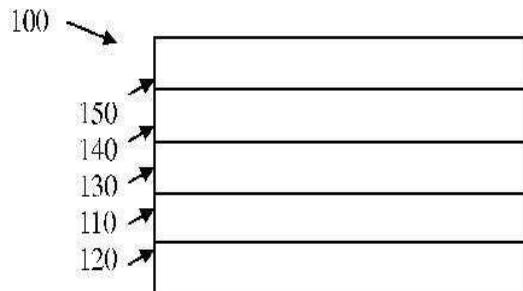

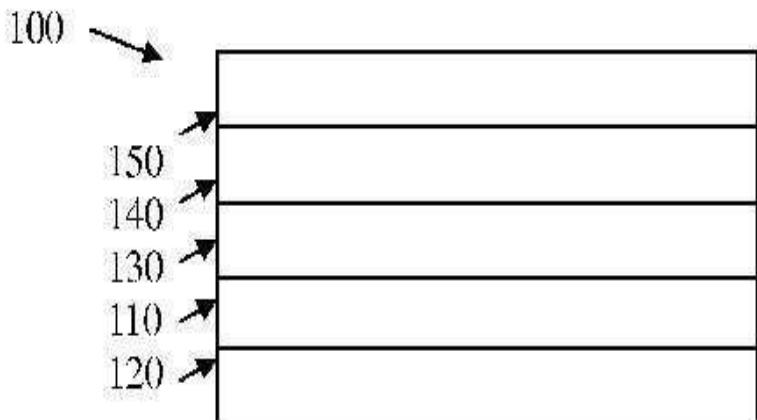

[0004] 도 1은 다층(multiple layers)을 가지는 광전지 소자의 도식이다.

도 2는 다층(multiple layers)을 가지는 광전지 소자의 도식이다.

### 발명을 실시하기 위한 구체적인 내용

[0005] 광전지는 기판 및 반도체 물질 층에 인접한 투명 전도성 산화물층을 포함할 수 있다. 반도체 물질 층은 n-타입 반도체 윈도우 층 및 p-타입 반도체 흡수층을 포함할 수 있는 이중층(bi-layer)을 포함할 수 있다. 상기 n-타입 윈도우 층 및 p-타입 흡수층은 전기장 형성을 위해 서로 접촉하여 위치할 수 있다. 광자는 n-타입 윈도우 층과 접촉 시 전자-정공 쌍을 자유롭게 할 수 있으며, 전자는 n쪽으로 정공은 p 쪽으로 보내게 된다. 전자는 외부 전류 경로를 통하여 p쪽으로 되돌아 흘러올 수 있다. 그 결과로 초래된 전자 흐름은 전류를 제공하고, 전기장으로 생성된 전압과 결합되어 전력을 형성한다. 이 결과로 광 에너지는 전력으로 전환된다.

[0006] 따라서 광전지는 카드뮴 설파이드(sulfide) 윈도우 층 및 카드뮴 텔루라이드(telluride) 흡수층을 포함할 수 있다. 카드뮴 아연 설파이드 층이 결합되어 밴드-갭(band-gap) 에너지를 넓히고, 카드뮴 아연 설파이드 및 상기 카드뮴 텔루라이드 사이의 밴드-오프셋(band-offset) 조율을 가능하게 할 수 있다. 상기 카드뮴 아연 설파이드 층은 아연을 포함하는 층의 증착(deposition)을 포함하는 다양한 테크닉을 통해 제조될 수 있다. 예를 들어, 카드뮴 아연 텔루라이드 층은 카드뮴 설파이드 층 위에 증착될 수 있고, 이에 따라, 예컨대 기상 수송 증착(vapor transport deposition)에서와 같이, 사후-증착 어닐링(post-deposition annealing) 단계를 통하여나 또는 고온에서 층들을 증착함으로써 아연이 카드뮴 설파이드 내로 분산되도록 할 수 있다. 유사하게, 아연 설파이드 층은 카드뮴 설파이드 층에 증착될 수 있고, 아연이 분산되도록 할 수 있다. 대안적으로, 카드뮴, 아연 및 황 분말은 함께 혼합될 수 있고 이어서 증착될 수 있다. 이러한 구조와 일치하게 제조된 소자(devices)는 증가된 개회로 전압 및 단락전류(short circuit current)를 보여준다. 그러나 아연의 함량만을 변화하여 상기 카드뮴 설파이드 층 및 카드뮴 아연 텔루라이드 층 사이의 교환 반응을 조절하는 것이 바람직하다.

[0007] 카드뮴 설파이드에서 카드뮴 아연 설파이드로의 반응을 조절하는 것은 구조의 초기 아연 분포를 다양하게 함으로써 얻어질 수 있다. 예를 들어, 상기 반응은 순수한 아연 텔루라이드 층을 증착시킴으로서 촉진될 수 있고 이어서 낮은 아연 퍼센티지의 카드뮴 아연 텔루라이드 층으로 층 증착을 수행함으로써 지속될 수 있다. 카드뮴 설파이드에서 카드뮴 아연 설파이드로의 전환은 어닐링 없이도 증착 과정 동안 일어날 수 있다. 상기 두 층의 조합은 전체적인 전환에 더 나은 조절성(controllability)을 가능하게 한다. 적합한 구조는 CdS/ZnTe/CdZnTe/CdTe, CdS/CdZnTe/CdTe, CdS/ZnTe/CdTe, CdS/ZnS/CdTe 및 그것들의 유도체 또는 변형을 포함한다.

[0008] 아연 텔루라이드 층의 층 두께는 충분한 아연이 제공되어 카드뮴 설파이드 층을 원하는 만큼 전환하는 정도가 될 수 있고, 만약 다른 아연 포함층이 존재하지 않거나 또는 원하는 정도 보다 적으면, 예를 들어, 카드뮴 아연 설파이드에서 20% 내지 약 40%의 아연인 경우, 5% 내지 약 10%의 아연 함량을 가지는 카드뮴 아연 텔루라이드 필름의 증착에 의하여 연속되도록 할 수 있다. 결정화도는 다양할 수 있고, 예를 들어, 카드뮴 아연 설파이드는 근사적으로 비결정질(nearly amorphous) 또는 고 결정성(highly crystalline) 일 수 있다.

[0009] 하나의 측면에서, 광전지 제조 방법은 투명 전도성 산화물 스택에 카드뮴 설파이드 층을 증착하는 단계; 상기 카드뮴 설파이드 층에 아연 포함 층을 증착하는 단계; 및 상기 아연 포함 층에 카드뮴 텔루라이드 층을 증착하는 단계를 포함할 수 있다.

[0010] 상기 방법은 카드뮴 아연 설파이드 형성 단계를 포함할 수 있고, 여기서 상기 형성 단계는 하나 또는 그 이상의 층을 어닐링 하는 것을 포함한다. 하나 이상의 상기 증착 단계들은 약 400°C 내지 약 800°C, 약 500°C 내지 약 700°C 또는 약 550°C 내지 약 650°C 범위의 온도에서 수행될 수 있다. 하나 이상의 상기 증착 단계들은 약 550°C 또는 약 600°C에서 수행될 수 있다. 하나 이상의 상기 증착 단계들은 기상 수송(transporting a vapor)을 포함할 수 있다. 상기 방법은 카드뮴 설파이드 층 및 아연 포함 층을 어닐링 하는 것을 포함할 수 있다. 상기 방법은 카드뮴 텔루라이드 층을 어닐링 하는 것을 포함할 수 있다. 상기 어닐링은 카드뮴 설파이드

드 층 및 아연 포함 층을 약 400°C 내지 약 800°C, 약 500°C 내지 약 700°C 또는 약 550°C 내지 약 650°C 범위의 온도로 가열하는 것을 포함할 수 있다. 상기 어닐링은 카드뮴 설파이드 층 및 아연 포함 층을 약 550°C 또는 약 650°C에서 가열하는 것을 포함할 수 있다. 상기 아연 포함 층은 아연 텔루라이드 또는 카드뮴 아연 텔루라이드를 포함할 수 있다. 상기 카드뮴 아연 텔루라이드는 약 2% 내지 약 10%의 아연 함량을 가질 수 있다. 상기 카드뮴 아연 텔루라이드는 약 4% 내지 약 8% 범위의 아연 함량을 가질 수 있다. 상기 카드뮴 아연 텔루라이드는 약 5% 내지 약 6% 범위의 아연 함량을 가질 수 있다. 하나 이상의 중착 단계들은 카드뮴 설파이드 층 및 카드뮴 아연 텔루라이드 사이의 교환 반응을 조절할 수 있다. 상기 아연 포함 층은 또한 아연 설파이드를 포함할 수 있다. 상기 아연 포함 층은 아연 텔루라이드 층 상의 카드뮴 아연 텔루라이드 층을 포함할 수 있다. 상기 카드뮴 아연 텔루라이드 층은 아연 텔루라이드 층보다 작은 아연 농도를 포함할 수 있다. 상기 카드뮴 아연 텔루라이드 층은 약 2% 내지 약 10%의 아연 함량을 가질 수 있다. 상기 카드뮴 아연 텔루라이드 층은 약 4% 내지 약 8% 범위의 아연 함량을 가질 수 있다. 상기 카드뮴 아연 텔루라이드 층은 약 5% 내지 약 6% 범위의 아연 함량을 가질 수 있다. 하나 이상의 중착 단계들은 상기 카드뮴 설파이드 층 및 카드뮴 아연 텔루라이드 층 사이의 교환반응을 조절할 수 있다. 상기 투명 전도성 산화물 스택은 투명 전도성 산화물 층 위에 완충층(buffer layer)을 포함할 수 있고, 여기서 투명 전도성 산화물 층은 하나 이상의 장벽층(barrier layers) 위에 위치된다.

[0011] 상기 방법은 제 1 기판 위에 상기 투명 전도성 산화물 스택을 중착하는 것을 포함할 수 있다. 제 1 기판은 유리 예를 들어, 소다석회유리(soda-lime glass)를 포함할 수 있다. 하나 이상의 장벽층 각각은 실리콘 질화물, 알루미늄 도핑 된 실리콘 질화물, 실리콘 산화물, 알루미늄 도핑 된 실리콘 산화물, 봉소 도핑 된 실리콘 질화물, 인 도핑 된 실리콘 질화물, 실리콘 산화물 질화물(silicon oxide-nitride) 또는 주석 산화물을 포함할 수 있다. 상기 투명 전도성 산화물 층은 카드뮴 및 주석, 주석 산화물 또는 아연 산화물 층을 포함할 수 있다. 상기 완충층은 아연 주석 산화물, 주석 산화물, 아연 산화물 또는 아연 마그네슘 산화물을 포함할 수 있다. 상기 방법은 상기 투명 전도성 산화물 스택을 어닐링 하는 것을 포함할 수 있다. 상기 방법은 카드뮴 텔루라이드 층 위에 후면 컨택트(back contact)를 중착하는 것을 포함할 수 있다. 상기 방법은 상기 후면 컨택트(back contact) 위에 후면 서포트(back support)를 중착하는 것을 포함할 수 있다.

[0012] 하나의 측면에서 광전지는 카드뮴 아연 설파이드 층 및 카드뮴 아연 설파이드 층 위에 카드뮴 텔루라이드 층을 포함할 수 있고, 여기서 카드뮴 아연 설파이드 층은 증가된 효율성을 가진다.

[0013] 상기 카드뮴 아연 설파이드 층의 결정성은 높거나 또는 거의 비결정성일 수 있다. 상기 카드뮴 아연 설파이드 층은 약 20% 내지 약 40%의 아연을 가질 수 있다. 상기 광전지는 카드뮴 아연 설파이드 층 및 카드뮴 텔루라이드 층 사이에 카드뮴 아연 텔루라이드 층을 포함할 수 있다. 상기 카드뮴 아연 텔루라이드 층은 약 2% 내지 약 10%의 아연 함량을 가질 수 있다. 상기 카드뮴 아연 텔루라이드 층은 약 4% 내지 약 8% 범위의 아연 함량을 가질 수 있다. 상기 카드뮴 아연 텔루라이드 층은 약 5% 내지 약 6% 범위의 아연 함량을 가질 수 있다. 상기 광전지는 투명 전도성 산화물 스택을 포함할 수 있고, 여기서 카드뮴 아연 설파이드 층은 투명 전도성 산화물 스택 위에 위치한다. 상기 광전지는 제 1 기판을 포함할 수 있고, 여기서 투명 전도성 산화물 스택은 제 1 기판 위에 위치한다. 제 1 기판은 유리 예를 들어, 소다석회유리를 포함할 수 있다.

[0014] 상기 투명 전도성 산화물 스택은 투명 전도성 산화물 층 위에 완충층을 포함할 수 있고, 여기서 투명 전도성 산화물 층은 하나 이상의 장벽층 상에 위치한다. 상기 투명 전도성 산화물 층은 카드뮴 스테네이트, 주석 산화물 또는 아연 산화물을 포함할 수 있다. 상기 완충층은 아연 주석 산화물, 주석 산화물, 아연 산화물 또는 아연 마그네슘 산화물을 포함할 수 있다. 하나 이상의 장벽층 각각은 실리콘 질화물, 알루미늄 도핑 된 실리콘 질화물, 실리콘 산화물, 알루미늄 도핑 된 실리콘 산화물, 봉소 도핑 된 실리콘 질화물, 인 도핑 된 실리콘 질화물, 실리콘 산화물 질화물(silicon oxide-nitride) 또는 주석 산화물을 포함할 수 있다. 상기 광전지는 카드뮴 텔루라이드 층 상에 후면 컨택트(back contact), 그리고 상기 후면 컨택트 상에 후면 서포트(back support)를 포함할 수 있다.

[0015] 하나의 측면에서, 광전지는 또한 카드뮴 설파이드 층, 상기 카드뮴 설파이드 층 상에 아연 포함 층, 상기 아연 포함 층 상에 카드뮴 텔루라이드 층을 포함할 수 있다.

[0016] 상기 아연 포함 층은 아연 텔루라이드, 아연 설파이드, 카드뮴 아연 텔루라이드, 또는 아연 텔루라이드 층 위에 카드뮴 아연 텔루라이드 층을 포함할 수 있다. 상기 광전지는 기판 위에 투명 전도성 산화물 스택을 포함할 수 있고, 여기서 투명 전도성 산화물 스택은 하나 이상의 장벽층 상에 투명 전도성 산화물 층 및 상기 투명 전도성 산화물 층 상에 완충층을 포함하고, 여기서 카드뮴 설파이드 층은 투명 전도성 산화물 스택 상에

위치한다.

[0017] 도 1을 참조하면, 광전지(100)는 카드뮴 설파이드 층(110)을 포함할 수 있다. 상기 카드뮴 설파이드 층(110)은 기판(120) 위에 증착될 수 있다. 상기 기판(120)은 유리 예를 들어, 소다석회유리를 포함할 수 있다. 아연 포함 층은 카드뮴 설파이드 층(110) 위에 증착될 수 있다. 예를 들어, 아연 텔루라이드 층(130)은 카드뮴 설파이드 층(110) 위에 증착될 수 있다. 다른 아연 포함 층이 또한 카드뮴 설파이드 층(110)에 증착될 수 있으며, 카드뮴 아연 텔루라이드 및 아연 설파이드를 포함한다. 카드뮴 아연 텔루라이드 층(140)은 아연 텔루라이드 층(130) 위에 증착될 수 있다. 상기 층은 고온 예를 들어, 카드뮴 아연 설파이드를 형성하도록 아연의 분산을 용이하게 하도록 약 380°C 보다 높은 온도에서 증착될 수 있다. 예를 들어, 소자(device) 층은 약 400°C 또는 약 420°C에서 증착될 수 있다. 상기 층은 예를 들어 약 400°C 내지 약 800°C, 약 500°C 내지 약 700°C 또는 약 550°C 내지 약 650°C를 포함하는 적합한 온도 범위에서 증착될 수 있다. 예를 들어, 상기 층은 약 550°C에서 증착될 수 있다. 카드뮴 아연 텔루라이드 층(140)과 관련하여, 어떠한 퍼센티지의 아연도 적용 가능하다. 예를 들어, 약 0.1%의 아연은 성능을 향상시킬 것이다. 약 0 내지 약 0.30 범위(즉, 0 내지 약 15% 아연)가 허용 가능하지만 약 0.10 내지 약 0.12 범위의 x를 가진  $Cd_{1-x}Zn_x$ 의 구성이 특히 유리하다는 것이 증명되었다. 상기 카드뮴 아연 텔루라이드 층을 위한 아연의 최적 비율은 증착의 세부사항(즉, 온도 프로파일)에 따라 다양할 수 있다는 것이 주목되어야 한다. 카드뮴 텔루라이드 층(150)은 카드뮴 아연 텔루라이드 층(140) 상에, 또는 이전의 아연 포함 층 바로 위에 증착될 수 있다. 이러한 다층 구조는 카드뮴 텔루라이드 층(150)의 증착 이전 또는 이후에 어닐링 될 수 있다.

[0018] 상기 어닐링은 적합한 조건 하에서 수행될 수 있다. 예를 들어, 상기 어닐링은 어닐링의 측면을 조절하기 위해 선택된 가스 예를 들어, 질소 가스의 존재 하에서 수행할 수 있다. 상기 어닐링은 적합한 압력 하 예를 들어, 저 진공 또는 약  $0.01Pa(10^{-4} \text{ Torr})$ 의 감소된 압력 하에서 수행할 수 있다. 상기 어닐링은 또한 어떠한 적합한 온도 또는 온도 범위 예를 들어, 약 380°C 보다 높은 온도에서 수행될 수 있다. 상기 다층 구조는 약 400°C 내지 약 800°C, 약 500°C 내지 약 700°C 또는 약 550°C 내지 약 650°C에서 어닐링 될 수 있다. 상기 구조는 또한 적합한 지속시간 예를 들어, 약 10 내지 약 25분 또는 약 15 내지 약 20분 동안 어닐링 될 수 있다.

[0019] 다양한 증착 테크닉이 이상에서 기술한 층들의 증착에 이용 가능하며, 예를 들어, 저압화학기상증착법(low pressure chemical vapor deposition), 상압화학기상증착법(atmospheric pressure chemical vapor deposition), 플라즈마화학기상증착법(plasma-enhanced chemical vapor deposition), 열화학기상증착법(thermal chemical vapor deposition), DC 또는 AC 스퍼터링(sputtering), 스핀-온 증착 spin-on deposition 방법 및 분무 열분해(spray-pyrolysis)를 포함한다. 예를 들어, 상기 카드뮴 설파이드 및 아연 설파이드 층은 스퍼터링 될 수 있다. 상기 카드뮴 아연 텔루라이드, 카드뮴 설파이드, 카드뮴 텔루라이드 및 아연 텔루라이드는 기상 수송 증착(vapor transport deposition) 방법을 사용하여 모두 증착될 수 있다.

[0020] 이상에서 기술된 구조 내의 층들로부터의 하나 또는 그 이상의 화학물질 분산이 도 2에 나타난 바와 같은 광전지(200)를 형성하게 할 수 있다. 예를 들어, 상기 아연 텔루라이드 층(130)으로부터의 아연이 카드뮴 설파이드 층(110)으로 분산되어 카드뮴 아연 설파이드를 형성할 수 있다. 도 1에 나타난 바와 같은 증착된 아연 텔루라이드의 두께는 카드뮴 설파이드에서 카드뮴 아연 설파이드로의 전환을 조절하는 것에 의해 달라질 수 있다. 도 2를 참조하면, 광전지(200)는 카드뮴 아연 설파이드 층(210)을 포함할 수 있다. 카드뮴 아연 설파이드 층(210)은 적합한 양의 아연을 포함할 수 있다. 테스트는 아연 비율이 0 보다 많으면 전달(transmission) 및 밴드 얼라인먼트(band alignment)를 증가시키는 것에 이로울 수 있다는 것을 보여준다. 20% 내지 약 40% 범위(즉,  $Cd_{0.6}Zn_{0.4}S$ 에서  $Cd_{0.2}Zn_{0.8}S$ 까지 범위의 조성물)의 아연 퍼센티지를 가진 조성물은 특히 높은 효율을 보인다. 상기 카드뮴 아연 설파이드 층(210)은 기판(220) 위에 위치할 수 있다. 상기 기판(220)은 유리 예를 들어, 소다석회유리를 포함할 수 있다. 카드뮴 텔루라이드 층(230)은 카드뮴 아연 설파이드 층(110) 위에 위치할 수 있다. 하나의 변형예에서는, 형성된 구조는 카드뮴 아연 설파이드 및 카드뮴 텔루라이드 사이에 카드뮴 아연 텔루라이드를 포함할 수 있다.

[0021] 각각의 층은, 필요에 따라 각 스테이션에 있는 진공 밀봉된 증착 챔버 및 별도의 증착 가스 공급부를 가지는 제조 라인의 다른 증착 스테이션에서 증착될 수 있다. 상기 기판은 증착 스테이션에서 증착 스테이션으로 모든 원하는 층이 증착 될 때까지 롤링 컨베이어를 통해 이송될 수 있다. 맨 위의 기판 층은 샌드위치를 형성하고 광전지를 완성하도록 최상층의 위에 위치될 수 있다.

[0022] 광전지 소자의 제조에 있어서 반도체 층의 증착은 각각 참조로서 전체 내용이 여기에 결합되어 있는 예컨대

미국 특허 제5,248,349호, 제5,372,646호, 제5,470,397호, 제5,536,333호, 제5,945,163호, 제6,037,241호 및 제6,444,043호에 설명되어 있다. 상기 증착은 소스(source)에서 기판으로 증기를 수송하는 것 또는 닫힌 계에서 고체를 승화시키는 것을 포함할 수 있다. 광전지 제조를 위한 장치는 컨베이어 예를 들어, 롤러가 있는 롤 컨베이어를 포함할 수 있다. 다른 종류의 컨베이어도 가능하다. 상기 컨베이어는 기판의 노출된 표면 위에 물질 증을 증착하기 위해서 기판을 하나 이상의 일련의 증착 스테이션으로 수송한다. 컨베이어는 여기에 참조로 결합된 미국 출원 제11/692,667호에 기술되어 있다.

[0023] 상기 증착 챔버는 약 380°C 내지 약 700°C, 예를 들어 약 450°C 내지 약 550°C, 약 550°C 내지 약 650°C, 약 570°C 내지 약 600°C, 약 600°C 내지 약 640°C 또는 기타 적합한 온도 범위의 공정 온도에 도달하도록 가열될 수 있다. 상기 증착 챔버는 증착 증기 공급부에 연결된 증착 분배기(distributor)를 포함한다. 상기 분배기는 다양한 종의 증착을 위한 다중 증기 공급부에 연결될 수 있거나, 또는 기판이 자신의 증기 분배기 및 공급부와 함께 다중 및 다양한 증착 스테이션을 통하여 이동될 수 있다. 상기 분배기는 증기 공급의 일정한 분배를 용이하게 하기 위한 다양한 노즐 구조(geometries)를 가지는 분무 노즐 형태일 수 있다.

[0024] 상기 원도우 층 및 흡수층은 예를 들어 ZnO, ZnS, ZnSe, ZnTe, CdO, CdS, CdSe, CdTe, MgO, MgS, MgSe, MgTe, HgO, HgS, HgSe, HgTe, MnO, MnS, MnTe, AlN, AlP, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InN, InP, InAs, InSb, TiN, TiP, TiAs, TiSb 또는 그것들의 혼합물과 같은 II-IV, III-V 또는 IV 측 반도체와 같은 바이너리 반도체(binary semiconductor)를 포함할 수 있다. 원도우 층 및 흡수층의 예는 CdTe층으로 코팅된 CdS층이다. 최상층은 반도체 층을 커버할 수 있다. 상기 최상층은 예를 들어, 알루미늄, 몰리브데늄, 크로뮴, 코발트, 니켈, 티타늄, 텉스텐 또는 그것들의 합금과 같은 금속을 포함할 수 있다. 상기 최상층은 또한 금속 산화물 또는 금속 질화물 또는 그것들의 합금을 포함할 수 있다.

[0025] 이상에서 설명한 바와 같이, 광전지는 기판의 표면 위에 투명 전도성 층, 제 1 반도체 층, 반도체 층을 지지하는 기판 및 반도체 층에 접촉하는 금속층을 포함할 수 있다.

[0026] 상기 광전지의 바닥층은 투명 전도성 층일 수 있다. 얇은 캐핑(capping) 층은 투명 전도성 층의 최상부이고 적어도 부분적으로 투명 전도성 층을 커버할 수 있다. 그 다음 증착된 층은 원도우 층 역할을 할 수 있는 제 1 반도체 층이고, 투명 전도성 층 및 캐핑층의 사용에 따라 더 얇아질 수 있다. 증착된 그 다음 층은 흡수층 역할을 하는 제 2 반도체 층이다. 필요에 따라 도판트를 포함하는 층과 같은 다른 층들이 증착되거나 또는 제조 공정 동안 기판상에 위치할 수 있다.

[0027] 상기 바닥층은 투명 전도성 층일 수 있으며, 예를 들어, 카드뮴 스테네이트 산화물, 주석 산화물 또는 불소 도핑 된 주석 산화물과 같은 투명 전도성 산화물일 수 있다. 고온에서 투명 전도성 산화물 층 위에 반도체 층을 직접 증착하는 것은 광전지 소자의 안정성 및 성능에 부정적인 영향을 미치는 반응들을 일으킬 수 있다. 실리콘 이산화물, 디알루미늄 삼산화물, 티타늄 이산화물, 디보론 삼산화물 및 기타 유사한 것들과 같은 높은 화학적 안정성을 가진 물질의 캐핑층 증착은 소자의 성능 및 안정성에 대한 상기 반응들의 영향을 상당히 감소시킬 수 있다. 상기 캐핑층의 두께는 사용된 물질의 높은 저항성 때문에 최소화되어야 한다. 그렇지 않으면, 원하는 전류 흐름에 역행하는 저항성 블록(resistive block)이 일어날 수 있다. 캐핑층은 원도우 층의 증착을 돋고 원도우 층이 얇은 크로스-섹션을 갖도록 하는 표면의 불균일(irregularities)을 채움으로써 투명 전도성 산화물 층의 표면 거칠기를 감소시킬 수 있다. 상기 감소된 표면 거칠기는 원도우 층의 균일성을 향상시키는데 도움을 줄 수 있다. 광전지에서 캐핑층을 포함하는 것의 다른 장점은 광학적 명확성(optical clarity)을 향상시킬 수 있고, 밴드 갭의 일관성을 향상시킬 수 있으며, 접합 지점(junction)에서 더 나은 필드 세기(field strength)를 제공하고, 개회로전압 손실에 의해 측정되는 더 나은 소자 효율성을 제공하는 것을 포함할 수 있다. 캐핑층은, 예를 들어, 여기에 그 전체 내용이 참조로 결합된 미국 특허 출원 공개 제20050257824호에 설명되어 있다.

[0028] 광전지의 바닥층은 투명 전도성 층일 수 있다. 얇은 캐핑층은 투명 전도성 층의 최상부이고 적어도 부분적으로는 투명 전도성 층을 커버할 수 있다. 증착된 그 다음 층은 원도우 층 역할을 할 수 있고, 투명 전도성 층 및 캐핑층의 사용에 따라 더 얇아질 수 있는 제 1 반도체 층이다. 증착된 그 다음 층은 흡수층 역할을 하는 제 2 반도체 층이다. 필요에 따라 도판트를 포함하는 층과 같은 다른 층들이 증착되거나 또는 제조 공정 동안 기판상에 위치할 수 있다.

[0029] 상기 제 1 반도체 층은 제 2 반도체 층을 위한 원도우 층 역할을 할 수 있다. 상기 제 1 반도체 층은 제 2 반도체 층보다 얇을 수 있다. 더 얇기 때문에, 제 1 반도체 층은 더 단파장의 입사광을 제 2 반도체 층에 대하여 더 많이 침투하게 할 수 있다.

[0030] 제 1 반도체 층은 예를 들어, ZnO, ZnS, ZnSe, ZnTe, CdO, CdS, CdSe, CdTe, MgO, MgS, MgSe, MgTe, HgO, HgS, HgSe, HgTe, MnO, MnS, MnTe, AlN, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InN, InP, InAs, InSb, TIN, TIP, TlAs, TlSb 또는 그것들의 합금 또는 혼합물과 같은 II-IV, III-V 또는 IV 족의 반도체일 수 있다. 이는 바이너리 반도체(binary semiconductor)일 수 있으며, 예를 들어 CdS 일 수 있다. 제 2 반도체 층은 제 1 반도체 층 위에 증착될 수 있다. 제 2 반도체는 제 1 반도체 층이 원도우 층 역할을 할 때 입사광에 대한 흡수층 역할을 할 수 있다. 제 1 반도체 층에 유사하게 제 2 반도체 층 또한 예를 들어, ZnO, ZnS, ZnSe, ZnTe, CdO, CdS, CdSe, CdTe, MgO, MgS, MgSe, MgTe, HgO, HgS, HgSe, HgTe, MnO, MnS, MnTe, AlN, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InN, InP, InAs, InSb, TIN, TIP, TlAs, TlSb 또는 그것들의 혼합물과 같은 II-IV, III-V 또는 IV 족 반도체일 수 있다.

[0031] 제 2 반도체 층은 제 1 반도체 층 위에 증착될 수 있다. 캐핑층은 제 1 반도체 층으로부터 투명 전도성 층을 전기적 및 화학적으로 고립시키는 역할을 하며 성능 및 안정성에 부정적인 영향을 줄 수 있는 고온 발생 반응을 방지할 수 있다. 상기 투명 전도성 층은 기판에 증착될 수 있다.

[0032] 여기에 설명된 방법을 사용하여 제조한 광전지 소자/전지는 하나 이상의 광전지 모듈에 포함될 수 있다. 상기 모듈은 전기를 생산하기 위한 다양한 시스템에 결합될 수 있다. 예를 들어, 광전지는 광전류를 생산하기 위해 광선(beam of light)로 조사될(illuminated) 수 있다. 상기 광전류는 모아지고 직류(DC)에서 교류(AC)로 전환되고, 파워그리드로 분배된다. 예를 들어 400nm초과 또는 700nm 미만 (예를 들어, 자외선)을 포함하는 적합한 파장의 빛이 광전류를 생산하기 위해 광전지로 향할 수 있다. 하나의 광전지로부터 생산된 광전류는 다른 광전지로부터 생산된 광전류와 결합될 수 있다. 예를 들어, 상기 광전지는 광전지 어레이의 하나 이상의 광전지 모듈의 일부분일 수 있고, 이로부터 집합 전류(aggregate current)가 동력화되고(harnessed) 분배될 수 있다.

[0033] 이상 설명된 구현 예는 예시적인 것으로서 제공된다. 상기 제공된 예시들이 특정한 측면에서 수정될 수 있지만 여전히 청구항의 범위 내에 있다는 것이 이해될 것이다. 본 발명이 상기 바람직한 구현 예를 참조하여 설명되었지만, 다른 구현 예들도 청구항의 범위 내에 속하는 것임이 이해될 것이다.

## 도면

### 도면1

도면2