(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-331095

(P2007-331095A)

(43) 公開日 平成19年12月27日(2007.12.27)

| (51) Int.CI.         | F 1        | テーマコード (参考) |

|----------------------|------------|-------------|

| B81C 3/00 (2006.01)  | B81C 3/00  | 2H141       |

| B81B 3/00 (2006.01)  | B81B 3/00  | 3C081       |

| G02B 26/08 (2006.01) | G02B 26/08 | E           |

| H01H 59/00 (2006.01) | H01H 59/00 |             |

| H01H 49/00 (2006.01) | H01H 49/00 | L           |

審査請求 未請求 請求項の数 16 O L (全 68 頁) 最終頁に続く

|              |                              |            |                                                                                                     |

|--------------|------------------------------|------------|-----------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-131665 (P2007-131665) | (71) 出願人   | 000153878                                                                                           |

| (22) 出願日     | 平成19年5月17日 (2007.5.17)       |            | 株式会社半導体エネルギー研究所                                                                                     |

| (31) 優先権主張番号 | 特願2006-138835 (P2006-138835) |            | 神奈川県厚木市長谷398番地                                                                                      |

| (32) 優先日     | 平成18年5月18日 (2006.5.18)       | (74) 代理人   | 100108741                                                                                           |

| (33) 優先権主張国  | 日本国 (JP)                     |            | 弁理士 渡邊 順之                                                                                           |

|              |                              | (72) 発明者   | 山口 真弓<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                        |

|              |                              | (72) 発明者   | 泉 小波<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                         |

|              |                              | F ターム (参考) | 2H141 MA02 MA12 MB22 MB23 MB29<br>MB56 MC06 MC09 MD04 MD12<br>MD20 MF26 MZ03 MZ06 MZ22<br>MZ24 MZ28 |

|              |                              |            | 最終頁に続く                                                                                              |

(54) 【発明の名称】微小構造体、マイクロマシンおよび半導体装置、ならびに微小構造体およびマイクロマシンの作製方法

## (57) 【要約】

【課題】犠牲層エッチングを行わずに微小構造体及びマイクロマシンを作製する。

【解決手段】基板101上に剥離層102を形成し、剥離層102上に可動電極となる層103を形成する。剥離層102を境界に、可動電極となる層103を基板から剥離する。別の基板105に固定電極となる層106を形成する。可動電極となる層103と固定電極となる層106が向かい合うように、部分的に設けられたスペーサ層108を挟んで、可動電極となる層103を基板105に固定する。これにより、犠牲層エッチングを行わずに、層103と層106の間に空間部分109が形成される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1の仮基板上に剥離層を形成し、

前記剥離層上に第1の層を形成し、

前記第1の層を、前記剥離層の一部が露出するように加工し、

前記第1の層上に、接着層を介して第2の仮基板を貼り合わせ、

前記第1の層を、前記第1の仮基板から前記第2の仮基板へ移し、

第1の本基板に、選択的にスペーサ層を形成し、

前記第1の層と前記第1の本基板とを、前記スペーサ層を挟んで向かい合うように接着し、

前記第2の仮基板と前記第1の層とを分離させることを特徴とする微小構造体の作製方法。

10

**【請求項 2】**

第1の仮基板上に剥離層を形成し、

前記剥離層上に第1の層を形成し、

前記第1の層を、前記剥離層の一部が露出するように加工し、

前記第1の層上に、接着層を介して第2の仮基板を貼り合わせ、

前記第1の層を、前記第1の仮基板から前記第2の仮基板へ移し、

第1の本基板に選択的に第1のスペーサ層を形成し、

第2の本基板に、選択的に第2のスペーサ層を形成し、

前記第1の層と前記第1の本基板とを、前記第1のスペーサ層を挟んで向かい合うように接着し、

前記第2の仮基板と前記第1の層とを分離させ、

前記第1の層と前記第2の本基板とを、前記第2のスペーサ層を挟んで向かい合うように接着することを特徴とする微小構造体の作製方法。

20

**【請求項 3】**

請求項2において、

前記第2の本基板に、第3の層が設けられていることを特徴とする微小構造体の作製方法。

30

**【請求項 4】**

請求項1乃至請求項3のいずれか一において、

前記第1の本基板に、第2の層が設けられていることを特徴とする微小構造体の作製方法。

40

**【請求項 5】**

第1の仮基板上に剥離層を形成し、

前記剥離層上に第1の層を形成し、

前記第1の層を、前記剥離層の一部が露出するように加工し、

前記第1の層上に、接着層を介して第2の仮基板を貼り合わせ、

前記第1の層を、前記第1の仮基板から前記第2の仮基板へ移し、

第1の本基板上に半導体素子を有する層を形成し、

前記半導体素子を有する層に、選択的にスペーサ層を形成し、

前記第1の層と前記第1の本基板とを、前記スペーサ層を挟んで向かい合うように接着し、

前記第2の仮基板と前記第1の層とを分離させることを特徴とするマイクロマシンの作製方法。

**【請求項 6】**

第1の仮基板上に剥離層を形成し、

前記剥離層上に第1の層を形成し、

前記第1の層を、前記剥離層の一部が露出するように加工し、

前記第1の層上に、接着層を介して第2の仮基板を貼り合わせ、

50

前記第1の層を、前記第1の仮基板から前記第2の仮基板へ移し、

前記半導体素子を有する層に、選択的に第1のスペーサ層を形成し、

第2の本基板に、選択的に第2のスペーサ層を形成し、

前記第1の層と前記第1の本基板とを、前記第1のスペーサ層を挟んで向かい合うよう

に接着し、

前記第2の仮基板と前記第1の層とを分離させ、

前記第1の層と前記第2の本基板とを、前記第2のスペーサ層を挟んで向かい合うよう

に接着することを特徴とする微小構造体の作製方法。

#### 【請求項7】

第1の本基板上に選択的に設けられた第1のスペーサ層と、前記第1のスペーサ層上に 10

設けられた第1の層とを有し、

前記第1の層には、前記第1のスペーサ層上に設けられた固定されている部分と、前記

スペーサがないところに設けられた可動する部分があり、前記固定されている部分と前

記可動する部分とは、少なくとも一部が物理的に接続しており、

前記第1の層は、前記第1の本基板と前記可動する部分との間に空間があることを特徴

とする微小構造体。

#### 【請求項8】

第1の本基板上に選択的に設けられた第1のスペーサ層と、前記第1のスペーサ層上に 20

設けられた第1の層と、前記第1の層に選択的に設けられた第2のスペーサ層と、前記第

2のスペーサ層上に設けられた第2の本基板とを有し、

前記第1の層には、前記第1のスペーサ層上に設けられた固定されている部分と、前記

第1のスペーサ層がないところに設けられた可動する部分があり、前記固定されている

部分と前記可動する部分とは、少なくとも一部が物理的に接続しており、

前記第1の層は、前記第1の本基板と前記可動する部分との間及び前記第2の本基板と

前記可動する部分との間に空間があり、

前記可動する部分は、前記第1の本基板に対して垂直な方向又は平行な方向に変位する

ことを特徴とする微小構造体。

#### 【請求項9】

請求項8において、

前記第2の本基板は、前記第1の層に向かい合う様に設けられた第3の層を有すること 30

を特徴とする微小構造体。

#### 【請求項10】

請求項7乃至請求項9のいずれか一において、

前記第1の本基板は、前記第1の層に向かい合うように設けられた第2の層を有するこ

とを特徴とする微小構造体。

#### 【請求項11】

請求項7乃至請求項10において、

前記第1のスペーサ層は、有機材料で形成されていることを特徴とする微小構造体。

#### 【請求項12】

請求項7又は請求項11において、

前記第1の層は、導電性を有する材料で形成されていることを特徴とする微小構造体。 40

#### 【請求項13】

請求項7乃至請求項12のいずれか一において、

前記第1のスペーサ層は、前記第1の層とは異なる材料を用いて形成されていることを

特徴とする微小構造体。

#### 【請求項14】

請求項7乃至請求項13のいずれか一において、

前記可動する部分が変位することによって、機械的な変化を電気的な変化に変換する、

又は電気的な変化を機械的な変化に変換することを特徴とする微小構造体。

#### 【請求項15】

10

20

30

40

50

第1の本基板上に設けられた電気回路及び前記電気回路と電気的に接続された微小構造体を有し、

前記電気回路は、前記第1の本基板上に選択的に設けられた第1のスペーサ層及び前記第1のスペーサ層上に設けられた第1の層を有し、

前記第1の層には、前記第1のスペーサ層上に設けられた固定されている部分と、前記第1のスペーサ層がないところに設けられた可動する部分とがあり、前記固定されている部分と前記可動する部分とは、少なくとも一部が物理的に接続しており、

前記第1の層は、前記第1の本基板と前記可動する部分との間に空間があり、

前記可動する部分は、前記第1の本基板に対して垂直な方向に変位することを特徴とするマイクロマシン。

10

#### 【請求項 1 6】

第1の本基板上に設けられた電気回路及び前記電気回路と電気的に接続された微小構造体を有し、

前記電気回路は半導体素子を有し、

前記微小構造体は、前記第1の本基板上に選択的に設けられた第1のスペーサ層と、前記第1のスペーサ層上に設けられた第1の層と、前記第1の層に選択的に設けられた第2のスペーサ層と、前記第2のスペーサ層上に設けられた第2の本基板とを有し、

前記第1の層には、前記第1のスペーサ層上に設けられた固定されている部分と、前記第1のスペーサ層がないところに設けられた可動する部分とがあり、前記固定されている部分と前記可動する部分とは、少なくとも一部が物理的に接続しており、

20

前記第1の層は、前記第1の本基板と前記可動する部分との間及び前記第2の本基板と前記可動する部分との間に空間があり、

前記可動する部分は、前記第1の本基板に対して垂直な方向に変位することを特徴とするマイクロマシン。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は、マイクロマシンを構成する微小構造体およびマイクロマシンおよび半導体装置に関する。また、微小構造体、微小構造体を有するマイクロマシンの作製方法に関する。

30

##### 【背景技術】

##### 【0 0 0 2】

マイクロマシンは、MEMS (Micro Electro Mechanical System)、MST (Micro System Technology)とも呼ばれ、微小な機械的微小構造体と、電気回路とを融合した総合的なシステムを指す。上記微小構造体は一般的な半導体素子と異なり、三次元的な立体構造を有し、一部が可動する場合が多い。そして当該マイクロマシンは、センサやアクチュエータ、インダクタまたは可変容量等の受動素子、スイッチ等、様々な機能を有することができる。また、上記電気回路は一般的に半導体素子によって構成され、前記微小構造体の動作を制御することや、微小構造体から出力される微小な信号を受信して処理することができる。

40

##### 【0 0 0 3】

さらに、マイクロマシンは作製方法によって分類することができ、シリコン基板の結晶異方性を利用して微小構造体を作製するバルクマイクロマシンと、様々な基板上に薄膜を積層して立体的な微小構造体を作製する表面マイクロマシンとがある（特許文献1参照）。とりわけ表面マイクロマシンは、微小構造体および電気回路を同一基板上に形成することができるため、特に米国において非常に研究が進められている。

##### 【特許文献1】特許第3590283号公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0 0 0 4】

50

マイクロマシンを構成する微小構造体は、基板上に固定された部分、一部が基板に固定されて可動する部分（構造層）、およびそれらの間に設けられた空間部分を有するような三次元的な立体構造で構成される。微小構造体が空間部分を有するためには、いったん空間部分の形を作るための層（犠牲層と呼ぶ）を形成し、最後にその犠牲層を除去する犠牲層エッティングと呼ばれる工程を必要とする。これは、一般的な半導体素子を作製する工程とは異なるため、電気回路を構成する半導体素子と微小構造体とは、別の基板上に別の工程を経て作製されることが多い。そしてそれらを別々に作製した後に、基板同士を貼り合わせたり、一つのパッケージに入れて接続することによって一体にし、マイクロマシンを作製することが多い。

#### 【0005】

微小構造体の作製において犠牲層エッティングは重要な工程であるが、多くの問題を有する律速点もある。まず、犠牲層エッティングにおいて最もよく挙げられる課題は、非常に長い時間を要するという点である。例えば $2 \sim 3 \mu\text{m}$ 厚の犠牲層を除去するのに数時間から十数時間要することもある。これは、犠牲層を除去することによって微小構造体の空間を形作るため、面積が大きく、膜厚が厚い大量の犠牲層をエッティングによって除去しなければならないからである。さらに、当該犠牲層が構造層の下に存在するという複雑な形状ゆえに、等方性エッティングを適用して犠牲層エッティングを行うためである。

#### 【0006】

また、犠牲層エッティングを行うための等方性のエッティングとしては、ウェットエッティングを適用することが多い。しかし、液体を用いた犠牲層エッティングは、エッティング終了後の乾燥時に毛管現象によって構造層と基板とが付着し、微小構造体が座屈（スティッキングとも記載する）するという問題が生じる。

#### 【0007】

また、基板面内や基板間で、構造層の下に存在している犠牲層のエッティングできた部分とできなかつた部分とが生じ、歩留まりを低下させるという問題がある。さらに、犠牲層エッティングを経ることによって、基板上に作製される微小構造体の空間部分の大きさ、すなわち、基板と構造層との間の距離等にばらつきが生じるという問題がある。犠牲層エッティングに至る各工程で、基板上の被加工物には短時間のエッティングでは影響が出ないような微小なばらつきが存在している。長時間を要する犠牲層エッティングによってそのばらつきが顕在化し、空間部分の大きさのばらつきに大きな影響を及ぼしている。

#### 【0008】

また、犠牲層の膜厚は一定の範囲内に限定される。例えば、犠牲層が厚すぎると、犠牲層エッティングに長い時間を要し、逆に犠牲層が薄すぎると、エッティング剤が拡散せずに犠牲層エッティングが進行せず、また構造層が基板と貼り付きやすくなるといった問題が生じるためである。さらに、犠牲層を形成する面積も一定の範囲内に限定されることが多い。これは、貼り付きを生じさせないためであり、また犠牲層エッティングに要する時間をできる限り短くしたいためである。

#### 【0009】

また、犠牲層エッティングは長時間にわたって行われるため、エッティングによって除去しない他の層に悪影響を及ぼすことがある。例えば、犠牲層エッティングを行っている間に、エッティング剤によって構造層や配線層が少しずつ除去されていくといった問題が生じる。このような問題を少しでも回避するため、薄膜の積層関係や使用する材料を非常に考慮する必要がある。これは、積層関係や使用する材料に大きな限定を加えることになる。さらに、マイクロマシンの作製工程を複雑にする原因となり、例えば異なる機能を有する微小構造体を同一基板上に同時に作製することが非常に難しくなることもある。

#### 【0010】

犠牲層エッティングは他の部分に悪影響を与えるため、犠牲層エッティングをする微小構造体は、半導体素子等の他のものと同一基板上に同時に形成することも非常に困難である。さらに、半導体素子の歩留まりの原因と、微小構造体の歩留まりの原因とは異なる。これらを同一基板上に形成した場合、完成品の歩留まりは各々の歩留まりの積となるため、

10

20

30

40

50

歩留まりを非常に低下させることになる。

【0011】

また、微小構造体はある程度の厚みを持った薄膜の成膜と加工を繰り返し、複数の層を積層して作製する。このような工程において、下の層によって生じる段差部分の上に成膜された薄膜は、平坦な部分と比較して膜厚が不均一となり、その部分からの破壊が起こりやすく、微小構造体の強度を低下させることになる。

【0012】

このように、犠牲層エッチングという工程を有する微小構造体の作製、および当該微小構造体を有するマイクロマシンの作製は多くの課題を有している。

【0013】

本発明は、上記のように犠牲層エッチングという工程に起因して生じる、作製に長時間を要する問題、および不良が高い頻度で発生するという問題を解決するためになされたものである。

【課題を解決するための手段】

【0014】

まず、マイクロマシン、およびマイクロマシンを構成する微小構造体を説明する。まず、マイクロマシンは、選択的に形成された空間部分を有して三次元的な立体構造を有する微小構造体と、その微小構造体を制御する、または微小構造体からの出力を検知するための電気回路を有する。電気回路は半導体素子で構成される。微小構造体は、空間部分を挟んで向かい合う二つの電極を有する。そのうち一つは、一部が基板に固定されていて可動することのできる可動電極（本明細書では第1の導電層とも記す）であり、もう一つは、基板に固定されていて可動することのない固定電極（本明細書では第2の導電層とも記す）である。また、可動することができる第1の導電層は単層で形成されていることもあるが、第1の導電層の上下に絶縁層や半導体層等を積層することで可動する部分を構成することも可能である。本明細書では、この第1の導電層や絶縁層を単層または積層により形成した可動する層を構造層と記載する。

【0015】

また一般的には、上記微小構造体が有する空間部分は、初めに犠牲層を形成することによって空間の形状を形成し、最後に犠牲層を除去することによって空間部分となる。この犠牲層の除去はエッチングによって行われ、本明細書ではその工程を犠牲層エッチングと記載する。

【0016】

上記微小構造体は、構造層が空間部分内を可動することができる場合が多い。ここで構造層の動作は、ある1点または1点以上が基板に接続されて支持された状態で、上下（基板面と垂直な方向）、左右（基板面と平行な方向）に移動すること、または、ある軸を中心に回転することを含んでいる。

【0017】

上記の課題を解決するため、本発明は、犠牲層の形成、および犠牲層エッチングの工程を経ずに微小構造体を作製することを特徴とする。すなわち、第1の基板（第1の仮基板とも記す）上に第1の層を形成し、第2の基板（第1の本基板とも記す）上に第2の層を形成する。そして、第1の基板から第1の層を剥離し、当該第1の層をスペーサ層を介して第2の基板上に貼り合わせる。スペーサ層を介して第1の層および第2の層を貼り合わせることによって、第2の基板上に形成された第2の層と、その上に貼り合わされた第1の層との間に空間部分を形成することができ、第1の層が可動する微小構造体を形成することを特徴とする。

【0018】

本発明に係る微小構造体の一つは、第1の本基板上に、スペーサ層と第1の層とを有し、表面と第1の層との間にはスペーサ層が選択的に設けられ、構造層は、前記スペーサ層によって前記表面に固定されている部分と、表面と離れて向かい合っている部分を有することを特徴とする。スペーサ層は第1の層と表面とが非接触部分を有するように設けられ

ており、これにより、第1の層は第1の本基板に固定されつつ、可動することが可能になる。

#### 【0019】

本発明に係る微小構造体は、第1の本基板上に、第1のスペーサ層、第1の層、第2のスペーサ層、および保護基板（第2の本基板とも記す）を有する。前記保護基板は前記表面と向かい合って設けられている。前記表面と構造層との間には第1のスペーサ層が設けられている。前記構造層と前記保護基板との間には第2のスペーサ層が設けられている。前記構造層は前記第1のスペーサ層により前記表面に固定されるとともに、前記第2のスペーサ層により前記保護基板に固定されている部分と、前記表面および前記保護基板と離れて向かい合っている部分とを有することを特徴とする。第1および第2のスペーサ層は、第1の層が、第1の本基板、保護基板、他の層等と接触しないように、第1の層を固定するためのものである。

#### 【0020】

本発明に係る微小構造体において、第1の層は、第1の領域、第2の領域、および第3の領域を有している。第1の領域は、第1の本基板と第1の層の間に設けられた第1のスペーサ層により表面に固定されている。第2の領域は、第1の領域とは切り離され、表面と離れて向かい合っている。第3の領域はバネとして機能し、第1の領域と第2の領域とを接続している。表面と第2の領域および第3の領域との間には、それぞれ、空間部分が設けられ、前記第2の領域は前記表面と離れて向かい合っている。また、保護基板（第2の本基板）を設けた場合は、第1の層は、第1の領域において第2のスペーサ層により保護基板に固定される。

#### 【0021】

本発明に係る微小構造体は、第1の本基板の一部または全部に密着して設けられた第2の層を設けることができる。第2の層は導電性を有する層を含んだ層として設けることができる。また、さらに、第3の層を有していてもよい。第3の層は、保護基板（第2の本基板）の第1の層と向かい合う面の一部または全部に密着して設けられる。第3の層は導電性を有する層を含んだ層として設けることができる。

#### 【0022】

また、本発明に係る微小構造体は一対の基板（第1の本基板と第2の本基板）の間に構造層を設けることができる。本発明に係る微小構造体の1つは、対向する一対の基板と、対向する基板の間に、第1の層、第1のスペーサ層および第2のスペーサ層を有する。また、一対の基板の間に、第2の層を形成することができる。さらに第3の層を形成することができる。

#### 【0023】

第1および第2のスペーサ層は、第1の層が一対の基板（第1の本基板と第2の本基板）、第2の層や第3の層など他の層と接触しないように、第1の層を一対の基板に固定するためのものである。第1のスペーサ層は一方の基板と第1の層の間に設けられ、一方の基板に選択的に形成され、第2のスペーサ層は他方の基板と第1の層の間に設けられ、他方の基板に選択的に形成されている。第1の層は、一部が可動し、他の一部が前記第1のスペーサ層により前記一方の基板に固定され、かつ第2のスペーサ層により他方の基板に固定されていることを特徴とする。

#### 【0024】

また、本発明に係る微小構造体は、第1の層の可動する部分が変位することによって、機械的な変化を電気的な変化に変換する、又は電気的な変化を機械的な変化に変換することを特徴とする。本明細書において、機械的な変化とは第1の層の可動する部分が加速度、圧力、又は静電引力等の様々な外力を受けて基板面と垂直な方向又は平行な方向に変位することである。電気的な変化とは、電圧の変化、電流量の変化、抵抗値の変化、又は容量の変化等の電磁気学的物理量の変化のことをいう。

#### 【発明の効果】

#### 【0025】

本発明は、犠牲層エッティングを行わずに微小構造体を作製することができる。すなわち、犠牲層エッティングと同様の工程を、剥離および貼り合わせによって行うため、非常に短時間でその工程を行うことができる。また、微小構造体がウェットエッティングのように液体のエッティング剤に触れることがなく、毛管現象による構造層と基板との貼り付きを生じないように作製することができる。このように本発明を適用することによって、作製に要する時間を短縮し、犠牲層エッティングというプロセスによって生じる様々な不良の発生を低減することができる。

#### 【発明を実施するための最良の形態】

##### 【0026】

本発明の実施の形態について、図面を用いて以下に説明する。ただし、本発明は以下の説明に限定されない。本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々なに変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

##### 【0027】

###### (実施の形態1)

本実施の形態では、本発明の微小構造体を作製する方法について説明する。

##### 【0028】

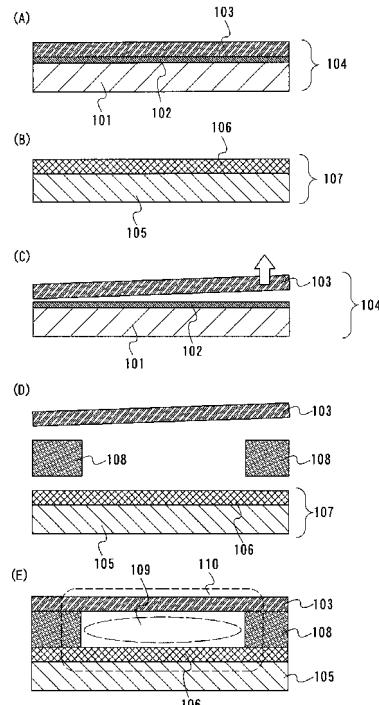

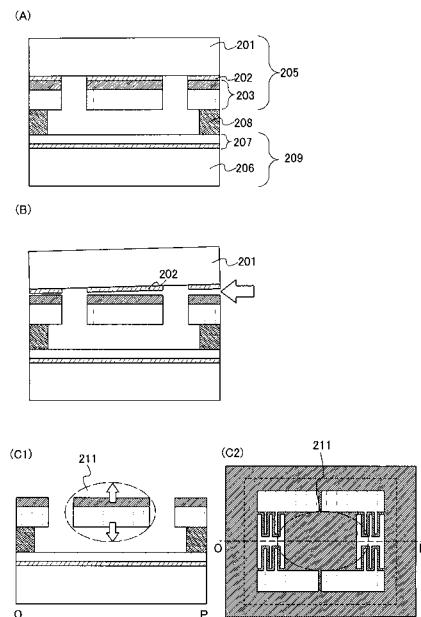

初めに、図1を用いて、本発明の微小構造体を作製する方法、および当該方法を実施するにあたって重要である剥離の方法について説明する。ここで、図は基板断面図を示している。

##### 【0029】

本発明の微小構造体は、まず図1(A)に示すように、第1の基板101(第1の仮基板とも記す)上に剥離層102および第1の層103を形成して、第1の層を有する基板104を作製する。次に、図1(B)に示すように、第2の基板105(第1の本基板とも記す)上に第2の層106を形成して、第2の層を有する基板107を作製する。

##### 【0030】

そして、図1(C)に示すように、剥離層102を境界として第1の層を有する基板104から第1の層103を剥離する。図1(D)に示すように、当該第1の層103を第2の層を有する基板107上にスペーサ層108を介して貼り合わせる。ここでスペーサ層108は、第1の層103または第2の層106上に、選択的に形成される。

##### 【0031】

このように、スペーサ層108を介して第1の層103を第2の層を有する基板107上に貼り合わせることによって、図1(E)に示すように、第2の基板105上に形成された第2の層106と、その上に貼り合わされた第1の層103との間に空間部分109が形成される。換言すると、スペーサ層108によって、第1の層103に、第2の層106と接触しない、密着しない部分が形成され、第1の層103を動かすことができる。この場合は、第1の層103が第2の基板105と垂直な方向に可動する層(=構造層)となる微小構造体110を作製することができる。

##### 【0032】

第1の基板101から第1の層103を剥がし取るための境界を作る剥離層102は、積層時に物理的に密着性が低い積層関係を有する複数の膜、または加熱やレーザ光照射、紫外線照射等、何らかの処理により質が変化して脆弱化するような膜、もしくは積層された膜同士の密着性を低下することができる膜を用いる。

##### 【0033】

そして、その密着性の低下した膜の界面から、第1の基板101と第1の層103とを剥離することができる。例えば、貴金属のように酸化し難い金属膜と酸化膜(例えば珪素の酸化膜)とは密着性が低いことが知られている。これを利用し、第1の基板101上に剥離層102として金属膜および珪素の酸化膜を積層し、その上に第1の層103を形成

10

20

30

40

50

することによって、金属膜と珪素の酸化膜との界面で第1の基板101から第1の層103を剥離することができる。

#### 【0034】

第1の基板101上に形成する剥離層102の材料、および第1の基板101から第1の層103を剥離する方法としては、下記(1)～(4)のような例を挙げることができる。

#### 【0035】

(1) 第1の基板101上に剥離層102として、単層もしくは積層の金属酸化膜を設ける。そして、加熱やレーザ光照射等により剥離層102である金属酸化膜を脆弱化させ、第1の基板101と第1の層103とを剥離する。ここで、第1の基板101としてガラス基板や石英基板のように光透過性基板を用いた場合、基板裏面からレーザ照射を行うことができる。加熱やレーザ照射により金属酸化膜が脆弱化するのは、当該金属酸化膜が結晶化されるためであると考えられる。10

#### 【0036】

(2) 第1の基板101上に剥離層102として水素を含む非晶質珪素膜を設ける。そして、加熱やレーザ光の照射により剥離層102を脆弱化させる、または剥離層102をエッチングにより除去することで、第1の基板101と第1の層103とを剥離する。

#### 【0037】

(3) 剥離層102を設けずに、第1の基板101上に、第1の層103を設ける。そして、第1の基板101を裏面から研磨して薄くするもしくは除去する、またはエッチングにより基板を除去することにより第1の層103を得る。例えば、第1の基板101として石英基板を用いた場合、HF溶液や蒸気、CHF<sub>3</sub>、またはC<sub>4</sub>F<sub>8</sub>とH<sub>2</sub>との混合ガス等を用いたエッチングで基板を除去することができる。また、第1の基板101としてシリコン基板を用いた場合には、NF<sub>3</sub>、BrF<sub>3</sub>、ClF<sub>3</sub>等のフッ化ハロゲンガスによるエッチングで基板を除去することができる。20

#### 【0038】

(4) 第1の基板101上に剥離層102として金属および金属酸化膜を積層して設ける。そして、加熱やレーザ照射等により金属酸化膜を脆弱化させ、その後、剥離層102の一部をエッチングにより除去し、脆弱化された金属酸化膜と金属の界面において物理的に剥離する。剥離層102のエッチングは、例えば、剥離層102をタンクステン(W)やモリブデン(Mo)等の金属を用いて形成した場合、アンモニア過水等の溶液、またはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガスにO<sub>2</sub>を組み合わせて用いることができる。また、剥離層102をアルミニウム(A1)やチタン(Ti)等の金属を用いて形成した場合、酸性溶液、またはCl<sub>2</sub>ガスを用いることができる。30

#### 【0039】

ここで、金属酸化膜を脆弱化させる工程、または剥離層102をエッチングする工程を経ずに物理的に剥離することもできる。また、物理的に剥離する方法は、例えば、第1の基板101端部に切り込みを入れ、第1の基板101と第1の層103との間に剥離するためのきっかけを作り、そこから第1の層103を剥がし取ることができる。

#### 【0040】

上記に示した工程により、犠牲層エッチングという工程を経ることなく、微小構造体110を作製することができる。このように作製された微小構造体110は、例えば、外部から力を受けると構造層が力を受けた方向に可動するため、その動きを検知することによってセンサとして機能させることができる。40

#### 【0041】

本実施の形態で説明した本発明の微小構造体を作製することによって、犠牲層エッチングを行わずに微小構造体110を作製することができるため、上記発明が解決しようとする課題で説明したような、犠牲層エッチングに起因する問題を回避することができる。以下に、本発明は次の有用な効果(a)～(e)を示す。

## 【0042】

(a) 代表的には、本発明を適用することにより犠牲層エッティングを行わずに微小構造体を作製することができる。すなわち、犠牲層エッティングと同様の工程を、剥離および貼り合わせによって行うため、非常に短時間でその工程を行うことができる。

## 【0043】

(b) このように、犠牲層エッティングを剥離および貼り合わせによって代替することで、ウェットエッティングを行うときのように微小構造体が液体のエッティング剤に触れることがないため、毛管現象による構造層と基板との貼り付きを生じないように、微小構造体110を作製することができる。

## 【0044】

(c) 剥離および貼り合わせにより微小構造体110を作製するため、空間部分109に犠牲層やエッティング時の副生成物が残留するといった問題を生じさせることなく微小構造体110を作製することができる。すなわち、ある基板、または基板の一部では犠牲層エッティングができているにも関わらず、他の基板、または基板内の他の部分では犠牲層エッティングが終了しなかった、という問題を回避することができる。さらに本発明の方法は、第1の基板101から剥離した第1の層103を、第2の層106を有する第2の基板105に貼り合わせるため、基板上に作製されるすべての微小構造体110の空間部分109を均一に形成することができる。

## 【0045】

(d) 長時間の犠牲層エッティングに起因する、基板面内のエッティングレートのばらつきがないので、大きな基板を用いて微小構造体、マイクロマシンを作製することが可能である。このように大きな基板を用いることによって、一度に多くの製品を作製することができ、製品の価格を下げるようになる。

## 【0046】

(e) 長時間を要する犠牲層エッティング工程を不要とするため、他の層に悪影響を与えることがない。例えば、犠牲層エッティングによる構造層の膜減りが起こらないので、構造層の膜厚を均一に形成することができる。また、剥離層エッティングを行う場合に、当該エッティングによって時に影響が懸念される材料を使用することがあったとしても、剥離層エッティングを行わない第2の基板105上に当該材料を形成することによって、その影響を回避することができる。

## 【0047】

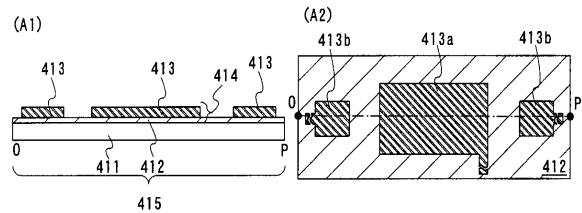

## (実施の形態2)

図2～図4を用いて、本実施の形態では、実施の形態1で説明した微小構造体の作製方法をより具体的に説明する。なお、図面は右側が基板上面図を示し、左側が上面図の鎖線OPにおける断面図を示す。

## 【0048】

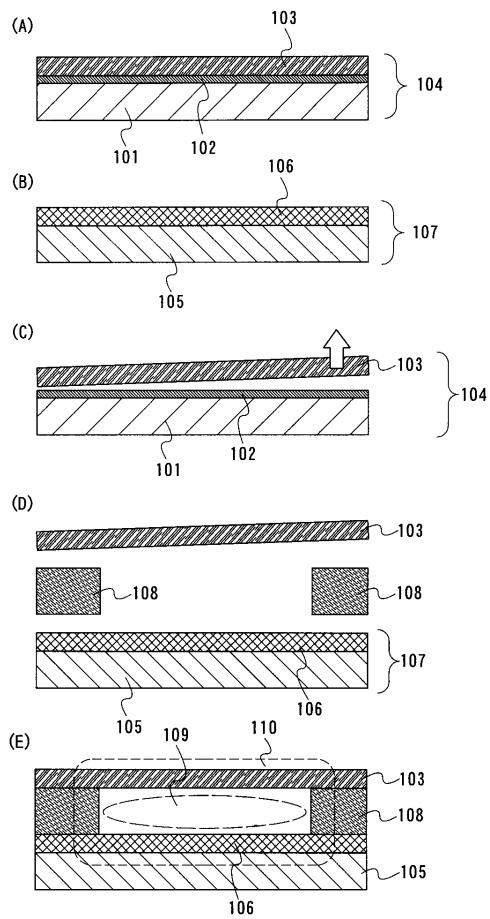

初めに、図2を用いて、第1の層を有する一方の基板の加工方法を説明する。

## 【0049】

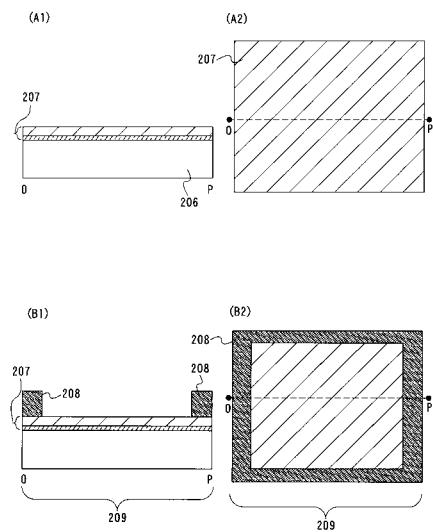

図2(A1)、(A2)に示すように、第1の基板201(第1の仮基板とも記す)上に剥離層202を形成する。ここで、第1の基板201は、シリコン基板のような半導体性を有する基板の他、ガラスや石英、プラスチック等の絶縁性を有する基板、または金属のように導電性を有する基板等、様々な基板を用いることができる。

## 【0050】

また、剥離層202は、上記(1)～(4)の例に示したように、金属や珪素などの元素や化合物を用い、CVD法やスパッタリング法等を適用して成膜する。剥離層202は、第1の基板201の全面に成膜しても良いが、基板の一部分に選択的に形成することも可能である。剥離層202を基板の一部に選択的に形成する場合、成膜された剥離層202上にフォトリソグラフィ法を用いてレジストマスクを形成し、エッティングを行うことで加工することができる。

## 【0051】

10

20

30

40

50

次に、図2(A1)、(A2)に示すように、剥離層202上に、構造層となる第1の層203を形成する。第1の層203は珪素やその化合物、金属元素やその化合物等様々な材料を用い、CVD法やスパッタリング法等の成膜方法を適用して成膜することができる。ここで、第1の層203は単一材料で単層構造でも良く、複数の材料を用いて積層構造にすることも可能である。第1の層203を積層構造で形成する場合、複数の層を連続して成膜することもできるが、成膜と加工とを繰り返して形成することも可能である。

#### 【0052】

本実施の形態では図2(A1)、(A2)に示すように、第1の層203は、2種類の膜を連続して成膜する積層構造の例を示す。第1の層203の構造は本例に限定されることなく、例えば金属や密度の高い材料の成膜と加工を行い、電極やマス(重り)を有することができる。

#### 【0053】

次に、図2(B1)、(B2)に示すように、構造層の形状を決定するように第1の層203を加工する。第1の層203の加工は、フォトリソグラフィ法を用いて第1の層203上にレジストマスクを形成し、エッチングを行うことで、図2(B1)、(B2)に示すように、第1の層203に孔204を開けることができる。第1の層203に孔204を開けるためのエッチングは、第1の層203を構成する材料にあわせて、ウェットエッティングやドライエッティングを用いることができ、その両方を組み合わせて行うことも可能である。

#### 【0054】

また、第1の層203の加工は、図2(B1)、(B2)に示すように、第1の層203のみならず、剥離層202まで到達するように加工することができる。しかしながら、第1の層203のみに孔204を開けるように加工することも可能である。

#### 【0055】

上記の工程により、第1の層を有する基板205を形成することができる。

#### 【0056】

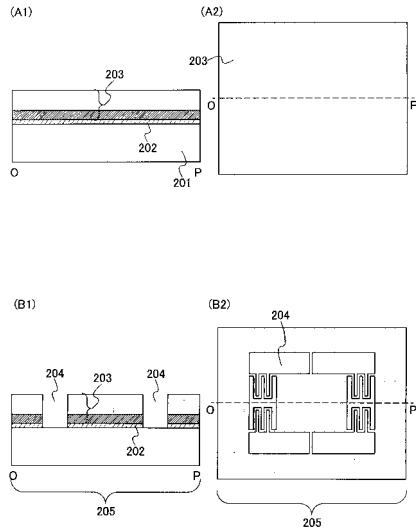

次に、図3を用いて、第2の層を有する基板の加工について説明する。図3(A1)、(A2)に示すように、第2の基板206(第1の本基板とも記す)上に、第2の層207を形成する。第2の基板206は、第1の基板201と同様、半導体性を有する基板、絶縁性を有する基板、導電性を有する基板等、様々な基板を用いることができる。

#### 【0057】

第2の層207は、第1の層203と同様、珪素やその化合物、金属元素やその化合物等様々な材料を用い、CVD法やスパッタリング法等の成膜方法を適用して成膜することができる。また、第2の層207は第1の層203と同様、単層構造または積層構造で形成することができる。積層構造で形成する場合には、複数の層を連続して成膜することもできるが、成膜と加工とを繰り返して形成することも可能である。例えば第2の基板206が特殊な機能性を有する基板であるような場合には、第2の層207を形成せずに次の工程に進むことも可能である。

#### 【0058】

本実施の形態では図3(A1)、(A2)に示すように、第2の層207は第1の層203と同様、2種類の膜を連続して成膜する積層構造の例を示す。しかしながら、第2の層207の構造は本例に限定されることなく、例えば金属膜等を成膜して加工することにより、電極や配線等を形成することができる。

#### 【0059】

次に、図3(B1)、(B2)に示すように、第2の層207上にスペーサ層208を形成する。スペーサ層208は、第1の層を有する基板205と第2の層207が形成される第2の基板206とを、スペースを保ちながら接着するための層である。そのため、本明細書では接着層とも記載することがある。スペーサ層208は、絶縁性を有する無機化合物や有機化合物等を用い、単層もしくは積層構造で形成することができる。さらには、ポリイミドやエポキシ等の有機化合物を主原料とする永久性の厚膜レジストを使用する

10

20

30

40

50

ことも可能である。

#### 【0060】

スペーサ層208は、第2の層207上に選択的に形成する。したがって、厚膜レジストのように感光性の材料を用いることで、成膜、露光、および現像のみで容易にスペーサ層208を形成することができる。また、感光性でない材料を用いる場合でも、成膜後にフォトリソグラフィ法を用いてレジストマスクを形成し、エッチングを行うことで加工することができる。さらには、スクリーン印刷法や、インクジェットに代表される液滴吐出法等を用いてスペーサ層208を形成することも可能である。

#### 【0061】

本実施の形態では、第2の層207上にスペーサ層208を形成する例を示したが、第1の層を有する基板205上にスペーサ層208を形成することもできる。10

#### 【0062】

上記の工程により、第2の層を有する基板209を形成することができる。

#### 【0063】

次に、図4を用いて、第1の層を有する基板205、および第2の層を有する基板209を用いて微小構造体を作製する方法の例を説明する。

#### 【0064】

図4(A)に示すように、上記工程にて形成した第1の層を有する基板205、および第2の層を有する基板209を、スペーサ層208を介して第1の層203と第2の層207とが向かい合うように貼り合わせる。これらの基板を貼り合わせるため、スペーサ層208は接着性を有する。スペーサ層208により、第1の層203は第2の層207と接触しないで第2の基板206に固定される。20

#### 【0065】

そして、図4(B)に示すように、剥離層202を界面として(図4(B)矢印で示す部分)、その界面から第1の基板201を剥離し、第1の基板201を取り外す。第1の層203を第1の基板201から分離する方法は、上記(1)~(4)の例に示した方法を用いて行うことができる。ここで、第1の層203に、剥離層202が残留していても良い。また、残留した剥離層202を除去する工程を加えても良い。また、取り外した第1の基板201は、繰り返して使用することが可能である。

#### 【0066】

上記の工程により、第1の基板201を取り外すことで、犠牲層エッチングという工程を経ることなく、第2の基板206板上に第2の層207、スペーサ層208、および第1の層203を積層させることができる。そして、図4(C1)、(C2)に示すように、第2の基板206と第1の層203との間に空間部分を有し、第1の層203が可動する層(構造層)となる微小構造体を形成することができる。30

#### 【0067】

形成された微小構造体は、第1の層203が構造層(または、可動層、可動電極とも記載する。)となり、第2の層207が、第2の基板206板上に固定された固定層(または、固定電極とも記載する。)となる。そして、構造層(第1の層203)はスペーサ層208および第2の層207を介して第2の基板206に固定されている。そして、基板垂直方向、もしくは基板と平行な方向、またはそれらを組み合わせ基板とある角度を有するような方向に可動することができる。この第1の層203は、可動する部分にS字型を複数連ねた形状の部分を有し、この部分でスペーサ層208により固定される部分と連結されている。40

#### 【0068】

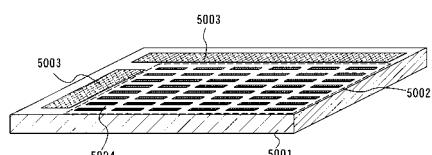

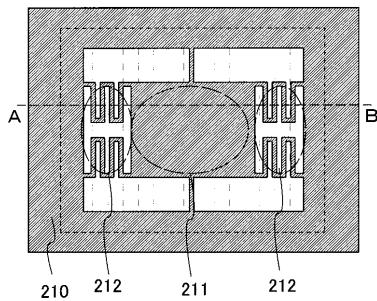

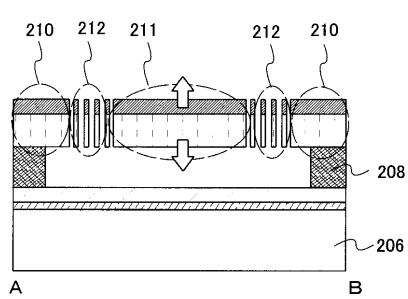

すなわち、図38(A)(B)に示すように構造層(第1の層203)は、基板に固定される第1の領域210と、可動する第2の領域211、およびバネとして機能する第3の領域212を有している。構造層の第1の領域と第2の基板206の間にはスペーサ層208が設けられ、第1の領域210は、スペーサ層208により第2の基板206に固定されている。第2の層を有する基板209の表面と第2の領域211および第3の領域50

212との間には、それぞれ、空間部分が設けられ、第2の領域211は第2の層を有する基板209の表面と離れて向かい合っている。第2の領域211は、第1の領域210とは切り離され、第2の基板206と離れて向かい合っており、可動部分となる。第3の領域212は固定されている第1の領域210と可動する第2の領域211とを連結している。第3の領域212は、蛇行する様に折り曲げた形状、Sを複数連ねた形状に加工する。このように加工することにより、第3の領域212は、バネとして機能することができる。

#### 【0069】

ここで、第2の層を有する基板209と第1の層203との間の距離は、スペーサ層208の厚さによって決定される。また、第1の層203の可動することのできる部分と、スペーサ層208によって固定されている部分との距離は、図2(B1)(B2)を用いて説明した第1の層203の加工によって決定される。したがって、第2の基板206と第1の層203との間に形成される空間部分や、第1の層203の間に形成される穴の大きさは、スペーサ層208の厚さや第1の層203の加工によって任意に調節することができる。

#### 【0070】

本実施の形態で説明した微小構造体を作製する方法は、単純な例を示しているが、第1の層203、第2の層207、およびスペーサ層208を積層構造とすることや、任意の形状に加工して形成することにより、様々な機能を有する微小構造体を作製することができる。

#### 【0071】

このように作製された微小構造体は、例えば、外部から力を受けると構造層が力を受けた方向に可動するため、その動きを検知することによってセンサとして機能させることができる。また、第1の層203および第2の層207に向かい合う電極を形成し、静電引力で可動させることによりアクチュエータとして機能させることも可能である。そして、このアクチュエータを利用して、スイッチや容量が可変のコンデンサ等を作製することもできる。

#### 【0072】

本実施の形態で説明した本発明の微小構造体を作製する方法を適用することによって、犠牲層エッチングを行わずに微小構造体を作製することができるため、上記発明が解決しようとする課題で説明したような、犠牲層エッチングに起因する問題を回避することができる。すなわち、実施形態1と同じ効果(a)~(e)を得ることができる。

#### 【0073】

さらに、本実施形態によれば、次の効果(f)~(i)を有することができる。

(f) 本発明の方法は、基板と第1の層との間の空間部分の距離が、スペーサ層の厚さによって決定され、第1の層において、基板に固定されている部分と可動できる部分との間の空間の距離は第1のエッチングによって決めることができる。したがって、微小構造体が有する空間部分の大きさは、犠牲層エッチングに起因する犠牲層の厚さや面積によって限定されることなく任意に設計することができる。

#### 【0074】

(g) 本発明は剥離および貼り合わせによって微小構造体を作製するので、大きさを限定することなく、任意の大きさの微小構造体を作製することができる。例えば、数mmから十数mm角のように大きな微小構造体の作製を行うことも可能である。

#### 【0075】

(h) 上記のように、本発明は第1の層と第2の層との二つの層を貼り合わせて微小構造体を作製するため、使用する材料の自由度および構造の自由度が高くなる。具体的には、図2(B1)、(B2)に示す第1のエッチングによる第1の層の加工により構造層の形状を決定するため、形状の自由度が高い微小構造体を作製することができる。また、犠牲層エッチングを考慮しなくて良いので積層関係のバリエーションが広くなり、異なる機能を有する微小構造体を同時に作製することが容易になる。例えば、センサと受動素子

10

20

30

40

50

と同時に形成することが可能である。

#### 【0076】

(i) また、本発明は犠牲層を形成せず、さらに、第1の層と第2の層とを別々に形成して貼り合わせを行うため、犠牲層のように厚い膜によって生じる段差部分がなく、その段差乗り越え部分から生じる破壊が起こらない。したがって、強度の高い微小構造体を作製することができる。

#### 【0077】

なお、本実施の形態は他の実施の形態と自由に組み合わせて行うことができる。

#### 【0078】

##### (実施の形態3)

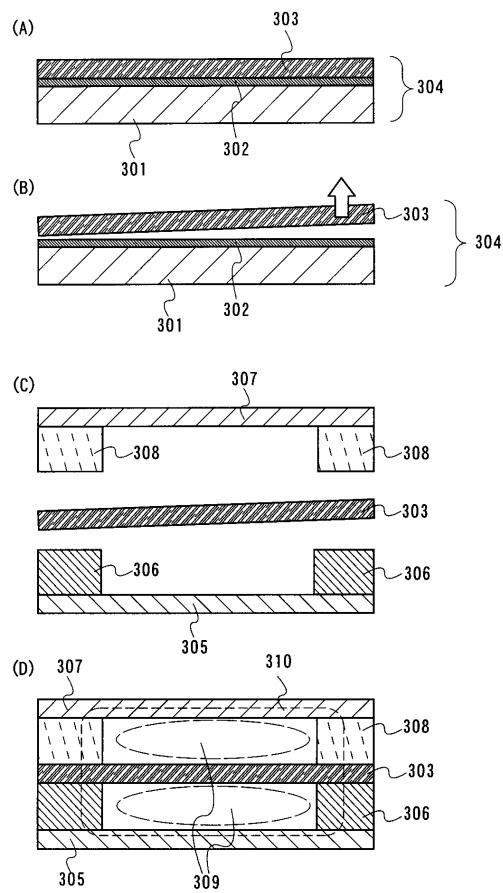

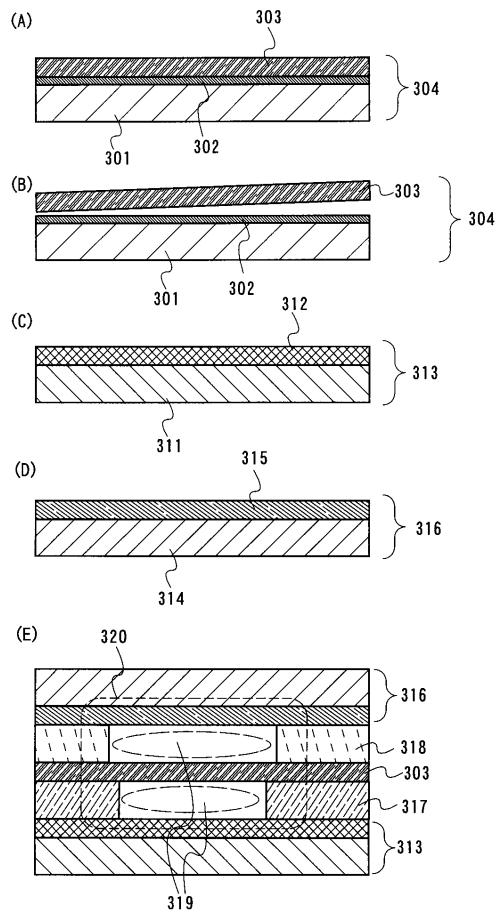

本実施の形態では、実施の形態1で説明した方法を応用し、微小構造体を作製する例を図5～図9用いて説明する。ここで、図面は断面図を示している。

#### 【0079】

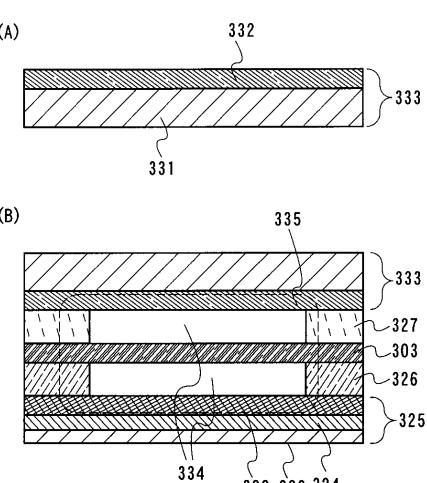

図5(A)に示すように、第1の基板301(第1の仮基板とも記す)上に第1の剥離層302および第1の層303を形成して第1の層を有する基板304を作製する。図5(B)に示すように、第1の剥離層302を境界として第1の層を有する基板304から第1の層303を剥離する。

#### 【0080】

次に、第2の基板305(第1の本基板とも記す)に第1のスペーサ層306を選択的に形成し、第3の基板307(第2の本基板とも記す)に第2のスペーサ層308を選択的に形成する。第1のスペーサ層306を有する第2の基板305、および第2のスペーサ層308を有する第3の基板307を、第1の層303を挟み込むように接着する(図5(C)参照)。

#### 【0081】

このように、第1のスペーサ層306および第2のスペーサ層308を介して第1の層303を挟み込むように、第2の基板305と第3の基板307とを貼り合わせることによって、第2の基板305と第1の層303との間、および第3の基板307と第1の層303との間に空間部分309が形成される。このようにして、第2の基板305と第3の基板307で封止され、第1の層303が可動する層(=構造層)となる微小構造体310を作製することができる(図5(D)参照)。

#### 【0082】

ここで、第1の基板301は、基板上に薄膜を形成するため、高い温度での成膜やエッチング剤を用いた加工に耐えられるような基板、例えば、ガラス、石英、金属、半導体、等の基板を用いることが好ましい。なお、成膜条件や加工条件を満たす場合には、プラスチックのような有機樹脂材料で形成された基板を用いることも可能である。また、第2の基板305(第1の本基板とも記す)、および第3の基板307(第2の本基板とも記す)は、空間部分を介して第1の層303を保護する、パッケージとしての役割を有するので、薄くて柔らかく、安価な基板、例えば、プラスチックフィルムのような基板を用いることができる。なお、第1の基板301と同様、ガラスや石英等の基板を用いることもできる。

#### 【0083】

第1の基板301上に形成する第1の剥離層302の材料や形成方法、および第1の層を有する基板304から第1の層303を剥離する方法は、上記実施の形態1、2で説明した方法を適用することができる。

#### 【0084】

第1の層303には、可動することにより機能を発揮する層となるように材料を選択し、加工を行う。例えば、可動することによって歪みが生じ、電気抵抗等の膜の特性が変化するような材料を用い、可動によって歪みを大きくできる構造に加工することができる。

#### 【0085】

第1のスペーサ層306、第2のスペーサ層308には、前記実施の形態2のスペーサ

10

20

30

40

50

層と同様に、絶縁性を有する無機化合物や有機化合物等を用い、単層もしくは積層構造で形成することができる。また、アクリルやエポキシ、ポリイミド等を主原料とする永久性の厚膜レジストを使用することも可能である。

#### 【0086】

上記工程により、第1の層303が空間部分309を可動することにより機能する微小構造体310を作製することができる。例えば、第1の層303(構造層)を、歪みによって電気抵抗が変化するように形成することで、加速度や圧力等の外力を受けて構造層が可動したことを電気的に検知し、センサとして機能する微小構造体310を作製することができる。

#### 【0087】

図6を用いて、図5の作製例を応用した微小構造体の他の作製例について、説明する。図6(A)に示すように、第1の基板301(第1の仮基板とも記す)上に第1の剥離層302および第1の層303を形成して第1の層を有する基板304を作製する。図6(B)に示すように、第1の剥離層302を境界として第1の層を有する基板304から第1の層303を剥離する。

#### 【0088】

次に、図6(C)に示すように、第2の基板311(第1の本基板とも記す)上に第2の層312を形成して第2の層を有する基板313を作製する。同様に図6(D)に示すように、第3の基板314(第2の本基板とも記す)上に第3の層315を形成して第3の層を有する基板316を作製する。

#### 【0089】

そして、第2の層を有する基板313に第1のスペーサ層317を選択的に形成し、第3の層を有する基板316上に第2のスペーサ層318を選択的に形成する。第1のスペーサ層317を有する第2の層を有する基板313、および第2のスペーサ層318を有する第3の層を有する基板316を、第2の層312と第3の層315とが向かい合い、第1の層303を挟み込むように接着する。

#### 【0090】

このように、第1のスペーサ層317および第2のスペーサ層318を介して第1の層303を挟み込み、第2の層312と第3の層315とが向かい合うように第2の層を有する基板313と第3の層を有する基板316とを貼り合わせることによって、第2の層312と第1の層303との間、および第3の層315と第1の層303との間に空間部分319が形成される。このようにして、第2の基板311と第3の基板314とで封止され、第1の層303が可動する層(=構造層)となる微小構造体320を作製することができる。

#### 【0091】

ここで、第2の基板311、および第3の基板314は、基板上に薄膜を形成するため、高い温度の成膜やエッチング剤を用いた加工に耐えられるような基板、例えば、ガラス、石英、金属、半導体、等の基板を用いることが好ましい。なお、成膜条件や加工条件を満たす場合には、プラスチックのような有機樹脂材料で形成された基板を用いることも可能である。とりわけ、薄くて軽量の基板を第2の基板311および第3の基板314に適用することで小型の微小構造体を作製することが可能となる。

#### 【0092】

第1の層303、第2の層312、および第3の層315は、図6(E)に示すように、空間部分319を介して向かい合うことによって機能を発揮するように各々の材料を選択し、加工を行う。例えば、第1の層303、第2の層312、または第3の層315のうち少なくとも2つの層に導電性を有する材料を用いて形成すれば、向かい合う二つの導電層を容量とすることができます。

#### 【0093】

上記工程により、空間部分を第1の層303が可動し、第1の層303、第2の層312、および第3の層315が協働して機能する微小構造体320を形成することができる

10

20

30

40

50

。例えば、第1の層303、第2の層312、および第3の層315に導電性を有する材料を用いて形成した場合、加速度や圧力等の外力を受けて構造層が可動したときに、第2の層312と第1の層303、および第3の層315と第1の層303との間の各々の距離が変化するため、その変化を静電容量の変化として検出することでセンサとして機能する微小構造体320を作製することができる。

#### 【0094】

また、このように作製した微小構造体320によって、外部から第1の層303を電磁的に切り離すことも可能である。例えば、第1の層303を、高い周波数の信号を伝送する導波路として形成し、第2の層312および第3の層315を接地電位（グランド電位）にすることで、低損失の伝送路を形成することができる。この場合、第1の層303は可動する必要はない。10

#### 【0095】

さらに、図7を用いて、図5の作製例を応用した微小構造体の他の作製例について説明する。本発明の微小構造体は、図7(A)に示すように、第1の基板301(第1の仮基板とも記す)上に第1の剥離層302および第1の層303を形成して第1の層を有する基板304を作製する。図7(B)に示すように、第1の剥離層302を境界として第1の層を有する基板304から第1の層303を剥離する。

#### 【0096】

次に、図7(C)に示すように、第2の基板311(第2の仮基板とも記す)上に第2の剥離層321を形成し、第2の剥離層321上に第2の層322を形成する。第2の層322上面から、第1の保護基板323(第1の本基板とも記す)を接着剤324を用いて貼り付ける。20

#### 【0097】

第2の剥離層321を境界として第2の基板311から第2の層322を剥離して、第1の保護基板323側へ写し取ることで、第2の層を有する基板325を作製する(図7(D)参照)。

#### 【0098】

そして、第2の層を有する基板325に第1のスペーサ層326を選択的に形成し、第3の基板328(第2の本基板とも記す)上に第2のスペーサ層327を選択的に形成する。第2の層を有する基板325および第3の基板328を、第1の層303を挟み込むように接着する(図7(E)参照)。30

#### 【0099】

このように、第1のスペーサ層326を介して第2の層を有する基板325と第1の層303の一方の面とを貼り合わせ、第2のスペーサ層327を介して第3の基板328と第1の層303の他方の面とを貼り合わせることにより、第2の層322と第1の層303との間、および第3の基板328と第1の層303との間に空間部分329が形成される。このようにして、第1の保護基板323および第3の基板328で封止され、第1の層303が可動する層(=構造層)となる微小構造体330を形成することができる。

#### 【0100】

ここで、第1の保護基板323、および第3の基板328は、空間部分329を介して第1の層303を保護するパッケージとしての役割を有するので、薄くて柔らかく、安価な基板、例えば、プラスチックフィルムのような基板を用いることができる。なお、第1の基板301と同様、ガラスや石英等の基板を用いることも可能である。40

#### 【0101】

第1の層303および第2の層322は、図7(E)に示すように、空間部分329を介して向かい合うことによって機能を発揮するように各々の材料を選択し、加工を行う。例えば、各層に導電性を有する材料を用いて形成すれば、向かい合う二つの導電層を容量とすることができる。

#### 【0102】

第2の剥離層321および第1のスペーサ層326、第2のスペーサ層327は、上記50

例と同様に形成することができ、第1の層を有する基板304から第1の層303を剥離する方法は、実施の形態1、2で説明した方法を適用することができる。

#### 【0103】

さらに、図8を用いて、図7に示した作製例を変形した例を説明する。図8(A)に示すように、第3の基板331(第2の本基板とも記す)上に第3の層332を形成することで第3の層を有する基板333を作製する。

#### 【0104】

そして、図7(E)の第3の基板328の代わりに、第3の層を有する基板333を用い、この第3の層を有する基板333上に第2のスペーサ層327を選択的に形成する。

#### 【0105】

第1のスペーサ層326を介して第2の層を有する基板325と第1の層303の一方の面とを貼り合わせ、第2のスペーサ層327を介して第3の層を有する基板333と第1の層303の他方の面とを、第3の層332が第1の層303と向かい合うように貼り合わせる。これによって、第2の層322と第1の層303との間、および第3の層332と第1の層303との間に空間部分334が形成される。このようにして、第1の保護基板323および第3の基板331で封止され、第1の層303が可動する層(=構造層)となる微小構造体335を形成することができる。なお、他の工程、使用される材料、部材については、図5～図7と同様とすることができる。

#### 【0106】

第1の層303、第2の層322、および第3の層332は、図8(B)に示すように、空間部分334を介して向かい合うことによって機能を発揮するように、各々の材料を選択し、加工を行う。例えば、第1の層303、第2の層322、または第3の層332のうち少なくとも2つの層を導電性を有する材料を用いて形成すれば、向かい合う二つの導電層を容量とすることができます。

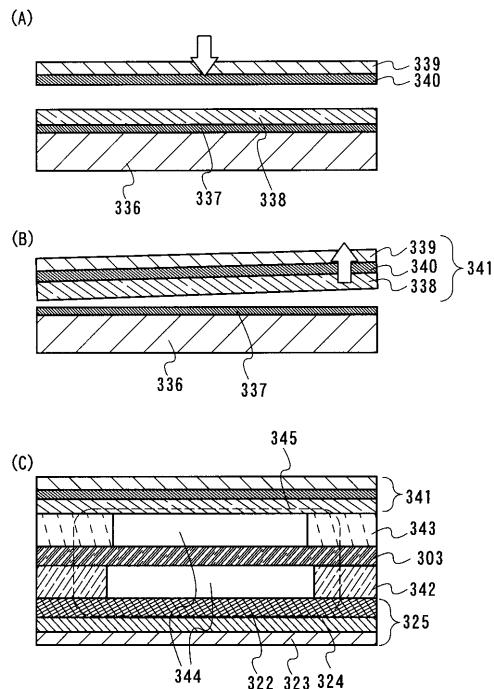

#### 【0107】

さらに、図9を用いて、図7の作製方法の変形例を説明する。図9(A)に示すように、第3の基板336(第3の仮基板とも記す)上に第3の剥離層337および第3の層338を形成し、第3の層338上面に、第2の保護基板339(第2の本基板とも記す)を接着剤340を用いて貼り付ける。

#### 【0108】

図9(B)に示すように、第3の剥離層337を境界として第3の基板336から第3の層338を剥離して第2の保護基板339側へ写し取ることで、第3の層を有する基板341を作製する。

#### 【0109】

第3の層を有する基板341上に第2のスペーサ層343を選択的に形成する。第1の層303を挟み込むように、第2の層を有する基板325と第2のスペーサ層343を有する第3の層を有する基板341を対向させて接着する(図9(C)参照)。

#### 【0110】

このように、第1のスペーサ層342を介して第2の層を有する基板325と第1の層303の一方の面を貼り合わせ、第2のスペーサ層343を介して第3の層を有する基板341と第1の層303の他方の面とを、第3の層338が第1の層303と向かい合うように貼り合わせることによって、第2の層322と第1の層303との間、および第3の層338と第1の層303との間に空間部分344が形成される。このようにして、第1の保護基板323および第2の保護基板339で封止され、第1の層303が可動する層(=構造層)となる微小構造体345を形成することができる。なお、他の工程、使用される材料、部材については、図5～図7と同様とすることができる。

#### 【0111】

第1の層303、第2の層322、および第3の層338は、図9(C)に示すように、空間部分344を介して向かい合うことによって機能を発揮するように各々の材料を選択し、加工を行う。例えば、第1の層303、第2の層322、または第3の層338の

10

20

30

40

50

うち少なくとも 2 つの層に導電性を有する材料を用いて形成すれば、向かい合う二つの導電層を容量とすることができる。

【 0 1 1 2 】

上記工程により、空間部分を第 1 の層 303 が可動し、第 1 の層 303、第 2 の層 322、および第 3 の層 338 が協働して機能する微小構造体 345 を形成することができる。例えば、第 1 の層 303、第 2 の層 322、および第 3 の層 338 に導電性を有する材料を用いて形成した場合、加速度や圧力等の外力を受けて構造層が可動したときに、第 2 の層 322 と第 1 の層 303、および第 3 の層 338 と第 1 の層 303 との間の各々の距離が変化するため、その変化を静電容量の変化として検出することでセンサとして機能する微小構造体 345 を作製することができる。

10

【 0 1 1 3 】

また、このように作製した微小構造体 345 によって、外部から第 1 の層 303 を電磁的に切り離すことも可能である。例えば、第 1 の層 303 を、高い周波数の信号を伝送する導波路として形成し、第 2 の層 322 および第 3 の層 332 を接地電位（グランド電位）にすることで、低損失の伝送路を形成することができる。この場合、第 1 の層 303 は可動する必要はない。

【 0 1 1 4 】

このように、本発明の微小構造体の作製方法を適用することによって、実施形態 1、2 と同様、次の効果を得ることができる。

( a ) 犠牲層エッチングを行わずに微小構造体を作製することができる。すなわち、犠牲層エッチングと同様の工程を、剥離および貼り合わせによって行うため、非常に短時間でその工程を行うことができる。

20

【 0 1 1 5 】

( b ) また、犠牲層エッチングを剥離および貼り合わせによって代替することで、ウエットエッチングを行うときのように微小構造体が液体のエッチング剤に触れることがなく、毛管現象による構造層と基板との張り付きを生じないように作製することができる。

【 0 1 1 6 】

( c ) また、本発明は長時間を要する犠牲層エッチング工程を不要とするため、他の層に悪影響を与えることがない。例えば、犠牲層エッチング時に構造層の膜減りが起こらないので、構造層の膜厚を均一に形成することができる。また、剥離層エッチングを行う場合に、当該エッチングによって時に影響が懸念される材料を使用することがあったとしても、当該材料を剥離層エッチングを行わない第 2 の基板上または第 3 の基板上に形成することによってその影響を回避することができる。

30

【 0 1 1 7 】

( d ) また、本発明の方法は、基板と第 1 の層との間の空間部分の距離が、スペーサ層の厚さによって決定され、第 1 の層において、基板に固定されている部分と可動できる部分との間の空間の距離は第 1 のエッチングによって決めることができる。したがって、微小構造体が有する空間部分の大きさは、犠牲層エッチングに起因する犠牲層の厚さや面積によって限定されることなく任意に設計することができる。

【 0 1 1 8 】

( e ) 同様に、本発明は剥離および貼り合わせによって微小構造体を作製するので、大きさを限定することなく、任意の大きさの微小構造体を作製することができる。例えば、數 mm から十数 mm 角のように大きな微小構造体の作製を行うことも可能である。

40

【 0 1 1 9 】

( f ) また、本発明は犠牲層を形成せず、さらに、第 1 の層と第 2 の層とを別々に形成して貼り合わせを行うため、犠牲層のように厚い膜によって生じる段差部分がなく、その段差乗り越え部分から生じる破壊が起こらない。したがって、強度の高い微小構造体を作製することができる。

【 0 1 2 0 】

なお、本実施の形態は、他の実施の形態と自由に組み合わせて行うことができる。

50

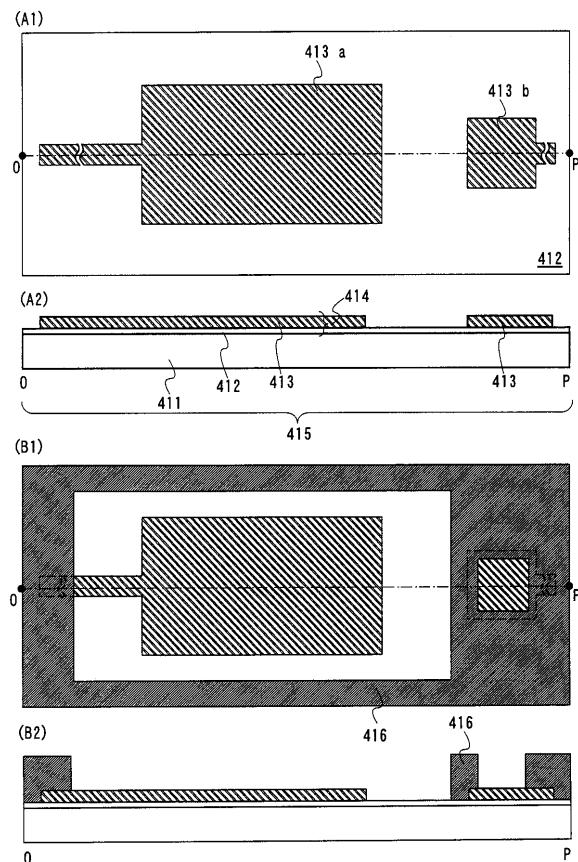

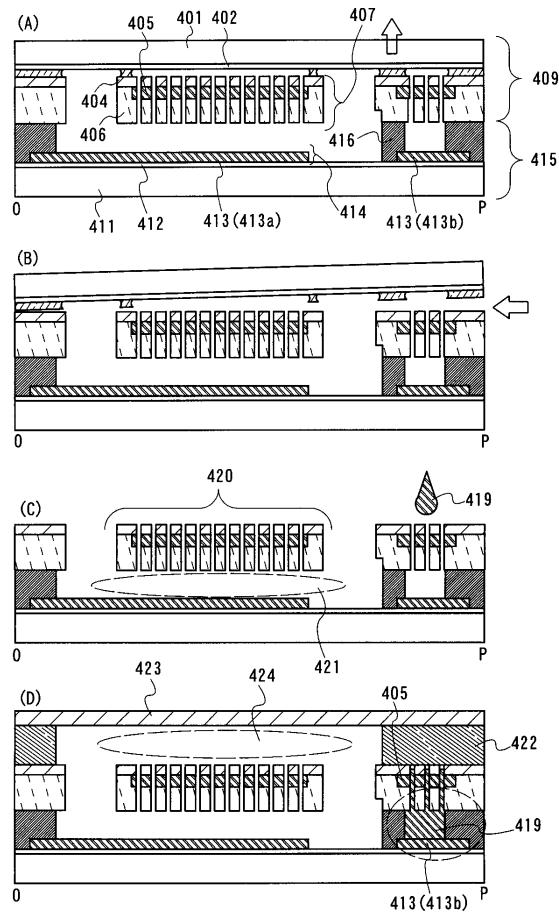

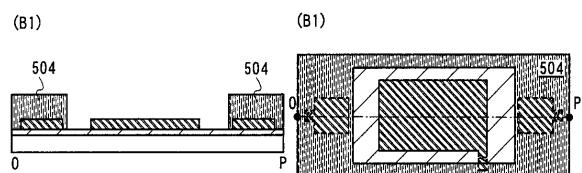

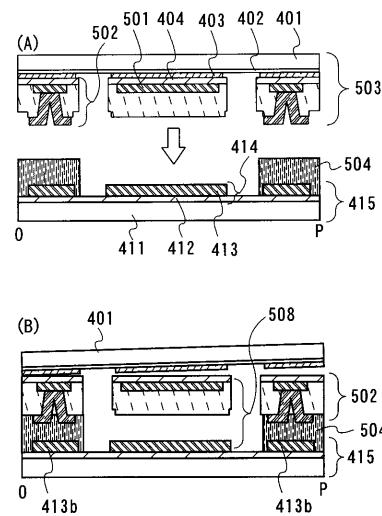

## 【0121】

(実施の形態4)

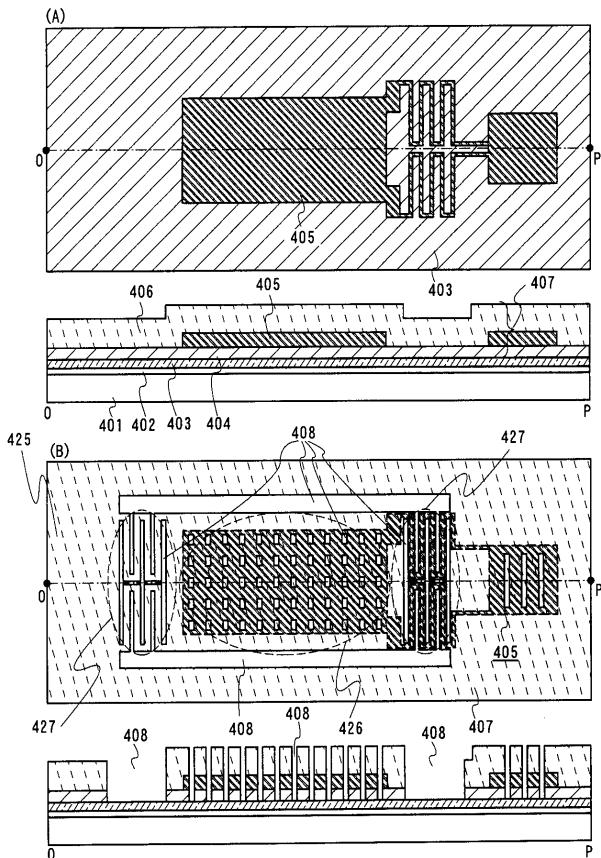

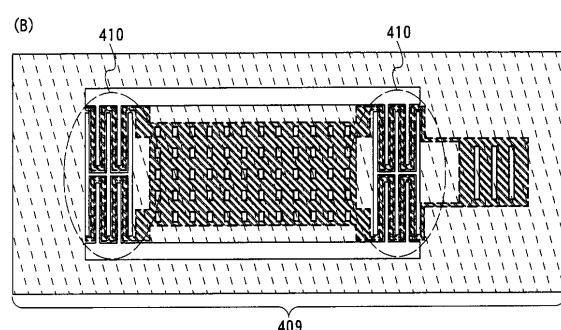

図10～図16を用いて、本実施の形態では、実施の形態1で説明した本発明の微小構造体の作製方法について、具体的に説明する。なお、図10(A1)、図10(B1)、図12(B)、図13(A1)、図13(B1)は上面図である。また、図10(A2)、図10(B2)、図11、図12(A)、図13(A2)、図13(B2)、図14(A)～図16(D)は断面図である。

## 【0122】

初めに、図10、図11を用いて、第1の層を有する基板を作製する例を示す。

## 【0123】

まず、図10(A1)、(A2)に示すように、第1の基板401(第1の仮基板とも記す)上に剥離層403を形成する。ここで第1の基板401は、例えばガラス基板や石英基板、プラスチック基板等を用いることができる。さらには、金属等の導電性を有する基板や、シリコン、ゲルマニウム、またはシリコンとゲルマニウムの化合物等の半導体性を有する基板を用いることも可能である。本実施の形態では、ガラス基板を用いて微小構造体を作製する例を示す。

## 【0124】

また上記で示した基板を用いる場合、準備した基板をそのまま用いることも可能であるが、基板表面に表面を保護する層(例えば絶縁性を有する層)を形成してから用いることもできる。このような保護層402は、例えば、酸化シリコン、窒化シリコンまたは酸化窒化シリコン等の絶縁性を有する膜を用いて形成することができる。本実施の形態では、第1の基板401上に保護層402として、厚さ100nmの酸化窒化シリコン層をCVD法によりを形成し、保護層402の上に剥離層403を形成する例を示す。

## 【0125】

そして、保護層402上に剥離層403を形成する。剥離層403には、例えば、タンゲステン、モリブデン、チタン、タンタル、ニオブ、ニッケル、コバルト、ジルコニウム、亜鉛、ルテニウム、ロジウム、鉛、オスミウム、イリジウム、シリコンから選択された元素でなる材料、これらの元素を主成分とする合金材料、またはこれらの元素の酸化物や窒化物等の化合物材料を用いることができる。これらの材料は、スパッタリング法やプラズマCVD法等の公知の手段により成膜することができる。剥離層403は、単一の材料を用いて単層構造で形成することができ、また複数の材料を用いて積層構造で形成することも可能である。

## 【0126】

剥離層403を積層構造で形成する場合、例えば、1層目としてタンゲステン層、モリブデン層、またはタンゲステンとモリブデンの混合物を含む層のいずれか1層を形成し、2層目として、タンゲステン、モリブデン、または、タンゲステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物、もしくは窒化酸化物を形成することができる。

## 【0127】

剥離層403として、タンゲステン等の金属を含む層と当該金属の酸化物を含む層との積層構造を形成する場合、金属を含む層上に酸化シリコンを含む層を形成することで、金属を含む層と酸化シリコンを含む層との界面に当該金属の酸化物を含む層が形成されることを利用しても良い。

## 【0128】

また、タンゲステン等の金属を含む層の表面を、熱酸化処理、酸素プラズマ処理、またはオゾン水等酸化力の強い溶液での処理等を行い、金属を含む層上に当該金属の酸化物を含む層を形成した後、その上層に窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層を形成することができる。これは、上記金属の窒化物、酸化窒化物、および窒化酸化物を含む層を形成する場合も同様である。本実施の形態では、剥離層403として、厚さ30nmのタンゲステン層をスパッタリング法により形成する例を示す。

## 【0129】

10

20

30

40

50

次に、剥離層403上に、下地層404を形成する。下地層404は、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン等を、スパッタリング法やプラズマCVD法等の公知の手段により成膜することができる。下地層404を形成することで、外部からの不純物の侵入を防止することができる。本実施の形態では、下地層404として、厚さ50nmの窒化酸化シリコンからなる層と、膜厚100nmの酸化窒化シリコンからなる層をCVD法により積層させて形成する例を示す。

#### 【0130】

次に、下地層404上に、微小構造体を駆動するときの可動電極となる第1の導電層405を形成する。第1の導電層405は、導電性を有する金属元素やそれらの化合物を用いて成膜し、フォトリソグラフィ法を用いてレジストマスクを形成し、エッチングを行うことで加工することができる。第1の導電層405の形状は、形成する構造層(第1の層407)の構造を考慮して決定される。本実施の形態では、第1の導電層405は、第1の層の形状を基に、その形状の各寸法からアライメントマージンを差し引いた形状に加工する例を示している。

#### 【0131】

第1の導電層405は、アルミニウム(A1)、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)等の金属元素、またはこれらの金属元素を主成分として導電性を有する化合物を用い、スパッタリング法やプラズマCVD法等の公知の手段を適用して成膜することができる。本実施の形態では、第1の導電層405として、厚さ400nmのチタンをスパッタリング法により形成する例を示す。

#### 【0132】

また、第1の導電層405の加工は、ウエットエッチングやドライエッチング等のエッチングによって行うことができる。なかでも異方性のドライエッチングを適用するが多く、その例としては、ICP(Inductive Coupled Plasma: 誘導結合型プラズマ)エッチング法を用いることができる。このとき、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度、等)を適宜調節することで、加工性(エッチング速度や、加工する層の側面の形状、等)を高めることができる。エッチング用ガスとしては、例えば第1の導電層405がアルミニウムで形成されている場合、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>等を用いることができる。また、第1の導電層405がタンゲステンやモリブデン等の金属で形成されている場合、CCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガスにO<sub>2</sub>を組み合わせて用いることができる。

#### 【0133】

次に、第1の導電層405上に、第1の絶縁層406を形成する。なお、図10(A1)の上面図においては第1の絶縁層406は図示されていない。第1の絶縁層406は、第1の導電層405と共に構造層の骨格をなすものであり、作製する微小構造体の性能(例えば、構造層の重さ、バネ定数、または可動範囲、等)を考慮して、その材料、膜厚、積層構造等を決定する。第1の層407は、絶縁性を有する無機化合物や有機化合物等を単層もしくは積層により成膜し、形成することができる。例えば、第1の絶縁層406を形成する無機材料としては、酸化シリコン、窒化シリコンを用いることができる。また、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる。本実施の形態では、第1の絶縁層406として、厚さ900nmの酸化窒化シリコンをCVD法により形成する例を示す。

#### 【0134】

本実施の形態では、上記で形成した下地層404、第1の導電層405、および第1の絶縁層406の積層構造を第1の層407と記載する。第1の層407は微小構造体を形成する構造層となる。

#### 【0135】

次に、図10(B1)、(B2)に示すように、第1の層407の形状を決めるための

10

20

30

40

50

第1のエッティングを行う。第1のエッティングによって、第1の層407の形状を決定するように、孔408を形成する。第1のエッティングによる孔408の形成は、フォトリソグラフィ法を用いてレジストマスクを形成し、レジストマスクを用いて、エッティングを行うことで加工することができる。本実施の形態では、第1の導電層405を加工した後に第1の絶縁層406を形成しているため、第1のエッティングは下地層404および第1の絶縁層406を加工する。本発明は、第1のエッティングにおいて第1の層407を形成するすべての層を加工することもできる。

### 【0136】

第1のエッティングは、ウエットエッティングやドライエッティング等のエッティングによって行うことができ、本実施の形態では異方性のドライエッティングを適用する。本実施の形態では、酸化窒化シリコンを用いて第1の絶縁層406を形成しているので、第1のエッティングを行うエッティング用ガスとして、CHF<sub>3</sub>、HF、C<sub>2</sub>F<sub>6</sub>、ならびにC<sub>4</sub>F<sub>8</sub>およびH<sub>2</sub>等を用いることができる。また、上記のガスにAr、He等を混合することにより、エッティング時に発生する化合物の堆積を抑制することができる。また第1の絶縁層406を複数の材料を用いて積層している場合、第1のエッティングではエッティング用ガスを切り替えることにより、複数の層を連続してエッティングすることが可能である。

10

### 【0137】

本実施の形態では、構造層のバネ定数を小さくして可動しやすくするため、第1のエッティングにおいて、構造層の支持梁となる第1の層407を蛇行する様に折り曲げた形状、S字を複数連ねた形状に加工する。また本実施の形態では、構造層を形成する第1の導電層405を、外部電源や信号線と電気的に接続するため、第1の導電層405が支持梁内を通るように加工した。第1の導電層405と第1の絶縁層406とを同時に第1のエッティングで加工することも可能である。

20

### 【0138】

図10(B1)、(B2)に示すように、第1の層407を両持ち梁型に加工することで、構造層が基板垂直方向(上下方向)に可動する微小構造体を作製することができる。さらに、構造層のバネ定数を低くし、微小構造体の可動範囲を大きくするために、梁を長くすることや、片持ち梁形状に加工することも可能である。また、第1の層407を厚く成膜し、櫛歯型に加工することで横方向へ可動する構造層を有する微小構造体を作製することもできる。

30

### 【0139】

次に、図11に示すように剥離層403の一部を除去するため剥離層のエッティングを行う。エッティングによって、第1の基板401から第1の層407を剥離しやすくすることができる。例えば、本実施の形態のように剥離層403をタンゲステンで形成した場合、剥離層403エッティングは、アンモニア過水を用いたウエットエッティングによって行うことができる。ここでアンモニア過水とは、アンモニア、過酸化水素水及び純水を混合した液体であり、例えば28%のアンモニアと31%の過酸化水素水と純水とを3:5:2で混合することで得られる。

### 【0140】

図11に示すように剥離層のエッティングを行うことなく工程を進めることも可能である。また、剥離層のエッティングの代わりに、第1の基板401を加熱する、または裏面からレーザ光を照射することで剥離層403を脆弱化させ、第1の基板401から第1の層407を剥離しやすくする工程を行うことも可能である。

40

### 【0141】

上記工程により、第1の層を有する基板409を形成することができる。第1の層を有する基板409は上記例のみに限定されず、例えば、図12(A)に示すように、第1の層407内に重りとなる層を形成し、構造層の可動性を高めることができる。ここで重りとなる層は、金属のように密度の高い物質を用いて形成することができる。

### 【0142】

図10(B1)、(B2)に示すように、片方の梁のみに第1の導電層405が形成さ

50

れていると、左右でバネ定数が異なるため、図12(B)に示すように、両方の梁410に第1の導電層405を形成し、両持ち梁の左右の梁410のバランスを取るように加工することも可能である。

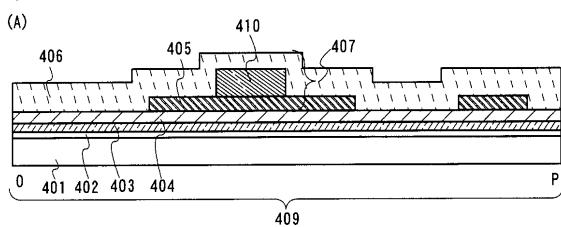

#### 【0143】

次に、図13(A1)、(A2)を用いて、第2の層を有する基板を作製する例を示す。

#### 【0144】

まず、図13(A1)、(A2)に示すように、第2の基板411(第1の本基板とも記す)上に第2の導電層413を形成する。ここで第2の基板411は、第1の基板401と同様に、ガラス基板や石英基板、プラスチック基板、さらには、金属等の導電性を有する基板や、シリコン、ゲルマニウム、またはシリコンとゲルマニウムの化合物等の半導体性を有する基板を用いることができる。本実施の形態では、第1の基板401と同様、ガラス基板を用いる例を示す。

#### 【0145】

第1の基板401、または第2の基板411として使用する基板は、本実施の形態の例に限定されず、他の基板を用いることができる。例えば、高温で成膜および加工を行うプロセスを適用したい場合、第1の基板401もしくは第2の基板411のいずれか一方にシリコン等の半導体基板を適用し、もう一方にガラスや石英等の安価な基板を用いることも可能である。具体的には、一方の基板は半導体基板を用いて半導体素子で電子回路を形成し、他方の基板はガラス基板を用いて構造層(第1の層407)を形成する、等のように基板を使い分けることによって目的に応じた微小構造体を作製することも可能である。

#### 【0146】

第2の基板411は、前記第1の基板401と同様、準備した基板をそのまま用いてよく、酸化シリコン、窒化シリコンまたは酸化窒化シリコン等の絶縁性を有する膜を用いて保護層を形成してから用いることもできる。本実施の形態では、第1の基板401と同様、第2の基板411上に保護層412として厚さ100nmの酸化窒化シリコン層をCVD法により形成し、保護層412の上に第2の導電層413を形成する例を示す。

#### 【0147】

次に、図13(A1)、(A2)に示すように、保護層412上に、第2の導電層413を形成する。第2の導電層413は、第1の導電層405と共に構造層を駆動させるための導電層であり、基板上に固定された固定電極となる。第2の導電層413の形成は、次のように行うことができる。導電性を有する材料をスパッタリング法やプラズマCVD法等を用いて成膜する。成膜された材料上に、フォトリソグラフィ法を用いてレジストマスクを形成する。レジストマスクを用いて成膜された材料をエッチングにより加工する。第2の導電層413の材料は、第1の導電層405と同様、アルミニウム(A1)、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)等の金属元素、またはこれらの金属元素を主成分とする導電性を有する化合物を用いることができる。本実施の形態では、第2の導電層413として、厚さ100nmのチタン、および400nmのアルミニウムをスパッタリング法により積層させて形成する例を示す。

#### 【0148】

本実施の形態では、第2の導電層413として、微小構造体を駆動させるために使用する固定電極413aと、可動電極(第1の導電層405)および固定電極と電源や信号線に接続する配線413bとを形成する。図13(A1)、(A2)に示す配線413bは、第1の導電層405と電気的に接続される配線である。これらの配線は、基板内または基板外のいずれかに接続されるが、説明の都合上、固定電極413a、配線413bは紙面の範囲内で記載している。

#### 【0149】

本実施の形態では、上記で形成した保護層412、第2の導電層413の積層構造を第2の層414と記載する。上記工程により、第2の層を有する基板415を形成することができる。

10

20

30

40

50

## 【0150】

次に、図13( B1 )、( B2 )に示すように、第2の層を有する基板415上に、選択的に第1のスペーサ層416を形成する。第1のスペーサ層416は、実施の形態1乃至3と同様、絶縁性を有する無機化合物や有機化合物等を用い、単層もしくは積層構造で形成することができる。例えば、第1のスペーサ層416を形成する無機材料としては、酸化シリコン、窒化シリコンを用いることができる。また、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シリコサン、ポリシラザンを用いることができる。さらには、ポリイミドやエポキシ等の有機化合物を主原料とする永久性の厚膜レジストを使用することも可能である。

## 【0151】

選択的領域に第1のスペーサ層416を形成する方法としては、スクリーン印刷法や、インクジェットに代表される液滴吐出法等を適用することも可能である。これらの方法は、特に溶媒によって粘度を調節することのできる有機材料を用いる場合に有効であることが多い。また、レジストのように感光性の材料を用いることで、成膜、露光、および現像のみで第1のスペーサ層416を形成することもできる。

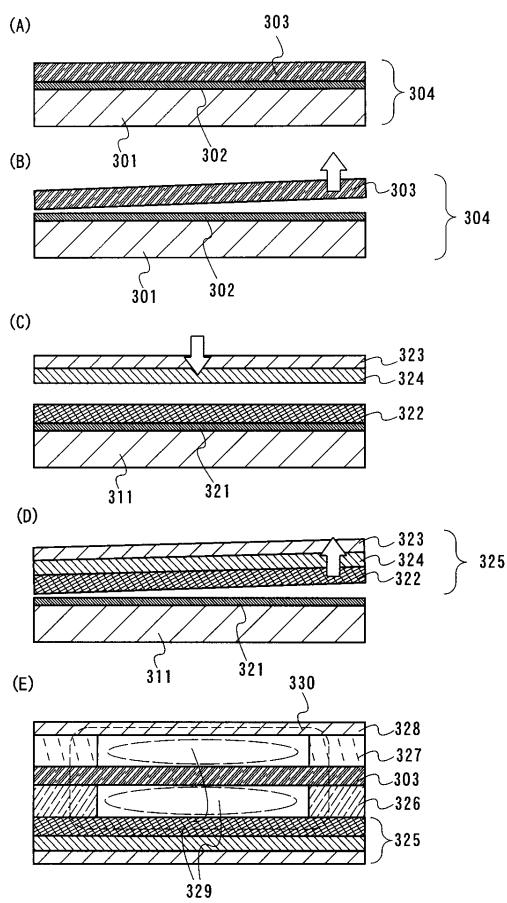

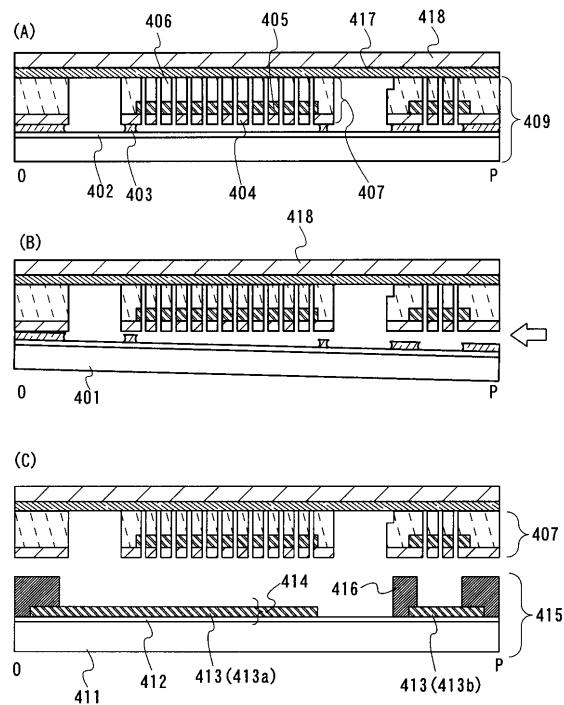

## 【0152】

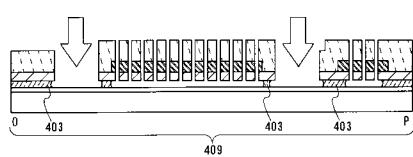

次に、図14～図15を用いて、第1の層を有する基板409から第1の層407を剥離し、第2の層を有する基板415に貼り合わせる例を説明する。なお、図面は第1の層を有する基板409および第2の層を有する基板415の上面図の鎖線OPにおける断面図を示している。

## 【0153】

図14(A)に示すように、第1の層を有する基板409上面に第3の基板418(第2の仮基板とも記す)を貼り合わせる。第3の基板418は、第1の基板401から第1の層407を剥離するための支持基板であるため、ガラス基板やプラスチック基板以外に、フィルムのように薄くて柔らかい基板を使用することができる。

## 【0154】

また、第3の基板418と第1の層を有する基板409との貼り合わせには、接着性が弱く、容易に取りはずすことができる接着剤417を利用することができます。ここで、容易に取りはずすことができる接着剤417の代表例としては、熱可塑性樹脂を挙げることができる。熱可塑性樹脂とは、加熱処理により接着力が低下する層となり、例えば、加熱によって軟化する材料、加熱により膨張するマイクロカプセルや発泡剤を混入した材料、熱硬化性樹脂に熱溶融性や熱分解性を付与した材料、水の侵入による界面強度劣化やそれに伴って吸水性樹脂が膨張する材料を用いて形成される。また、接着剤417は紫外線照射を行うことによって、接着力が低下する樹脂を用いることもできる。さらに、第1の層407において構造層となる部分には接着剤が付着しないよう、第3の基板418上に接着剤417を選択的に形成することも可能である。

## 【0155】

次に、図14(B)に示すように、基板409から第1の層407を剥離する。本実施の形態では、剥離層403としてタンゲステンを成膜し、その上に下地層404として窒化酸化シリコンを形成しているので、剥離層403と下地層404との間には酸化タンゲステンの層が形成され、当該酸化タンゲステンの層と下地層404との界面で密着性が低下している。さらに剥離層403エッティングによって剥離層403の一部を除去しているので、剥離は第1の層407を第3の層へ物理的に写し取る方法を適用する。このとき、さらに剥離層403の密着性を低下させるために、基板裏面からレーザ光の照射を行うことも可能である。

## 【0156】

物理的に写し取る方法(転写方法)として、具体的には、剥離層403エッティングを行った第1の層を有する基板409上に、第3の基板418を貼り合わせ、当該第3の基板418を第1の基板401から引きはがすことで第1の層407を第3の基板418側へ写し取ることができる。このとき、第1の層407に剥離層403が付着している場合が

あるので、第1の層407から剥離層403を除去する工程を追加することも可能である。

### 【0157】

次に、図14(C)に示すように、第3の基板418に貼り合わされている第1の層407を、第2の層を有する基板415上面から貼り合わせる。図14(C)では、第1の層407が第1の基板401と接着していた側に、第1のスペーサ層416を介して、第2の層を有する基板415と貼り合わせる例を示している。

### 【0158】

次に、図15(A)に示すように、加熱等の処理により接着剤417の接着力を低下させ、第1の層407と第3の基板418とを分離する。例えば、接着剤417として熱可塑性樹脂を用いた場合には、120度程度の加熱処理によって第3の基板418を分離することができる。このとき、接着剤417は第3の基板418側に付着しており、第1の層407には残留しない。

### 【0159】

第1の層407と第3の基板418を分離することにより、図15(B)に示すような微小構造体420が形成される。微小構造体420には、第2の基板411上に第2の層414、第1のスペーサ層416、および第1の層407が積層され、第1のスペーサ層416が存在しない部分には、第1の層407と第2の層との間に空間部分421が形成される。また、第1の層407はその空間部分421の上に存在する。また、第1の層407は、第1のスペーサ層416と接着している部分が第2の基板411に支持され、第2の層を有する基板415と離れて設けられる部分が可動することができる構造層となる。

### 【0160】

次に、第1の層407内の第1の導電層405と、配線を形成する第2の導電層413とを電気的に接続するため、図15(B)に示すように、配線を形成する領域上に導電性ペースト419を滴下する。そして、図15(C)に示すように、導電性ペースト419によって第1の層407と第2の層414との間隙を埋めることにより、第1の導電層405を、第2の導電層413で形成した配線413bと電気的に接続することができる。

### 【0161】

ここで導電性ペースト419とは、粒径が数 $\mu\text{m}$ から数十 $\mu\text{m}$ の導電性粒子を有機樹脂に溶解又は分解させたものを指す。導電性粒子としては、銀、銅、アルミニウム、金、ニッケル、白金、パラジウム、タンタル、モリブデン、およびチタン、等の金属粒子、ハロゲン化銀の微粒子、または分散性ナノ粒子等を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子バインダー、溶媒、分散剤及び被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、フェノール樹脂、シリコン樹脂等の有機樹脂が挙げられる。また、導電層の形成にあたり、ペーストを滴下した後に焼成することが好ましい。例えば、ペーストの材料として、銀を主成分とする微粒子（例えば粒径1nm以上100nm以下）を用いる場合、150~300の温度範囲で焼成することにより硬化させて導電層を得ることができる。

### 【0162】

また、微小構造体420を保護するため、図15(D)に示すように、第1の層407上に第2のスペーサ層422を形成して、第1の層を有する基板409と第4の基板423(第2の本基板とも記す)を貼り合わせることができる。第2のスペーサ層422は、第1のスペーサ層416と同様、絶縁性を有する無機化合物や有機化合物等を用い、単層もしくは積層構造で形成することができる。また、第2のスペーサ層422は、第4の基板423上に形成し、第1の層を有する基板409と第4の基板423とを貼り合わせることも可能である。そして、第4の基板423は、空間部分424を介して第1の層407を保護するパッケージとしての役割を有するので、薄くて柔らかく、安価な基板、例えば、プラスチックフィルムのような基板を用いることができる。しかし、第1の基板401と同様、ガラスや石英等の基板を用いることも可能である。

10

20

30

40

50

**【 0 1 6 3 】**

上記の工程でえられた微小構造体 4 2 0 の第 1 の層の上面図を、図 1 0 ( B 1 ) に示す。第 1 の層 4 0 7 ( 構造層 ) は、第 1 の領域 4 2 5 、第 2 の領域 4 2 6 、および第 3 の領域 4 2 7 を有している。第 1 の領域 4 2 5 は第 1 のスペーサ層 4 1 6 および第 2 のスペーサ層 4 2 2 により固定されている領域である。第 2 の層を有する基板 4 1 5 の表面と第 1 の領域 4 2 5 との間には第 1 のスペーサ層 4 1 6 が設けられ、第 1 の領域 4 2 5 を第 2 の基板 4 1 1 に固定している。また、第 1 の領域 4 2 5 と第 4 の基板 4 2 3 ( 保護基板 ) との間には第 2 のスペーサ層 4 2 2 が設けられ、第 1 の領域 4 2 5 は第 4 の基板 4 2 3 に固定されている。第 2 の層を有する基板 4 1 5 の表面と第 2 の領域 4 2 6 および第 3 の領域 4 2 7 との間、および第 2 の領域 4 2 6 および第 3 の領域 4 2 7 と第 4 の基板 4 2 3 との間には、それぞれ、空間部分が設けられている。第 2 の領域 4 2 6 は第 2 の層を有する基板 4 1 5 の表面および第 4 の基板 4 2 3 と離れて向かい合っており、可動する領域である。第 3 の領域 4 2 7 はバネとして機能し、固定された第 1 の領域 4 2 5 と可動する第 2 の領域 4 2 6 とを連結している。

**【 0 1 6 4 】**

次に、上記とは異なり、接着剤 4 1 7 および第 3 の基板 4 1 8 を使用せずに第 1 の層 4 0 7 を第 2 の層を有する基板 4 1 5 に貼り合わせる方法について、図 1 6 を用いて説明する。

**【 0 1 6 5 】**

図 1 6 ( A ) に示すように、第 1 の層を有する基板 4 0 9 と第 2 の層を有する基板 4 1 5 とが、第 1 のスペーサ層 4 1 6 を介して層同士が向かい合うように貼り合わせる。次に、図 1 6 ( B ) に示すように、第 1 の層を有する基板 4 0 9 から、第 1 の基板 4 0 1 を剥離する。ここでは、第 1 の基板 4 0 1 と共に、保護層 4 0 2 も剥離している。次に、第 1 の導電層 4 0 5 と第 2 の導電層 4 1 3 とを接続するために、図 1 6 ( C ) に示すように、配線 4 1 3 b を形成した部分の上から導電性ペースト 4 1 9 を滴下する。そして、図 1 6 ( D ) に示すように、第 2 のスペーサ層 4 2 2 を形成し、第 4 の基板 4 2 3 ( 第 2 の本基板とも記す ) を貼り合わせることにより、微小構造体 4 2 0 を保護することも可能である。

**【 0 1 6 6 】**

上記、図 1 4 及び図 1 5 を用いて説明した貼り合わせの方法は、第 1 の基板 4 0 1 から第 1 の層 4 0 7 を剥離した後に、第 1 の層 4 0 7 と第 2 の層を有する基板 4 1 5 とを貼り合わせている。また、図 1 6 を用いて説明した貼り合わせの方法は、第 1 の層を有する基板 4 0 9 と第 2 の層を有する基板 4 1 5 とを貼り合わせた後に、第 1 の基板 4 0 1 を第 1 の層 4 0 7 から剥離している。このように、上記 2 例は工程の順序が異なっている。そして、この工程の違いによって、第 1 の層 4 0 7 が有する二つの面のうちどちらの面が第 2 の層 4 1 4 と向かい合うかが異なる。すなわち、前者の工程を経た場合には、第 1 の層 4 0 7 が第 1 の基板 4 0 1 と接していた方の面が、第 2 の層 4 1 4 と向かい合う面となり、後者の工程を経た場合には、他方の面が第 2 の層 4 1 4 と向かい合う面となる。したがって、どちらの方法を採用するかによって、第 1 の層 4 0 7 の積層関係が逆転する場合もある。

**【 0 1 6 7 】**

このように作製された微小構造体は、例えば、外部から力を受けると構造層が力を受けた方向に可動するため、その動きを検知することによってセンサとして機能させることができる。また、第 1 の層 4 0 7 および第 2 の層 4 1 4 に向かい合う電極を形成し、静電引力で可動させることによりアクチュエータとして機能させることも可能である。そして、このアクチュエータを利用して、スイッチや容量が可変のコンデンサ等を作製することもできる。

**【 0 1 6 8 】**

本実施の形態で説明した本発明の微小構造体を作製する方法を適用することによって、犠牲層エッティングを行わずに微小構造体を作製することができるため、実施形態 1 乃至 3

10

20

30

40

50

と同様、犠牲層エッティングに起因する問題を回避することができる。以下、本実施形態による効果のいくつかを示す。

【0169】

(a) 代表的には、犠牲層エッティングと同様の工程を、剥離および貼り合わせによって行うため、非常に短時間でその工程を行うことができる。

【0170】

(b) 犠牲層エッティングを剥離および貼り合わせによって代替することで、ウェットエッティングを行うときのように微小構造体が液体のエッティング剤に触れることがなく、毛管現象による構造層と基板との貼り付きを生じないように作製することができる。

【0171】

(c) 本発明の方法は、剥離および貼り合わせにより微小構造体を作製するため、空間部分に犠牲層やエッティング時の副生成物が残留するといった問題を生じさせることなく微小構造体を作製することができる。すなわち、ある基板、または基板の一部では犠牲層エッティングができているにも関わらず、他の基板、または基板内の他の部分では犠牲層エッティングが終了しなかった、という問題を回避することができる。さらに本発明の方法は、第1の基板401から剥離した第1の層407を、第2の層を有する第2の基板411に貼り合わせるため、基板上に作製されるすべての微小構造体の空間部分を均一に形成することができる。

【0172】

(e) また、本発明は長時間を要する犠牲層エッティング工程を不要とするため、他の層に悪影響を与えることがない。例えば、犠牲層エッティング時に構造層の膜減りが起こらないので、構造層の膜厚を均一に形成することができる。また、剥離層403エッティングを行う場合に、当該エッティングによって時に影響が懸念される材料を使用することがあったとしても、当該材料を剥離層403エッティングを行わない第2の基板411上に形成することによってその影響を回避することが可能である。

【0173】

(f) また、本発明の方法は、基板と第1の層407との間の空間部分の距離が、第1のスペーサ層416の厚さによって決定され、第1の層407において、基板に固定されている部分と可動できる部分との間の空間の距離は第1のエッティングによって決めることができる。したがって、微小構造体が有する空間部分の大きさは、犠牲層エッティングに起因する犠牲層の厚さや面積によって限定されることなく任意に設計することができる。

【0174】

(g) 同様に、本発明は剥離および貼り合わせによって微小構造体を作製するので、大きさを限定することなく、任意の大きさの微小構造体を作製することができる。例えば、数mmから十数mm角のように大きな微小構造体の作製を行うことも可能である。

【0175】

(i) また、本発明は犠牲層を形成せず、さらに、第1の層407と第2の層とを別々に形成して貼り合わせを行うため、犠牲層のように厚い膜によって生じる段差部分がなく、その段差乗り越え部分から生じる破壊が起こらない。したがって、強度の高い微小構造体を作製することができる。

【0176】

なお、本実施の形態は他の実施の形態と自由に組み合わせて行うことができる。

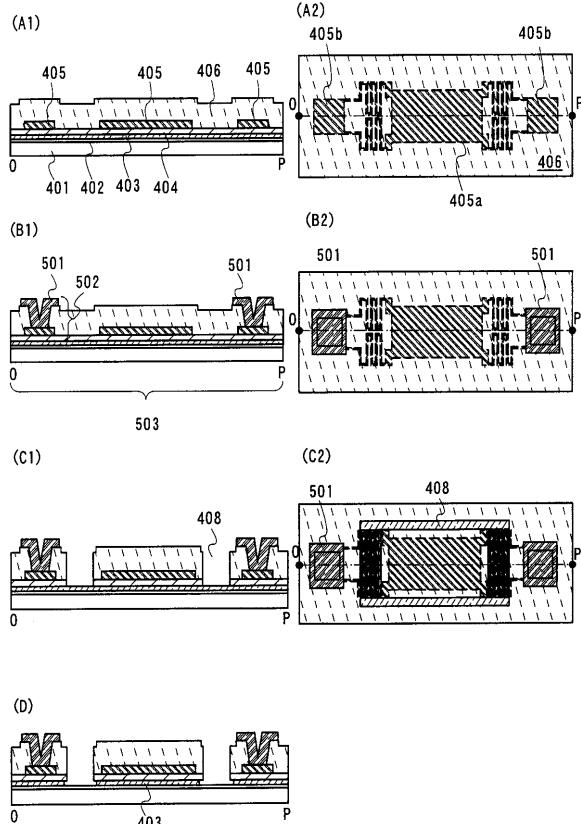

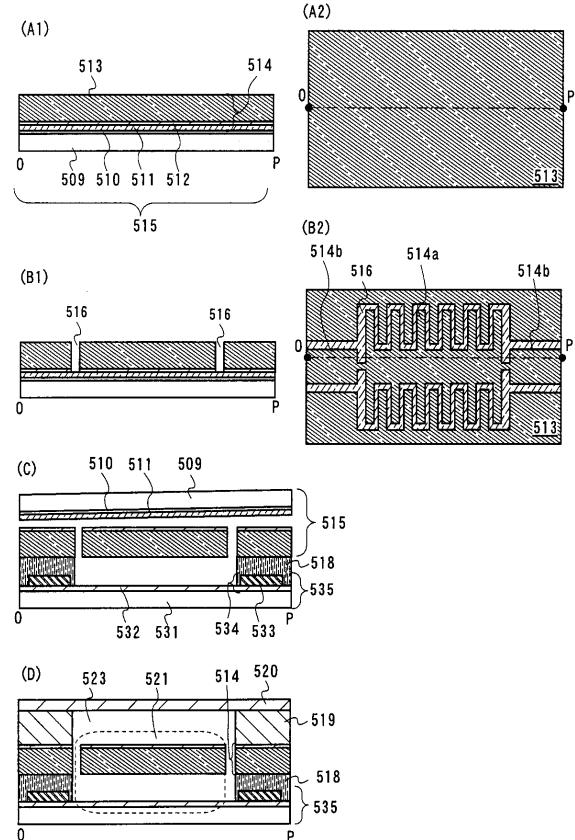

【0177】

(実施の形態5)

本実施の形態では、上記実施の形態で説明した微小構造体の作製方法を、図17～図20を用いて具体的に説明する。なお、図面において図面は右側が基板上面図、左側が上面図の鎖線OPにおける断面図を示す。

【0178】

初めに、図17を用いて、第1の基板の加工方法を説明する。

【0179】

10

20

30

40

50

まず、図17(A1)、(A2)に示すように、第1の基板401(第1の仮基板とも記す)上に保護層402、剥離層403、下地層404、第1の導電層405、および第1の絶縁層406を順次形成する。ここまで工程は、上記実施の形態4で説明したものと同様の方法を適用することができる。

#### 【0180】

ここで第1の導電層405は、微小構造体の可動電極を形成する部分405aと、可動電極を他の導電層と電気的に接続する配線を形成する部分405bとを有する。また、上記実施の形態4と同様に、第1の層を折れ曲がった支持梁を有する両持ち梁構造とするため、第1の導電層405は配線と可動電極との間に設けられている支持梁内を支持梁の形状に沿って設けられている。10

#### 【0181】

次に、図17(B1)、(B2)に示すように、第1の導電層405の配線部分405bの上にある第1の絶縁層406に、第1の導電層が露出するようにコンタクトホールを設け、第1の絶縁層406上およびコンタクトホール上に第3の導電層501を形成する。10

#### 【0182】

コンタクトホールは、フォトリソグラフィ法を用いてレジストマスクを形成し、エッチングを行うことで形成することができる。例えば、第1の絶縁層に酸化窒化珪素を用いて形成し、異方性のドライエッチングを適用してコンタクトホールを形成する場合、エッチング用ガスとして、CHF<sub>3</sub>、HF、C<sub>2</sub>F<sub>6</sub>、ならびにC<sub>4</sub>F<sub>8</sub>およびH<sub>2</sub>等を用いることができる。また、上記のガスにAr、He等を混合することにより、エッチング時に発生する化合物の堆積を抑制することができる。20

#### 【0183】

第3の導電層501は、第1の導電層405と同様、アルミニウム(A1)、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)等の導電性を有する金属元素、またはこれらの金属元素を主成分として導電性を有する化合物を用いる。このような導電性の材料をスパッタリング法やプラズマCVD法等の公知の手段を適用して成膜する。フォトリソグラフィ法を用いてレジストマスクを形成し、成膜された導電性の材料にエッチングを行うことで所定の形状に加工することで、第3の導電層501を形成することができる。本実施の形態では、第3の導電層501として、厚さ400nmのアルミニウムをスパッタリング法により形成する例を示す。30

#### 【0184】

上記工程により、第1の導電層405と電気的に接続した第3の導電層501が、最上層に設けられる。ここで、上記工程により形成された下地層404、第1の導電層405、第1の絶縁層406、第3の導電層501を第1の層502と記載する。

#### 【0185】

次に、図17(C1)、(C2)に示すように、孔408を形成して第1の層502の形状を決めるための第1のエッチングを行う。そして、図17(D)に示すように剥離層の一部を除去する剥離層エッチングを行う。第1のエッチング、および剥離層エッチングは、上記実施の形態4と同様の方法を適用して行うことができる。40

#### 【0186】

第1のエッチングでは、構造層のバネ定数を小さくして可動しやすくするため、構造層の支持梁となる第1の層502をS字が複数連なった、蛇行するように折り曲げた形状に加工する。また、構造層を形成する第1の導電層405を、外部電源や信号線と電気的に接続するため、第1の導電層405が支持梁内を通るように加工した。しかしながら、第1の導電層405と第1の絶縁層406とを同時に第1のエッチングで加工することも可能である。

#### 【0187】

上記工程により、第1の層を有する基板503を形成することができる。

#### 【0188】

10

20

30

40

50

次に、図18を用いて、第2の層を有する基板を作製する例を示す。

【0189】

まず、図18(A1)、(A2)に示すように、第2の基板411(第1の本基板とも記す)上に保護層412、および第2の導電層413を形成する。ここまででの工程は、上記実施の形態4で説明したものと同様の方法を適用することができる。

【0190】

本実施の形態では、第2の導電層413として、微小構造体を駆動させるために使用する固定電極413aと、可動電極(第1の導電層)および固定電極と電源や信号線に接続する配線413bとを形成する。図18(A1)、(A2)に示す配線413bは、第3の導電層501と電気的に接続される配線である。これらの配線413bは、基板内または基板外のいずれかに接続される配線である。

10

【0191】

保護層412、第2の導電層413の積層体を第2の層414ということとする。上記工程により、第2の層を有する基板415を形成することができる。

【0192】

次に、図18(B1)、(B2)に示すように、第2の層を有する基板415上に、選択的に第1のスペーサ層504を形成する。第1のスペーサ層504は、基板面と垂直方向のみに導電性を有する接着剤(ここでは異方性導電接着剤と記載)を用いる。第1のスペーサ層504を形成する方法は、スクリーン印刷法や液滴吐出法等、上記実施の形態4と同様の方法を適用して行うことができる。

20

【0193】

次に、第1の層502と第2の層414とを貼り合わせる方法について、図19を用いて説明する。図19(A)に示すように、第1の層を有する基板503と第2の層を有する基板415とが、第1のスペーサ層504を介して層同士が向かい合うように貼り合わせる。このように、異方性導電接着剤(第1のスペーサ層504)を介して、第1の層502と第2の層414とが向かい合うように貼り合わせることで、第2の導電層413の配線413bと第3の導電層501の配線部分とが電気的に接続される。

【0194】

次に、図19(B)に示すように、第1の層を有する基板503から第1の基板401を剥離する。第1の基板401と共に保護層402も剥離している。そして、図19(C)に示すように、第2のスペーサ層505を形成し、第4の基板506(第2の本基板とも記す)を貼り合わせることにより、微小構造体508を保護することも可能である。507は空間部分である。第1の層502と第1の基板401を剥離する方法、第2のスペーサ層505を形成して第4の基板506を貼り合わせる方法は、上記実施の形態4と同様の方法を適用して行うことができる。

30

【0195】

このように作製された微小構造体508は、例えば、外部から力を受けると構造層が力を受けた方向に可動するため、その動きを検知することによってセンサとして機能させることができる。また、第1の層502および第2の層414に向かい合う電極を形成し、静電引力で可動させることによりアクチュエータとして機能させることも可能である。そして、このアクチュエータを利用して、スイッチや容量が可変のコンデンサ等を作製することもできる。

40

【0196】

このように、任意の機能を有する微小構造体を作製するためには、それらの用途に合わせて第1の層を加工する。例えば、本例で図17(C1)、(C2)に示すように、第1の層502を両持ち梁型に加工することで、構造層が基板垂直方向(上下方向)に可動する微小構造体を作製することができる。さらに、構造層のバネ定数を低くし、微小構造体の可動範囲を大きくするために、梁を長くすることや、片持ち梁形状に加工することも可能である。また、第1の層502を厚く成膜し、櫛歯型に加工することで横方向へ可動する構造層を有する微小構造体を作製することもできる。

50

## 【0197】

例えば、水平方向へ可動する構造層を有する微小構造体を作製する場合、図20(A1)、(A2)に示すように第1の層514を形成することができる。第1の層514は、保護層510および剥離層511が形成された第1の基板509(第1の仮基板とも記す)上に、下地層512、第1の導電層513が形成されている。第1の導電層513は、上記実施の形態4と同様の方法を適用して形成することができるが、めっき等の方法により短時間で厚い層を形成するような方法を適用しても良い。

## 【0198】

次に、図20(B1)、(B2)に示すように、第1のエッティングを行い、開口部516を形成し、可動電極514aと配線514bとを形成する。開口部516により、可動電極514aと配線514bは、その他の部分から絶縁するために物理的に切り離される。以上で、第1の層を有する基板515が形成される。ここで、第1のエッティング後に剥離層エッティング等、剥離層を脆弱化させる工程を有してもよい。

## 【0199】

第2の層を有する基板535を形成する。第2の層を有する基板535を形成する方法は、図18で示した第2の層を有する基板415と同様に形成することができる。第2の基板531(第2の本基板とも記す)上に積層構造の第2の層534が形成される。第2の層534は保護層532と第2の導電層533の積層体である。

## 【0200】

次に、図20(C)に示すように、第1の層を有する基板515と第2の層を有する基板535とを、第1のスペーサ層518(異方性導電接着剤)を介して貼り合わせる。これにより、第1の層514の配線514bと第2の層534の第2の導電層533が電気的に接続される。次に、第1の基板509を第1の層514から剥離し、第1の基板509を取り除く。ここでは、第1の基板509と共に保護層510および剥離層511も剥離している。

## 【0201】

そして、図20(D)に示すように、第2のスペーサ層519(異方性導電接着剤)を介して第1の層514上に保護基板520(第2の本基板とも記す)を貼り合わせ、微小構造体521を保護する。保護基板520を設けることにより、第1の層514と第2の層534との間、および第1の層514と保護基板520との間に空間部分523が形成される。

## 【0202】

ここで、第2のスペーサ層519(異方性導電接着剤)を介して第1の層を有する基板515と第2の層を有する基板535とを貼り合わせる方法、第1の層514から第1の基板509を剥離する方法、および保護基板520を貼り合わせる方法については、上記実施の形態4等に記載した方法を適用して形成することができる。このように作製された微小構造体521の構造層は、第1の層502を櫛歯型に加工することで第2の基板531に対して平行方向へ可動することができる。例えば、外部から力を受けると構造層が第2の基板531に対して平行方向に可動するため、その動きを検知することによってセンサとして機能させることができる。また、可動電極514aおよび第1の導電層513に向かい合う電極を形成し、静電引力で可動させることによりアクチュエータとして機能させることができる。そして、このアクチュエータを利用して、スイッチや容量が可変のコンデンサ等を作製することもできる。

## 【0203】

本実施の形態で説明した微小構造体を作製する方法を適用することによって、犠牲層エッティングを行わずに微小構造体を作製することができる。すなわち、本実施形態を実施することにより、実施形態1、2で説明した効果(a)~(i)を得ることができる。犠牲層エッティングと同様の工程を、剥離および貼り合わせによって行うため、非常に短時間でその工程を行うことができる。また、微小構造体がウエットエッティングのように液体のエッティング剤に触れることがなく、毛管現象による構造層と基板との貼り付きを生じないよ

10

20

30

40

50

うに作製することができる。このように本発明を適用することによって、微小構造体の作製に要する時間を短縮し、不良の発生を低減することができる。

【0204】

なお、本実施の形態は他の実施の形態と自由に組み合わせて行うことができる。

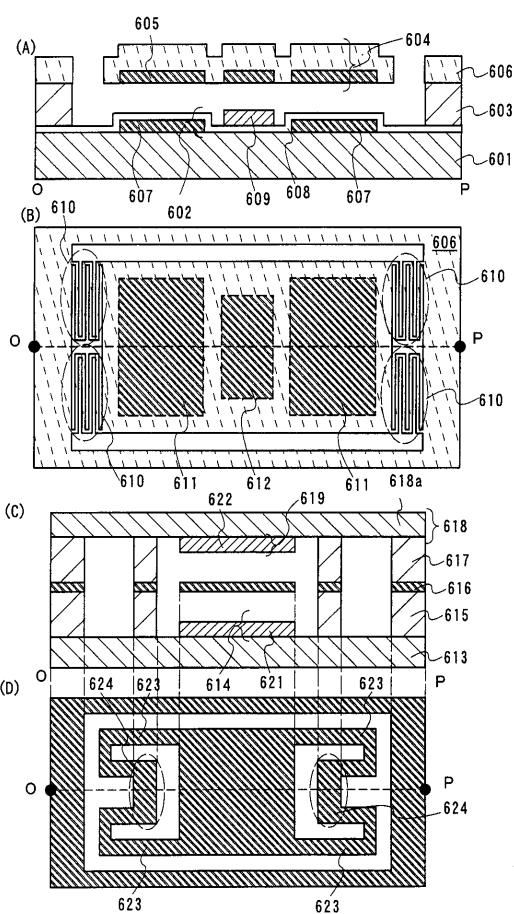

【0205】

(実施の形態6)

本実施の形態では、実施の形態1乃至5で説明した方法で作製できる微小構造体について、機能および形状の例を説明する。

【0206】

図21(A)には、スイッチとして機能する微小構造体(マイクロスイッチとも記載する)の断面図を示す。微小構造体は、第2の基板601(第1の本基板とも記す)上に形成された第2の層602、スペーサ層603、およびスペーサ層603によって第2の基板601上に貼り合わせられた第1の層604を有する。第1の層604および第2の層602は、任意の材料を用いて単層構造又は積層構造として形成することができる。本例では、第1の層604は第1の導電層611、612および第1の絶縁層606を有し、第2の層602は、第2の導電層607、第2の絶縁層608、および第3の導電層609を有する例を示す。

【0207】

図21(B)に、当該微小構造体が有する第1の層604の上面図を示す。第1の層604により、蛇状に折れ曲がった4本の梁610(ビームとも記載する)によって支持された構造層が形成される。梁610は第1の絶縁層606によって形成される。そして、構造層は、静電引力によって微小構造体を可動させる電極(図21(B)内では構造層の第1の導電層611を指す、引き下げ電極とも記載する)、および接触や静電容量の変化によって信号を伝える電極(図21(B)内では構造層の第2の導電層612を指す)を有する。また、図21(A)に示す、第2の導電層607が、引き下げ電極(第1の導電層611)と対になる電極として機能する。

【0208】

第1の導電層611と第2の導電層607とが対になって形成される上下の引き下げ電極間に電圧を印加すると、構造層が静電引力によって第2の基板601側(下方向)に引き下げられる。そして、第1の導電層605によって形成される信号を伝える電極(第2の導電層612)が、第3の導電層609と接触する、または第1の導電層605と第3の導電層609間の距離が変わることによって静電容量が変化することにより、マイクロスイッチはスイッチとして機能する。

【0209】

前記実施の形態でも示したように、構造層を支持するビーム610を細くすることによって、バネ定数を低くすることができるため、構造層を引き下げる時の駆動電圧を小さくすることができる。また、ビーム610を蛇状に折り曲げた構造にすることで、微小構造体が占める面積を小さくすることができる。

【0210】

このようなマイクロスイッチは、半導体素子とは異なり、導電層の接触により信号を伝達し、信号を伝達しない時は導電層が離れているので、信号伝達時の損失が少なく、信号を伝達しない時の絶縁性が優れたスイッチとなる。

【0211】

次に、図21(C)には、動きセンサとして機能する微小構造体(センサとも記載する)の断面図を示す。微小構造体は、第2の基板613(第1の本基板とも記す)上に形成された第2の層614、第1のスペーサ層615、第1の層616、第2のスペーサ層617、および第3の層を有する基板618を有する。第1の層616は、第1のスペーサ層615によって第2の基板613上に貼り合わせられている。第2のスペーサ層617によって、第3の層を有する基板618は第1の層616に貼り合わせられている。第3の層を有する基板618は基板618a(第2の本基板とも記す)上に単層構造の第3の

10

20

30

40

50

層 6 1 9 を有する。

【 0 2 1 2 】

第 1 の層 6 1 6 、第 2 の層 6 1 4 、および第 3 の層 6 1 9 は、任意の材料を用いた積層構造として形成することができる。本例ではそれぞれ、第 1 の層 6 1 6 は第 1 の導電層 6 2 0 を有し、第 2 の層 6 1 4 は第 2 の導電層 6 2 1 を有し、および第 3 の層 6 1 9 は第 3 の導電層 6 2 2 を有する。また、第 1 の層 6 1 6 、第 2 の層 6 1 4 、および第 3 の層 6 1 9 は、さらに、絶縁層等を重ねた積層構造を有していても良い(図 2 1 ( C ) 内には示していない)。

【 0 2 1 3 】

また、図 2 1 ( D ) に、当該微小構造体が有する第 1 の層 6 1 6 の上面図を示す。第 1 の層は、折りたたまれた梁 6 2 3 ( ビームとも記載する ) を有する。構造層を支える梁が折り返された先、すなわち構造層のすぐ横(図 2 1 ( D ) 中丸で囲んだ部分)で基板に支持された微小構造体を形成する。このような、構造層を支持する梁 6 2 3 が基板に固定されている部分をアンカー 6 2 4 と記載する。アンカー 6 2 4 は、第 1 のスペーサ層 6 1 5 および第 2 のスペーサ層 6 1 7 によって、固定されている。このような形状を有する第 1 の層 6 1 6 によって形成された微小構造体は、外部から基板面と垂直な方向に与えられた力によって、力と同方向に可動することができる。そして、この構造層の動きを検知することによってセンサとして機能することができる。

【 0 2 1 4 】

このように、折りたたまれたビーム 6 2 3 によって構造層を支持することで、基板面と平行方向の振動を低減し、基板面と垂直方向の動きを捕らえやすくすることができる。また、折り返したビームの太さや積層構造を変えることで、微小構造体のバネ定数を複数段階に変化させることができる。複数のバネ(通常 2 ~ 3 個のバネ)によって支持されるモデルで表される梁構造にすることができ、例えば、始動時は柔らかいバネで支持し、可動範囲が大きくなる程硬いバネで支持するよう微小構造体の動きを制御することができる。

【 0 2 1 5 】

このようなセンサは、第 1 の層 6 1 6 と第 2 の層 6 1 4 との間の静電容量の変化、および第 1 の層 6 1 6 と第 3 の層 6 1 9 との間の静電容量の変化から、第 1 の層 6 1 6 の可動量を検出することができる。また、第 1 の層 6 1 6 のビーム 6 2 3 に、歪みによって電気特性が変化する材料を用いれば、その電気特性から第 1 の層 6 1 6 の可動量を検出することも可能である。そして、このようなセンサは、検出対象となる外力(物理量)の分解能に応じて検出精度を高めることができる。

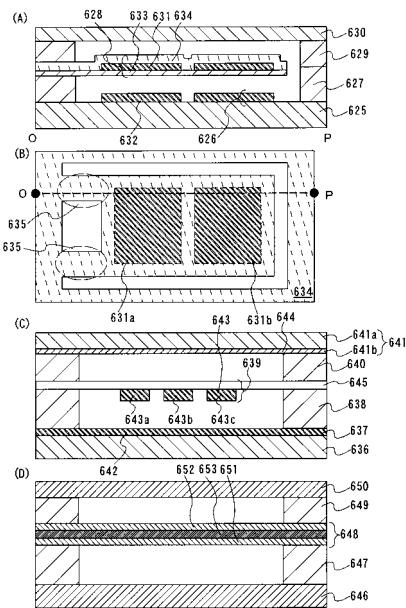

【 0 2 1 6 】

次に、図 2 2 ( A ) には、可変容量として機能する、片持ち梁構造の微小構造体(バラクタとも記載する)の断面図を示す。微小構造体は、第 2 の基板 6 2 5 ( 第 1 の本基板とも記す ) 上に形成された第 2 の層 6 2 6 、第 1 のスペーサ層 6 2 7 、第 1 のスペーサ層 6 2 7 によって第 2 の基板 6 2 5 上に貼り合わせられた第 1 の層 6 2 8 、第 2 のスペーサ層 6 2 9 、および第 2 のスペーサ層 6 2 9 によって第 1 の層 6 2 8 に貼り合わせられた保護基板 6 3 0 ( 第 2 の本基板とも記す ) を有する。

【 0 2 1 7 】

第 1 の層 6 2 8 および第 2 の層 6 2 6 は、任意の材料を用いて単層構造又は積層構造として形成することができる。本例では、第 1 の層 6 2 8 は第 1 の導電層 6 3 1 を有し、第 2 の層 6 2 6 は第 2 の導電層 6 3 2 を有する。また、第 1 の層 6 2 8 および第 2 の層 6 2 6 は、絶縁層等を重ねた積層構造を有していても良く、ここでは、第 1 の層 6 2 8 は第 1 の導電層 6 3 1 を挟むように第 1 の絶縁層 6 3 3 と第 2 の絶縁層 6 3 4 を有する例を示す。

【 0 2 1 8 】

また、図 2 2 ( B ) に、当該微小構造体が有する第 1 の層 6 2 8 の上面図を示す。第 1 の層 6 3 9 ( 構造層 ) は、二つの支持梁 6 3 5 ( ビームとも記載する ) によって可動部分

10

20

30

40

50

が支えられた片持ち梁形状を有する。

【0219】

すなわち、第1の層628（構造層）は、第1の領域、第2の領域、および第3の領域を有している。第1の領域は第1のスペーサ層627および第2のスペーサ層629により固定されている領域である。第2の基板625の表面と第1の領域との間には第1のスペーサ層627が設けられ、第1の領域を第2の基板625に固定している。また、第1の領域と保護基板630との間には第2のスペーサ層629が設けられ、第1の領域は保護基板630に固定されている。第2の基板625の表面と第2の領域および第3の領域との間、および第2の領域および第3の領域と保護基板630との間には、それぞれ、空間部分が設けられている。第2の領域は第2の基板625の表面および保護基板630と離れて向かい合っており、可動する領域である。第3の領域はバネとして機能し、固定された第1の領域と可動する第2の領域とを連結している。

10

【0220】

そして、構造層は静電引力によって微小構造体を可動させる電極631a（図22内では支持梁の横の電極、引き下げ電極とも記載する）、および容量を構成する電極631b（図内では片持ち梁の先の電極）を有する。これらの電極は、第1の導電層631によって形成される。また、第2の導電層632の一方（図22（A）の左側）が、引き下げ電極631aと対になる電極として機能し、他方（図22（A）右側）が電極631bと対になって容量を構成する。

20

【0221】

第1の導電層631と第2の導電層632とが対になって形成される上下の引き下げ電極間に電圧を印加すると構造層が静電引力によって第2の基板625側（下方向）に引き下げられる。そして、第1の導電層631と第2の導電層632とによって形成される容量電極間の距離が変わることによって静電容量が変化するため、図22（A）、（B）に示す微小構造体は可変容量として機能することができる。

30

【0222】

このように片持ち梁構造にすることで、微小構造体のバネ定数を低くし、構造体を可動させるための電圧を低くすることができる。また、図22（B）に示すように、微小構造体を支持する梁635を二つに分けることで、さらにバネ定数を低くすることができる。

【0223】

上記3例のように、第1の層をエッチングによってある形状に加工した後に、第2の基板に貼り合わせることで、様々な形状の微小構造体を形成することができる。しかしながら、第1の層の形状をエッチングによって加工せず、そのまま第2の基板に貼り合わせることによっても微小構造体を作製することが可能である。このように、第1の層をエッチングによって加工せず、第2の層に貼り合わせることによって作製した微小構造体の例を示す。

30

【0224】

まず、図22（C）に、高い周波数の信号を伝達するための導波路として機能する微小構造体の断面図を示す。微小構造体は、第2の基板636（第1の本基板とも記す）上に形成された第2の層637、第1のスペーサ層638、第1のスペーサ層638によって第2の基板636上に貼り合わせられた第1の層639、第2のスペーサ層640、および、第2のスペーサ層640により第1の層639に貼り合わせられた第3の層を有する基板641を有する。第3の層を有する基板641は、基板641a（第2の本基板とも記す）に第3の層641bが形成されている。

40

【0225】

第1の層639、第2の層637および第3の層641bは、任意の材料を用いて積層構造を有することができる。本例では、第1の層639は第1の導電層643及び第1の絶縁層645を有し、第2の層637は第2の導電層642を有し、第3の層641bは第3の導電層644を有する。また、これらの層は絶縁層等を重ねた積層構造を有しても良く、ここでは、第1の層639が第1の絶縁層645を有する例を示す。

50

## 【0226】

第1の層639は、平行に形成された3本の導電層643a～643cを有する。両端の2本の導電層643a、643c、および第2の導電層642、ならびに第3の導電層644を接地電位（グランド電位、アース、基準電位とも記載する）にし、第1の導電層643の中心の1本の導電層643bを信号線として、高周波の信号を伝達するための導波路を形成することができる。

## 【0227】

上記のように作製することで、第1のエッティングによって第1の層を加工すること無しに、導波路として機能する微小構造体を形成することができる。また、当該導波路は、信号線を空間で分離し、周囲をグランド電位でシールドすることで、外部からのノイズを受けにくく、伝達時の損失を少なくすることができる。10

## 【0228】

また、図22(D)には、圧電素子としての微小構造体の断面図を示す。微小構造体は、第1の保護基板646(第1の本基板とも記す)、第1のスペーサ層647によって第1の保護基板646上に貼り合わせられた第1の層648、第2のスペーサ層649、および第2のスペーサ層649により第1の層648に貼り合わせられた第2の保護基板650(第2の本基板とも記す)を有する。

## 【0229】

第1の層648は、任意の材料を用いて積層構造を有することができ、第1の導電層651、第2の導電層652、および第1の導電層651と第2の導電層652に挟まれた圧電層653を有する。また、圧電層653は、ZnO、AlN、PZT等の圧電性を有する材料を用いて形成される。また、第1の層648を圧電層と導電層とを複数回積層して形成してもよい。さらに、第1の保護基板646および第2の保護基板650上に、任意の材料を用いて積層構造を有する第2の層および第3の層を形成してもよい。20

## 【0230】

このように、第1の導電層651と第2の導電層652によって圧電層653を挟んだ圧電素子は、複数の周波数帯域を有する交流信号から、特定の周波数の信号のみを取り出すフィルタ、圧力や加速度を受けて可動することにより電圧を発生させるセンサ、または電圧を印加することにより可動するアクチュエータ、等として機能する微小構造体となる。30

## 【0231】

具体的には、複数の圧電素子を並列または直列に接続することによって、複数の周波数帯域を有する交流信号から、特定の周波数の信号のみを取り出すフィルタを形成することができる。また、第1の層648を可動する構造に形成すれば、外部から圧力や加速度等の力を受けて第1の層が可動することにより、第1の導電層651と第2の導電層652との間に電位差が生じるため、これを検知することによりセンサとして機能させることができる。さらに、第1の導電層651と第2の導電層652との間に電圧を印加することで、第1の層648を可動させることができ、この動きを利用したマイクロポンプのようなアクチュエータを形成することができる。

## 【0232】

本実施の形態で示したように、本発明の微小構造体を作製する方法は、第1の層を第1のエッティングによって加工することで、様々な形状を有する微小構造体を作製することができる。また、本発明の微小構造体を作製する方法は、任意の材料を用いて積層構造を有する第1の層、第2の層、または第3の層を形成することで、様々な機能を有する微小構造体を作製することができる。40

## 【0233】

なお、本実施の形態は他の実施の形態と自由に組み合わせて行うことができる。

## 【0234】

(実施の形態7)

本発明のマイクロマシンは、電気回路および微小構造体を有し、電気回路は複数の半導

50

体素子によって構成され、微小構造体は構造層と構造層に隣接する空間部分を有することを特徴とする。電気回路は微小構造体に電気的に接続され、微小構造体の動作を制御する、または微小構造体から出力される微小さな信号を受信して処理する。本実施の形態では、微小構造体、および電子回路を構成する半導体素子を同一基板上に作製する方法について、図面を用いて説明する。

#### 【0235】

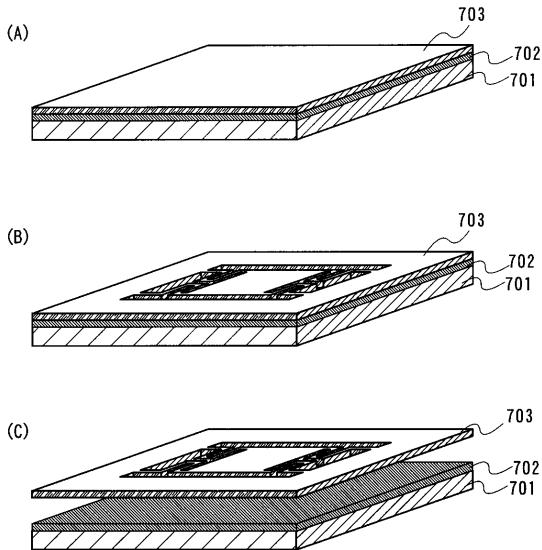

本発明のマイクロマシンの作製方法は、まず、図23(A)に示すように、第1の基板701(第1の仮基板とも記す)上に剥離層702、および第1の層703を形成する。第1の層703は、任意の材料を用いて積層構造に形成することができ、微小構造体の構造層を構成する。第1の層703を積層で形成する場合、複数の層を連続して成膜することも可能であるが、成膜と加工を繰り返して積層することも可能である。成膜した層の加工は、フォトリソグラフィ法によるレジストマスクの形成、およびエッチングによって行うことができる。

#### 【0236】

次に、図23(B)に示すように、第1のエッチングによって第1の層703を加工することで、構造層の形状を作成する。第1のエッチングは、上記第1の層703を形成する層の加工と同様、フォトリソグラフィ法によるレジストマスクの形成、およびエッチングによって行うことができる。第1の層703が複数の異なる材料の積層で形成されている場合、第1のエッチングによる第1の層703の加工にドライエッチングを適用することで、エッティングガスを切り替えながら連続的に積層された層を加工することが可能である。

#### 【0237】

次に、図23(C)に示すように、第1の基板701から第1の層703を剥離する。第1の層703の剥離は、密着性の低い(または低くすることができる)剥離層702と第1の層703との界面から行うことができる。剥離層702の形成方法、および第1の層の剥離方法は、上記実施の形態1などで説明した方法を適用することができる。

#### 【0238】

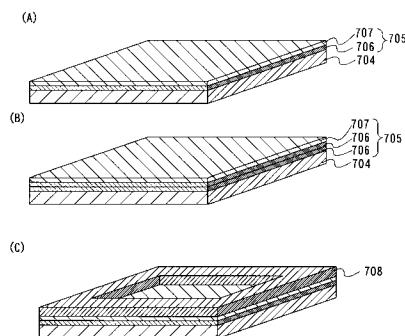

次に、本発明のマイクロマシンの作製方法は、図24(A)に示すように、第2の基板704(第1の本基板とも記す)上に第2の層705を形成する。本発明のマイクロマシンが有する電気回路は、第2の層705に半導体素子を形成することによって作製する。したがって、第2の層705は、半導体素子を有する層706、および、第1の層と対になって微小構造体を形成する層707を有する。

#### 【0239】

また、半導体素子を有する層を複数積層されていてもよい。図24(B)は、第2の基板704上に半導体素子を有する層706を2層積層する例を示す。このように半導体素子を有する層706を積層する場合、第2の基板704上に直接積層させて形成してもよく、別の基板に作製した半導体素子を有する層706を、上記実施の形態で説明した剥離プロセスを用いて複数層を第2の基板704に積層させることも可能である。

#### 【0240】

次に、図24(C)に示すように、第2の層705が形成された第2の基板上の選択的領域にスペーサ層708を形成する。スペーサ層708は、実施の形態2等で説明したように、絶縁性を有する無機化合物や有機化合物等を用い、単層もしくは積層構造で形成することができる。選択的領域にスペーサ層を形成する方法としては、スクリーン印刷法や、インクジェットに代表される液滴吐出法等を適用することも可能である。これらの方法は、特に溶媒によって粘度を調節することのできる有機材料を用いる場合に有効であることが多い。また、レジストのように感光性の材料を用いることで、成膜、露光、および現像のみでスペーサ層を形成することもできる。

#### 【0241】

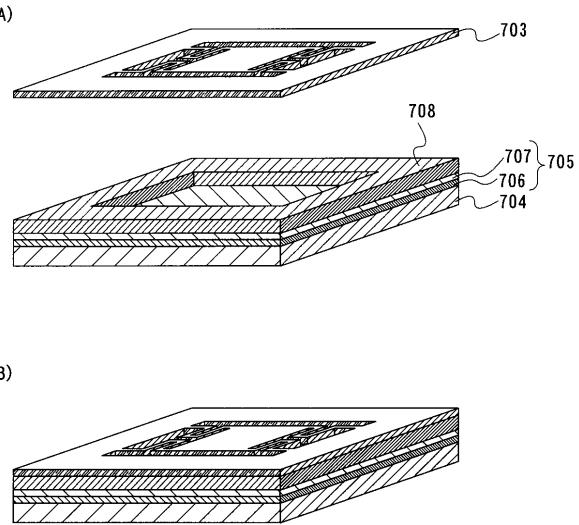

そして、本発明のマイクロマシンの作製方法は、図25(A)、(B)に示すように、上記工程で作製した第1の層703、および第2の層705が形成された第2の基板70

10

20

30

40

50

4を、スペーサ層708を介して貼り合わせる。このように、第1の層703と第2の層705とをスペーサ層708を介して貼り合わせることによって、電気回路および微小構造体を有するマイクロマシンを作製することができる。

#### 【0242】

次に、第2の層が有する半導体素子を有する層の作製方法について図面を用いて説明する。図面において、図26(A1)、図26(B1)、図27(A)、図28(A)、及び図29(A)には上面図を示し、上面図の鎖線O-Pにおける断面図を図26(A2)、図26(B2)、図27(B)、図28(B)、及び図29(B)に示す。

#### 【0243】

本発明のマイクロマシンが有する微小構造体、および半導体素子は、ガラス基板や、石英基板、プラスチック基板等、絶縁性を有する基板上に作製することができる。また、金属等の導電性を有する基板や、シリコン、ゲルマニウム、またはシリコンとゲルマニウムの化合物等の半導体性を有する基板を用いることも可能である。上記のような基板を用いる場合、基板をそのまま用いることも可能であるが、基板表面に絶縁性を有する層を形成してから用いることもできる。

#### 【0244】

例えば、プラスチックのように薄くて柔らかい基板に微小構造体および半導体素子を形成することで、柔軟性が高く、薄型なマイクロマシンを作製することができる。またガラス基板を用いて微小構造体および半導体素子を作製した場合、基板を裏面から研磨して薄くすることによって、薄型なマイクロマシンを形成することも可能である。

#### 【0245】

本実施の形態では、絶縁性の表面を有する基板709上に下地となる層(下地層710)を形成する(図26(A2)参照)。下地層710は酸化シリコン、窒化シリコンまたは酸化窒化シリコン等の絶縁性を有する膜を用いて形成することができる。また、下地層710は上記に挙げた材料を用いて単層で形成してもよく、複数の材料を積層して形成することも可能である。本実施の形態では下地層を2層に積層する例を示す。

#### 【0246】

下地層710の一層目としては、プラズマCVD法を用い、SiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>O及びH<sub>2</sub>を反応ガスとして成膜される酸化窒化シリコン膜を10~200nm(好ましくは50~100nm)形成することができる。本実施の形態では、膜厚50nmの酸化窒化シリコン膜を形成する。次いで下地層710の二層目に、プラズマCVD法を用い、SiH<sub>4</sub>及びN<sub>2</sub>Oを反応ガスとして成膜される酸化窒化シリコン膜を50~200nm(好ましくは100~150nm)の厚さに積層形成することができ、本実施の形態では膜厚100nmの酸化窒化シリコン膜を形成する。

#### 【0247】

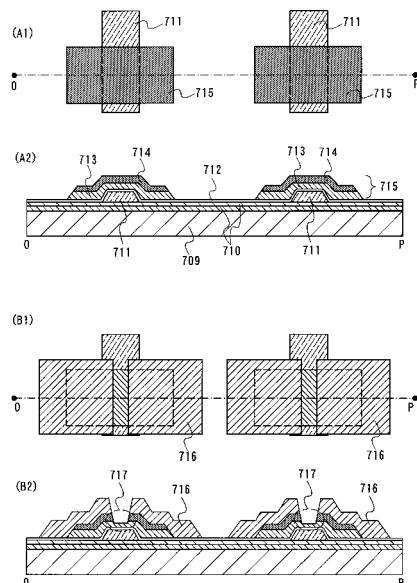

次に、下地層710上に、半導体素子を構成するゲート電極711(第1の導電層)を形成する。ゲート電極711は、モリブデンやタンクスチタン等、導電性を有する金属や化合物をスパッタリング法やCVD法等を用いて成膜し、フォトリソグラフィ法およびエッチングにより加工する(図26(A1)参照)。

#### 【0248】

ゲート電極711の加工はエッチング(特に異方性のドライエッチング)によって行う。異方性のドライエッチングの例としては、ICP(Inductive Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。このとき、エッチング条件(コイル型の電極に印加される電力量、基板709側の電極に印加される電力量、基板側の電極温度等)を適宜調節することで、加工性を高めることができる。なお、第1の導電層、および第2の導電層ならびにゲート電極を加工するエッチング用ガスとしては、CCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガスにO<sub>2</sub>を組み合わせて用いることができる。

#### 【0249】

また、上記エッチング条件を調節することで、ゲート電極711がテーパー角を有する

10

20

30

40

50

台形状等、任意の形状に加工することも可能である(図26(A1)参照)。ここでテーパー角とは、基板と層断面との角度が鈍角になる角のことであり、テーパー角を有する層の断面は台形状となる。また、このようなエッティングによる加工性を向上させるため、ゲート電極を形成する層を、異なる材料を用いて積層させることもできる。このように、ゲート電極がテーパー角を有する形状に形成することで、段差上に成膜される層を均一に成膜することができる。

#### 【0250】

次に、ゲート電極711上に、第1の絶縁層712(ゲート絶縁層)を形成する。第1の絶縁層712は、上記説明した下地層710と同様、酸化シリコン、窒化シリコン等のシリコンを含む材料を、プラズマCVD法またはスパッタリング法等を用いて成膜することができる。例えば第1の絶縁層712は、プラズマCVD法により115nmの厚さで酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成することができる。しかしながら、当該第1の絶縁層712は酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。

#### 【0251】

また、第1の絶縁層712の材料として、高誘電率を有する金属酸化物、例えば、ハフニウム酸化物やチタン酸化物等を用いることもできる。このような高誘電率材料を用いて第1の絶縁層を形成することにより、半導体素子を低い電圧で駆動することができ、低消費電力のマイクロマシンを作製することができる。

#### 【0252】

また、第1の絶縁層712は高密度プラズマ処理によって成膜することができる。高密度プラズマ処理とは、プラズマ密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上、好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ から $9 \times 10^{15} \text{ cm}^{-3}$ 以下であり、マイクロ波(例えば周波数2.45GHz)といった高周波を用いたプラズマ処理である。このような条件でプラズマを発生させると、低電子温度が0.2eVから2eVとなる。このように低電子温度が特徴である高密度プラズマは、活性種の運動エネルギーが低いため、プラズマダメージが少なく、欠陥の少ない膜を形成することができる。

#### 【0253】

このようなプラズマ処理を可能とする成膜室に基板を配置し、プラズマ発生用の電極、所謂アンテナと被形成体との距離を20mm以上80mm以下、好ましくは20mm以上60mm以下として成膜処理を行う。このような高密度プラズマ処理は、低温プロセス(基板温度400以下)の実現が可能となる。そのため、耐熱性の低いガラスやプラスチックを基板として利用することができる。

#### 【0254】

このような絶縁膜の成膜雰囲気は窒素雰囲気、又は酸素雰囲気とすることができる。窒素雰囲気とは、代表的には、窒素と希ガスとの混合雰囲気、又は窒素と水素と希ガスとの混合雰囲気である。希ガスは、ヘリウム、ネオン、アルゴン、クリプトン、キセノンの少なくとも1つを用いることができる。また酸素雰囲気とは、代表的には、酸素と希ガスとの混合雰囲気、酸素と水素と希ガスとの混合雰囲気、又は一酸化二窒素と希ガスとの混合雰囲気である。希ガスは、ヘリウム、ネオン、アルゴン、クリプトン、キセノンの少なくとも1つを用いることができる。

#### 【0255】

高密度プラズマ処理により形成された絶縁膜は、他の被膜に与えるダメージが少なく、緻密なものとなり、形成された絶縁膜と接触する界面状態を改善することができる。例えば高密度プラズマ処理を用いて第1の絶縁層を形成すると、絶縁層上に形成する半導体層との界面状態を改善することができる。その結果、半導体素子の電気特性を向上させることができる。さらに、このように絶縁膜を微小構造体層上に成膜することによって、微小構造体を形成する層等に与えるダメージを少なくすることができ、構造層の強度を保つことができる。また、第1の絶縁層のみではなく、下地層や他の絶縁膜を成膜する場合にも、高密度プラズマ処理を用いることができる。

10

20

30

40

50

## 【0256】

次に、第1の絶縁層712の上に、半導体素子を構成する第1の半導体層713を成膜する(図26(A1)参照)。第1の半導体層713は、珪素を有する材料から形成することができる。珪素を有する材料には、珪素、ゲルマニウムを0.01~4.5 atom %程度に有するシリコンゲルマニウム等がある。本発明は、非晶質半導体層を形成し、加熱処理により結晶化された結晶性の半導体層を形成する。加熱処理とは、加熱炉、レーザ照射、もしくはレーザ光の代わりにランプから発する光の照射(ランプアニールとも記載)等があり、それらを組み合わせて用いることもできる。

## 【0257】

非晶質半導体層を結晶化して結晶性を有する半導体層を形成するための加熱処理にレーザ照射を用いる場合、連続発振型のレーザビーム(CWレーザビーム)やパルス発振型のレーザビーム(パルスレーザビーム)を用いることができる。レーザビームとしては、Arレーザ、Krレーザ、エキシマレーザ、YAGレーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンンドライトレーザ、Ti:Sファイイヤレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及び当該基本波の第2高調波から第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10~2000cm/sec程度として照射する。

10

20

30

40

50

## 【0258】

なお連続発振の基本波のレーザビームと連続発振の高調波のレーザビームとを照射するようにしてもよいし、連続発振の基本波のレーザビームとパルス発振の高調波のレーザビームとを照射するようにしてもよい。複数のレーザビームを照射することにより、エネルギーを補うことができる。

## 【0259】

またパルス発振型のレーザビームであって、半導体層がレーザビームによって溶融してから固化するまでに、次のパルスのレーザビームを照射できるような発振周波数でレーザレーザビームを発振させるレーザを用いることもできる。このような周波数でレーザビームを発振させることで、走査方向に向かって連続的に成長した結晶粒を得ることができる。具体的なレーザビームの発振周波数は10MHz以上であって、通常用いられている数十Hz~数百Hzの周波数帯よりも著しく高い周波数帯を使用する。

## 【0260】

その他の加熱処理として加熱炉を用いる場合には、非晶質半導体層を400~550で2~20時間かけて加熱する。このとき、徐々に高温となるように温度を400~550の範囲で多段階に設定するとよい。最初の400程度の低温加熱工程により、非晶質半導体層の水素等が出てくるため、結晶化の際の膜荒れを低減することができる。さらに、結晶化を促進させる金属元素、例えばNiを非晶質半導体層上に形成すると、加熱温度を低減することができ好ましい。金属元素としては、Fe、Ru、Rh、Pd、Os、Ir、Pt、Cu、Au等の金属を用いることもできる。さらに加熱処理に加えて、上記のようなレーザを用いて照射を行って結晶性半導体層を形成してもよい。

## 【0261】

また、結晶化を助長させる金属元素はマイクロマシンの汚染源となるため、結晶化した後に除去することも可能である。この場合、加熱処理又はレーザビーム照射による結晶化の後、半導体層上にゲッタリングシンクとなる層を形成し、加熱することにより、金属元素をゲッタリングシンクへ移動させることができる。ゲッタリングシンクには、多結晶半導体層や不純物が添加された半導体層を用いることができる。例えば、半導体層上にアルゴン等の不活性元素が添加された多結晶半導体層を形成し、これをゲッタリングシンクと

して適用することができる。不活性元素を添加することによって、多結晶半導体層にひずみを生じさせることができ、ひずみにより効率的に金属元素を捕獲することができる。またリン等の元素を添加した半導体層を形成することによって、金属元素を捕獲することもできる。

#### 【0262】

また、第1の半導体層は、非晶質シリコンの中に微小な結晶粒を有するシリコン層であっても良い。例えば、CVD法を用いてシリコンの成膜条件を適宜選択することにより、数十nm～数μmの半径を有する結晶粒を形成することができる。また、上記第1の絶縁層の成膜に高密度プラズマ処理を用いる方法を説明したが、上記のように結晶化した半導体層に高密度プラズマ処理を施してもよい。高密度プラズマ処理によって、半導体層表面の改質を行うことができる。その結果、界面状態を改善でき、半導体素子の電気特性を向上させることができる。

#### 【0263】

続いて、上記で成膜した第1の半導体層713上に、N型を付与する不純物元素またはP型を付与する不純物元素が添加された非晶質構造を有する第2の半導体層714を形成する。N型を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用い、P型を付与する不純物元素としては、ボロン(B)を用いることができる。当該不純物を有する半導体には、 $1 \times 10_{20} \sim 1 \times 10_{21} / \text{cm}^3$ の濃度範囲で不純物元素が添加されることが望ましい。本実施の形態では、N型を付与する不純物元素が添加された非晶質半導体を第2の半導体層714として形成する例を示す。

#### 【0264】

次に、上記で形成した第1の半導体層713および第2の半導体層714を任意の形状に加工することで、半導体素子を形成する半導体層715を形成する(図26(A1)、(A2)参照)。半導体層715の加工は、上記と同様、フォトリソグラフィ法およびエッチングによって行うことができる。

#### 【0265】

次に、第2の半導体層714上に、第2の導電層716を形成する(図26(B1)、(B2)参照)。第2の導電層716は、導電性を有するアルミニウム(A1)、チタン(Ti)、モリブデン(Mo)、タンゲステン(W)もしくはシリコン(Si)等の金属元素または化合物等を用いて成膜し、加工することで形成することができる。

#### 【0266】

第2の導電層716は、半導体素子のソース電極、またはドレイン電極を接続する導電層となるため、マイクロマシンを構成するための電気的な接続関係を構成するように加工することができる。このとき第2の導電層716は、半導体素子のチャネル領域となる部分上には形成しない。そして、当該第2の導電層716をマスクとして、第2の半導体層714、および第1の半導体層713の一部をエッチングにより除去することで、半導体素子のチャネル領域717を形成する(図26(B1)、(B2)参照)。本実施の形態では上記の工程により、半導体素子として、Nチャネル型の薄膜トランジスタが形成される(図26(B1)、(B2)参照)。

#### 【0267】

続いて、N型半導体素子、および微小構造体となる部分を覆うように、第2の絶縁層718を形成する(図27(A)参照)。第2の絶縁層718は、絶縁性を有する無機化合物や、有機化合物等により形成することができる。当該第2の絶縁層718は、上記の絶縁性を有する材料を用いて単層で形成してもよく、2層以上に積層させて形成しても良い。この第2の絶縁層718は、第2の導電層716と上層に形成する導電層とを絶縁して寄生容量を低減する。

#### 【0268】

第2の絶縁層718を形成する無機材料としては、酸化珪素、窒化珪素を用いることができる。また、有機材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる

10

20

30

40

50

。なお、シロキサン樹脂とはシリコン(Si)と酸素(O)との結合で骨格構造が構成され、Si-O-Si結合を含む樹脂に相当する。シロキサン樹脂の置換基としては、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)、またはフルオロ基を用いることができる。また、ポリシラザンは、珪素(Si)と窒素(N)の結合を有するポリマー材料を出発原料として形成される。

#### 【0269】

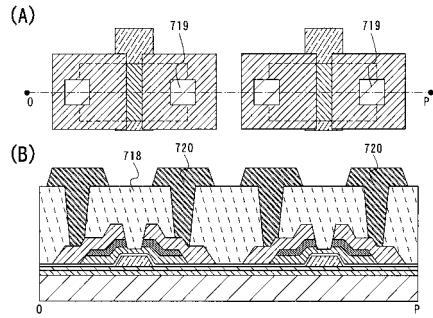

次に、上記第2の絶縁層718をエッティングし、コンタクトホール719を形成する(図27(A)、(B)参照)。このときのエッティング処理は、ドライエッティング処理またはウェットエッティング処理を適用することができる。本実施の形態では、異方性のドライエッティングにより第1のコンタクトホールを形成する例を示す。

10

#### 【0270】

次に、第2の絶縁層718およびコンタクトホール719上に、第3の導電層720を形成する。(図27(B)参照)第3の導電層720は、上記第2の導電層716と同様、導電性を有する金属元素やそれらの化合物等を用いて形成し、加工することができる。第3の導電層720は、半導体素子のソース電極およびドレイン電極との電気的接続は可能であるが、ゲート電極との接続はできないため、ゲート電極に達するコンタクトホールを形成し、当該第3の導電層720と同じ工程で形成された電極を設けて、ゲート電極との接続を行うことができる。

#### 【0271】

上記工程により、半導体素子を有する層を形成することができる。また、上記方法とは異なり、半導体層を形成した後に、選択的領域に不純物元素を添加することにより半導体素子を形成することもできる。以下、そのように半導体素子を形成する方法を説明する。

20

#### 【0272】

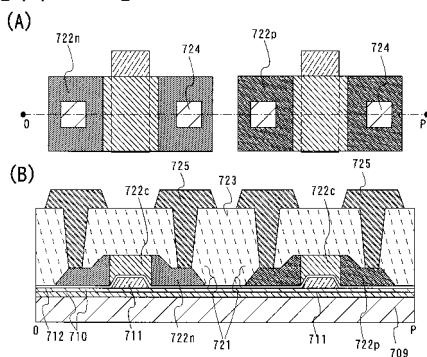

図26及び図27を用いて説明した作製例のように、基板709上に下地層710、第1の導電層711(ゲート電極)、第1の絶縁層712(ゲート絶縁層)を形成した後、半導体層721を形成する(図28参照)。半導体層721は、上記例と同様、珪素を有する材料から形成することができる。本発明は、非晶質半導体層を形成し、加熱処理またはレーザ照射により結晶化された結晶性の半導体層を形成し、所定の形状に加工する。

#### 【0273】

次に、半導体層721に不純物元素を選択的に添加してN型不純物領域722n、および(または)P型不純物領域722pを形成する(図28参照)。不純物領域は、フォトリソグラフィ法により選択的にレジストマスクを形成し、不純物元素を添加することで形成することができる。不純物元素を添加する方法は、イオンドープ法またはイオン注入法で行うことができる。N型を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用い、P型を付与する不純物元素としては、ボロン(B)を用いることができる。N型不純物領域722nには、 $1 \times 10_{20} \sim 1 \times 10_{21} / cm^3$ の濃度範囲でN型を付与する不純物元素が添加されることが望ましい。また、半導体層721に選択的に不純物領域722n、722pを形成することで、チャネル形成領域722cも形成される。

30

#### 【0274】

不純物領域722n、722pを形成した後、不純物元素を活性化するために加熱処理、赤外線の照射、またはレーザ光の照射を行う。特に、室温~300の雰囲気中において、表面または裏面からエキシマレーザを用いて不純物元素を活性化させると、効果的な活性化を行うことができる。このような活性化によって、同時に第1の絶縁層へのプラズマダメージや第1の絶縁層と半導体層との界面へのプラズマダメージを回復することも可能である。またYAGレーザの第2高調波を照射して活性化させてもよく、YAGレーザはメンテナンスが少ないため好ましい活性化手段である。

40

#### 【0275】

また、半導体層721および構造層を覆うように、酸化窒化シリコン膜、酸化シリコンなどの絶縁膜からなるパッシベーション膜を形成し、水素化を行うことも可能である。水

50

素化とは、不純物元素添加によって生じた半導体層 721 のダングリングボンドを、パッシベーション膜に含まれる水素により終端することである。また同時に、上述の不純物領域の活性化処理を行うこともできる。上記水素化は例えば、半導体層上に、プラズマ CVD 法を用いて酸化窒化シリコン膜を 100 nm の厚さに形成し、その後、クリーンオーブンを用いて、300 ~ 550 °C で 1 ~ 12 時間加熱し、半導体層の水素化を行うことができる。また、窒素雰囲気中で 410 °C 、1 時間加熱することも可能である。

#### 【0276】

上記の工程により、半導体素子として、N チャネル型の薄膜トランジスタ及び P チャネル型の薄膜トランジスタが形成される（図 28 参照）。本実施の形態では、N 型半導体素子および P 型半導体素子を形成しているが、いずれか一方のみを用いて電気回路を形成することもできる。このように N 型半導体素子、または P 型半導体素子のいずれか一方のみで電気回路を形成することによって、フォトリソグラフィに使用するレチカル（フォトマスク）の枚数を削減し、作製工程を減らすことができる。

#### 【0277】

続いて、半導体素子上に第 2 の絶縁層 723 を形成する（図 28 (B) 参照）。第 2 の絶縁層 723 は、第 2 の絶縁層 718 と同様、絶縁性を有する無機化合物や、有機化合物等により形成することができる。第 2 の絶縁層は、上記の絶縁性を有する材料を用いて単層で形成してもよく、2 層以上に積層させて形成しても良い。

#### 【0278】

次に、第 2 の絶縁層 723 をエッティングし、コンタクトホール 724 を形成する（図 28 (A) 参照）。このときの、エッティング処理は、ドライエッティング処理またはウェットエッティング処理を適用することができる。本実施の形態では、異方性のドライエッティングによりコンタクトホール 724 を形成する例を示す。

#### 【0279】

次に、第 2 の絶縁層 723 、およびコンタクトホール 724 上に、第 3 の導電層 725 を形成する。第 3 の導電層 725 は、上記例で説明した第 3 の導電層 720 と同様、導電性を有する金属元素やそれらの化合物等を用いて形成し、加工することができる。第 3 の導電層は、半導体素子と接続してソース電極や、ドレイン電極を形成するほか、微小構造体および半導体素子を電気的に接続する。（図 28 (B) 参照）。

#### 【0280】

上記工程により、半導体素子を有する層を形成することができる。また、図 28 に示す方法とは異なり、半導体層を形成した後に第 1 の導電層（ゲート電極）を形成し、第 1 の導電層をマスクとして半導体層に不純物元素を添加することにより半導体素子を形成することもできる。図 29 を用いて、そのような作製例を説明する。

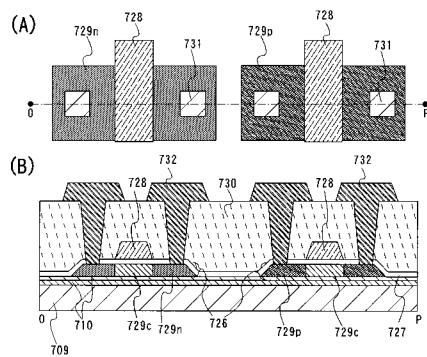

#### 【0281】

この場合は、基板 709 上に下地層 710 を形成し、下地層 710 上に半導体層 726 を形成する。半導体層 726 は、上記例と同様、珪素を有する材料から形成することができる。本発明は、非晶質半導体層を形成し、加熱処理またはレーザ照射により結晶化された結晶性の半導体層を形成し、所定の形状に加工する。

#### 【0282】

次に、半導体層 726 上に第 1 の絶縁層 727（ゲート絶縁膜）を形成する。第 1 の絶縁層 727 は、上記例と同様、酸化シリコン、窒化シリコン等のシリコンを含む材料を、プラズマ CVD 法またはスパッタリング法等を用いて成膜することができる。また、第 1 の絶縁層 727 は高密度プラズマ処理によって成膜することができる。高密度プラズマ処理により形成された絶縁膜は、他の被膜に与えるダメージが少なく、緻密なものとなり、形成された絶縁膜と接触する界面状態を改善することができる。第 1 の絶縁層 727 上に第 1 の導電層 728（ゲート電極）を形成する。第 1 の導電層 728 は、上記例の第 1 の導電層 711 と同様、導電性を有する金属元素やそれらの化合物等を用いて形成し、加工することができる。

#### 【0283】

10

20

30

40

50

次に、上記例と同様、半導体層 726 に不純物元素を選択的に添加して N 型不純物領域 729n、P 型不純物領域 729p を形成する。また、不純物元素を選択的に添加することによりチャネル形成領域 729c も形成される。ここで、チャネル長が短い半導体素子を作製する場合には、オフ電流値（半導体素子がオフ動作時に流れるドレイン電流）を十分低くすることが重要になる。このようなオフ電流値を低減するため、低濃度ドレイン（LDD：Light Doped Drain）領域を有する半導体素子を作製することが好ましい。N チャネル型のトランジスタに、チャネル形成領域 729c と高濃度純物領域（N 型不純物領域 729n）との間に、低濃度不純物領域を設けることが好ましい。

#### 【0284】

低濃度不純物領域を形成する方法は、例えば、第 1 の導電層 728 をマスクにして不純物元素を選択的に添加し、N 型の低濃度不純物領域を形成し、その後、第 1 の導電層 728 上に絶縁層を形成し、当該絶縁層に異方性エッチングを施すことにより、第 1 の導電層 728 の側面にサイドウォールと呼ばれる絶縁層を形成し、半導体層 726 の N 型の低濃度不純物領域となる領域と重なるようにする。そして第 1 の導電層 728 及びサイドウォールをマスクとして、N 型の低濃度不純物領域を有する半導体層 726 に N 型の不純物元素を添加し、上記 N 型の低濃度不純物領域よりも不純物元素の濃度が高い高濃度不純物領域を形成することができる。以上により、LDD 領域を有する N 型半導体素子を形成することができる。

#### 【0285】

また、ホットキャリアの注入による劣化によってオン電流値（半導体素子がオン動作時に流れるドレイン電流）が低下するのを防ぐため、ゲート絶縁膜を介して、LDD 領域をゲート電極と重ねて配置させた、GOLD (Gate-drain Overlapped LDD) 構造を有する半導体素子を作製することが好ましい。このような構造とすることで、ドレイン近傍の高電界が緩和されてホットキャリア注入を防ぎ、半導体素子の劣化を防止することができる。

#### 【0286】

続いて、半導体素子上に第 2 の絶縁層 730 を形成する（図 29 (B) 参照）。第 2 の絶縁層 730 は、上記例の第 2 の絶縁層 718 と同様、絶縁性を有する無機化合物や、有機化合物等により形成することができる。第 2 の絶縁層は、上記の絶縁性を有する材料を用いて単層で形成してもよく、2 層以上に積層させて形成しても良い。

#### 【0287】

次に、第 2 の絶縁層 730 をエッチングし、コンタクトホール 731 を形成する。このときの、エッチング処理は、ドライエッチング処理またはウェットエッチング処理を適用することができる。本実施の形態では、異方性のドライエッチングにより第 1 のコンタクトホールを形成する例を示す。

#### 【0288】

次に、第 2 の絶縁層 730、および第 1 のコンタクトホール 731 上に、第 2 の導電層 732 を形成する。第 2 の導電層 732 は、上記例で説明した第 3 の導電層 725 と同様、導電性を有する金属元素やそれらの化合物等を用いて形成し、加工することができる。第 2 の導電層 732 は、半導体素子と接続してソース電極や、ドレイン電極を形成するほか、微小構造体および半導体素子を電気的に接続する。（図 29 (B) 参照）。

#### 【0289】

上記工程により、半導体素子を有する層を形成することができる。

#### 【0290】

ここで、上記図 26 乃至図 29 に示した作製例において、第 1 の導電層、第 2 の導電層、および第 3 の導電層が角を有するパターンの場合、当該角部を、丸みを帯びた形状に加工することができる。そうすることによって、層の角部が剥がれ落ちることによって生じるごみの発生を抑えたり、基板上に存在するごみを効率よく洗浄することができる。これは、第 1 の導電層、第 2 の導電層、およびゲート電極等、金属や金属化合物を用いて形成されている場合や、厚さが厚い層を加工する場合に適用することが好ましい。また、こ

10

20

30

40

50

これらの導電層は、半導体層や下地層に比較して厚い層であるため、断面がテーパー角を有するように加工することによっても、層の角部が剥がれ落ちることによって生じるごみの発生を抑えたり、基板上に存在するごみを効率よく洗浄することができる。

#### 【0291】

そして、上記のように作成した半導体素子を有する層の上に、必要に応じて、さらに微小構造体を形成する層を積層させても良い。例えば、第2の絶縁層および第3の導電層上に、第3の絶縁層および第4の導電層を形成することが可能である。しかしながら、第3の絶縁層を、微小構造体を形成する層として使用することも可能である。

#### 【0292】

このようにして、基板上に半導体素子を有する第2の層を形成することができる。

10

#### 【0293】

本発明の作製方法は犠牲層エッチングを行わないため、微小構造体の他、半導体素子等の他の素子を同時に形成することも可能である。とりわけ、第2の層（貼り合わせ時に剥離しない方の層）を形成する第2の基板上に半導体素子を作製することで、犠牲層エッチング等の工程を経て特性が低下することなく、従来の特性の半導体素子を有するマイクロマシンを作製することができる。

#### 【0294】

上記本発明のマイクロマシンの作製方法を適用することによって、実施の形態1などで説明した微小構造体の作製方法と同様の効果（a）乃至（i）を得ることができることができる。いくつかの効果を下記に示す。

20

#### 【0295】

（a）犠牲層エッチングを行わずに微小構造体を作製することができる。すなわち、犠牲層エッチングと同様の工程を、剥離および貼り合わせによって行うため、非常に短時間でその工程を行うことができる。

#### 【0296】

（b）犠牲層エッチングを剥離および貼り合わせによって代替することで、ウェットエッチングを行うときのように微小構造体が液体のエッチング剤に触れることがなく、毛管現象による構造層と基板との張り付きを生じないように作製することができる。

#### 【0297】

（i）本発明は犠牲層を形成せず、さらに、第1の層と第2の層とを別々に形成して貼り合わせを行うため、犠牲層のように厚い膜によって生じる段差部分がなく、その段差乗り越え部分から生じる破壊が起こらない。したがって、強度の高い微小構造体を作製することができる。

30

#### 【0298】

なお、本実施の形態は上記実施の形態に記載の微小構造体と自由に組み合わせることで、マイクロマシンを作製することができる。すなわち、電子回路を構成する半導体素子を作製する工程と同一の工程で、微小構造体を構成するいずれかの構造層を作製することで、微小構造体と電子回路でなるマイクロマシンを作製することができる。

#### 【0299】

##### （実施の形態8）

40

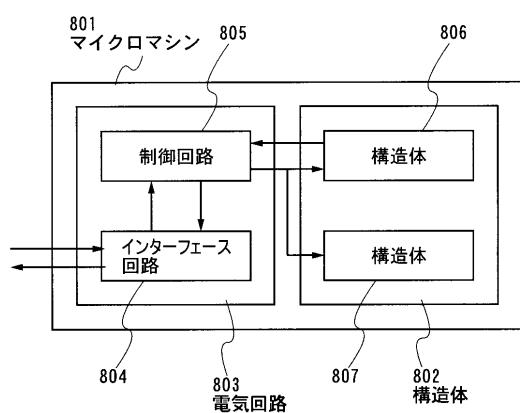

本実施の形態では、本発明のマイクロマシンの構成およびその機能についての一例を示す。本発明のマイクロマシンは、三次元的な立体構造を有する微小構造体、および半導体素子を有して前記微小構造体を制御する電気回路を有することを特徴とする。

#### 【0300】

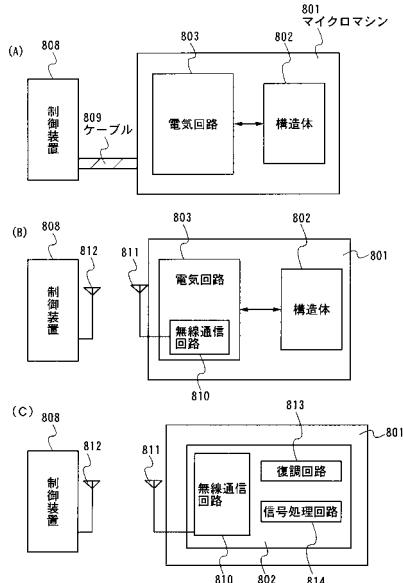

図30にマイクロマシンの概念図を示す。マイクロマシン801は、微小構造体802、および半導体素子によって構成される電気回路803を有する。

#### 【0301】

マイクロマシン801を構成する微小構造体802は、基板と構造層との間に形成された空間を有し、構造層はその空間の内部を可動することができることが多い。このような微小構造体は、物理量を検知するセンサや、電気回路803からの信号を変位に変換する

50

アクチュエータとして機能することができる。また、図30に示すように、マイクロマシン801は複数の微小構造体（図中、第1の微小構造体806、および第2の微小構造体807、等）を有することができる。

#### 【0302】

また、マイクロマシン801を構成する電気回路803は、外部の制御装置との通信を行うためのインターフェース回路804、微小構造体を制御するための信号を処理する制御回路805を有する。その他にも、電気回路は微小構造体からの出力信号を増幅する増幅回路や、外部の制御装置からの制御信号をアナログからデジタルに変換するA/Dコンバータ、デジタルからアナログに変換するD/Aコンバータ、微小構造体の制御プログラムを記憶するメモリ、当該メモリを制御するメモリ制御回路等を有することができる。

10

#### 【0303】

次に、図31を用いて、上記の構成を有するマイクロマシンの機能の例を説明する。例えば、図31(A)に示すように、本発明のマイクロマシン801は微小構造体802および電気回路803を有する。そして、マイクロマシン801を制御するための外部の制御装置808とケーブル809(伝送線)で接続されており、外部の制御装置808からマイクロマシン801に制御信号や駆動電源を供給する構成を有することができる。ここで、制御信号を送受信するための伝送線と、電源を供給する伝送線とは同一であっても別々であっても良い。

#### 【0304】

例えば、微小構造体802がある物理量や物質の濃度等を検知する機能を有する場合、マイクロマシン801は微小構造体802が検知した情報を電気回路803で処理し、外部の制御装置808に伝達するセンサとして機能することができる。この場合、電気回路803は、上記に説明したような制御回路、A/Dコンバータ、D/Aコンバータ、メモリ、およびメモリ制御回路等を有することができる。

20

#### 【0305】

また、図31(B)に示すように、本発明のマイクロマシン801は、無線で外部の制御装置と通信を行う無線通信回路810、ならびにその他の回路から構成される電気回路803、および微小構造体802を有することもできる。ここで無線通信回路810は、電磁波を送受信するためのアンテナ811や、アンテナで受信した電磁波から電気回路803および微小構造体802の駆動電力を生成する電源回路、アンテナ811が受信した電磁波から信号を復調する復調回路等を有することができる。また、電磁波から駆動電源を生成する電源回路の他に、電池、または光や熱等によって発電を行う発電回路等の電源を有することも可能である。

30

#### 【0306】

このように、マイクロマシンが無線通信回路810を有し、電磁波を用いて無線で外部の制御装置808と通信を行うことにより、マイクロマシン801は伝送ケーブルに制限されることなく、機能が発揮できる範囲の自由度を広くすることができる。また、上記のように無線通信を行うことによって、どこにでも存在できる利用者にとって身近なマイクロマシンを実現することが可能となる。この場合、マイクロマシン801を制御する外部の制御装置808も、マイクロマシン801と通信を行うための無線通信回路やアンテナ812等を有することになる。

40

#### 【0307】

また図31(C)に示すように、マイクロマシン801は無線通信を行う半導体装置（例えばRFIDやICタグ等）を構成することも可能である。すなわち、無線通信回路810を構成するコンデンサやインダクタ等の受動素子、スイッチ、または高周波信号を伝達するための導波路等を微小構造体によって形成した半導体装置（＝マイクロマシン）を作製することができる。

#### 【0308】

この場合、マイクロマシン801は無線通信回路810、復調回路813、信号処理回路814等を有する電気回路803を有し、当該無線通信回路810や復調回路813等

50

は、微小構造体によって構成される受動素子やスイッチ等を有する。

【0309】

微小構造体を用いて受動素子を形成することで、従来よりも良好な特性を得ることができるため、これらを用いて無線通信回路を構成することで、感度の高い無線通信を行うことができる。さらには、従来よりも高い周波数帯域や、広い周波数帯域での通信が可能な半導体装置を提供することができる。

【0310】

本明細書において説明した微小構造体は一例であり、目的に応じた形状を目的に応じた工程で形成し、様々な駆動方法により所定の機能を備えた微小構造体を作製することができる。例えば、基板上面からの力を受けて構造層が変位することを検出するセンサとして使用することも可能であり、二つの電極間の静電容量を変化させる可変容量として使用することもできる。このように、同じ微小構造体が異なる駆動方法によって異なる機能を持つことも可能である。

【0311】

このように、本発明のマイクロマシンが有する微小構造体は、センサやアクチュエータのみならず、受動素子や導波路等、電気回路の一部分を構成することも可能である。例えば、高周波領域を使って無線通信を行う場合、受動素子（容量、インダクタ、抵抗等）は重要な構成要素であるが、一般的な半導体素子（CMOS、BiCMOS等）を形成する工程では、損失が小さく高速動作する受動素子を形成することが難しかった。しかしながら上記に示した工程を適用し、受動素子を微小構造体で形成することで、良好な特性を得ることができる。

【0312】

従来、ミリメートル単位以下といった微小なものを扱う場合、まず微小な対象物の構造を拡大し、人間やコンピュータがその情報を得て情報処理および動作の決定を行い、そして、その動作を縮小して微小な対象物に伝えるというプロセスを必要としていた。しかしながら、本実施の形態に示すマイクロマシンは、人間やコンピュータが上位概念的な命令を伝えるだけで、微小なものを扱うことが可能になる。すなわち、人間やコンピュータが目的を決定して命令を伝えると、当該マイクロマシンはセンサ等を用いて対象物の情報を得て情報処理を行い、可動することができるようになる。

【0313】

なお、本実施の形態は他の実施の形態と自由に組み合わせて行うことができる。

【0314】

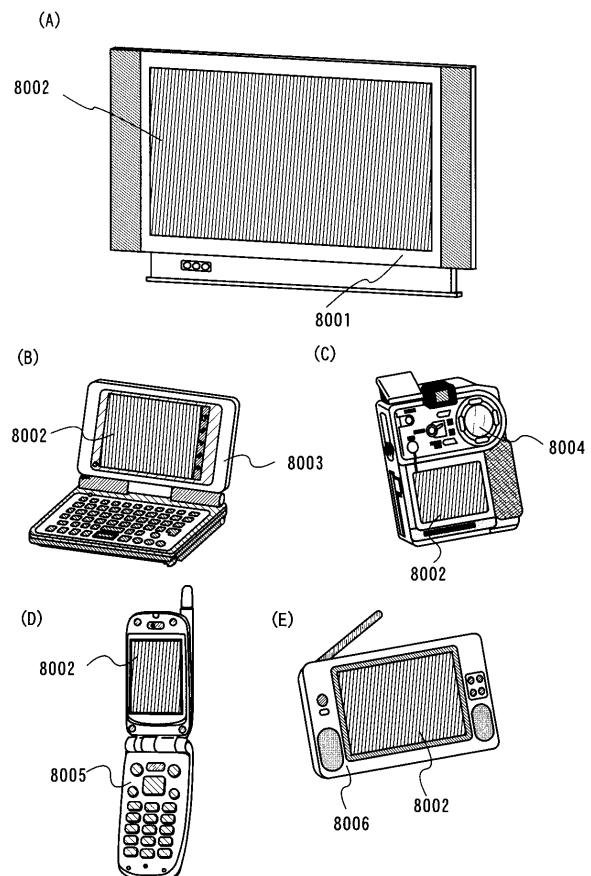

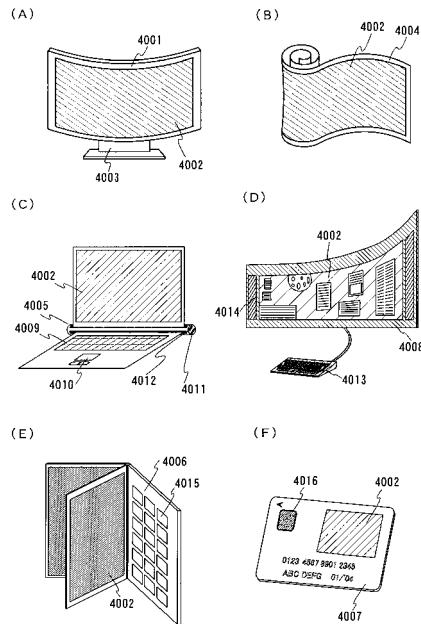

（実施の形態9）

本実施の形態では、上記実施の形態で説明した微小構造体を利用して作製される半導体装置および電子機器の形態例を示す。はじめに、非接触でデータのやりとりが可能である半導体装置に関して図32～図34を参照して以下に説明する。

【0315】

半導体装置80は、半導体装置外部に設けられたリーダ／ライタと非接触でデータを交信する機能を有する。リーダ／ライタは半導体装置80に信号を送り、当該半導体装置80は送られてきた信号に応じた信号を返す。リーダ／ライタは半導体装置から送信された信号を受信することによって、半導体装置のデータを読み取ることが可能となる。

【0316】

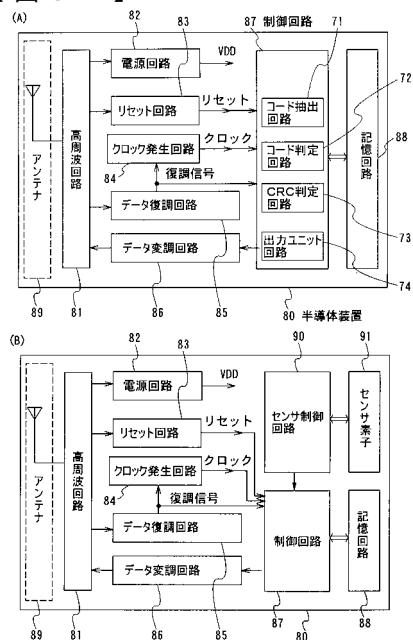

半導体装置80は、高周波回路81、電源回路82、リセット回路83、クロック発生回路84、データ復調回路85、データ変調回路86、他の回路の制御を行う制御回路87、記憶回路88およびアンテナ89を有している（図32（A））。

【0317】

高周波回路81はアンテナ89より信号を受信して、データ変調回路86より受信した信号をアンテナ89から出力する回路であり、電源回路82は受信信号から電源電位を生成する回路である。また、リセット回路83はリセット信号を生成する回路であり、クロック発生回路84はアンテナ89から入力された受信信号を基に各種クロック信号を生成

10

20

30

40

50

する回路である。そして、データ復調回路 8 5 は受信信号を復調して制御回路 8 7 に出力する回路であり、データ変調回路 8 6 は制御回路 8 7 から受信した信号を変調する回路である。

### 【 0 3 1 8 】