(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-54707

(P2009-54707A)

(43) 公開日 平成21年3月12日(2009.3.12)

(51) Int.Cl.

**H01L 21/8247 (2006.01)**

**H01L 27/115 (2006.01)**

**H01L 27/10 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

F 1

H01L 27/10 4 3 4

H01L 27/10 4 8 1

H01L 29/78 3 7 1

テーマコード(参考)

5 F 0 8 3

5 F 1 0 1

審査請求 未請求 請求項の数 19 O L (全 31 頁)

(21) 出願番号

(22) 出願日特願2007-218498 (P2007-218498)

平成19年8月24日 (2007.8.24)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人

100080001

弁理士 筒井 大和

(72) 発明者

石丸 哲也

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者

川嶋 祥之

東京都千代田区大手町二丁目6番2号 株

式会社ルネサステクノロジ内

(72) 発明者

嶋本 泰洋

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体記憶装置およびその製造方法

## (57) 【要約】

【課題】スプリットゲート型MONOSメモリセルにおいて、SS1方式による書き込み時のディスターブ耐性を向上させることのできる技術を提供する。

【解決手段】選択用nMISQnCと、選択用nMISQnCの側面に絶縁膜6b、6tおよび電荷蓄積層CSLを介して形成されたメモリ用nMISQnmとを含むメモリセルMC1において、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さが、ゲート長方向中央部下のゲート絶縁膜4の厚さよりも厚く形成され、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さが、半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さの1.5倍以下に形成される。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

半導体基板の正面の第1領域に第1電界効果トランジスタを含み、第2領域に前記第1電界効果トランジスタに隣接する第2電界効果トランジスタを含む不揮発性メモリセルを有する半導体記憶装置であって、

前記第1領域に形成された前記第1電界効果トランジスタの第1ゲート電極と、前記第2領域に形成された前記第2電界効果トランジスタの第2ゲート電極と、前記半導体基板と前記第1ゲート電極との間に形成された第1ゲート絶縁膜と、前記半導体基板と前記第2ゲート電極との間および前記第1ゲート電極と前記第2ゲート電極との間に形成された前記電荷蓄積層と、前記半導体基板と前記電荷蓄積層との間および前記第1ゲート電極と前記電荷蓄積層との間に形成された第1絶縁膜とを有し、

前記第1ゲート電極のゲート長方向端部下の前記第1ゲート絶縁膜の厚さが、前記第1ゲート電極のゲート長方向中央部下の前記第1ゲート絶縁膜の厚さよりも厚く、

前記第1ゲート電極と前記電荷蓄積層との間に位置し、かつ前記半導体基板に最も近い前記第1絶縁膜の厚さが、前記半導体基板と前記電荷蓄積層との間の前記第1絶縁膜の厚さの1.5倍以下であることを特徴とする半導体記憶装置。

## 【請求項 2】

請求項1記載の半導体記憶装置において、前記第1ゲート電極のゲート長方向端部下の前記第1ゲート絶縁膜の厚さが、前記第1ゲート電極のゲート長方向中央部下の前記第1ゲート絶縁膜の厚さよりも0.5nm以上厚いことを特徴とする半導体記憶装置。

## 【請求項 3】

請求項1記載の半導体記憶装置において、さらに、前記半導体基板の正面の第3領域に論理演算を行う第3電界効果トランジスタを有し、

前記第3領域に形成された前記第3電界効果トランジスタの第3ゲート電極と、前記半導体基板と前記第3ゲート電極との間に形成された第2ゲート絶縁膜とを有し、

前記第3ゲート電極のゲート長方向端部下の前記第2ゲート絶縁膜の厚さと、前記第3ゲート電極のゲート長方向中央部下の前記第2ゲート絶縁膜の厚さとの差が0.5nm以下であることを特徴とする半導体記憶装置。

## 【請求項 4】

請求項1記載の半導体記憶装置において、前記第1ゲート電極の片方のゲート長方向端部下の前記第1ゲート絶縁膜の厚さが、前記第1ゲート電極のゲート長方向中央部下の前記第1ゲート絶縁膜の厚さよりも厚いことを特徴とする半導体記憶装置。

## 【請求項 5】

請求項1記載の半導体記憶装置において、前記電荷蓄積層は窒化シリコン膜、酸窒化シリコン膜、酸化タンタル膜、または酸化アルミニウム膜であることを特徴とする半導体記憶装置。

## 【請求項 6】

請求項1記載の半導体記憶装置において、前記第1絶縁膜は酸化シリコン膜であることを特徴とする半導体記憶装置。

## 【請求項 7】

請求項1記載の半導体記憶装置において、前記第2ゲート電極と前記電荷蓄積層との間に第2絶縁膜を有することを特徴とする半導体記憶装置。

## 【請求項 8】

請求項7記載の半導体記憶装置において、前記第2絶縁膜は酸化シリコン膜、酸化シリコン膜の間に窒化シリコン膜が挿入された絶縁膜、または酸化シリコン膜の間に非晶質シリコン膜が挿入された絶縁膜であることを特徴とする半導体記憶装置。

## 【請求項 9】

請求項1記載の半導体記憶装置において、前記電荷蓄積層にSSII方式によりホットエレクトロンを注入することにより、情報を書込むことを特徴とする半導体記憶装置。

## 【請求項 10】

10

20

30

40

50

請求項 1 記載の半導体記憶装置において、前記電荷蓄積層に B T B T 現象を利用してホットホールを注入することにより、情報を消去することを特徴とする半導体記憶装置。

【請求項 1 1】

半導体基板の主面の第 1 領域に第 1 電界効果トランジスタを含み、第 2 領域に前記第 1 電界効果トランジスタに隣接する第 2 電界効果トランジスタを含む不揮発性メモリセルを形成する半導体記憶装置の製造方法であって、以下の工程を有することを特徴とする半導体記憶装置の製造方法：

- ( a ) 前記第 1 領域の前記半導体基板の主面上に第 1 ゲート絶縁膜を形成する工程、

- ( b ) 前記半導体基板の主面上に第 1 導体膜を堆積した後、前記第 1 領域に前記第 1 ゲート絶縁膜を介して前記第 1 導体膜からなる前記第 1 電界効果トランジスタの第 1 ゲート電極を形成する工程、

- ( c ) 前記第 1 ゲート電極下の前記第 1 ゲート絶縁膜を残して、その他の領域の前記第 1 ゲート絶縁膜を除去する工程、

- ( d ) 前記半導体基板に対して第 1 酸化処理を施して、前記第 1 ゲート電極のゲート長方向端部下の前記第 1 ゲート絶縁膜の厚さを前記第 1 ゲート電極のゲート長方向中央部下の前記第 1 ゲート絶縁膜の厚さよりも厚くする工程、

- ( e ) 前記 ( d ) 工程の後、前記第 1 酸化処理により形成された酸化膜の全部または一部を除去した後、前記半導体基板に対して第 2 酸化処理を施して、第 1 絶縁膜を形成する工程、

- ( f ) 前記 ( e ) 工程の後、前記第 1 絶縁膜上に電荷蓄積層を形成する工程、

- ( g ) 前記 ( f ) 工程の後、前記半導体基板の主面上に第 2 導体膜を堆積した後、前記第 2 導体膜を異方性エッティングにより加工して、前記第 1 ゲート電極の両側面に前記第 2 導体膜からなるサイドウォールを形成する工程、

- ( h ) 前記第 1 ゲート電極の一方の側面に形成された前記サイドウォールを除去し、前記第 1 ゲート電極の他の側面に残る前記サイドウォールを第 2 ゲート電極とする工程、

- ( i ) 前記第 1 ゲート電極と前記第 2 ゲート電極との間、および第 2 領域に形成された前記第 1 絶縁膜および前記電荷蓄積層を残して、その他の領域の前記第 1 絶縁膜および前記電荷蓄積層を除去する工程。

【請求項 1 2】

請求項 1 1 記載の半導体記憶装置の製造方法において、前記 ( e ) 工程で、前記第 1 ゲート電極と前記電荷蓄積層との間に位置し、かつ前記半導体基板に最も近い前記第 1 絶縁膜の厚さが、前記半導体基板と前記電荷蓄積層との間の前記第 1 絶縁膜の厚さの 1.5 倍以下となるように、前記第 1 絶縁膜を形成することを特徴とする半導体記憶装置の製造方法。

【請求項 1 3】

請求項 1 1 記載の半導体記憶装置の製造方法において、前記第 1 ゲート電極のゲート長方向端部下の前記第 1 ゲート絶縁膜の厚さを、前記第 1 ゲート電極のゲート長方向中央部下の前記第 1 ゲート絶縁膜の厚さよりも 0.5 nm 以上厚く形成することを特徴とする半導体記憶装置の製造方法。

【請求項 1 4】

請求項 1 1 記載の半導体記憶装置の製造方法において、前記 ( f ) 工程と前記 ( g ) 工程との間に、さらに、以下の工程を有することを特徴とする半導体記憶装置の製造方法：

- ( j ) 前記電荷蓄積層上に第 2 絶縁膜を形成する工程。

【請求項 1 5】

請求項 1 1 記載の半導体記憶装置の製造方法において、前記第 2 酸化処理は、前記半導体基板に対して I S S G 酸化処理を施すことにより形成されることを特徴とする半導体記憶装置の製造方法。

【請求項 1 6】

請求項 1 1 記載の半導体記憶装置の製造方法において、前記第 1 酸化処理は、ウエット酸化処理であることを特徴とする半導体記憶装置の製造方法。

10

20

30

40

50

## 【請求項 17】

請求項 11 記載の半導体記憶装置の製造方法において、前記第 1 酸化処理は、ドライ酸化処理であることを特徴とする半導体記憶装置の製造方法。

## 【請求項 18】

請求項 17 記載の半導体記憶装置の製造方法において、さらに、前記 (c) 工程で、前記第 1 ゲート電極のゲート長方向端部下の前記第 1 ゲート絶縁膜を、前記第 1 ゲート電極の端部から 3 ~ 20 nm エッチングすることを特徴とする半導体記憶装置の製造方法。

## 【請求項 19】

請求項 11 記載の半導体記憶装置の製造方法において、さらに、前記 (d) 工程は、

10 (d1) 前記半導体基板の主面上に第 3 絶縁膜を形成する工程、

(d2) 前記第 1 ゲート電極の側面に、前記第 3 絶縁膜を介して、第 4 絶縁膜からなるサイドウォールを形成する工程、

(d3) 前記第 1 ゲート電極下の前記第 1 ゲート絶縁膜が露出するまで、前記第 3 絶縁膜を除去する工程、

(d4) 前記半導体基板に対してドライ酸化処理を施して、前記第 1 ゲート電極のゲート長方向端部下の前記第 1 ゲート絶縁膜の厚さを前記第 1 ゲート電極のゲート長方向中央部下の前記第 1 ゲート絶縁膜の厚さよりも厚く形成する工程を有し、

さらに、前記 (e) 工程は、

(e1) 前記第 1 ゲート電極下の前記第 1 ゲート絶縁膜を残して、その他の領域の前記第 3 絶縁膜、前記サイドウォールおよび前記ドライ酸化処理により形成された酸化膜を除去する工程を有することを特徴とする半導体記憶装置の製造方法。

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体記憶装置およびその製造技術に関し、特に、窒化膜を電荷蓄積層とする MONOS (Metal Oxide Nitride Oxide Semiconductor) メモリセルを有する半導体記憶装置に適用して有効な技術に関するものである。

## 【背景技術】

## 【0002】

電気的に書き込み、消去が可能な不揮発性半導体記憶装置として、現在、EEPROM (Electrical Erasable and Programmable Read Only Memory) が使用されている。フラッシュメモリに代表される不揮発性半導体記憶装置のメモリセルは、MIS (Metal Oxide Semiconductor) トランジスタのゲート電極下に、酸化膜で囲まれた導電性の浮遊ゲート電極またはトラップ性絶縁膜に代表される電荷蓄積領域を有しており、この電荷蓄積領域に記憶情報として電荷を蓄積し、それを MIS トランジスタのしきい値電圧として読み出すものである。

30

## 【0003】

トラップ性絶縁膜を電荷蓄積領域とするメモリセルとしては、MONOS 方式のメモリセルがある。なかでも、1 つのメモリセルがメモリゲート電極と選択ゲート電極との 2 つのゲート電極を持つスプリットゲート型メモリセルが、近年、広く使用されている。スプリットゲート型メモリセルは、電荷蓄積領域としてトラップ性絶縁膜を用いているので、離散的に電荷を蓄積することができてデータ保持の信頼性に優れる。また、データ保持の信頼性に優れていることから、トラップ性絶縁膜の上下に形成される酸化膜を薄膜化することができるので、書き込み・消去動作の低電圧化が可能である等の利点を有している。また、スプリットゲート型メモリセルを用いることで、注入効率の優れたSSI (Source Side Injection: ソースサイド注入) 方式によりホットエレクトロンをトラップ性絶縁膜へ注入することができるので、高速、低電流の書き込みを図ることができる。また、書き込み、消去動作の制御が簡単であることから、周辺回路を小規模にすることができますという利点も有している。トラップ性絶縁膜とは、電荷蓄積を可能とする絶縁膜をいい、一例として、窒化シリコン膜を挙げることができる。

40

50

## 【0004】

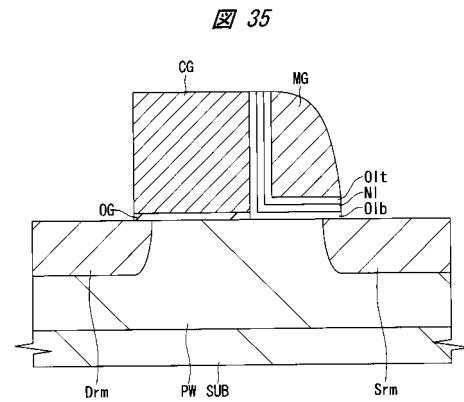

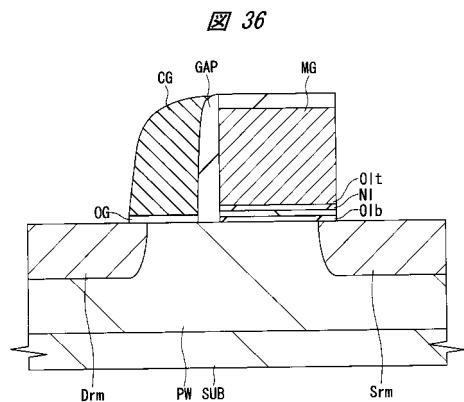

スプリットゲート型メモリセルのセル構造は、大きく分けて図35および図36に示す2種類に分けることができる。図35に示すセル構造の第1メモリセルでは、先に選択ゲート電極CGを形成した後、下部酸化膜OIb、窒化シリコン膜NIおよび上部酸化膜OItからなるONO膜を形成し、メモリゲート電極MGを側壁スペーサの形状で形成する（例えば特許文献1参照）。これに対し、図36に示すセル構造の第2メモリセルでは、先に下部酸化膜OIb、窒化シリコン膜NIおよび上部酸化膜OItからなるONO膜を形成し、その上にメモリゲート電極MGを形成した後、メモリゲート電極MGと選択ゲート電極CGとの間の耐圧を確保するための側壁酸化膜GAP、および選択ゲート電極CGのゲート絶縁膜OGを成膜する。その後、選択ゲート電極CGを側壁スペーサの形状で形成する。

10

## 【0005】

上記第1メモリセルの利点は、メモリゲート電極MGと選択ゲート電極CGとの間にONO膜があるため、メモリゲート電極MGと選択ゲート電極CGとの間の耐圧を確保しやすく、両者間の距離をONO膜の厚さ程度に短くできることである。メモリゲート電極MGと選択ゲート電極CGとの間の距離が短くできることで、メモリゲート電極MGと選択ゲート電極CGとの間の下のチャネル部のギャップ抵抗が小さくなり、上記第2メモリセルよりも大きな読み出し電流を得ることができる。なお、図35および図36中、符号SUB、PW、SrmおよびDrmは、それぞれ半導体基板、pウェル、ソース領域およびドレイン領域を示す。

20

【特許文献1】特開2005-123518号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

スプリットゲート型MONOSメモリセルにおいて、SSI方式による書き込みを行うと、書き込み時のディスターブが問題となる。ここでいう書き込み時のディスターブとは、あるメモリセルを選択し、そのメモリセルの書き込み動作を行うと、選択メモリセルに印加した電圧が同じ配線に接続されている選択していない非選択メモリセルにも印加され、非選択メモリセルが弱い書き込みおよび弱い消去動作を行って、徐々にデータが失われている現象をいう。SSI方式による書き込みでは、複数のメモリセルのソース領域が接続されたソース線と、複数のメモリセルのメモリゲート電極が接続されたメモリゲート線との両方に高電圧が印加される。このため、ソース領域とメモリゲート電極との両方に書き込みの高電圧が印加される非選択メモリセルが存在し、その非選択メモリセルにおいて電荷蓄積領域に電子が注入される弱い書き込みが起こり、問題となる。

30

## 【0007】

ディスターブを解決する方法として、同一のソース線および同一のメモリゲート線に接続されるメモリセルの数を減らす方法が考えられる。しかしながら、この方法では、1本の配線を複数本に分割し、かつ配線を駆動するドライバの数を増やす必要があるため、メモリモジュールの面積が増加してしまう。

40

## 【0008】

本発明の目的は、スプリットゲート型MONOSメモリセルにおいて、SSI方式による書き込み時のディスターブ耐性を向上させることのできる技術を提供することにある。

## 【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

## 【課題を解決するための手段】

## 【0010】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

## 【0011】

50

本発明は、スプリットゲート型MONOSメモリセルを有する半導体記憶装置であって、選択用電界効果トランジスタの選択ゲート電極と、メモリ用電界効果トランジスタのメモリゲート電極と、半導体基板と選択ゲート電極との間に形成されたゲート絶縁膜と、半導体基板とメモリゲート電極との間および選択ゲート電極とメモリゲート電極との間に形成された下層の絶縁膜、電荷蓄積層および上層の絶縁膜からなる積層構造の電荷保持用絶縁膜とを有し、選択ゲート電極のゲート長方向端部下のゲート絶縁膜の厚さが、選択ゲート電極のゲート長方向中央部下のゲート絶縁膜の厚さよりも厚く、選択ゲート電極と電荷蓄積層との間に位置し、かつ半導体基板に最も近い下層の絶縁膜の厚さが、半導体基板と電荷蓄積層との間の下層の絶縁膜の厚さの1.5倍以下とするものである。

【0012】

10

本発明は、スプリットゲート型MONOSメモリセルを有する半導体記憶装置の製造方法であって、半導体基板の正面に選択用電界効果トランジスタのゲート絶縁膜を形成する工程と、ゲート絶縁膜上に第1導体膜からなる選択用電界効果トランジスタの選択ゲート電極を形成する工程と、選択ゲート電極下のゲート絶縁膜を残して、その他の領域のゲート絶縁膜を除去する工程と、半導体基板に対して酸化処理を施して、選択ゲート電極のゲート長方向端部下のゲート絶縁膜の厚さを選択ゲート電極のゲート長方向中央部下のゲート絶縁膜の厚さよりも厚く形成する工程と、選択ゲート電極下のゲート絶縁膜を残して、半導体基板の正面を露出させる工程と、半導体基板の正面に下層の絶縁膜を形成する工程と、下層の絶縁膜上に電荷蓄積層を形成する工程と、電荷蓄積層上に上層の絶縁膜を形成する工程と、選択ゲート電極の側面に第2導体膜からなるメモリ用電界効果トランジスタのメモリゲート電極を形成する工程と、選択ゲート電極の片側に形成されたメモリゲート電極を除去する工程と、選択ゲート電極とメモリゲート電極との間、およびメモリゲート電極と半導体基板との間の下層の絶縁膜、電荷蓄積層および上層の絶縁膜を残して、その他の下層の絶縁膜、電荷蓄積層および上層の絶縁膜を除去する工程とを有するものである。

20

【発明の効果】

【0013】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0014】

30

スプリットゲート型MONOSメモリセルにおいて、読み出し電流を低減させずに、S/I方式による書き込み時のディスターブ耐性を向上させることができる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減することができる。

【発明を実施するための最良の形態】

【0015】

本実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0016】

40

また、本実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、本実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、本実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0017】

50

また、本実施の形態においては、電界効果トランジスタを代表するM I S · F E T (Metal Insulator Semiconductor Field Effect Transistor)をM I Sと略し、nチャネル型のM I S · F E TをnM I Sと略す。なお、M O S F E T (Metal Oxide Semiconductor F E T)は、そのゲート絶縁膜が酸化シリコン(S i O<sub>2</sub>等)膜からなる構造の電界効果トランジスタであり、上記M I Sの下位概念に含まれるものとする。また、本実施の形態で記載するM O N O S型メモリセルについても、上記M I Sの下位概念に含まれることは勿論である。また、本実施の形態において、窒化シリコン、窒化ケイ素またはシリコンナイトライドというときは、S i<sub>3</sub>N<sub>4</sub>は勿論であるが、それのみではなく、シリコンの窒化物で類似組成の絶縁膜を含むものとする。また、本実施の形態において、ウエハと言うときは、S i (Silicon) 単結晶ウエハを主とするが、それのみではなく、S O I (Silicon On Insulator)ウエハ、集積回路をその上に形成するための絶縁膜基板等を指すものとする。その形も円形またはほぼ円形のみでなく、正方形、長方形等も含むものとする。

10

#### 【0018】

また、本実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

#### 【0019】

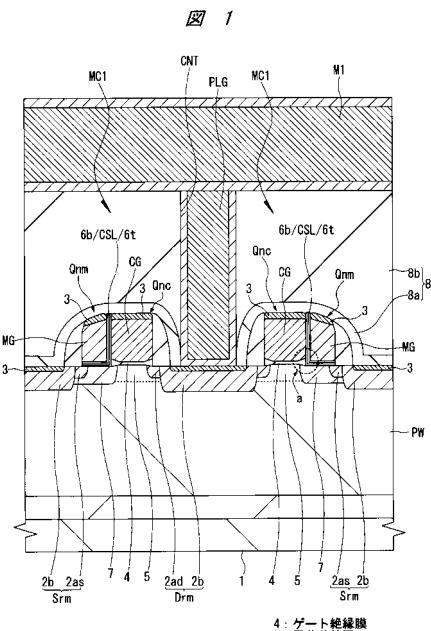

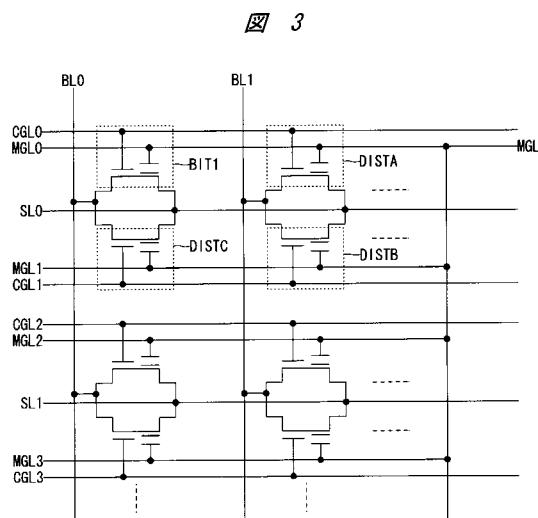

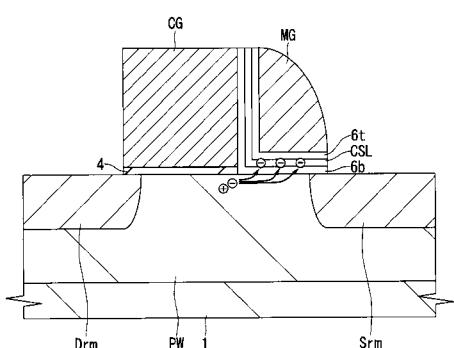

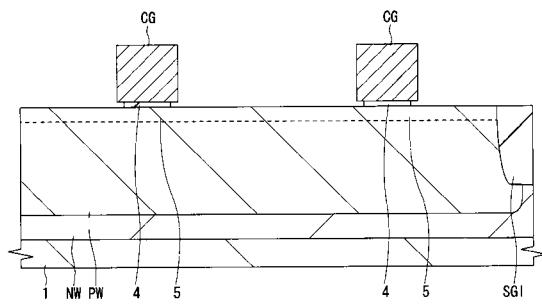

##### (実施の形態1)

本発明の実施の形態1によるスプリットゲート型M O N O Sメモリセルの構造の一例を図1および図2を用いて説明する。図1はチャネルをメモリゲート電極に対して交差する方向に沿って切断したスプリットゲート型M O N O Sメモリセルの要部断面図、図2は図1のa領域を拡大して示した要部断面図である。

20

#### 【0020】

図1に示すように、半導体基板1は、例えばp型の単結晶シリコンからなり、p型の不純物が導入されてなるpウェルP Wが形成されている。半導体基板1の正面(デバイス形成面)の活性領域には、本実施の形態1によるメモリセルM C 1の選択用nM I S (Q n c)とメモリ用nM I S (Q n m)とが配置されている。このメモリセルM C 1のドレイン領域D r mおよびソース領域S r mは、例えば相対的に低濃度のn<sup>-</sup>型の半導体領域2 a d, 2 a sと、そのn<sup>-</sup>型の半導体領域2 a d, 2 a sよりも不純物濃度の高い相対的に高濃度のn<sup>+</sup>型の半導体領域2 bとを有している(L D D (Lightly Doped Drain)構造)。n<sup>-</sup>型の半導体領域2 a d, 2 a sは、メモリセルM C 1のチャネル領域側に配置され、n<sup>+</sup>型の半導体領域2 bは、メモリセルM C 1のチャネル領域側からn<sup>-</sup>型の半導体領域2 a d, 2 a s分だけ離れた位置に配置されている。

30

#### 【0021】

このドレイン領域D r mとソース領域S r mとの間の半導体基板1の正面には、上記選択用nM I S (Q n c)の選択ゲート電極C Gと、上記メモリ用nM I S (Q n m)のメモリゲート電極M Gとが隣接して延在しており、その延在方向において複数のメモリセルM C 1は半導体基板1に形成された素子分離部を介して隣接している。選択ゲート電極C Gは半導体基板1の正面の第1領域に配置され、メモリゲート電極M Gは半導体基板1の正面の第1領域とは異なる第2領域に配置されている。選択ゲート電極C Gは、例えばn型の多結晶シリコン膜からなり、その不純物濃度は、例えば $2 \times 10^{20} \text{ cm}^{-3}$ 程度、そのゲート長は、例えば100~150nm程度である。メモリゲート電極M Gは、例えばn型の多結晶シリコン膜からなり、その不純物濃度は、例えば $2 \times 10^{20} \text{ cm}^{-3}$ 程度、そのゲート長は、例えば50~100nm程度である。

40

#### 【0022】

選択ゲート電極C Gと、メモリゲート電極M Gと、ソース領域S r mおよびドレイン領域D r mの一部を構成するn<sup>+</sup>型の半導体領域2 bの上面には、例えばコバルトシリサイド、ニッケルシリサイド、チタンシリサイド等のようなシリサイド層3が形成されている。M O N O S型メモリセルでは、選択ゲート電極C Gおよびメモリゲート電極M Gの双方

50

に電位を供給する必要があり、その動作速度は選択ゲート電極 C G およびメモリゲート電極 M G の抵抗値に大きく依存する。従ってシリサイド層 3 を形成することにより選択ゲート電極 C G およびメモリゲート電極 M G の低抵抗化を図ることが望ましい。シリサイド層 3 の厚さは、例えば 20 nm 程度である。

【 0 0 2 3 】

選択ゲート電極 C G と半導体基板 1 の正面との間には、例えば厚さ 1 ~ 5 nm 程度の薄い酸化シリコン膜からなるゲート絶縁膜 4 が設けられている。従って素子分離部上およびゲート絶縁膜 4 を介した半導体基板 1 の第 1 領域上に選択ゲート電極 C G が配置されている。さらに、ゲート絶縁膜 4 の構造はバーズビーク形状であり、ゲート絶縁膜 4 のゲート長方向端部下の厚さが、ゲート絶縁膜 4 のゲート長方向中央部下の厚さよりも厚く形成されている。

10

【 0 0 2 4 】

ゲート絶縁膜 4 の下方の半導体基板 1 の正面には、例えばボロンが導入されて p 型の半導体領域 5 が形成されている。この半導体領域 5 は、選択用 nMIS (Qnc) のチャネル形成用の半導体領域であり、この半導体領域 5 により選択用 nMIS (Qnc) のしきい値電圧が所定の値に設定されている。

【 0 0 2 5 】

メモリゲート電極 M G は選択ゲート電極 C G の側面の片側に設けられており、下層の絶縁膜 6 b 、電荷蓄積層 C S L および上層の絶縁膜 6 t を積層した電荷保持用絶縁膜（以下、絶縁膜 6 b , 6 t および電荷蓄積層 C S L と記す）により選択ゲート電極 C G とメモリゲート電極 M G との絶縁がなされている。また、絶縁膜 6 b , 6 t および電荷蓄積層 C S L を介した半導体基板 1 の第 2 領域上にメモリゲート電極 M G が配置されている。なお、図 1 では絶縁膜 6 b , 6 t および電荷蓄積層 C S L の表記を 6 b / C S L / 6 t として表現している。

20

【 0 0 2 6 】

電荷蓄積層 C S L は、その上下を絶縁膜 6 b , 6 t に挟まれた状態で設けられており、例えば窒化シリコン膜からなり、その厚さは、例えば 5 ~ 20 nm 程度である。窒化シリコン膜は、その膜中に離散的なトラップ準位を有し、このトラップ準位に電荷を蓄積する機能を有する絶縁膜である。絶縁膜 6 b , 6 t は、例えば酸化シリコン膜等からなり、下層の絶縁膜 6 b の厚さは、例えば 1.5 ~ 6 nm 程度、上層の絶縁膜 6 t の厚さは、例えば 0 ~ 8 nm 程度である。絶縁膜 6 b , 6 t は窒素を含んだ酸化シリコン膜で形成することもできる。

30

【 0 0 2 7 】

上記下層の絶縁膜 6 b の下方、p 型の半導体領域 5 とソース領域 S r m との間の半導体基板 1 の正面には、例えばヒ素またはリンが導入されて n 型の半導体領域 7 が形成されている。この半導体領域 7 は、メモリ用 nMIS (Qnm) のチャネル形成用の半導体領域であり、この半導体領域 7 によりメモリ用 nMIS (Qnm) のしきい値電圧が所定の値に設定されている。選択ゲート電極 C G およびメモリゲート電極 M G の上方には窒化シリコン膜 8 a および酸化シリコン膜 8 b からなる層間絶縁膜 8 が形成されており、この層間絶縁膜 8 にはドレイン領域 D r m に達するコンタクトホール C N T が形成されている。ドレイン領域 D r m には、コンタクトホール C N T に埋め込まれたプラグ P L G を介して、第 1 方向に延在するメモリゲート電極 M G (または選択ゲート電極 C G ) に対して交差する方向である第 2 方向に延在する第 1 層配線 M 1 が接続されている。この配線 M 1 が、各メモリセル M C 1 のビット線を構成している。

40

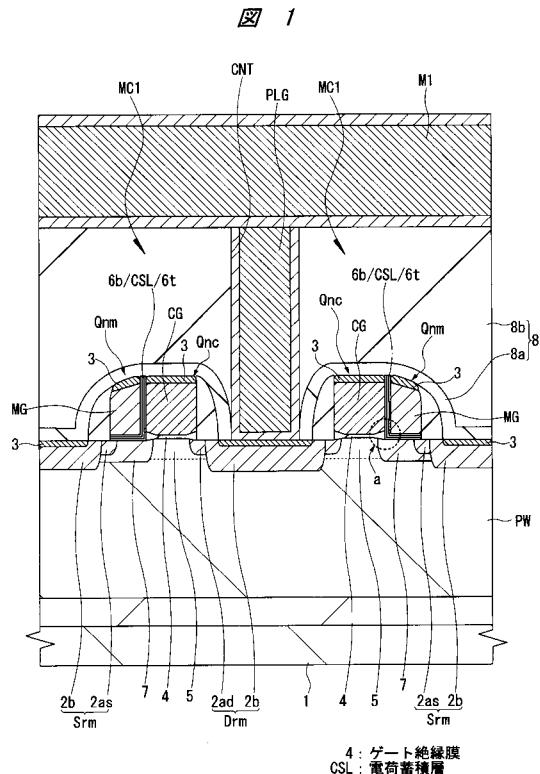

【 0 0 2 8 】

図 2 に、メモリセル M C 1 のギャップ部における選択ゲート電極 C G のゲート絶縁膜 4 、下層の絶縁膜 6 b 、電荷蓄積層 C S L および上層の絶縁膜 6 t の拡大図を示す。

【 0 0 2 9 】

本実施の形態 1 において説明されるメモリセル M C 1 の特徴は、選択ゲート電極 C G のゲート絶縁膜 4 の構造がバーズビーク形成であり、加えて、選択ゲート電極 C G と電荷蓄

50

積層 C S L との間に位置する下層の絶縁膜 6 b を厚く形成せず、所定の厚さに設定する点にある。より具体的には、(1)選択ゲート電極 C G のゲート長方向端部下のゲート絶縁膜 4 の厚さ (t<sub>oxe</sub>) が、ゲート長方向中央部下のゲート絶縁膜 4 の厚さ (t<sub>oxc</sub>) よりも厚く形成され、(2)選択ゲート電極 C G と電荷蓄積層 C S L との間に位置し、かつ半導体基板 1 (p ウェル P W) に最も近い下層の絶縁膜 6 b の厚さ (t<sub>oxs</sub>) が、半導体基板 1 と電荷蓄積層 C S L との間に位置する下層の絶縁膜 6 b の厚さ (t<sub>oxb</sub>) の 1.5 倍以下である。後に、このメモリセル M C 1 のアレイ構成およびメモリ動作 (書き込み、書き込みディスクープ、消去および読み出し) については図 3 ~ 図 11 を用いて、このメモリセル M C 1 の製造方法については図 12 ~ 図 20 を用いて詳細に説明する。

## 【0030】

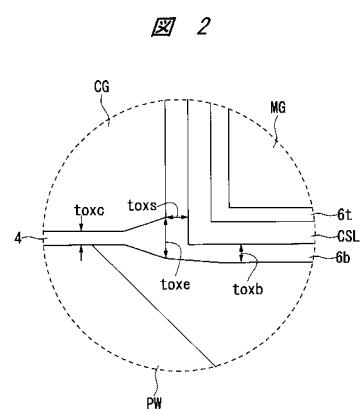

10

まず、本発明の実施の形態 1 によるスプリットゲート型 M O N O S メモリセルのアレイ構成の一例を図 3 を用いて説明する。図 3 はメモリセルのアレイ構成を示す回路図である。なお、図 3 では、簡略化のため、2 × 4 個のメモリセルのみを示している。

## 【0031】

各メモリセル M C 1 の選択ゲート電極 C G を接続する選択ゲート線 (ワード線) C G L 0 ~ C G L 3 、メモリゲート電極 M G を接続するメモリゲート線 M G L 0 ~ M G L 3 および 2 つの隣接したメモリセルが共有するソース領域 S r m を接続するソース線 S L 0 , S L 1 は第 1 の方向にそれぞれ平行に延在する。また、メモリセル M C 1 のドレイン領域 D r m を接続するビット線 B L 0 , B L 1 は第 2 の方向、すなわち、選択ゲート線 C G L 0 等と直交する方向に延在する。なお、これらの配線は、回路図上だけでなく、各メモリセル M C 1 または配線のレイアウト上も前述した方向に延在する。また、選択ゲート線 C G L 0 等は、選択ゲート電極 C G により構成しても良く、選択ゲート電極 C G に接続される配線により構成してもよい。

20

## 【0032】

ソース線 S L 0 , S L 1 とメモリゲート線 M G L 0 ~ M G L 3 には、書き込み・消去時に高電圧が印加されるので、高耐圧の M I S からなる昇圧ドライバが接続されている (図示は省略)。また、選択ゲート線 C G L 0 ~ C G L 3 には、1.5 V 程度の低電圧のみが印加されるので、低耐圧で高速の昇圧ドライバが接続されている (図示は省略)。1 本のローカルビット線には 16 個、32 個または 64 個のメモリセルが接続され、ローカルビット線はローカルビット線を選択する M I S を介してグローバルビット線に接続され、グローバルビット線はセンスアンプに接続されている。

30

## 【0033】

図 3 に示したアレイ構成では、ソース線 S L 0 , S L 1 は一本毎に独立して配線され、メモリゲート線 M G L 0 ~ M G L 3 は複数本を接続して共通のメモリゲート線 M G L としてあるが、ソース線 S L 0 , S L 1 およびメモリゲート線 M G L 0 ~ M G L 3 ともに複数本を接続して、それぞれ共有のソース線およびメモリゲート線としても良い。共有の配線とすることで、それぞれの線を駆動する高耐圧のドライバ数が削減され、チップ面積を低減することができる。逆に、ソース線 S L 0 , S L 1 およびメモリゲート線 M G L 0 ~ M G L 3 ともに一本毎に独立して配線しても良い。この場合、高耐圧のドライバ数は多くなるが、書き込みおよび消去時にディスクープを受ける時間を減らすことができる。

40

## 【0034】

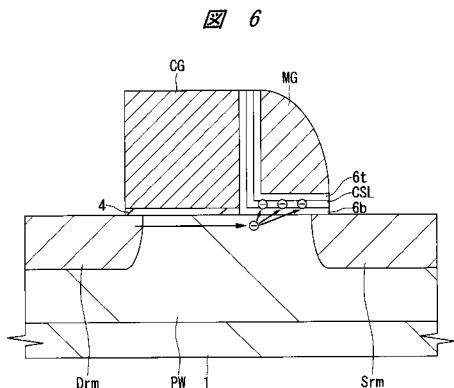

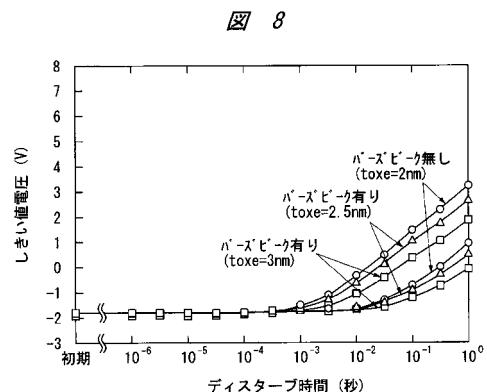

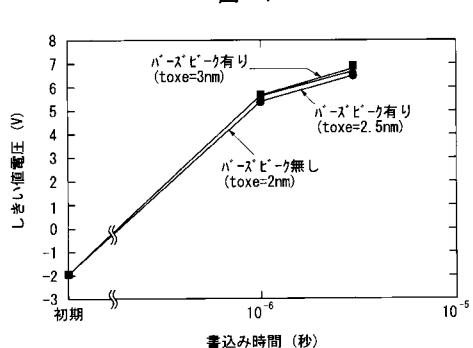

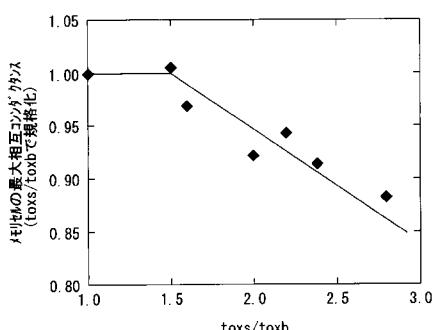

次に、本発明の実施の形態 1 によるスプリットゲート型 M O N O S メモリセルのメモリ動作 (書き込み、書き込みディスクープ、消去および読み出し) の一例を図 4 ~ 図 11 を用いて説明する。図 4 は前記図 3 に示した選択セル B I T 1 の書き込み、消去および読み出し時ににおいて、各配線 (選択ゲート線 C G L 0 ~ C G L 3 、メモリゲート線 M G L 、ソース線 S L 0 , S L 1 、ビット線 B L 0 , B L 1 ) に印加される電圧条件の一例、図 5 は前記図 3 に示した選択セル B I T 1 に情報を書き込む場合に、選択セル B I T 1 、非選択セル D I S T A , D I S T B , D I S T C の各端子に印加される電圧条件の一例、図 6 は書き込み選択メモリセルの電荷の動きを示すメモリセルの要部断面図、図 7 はメモリセルの書き込み特性を示すグラフ図、図 8 はディスクープ特性を示すグラフ図、図 9 は選択ゲート電極のゲー

50

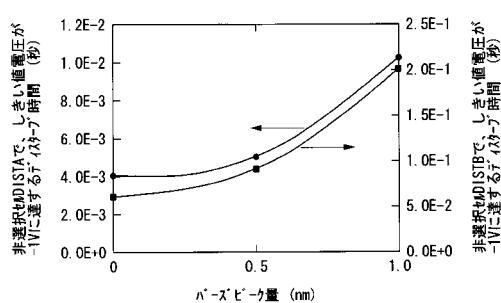

ト長方向端部下のゲート絶縁膜のバーズピーク量としきい値電圧が-1Vに達するディスタート時間との関係を示すグラフ図、図10は、ディスタート時の電子注入のメカニズムを説明するためのメモリセルの要部断面図、図11は選択ゲート電極と電荷蓄積層との間に位置する下層の絶縁膜の厚さとメモリ用nMISの最大相互コンダクタンスとの関係を示すグラフ図である。ここでは、電荷蓄積層CSLへの電子の注入を「書き込み」、ホールの注入を「消去」と定義する。

#### 【0035】

「書き込み」と「書き込みディスタート」について説明する。

#### 【0036】

書き込みは、いわゆるSSI方式によって行なわれる。非選択セルDISTAは、選択セルBIT1と同じメモリゲート線MGL、ソース線SL0および選択ゲート線CGL1に接続されたメモリセル、非選択セルDISTB, DISTCは、選択セルBIT1と同じメモリゲート線MGL、ソース線SL0に接続されたメモリセルである。

10

#### 【0037】

図4および図5に示すように、選択セルBIT1のソース領域Srmに印加する電圧Vsを5V、メモリゲート電極MGに印加する電圧Vmgを10V、選択ゲート電極CGに印加する電圧Vsgを1Vとする。そして、ドレイン領域Drmに印加する電圧Vdは書き込み時のチャネル電流がある設定値となるように制御する。このときの電圧Vdはチャネル電流の設定値と選択用MIS(Qnc)のしきい値電圧によって決まり、例えば設定電流値1μAで0.4V程度となる。pウェルPWに印加する電圧Vwellは0Vである。

20

#### 【0038】

図6に、選択セルBIT1に書き込み電圧を印加したときの電荷の動きを示す。ドレイン領域Drmよりも大きな電圧を選択ゲート電極CGに印加して選択用MIS(Qnc)をオン状態とし、ソース領域Srmに正の高電圧を印加することで、ドレイン領域Drmからソース領域Srmへ電子が流れる。チャネル領域を流れるこの電子は、選択ゲート電極CGとメモリゲート電極MGとの境界付近下のチャネル領域(ソース領域Srmとドレイン領域Drmとの間)で加速されてホットエレクトロンになる。そして、ホットエレクトロンは、メモリゲート電極MGに印加された正電圧によってメモリゲート電極MGに引き寄せられメモリゲート電極MG下の電荷蓄積層CSL中に注入される。注入されたホットエレクトロンは、電荷蓄積層CSL中のトラップ準位に捕獲され、その結果、電荷蓄積層CSLに電子が蓄積されてメモリ用nMIS(Qnm)のしきい値電圧が上昇する。

30

#### 【0039】

書き込みディスタートを受ける非選択セルDISTAでは、ソース領域Srmに印加する電圧Vsを5V、メモリゲート電極MGに印加する電圧Vmgを10V、選択ゲート電極CGに印加する電圧Vsgを10Vとし、選択セルBIT1と同じ電圧を印加する。ドレイン領域Drmに印加する電圧Vdは選択セルBIT1とは異なり、選択ゲート電極CGに印加する電圧Vsgよりも大きい1.5Vとしている。選択ゲート電極CGよりも大きな電圧をドレイン領域Drmに印加して、選択用nMIS(Qnc)をオフ状態として書き込みを禁止する。

40

#### 【0040】

書き込みディスタートを受ける非選択セルDISTB, DISTCでは、ソース領域Srmに印加する電圧Vsは5V、メモリゲート電極MGに印加する電圧Vmgは10Vとし、選択セルBIT1と同じ電圧を印加する。選択ゲート電極CGに印加する電圧Vsgは非選択の0V、ドレイン領域Drmに印加する電圧Vdは、選択セルBIT1と同じビット線BL0に接続された非選択セルの場合は0.4V、選択セルBIT1と異なるビット線BL1に接続された非選択セルの場合は1.5Vが印加される。選択ゲート電極CGに印加する電圧Vsgよりもドレイン領域Drmに印加する電圧Vdが大きく、選択用nMIS(Qnc)をオフ状態として書き込みを禁止する。

#### 【0041】

50

図7および図8に、本実施の形態1によるメモリセルの書き込み特性およびディスターブ特性をそれぞれ示す。比較のために、これら図には、選択用nMIS(Qnc)のゲート絶縁膜4にバーズピークのないメモリセル(以下、従来のメモリセルと記す)の書き込み特性およびディスターブ特性も示す。図7および図8中、選択用nMIS(Qnc)のゲート絶縁膜4にバーズピークがあり、選択ゲート電極CGのゲート長方向中央部下のゲート絶縁膜4の厚さ(toxic)が2nm、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さ(toxe)が2.5nmの本実施の形態1によるメモリセルA、選択用nMIS(Qnc)のゲート絶縁膜4にバーズピークがあり、選択ゲート電極CGのゲート長方向中央部下のゲート絶縁膜4の厚さ(toxic)が2nm、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さ(toxe)が3nmの本実施の形態1によるメモリセルB、選択用nMISのゲート絶縁膜にバーズピークがなく、ゲート絶縁膜の厚さが2nmの従来のメモリセルCのそれぞれの特性を示している。

10

## 【0042】

図7に示すように、本実施の形態1によるメモリセルA、Bも従来のメモリセルCも、書き込み速度はほぼ変わらない。すなわち、書き込み速度は選択ゲート電極CGのゲート絶縁膜4の厚さにはほとんど依存しない。これは、書き込みで注入する電子はドレイン領域Drmから供給され、この電子の供給量は選択ゲート電極CGのバーズピークの影響を受けないためであると考えられる。

## 【0043】

これに対し、図8に示すように、ディスターブ特性では、選択ゲート電極CGに印加する電圧Vsgが1Vの非選択セルDISTAと選択ゲート電極CGに印加する電圧Vsgが0Vの非選択セルDISTB、DISTCの両者ともに、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さ(toxe)が増加するに従って、しきい値電圧の上昇が抑制されている。すなわち、選択ゲート電極CGのゲート長方向端部下にバーズピークを導入することにより、ディスターブ耐性が向上する。

## 【0044】

図9に、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4のバーズピーク量としきい値電圧が-1Vに達するディスターブ時間との関係を示す。選択ゲート電極CGのゲート長方向中央部下のゲート絶縁膜4の厚さ(toxic)と選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さ(toxe)との差をバーズピーク量とする。

30

## 【0045】

図9に示すように、バーズピーク量が大きくなると、しきい値電圧が1V上昇するまでの時間が長くなり、ディスターブ耐性が向上しているのが分かる。バーズピーク量が0.5nm以上となると、急激にディスターブ耐性が向上する。

## 【0046】

図10に、ディスターブ時の電子注入のメカニズムを示す。前記図5のディスターブ電圧が印加された場合、メモリゲート電極MGに正電圧が印加され、メモリゲート電極MG下にチャネル領域が形成されるため、ソース領域Srmに印加した5Vの高電圧が選択ゲート電極CGの端部付近まで達する。選択ゲート電極CGに印加する電圧Vsg(1Vまたは0V)よりも大きな電圧が、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4のさらに下にかかることになるため、いわゆるGIDL(Gate Induced drain leakage)電流が流れる。このGIDL電流は、選択ゲート電極CGのゲート長方向端部下の半導体基板1(半導体領域5)で生成した電子正孔対によるもので、このうち電子がソース領域Srmとメモリゲート電極MGに印加した正の高電圧に引っ張られて電荷蓄積層CSL中に注入される。前記図8に示したディスターブ特性では、選択ゲート電極CGに印加する電圧Vsgが1Vの非選択セルDISTAよりも選択ゲート電極CGに印加する電圧Vsgが0Vの非選択セルDISTB、DISTCの方がしきい値電圧の上昇が大きくなっている。ドレイン領域Drmとソース領域Srmとの間のチャネル電流ではなく、選択ゲート電極CG下のGIDL電流によってディスターブの電子注入が起こっていると考えられる。バーズピークを導入すると、電子正孔対が生成される箇所の上のゲート絶縁膜4

40

50

にかかる垂直方向電界が小さくなり、その結果、GIDL電流が減少するため、ディステープ耐性が向上する。

【0047】

次に、「消去」について説明する。

【0048】

前記図4の「消去」欄に示すように、消去は、BTBT(Band-To-Band Tunneling)現象によりホールを発生させ電界加速することでホットホールを電荷蓄積層CSL中に注入するBTBT消去、メモリゲート電極MGまたは半導体基板1からホールをFN(Fowler-Nordheim)トンネリングで電荷蓄積層中に注入するFN消去のいずれかによって行う。

【0049】

BTBT消去を行う場合は、メモリゲート電極MGに印加する電圧Vmgを-6V、ソース領域Srmに印加する電圧Vsを6V、選択ゲート電極CGに印加する電圧Vsgを0Vとし、ドレイン領域Drmは浮遊状態する。pウェルPWには0V(Vwell)を印加する。上記電圧を印加した場合、ソース領域Srmとメモリゲート電極MGとの間にかかる電圧によってソース領域Srmの端部においてBTBT現象で生成されたホールが、ソース領域Srmに印加された高電圧によって加速されてホットホールとなり、メモリゲート電極MGに印加された高電圧によってホットホールがメモリゲート電極MG方向へと引っ張られ、電荷蓄積層CSL中に注入される。注入されたホットホールは電荷蓄積層CSL中のトラップ準位に捕獲され、メモリ用nMIS(Qnm)のしきい値電圧が低下する。

10

【0050】

メモリゲート電極MGからホールを注入するFN消去の場合、ホールのFNトンネル注入が起こりやすいように、前記図1のメモリセルMC1で上層の絶縁膜6tの厚さを3nm以下とするか、上層の絶縁膜6tがない構造とする。上層の絶縁膜6tがある構造の場合、よりホールが注入しやすいように、上層の絶縁膜6tの間に厚さ1nm程度の窒化シリコン膜またはアモルファスシリコン膜を挿入した構造にすると良い。また、上層の絶縁膜6tがない構造の場合、よりホールが注入しやすいように、電荷蓄積層CSLを酸窒化シリコン膜を用いた構造、または窒化シリコン膜および酸窒化シリコン膜を半導体基板側から順に積層した構造とすると良い。メモリゲート電極MGからホール注入するFN消去の印加電圧としては、メモリゲート電極MGに印加する電圧Vmgを15Vとし、その他ソース領域Srmに印加する電圧Vs、選択ゲート電極CGに印加する電圧Vsg、ドレイン領域Drmに印加する電圧Vd、pウェルPWに印加する電圧Vwellは0Vとする。上記電圧を印加すると、メモリゲート電極MGからホールがFNトンネリングで電荷蓄積層CSLに注入される。加えて、書き込み時に電荷蓄積層CSLに蓄積された電子がメモリゲート電極MGへ引き抜かれる。

20

【0051】

半導体基板1からホールを注入するFN消去の場合、ホールのFNトンネル注入が起こりやすいように、前記図1に示したメモリセルMC1において、下層の絶縁膜6bを3nm以下の膜厚にするか、よりホールを注入しやすいように下層の絶縁膜6bの間に厚さ1nm程度の窒化シリコン膜またはアモルファスシリコン膜を挿入した構造とする。半導体基板1からホール注入するFN消去の印加電圧としては、メモリゲート電極MGに印加する電圧Vmgを-15Vとし、その他ソース領域Srmに印加する電圧Vs、選択ゲート電極CGに印加する電圧Vsg、ドレイン領域Drmに印加する電圧Vd、pウェルPWに印加する電圧Vwellは0Vとする。上記電圧を印加すると、半導体基板1からホールがトンネリングで電荷蓄積層CSLに注入される。加えて、書き込み時に電荷蓄積層CSLに蓄積された電子が半導体基板1へ引き抜かれる。

30

【0052】

次に、「読み出し」について説明する。

【0053】

前記図4の「読み出し」欄に示すように、読み出しには、書き込みと逆方向に電流を流して読

40

50

み出す方法と同方向に電流を流して読み出す方法の2種類がある。前記図4に示すように、書込みと逆方向に電流を流して読み出す場合、ドレイン領域Drmに印加する電圧Vdを1.5V、ソース領域Srmに印加する電圧Vsを0V、選択ゲート電極CGに印加する電圧Vsgを1.5V、メモリゲート電極MGに印加する電圧Vmgを1.5Vとする。書込みと同方向に電流を流して読み出す場合、ドレイン領域Drmに印加する電圧Vdとソース領域Srmに印加する電圧Vsを入れ替え、それぞれ0V、1.5Vとする。

#### 【0054】

読み出し時のメモリゲート電極MGに印加する電圧Vmgは、書込み状態におけるメモリ用nMIS(Qnm)のしきい値電圧と消去状態におけるメモリ用nMIS(Qnm)のしきい値電圧との間に設定する。書込み状態および消去状態のしきい値電圧をそれぞれ4Vおよび-1Vに設定すると、上記読み出し時のVmgは両者の中間値となる。中間値とすることで、データ保持中に書込み状態のしきい値電圧が2V低下しても、消去状態のしきい値電圧が2V上昇しても、書込み状態と消去状態を判別することができ、データ保持特性のマージンが広がる。消去状態におけるメモリセルMC1のしきい値電圧を十分低くしておけば、読み出し時の電圧Vmgを0Vとすることもできる。読み出し時の電圧Vmgを0Vとすることで、読み出しディスターブ、すなわち、メモリゲート電極MGへの電圧印加によるしきい値電圧の変動を避けることが可能となる。

10

#### 【0055】

ところで、本実施の形態1によるメモリセルMC1では、選択ゲート電極CGのゲート絶縁膜4にバーズピークを導入する酸化工程において選択ゲート電極CGの側面に厚い絶縁膜が形成されて、この厚い絶縁膜がメモリセルMC1を完成したときに残ると、読み出し電流が減少してしまう。

20

#### 【0056】

図11に、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さ(toxs)とメモリ用nMIS(Qnm)の最大相互コンダクタンスとの関係を示す。選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さ(toxs)は、半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さ(toxb)との比で表している。メモリ用nMIS(Qnm)の最大相互コンダクタンスは、その値が大きいほど大きな読み出し電流が取れることを示しており、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さ(toxs)と半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さ(toxb)との比toxs/toxbが1のときの値で規格化してある。

30

#### 【0057】

図11に示すように、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さ(toxs)と半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さ(toxb)との比toxs/toxbが1.5倍以下であれば、大きな相互コンダクタンスを確保でき、大きな読み出し電流が得られることが分かる。しかしながら、上記比toxs/toxbが1.5倍以上になると、相互コンダクタンスが小さくなり、読み出し電流が減少する。選択ゲート電極CGとメモリゲート電極MGとの間の距離を離していくと、両電極間下のチャネル領域に選択ゲート電極CGおよびメモリゲート電極MGの電圧の影響を受けにくい領域が現れ、それが拡がって両電極間下のチャネル領域の抵抗成分を増やしてしまう。このため、読み出し電流が減少していくことになる。

40

#### 【0058】

以上、前記図4および図5においてメモリ動作の電圧条件を示したが、これらの条件は一例であり、ここで示した数値をもって本発明が限定されるものではない。

#### 【0059】

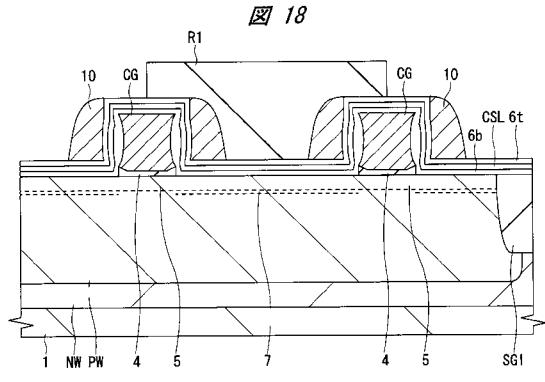

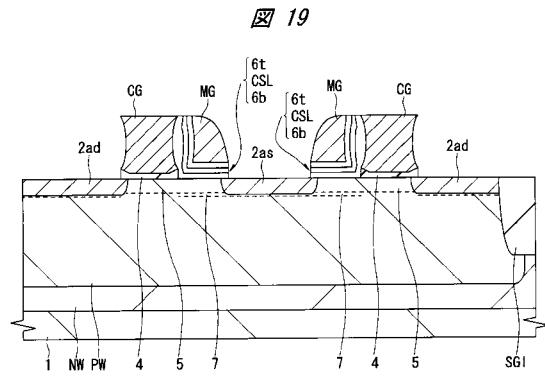

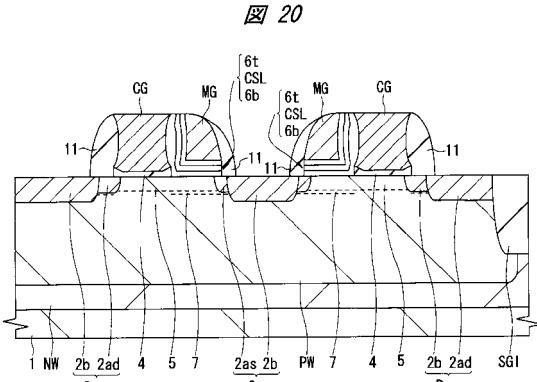

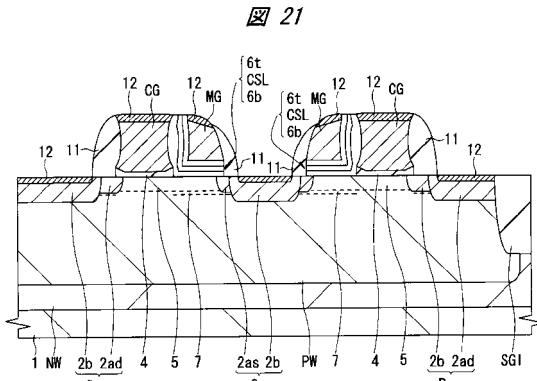

次に、本発明の実施の形態1によるスプリットゲート型MONOSメモリセルの製造方法の一例を図12～図21を用いて説明する。図12～図16、図18～図21は、半導

50

体装置の製造工程中におけるメモリセルの要部断面図であり、前記図1に示したメモリセルの要部断面図と同じ箇所を示し、図17は、多結晶シリコンおよび単結晶シリコンの酸化速度と温度との関係を示すグラフ図である。

#### 【0060】

まず、図12に示すように、例えば $1 \sim 10 \text{ cm}$ 程度の比抵抗を有するp型の単結晶シリコンからなる半導体基板（この段階では半導体ウエハと称する平面略円形状の半導体の薄板）1を準備する。続いて半導体基板1の主面に、例えば溝型の素子分離部SGIおよびこれに取り囲まれるように配置された活性領域等を形成する。すなわち半導体基板1の所定箇所に分離溝を形成した後、半導体基板1の主面上に、例えば酸化シリコン膜からなる絶縁膜を堆積し、さらにその絶縁膜が分離溝内のみに残されるように絶縁膜をCMP（Chemical Mechanical Polishing）法等によって研磨することで、素子分離部SGIを形成する。

10

#### 【0061】

次に、半導体基板1の所定部分に所定の不純物を所定のエネルギーで選択的にイオン注入法等によって導入することにより、埋め込みnウェルNWおよびpウェルPWを形成する。続いて半導体基板1の主面にp型不純物、例えばボロンをイオン注入することにより、選択用nMIS（Qnc）のチャネル形成用のp型の半導体領域5を形成する。この時のp型不純物イオンの打ち込みエネルギーは、例えば $20 \text{ keV}$ 程度、ドーズ量は、例えば $1.5 \times 10^{13} \text{ cm}^{-2}$ 程度である。

20

#### 【0062】

次に、半導体基板1に対して酸化処理を施すことにより、半導体基板1の主面に、例えば酸化シリコン膜からなる厚さ $1 \sim 5 \text{ nm}$ 程度のゲート絶縁膜4を形成する。続いて、半導体基板1の主面上に、例えば $2 \times 10^{20} \text{ cm}^{-3}$ 程度の不純物濃度を有する多結晶シリコン膜からなる第1導体膜9を堆積する。この第1導体膜9はCVD（Chemical Vapor Deposition）法により形成され、その厚さは、例えば $150 \sim 250 \text{ nm}$ 程度を例示することができる。

20

#### 【0063】

次に、図13に示すように、レジストパターンをマスクとして上記第1導体膜9を加工することにより、選択ゲート電極CGを形成する。選択ゲート電極CGのゲート長は、例えば $100 \sim 150 \text{ nm}$ 程度である。選択ゲート電極CGは図面の奥行き方向に延在し、線状のパターンである。このパターンは、例えば前記図3に示したメモリセルのアレイ構成における選択ゲート線CGL0～CGL3に相当する。続いて、露出したゲート絶縁膜4を、例えばフッ酸水溶液で除去する。

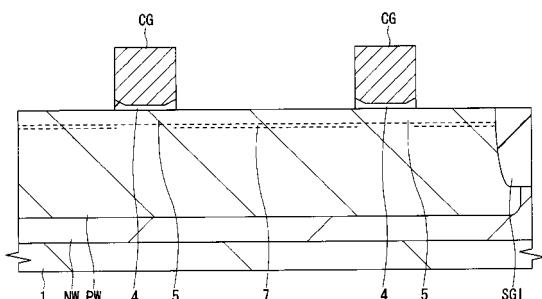

30

#### 【0064】

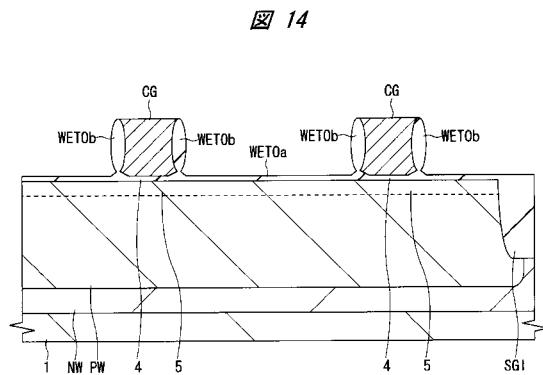

次に、図14に示すように、半導体基板1に対してウエット酸化処理を施すことにより、半導体基板1の主面に、例えば $4 \text{ nm}$ 程度の厚さの酸化シリコン膜WETOaを形成する。ウエット酸化処理の温度は、例えば $750$ である。ウエット酸化処理を行うと、選択ゲート電極CGの側面の多結晶シリコン膜が増速酸化されて、選択ゲート電極CGの側面に釣鐘型の酸化シリコン膜WETObが形成される。さらに、ウエット酸化処理を行うと、選択ゲート電極CGと半導体基板1（半導体領域5）との間のゲート長方向端部下のゲート絶縁膜4にバーズピークが形成される。上記ウエット酸化処理の条件により、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さ（ $t_{oxe}$ ）を、ゲート長方向中央部下のゲート絶縁膜4の厚さ（ $t_{oxc}$ ）よりも $1 \text{ nm}$ 程度厚くすることができる。ウエット酸化処理に代わり、ドライ酸化処理を用いてもよい。ドライ酸化処理は、ウエット酸化処理に比べてバーズピークは形成されにくいことから、ウエット酸化処理よりも酸化量を多くする。例えば半導体基板1の主面に $6 \text{ nm}$ 程度の厚さの酸化シリコン膜WETOaが形成されるまでドライ酸化処理を行う。ドライ酸化処理の温度は、例えば $800$ とする。ドライ酸化処理の場合、選択ゲート電極CGの側面の多結晶シリコン膜は、側面内でほぼ同じ速度で酸化される。

40

#### 【0065】

50

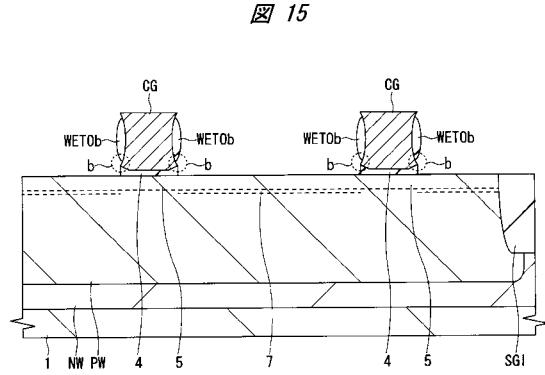

次に、図15に示すように、例えばフッ酸水溶液を用いたウェットエッチング法により、酸化シリコン膜WETO<sub>b</sub>の一部を残して、酸化シリコン膜WETO<sub>a</sub>、WETO<sub>b</sub>をエッチングする。この際、図中、b領域で示す選択ゲート電極CGの側面の下部において残存する酸化シリコン膜WETO<sub>b</sub>の厚さが、後に形成される電荷保持用絶縁膜の下層の絶縁膜6<sub>b</sub>の厚さ以下となるように制御する。選択ゲート電極CGの側面の下部が露出するまで、酸化シリコン膜WETO<sub>b</sub>をエッチングしてもよい。上記エッチングにより、選択ゲート電極CGの側面の中央部に酸化シリコン膜WETO<sub>b</sub>が残るが、これはメモリセルMC1の電気的特性に影響を及ぼさない。続いて、選択ゲート電極CGおよびレジストパターンをマスクとして、半導体基板1の主面にn型不純物、例えばヒ素またはリンをイオン注入することにより、メモリ用nMISのチャネル形成用のn型の半導体領域7を形成する。この時のn型不純物イオンの打ち込みエネルギーは、例えば25keV程度、ドーズ量は、例えば $6.5 \times 10^{12} \text{ cm}^{-2}$ 程度である。

10

## 【0066】

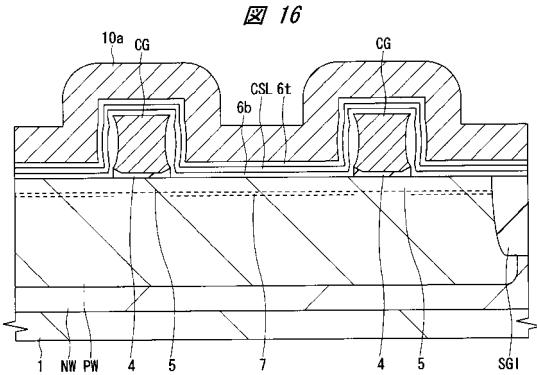

次に、図16に示すように、半導体基板1の主面上に、例えば酸化シリコン膜からなる下層の絶縁膜6<sub>b</sub>、窒化シリコン膜からなる電荷蓄積層CSLおよび酸化シリコン膜からなる上層の絶縁膜6<sub>t</sub>を順次堆積する。下層の絶縁膜6<sub>b</sub>はISSG (In-Situ Stream Generation)酸化法により形成され、その厚さは、例えば1.5~6nm程度、電荷蓄積層CSLはCVD法により形成され、その厚さは、例えば5~20nm程度、上層の絶縁膜6<sub>t</sub>はISSG酸化法またはCVD法により形成され、その厚さは、例えば0~8nm程度を例示することができる。

20

## 【0067】

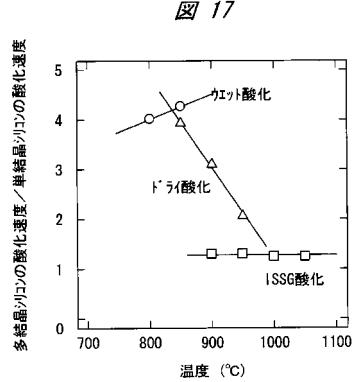

下層の絶縁膜6<sub>b</sub>の成膜にISSG酸化法を用いるのは、高温でなくても半導体基板1を構成する単結晶シリコンと選択ゲート電極CGを構成する多結晶シリコン膜とがほぼ同じ速度で酸化されるためである。図17に、ウェット酸化法、ドライ酸化法およびISSG酸化法を用いた多結晶シリコンの酸化速度と単結晶シリコンの酸化速度との比を示す。酸化温度が900では、ウェット酸化法およびドライ酸化法を用いると、多結晶シリコンは単結晶シリコンよりも3倍以上の速度で酸化するが、ISSG酸化法を用いると、多結晶シリコンと単結晶シリコンとはほぼ同じ速度で酸化することができる。

30

## 【0068】

従って、選択ゲート電極CGの側面に位置し、かつ半導体基板1に最も近い下層の絶縁膜6<sub>b</sub>の厚さ(t<sub>0</sub>×s)と半導体基板1上の下層の絶縁膜6<sub>b</sub>の厚さ(t<sub>0</sub>×b)とを同程度とすることができるので、前記図11を用いて説明したように、メモリセルMC1の読み出し電流を低減させないことができる。また、ISSG酸化法では、既に表面に酸化膜が形成されているシリコンでは、酸化種である活性な酸化ラジカルがシリコンの表面まで届きにくいため、酸化が進みにくいという利点もある。これらにより、前記図15にb領域で示した選択ゲート電極CGの側面の下部に、酸化シリコン膜WETO<sub>b</sub>が下層の絶縁膜6<sub>b</sub>と同程度の厚さで残っていても、ISSG酸化中に酸化シリコン膜WETO<sub>b</sub>の厚さが大きく増えることはなく、読み出し電流の減少を抑制することができる。酸化温度を1000付近まで上げると、ドライ酸化法でも選択ゲート電極CGの側面に厚い酸化膜を形成することなく、下層の絶縁膜6<sub>b</sub>を形成することができる。酸化温度が高いために不純物の拡散が起こるが、バッチ式の酸化装置を使うことができるので、酸化工程において高スループットを実現することができる。

40

## 【0069】

絶縁膜6<sub>b</sub>、6<sub>t</sub>および電荷蓄積層CSLを構成する各膜の構成は、製造する半導体装置の使用方法によって変わるため、ここでは代表的な構成および値のみを例示しているが、上記構成および値に限定されるものではない。

## 【0070】

次に、半導体基板1の主面上に、例えば $2 \times 10^{20} \text{ cm}^{-3}$ 程度の不純物濃度を有する多結晶シリコン膜からなる第2導体膜10aを堆積する。この第2導体膜10aはCVD法により形成され、その厚さは、例えば50~100nm程度を例示することができる

50

。

## 【0071】

次に、図18に示すように、上記第2導体膜10aを異方性のドライエッチング法でエッチバックすることにより、選択ゲート電極CGの両側面に絶縁膜6b, 6tおよび電荷蓄積層CSLを介してサイドウォール10を形成する。図示は省略するが、レジストパターンをマスクとして第2導体膜10aを加工し、後にメモリゲート電極MGに接続するコンタクトホールを形成する領域に引き出し部を形成しておく。また、このサイドウォール10の形成工程では、上層の絶縁膜6tをエッチングストップ層として第2導体膜10aがエッチバックされるが、エッチバックにより上層の絶縁膜6tおよびその下の電荷蓄積層CSLがダメージを受けて損傷しないように、低ダメージのエッチング条件を設定することが望ましい。上層の絶縁膜6tおよび電荷蓄積層CSLが損傷すると、電荷保持特性が劣化するなどのメモリセルの特性劣化が生じることになる。

10

## 【0072】

次に、レジストパターンR1をマスクとして、そこから露出するサイドウォール10をエッチングして、選択ゲート電極CGの側面の片側のみに、サイドウォール10からなるメモリゲート電極MGを形成する。メモリゲート電極MGのゲート長は、例えば50~100nm程度である。

## 【0073】

次に、図19に示すように、レジストパターンR1を除去した後、選択ゲート電極CGとメモリゲート電極MGとの間および半導体基板1とメモリゲート電極MGとの間の絶縁膜6b, 6tおよび電荷蓄積層CSLを残して、その他の領域の絶縁膜6b, 6tおよび電荷蓄積層CSLを選択的にエッチングする。

20

## 【0074】

次に、その端部が選択ゲート電極CGの上面に位置してメモリゲート電極MGと反対側の選択ゲート電極CGの一部を覆うレジストパターンを形成した後、選択ゲート電極CG、メモリゲート電極MGおよびレジストパターンをマスクとしてn型不純物、例えばヒ素を半導体基板1の正面にイオン注入することにより、半導体基板1の正面にn-型の半導体領域2asをメモリゲート電極MGに対して自己整合的に形成する。この時の不純物イオンの打ち込みエネルギーは、例えば5keV程度、ドーズ量は、例えば $1 \times 10^{15} \text{ cm}^{-2}$ 程度である。

30

## 【0075】

次に、その端部が選択ゲート電極CGの上面に位置してメモリゲート電極MG側の選択ゲート電極CGの一部およびメモリゲート電極MGを覆うレジストパターンを形成した後、選択ゲート電極CG、メモリゲート電極MGおよびレジストパターンをマスクとしてn型不純物、例えばヒ素を半導体基板1の正面にイオン注入することにより、半導体基板1の正面にn-型の半導体領域2adを選択ゲート電極CGに対して自己整合的に形成する。この時のn型不純物イオンの打ち込みエネルギーは、例えば7keV程度、ドーズ量は、例えば $1 \times 10^{15} \text{ cm}^{-2}$ である。

## 【0076】

ここでは、先にn-型の半導体領域2asを形成し、その後n-型の半導体領域2adを形成したが、先にn-型の半導体領域2adを形成し、その後n-型の半導体領域2asを形成してもよく、同時にn-型の半導体領域2as, 2adを形成してもよい。また、n-型の半導体領域2adを形成するn型不純物のイオン注入に続いて、p型不純物、例えばボロンを半導体基板1の正面にイオン注入し、n-型の半導体領域2as, 2adの下部を囲むようにp型の半導体領域を形成してもよい。p型不純物イオンの打ち込みエネルギーは、例えば20keV程度、ドーズ量は、例えば $2.5 \times 10^{13} \text{ cm}^{-2}$ である。

40

## 【0077】

次に、図20に示すように、半導体基板1の正面に、例えば酸化シリコン膜からなる厚さ80nm程度の絶縁膜をプラズマCVD法により堆積した後、これを異方性のドライ

50

エッチング法でエッチバックすることにより、選択ゲート電極 C G の片側面およびメモリゲート電極 M G の片側面にそれぞれサイドウォール 1 1 を形成する。サイドウォール 1 1 のスペーサ長は、例えば 60 nm 程度である。これにより、選択ゲート電極 C G と半導体基板 1 との間のゲート絶縁膜 4 の露出していた側面、ならびにメモリゲート電極 M G と半導体基板 1 との間の絶縁膜 6 b , 6 t および電荷蓄積層 C S L の露出していた側面をサイドウォール 1 1 によって覆うことができる。

#### 【 0 0 7 8 】

次に、サイドウォール 1 1 をマスクとして n 型不純物、例えばヒ素およびリンを半導体基板 1 の正面にイオン注入することにより、半導体基板 1 の正面に n<sup>+</sup> 型の半導体領域 2 b を選択ゲート電極 C G およびメモリゲート電極 M G に対して自己整合的に形成する。この時の n 型不純物イオンの打ち込みエネルギーは、例えば 50 keV 程度、ドーズ量は、例えば  $4 \times 10^{15} \text{ cm}^{-2}$  、リンイオンの打ち込みエネルギーは、例えば 40 keV 程度、ドーズ量は、例えば  $5 \times 10^{13} \text{ cm}^{-2}$  である。これにより、n<sup>-</sup> 型の半導体領域 2 a d および n<sup>+</sup> 型の半導体領域 2 b からなるドレイン領域 D r m 、n<sup>-</sup> 型の半導体領域 2 a s および n<sup>+</sup> 型の半導体領域 2 b からなるソース領域 S r m が形成される。

#### 【 0 0 7 9 】

次に、図 2 1 に示すように、選択ゲート電極 C G およびメモリゲート電極 M G の上面、ならびに n<sup>+</sup> 型の半導体領域 2 b の上面に、例えばコバルトシリサイド (CoSi<sub>2</sub>) 層 1 2 を自己整合法、例えばサリサイド (Salicide: Self Align silicide) プロセスにより形成する。まず、半導体基板 1 の正面にスパッタリング法によりコバルト膜を堆積する。続いて、半導体基板 1 に R T A (Rapid Thermal Anneal) 法を用いた熱処理を施すことにより、コバルト膜と選択ゲート電極 C G を構成する多結晶シリコン膜およびメモリゲート電極 M G を構成する多結晶シリコン膜、コバルト膜と半導体基板 1 (n<sup>+</sup> 型の半導体領域 2 b ) を構成する单結晶シリコンとを反応させてコバルトシリサイド層 1 2 を形成する。その後、未反応のコバルト膜を除去する。コバルトシリサイド層 1 2 を形成することにより、コバルトシリサイド層 1 2 と、その上部に形成されるプラグ等との接触抵抗を低減することができ、また選択ゲート電極 C G 、メモリゲート電極 M G 、ソース領域 S r m およびドレイン領域 D r m 自身の抵抗を低減することができる。

#### 【 0 0 8 0 】

次に、半導体基板 1 の正面に、例えば窒化シリコン膜 8 a および酸化シリコン膜 8 b からなる層間絶縁膜 8 を C V D 法により形成する。続いて層間絶縁膜 8 にコンタクトホール C N T を形成した後、コンタクトホール C N T 内にプラグ P L G を形成する。プラグ P L G は、例えばチタンおよび窒化チタンの積層膜からなる相対的に薄いバリア膜と、そのバリア膜に包まれるように形成されたタンゲステンまたはアルミニウム等からなる相対的に厚い導体膜とを有している。その後、層間絶縁膜 8 上に、例えばタンゲステン、アルミニウムまたは銅等からなる第 1 層配線 M 1 を形成することによって、前記図 1 に示したメモリセル M C 1 が略完成する。これ以降は、通常の半導体装置の製造工程を経て、半導体装置を製造する。

#### 【 0 0 8 1 】

このように、本実施の形態 1 によれば、選択ゲート電極 C G のゲート長方向端部下のゲート絶縁膜 4 の厚さ (t<sub>o</sub> × e) をゲート長方向中央部下のゲート絶縁膜 4 の厚さ (t<sub>o</sub> × c) よりも厚く形成し、選択ゲート電極 C G と電荷蓄積層 C S L との間に位置し、かつ半導体基板 1 に最も近い下層の絶縁膜 6 b の厚さを半導体基板 1 と電荷蓄積層 C S L との間に位置する下層の絶縁膜 6 b の厚さの 1.5 倍以下とすることにより、読み出し電流を低減させることなく、S S I 方式による書き込み時の非選択メモリセルのディスターブ耐性を向上させることができる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減することができる。

#### 【 0 0 8 2 】

(実施の形態 2 )

本実施の形態 2 では、選択用 n M I S のゲート絶縁膜の形成方法が前述した実施の形態

10

20

30

40

50

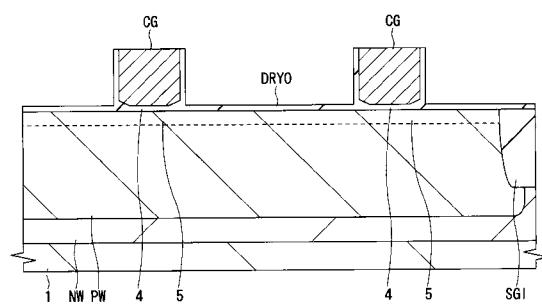

1 とは異なるスプリットゲート型 MONOS メモリセルの製造方法の一例を説明する。本実施の形態 2 によるスプリットゲート型 MONOS メモリセルの製造方法を図 22 ~ 図 24 を用いて説明する。図 22 ~ 図 24 は半導体装置の製造工程中におけるメモリセルの要部断面図である。本実施の形態 2 であるスプリットゲート型 MONOS メモリセルのアレイ構成および動作条件は、前述した実施の形態 1 と同一である。なお、選択用 nMIS のゲート絶縁膜を形成する工程以外の製造過程は、前述した実施の形態 1 のメモリセル MC1 の製造過程と同様であるため、その説明を省略する。

#### 【 0083 】

前述した実施の形態 1 の前記図 13 を用いて説明したように、選択ゲート電極 CG を形成した後、露出したゲート絶縁膜 4 を、例えばフッ酸水溶液で除去する。この際、図 22 に示すように、選択ゲート電極 CG のゲート長方向端部下のゲート絶縁膜 4 を所定の距離ほどサイドエッティングする。選択ゲート電極 CG のゲート長方向端部から除去される距離は、例えば 3 ~ 20 nm である。

10

#### 【 0084 】

次に、図 23 に示すように、半導体基板 1 に対してドライ酸化処理または ISSG 酸化処理を施すことにより、半導体基板 1 の主面に、例えば 4 nm 程度の厚さの酸化シリコン膜 DRYO を形成する。ドライ酸化処理の温度は、例えば 800 、 ISSG 酸化処理の温度は、例えば 900 である。選択ゲート電極 CG のゲート長方向端部下が露出した状態で酸化処理を行うと、ウエット酸化処理に比べてバーズピークが形成されにくくドライ酸化処理および ISSG 酸化処理を用いても、効率よくバーズピークを形成することができる。また、ドライ酸化処理および ISSG 酸化処理では、選択ゲート電極 CG の側面の多結晶シリコン膜が增速酸化されにくく、ウエット酸化処理では形成される選択ゲート電極 CG の側面の釣鐘型の酸化シリコン膜が形成されない。

20

#### 【 0085 】

次に、図 24 に示すように、例えばフッ酸水溶液を用いたウエットエッティング法により、酸化シリコン膜 DRYO をエッティングする。この際、選択ゲート電極 CG の側面の下部において残存する酸化シリコン膜 DRYO の厚さが、後に形成される電荷保持用絶縁膜の下層の絶縁膜 6b の厚さ以下となるように制御する。選択ゲート電極 CG の側面の下部が露出するまで、酸化シリコン膜 DRYO をエッティングしてもよい。続いて、選択ゲート電極 CG およびレジストパターンをマスクとして、半導体基板 1 の主面に n 型不純物、例えばヒ素またはリンをイオン注入することにより、メモリ用 nMIS (Q nm) のチャネル形成用の n 型の半導体領域 7 を形成する。

30

#### 【 0086 】

このように、本実施の形態 2 によれば、選択ゲート電極 CG のゲート長方向端部下のゲート絶縁膜 4 にバーズピークを形成することができるので、前述した実施の形態 1 と同様の効果が得られる。また、バーズピークを形成する際には、ドライ酸化処理または ISSG 酸化処理を用いていることから、前述した実施の形態 1 のように、選択ゲート電極 CG の側面に釣鐘型の酸化シリコン膜が形成されないので、選択ゲート電極 CG の形状や寸法の変動を抑えることができる。

40

#### 【 0087 】

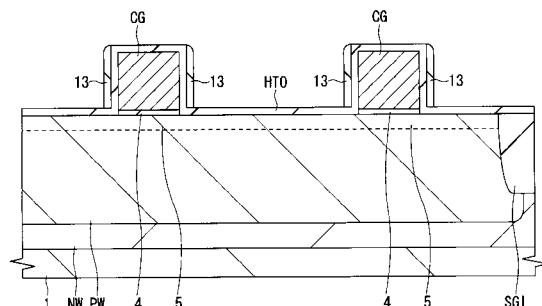

##### ( 実施の形態 3 )

本実施の形態 3 では、選択用 nMIS のゲート絶縁膜の形成方法が前述した実施の形態 1 、 2 とは異なるスプリットゲート型 MONOS メモリセルの製造方法の一例を説明する。本実施の形態 3 によるスプリットゲート型 MONOS メモリセルの製造方法を図 25 ~ 図 28 を用いて説明する。図 25 ~ 図 28 は半導体装置の製造工程中におけるメモリセルの要部断面図である。本実施の形態 3 であるスプリットゲート型 MONOS メモリセルのアレイ構成および動作条件は、前述した実施の形態 1 と同一である。なお、選択用 nMIS のゲート絶縁膜を形成する工程以外の製造過程は、前述した実施の形態 1 のメモリセル MC1 の製造過程と同様であるため、その説明を省略する。

#### 【 0088 】

50

前述した実施の形態 1 の前記図 1 3 を用いて説明したように、選択ゲート電極 C G を形成した後、露出したゲート絶縁膜 4 を、例えばフッ酸水溶液で除去する。

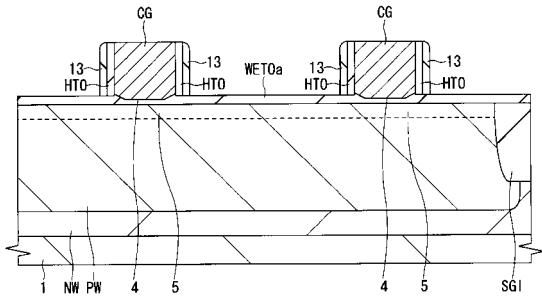

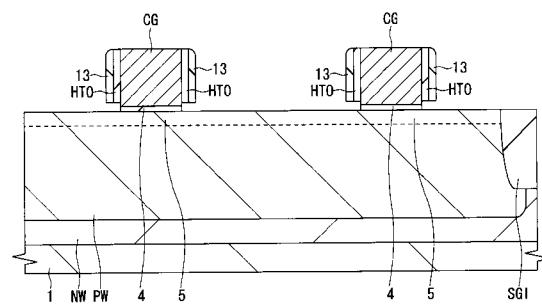

【 0 0 8 9 】

次に、図 2 5 に示すように、半導体基板 1 の主面上に C V D 法により、例えば 5 nm 程度の厚さの高温酸化シリコン膜 H T O を形成する。高温酸化シリコン膜 H T O を用いると、その後のウエットエッチングにより容易に除去できるという利点があるが、ウエット酸化処理、ドライ酸化処理または I S S G 酸化処理により酸化シリコン膜を形成してもよい。続いて、半導体基板 1 の主面上に低圧 C V D 法により、例えば 5 nm 以上の厚さの窒化シリコン膜を形成した後、この窒化シリコン膜を異方性のドライエッチング法でエッチバックすることにより、選択ゲート電極 C G の両側面に高温酸化シリコン膜 H T O を介してサイドウォール 1 3 を形成する。

10

【 0 0 9 0 】

次に、図 2 6 に示すように、例えばフッ酸水溶液を用いたウエットエッチング法により、選択ゲート電極 C G の下のゲート絶縁膜 4 が露出するまで、高温酸化シリコン膜 H T O をエッチングする。

【 0 0 9 1 】

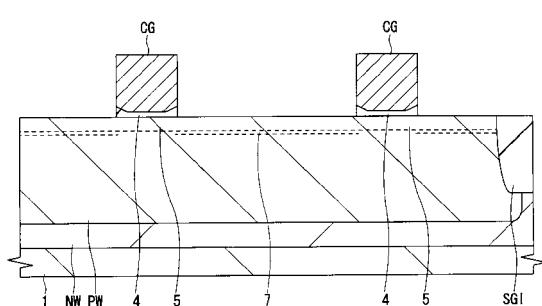

次に、図 2 7 に示すように、半導体基板 1 に対してウエット酸化処理を施すことにより、半導体基板 1 の主面上に、例えば 4 nm 程度の厚さの酸化シリコン膜 W E T O a を形成する。ウエット酸化処理の温度は、例えば 750 である。ウエット酸化処理を行うと、選択ゲート電極 C G と半導体基板 1 ( 半導体領域 5 ) との間のゲート長方向端部下に位置するゲート絶縁膜 4 の端部にバーズピークが形成される。また、選択ゲート電極 C G の側面が露出していない状態でウエット酸化処理を行うので、選択ゲート電極 C G の側面の多結晶シリコン膜が増速酸化されない。ウエット酸化処理に代わり、ドライ酸化処理を用いてもよい。ドライ酸化処理は、ウエット酸化処理に比べてバーズピークは形成されにくいことから、ウエット酸化処理よりも酸化量を多くする。例えば半導体基板 1 の主面上に 6 nm 程度の厚さの酸化シリコン膜 W E T O a が形成されるまでドライ酸化処理を行う。ドライ酸化処理の温度は、例えば 800 とする。

20

【 0 0 9 2 】

次に、図 2 8 に示すように、例えば熱リン酸を用いて選択ゲート電極 C G の側面のサイドウォール 1 3 を除去し、フッ酸水溶液を用いたウエットエッチング法により、酸化シリコン膜 W E T O a および高温酸化シリコン膜 H T O を除去する。続いて、選択ゲート電極 C G およびレジストパターンをマスクとして、半導体基板 1 の主面上に n 型不純物、例えばヒ素またはリンをイオン注入することにより、メモリ用 n M I S ( Q nm ) のチャネル形成用の n 型の半導体領域 7 を形成する。

30

【 0 0 9 3 】

このように、本実施の形態 3 によれば、選択ゲート電極 C G のゲート長方向端部下のゲート絶縁膜 4 にバーズピークを形成することができる。前述した実施の形態 1 と同様の効果が得られる。また、バーズピークを形成する際には、選択ゲート電極 C G の側面に高温酸化シリコン膜 H T O および窒化シリコン膜からなるサイドウォール 1 3 を形成しており、選択ゲート電極 C G の側面に釣鐘型の酸化シリコン膜が形成されないので、選択ゲート電極 C G の形状や寸法の変動を抑えることができる。

40

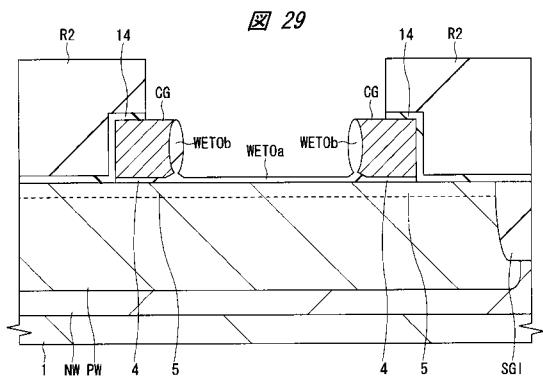

【 0 0 9 4 】

( 実施の形態 4 )

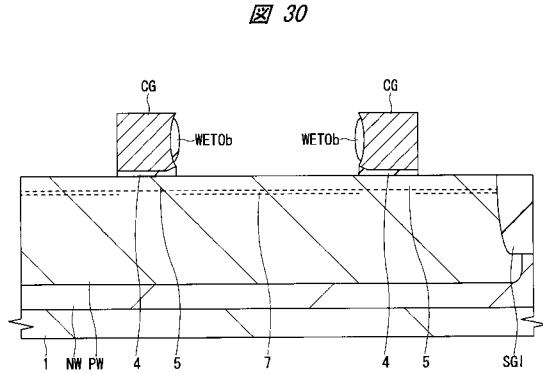

本実施の形態 4 では、選択用 n M I S の選択ゲート電極 C G のゲート長方向の片端部下のゲート絶縁膜のみにバーズピークを形成する。前述した実施の形態 1 ~ 3 では、選択ゲート電極のゲート長方向の両端部下のゲート絶縁膜にバーズピークを形成したが、片側のみにバーズピークを形成しても、読み出し電流の低減を抑制することができて、非選択メモリセルのディスターブ耐性を向上させることができる。本実施の形態 4 によるスプリットゲート型 M O N O S メモリセルの製造方法を図 2 9 および図 3 0 を用いて説明する。図 2 9 および図 3 0 は半導体装置の製造工程中におけるメモリセルの要部断面図である。本実

50

施の形態 4 であるスプリットゲート型 MONOS メモリセルのアレイ構成および動作条件は、前述した実施の形態 1 と同一である。なお、選択用 nMIS (Qnm) のゲート絶縁膜を形成する工程以外の製造過程は、前述した実施の形態 1 のメモリセル MC1 の製造過程と同様であるため、その説明を省略する。

【0095】

前述した実施の形態 1 の前記図 14 を用いて説明したように、半導体基板 1 の主面に、例えば 4 nm 程度の厚さの酸化シリコン膜 WETOa を形成し、選択ゲート電極 CG の側面に釣鐘型の酸化シリコン膜 WETOb を形成し、選択ゲート電極 CG と半導体基板 1 (半導体領域 5) との間のゲート長方向端部下のゲート絶縁膜 4 にバーズピークを形成する。

10

【0096】

次に、図 29 に示すように、選択用 nMIS (Qnm) のゲート絶縁膜 4 にバーズピークを形成するドレイン領域 Drm 側を覆うレジストパターンを形成し、これをマスクとして、そこから露出するソース領域 Srm 側の酸化シリコン膜 WETOa, WETOb を除去する。続いて、上記レジストパターンを除去した後、半導体基板 1 の主面上に、例えば窒化シリコン膜 14 を形成した後、選択用 nMIS (Qnm) のゲート絶縁膜 4 にバーズピークを形成しないソース領域 Srm を覆うレジストパターン R2 を形成する。

【0097】

次に、図 30 に示すように、例えばフッ酸水溶液を用いたウエットエッチング法により、レジストパターン R2 をマスクとして、そこから露出する窒化シリコン膜 14 を除去し、さらに、酸化シリコン膜 WETOb の一部を残して、酸化シリコン膜 WETOa, WETOb をエッチングする。この際、選択ゲート電極 CG の側面の下部において残存する酸化シリコン膜 WETOb の厚さが、後に形成される電荷保持用絶縁膜の下層の絶縁膜 6b の厚さ以下となるように制御する。選択ゲート電極 CG の側面の下部が露出するまで、酸化シリコン膜 WETOb をエッチングしてもよい。

20

【0098】

次に、レジストパターン R2 を除去し、窒化シリコン膜 14 を除去した後、選択ゲート電極 CG およびレジストパターンをマスクとして、半導体基板 1 の主面に n 型不純物、例えばヒ素またはリンをイオン注入することにより、メモリ用 nMIS (Qnm) のチャネル形成用の n 型の半導体領域 7 を形成する。

30

【0099】

このように、本実施の形態 4 によれば、選択ゲート電極 CG のゲート長方向の片端部下のゲート絶縁膜 4 にバーズピークを形成することができるので、前述した実施の形態 1 と同様の効果が得られる。また、選択ゲート電極 CG の片方の側面のみに釣鐘型の酸化シリコン膜が形成されるので、選択ゲート電極 CG の形状や寸法の変動を前述した実施の形態 1 のメモリセルよりも抑えることができる。

【0100】

(実施の形態 5)

前述した実施の形態 1 ~ 4 では、メモリセルのみの製造方法を例示したが、実際は、同時に混載する周辺回路の MIS も合わせて形成される。周辺回路の MIS には、コアロジック用の MIS と高電圧制御用の高耐圧 MIS とがある。このうち、コアロジック用の MIS のゲート電極とメモリセルの選択ゲート電極とを同時に形成せず、メモリセルの選択ゲート電極を形成した後にコアロジック用の MIS のゲート電極を形成することで、コアロジック用の MIS のゲート絶縁膜にはバーズピークを形成せず、メモリセルの選択 nMIS のゲート絶縁膜にはバーズピークを形成することができる。コアロジック用の MIS にバーズピークを形成しなければ、コアロジック用の MIS のオン電流は低減しないので、コアロジック回路の高速動作を確保することができる。また、先にメモリセルを形成することにより、メモリセルを形成する際の熱負荷が周辺回路の MIS を形成する前にかかるため、メモリセルの製造過程に影響されずに周辺回路の MIS を最適な条件で形成することができる。これにより、高速動作に適した周辺回路の MIS を形成することができる。

40

50

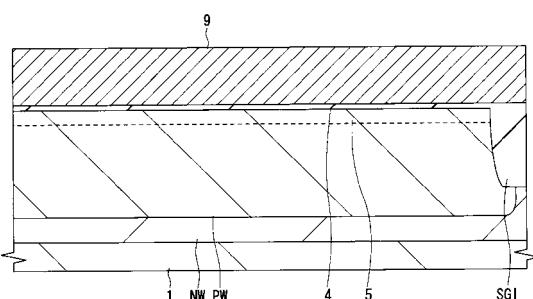

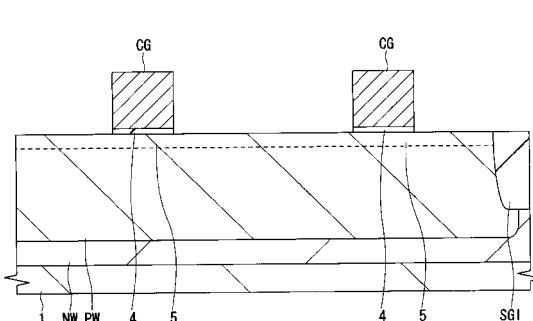

## 【0101】

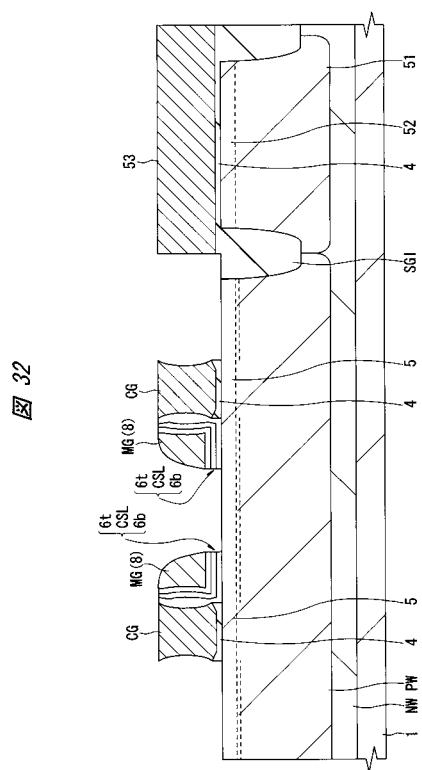

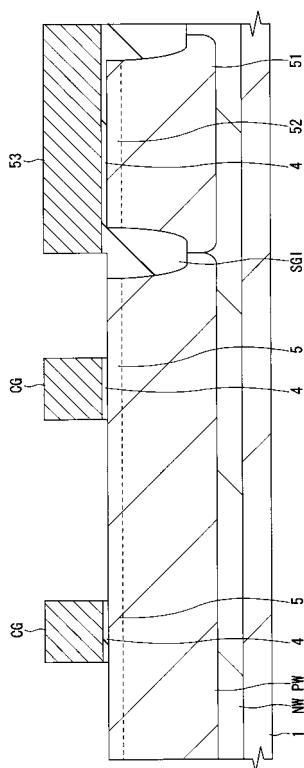

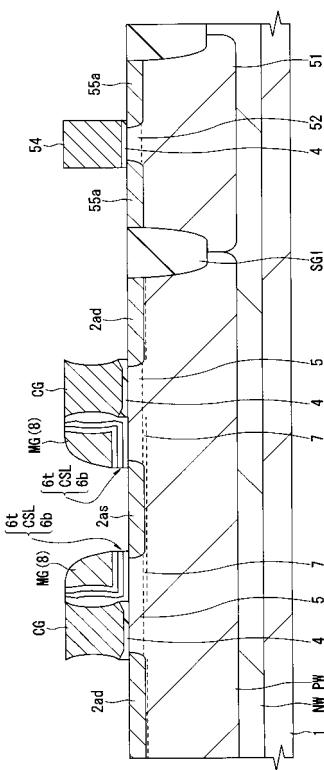

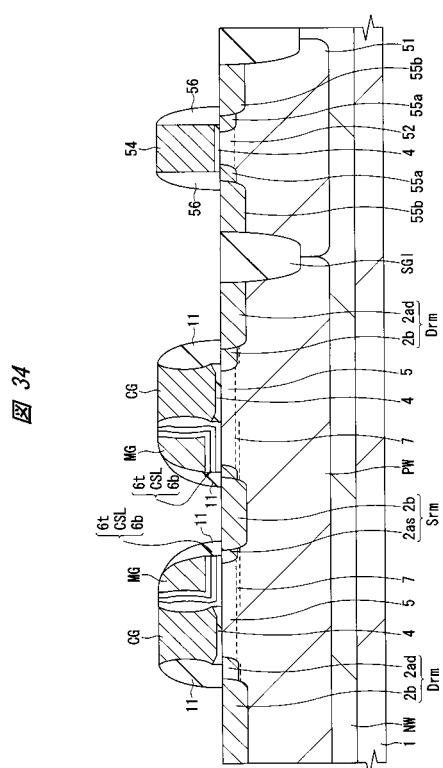

本実施の形態5による周辺回路のnMISおよびスプリットゲート型MONOSメモリセルの製造方法を図31～図34を用いて説明する。図31～図34は半導体装置の製造工程中における周辺回路のnMISおよびメモリセルの要部断面図である。本実施の形態4であるスプリットゲート型MONOSメモリセルのアレイ構成および動作条件は、前述した実施の形態1と同一である。なお、メモリセルの製造方法は、前述した実施の形態1のメモリセルMC1の製造方法と同様であるため、その詳細な説明は省略する。

## 【0102】

まず、図31に示すように、前述した実施の形態1（前記図12参照）と同様にして、半導体基板1の主面に素子分離部SGIを形成し、メモリセル領域および周辺回路領域に埋め込みnウェルNWおよびpウェルPW, 51を形成する。続いて、メモリセル領域に選択用nMIS（Qnc）のチャネル形成用の半導体領域5を形成し、周辺回路領域にコアロジック用のnMISのチャネル形成用の半導体領域52を形成する。

10

## 【0103】

次に、半導体基板1の主面にゲート絶縁膜4を形成した後、半導体基板1の主面上に多結晶シリコン膜からなる第1導体膜53を堆積する。続いて、レジストパターンをマスクとして上記第1導体膜53を加工することにより、メモリセル領域に選択ゲート電極CGを形成する。周辺回路領域にコアロジック用のnMISのゲート電極も同時に形成することはできるが、ここでは周辺回路領域の第1導体膜53をレジストパターンで覆い、コアロジック用のnMISのゲート電極の加工は行わない。その後、露出したゲート絶縁膜4を、例えばフッ酸水溶液で除去する。

20

## 【0104】

次に、図32に示すように、前述した実施の形態1（前記図14～図19参照）と同様にして、メモリセル領域においては、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4にバーズピークを形成し、電荷保持用絶縁膜（絶縁膜6b, 6tおよび電荷蓄積層CSL）を形成し、メモリゲート電極MGを形成する。この間、周辺回路領域においては、第1導体膜53は加工しない。

20

## 【0105】

次に、図33に示すように、レジストパターンをマスクとして、周辺回路領域の第1導体膜53をドライエッチング法により加工して、コアロジック用のnMISのゲート電極54を形成する。このとき、メモリセル領域はレジストパターンにより覆う。続いて、ゲート電極54をマスクとしてn型不純物を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn<sup>-</sup>型の半導体領域55aをゲート電極54に対して自己整合的に形成する。

30

## 【0106】

次に、図34に示すように、半導体基板1の主面上に、例えば酸化シリコン膜からなる絶縁膜をプラズマCVD法により堆積した後、これを異方性のドライエッチング法でエッチバックすることにより、メモリセル領域の選択ゲート電極CGの片側面およびメモリゲート電極MGの片側面にそれぞれサイドウォール11を形成し、同時に周辺回路領域のコアロジック用のnMISのゲート電極54の両側面にサイドウォール56を形成する。続いて、メモリセル領域では、サイドウォール11をマスクとしてn型不純物を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn<sup>+</sup>型の半導体領域2bを選択ゲート電極CGおよびメモリゲート電極MGに対して自己整合的に形成する。これにより、n<sup>-</sup>型の半導体領域2adおよびn<sup>+</sup>型の半導体領域2bからなるドレイン領域Drm、n<sup>-</sup>型の半導体領域2asおよびn<sup>+</sup>型の半導体領域2bからなるソース領域Srmが形成される。また、周辺回路領域では、サイドウォール56をマスクとしてn型不純物を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn<sup>+</sup>型の半導体領域55bをゲート電極54に対して自己整合的に形成する。これにより、n<sup>-</sup>型の半導体領域55aおよびn<sup>+</sup>型の半導体領域55bからなるドレイン・ソースが形成される。その後は、例えば前述した実施の形態1（前記図21参照）と同様にして、配線等を

40

50

形成する。

【0107】

このように、本実施の形態5によれば、メモリセルを形成した後に、周辺回路のMISを形成することで、ゲート絶縁膜4にバーズピークが形成されたメモリセルの選択用nMIS(Qnc)と、ゲート絶縁膜にバーズピークが形成されない周辺回路のMISとを同一基板上に混載した半導体装置を製造することができる。

【0108】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0109】

例えば、本実施の形態においては、メモリセルの電荷保持用絶縁膜として、窒化シリコン膜からなる電荷蓄積層を用いたが、窒化シリコン膜に代わり、酸窒化シリコン膜、酸化タンタル膜、酸化アルミニウム膜等の電荷トラップ性絶縁膜を用いてもよい。また、電荷蓄積層として多結晶シリコン膜等の導電性材料または導電性材料からなる微粒子(ドット)を用いてもよい。

【産業上の利用可能性】

【0110】

本発明は、窒化膜のような絶縁膜に電荷を蓄える不揮発性メモリセルを有する半導体記憶装置に適用することができる。

【図面の簡単な説明】

【0111】

【図1】本発明の実施の形態1によるチャネルをメモリゲート電極に対して交差する方向に沿って切断したスプリットゲート型MONOSメモリセルの要部断面図である。

【図2】図1のa領域を拡大して示した要部断面図である。

【図3】本発明の実施の形態1によるメモリセルのアレイ構成を示す回路図である。

【図4】本発明の実施の形態1による選択セルの書き込み、消去および読出し時において、各配線(選択ゲート線、メモリゲート線、ソース線およびビット線)に印加される電圧条件の一例である。

【図5】本発明の実施の形態1による選択セルに情報を書込む場合に、選択セル、非選択セルの各端子に印加される電圧条件の一例である。

【図6】本発明の実施の形態1による書き込み選択メモリセルの電荷の動きを示すメモリセルの要部断面図である。

【図7】本発明の実施の形態1によるメモリセルの書き込み特性を示すグラフ図である。

【図8】本発明の実施の形態1によるディスターブ特性を示すグラフ図である。

【図9】本発明の実施の形態1による選択ゲート電極のゲート長方向端部下のゲート絶縁膜のバーズピーク量としきい値電圧が-1Vに達するディスターブ時間との関係を示すグラフ図である。

【図10】本発明の実施の形態1によるディスターブ時の電子注入のメカニズムを説明するためのメモリセルの要部断面図である。

【図11】本発明の実施の形態1による選択ゲート電極と電荷蓄積層との間に位置する下層の絶縁膜の厚さとメモリ用nMISの最大相互コンダクタンスとの関係を示すグラフ図である。

【図12】本発明の実施の形態1によるスプリットゲート型MONOSメモリセルの製造工程中の要部断面図である。

【図13】図12に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

【図14】図13に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

【図15】図14に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

10

20

30

40

50

- 【図16】図15に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

- 【図17】本発明の実施の形態1による多結晶シリコン膜および単結晶シリコン膜の酸化速度と温度との関係を示すグラフ図である。

- 【図18】図16に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

- 【図19】図18に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

- 【図20】図19に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である 10

- 【図21】図20に続くメモリセルの製造工程中の図12と同じ箇所の要部断面図である。

- 【図22】本発明の実施の形態2によるスプリットゲート型MONOSメモリセルの製造工程中の要部断面図である。

- 【図23】図22に続くメモリセルの製造工程中の図22と同じ箇所の要部断面図である。

- 【図24】図23に続くメモリセルの製造工程中の図22と同じ箇所の要部断面図である。

- 【図25】本発明の実施の形態3によるスプリットゲート型MONOSメモリセルの製造工程中の要部断面図である 20

- 【図26】図25に続くメモリセルの製造工程中の図25と同じ箇所の要部断面図である。

- 【図27】図26に続くメモリセルの製造工程中の図25と同じ箇所の要部断面図である。

- 【図28】図27に続くメモリセルの製造工程中の図25と同じ箇所の要部断面図である。

- 【図29】本発明の実施の形態4によるスプリットゲート型MONOSメモリセルの製造工程中の要部断面図である。

- 【図30】図29に続くメモリセルの製造工程中の図29と同じ箇所の要部断面図である 30

- 【図31】本発明の実施の形態5によるスプリットゲート型MONOSメモリセルの製造工程中の要部断面図である。

- 【図32】図31に続くメモリセルの製造工程中の図31と同じ箇所の要部断面図である。

- 【図33】図32に続くメモリセルの製造工程中の図31と同じ箇所の要部断面図である。

- 【図34】図33に続くメモリセルの製造工程中の図31と同じ箇所の要部断面図である。

- 【図35】本発明者らが検討したスプリットゲート型メモリセルを示す要部断面図である 40

- 【図36】本発明者らが検討したスプリットゲート型メモリセルを示す要部断面図である。

- 【符号の説明】

- 【0112】

- 1 半導体基板

- 2 a d , 2 a s , 2 b 半導体領域

- 3 シリサイド層

- 4 ゲート絶縁膜

- 5 半導体領域

|                                               |              |    |

|-----------------------------------------------|--------------|----|

| 6 b , 6 t                                     | 絶縁膜          |    |

| 7                                             | 半導体領域        |    |

| 8                                             | 層間絶縁膜        |    |

| 8 a                                           | 窒化シリコン膜      |    |

| 8 b                                           | 酸化シリコン膜      |    |

| 9                                             | 第1導体膜        |    |

| 10                                            | サイドウォール      |    |

| 10 a                                          | 第2導体膜        |    |

| 11                                            | サイドウォール      |    |

| 12                                            | コバルトシリサイド層   | 10 |

| 13                                            | サイドウォール      |    |

| 14                                            | 窒化シリコン膜      |    |

| 5 1                                           | p ウェル        |    |

| 5 2                                           | 半導体領域        |    |

| 5 3                                           | 第1導体膜        |    |

| 5 4                                           | ゲート電極        |    |

| 5 5 a , 5 5 b                                 | 半導体領域        |    |

| 5 6                                           | サイドウォール      |    |

| B I T 1                                       | 選択セル         |    |

| B L 0 , B L 1                                 | ビット線         | 20 |

| C G                                           | 選択ゲート電極      |    |

| C G L 0 , C G L 1 , C G L 2 , C G L 3         | 選択ゲート線(ワード線) |    |

| C N T                                         | コンタクトホール     |    |

| C S L                                         | 電荷蓄積層        |    |

| D I S T A , D I S T B , D I S T C             | 非選択セル        |    |

| D r m                                         | ドレイン領域       |    |

| D R Y O                                       | 酸化シリコン膜      |    |

| G A P                                         | 側壁酸化膜        |    |

| H T O                                         | 高温酸化シリコン膜    |    |

| M 1                                           | 第1層配線        | 30 |

| M C 1                                         | メモリセル        |    |

| M G                                           | メモリゲート電極     |    |

| M G L , M G L 0 , M G L 1 , M G L 2 , M G L 3 | メモリゲート線      |    |

| N I                                           | 窒化シリコン膜      |    |

| N W                                           | 埋め込みnウェル     |    |

| O I b                                         | 下部酸化膜        |    |

| O I t                                         | 上部酸化膜        |    |

| O G                                           | ゲート絶縁膜       |    |

| P L G                                         | プラグ          |    |

| P W                                           | p ウェル        | 40 |

| Q n c                                         | 選択用nMIS      |    |

| Q n m                                         | メモリ用nMIS     |    |

| R 1 , R 2                                     | レジストパターン     |    |

| S G I                                         | 素子分離部        |    |

| S L 0 , S L 1                                 | ソース線         |    |

| S r m                                         | ソース領域        |    |

| S U B                                         | 半導体基板        |    |

| W E T O a , W E T O b                         | 酸化シリコン膜      |    |

【図1】

【図2】

【図3】

【図4】

|      | CGLO        | CGL1~3 | MGL | SLO | SL1 | BL0 | BL1  | 選択ビ               |

|------|-------------|--------|-----|-----|-----|-----|------|-------------------|

| 書き込み | ソサイド注入      | 1.5    | 0   | 10  | 5   | 0   | 0.8  | 1.5               |

|      | BTBT        | 0      | 0   | -6  | 6   | 0   | OPEN | OPEN              |

|      |             |        |     |     |     |     |      | SLO, MGL両方に接続されたビ |

| 消去   | ゲートホール FN注入 | 0      | 0   | 15  | 0   | 0   | 0    | 0                 |

|      | 基板ホール FN注入  | 0      | 0   | -15 | 0   | 0   | 0    | 0                 |

| 読み出し | 書き込み逆方向     | 1.5    | 0   | 1.5 | 0   | 0   | 1.5  | 0                 |

|      | 書き込み同方向     | 1.5    | 0   | 1.5 | 1.5 | 0   | 0    | 1.5               |

|      |             |        |     |     |     |     |      | BIT1              |

【図5】

図5

| 選択ビ     | Vsg   | Vmg | Vs | Vd | Vwell      |

|---------|-------|-----|----|----|------------|

| 書き込み    | BIT1  | 1.0 | 10 | 5  | 0.4        |

| 書き込み    | DISTA | 1.0 | 10 | 5  | 1.5        |

| データアクセス | DISTB | 0   | 10 | 5  | 0.4 or 1.5 |

|         | DISTC |     |    |    | 0          |

【図 6】

図 6

【図 8】

図 8

【図 7】

図 7

【図 9】

図 9

【図 10】

図 10

【図 12】

図 12

【図 11】

図 11

【図 13】

図 13

【図 14】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図 2 2】

図 22

【図 2 4】

図 24

【図 2 3】

図 23

【図 2 5】

図 25

【図 2 7】

図 27

【図 2 6】

図 26

【図 2 8】

図 28

【 図 2 9 】

【図30】

【 図 3 2 】

【 図 3 1 】

【 図 3 3 】

【 図 3 4 】

【図35】

【図36】

---

フロントページの続き

(72)発明者 安井 感

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

(72)発明者 有金 剛

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

(72)発明者 峰 利之

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

F ターム(参考) 5F083 EP17 EP18 EP23 EP33 EP35 EP36 EP48 EP49 EP63 EP68

EP77 ER02 ER11 GA09 GA15 GA16 HA02 JA03 JA04 JA05

JA06 JA33 JA35 JA36 JA37 JA39 JA40 JA53 MA05 NA01

PR05 PR09 PR12 PR34 PR43 PR44 PR45 PR53 PR54 PR55

ZA05 ZA07

5F101 BA23 BA35 BA42 BA45 BA46 BA47 BA54 BC12 BD07 BD10

BD15 BD22 BD35 BE02 BE05 BE07 BH03 BH16 BH21