### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-118045 (P2008-118045A)

(43) 公開日 平成20年5月22日(2008.5.22)

(51) Int.Cl.

FΙ

テーマコード (参考)

HO1L 21/822 HO1L 27/04 (2006.01) (2006.01) HO1L 27/04 HO1L 27/04

C P 5F038

審査請求 未請求 請求項の数 20 OL (全 19 頁)

(21) 出願番号 (22) 出願日 特願2006-301891 (P2006-301891) 平成18年11月7日 (2006.11.7) (71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74)代理人 100109210

弁理士 新居 広守

(72)発明者 西尾 明彦

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72)発明者 加藤 由明

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72)発明者 按田 義治

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

F ターム (参考) 5F038 AC02 AC05 AC15 AR07 AR16

CD18 EZ02 EZ14 EZ15 EZ20

(54) 【発明の名称】半導体装置および半導体装置の製造方法

# (57)【要約】

【課題】特に、ペロブスカイト構造の高誘電体酸化物による容量素子と窒化物による容量素子と高抵抗金属材料による抵抗素子とを同一化合物半導体基板上に集積化した半導体装置およびその製造方法に関し、素子の特性を損ねることなく、プロセスコストの低減を可能とする半導体装置およびその製造方法を提供する。

【解決手段】高誘電体酸化物による容量素子である高誘電体容量素子部20と窒化物による容量素子である窒化物容量素子部40との下部電極と、高抵抗金属材料による抵抗素子である金属抵抗素子30の下部電極とを同一材料の積層金属層103で同時に形成する。また、金属抵抗素子30の下部電極である積層金属層103と接するように形成することを特徴とする。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

第1および第2の容量素子と抵抗素子とを備える半導体装置であって、

半導体基板上に形成される第1の絶縁層と、

前記第1の容量素子の一方の電極として、前記第1の絶縁層上に形成された複数の金属層からなる第1の積層金属層と、

前記第1の積層金属層上に形成された高誘電体層と、

前記第1の容量素子の他方の電極として、前記高誘電体層上に形成された複数の金属層からなる第2の積層金属層と、

前記第2の容量素子の一方の電極として、前記第1の絶縁層上に形成された複数の金属層からなる第3の積層金属層と、

前記第1の積層金属層上に形成された第2の絶縁層と、

前記第2の容量素子の他方の電極として、前記第2の絶縁層上に形成された複数の金属層からなる第4の積層金属層と、

前記第1の絶縁層上に形成された複数の金属層からなる第5および第6の積層金属層と

前記第1の絶縁層上に、前記第5の積層金属層と前記第6の積層金属層との間に形成された第1の金属材料からなる抵抗体とを備え、

前記第1、第3、第5および第6の積層金属層は、同じ材料でかつ同じ層に島状に形成され、前記第5の積層金属層は前記抵抗体の一端に接し、前記第6の積層金属層は前記抵抗体の他端と接している

ことを特徴とする半導体装置。

#### 【請求項2】

前記第1、第3、第5および第6の積層金属層は、最上の金属層がPtからなることを特徴とする請求項1に記載の半導体装置。

### 【請求項3】

前記第1、第3、第5および第6の積層金属層は、最下の金属層がTiからなることを特徴とする請求項1に記載の半導体装置。

## 【請求項4】

前記第1、第3、第5および第6の積層金属層は、最上の金属層および最下の金属層の間にA1からなる中間の金属層を含む

ことを特徴とする請求項2に記載の半導体装置。

#### 【請求項5】

前記第1、第3、第5および第6の積層金属層は、さらに、前記中間の金属層と最上の金属層との間にTiからなる金属層を含む

ことを特徴とする請求項3に記載の半導体装置。

### 【請求項6】

前記半導体装置は、さらに、トランジスタ素子を備え、

前記トランジスタ素子は、前記第1の絶縁層を除去された領域における前記半導体基板上に形成された第3の絶縁層と、

前記第3の絶縁層を貫通し、前記トランジスタ素子の電極として形成された複数の金属層からなる第7の積層金属層とを有し、

前記第7の積層金属層は、前記第4の積層金属層と同じ材料で形成されることを特徴とする請求項1に記載の半導体装置。

#### 【請求項7】

前記第3の絶縁層は、前記第7の積層金属層の貫通する部分に形成された前記第4の絶縁層を有し、

前記第4の絶縁層は、前記第2の絶縁層と同じ材料でかつ同じ層で形成されることを特徴とする請求項6に記載の半導体装置。

## 【請求項8】

50

10

20

30

前記半導体素子は、閾値電圧の異なる2つの電界効果トランジスタを含むことを特徴とする請求項6に記載の半導体装置。

#### 【請求項9】

前記半導体基板はGaAsまたはInPで構成されることを特徴とする請求項1に記載の半導体装置。

### 【請求項10】

前記第1の絶縁層はSiOっで構成される

ことを特徴とする請求項1に記載の半導体装置。

#### 【 請 求 項 1 1 】

前記高誘電体層がSrTiO₃に代表されるペロブスカイト構造の高誘電体酸化物で構成される

ことを特徴とする請求項1に記載の半導体装置。

#### 【請求項12】

前記第2の絶縁層はSiNで構成される

ことを特徴とする請求項1に記載の半導体装置。

#### 【請求項13】

前記第3の絶縁層材料がSiN、SiO<sub>2</sub>、またはSiNとSiO<sub>2</sub>の積層により構成される

ことを特徴とする請求項6に記載の半導体装置。

# 【請求項14】

前記第2の積層金属層は、Pt、WSi、またはWSiNを含み構成されることを特徴とする請求項1に記載の半導体装置。

### 【請求項15】

前記第1の金属材料からなる抵抗体は、WSiN、WSi、またはWを含み構成されることを特徴とする請求項1に記載の半導体装置。

# 【請求項16】

前記第4の積層金属層は、半導体基板側よりTi、Al、Ti、またはWSi、Al、Ti、またはWSiN、Ti、Al、Ti、またはW、Ti、Al、Tiに積層される金属層からなる

ことを特徴とする請求項1に記載の半導体装置。

### 【請求項17】

請求項1に記載の半導体装置の製造方法であって、

半導体基板上に第1の絶縁層を形成する第1の工程と、

前記第1、第3、第5および第6の積層金属層を形成する第2の工程と、

前記第1の積層金属層上に高誘電体層を形成する第3の工程と、

前記高誘電体層上に第2の積層金属層を形成する第4の工程と、

前記第1の絶縁層上で、かつ前記第5の積層金属層と前記第6の積層金属層との間に、前記第5の積層金属層と前記第6の積層金属層と接するように第1の金属材料からなる抵抗体を形成する第5の工程と、

前記第3の積層金属層上に前記第2の絶縁層を形成する第6の工程と、

前記第2の絶縁層上に前記第4の積層金属層を形成する第7の工程と

#### を備える

ことを特徴とする半導体装置の製造方法。

# 【請求項18】

前記半導体装置は、前記第5の工程と前記第6の工程の間に、さらに、前記第1、第2、第3、第5および第6の積層金属層上に第4の絶縁層を形成する絶縁層形成工程と、前記第4の絶縁層に前記第1、第2、第3、第5および第6の積層金属層に達する開口

それぞれを同時に形成する開口工程と

### を含む

ことを特徴とする請求項17に記載の半導体装置の製造方法。

10

20

30

---

40

#### 【請求項19】

前記半導体装置は、さらに、トランジスタ素子を備え、

前記トランジスタ素子は、前記第1の絶縁層を除去された領域における前記半導体基板上に形成された第3の絶縁層と、

前記第3の絶縁層を貫通し、前記トランジスタ素子の電極として形成された複数の金属層からなる第7の積層金属層とを有し、

前記第7の積層金属層は、前記第4の積層金属層と同じ材料でかつ同じ層で形成されることを特徴とする請求項1に記載の半導体装置であって、

前記半導体装置の製造方法は、前記第5の工程と前記第6の工程の間に、さらに、前記第1の絶縁層の一部を除去する工程と、

前記第1絶縁層が除去された半導体基板上に前記第3の絶縁層と、前記第1、第2、第3、第5および第6の積層金属層上に前記第4の絶縁層とを同時に同材料で形成する絶縁層形成工程と、

前記第3の絶縁層を開口する工程を含む前記開口工程と、

前記第3の絶縁層の開口に前記第4の積層金属層を形成する工程を含む前記第7の工程と

を備えることを特徴とする請求項17に記載の半導体装置の製造方法。

## 【請求項20】

前記第6の工程において、さらに、前記第3の絶縁層の開口の側壁にも前記第2の絶縁層を形成する

ことを特徴とする請求項18に記載の半導体装置の製造方法。

【発明の詳細な説明】

### 【技術分野】

#### [ 0 0 0 1 ]

本発明は、半導体装置とその製造方法に関し、特に、ペロブスカイト構造の高誘電体酸化物による容量素子と窒化物による容量素子と高抵抗金属材料による抵抗素子とを同一化合物半導体基板上に集積化した半導体装置およびその製造方法に関する。

#### 【背景技術】

# [0002]

G a A s よりなる半絶縁性の半導体基板上に形成される電界効果型トランジスタ(以下、G a A s F E T と称する。)は、その優れた性能により、通信機器とりわけ携帯電話端末等のパワーアンプおよびスイッチ等に利用されている。この G a A s F E T 等の能動素子と、抵抗素子及び容量素子等の受動素子とを集積化したモノリシックマイクロ波集積回路(以下、G a A s M M I C と記載。)は特に広く実用化されている。近年では、G a A s よりなる半絶縁性の半導体基板上にトランジスタ等の能動素子を形成せず、容量素子や抵抗素子等の受動素子のみを集積した集積受動素子(以下、G a A s I P D と記載。)に対する需要も高まってきている。

# [0003]

G a A s M M I C において、直流成分のカットやグランドラインへのバイパスコンデンサ用に大容量の容量素子が必要とされている。しかしながら、大容量の容量素子を形成するには大きな面積が必要となり、チップ面積の 5 0 % 近くを容量素子が占めてしまう場合がある。

## [0004]

そこで、チップ面積低減のためにSrTi〇 $_3$ に代表されるペロブスカイト構造の高誘電体酸化物による大容量の容量素子(以下、STO容量と記載。)を搭載したGaAsMMICが知られている。これらペロブスカイト構造の高誘電体酸化物は、従来用いられてきたSi〇 $_2$ (酸化シリコン)やSiN(窒化シリコン)等に比べて比誘電率が10倍以上高く、容量素子の面積を10分の1以下に出来るメリットがある。そのため、ペロブスカイト構造の高誘電体酸化物は大容量の容量素子の材料として望ましい。

# [0005]

10

20

30

40

また、GaAsMMICでは、直流成分のカットやバイパスコンデンサに用いる大容量の容量素子のほかに、整合回路に用いる高精度で小容量の容量素子が必要とされている。このような容量素子は容量が数pFで容量の精度が5%以内のものである。高誘電体材料を用いた容量素子は高誘電率を有するために、高精度で小容量の容量素子を形成することは困難である。このため、GaAsMMICには高誘電体材料を用いた大容量の容量素子と精度が高く小容量の容量素子とを共存させて形成されることが望ましい。GaAsIPDにおいても同様のことが言える。

### [0006]

また、GaAs等の化合物半導体よりなる半導体装置の抵抗体には、抵抗としての必要な特性である線形性および高周波における安定性を実現するため、WSiNのようなW系からなる高抵抗金属膜が抵抗素子の抵抗体として使用されている。

[0007]

前述のGaAsMMICならびにGaAsIPDにおいては、近年、さらなる低コスト化が求められている。特にプロセス技術にはGaAsMMICやGaAsIPDとしての素子の性能を落とすことなくプロセス工程の簡素化を行い、プロセスコストの低減を実現することが強く要望されている。

[00008]

なお、このような要望に対応する技術としては、例えば、特許文献 1、 2 に記載のものがある。特許文献 1 は、高誘電体材料を用いた大容量の容量素子と、S i O  $_2$  または S i N を用いた小容量の容量素子があり、それぞれの下部電極は T i、 A u、 P t を順に積層した積層金属(以下、T i / A u / P t と記載)からなる電極としている。そして、下部電極をイオンミリング法により形成することで、上述の 2 種類の容量の下部電極の共用化を図っている。

[0009]

また、特許文献 2 は、W S i N を用いた抵抗体に層間絶縁膜 S i O 2 とのエッチング選択性を確保するために、抵抗体上部のコンタクト穴を形成する領域にエッチング選択性のある A u を堆積することで、エッチング停止膜として利用している。

【特許文献 1 】特開平 8 - 3 4 0 0 8 3 号公報

【特許文献2】特開平5-82519号公報

【発明の開示】

【発明が解決しようとする課題】

[0010]

しかしながら、上記特許文献1に記載の半導体装置は、下部電極の上部に貴金属であるAuが堆積されている。Auは化学反応機構のドライエッチング(以下、化学反応性ドライエッチングと記載。)による加工が難しい。そのため、Auを堆積した下部電極を加するのに、例えば、下部電極以外の領域をフォトレジストで保護しArによる物理的な機構のイオンミリング工程を実施した後に、フォトレジストを除去する工程を追加する必要があり、プロセス工数が増加してしまう。また、上記特許文献2に記載の半導体装置では、W系抵抗素子に直接コンタクトする。そのため、W系抵抗素子上部に堆積された絶縁にコンタクト穴をエッチングにより形成する必要があるが、W系抵抗素子がエッチングにより形成する必要があるため、プロセスれてしまわないように、必ずAuによる保護領域を形成する必要があるため、プロセスなが増加しプロセスコストが増加してしまう。W系抵抗素子にAuによる保護領域を設けない場合には、W系抵抗素子がエッチングにより削れてしまい、素子としての特性を損ねてしまう。

[0011]

そこで、本発明は、上記課題を解決するためになされたもので、素子の特性を損ねることなく、プロセスコストの低減を可能とする半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

[0012]

10

20

30

第1および第2の容量素子と抵抗素子とを備える半導体装置であって、半導体基板上に形成される第1の絶縁層と、前記第1の容量素子の一方の電極として、前記第1の海層金属層と、前記第1の積層金属層と、前記第1の積層金属層と、前記第1の容量素子の他方の電極として、前記第1の容量素子の他方の電極として、前記第2の容量素子の他方の電極として、前記第2の容量素子の積層金属層と、前記第2の容量素子の他方の電極とに形成された複数の金属層からなる第3の積層金属層と、前記第2の絶縁層上に形成された複数の金属層からなる第4の積層金属層と、前記第1の絶縁層上に形成された複数の金属層からなる第4の積層金属層と、前記第1の絶縁層上に、前記第5の積層金属層と前記第1の金属材料からなる抵抗体とを備え、前記第5の積層金属層は前記抵抗体の他端と接していることを備える。

[0013]

この構成によれば、誘電率の異なる容量素子ならびに抵抗素子を集積化する際、容量素子の片方の電極である第1の積層金属層と第3の積層金属層と抵抗素子を容量素子の電極とを接続する金属である第5および第6の積層金属層を同一の材料で同時に形成できるので、プロセス工数の抑制ができる。また、抵抗素子が第5、第6の積層金属層と接続されていることにより、抵抗素子とのコンタクトを形成する場合には、抵抗素子が接続されている第5、第6の積層金属層とコンタクトを形成すればよく、素子の特性を損ねないばかりか、抵抗素子に保護膜を形成するなどの余計な工程が付加されない分だけ、プロセス工数が低減される。例えば、抵抗素子上に形成された絶縁膜があり、抵抗素子上部の絶縁膜にエッチングによりコンタクト穴を形成し、抵抗素子とコンタクトを形成する場合には、抵抗素子も一部エッチングされてしまい、抵抗素子の特性を損ねてしまうというようなこともなくなる。

[0014]

また、前記第1、第3、第5および第6の積層金属層は、最上の金属層がPtからなることを備えてもよい。

[0015]

この構成によれば、第1の積層金属層と第4の積層金属層と抵抗素子を接続する金属である第5および第6の積層金属層を化学反応性のドライエッチングにより選択的に加工することが可能となるので、物理的なエッチングしかできず、物理的なエッチング対象以外を保護するプロセスを増やす必要のあった従来技術と比べてプロセス工数の抑制ができる。また、Ptを厚くすることで、容量素子の電極の低抵抗化も図れる。また、例えば、第1の積層金属層と第4の積層金属層と抵抗素子を接続する金属である第5および第6の積層金属層上に絶縁層を形成し、これらの積層金属層上部の絶縁層の開口を形成する場合には、ドライエッチングに用いる反応ガスを選択することにより、Ptがエッチング停止膜としての役割を果たすこともできるので、エッチング停止膜としてAuを付加するのが不要となり、プロセス工数の抑制が可能となる。

[0016]

また、前記第 1 、第 3 、第 5 および第 6 の積層金属層は、最下の金属層が T i からなっていても良い。

[0017]

この構成によれば、絶縁層と密着性のよい材料から積層金属層が形成できる。

また、前記第1、第3、第5および第6の積層金属層は、最上の金属層および最下の金属層の間にA1からなる中間の金属層を含んでもよい。

[0018]

この構成によれば、Alを用いることにより積層金属層の低抵抗化が可能になる。また、AlはCl $_2$ で容易に化学反応性ドライエッチングが可能であるので、積層金属層のドライエッチングの高速化が可能となる。

10

20

30

40

#### [0019]

また、前記第1、第3、第5および第6の積層金属層は、さらに、前記中間の金属層と 最上の金属層との間にTiからなる金属層を含んでもよい。

#### [0020]

この構成によれば、Tiを用いることにより中間の金属層と最上の金属層との密着性が向上する。

#### [0021]

また、前記半導体装置は、さらに、トランジスタ素子を備え、前記トランジスタ素子は、前記第1の絶縁層を除去された領域における前記半導体基板上に形成された第3の絶縁層と、前記第3の絶縁層を貫通し、前記トランジスタ素子の電極として形成された複数の金属層からなる第7の積層金属層とを有し、前記第7の積層金属層は、前記第4の積層金属層と同じ材料で形成されていてもよい。

#### [0022]

この構成によれば、半導体素子の電極と第4の積層金属層と同一の材料で同時に形成することができる。それにより、半導体素子と、第1の積層金属層と第3の積層金属層で挟まれる高誘電体からなる第1の容量素子と、第3の積層金属層と第4の積層金属層で挟まれる第2の絶縁体からなる第2の容量素子と、抵抗素子とを低コストで集積化することができる。

### [0023]

また、前記第3の絶縁層は、前記第7の積層金属層の貫通する部分に形成された前記第4の絶縁層を有し、前記第4の絶縁層は、前記第2の絶縁層と同じ材料でかつ同じ層で形成されてもよい。このとき、前記半導体素子は、閾値電圧の異なる2つの電界効果トランジスタを含んでいてもよい。

#### [0024]

この構成によれば、前記第3の絶縁層の開口部に電界効果トランジスタのソース電極、ドレイン電極、ゲート電極が形成されている場合、第3の絶縁層の開口部の側壁に第4の絶縁層が形成されることで、ゲート電極と半導体基板との接触面積が縮小されて短ゲート長化が実現される。また、第3の絶縁層の開口部の側壁に第4の絶縁層が形成されることで、ゲート電極とソース電極ならびにドレイン電極との距離が拡大されて電界効果トランジスタの高耐圧化が実現される。

### [0025]

また、本発明に関わる半導体装置の製造方法は、請求項1に記載の半導体装置の製造方法であって、半導体基板上に第1の絶縁層を形成する第1の工程と、前記第1、第3、第5および第6の積層金属層を形成する第2の工程と、前記第1の積層金属層上に高誘電体層を形成する第3の工程と、前記高誘電体層上に第2の積層金属層を形成する第4の工程と、前記第1の絶縁層上で、かつ前記第5の積層金属層と前記第6の積層金属層との間に、前記第5の積層金属層と前記第6の積層金属層と接するように第1の金属材料からなる抵抗体を形成する第5の工程と、前記第3の積層金属層上に前記第2の絶縁層を形成する第6の工程と、前記第2の絶縁層上に前記第4の積層金属層を形成する第7の工程とを備えることを特徴とする。

# [0026]

この構成によれば、第1の容量素子と、第2の容量素子との下部電極である第1および第3の積層金属層を同一材料で同時に形成でき、プロセスコストの抑制が可能になる。また、抵抗素子が第5、第6の積層金属層と接続されて形成されていることにより、抵抗素子とのコンタクトを形成する場合には、抵抗素子が接続されている第5、第6の積層金属層とコンタクトを形成すればよく、素子の特性を損ねないばかりか、抵抗素子に保護膜を形成するなどの余計な工程が付加されない分だけ、プロセス工数が低減される。例えば、抵抗素子上に形成された絶縁膜があり、抵抗素子上部の絶縁膜にエッチングによりコンタクト穴を形成し、抵抗素子とコンタクトを形成する場合には、抵抗素子も一部エッチングされてしまい、抵抗素子の特性を損ねてしまうというようなこともなくなる。

10

20

30

40

### [0027]

また、前記半導体装置の製造方法は、さらに、前記半導体装置は、前記第5の工程と前記第6の工程の間に、さらに、前記第1、第2、第3、第5および第6の積層金属層上に第4の絶縁層を形成する絶縁層形成工程と、前記第4の絶縁層に前記第1、第2、第3、第5および第6の積層金属層に達する開口それぞれを同時に形成する開口工程とを含んでもよい。

### [0028]

これによれば、第 1 、第 2 、第 3 、第 5 および第 6 の積層金属層に達する開口それぞれを同時にエッチングにより形成できるので、プロセスコストを低減することが出来る。

## [0029]

また、前記半導体装置は、さらに、トランジスタ素子を備え、前記トランジスタ素子は、前記第1の絶縁層を除去された領域における前記半導体基板上に形成された第3の絶縁層と、前記第3の絶縁層を貫通し、前記トランジスタ素子の電極として形成された複数の金属層からなる第7の積層金属層とを有し、前記第7の積層金属層は、前記第4の積層金属層と同じ材料でかつ同じ層で形成されることを特徴とする請求項第1に記載の半導体装置であって、前記半導体装置の製造方法は、前記第5の工程と前記第6の工程の間に、ちに、前記第1の絶縁層の一部を除去する工程と、前記第1絶縁層が除去された半導体基板上に前記第3の絶縁層の一部を除去する工程と、前記第1絶縁層が除去された半導体基板上に前記第3の絶縁層と、前記第1、第2、第3、第5および第6の積層金属層を開口する工程を含む前記開口工程と、前記第3の絶縁層の開口に前記第4の積層金属層を形成する工程を含む前記第7の工程とを備えてもよい。

#### [ 0 0 3 0 ]

これによれば、第1の容量素子と第2の容量素子と抵抗素子とに加えて、トランジスタ素子の同一半導体基板上で形成する際、第1の容量素子と第2の容量素子と抵抗素子との形成する途中の工程の一部とトランジスタ素子を形成する途中の工程の一部とを同一プロセスで形成できる。そのため、2種類の容量素子と抵抗素子と電界効果トランジスタの集積化のプロセスコストを低減し実現出来る。

#### [0031]

また、前記第6の工程において、さらに、前記第3の絶縁層の開口の側壁にも前記第2 の絶縁層を形成してもよい。

### [0032]

これによれば、前記第3の絶縁層の開口部に電界効果トランジスタのソース電極、ドレイン電極、ゲート電極が形成されている場合、第3の絶縁層の開口部の側壁に第4の絶縁層が形成されることで、ゲート電極と半導体基板との接触面積が縮小されて短ゲート長化が実現される。また、第3の絶縁層の開口部の側壁に第4の絶縁層が形成されることで、ゲート電極とソース電極ならびにドレイン電極との距離が拡大されてトランジスタ素子の高耐圧化が実現される。

### 【発明の効果】

## [0033]

本発明によれば、素子の特性を損ねることなく、プロセスコストの低減を可能とする半導体装置およびその製造方法を実現することができる。よって、本発明により、携帯電話端末等のパワーアンプおよびスイッチ等の通信機器として低コスト化されたGaAsIPDやGaAsMMICを実現することができ、実用的価値は極めて高い。

# 【発明を実施するための最良の形態】

#### [0034]

以下、本発明の実施の形態における半導体装置について、図面を参照しながら説明する

# [0035]

#### (第1の実施の形態)

本発明の第1の実施の形態に係る半導体装置は、高誘電体容量素子と窒化物容量素子と

10

20

30

30

40

金属抵抗素子とを集積化した、例えば G a A s I P D であり、高誘電体容量素子の下部電極と窒化物容量素子の下部電極と金属抵抗素子の下部電極とをエッチング停止膜を兼ねる材料で同時形成する。これにより、各素子の特性を損ねることなく、プロセス工数を抑制でき、プロセスコストの低減が実現できる。

# [0036]

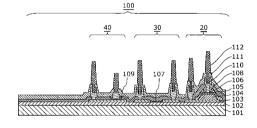

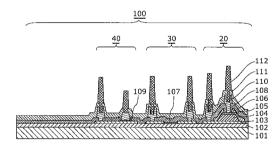

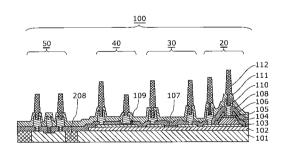

図1は、本発明の第1の実施の形態に係る半導体装置の構成を示す断面図である。 図1に示す半導体装置100は、GaAsからなる半絶縁性の半導体基板101上に、SiO2からなる絶縁層102が形成され、絶縁層102上には、高誘電体容量素子部20と、抵抗素子部30と、窒化物容量素子部40とが形成されている。

#### [0037]

高誘電体素子部20には、絶縁層102上に、下部電極となる積層金属層103と、容量層となるSrTi0₃からなる高誘電体層104と、上部電極となる金属材料層105とが順に形成されている。さらに、容量層となるSrTi0₃からなる高誘電体層104および上部電極となる金属材料層105を保護する絶縁層106が形成されている。抵抗素子部30には、Si0₂からなる絶縁層102上の積層金属層103の間に、すわなち、積層金属層103の形成されていない領域(以下、コンタクト形成領域と記載。)に抵抗体として金属材料層107が形成されている。このとき、抵抗体である金属材料層107は、積層金属層103と接するように形成されている。窒化物容量素子部40には、絶縁層102上に、下部電極となる積層金属層103と、容量層となるSiNからなる絶縁層109と、上部電極となる積層金属層100とが形成されている。半導体装置100は、さらに、高誘電体容量素子部20と抵抗素子部30と章化物容量素子部40とを保護する絶縁層111と、上層配線となる金属材料層112とが順に形成されている。

# [0038]

ここで、高誘電体素子部 2 0 と窒化物容量素子部 4 0 とで下部電極となる積層金属層 1 0 3 は、半導体装置 1 0 0 において下層配線となっており、窒化物容量素子部 4 0 で上部電極となる積層金属層 1 1 0 は半導体装置 1 0 0 において中層配線となっている。

#### [0039]

# [0040]

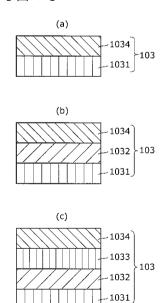

図2は、本発明の第1の実施の形態に係る半導体装置の下層配線の構造を示す模式的な断面図である。

# [0041]

10

20

30

40

10

20

30

40

50

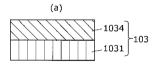

容易に化学反応性ドライエッチングが可能なAlが使用されており、Alを利用することによりドライエッチングの高速化と、材料コストの低減とが可能となっている。さらに、図2(c)に示すように、Alからなる低抵抗金属層1032とPtからなる最上金属層1034の間にTiからなる金属層1033を挿入しTi/Al/Ti/Pt層からなる積層金属層103を形成してもよい。それにより、Alからなる低抵抗金属層1032とPtからなる最上金属層1034との密着性を向上させることが可能となる。

[0042]

次に、以上のような構造を有する半導体装置の製造方法について詳細に説明する。なお、図1と同一の要素には同一の符号が付されており、それらに関する詳しい説明はここでは省略する。

[0043]

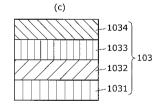

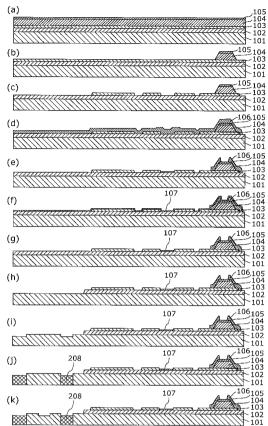

図3は、上記構造を有する半導体装置の製造方法を説明するための断面図である。

[0044]

(1)まず、図3(a)に示すように、GaAsからなる半絶縁性の半導体基板101上にP‐CVD法によりSiO $_2$ からなる絶縁層102を、DCスパッタ法によりTi/A1/Ti/Pt層からなる積層金属層103を、 $О_2$ ガスを用いたRFスパッタ法によりSrTi $O_3$ からなる高誘電体層104を、DCスパッタ法によりPtからなる金属材料層105を順次堆積させる。

[0045]

(2)次に、図3(b)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、 $C1_2/Ar$ ガスを用いた化学反応性ドライエッチングによりPtからなる金属材料層105と $SrTiO_3$ からなる高誘電体層104とをエッチングする。これにより、高誘電体容量素子部20の金属材料層105からなる上部電極と高誘電体層104からなる容量層が形成される。

[0046]

(3)次に、図3(c)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、Cl<sub>2</sub>/Arガスを用いた化学反応性ドライエッチングによりTi/Al/Ti/Pt層からなる積層金属層103をエッチングする。これにより、高誘電体容量素子部20と窒化物容量素子部40との積層金属層103からなる下部電極と、抵抗素子部30の積層金属層103がない領域からなるコンタクト形成領域と、半導体装置100の積層金属層103からなる下層配線とが形成される。

[0047]

(4)次に、図3(d)に示すように、P-CVD法によりSiO $_2$ からなる絶縁層106を堆積させる。

[ 0 0 4 8 ]

(5)次に、図3(e)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、希ふっ酸を用いたウェットエッチングにより高誘電体容量素子部20の側壁以外のSiO<sub>2</sub>からなる絶縁層106を除去することで、高誘電体容量素子部20と窒化物容量素子部40との積層金属層103からなる下部電極と、抵抗素子部30の積層金属層103がない領域からなるコンタクト形成領域とを露出させる。

[0049]

( 6 ) 次に、図 3 ( f ) に示すように、D C スパッタ法によりW S i N からなる金属材料層 1 0 7 を堆積させる。

[0050]

(7)次に、図3(g)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、C1<sub>2</sub>/O<sub>2</sub>ガスを用いた化学反応性ドライエッチングにより、積層金属層103がない領域からなるコンタクト領域をつなぐ抵抗体としてWSiNからなる金属材料層107を形成する。これにより、抵抗素子部30の抵抗体が形成される。

[0051]

(8)次に、図3(h)に示すように、P-CVD法により $SiN/SiO_2$ からなる

絶縁体108を積層させる。

[0052]

(9)次に、図3(i)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、CHF3/SF6ガスを用いた化学反応性ドライエッチングにより、高誘電体容量素子部20の上部電極および下部電極と、抵抗素子部30の積層金属層103と、窒化物容量素子部40の下部電極とのコンタクト用開口部を露出させる。

[0053]

ここで、積層金属層103は、絶縁層108をエッチングする際に、Ptからなる積層 金属層103の最上層1034がエッチング停止層として機能する。

[0.054]

( 1 0 ) 次に、図 3 ( j ) に示すように、P - C V D 法により窒化物容量素子部 4 0 の容量層となる S i N からなる絶縁層 1 0 9 を堆積させる。

[0055]

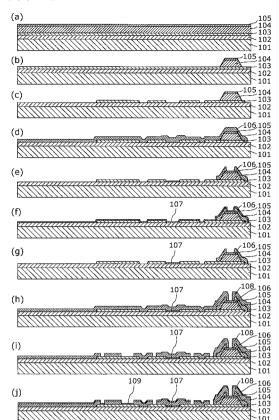

(11)次に、図4(k)に示すように、フォトリソグラフィーにより所定の領域をパタ・ンニングし、CHF<sub>3</sub>/SF<sub>6</sub>ガスを用いた化学反応性ドライエッチングにより、窒化物容量素子部40の領域を残してSiNからなる絶縁層109を除去する。

[0056]

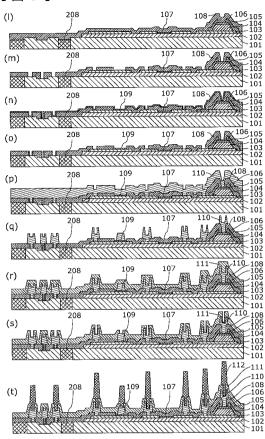

(12)次に、図4(l)に示すように、蒸着法によりTi/Al/Ti層からなる積層金属層110を蒸着する。

[0057]

なお、ここでは金属材料層110はTi/A1/Tiから構成しているが、例えば、W SiN/Ti/A1/TiからもしくはW/Ti/A1/Tiから構成しても良い。

[0058]

(13)次に、図4(m)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、C $1_2$ /BС $1_3$ ガスを用いた化学反応性ドライエッチングにより窒化物容量素子部40の上部電極ならびに半導体装置100の中層配線となる積層金属層110を形成する。

[0059]

(14)次に、図4(n)に示すように、P-CVD法によりSiNからなる絶縁層111を堆積する。

[0060]

(15)次に、図4(o)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、CHF<sub>3</sub>/SF<sub>6</sub>ガスを用いた化学反応性ドライエッチングに窒化物容量素子部40の上部電極ならびに半導体装置100の中層配線となる積層金属層110へのコンタクト用開口部を形成する。

[0061]

(16)次に、図4(p)に示すように、コンタクト用開口部付近に選択的にAuメッキを形成することで半導体装置100の上層配線となる金属材料層112が形成される。

[0062]

以上のように、本発明の第1の実施の形態の半導体装置及びその製造方法によれば、抵抗素子部30のPtからなる最上層1034を有する積層金属層103上の絶縁層108をCF4系のガスを用いて化学反応性ドライエッチングする。抵抗素子部30のコンタクト用開口部を形成する際、Ptからなる最上層1034を有する積層金属層103がエッチング停止層として機能する。そのため、WSiN等のW系で形成された抵抗体上にAu系のエッチング停止膜を形成する必要がないため、プロセス工数を抑制することが可能となる。すなわち、プロセスコストの低減が可能となる。

[0063]

また、高誘電体容量素子部20と窒化物容量素子部40との下部電極と、エッチング停止膜を兼ねた金属抵抗素子の下部電極とが積層金属層103により同一材料で共用されるので、プロセス工数を抑制することが可能となる。すなわち、プロセスコストの低減が可

10

20

30

40

能となる。

### [0064]

よって、本発明の第1の実施の形態の半導体装置及びその製造方法によれば、高誘電体容量素子と窒化物容量素子とを集積化することができるので、バイパスコンデンサ等に用いられる大容量の容量素子と整合回路等に用いられる高精度で小容量の容量素子とを集積化した半導体装置を実現することが出来る。

#### [0065]

(第2の実施の形態)

本発明の第2の実施の形態に係る半導体装置は、GaAsFETと、高誘電体容量素子と窒化物容量素子と金属抵抗素子とを集積化した、例えばGaAsMMICであり、高誘電体容量素子の下部電極と窒化物容量素子の下部電極と、金属抵抗素子の下部電極とが、エッチング停止膜を兼ねる同材料で同時形成され、GaAsFETのゲート電極およびソース電極、ドレイン電極と窒化物容量素子の上部電極とが同材料で同時形成される。これにより、各素子の特性を損ねることなく、プロセス工数を抑制でき、プロセスコストの低減が実現できる。

#### [0066]

以下、本発明の第2の実施の形態に関わる半導体装置の構成について図を用いて説明する。

#### [0067]

図 5 は、本発明の第 2 の実施の形態に係る半導体装置の構成を示す断面図である。ここでは、図 1 と同一の要素には同一の符号が付されている。

#### [0068]

図 6 に示す半導体装置 1 0 0 は、 G a A s からなる半絶縁性の半導体基板 1 0 1 上に高誘電体容量素子 2 0 と抵抗素子部 3 0 と窒化物容量素子部 4 0 と電界効果トランジスタ部 5 0 とが形成されている。

### [0069]

高誘電体素子部 2 0 には、G a A s からなる半絶縁性の半導体基板 1 0 1 上に、S i O  $_2$  からなる絶縁層 1 0 2 と、下部電極となる積層金属層 1 0 3 と、容量層となる S r T i O  $_3$  からなる高誘電体層 1 0 4 と、上部電極となる金属材料層 1 0 5 とが順に形成されている。さらに、S r T i O  $_3$  からなる高誘電体層 1 0 4 の容量層および金属材料層 1 0 5 の上部電極を保護する絶縁層 1 0 6 が形成されている。

# [0070]

抵抗素子部30には、GaAsからなる半絶縁性の半導体基板101上に、例えば、S i0₂からなる絶縁層102が形成されており、高誘電素子部20および窒化物容量素子 4 0 で下部電極となる積層金属層 1 0 3 とその間、すなわち、下部電極をつなぐ抵抗体と して、積層金属層103の上部と側壁に両端が接するように抵抗素子部30の領域の積層 金属層103の形成されていない領域(以下、コンタクト形成領域と記載。)に抵抗体と なる金属材料107が形成されている。窒化物容量素子部40には、GaAsからなる半 絶縁性の半導体基板101上に、例えば、Si0ゥからなる絶縁層102と、下部電極と なる 積 層 金 属 層 1 0 3 と 、 容 量 層 と な る S i N か ら な る 絶 縁 層 1 0 9 と 、 上 部 電 極 と な る 積層金属層110とが形成されている。電界効果トランジスタ50は、半導体基板101 上に、Si0っからなる絶縁膜108が形成され、形成された絶縁膜108の開口部にゲ ート電極およびソース電極およびドレイン電極となる積層金属層110が形成されている 。ゲート電極およびソース電極およびドレイン電極の側壁にはサイドウォールとなる絶縁 層109が形成されている。また、基板101は、チャネル層とチャネル層上に形成され た電子供給層と電子供給層に形成されたショットキー層を有している。さらに、電界効果 トランジスタ 5 0 における基板 1 0 1 には、他の素子と電気的に絶縁するための素子分離 領域208が形成されている。

### [0071]

半導体装置100は、さらに、高誘電体容量素子部20と抵抗素子部30と積層金属層

10

20

30

40

10

20

30

40

50

103とを保護する絶縁層108と、高誘電体容量層素子部20と抵抗素子部30と窒化物容量素子部40と電界効果トランジスタ部50とを保護する絶縁層111と、上層配線となる金属材料層112とが形成されている。

### [0072]

ここで、高誘電体素子部 2 0 と窒化物容量素子部 4 0 とで下部電極となる積層金属層 1 0 3 は、半導体装置 1 0 0 において下層配線であり、窒化物容量素子部 4 0 で上部電極となる積層金属層 1 1 0 は半導体装置 1 0 0 において中層配線である。

# [0073]

# [0074]

図 6 は、本発明の第 2 の実施の形態に係る半導体装置の下層配線の構造を示す模式的な断面図である。

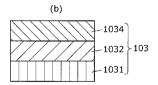

### [0075]

半導体装置100において下層配線である積層金属層103は図6(a)~図6(c) で示すように、2層~4層から構成される。絶縁層102と接触する積層金属層103の 最下金属層1031は、絶縁層102と密着性のよい材料からなり、ここではTiが使用 されている。SrTi0₃からなる高誘電体層104と接触する積層金属層103の最上 金属層1034は、酸化し難く、SrTiO₃の結晶方位を揃えやすい材料からなり、こ こではPtが使用されている。また、Ptはガスを選択することで化学反応性エッチング が可能になる。積層金属層103は図6(a)で示すように、Ti/Ptからなる最下金 属層1031と最上金属層1034の2層のみで構成されても良い。Pt膜厚を厚くし、 化学反応性ドライエッチングにより加工することで低抵抗な下層配線である積層金属層 1 0 3 を形成することが可能である。 T i と P t とのドライエッチングには C 1。を反応性 ガスに用いた化学反応性ドライエッチングを用いる。また、図6(b)で示すように、T iからなる最下金属層 1 0 3 1 と P t からなる最上金属層 1 0 3 4 の間に低抵抗金属から なる低抵抗の金属層1032を形成しても良い。ここでは、C1。で容易に化学反応性ド ライエッチングが可能なA1が使用されており、A1を利用することによりドライエッチ ングの高速化と、材料コストの低減とが可能となっている。さらに、図6(c)に示すよ うに、A1からなる低抵抗の金属層1032とPtからなる最上層1034の間にTiか らなる金属層 1 0 3 3 を挿入しTi/A1/Ti/Pt層からなる積層金属層 1 0 3 を形 成してもよい。それにより、A1からなる低抵抗金属層1032とPtからなる最上層1 034との密着性を向上させることが可能となる。

# [0076]

次に、以上のような構造を有する半導体装置の製造方法について詳細に説明する。なお、図 5 と同一の要素には同一の符号が付されており、それらに関する詳しい説明はここでは省略する。

# [ 0 0 7 7 ]

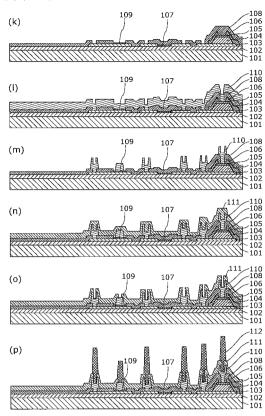

図 7 および図 8 は、上記構造を有する半導体装置の製造方法を説明するための断面図である。

# [0078]

(1)まず、図7(a)に示すように、GaAsからなる半絶縁性の半導体基板101上にP‐CVD法によりSiO $_2$ からなる絶縁層102を、DCスパッタ法によりTi/A1/Ti/Pt層からなる積層金属層103を、 $O_2$ ガスを用いたRFスパッタ法によりSrTi $O_3$ からなる高誘電体層104を、DCスパッタ法によりPtからなる金属材料層105を順次堆積させる。なお、ここで、図示していないが、GaAsからなる半絶縁性の半導体基板101はチャネル層とチャネル層上に形成された電子供給層と電子供給

層に形成されたショットキー層を有している。

### [0079]

(2)次に、図7(b)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、 $C1_2$  / A r ガスを用いた化学反応性ドライエッチングによりS r T i  $O_3$  からなる高誘電体層104と P t からなる金属材料層105とをエッチングする。これにより、高誘電体容量素子部20の高誘電体層104からなる容量層と金属材料層105からなる上部電極とが形成される。

### [0800]

(3)次に、図7(c)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、C1<sub>2</sub> / Arガスを用いた化学反応性ドライエッチングによりTi / Al / Ti / Ptの4層からなる積層金属層103をエッチングする。これにより、高誘電体容量素子部20と窒化物容量素子部40との積層金属層103からなる下部電極と、抵抗素子部30の積層金属層103がない領域からなるコンタクト形成領域と、半導体装置100の積層金属層103からなる下層配線とが形成される。

# [0081]

(4)次に、図7(d)に示すように、P-CVD法によりSiO<sub>2</sub>からなる絶縁層106を堆積させる。

# [0082]

(5)次に、図7(e)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、希ふっ酸を用いたウェットエッチングにより高誘電体容量素子部20の側壁以外のSiO2からなる絶縁層106を除去することで、高誘電体容量素子部20と窒化物容量素子部40の積層金属層103からなる下部電極と、抵抗素子部30の積層金属層103がない領域からなるコンタクト形成領域とを露出させる。

#### [0083]

(6)次に、図7(f)に示すように、DCスパッタ法によりWSiNからなる金属材料層107を堆積させる。

# [0084]

(7)次に、図7(g)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、C $1_2$ /O $_2$ ガスを用いた化学反応性ドライエッチングにより、積層金属層103がない領域からなるコンタクト形成領域に抵抗体としてWSiNからなる金属材料層107を形成する。これにより、抵抗素子部30の抵抗体が形成される。

# [0085]

(8)次に、図7(h)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、希ふっ酸を用いたウェットエッチングにより電界効果トランジスタ部50を形成する領域のSiO2からなる絶縁層102を除去し、半導体基板101の上部の電子供給層を露出させる。

# [0086]

(9)次に、図7(i)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、半導体基板101の上部にある電子供給層を除去する。そして、図9(j)に示すように、電子供給層を除去した半導体基板101の領域にイオン注入することにより電界効果トランジスタ部50と他の素子とを電気的に分離する素子分離領域208を形成する。

## [0087]

(10)次に、図7(k)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、半導体基板101の一部の領域の電子供給層を除去しショットキー層を露出させる。

### [0088]

(11)次に、図8(1)に示すように、P-CVD法によりSiN/SiO $_2$ からなる絶縁層108を堆積させる。

# [0089]

50

10

20

30

(12)次に、図8(m)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、CHF3/SF6ガスを用いた化学反応性ドライエッチングにより、高誘電体容量素子部20の上部電極および下部電極と、抵抗素子部30の積層金属層103と、窒化物容量素子部40の下部電極とのコンタクト用開口部を露出し電界効果トランジスタ部50のゲートとなる領域の半導体基板101のショットキー層と、ソースおよびドレインとなる領域の半導体基板101の電子供給層とを露出する。

[0090]

ここで、積層金属層103は、絶縁層108をエッチングする際に、Ptからなる積層 金属層20の最上層1034がエッチング停止層として機能する。

[0091]

(13)次に、図8(n)に示すように、P-CVD法により窒化物容量素子部40の容量層となるSiNからなる絶縁層109を堆積させる。

[0092]

(14)次に、図8(o)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、 $CHF_3/SF_6$ ガスを用いた化学反応性ドライエッチングにより、窒化物容量素子部40の領域を残してSiNからなる絶縁層109を除去する。このとき、同時に、電界効果トランジスタ部50のゲート電極およびソース電極およびドレイン電極の側壁にサイドウォールとしてSiNからなる絶縁層109を形成している。

[0093]

( 1 5 ) 次に、図 8 ( p ) に示すように、蒸着法によりTi/A1/Ti層からなる積層金属層110を蒸着する。

[0094]

なお、ここでは金属材料層110はTi/A1/Tiから構成しているが、例えば、WSiN/Ti/A1/TiからもしくはW/Ti/A1/Tiから構成しても良い。

[0095]

(16)次に、図8(q)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、 $C1_2$ /BC $1_3$ ガスを用いた化学反応性ドライエッチングにより、窒化物容量素子部40の上部電極と、電界効果トランジスタ部50のゲート電極およびソース電極およびドレイン電極と、半導体装置100において中層配線となる積層金属層110を形成する。

[0096]

(17)次に、図8(r)に示すように、P-CVD法によりSiNからなる絶縁層111を堆積する。

[0097]

(18)次に、図8(s)に示すように、フォトリソグラフィーにより所定の領域をパターンニングし、 $CHF_3/SF_6$ ガスを用いた化学反応性ドライエッチングにより、窒化物容量素子部 40の上部電極ならびに半導体装置 100において中層配線となる積層金属層 110へのコンタクト用開口部を形成する。

[0098]

(19)次に、図8(t)に示すように、コンタクト用開口部付近に選択的にAuメッキを形成することで半導体装置100の上層配線となる金属材料層112が形成される。 【0099】

以上のように、本発明の第2の実施の形態の半導体装置及びその製造方法によれば、抵抗素子部30のPtからなる最上層1034を有する積層金属層103上の絶縁層108をCF<sub>4</sub>系のガスによるドライエッチングし、抵抗素子部30のコンタクト用開口部を形成する際、Ptからなる最上層1034を有する積層金属層103がエッチング停止層として機能する。そのため、WSiN等のW系で形成された抵抗体上にAu系のエッチング停止膜を形成する必要がないため、プロセス工数を抑制することが可能となる。すなわち、プロセスコストの低減が可能となる。

[0100]

20

10

30

40

10

20

30

40

50

また、高誘電体容量素子部20と窒化物容量素子部30との下部電極とエッチング停止膜を兼ねた金属抵抗素子の下部電極とが積層金属層103により同一材料で共用化することができるので、プロセス工数を抑制することが可能となる。すなわち、プロセスコストの低減が可能となる。

# [0101]

また、電界効果トランジスタ部 5 0 のゲート電極およびソース電極およびドレイン電極と、窒化物容量素子部 4 0 の上部電極とがTi/A1/Tiからなる積層金属層110により同一材料で共用化され同時形成できるので、プロセス工数の抑制することが可能になる。すなわち、プロセスコストの低減が可能となる。

## [0102]

さらに、電界効果トランジスタ部 5 0 のゲート電極およびソース電極およびドレイン電極にはサイドウォールとなる絶縁膜 1 0 9 が形成されている。これにより、電界効果トランジスタの短ゲート長化ならびに高耐圧化が可能になり、高性能化が実現される。このとき、電界効果トランジスタ部において形成されるサイドウォールとなる絶縁膜 1 0 9 は窒化物容量素子部 4 0 で形成される容量層となる絶縁膜 1 0 9 と同一材料でかつ同時形成されるので、プロセスコストを増加させることなく実現される。

### [0103]

なお、集積される電界効果トランジスタとして、上述ではMESFET型について説明しているが、MOSFET型でもよいのは言うまでもない。また、例えば、エンハンスメント型とディプレッション型とからなる閾値電圧の異なる電界効果トランジスタを集積しても良い。

### [0104]

以上により、本発明の第2の実施の形態の半導体装置及びその製造方法によれば、電界効果トランジスタと高誘電体容量素子と窒化物容量素子とが集積化されているため、バイパスコンデンサ等に用いられる大容量の容量素子と整合回路等に用いられる高精度で小容量の容量素子とを含んだGaAsMMICを実現することが出来る。

# 【産業上の利用可能性】

#### [0105]

本発明は、半導体装置およびその製造方法に適用でき、特に、半絶縁性のGaAsよりなる半導体基板上に形成される大容量の容量素子と小容量の容量素子と抵抗素子とを集積化させたGaAsIPDや、半絶縁性のGaAsよりなる半導体基板上に形成される電界効果トランジスタと大容量の容量素子と小容量の容量素子と抵抗素子とを集積化させたGaAsMMICに適用できる。また、本発明はGaAsIPDやGaAsMMICを用いる通信機器に適用でき、特に、携帯電話端末等のパワーアンプおよびスイッチ等に適用することが出来る。

## 【図面の簡単な説明】

# [0106]

- 【図1】本発明の第1の実施の形態に係る半導体装置の構成を示す断面図である。

- 【図2】本発明の第1の実施の形態に係る半導体装置の下層配線の構造を示す模式的な断面図である。

【 図 3 】 本 発 明 の 第 1 の 実 施 の 形 態 に 係 る 半 導 体 装 置 の 製 造 方 法 を 説 明 す る た め の 断 面 図

【図4】本発明の第1の実施の形態に係る半導体装置の製造方法を説明するための断面図である。

- 【図5】本発明の第2の実施の形態に関わる半導体装置の構成を示す断面図である。

- 【図 6 】本発明の第 2 の実施の形態に係る半導体装置の下層配線の構造を示す模式的な断面図である。

- 【図7】本発明の第2の実施の形態に関わる半導体装置の製造過程における構成を示す図である。

- 【図8】本発明の第2の実施の形態に関わる半導体装置の製造過程における構成を示す図

# である。

# 【符号の説明】

# [ 0 1 0 7 ]

- 2 0 高誘電体容量素子部

- 3 0 抵抗素子部

- 4 0 窒化物容量素子部

- 50 電界効果トランジスタ部

- 100 半導体装置

- 1 0 1 半導体基板

- 1 0 2 絶縁層

- 1 0 3 積層金属層

- 1031 最下金属層

- 1 0 3 2 金属層

- 1 0 3 3 金属層

- 1 0 3 4 最上金属層

- 1 0 4 高誘電体層

- 1 0 5 金属材料層

- 106 絶縁層

- 1 0 7 金属材料層

- 108 絶縁層

- 1 0 9 絶縁層

- 1 1 0 積層金属層

- 1 1 2 金属材料層

- 208 素子分離領域

# 【図1】

# 【図2】

10

【図3】

【図4】

【図5】

【図6】

# 【図8】