# (19) World Intellectual Property Organization International Bureau

###

# (43) International Publication Date 23 August 2001 (23.08.2001)

#### **PCT**

# (10) International Publication Number WO 01/62056 A1

(51) International Patent Classification<sup>7</sup>:

H05K 7/14

(21) International Application Number: PCT/US01/01650

(22) International Filing Date: 18 January 2001 (18.01.2001)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

09/504,303

15 February 2000 (15.02.2000) US

- (71) Applicant: BITMICRO NETWORKS, INC. [US/US]; 45550 Northport Loop East, Fremont, CA 94538 (US).

- (72) Inventors: PORTMAN, Roland, F.; 3001 Warrenton Court, Pleasanton, CA 94588 (US). GREGORIOS, Edgar, Jhay; 1367 Gentry Lane, Tracy, CA 95376 (US).

- (74) Agents: SAWYER, Joseph, A., Jr. et al.; Sawyer Law Group LLP, P.O. Box 51418, Palo Alto, CA 94303 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report

[Continued on next page]

(54) Title: PRINTED CIRCUIT BOARD ASSEMBLY

(57) Abstract: A printed circuit board assembly (100) wherein the assembly comprises a first plate (104), a second plate (118) attachably coupled to the first plate (104), and at least one printed circuit board (108, 114) sandwiched between the first plate (104) and the second plate (118), the at least one circuit board (108, 114) extending over the entire area of the first and second plates (104, 118). Utilizing an assembly in accordance with the present invention maximizes the available space on each of the circuit boards. By maximizing the available space, more electronic circuitry can be incorporated onto the board. Furthermore, the exterior spacer design (113) together with interior spacer elements (112, 124) firmly secures each circuit board while maintaining a constant separation between each board. This facilitates the ability to stack more circuit boards, while maintaining the mechanical alignment and structural rigidity necessary for the stacking data connectors (109, 116) to function properly should the assembly be subjected to a sudden shock or vibration.

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

1

#### PRINTED CIRCUIT BOARD ASSEMBLY

#### CROSS REFERENCE TO RELATED APPLICATIONS

The present application is related to co-pending application Serial No. (JAS 1458P), entitled "A Removable Visual Indication Structure For a Printed Circuit Board" filed on the same day and assigned to the same Assignee as the present application.

5

10

15

20

25

#### FIELD OF THE INVENTION

The present invention relates generally to computer components and specifically to an improved technique to assemble and stack printed circuit boards.

#### **BACKGROUND OF THE INVENTION**

Computer systems continually require more functionality, more memory and faster operational speeds, and in many cases they need it in smaller physical packages.

Consequently to meet those requirements the packaging density of the Printed Circuit Boards (PCBs) of those computer systems increases accordingly. Additionally, there are many standard industry specifications that place additional dimensional constraints on the size of the PCBs as well as greatly increase tolerance to shock and vibration. Figure 1 shows a conventional PCB assembly 10 comprising a cover plate 12 and a bottom plate 16.

The PCB 14 is mounted in a chassis in between the cover plate 12 and the bottom plate 16.

While this type of conventional configuration is within standard industry requirements, it is not desirable for four reasons. First, it does not maximize the space available on the printed circuit board. The PCB is designed to fit inside the chassis with an air-gap separating the PCB and chassis, thus the usable area of the PCB is reduced. Second, the traditional design does not provide adequate support for PCBs which are subjected to high levels of shock and vibration. This lack of support contributes to an unstable PCB assembly. Third, the lack of adequate support limits the number of PCBs which can be stacked based on their relative instability. Fourth, it does not provide precise separation and alignment between the PCBs when the PCBs are joined together with a stacking data connector. This is of a significant concern since the mechanical stability of the assembly is

2

crucial to maintaining electrical integrity of the stacking data connector.

Accordingly, what is needed is an assembly that deals with each of these concerns. The present invention addresses these needs.

### **SUMMARY OF THE INVENTION**

An improved printed circuit board assembly is disclosed. The printed circuit board assembly comprises a first plate, a second plate attachably coupled to the first plate, and at least one printed circuit board sandwiched between the first plate and the second plate, the at least one printed circuit board extending over the entire area of the first and second plate.

By utilizing an assembly in accordance with the present invention, the available space on each of the plurality of printed circuit boards is maximized. By maximizing the available space, more electronic circuitry can be incorporated onto the board. Furthermore, the exterior spacer design together with interior spacer elements firmly secures each printed circuit board while maintaining a constant separation between each board. This facilitates the ability to stack more printed circuit boards, while maintaining the mechanical alignment and structural rigidity necessary for the stacking data connectors to function properly in the event the assembly is subjected to a sudden shock or vibration.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

Figure 1 is a conventional printed circuit board assembly.

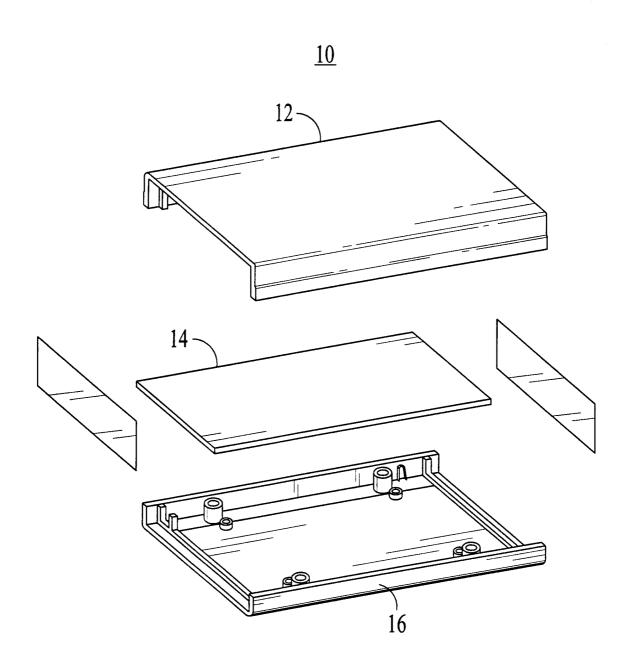

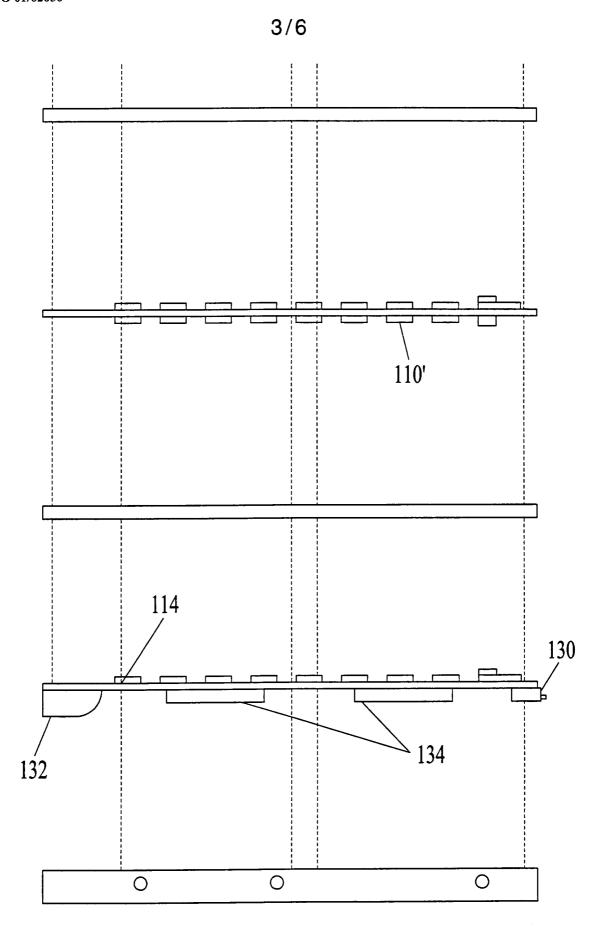

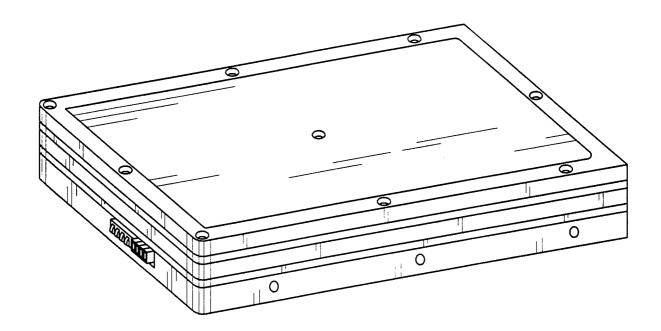

Figure 2 shows a printed circuit board assembly in accordance with the present invention.

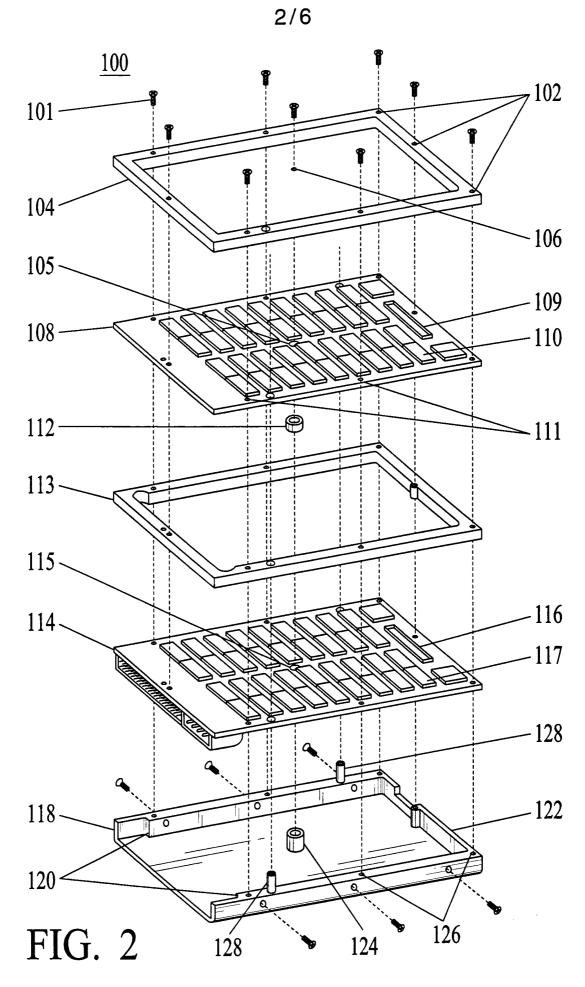

Figure 3 is a side view of the assembly in accordance with the present invention.

Figure 4 is a view of the completely assembled printed circuit board assembly in accordance with the present invention.

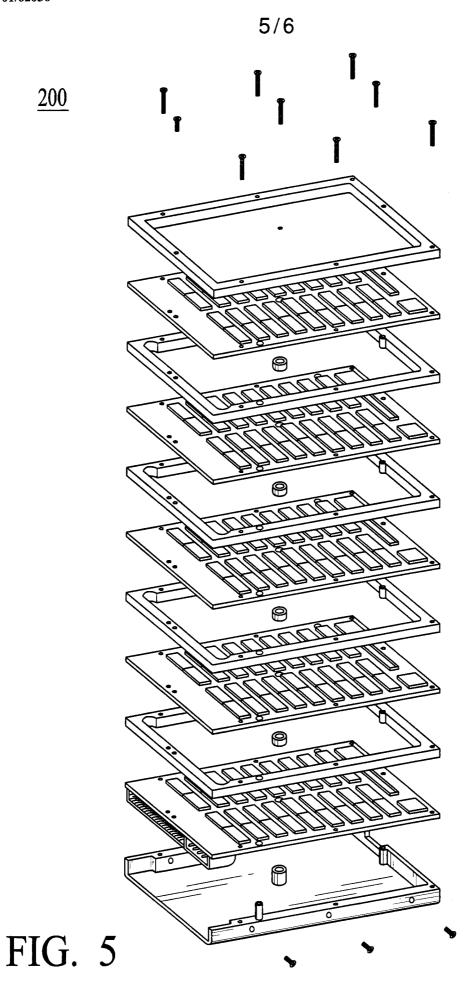

Figure 5 shows a 5-board printed circuit board assembly in accordance with the present invention.

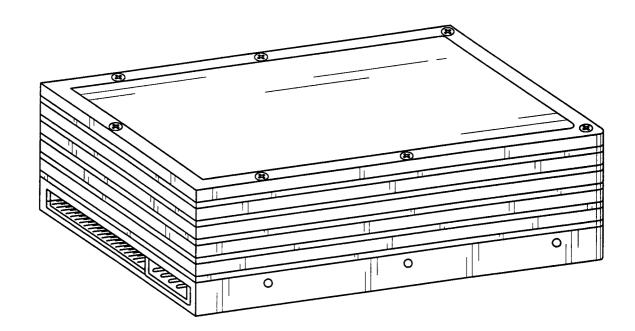

Figure 6 is a view of a completely assembled 5-board printed circuit board assembly in accordance with the present invention.

25

5

10

15

20

#### **DETAILED DESCRIPTION**

5

10

15

20

25

30

The present invention relates to a printed circuit board assembly. The following description is presented to enable one of ordinary skill in the art to make and use the invention and is provided in the context of a patent application and its requirements. Various modifications to the preferred embodiment and the generic principles and features described herein will be readily apparent to those skilled in the art. Thus, the present invention is not intended to be limited to the embodiment shown but is to be accorded the widest scope consistent with the principles and features described herein.

The apparatus in accordance with the present invention is presented in the context of a preferred embodiment. The preferred embodiment of the present invention is an improved printed circuit board assembly. The printed circuit board assembly in accordance with the present invention incorporates printed circuit boards that extend over the entire area of the bottom plate. By extending the printed circuit board over the entire area of the bottom plate, the available space on each of the printed circuit boards is maximized. By maximizing the available space, more electronic circuitry can be incorporated onto the board. Furthermore, the exterior spacer design together with interior spacer elements firmly secures each printed circuit board while maintaining a constant separation between each board. This facilitates the ability to stack more printed circuit boards, while maintaining the mechanical alignment and structural rigidity necessary for the stacking data connectors to function properly in the event the assembly is subjected to a sudden shock or vibration.

For a better understanding of the assembly in accordance with the present invention, please refer now to Figure 2. Figure 2 shows a printed circuit board (PCB) assembly 100 in accordance with the present invention. The assembly 100 includes a cover plate 104, a memory board 108, a perimeter spacer element 113, a controller board 114, and a bottom plate 118.

The cover plate 104, bottom plate 118 and perimeter spacer element 113 are preferably made of a hard anodized aluminum for rigidity, appearance, durability, and to prevent corrosion. However, the aluminum could be replaced if a suitable substitute was found which met the mechanical requirements. The cover plate 104 further includes a plurality of perimeter mounting holes 102 and a center mounting hole 106. Once the

5

10

15

20

25

30

memory board 108, the perimeter spacer element 113, the controller board 114, and the bottom plate 118 are stackably in place, the cover plate 104 is coupled to the bottom plate 118 via threaded fasteners 101 or similar connection means that are fitted into the center hole 106 and each of the perimeter mounting holes 102.

The memory board 108 includes a connector element 109, a plurality of memory chips 110, perimeter holes 111, and a center hole 105. Please refer now to Figure 3. Shown in Figure 3 is a second plurality of memory chips 110' that are located on the other side of the memory board 108. The connector element 109 is utilized to interconnect the memory board 108 with the controller board 114 via a second connector element 116. Each of the connector elements 109, 116 are preferably header/socket type connector elements.

Referring back to Figure 2, located between the memory board 108 and the controller board 114 is the perimeter spacer element 113. Preferably, the perimeter spacer element 113 has a height of 3mm and is implemented to rigidly support the connection between the memory board 108 and the controller board 114 while maintaining an optimum distance between the memory board 108 and the controller board 114. This becomes important if the PCB assembly is subjected to a sudden shock or vibration. If the connector elements 109, 116 are subjected to any vibrational forces while data is being transferred and the connection between the boards is temporarily misaligned, data integrity could be affected. The perimeter spacer element 113 also prevents the memory chips 110' from touching the memory chips 117 on the controller board 114. Accordingly, since the memory chips are approximately 1.1 mm thick, the 3mm perimeter spacer element 106 provides a distance of approximately .8 mm between the chips.

Although the preferred embodiment of the present invention discloses specific component dimensions, one of ordinary skill in the art will readily recognize that a variety of dimensions could be utilized while remaining within the spirit and scope of the present invention.

Also shown in Figure 2 is a center spacer ring 112 that is preferably located between each of the PCBs at the center hole 115 of the controller board 114. This center spacer ring 112 is preferably made of the same material and is the same height as the perimeter spacer 113. This is due to the thermal coefficient of expansion, i.e., it will expand/contract in size at the same rate as the perimeter spacer 113. The center spacer ring 112 should be of a

5

10

15

20

25

30

sufficient thickness to support a threaded fastener or similar connections means and is included to add stability to the center of PCB assembly 100 should the PCB assembly 100 be subjected to a sudden shock or vibration. The center spacer ring 112 is subsequently held in place by a threaded fastener or similar connection means that is fitted from the center hole 106 of the cover plate 104 to the threaded riser 124 of the bottom plate 118. The center spacer ring 112 is not threaded, however the threaded fastener passes easily through it.

The controller board 114 includes a plurality of memory chips 117, a plurality of perimeter holes 119, a center hole 115, and a connector 116. Please refer now to Figure 3. The controller board 114 also includes an LED portion 130 and an interface connector 132. Located on the bottom side of the controller board 114 are the control components 134. These include, but are not limited to, processors, memory, interface chips, DC-DC converters, etc.

The bottom plate 118 includes two side walls 120, a back wall 122, and a threaded riser 124. Each of the side walls 120 and the back wall 122 are of a sufficient thickness to support threaded fasteners or similar connections means and accordingly include a plurality of perimeter holes 126 for receiving the threaded fasteners. Also included on the bottom plate is a threaded riser 124. The threaded riser 124 is preferably machined into the bottom plate 118 and is located at the center of bottom plate 118. The riser 124, is the same height of the side walls 120 and is of a sufficient thickness to support a threaded fastener or similar connections means, is included to add stability to the center of PCB assembly should the PCB assembly be subjected to a sudden shock or vibration.

Finally, the bottom plate 118 includes two dowel holes wherein two dowel pins 128 are pressed into the bottom plate 118 during assembly. These dowel pins 128 are preferably made of stainless steel or another suitable material. These dowel pins 128 are preferably located diametrically opposite each other on the side walls 120 of the bottom plate 118 and add to the structural rigidity of the PCB assembly 100. Figure 4 is a view of the completely assembled printed circuit board assembly 100 in accordance with the present invention.

A key feature of the present invention involves the design of the printed circuit boards 108, 114. In accordance with the present invention, the PCBs 108, 114 are extended over the entire area of the bottom plate 118. Specifically, the PCBs 108, 114 are extended over the edges of the side walls 120 and back wall 122 of the bottom plate 118. By

extending the PCBs 108,114 over the edges of the side walls 120 and back wall 122 of the bottom plate 118, the available space on each of the PCBs 108, 114 is increased, thereby allowing the memory chips to be placed further towards the side edges of the PCBs 108,114. Consequently, by allowing the memory chips to be placed further towards the side edges of the PCBs 108,114 the PCBs are able to incorporate more memory chips.

5

10

15

20

25

30

Accordingly, if the PCBs 104, 114 were designed using conventional PCB design methods, they could only employ a maximum of 28 memory chips on each side of the PCBs because of the limited available space. By extending the PCBs over the edges of the side walls and back wall of the bottom plate, a PCB in accordance with the present invention is capable of employing 32 memory chips on each side of the PCBs. Increasing the amount of memory chips utilized in the PCB assembly in accordance with the present invention produces the desirable affect of increasing the available memory capacity and as physical package of the memory chips decreases in size, the number of chips utilized in the assembly will increase as well.

Although the above described embodiment of the present invention contemplates increasing the number of memory chips on a PCB, it should be readily apparent to one of ordinary skill in the art that any type of electronic circuitry could be incorporated onto the PCB while remaining within the spirit and scope of the present invention.

A further aspect of extending the PCBs over the edges of the side walls and back wall of the bottom plate is the fact that the PCBs are subsequently mounted along the perimeter edges at the perimeter mounting holes. By mounting the PCBs along their respective perimeters, the stability of the individual PCBs is increased which increases the overall stability of the PCB assembly. One of the main objectives of the present invention is to provide a PCB assembly that can stackably house as many PCBs as possible while maintaining a structurally rigid assembly. By extending the PCBs over the edges of the side walls and back wall of the bottom plate and by utilizing thinner PCBs in conjunction with the spacer elements (spacer assembly, center spacer) the PCB assembly in accordance with the present invention is capable of stacking numerous PCBs in a structurally rigid fashion. For example, Figures 5 and 6 respectively show a 5-board PCB assembly 200 in accordance with the present invention and a view of the completely assembled 5-board PCB assembly 200 in accordance with the present invention and a view of the completely assembled 5-board PCB assembly

7

Although the above described embodiment of the present invention discloses the ability to stack up to 5 PCBs in one PCB assembly, one of ordinary skill in the art should readily recognize that the preferred embodiment of the present invention should not be limited to 5 boards. As many as 10 PCBs may be stacked in one PCB assembly and as computer components become smaller, this number may increase. Accordingly, the maximum number of PCBs utilized in a PCB assembly in accordance with the present invention could vary while remaining within the spirit and scope of the present invention.

5

10

15

20

25

30

Additionally, for manufacturers that are especially concerned with protecting the PCB assembly against a sudden shock or vibration, an added component is contemplated. This component is a vibration dampener, preferably made of an elastomer material, that could be fitted on top of a memory chip. Consequently, each PCB in accordance with the present invention could incorporate a plurality of vibration dampeners that are fitted on the tops of a portion of the memory chips in order to provide added support to the PCB assembly. Preferably, the dampeners are pre-loaded 20%-40% in order to achieve maximum effectiveness. For instance, if the distance between the memory chips on a top layer of a PCB and the memory chips on the bottom layer of the PCB directly above it is .8mm, a 1mm thick dampener that is fitted on the top of one of the chips would be compressed (pre-loaded) by .2mm or 20%.

By utilizing an assembly in accordance with the present invention, the available space on each of the plurality of printed circuit boards is maximized. By maximizing the available space, more electronic circuitry can be incorporated onto the board. Furthermore, the exterior spacer design together with interior spacer elements firmly secures each printed circuit board while maintaining a constant separation between each board. This facilitates the ability to stack more printed circuit boards, while maintaining the mechanical alignment and structural rigidity necessary for the stacking data connectors to function properly in the event the assembly is subjected to a sudden shock or vibration.

Although the present invention has been described in accordance with the embodiments shown, one of ordinary skill in the art will readily recognize that there could be variations to the embodiments and those variations would be within the spirit and scope of the present invention. Accordingly, many modifications may be made by one of ordinary skill in the art without departing from the spirit and scope of the

8

appended claims.

#### **CLAIMS**

What is claimed is:

1

2

3

4

3

5

6

7

2

2

3

| 1 | 1. A printed circuit board assembly comprising:                                                  |

|---|--------------------------------------------------------------------------------------------------|

| 2 | a first plate;                                                                                   |

| 3 | a second plate attachably coupled to the first plate; and                                        |

| 4 | at least one printed circuit board sandwiched between the first plate and the                    |

| 5 | second plate, the at least one printed circuit board extending over the entire area of the first |

| 6 | and second plate.                                                                                |

- 2. The assembly of claim 1 wherein the at least one printed circuit board comprises a controller board, the controller board having a first and second side wherein the first side comprises a plurality of memory chips thereon and the second side comprises a plurality of control components thereon.

- 3. The assembly of claim 1 wherein the at least one printed circuit board comprises a controller board and at least one memory board, the controller board and at least one memory board having a connector element for connecting the controller board to the at least one memory board, the controller board having a first and second side wherein the first side comprises a plurality of memory chips thereon and the second side comprises a plurality of control components thereon, the at least one memory board having a first and second side, each of the first and second sides having a plurality of memory chips thereon.

- 4. The assembly of claim 3 further comprising a perimeter spacer element wherein the perimeter spacer element is sandwiched between the controller board and the at least one memory board.

- 5. The assembly of claim 4 wherein each of the controller board and the at least one memory board further includes a center mounting hole, the assembly further comprising a center spacer element located between the controller board and the at least one

| 4 | memory boar                                                                                 | d at the center mounting hole.                                                       |  |  |  |

|---|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| 1 | 6.                                                                                          | The assembly of claim 3 further comprising a dampener element                        |  |  |  |

| 2 | substantially                                                                               | compressed between the controller board and the at least one memory board.           |  |  |  |

| 1 | 7.                                                                                          | The assembly of claim 6 wherein the dampener element comprises an                    |  |  |  |

| 2 | elastomer material.                                                                         |                                                                                      |  |  |  |

| 1 | 8.                                                                                          | The assembly of claim 3 wherein the at least one memory board comprises a            |  |  |  |

| 2 | plurality of m                                                                              | nemory boards, each of the plurality of memory boards having a first and             |  |  |  |

| 3 | second side, each of the first and second sides having a plurality of memory chips thereon, |                                                                                      |  |  |  |

| 4 |                                                                                             | of the plurality of memory boards includes a connector element for                   |  |  |  |

| 5 | connecting each of the plurality of memory boards to the controller board, wherein each of  |                                                                                      |  |  |  |

| 6 |                                                                                             | rcuit boards is separated by a perimeter spacer element and a center spacer          |  |  |  |

| 7 | element.                                                                                    |                                                                                      |  |  |  |

| 1 | 9.                                                                                          | The assembly of claim 8 wherein the at least one memory board comprises              |  |  |  |

| 2 | at least 9 memory boards.                                                                   |                                                                                      |  |  |  |

| 1 | 10.                                                                                         | The assembly of claim 1 wherein the first plate comprises a cover plate and          |  |  |  |

| 2 | the second plate comprises a bottom plate.                                                  |                                                                                      |  |  |  |

| 1 | 11.                                                                                         | A printed circuit board assembly comprising:                                         |  |  |  |

| 2 |                                                                                             | a first plate;                                                                       |  |  |  |

| 3 |                                                                                             | a second plate attachably coupled to the first plate;                                |  |  |  |

| 4 |                                                                                             | a plurality of printed circuit boards sandwiched between the first plate and         |  |  |  |

| 5 | the second p                                                                                | late, each of the plurality of printed circuit boards extending over the entire area |  |  |  |

| 6 | of the first and second plate; and                                                          |                                                                                      |  |  |  |

| 7 |                                                                                             | at least one perimeter spacer element wherein the at least one perimeter             |  |  |  |

spacer element is sandwiched between each of the plurality of printed circuit boards.

| 1 | 12. The assembly of claim 11 wherein the plurality of printed circuit boards                  |  |  |  |

|---|-----------------------------------------------------------------------------------------------|--|--|--|

| 2 | comprises a controller board and at least one memory board, the controller board and at       |  |  |  |

| 3 | least one memory board having a connector element for connecting the controller board to      |  |  |  |

| 4 | the at least one memory board, the controller board having a first and second side wherein    |  |  |  |

| 5 | the first side comprises a plurality of memory chips thereon and the second side comprises a  |  |  |  |

| 6 | plurality of control components thereon, the at least one memory board having a first and     |  |  |  |

| 7 | second side, each of the first and second sides having a plurality of memory chips thereon.   |  |  |  |

| 1 | 13. The assembly of claim 12 wherein each of the plurality of printed circuit                 |  |  |  |

| 2 | boards further includes a center mounting hole, the assembly further comprising a center      |  |  |  |

| 3 | spacer element located between each of the plurality of printed circuit boards at the center  |  |  |  |

| 4 | mounting hole.                                                                                |  |  |  |

|   |                                                                                               |  |  |  |

| 1 | 14. The assembly of claim 13 further comprising a dampener element                            |  |  |  |

| 2 | substantially compressed between each of the plurality of printed circuit boards.             |  |  |  |

|   | 15 TH 11 C1' 14 1 ' 11 1                                                                      |  |  |  |

| 1 | 15. The assembly of claim 14 wherein the dampener element comprises an                        |  |  |  |

| 2 | elastomer material.                                                                           |  |  |  |

| 1 | 16. The assembly of claim 15 wherein the at least one memory board comprises                  |  |  |  |

| 2 | at least 9 memory boards.                                                                     |  |  |  |

|   | ·                                                                                             |  |  |  |

| 1 | 17. The assembly of claim 11 wherein the first plate comprises a cover plate and              |  |  |  |

| 2 | the second plate comprises a bottom plate.                                                    |  |  |  |

|   |                                                                                               |  |  |  |

| 1 | 18. A printed circuit board assembly comprising:                                              |  |  |  |

| 2 | a cover plate;                                                                                |  |  |  |

| 3 | a bottom plate attachably coupled to the cover plate;                                         |  |  |  |

| 4 | a plurality of printed circuit boards sandwiched between the cover plate and                  |  |  |  |

| 5 | the bottom plate, each of the plurality of printed circuit boards extending over the entire   |  |  |  |

| ( | area of the cover plate and the bottom plate, each of the plurality of printed circuit boards |  |  |  |

of printed circuit boards.

including a center mounting hole and a connector element for connecting the plurality of printed circuit boards, the plurality of printed circuit boards comprising at least one controller board and 9 memory boards, the controller board having a first and second side wherein the first side comprises a plurality of memory chips thereon and the second side comprises a plurality of control components thereon, each of the 9 memory boards having a first and second side, each of the first and second sides having a plurality of memory chips thereon;

a plurality of perimeter spacer elements wherein each of the plurality of perimeter spacer elements is sandwiched between each of the plurality of printed circuit boards;

a plurality of center spacer elements, each of the plurality of center spacer elements located between each of the plurality of printed circuit boards at the center mounting hole; and

an elastomer material substantially compressed between each of the plurality

FIG. 1

SUBSTITUTE SHEET (RULE 26)

FIG. 3

SUBSTITUTE SHEET (RULE 26)

FIG. 4

SUBSTITUTE SHEET (RULE 26)

FIG. 6

### INTERNATIONAL SEARCH REPORT

International application No. PCT/US01/01650

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(7) :H05K 7/14                                                                                                                                                                                      |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| US CL: 361/742, 758, 790, 796, 804; 439/74, 76.1 According to International Patent Classification (IPC) or to both national classification and IPC                                                                                          |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| B. FIELDS SEARCHED                                                                                                                                                                                                                          |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| Minimum documentation searched (classification system followed by classification symbols)                                                                                                                                                   |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| U.S. : 361/736, 737, 741, 742, 752, 756, 758, 785, 790, 796, 802, 803, 804; 439/74, 76.1; 257/686, 723                                                                                                                                      |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched NONE                                                                                                          |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)  NONE                                                                                                          |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                      |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| Category* Citation of document, with indication, where ap                                                                                                                                                                                   | propriate, of the relevant passages                                                                                                     | Relevant to claim No.                                             |  |  |  |  |  |  |

| X US 5,499,164 A (HILL-LINDSA)                                                                                                                                                                                                              | ,                                                                                                                                       | 1, 10, 11, 17                                                     |  |  |  |  |  |  |

| (12.03.1996), figs. 8-9 and col. 4, lin                                                                                                                                                                                                     | es 50-67.                                                                                                                               | 3-9, 12-16, 18                                                    |  |  |  |  |  |  |

| A                                                                                                                                                                                                                                           |                                                                                                                                         | 3-9, 12-10, 16                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| 3, lines 19-42; and col. 4, lines 22-25                                                                                                                                                                                                     |                                                                                                                                         | 2                                                                 |  |  |  |  |  |  |

|                                                                                                                                                                                                                                             |                                                                                                                                         | 2                                                                 |  |  |  |  |  |  |

| X US 4,226,491 A (KAZAMA et al) 07                                                                                                                                                                                                          | October 1980 (07.10.1980),                                                                                                              | 1, 10                                                             |  |  |  |  |  |  |

| figs. 1-3 and col. 2, lines 29-31.                                                                                                                                                                                                          |                                                                                                                                         | 2                                                                 |  |  |  |  |  |  |

| ı l                                                                                                                                                                                                                                         |                                                                                                                                         | 2                                                                 |  |  |  |  |  |  |

|                                                                                                                                                                                                                                             | US 5,864,463 A (TSUKADA et al) 26 January 1999 (29.01.1999), fig. 3; col. 1, lines 18-33; col. 2, lines 11-17; and col. 7, lines 17-50. |                                                                   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| Further documents are listed in the continuation of Box C                                                                                                                                                                                   | See patent family annex.                                                                                                                |                                                                   |  |  |  |  |  |  |

| Special categories of cited documents:  "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |                                                                                                                                         |                                                                   |  |  |  |  |  |  |

| to be of particular relevance  "E" earlier document published on or after the international filing date                                                                                                                                     | "X" document of particular relevance; the considered novel or cannot be conside when the document is taken alone                        | e claimed invention cannot be<br>red to involve an inventive step |  |  |  |  |  |  |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                     | "Y" document of particular relevance; the considered to involve an inventive                                                            |                                                                   |  |  |  |  |  |  |

| "O" document referring to an oral disclosure, use, exhibition or other means "P" document published prior to the international filing date but later than                                                                                   | combined with one or more other suc<br>being obvious to a person skilled in t                                                           | h documents, such combination                                     |  |  |  |  |  |  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                      | "&" document member of the same patent                                                                                                  | family                                                            |  |  |  |  |  |  |

| Date of the actual completion of the international search                                                                                                                                                                                   | Date of mailing of the international sea                                                                                                | •                                                                 |  |  |  |  |  |  |

| 07 MARCH 2001                                                                                                                                                                                                                               | 05                                                                                                                                      | APR 2001                                                          |  |  |  |  |  |  |

| Name and mailing address of the ISA/US<br>Commissioner of Patents and Trademarks                                                                                                                                                            | Authorized officer                                                                                                                      |                                                                   |  |  |  |  |  |  |

| Box PCT Washington, D.C. 20231                                                                                                                                                                                                              | JOHN B. VIGUSHIN                                                                                                                        |                                                                   |  |  |  |  |  |  |

| Facsimile No. (703) 305-3230                                                                                                                                                                                                                | Telephone No. (703) 308-1205                                                                                                            | na Kaster                                                         |  |  |  |  |  |  |