(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-504648

(P2005-504648A)

(43) 公表日 平成17年2月17日(2005.2.17)

(51) Int.C1.<sup>7</sup>B81C 1/00

B81B 3/00

G02B 26/08

F 1

B81C 1/00

B81B 3/00

G02B 26/08

E

テーマコード(参考)

2 H 0 4 1

審査請求 有 予備審査請求 未請求 (全 49 頁)

|               |                                                                                                       |          |                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2003-534312 (P2003-534312)                                                                          | (71) 出願人 | 501469788<br>ロックウェル・サイエンティフィック・ラ<br>イセンシング・エルエルシー                                                |

| (86) (22) 出願日 | 平成14年7月17日 (2002.7.17)                                                                                |          | アメリカ合衆国カリフォルニア州9135<br>8-0085, サウザンド・オークス, エ<br>ムシエイ 15, カミノ・ドス・リオス<br>1049, ピー・オー・ボックス 10<br>85 |

| (85) 翻訳文提出日   | 平成16年1月26日 (2004.1.26)                                                                                | (74) 代理人 | 100089705<br>弁理士 社本 一夫                                                                           |

| (86) 國際出願番号   | PCT/US2002/022782                                                                                     | (74) 代理人 | 100076691<br>弁理士 増井 忠式                                                                           |

| (87) 國際公開番号   | W02003/031321                                                                                         | (74) 代理人 | 100075270<br>弁理士 小林 泰                                                                            |

| (87) 國際公開日    | 平成15年4月17日 (2003.4.17)                                                                                |          |                                                                                                  |

| (31) 優先権主張番号  | 09/911,818                                                                                            |          |                                                                                                  |

| (32) 優先日      | 平成13年7月24日 (2001.7.24)                                                                                |          |                                                                                                  |

| (33) 優先権主張国   | 米国(US)                                                                                                |          |                                                                                                  |

| (81) 指定国      | EP(AT, BE, BG, CH, CY, CZ, DE, DK, EE,<br>ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), JP |          |                                                                                                  |

最終頁に続く

(54) 【発明の名称】ハイブリッドMEMS製造方法及び新規な光MEMSデバイス

## (57) 【要約】

光マイクロ電子機械システム(MEMS)デバイスを製造する新規なハイブリッド法が開示されている。この方法では、バルク及び表面マイクロマシニング技術の両方が用いられる。また、この新規な方法を用いて製造される新規な光MEMSデバイスも開示されている。本発明の方法は、ハンドル層をMEMS構造材料の1つ又は複数の層に実装するステップを含む(12)。次に、構造及び犠牲材料層が、表面マイクロマシニングを用いて、MEMS構造材料の上に構築する(14)。そして、駆動電子装置が、構造及び犠牲材料層の上に実装される(17)。ハンドル層が取り除かれてMEMS構造層を露出させ(18)、様々な層の中の犠牲材料が溶解される(20)。この新規な方法は、特に、光MEMSデバイスを製造するのに適用可能であり、ハンドル層(54)はSiミラー層(52)に隣接している。表面マイクロマシニング層は、電極(66)とバネ構造(67, 68)とを形成する。次に、駆動電子装置(92)が、構造材料層の上に実装され、それによって、バイアスがMEMS構造に加えられるようにする。ハンドル層(54)が

**【特許請求の範囲】****【請求項 1】**

マイクロ電子機械システム( MEMS )デバイスを製造するハイブリッドな方法( 10 )であって、

MEMS構造材料層に隣接してハンドル層を実装するステップ( 12 )と、

前記MEMS構造材料層の上に表面マイクロマシニングにより構造及び犠牲材料層を構築するステップ( 14 )と、

前記構造及び犠牲材料層に駆動電子装置を実装するステップ( 17 )と、

前記ハンドル層を前記MEMS構造材料から除去するステップ( 18 )と、

前記犠牲材料を溶解させることにより取り除くステップ( 20 )と、

を含むことを特徴とする方法。 10

**【請求項 2】**

請求項1記載の方法( 10 )において、前記ハンドル層は、犠牲実装層/材料によって前記MEMS構造材料層に実装される( 12 )ことを特徴とする方法。

**【請求項 3】**

請求項1記載の方法( 10 )において、前記ハンドル層は、グラインディングによって前記MEMS構造材料から除去される( 18 )ことを特徴とする方法。

**【請求項 4】**

請求項2記載の方法( 10 )において、前記ハンドル層は、前記ハンドル層を解放する化学的エッティングを用いて前記実装層/材料を溶解させることによって前記MEMS構造材料から除去される( 18 )ことを特徴とする方法。 20

**【請求項 5】**

請求項1記載の方法( 10 )において、前記駆動電子装置は、フリップチップ実装によって前記構造及び犠牲材料層に実装される( 17 )ことを特徴とする方法。

**【請求項 6】**

請求項1記載の方法( 10 )において、前記犠牲材料は化学的エッティングによって溶解される( 20 )ことを特徴とする方法。

**【請求項 7】**

請求項1記載の方法( 10 )において、前記MEMSデバイスはMEMSデバイスのアレイの中にあり、この方法は、前記駆動電子装置を実装する前に、前記MEMSデバイスの前記構造及び犠牲材料の上にリンク用フレームワークを構築する追加的ステップ( 22 )を含むことを特徴とする方法。 30

**【請求項 8】**

光マイクロ電子機械システム( MEMS )デバイスを製造するハイブリッドな方法であって、

ミラー層( 52 )に隣接してハンドル層( 54 )を実装して前記ミラー層( 52 )を保持及び保護するステップと、

前記ミラー層( 52 )の上に表面マイクロマシニングを用いて構造及び犠牲材料層( 60 )を構築するステップであって、前記構造材料( 66 、 67 、 68 )がMEMS構造を形成する、ステップと、

前記MEMS構造にバイアスが与えられ得るように、駆動電子装置( 92 )を前記構造及び犠牲材料層( 60 )に実装するステップと、

前記ハンドル層( 54 )を前記ミラー層( 52 )から除去するステップと、

前記犠牲材料( 64 )を溶解させて取り除き、前記MEMS構造を解放して、前記バイアス下で動作させるステップと、

を含むことを特徴とする方法。 40

**【請求項 9】**

請求項8記載の方法において、前記ミラー層( 52 )と前記ハンドル層( 54 )とは、両者でシリコン・オン・インシュレータ( SOI )基板を形成するシリコン( Si )であることを特徴とする方法。 50

**【請求項 10】**

請求項 8 記載の方法において、前記構造材料の表面マイクロマシニング(66、67、68)は、バネ構造と電極とを形成することを特徴とする方法。

**【請求項 11】**

請求項 10 記載の方法において、前記バイアスは前記ミラー(52)と前記電極(66)との間に与えられ、前記バネ構造(67、68)により、前記ミラー層(52)は、前記バイアスが与えられると移動し前記バイアスが取り除かれると復帰することが可能になることを特徴とする方法。

**【請求項 12】**

請求項 10 記載の方法において、前記バネ構造(67、68)は、前記駆動電子装置(92)と前記ミラー(52)との間を結合し、前記犠牲材料が溶解された後で、前記ミラー(52)を前記駆動電子装置(92)の上方に保持することを特徴とする方法。 10

**【請求項 13】**

請求項 10 記載の方法において、前記電極(66)は、前記駆動電子装置(92)と電気的に接続しており、前記駆動電子装置(92)と前記ミラー(52)との間に配置されていることを特徴とする方法。

**【請求項 14】**

請求項 11 記載の方法において、前記電極(66)と前記ミラー(52)との間にバイアスが与えられると、これら 2 つの間に静電応力が生じ、前記制限応力は前記ミラー(52)を前記駆動電子装置(92)の方向に引き寄せることを特徴とする方法。 20

**【請求項 15】**

請求項 8 記載の方法において、前記ハンドル層(54)は、犠牲実装層/材料(56)によって前記ミラー(52)に実装されることを特徴とする方法。

**【請求項 16】**

請求項 8 記載の方法において、前記ハンドル層(54)は、グラインディングによって前記ミラー層(52)から除去されることを特徴とする方法。

**【請求項 17】**

請求項 15 記載の方法において、前記ハンドル層(54)は、前記ハンドル層を解放する化学的エッティングを用いて前記実装層(56)を溶解させることによって前記ミラー層(52)から除去されることを特徴とする方法。 30

**【請求項 18】**

請求項 8 記載の方法において、前記駆動電子装置(92)は、フリップチップ実装によって前記構造及び犠牲材料層(60)に実装されることを特徴とする方法。

**【請求項 19】**

請求項 8 記載の方法において、前記構造及び犠牲材料(60)の中の前記犠牲材料(56)は化学的エッティングによって溶解される(20)ことを特徴とする方法。

**【請求項 20】**

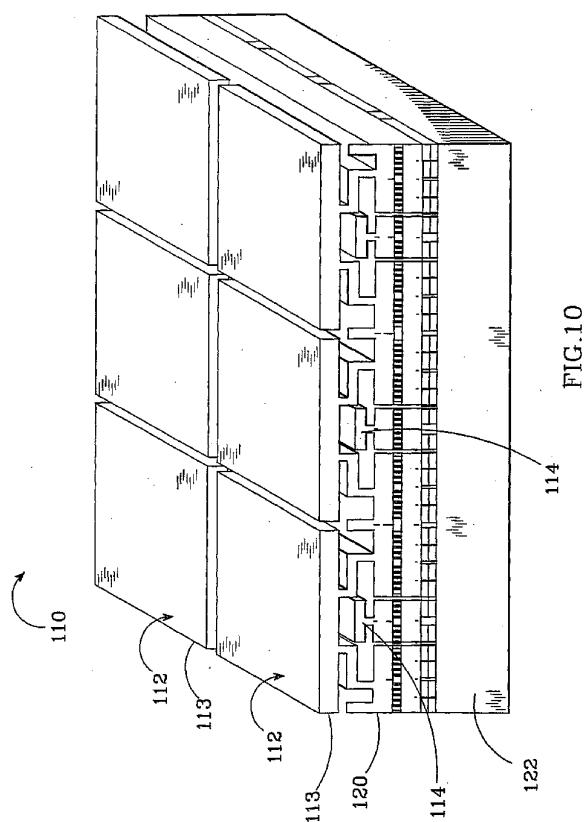

請求項 8 記載の方法において、前記光MEMSデバイス(112)はアレイ(110)の中の複数のMEMSデバイスの中の 1 つであり、この方法は、前記駆動電子装置を実装するステップの前に、前記構造及び犠牲材料層の上にリンク用フレームワーク(120)を構築する追加的ステップ(22)を含み、前記リンク用フレームワーク(120)は、前記構造及び犠牲材料層と前記電子装置との間に配置されていることを特徴とする方法。 40

**【請求項 21】**

請求項 20 記載の方法において、前記リンク用フレームワーク(120)は、追加的な構造及び犠牲材料層を構築することによって形成されることを特徴とする方法。

**【請求項 22】**

ハイブリッド製造プロセスを用いて製造された光マイクロ電子機械システム(MEMS)デバイスであって、

バルク・マイクロマシニングを用いて製造されたミラー(52)と、

前記ミラーを付勢する駆動電子装置を有する基板(92)と、 50

表面マイクロマシニング技術を用いて製造されたバネ構造(67、68)及び電極(66)と、

を備えており、前記バネ構造(67、68)は、前記基板(92)と前記ミラー(52)との間に接続されており前記ミラー(52)を前記基板の上方に保持し、前記電極(66)は、前記基板(92)の上に前記ミラー(52)と前記基板(92)との間に実装されており、前記ミラー(52)と前記電極(66)との間のバイアスが前記ミラー(52)を前記電極(66)の方向に引き寄せさせることを特徴とするデバイス。

【請求項23】

請求項22記載のデバイスにおいて、前記基板(92)と前記バネ構造(67、68)及び電極(66)との間にリンク用フレームワーク(70)を更に備えており、前記リンク用フレームワーク(70)は、前記MEMSデバイスをアレイの中の他のMEMSデバイスに接続することを特徴とするデバイス。

【請求項24】

光マイクロ電子機械システム(MEMS)デバイスのアレイであって、

複数の光MEMSデバイスであって、それぞれが、

バルク・マイクロマシニングを用いて製造されたミラー(113)と、

表面マイクロマシニング技術を用いて製造されたバネ構造及び電極(114)であって、

前記バネ構造は前記ミラー(113)に接続されている、バネ構造及び電極と、

を備えている複数の光MEMSデバイス(112)と、

前記光MEMSデバイス(112)に取り付けられ前記光MEMSデバイスを相互に隣接してリンクさせるリンク用フレームワークであって、前記バネ構造及び電極(114)はそれがこのフレームワークに接続されており、前記電極(114)はこのフレームワーク(120)と前記ミラー(113)との間に配置されている、リンク用フレームワーク(120)と、

駆動用電子装置を有し前記リンク用フレームワーク(120)に実装された基板であって、前記バネ構造と電極(114)との間にバイアスを加えて前記ミラー(113)を前記電極(114)の方向へ引きつけさせる、基板(122)と、

を備えていることを特徴とするアレイ。

【請求項25】

マイクロ電子機械システム(MEMS)デバイスを製造するハイブリッドな方法であって

、

バルク・マイクロマシニング材料層の上に表面マイクロマシニングにより構造及び犠牲材料層を構築するステップ(14)と、

前記構造及び犠牲材料層に駆動電子装置を実装するステップ(17)と、

前記バルク・マイクロマシニング材料層をエッチングするステップ(18)と、

前記犠牲材料を溶解させることにより取り除くステップ(20)と、

を含むことを特徴とする方法。

【請求項26】

請求項25記載の方法において、前記バルク・マイクロマシニング材料は、犠牲実装層/材料(56)によってMEMS構造材料層に実装されたハンドル層(54)を含むことを特徴とする方法。

【請求項27】

請求項26記載の方法において、前記MEMS構造材料はマイクロ・ミラー(52)であることを特徴とする方法。

【請求項28】

請求項25記載の方法において、前記犠牲材料(56)は化学的エッチングによって溶解されることを特徴とする方法。

【請求項29】

請求項25記載の方法において、前記MEMSデバイスはMEMSデバイス(112)のアレイ(110)の中にあり、この方法は、前記駆動電子装置を実装する前に、前記ME

10

20

30

40

50

M S デバイスの前記構造及び犠牲材料の上に、前記 M E M S デバイスを付着させるリンク用フレームワーク(120)を構築する追加的ステップ(22)を含むことを特徴とする方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロ電子機械システム(MEMS)デバイスに関し、更に詳しくは、MEMSデバイスを製造するためのハイブリッド方法とこの新しい方法を用いて製造される光MEMSデバイスとに関する。

【背景技術】

10

【0002】

最近、映写デバイス、ディスプレイ、ファイバ・スイッチ、センサ、ビーム・ステアリング及び光データ記憶デバイスなどの応用例のための光MEMSデバイスの開発に大きな関心が寄せられてきている。多くの場合、これらの光MEMSデバイスは、アレイ構成で製造されるが、そこでは、それぞれのアレイ要素が、異なる方向の光を反射するように個別制御が可能なマイクロ・ミラーを有している。

【0003】

MEMSデバイスを製造するための一般的なプロセスの1つとして、ディープ・エッチ処理を用いたバルク・マイクロマシニングによるものがあるが、これは、単一の基板層から材料をエッチングにより取り除いてMEMS構造を形成するものであるから、減算的な製造技術であると考えられている。より一般的な基板材料の1つにシリコン(Si)があり、シリコンは、光MEMSデバイスのための良質な反射面を与える。基板層は、数十ミクロン程度のオーダーと、比較的厚くてかまわない。この高度なプロセスによれば、カンチレバー、プリッジ、トレンチ、空乏、ノズル及び膜のような異なる構造の基板におけるマイクロマシニングが可能である。このプロセスを用いて製造されるMEMSデバイスは、他のプロセスによるデバイスと比較してより堅牢であると考えられ、処理の間にMEMSデバイスに対して作用する表面張力の影響を受けにくい。しかし、ただ1層の材料だけが用いられるため、MEMSデバイスの複雑度は制限されるのが一般的である。このプロセスの詳細については、J.K. Bhardwaj, H.J. Ashraf, Advanced Silicon Etching Using High Density Plasmas, Proc. SPIE, vol. 2639, Pg. 224 (1996, SPIE, Bellingham, WA), A.A. Aryon et al., Etching Characteristics and Profile Control in a Time Multiplexed Inductively Coupled Plasma Etcher, Solid State Sensor and Actuator Workshop, pg. 41 (June 1998, Hilton Head, SC)において論じられている。

20

【0004】

MEMSデバイスを製造する最も一般的な方法は、表面マイクロマシニング技術によるものである。これは加算的なプロセスであると考えているが、その理由は、構造層と犠牲スペーサ層とが交互に「ビルドアップ」されて、必要な機械的及び電気的特性を有するMEMS構造が構築されるからである。多結晶シリコン(ポリシリコン)が最も一般的に用いられる構造材料であり、二酸化シリコン(酸化物)ガラスが最も一般的に用いられる犠牲材料である。伝統的なマイクロマシニング・プロセスでは、これらの層は、シリコン基板の上に、シリコン窒化物の層を用いて分離されたポリシリコンと酸化物との対として形成される。これらの層は、フォトリソグラフィ技術を用いてパターニングされ、モータ、ギア、ミラー及びビームなどの複雑な構造が形成される。これらの層がビルドアップされていくつれて、酸化物層を貫通する切削がなされ、ポリシリコンを用いて充填されることにより、上部の構造層が基板に、又は、下位の構造層に固定される。ビルドアップ・プロセスの後で、犠牲(酸化物)層は、フッ化水素酸解放エッチングなどの様々な技術を用いて取り除かれ、これによって、デバイスが基板との関係で自由に移動できるようになる。M. A. Michalicek, J.H. Comtois, and H.K. Schriner, Design and Fabrication of Optical MEMS Using a Four-Level, Planarized, Surface Micromachined Polysilicon Process, Proc. SPIE Vol. 3276, pp. 48-55 (1998)を参照のこと。

30

40

50

## 【0005】

このプロセスを用いて製造されたMEMSデバイスは、バルク・マイクロマシニングによるデバイスよりも複雑である場合があり、デバイスの複雑度は、ポリシリコン／酸化物の対の数によって決定される。1つの対であれば、設計者は、単純なセンサに制限される。ギア付きの機構には2つの対が必要であり、第1の対からのポリシリコン層はギアを形成するのに用いられ、第2の対からのポリシリコン層はロッキング・ハブを形成するのに用いられる。モータ付きの機構には、最少でも3つの独立な層が必要である。更に最近では、5レベルの表面マイクロマシニング技術が開発され、この技術によると、他のサブアセンブリと係合して相互作用しうる並進可能なステージ上に複雑な可動コンポーネントを製造することができる。この技術は、一般的に、サンディア超平坦マルチレベルMEMS技術V(SUMMIT V)と称される。M.S. Rogers and J.J. Sniegowski, Designing Microelectromechanical System-On-A-Chip in a 5-Level Surface Micromachining Technology, 2nd Annual Int. Conf. On Engineering Design and Automation (August, 1998), and M.S. Rogers and J.J. Sniegowski, 5-Level Polysilicon Surface Micromachining Technology Application to Complex Mechanical Systems, Proc. 1998 Solid State Sensor and Actuator Workshop, pg. 144 (June 1998, Hilton Head, SC)などを参照のこと。

10

## 【0006】

マイクロミラー・アレイのために表面マイクロマシニング・プロセスを用いることの問題点として、薄いポリシリコン層はマイクロミラーとして用いられるのが通常であり残存する応力に対して極度に敏感でありうるということがある。このため、マイクロミラーにおいて著しい湾曲が生じることがあり、よって、個々のミラー及びアレイの光学的品質が劣化するのである。更に、ポリシリコン・マイクロミラーにより反射率の悪い表面が生じるが、反射率を向上させるには、ミラー表面を反射性の薄膜を用いて金属被覆することが可能である。しかし、そうすると、膜への追加的な応力が生じ、マイクロミラーの湾曲が更に生じうる。また、ポリシリコン層の1つをミラーに用いると、アクチュエータ、電極、バネなどに用いることができる利用可能な構造層の数が減少し、設計上の柔軟性と最終的なデバイスの複雑度とが低下する。

20

## 【0007】

最後に、ポリシリコン表面が粗いと、光学的品質が低下しうる。これは、表面の研磨(SUMMIT Vにおいて用いられている)やフリップ・チップ転送処理によって緩和しうる。最近開発された光MEMSデバイスには、このフリップチップ技術を用いて製造されたものがある。M.A. Michalicek et al., Micromirror Arrays Fabricated by Flip-Chip Assembly, SPIE vol. 3878, (20 September 1999)を参照のこと。シリコン・ミラーは、商用の鋳造プロセスを用いて酸化物によってシリコン基板に固定され、ボンディング・パッドがその上に積層される。次に、セラミック基板が金のワイヤとミラー・パッドと一致するインジウムのボンディング・パッドとを用いてパターニングされる。ミラー／基板構造は、次に、セラミック基板の上にフリップチップ実装され、フッ化水素酸エッチャリングを用いて酸化物を溶解することにより基板から分離される。結果的に得られるシリコン・ミラー表面は滑らかで、元の基板を複製しているが、このミラーは非常に薄い。コーティングがなされて反射率が増加させている場合には、ミラーは、応力を受け変形する可能性がある。また、ボンディング応力が変化すると、マイクロミラー・アレイの大局部的な一様性が損なわれる可能性がある。

30

40

## 【0008】

アレイの駆動電子装置をまず製造し次にその電子装置の上にマイクロミラーを構築することによって、別のタイプの光MEMSアレイが開発されている。L.J. Hornbeck, Digital Light Processing and MEMS: Timely Convergence for a Bright Future, Plenty Session, SPIE Micromachining and Microfabrication, Vol. 2639, Pg. 2 (October 1995, Austin, TX)を参照のこと。この製造プロセスには低温が必要であり、厳密な意味の表面マイクロマシニング・プロセスである。よって、別の応用例のための別の構造を製造するた

50

めにプロセスを変更する際には、柔軟性が制限される。また、ポリシリコン・マイクロミラーのように、これらのマイクロミラーは比較的薄いので、応力が加わると変形を生じやすい。例えば、反射率向上のためにミラーの上にコーティングを施す場合には、非常に薄くなければならず、さもないと、ミラーが変形する可能性がある。また、非常に薄いことにより、ミラーの位置合わせに誤差が生じることがあり、アレイの性能が低下することがありうる。

【発明の開示】

【0009】

本発明は、MEMSデバイスを製造する新規な方法と、その新規な方法を用いて製造された新規な光MEMSデバイスとを提供する。この新規な方法は、バルクの深いエッチングと表面マイクロマシニング製造技術とを組み合わせて両者の長所を取り入れている点でハイブリッドなものである。 10

【0010】

本発明によるハイブリッドな方法は、バルク・マイクロマシニング材料の層を提供し、表面マイクロマシニング技術を用いてバルク・マイクロマシニング材料の上に構造及び犠牲材料層を構築するステップを含む。次に、駆動電子装置を有する基板が、この構造及び犠牲材料層の上に実装される。そして、バルク材料は、マイクロマシニング加工がなされ、様々な表面層の内部にある犠牲材料が溶解される。

【0011】

本発明の方法は、特に、光MEMSデバイスの製造に応用可能である。この方法は、ハンドル層をミラー層に実装して、ミラー層を保持及び保護するステップで開始される。次に、構造及び犠牲材料層が、ミラー層の上に表面マイクロマシニングを用いて構築され、構造材料が、電極及びバネ構造を形成する。そして、駆動電子装置が構造材料層の上に実装され、それにより、電極及びバネ構造にバイアスを加えることができるようになる。ハンドル層はミラー層から取り除かれ、ミラーの反射面を露出させ、犠牲材料は表面マイクロマシニング層から溶解され、電極及びバネ構造が自由に動作するようになる。 20

【0012】

光及びそれ以外のMEMSデバイス・アレイの場合には、リンク用フレームワークを用いて、個々のMEMS要素を相互にリンクさせることができる。上述の方法では、リンク用フレームワークは、駆動電子装置を実装する前に、構造及び犠牲材料層の上に構築するのが好ましい。リンク用フレームワークは、また、同じ表面マイクロマシニング技術を用いて構築される。次に、駆動電子装置が、リンク用フレームワークに実装されて、MEMS構造との間に機械的及び電気的相互接続を提供する。 30

【0013】

本発明は、また、ハイブリッドな製造プロセスを用いて製造され、バルク・マイクロマシニング技術を用いて製造されるミラーと当該ミラーを付勢する駆動電子装置を有する基板とを含む新規な光MEMSデバイスを提供する。また、このデバイスは、バネ構造と表面マイクロマシニング技術を用いて製造された電極とを含む。バネ構造は、基板とミラーとの間に接続されており、ミラーを基板の上方に保持する。電極は、基板の上に、ミラーと基板との間に、実装されている。ミラーと電極との間に加えられるバイアスがデバイスを付勢し、ミラーを、バネ構造の作用に抗して、電極の方向に引きつける。 40

【0014】

本発明によるハイブリッド法と本発明による光MEMSデバイスとは、従来型の方法やデバイスと比較して多くの長所を有している。光MEMSデバイスのためには、マイクロミラーは、減算的なバルクの深いエッチング・プロセスによって形成され、その際、ハンドル層はSi層から取り除かれる。結果的に得られるマイクロミラーは、表面マイクロマシニング・プロセスにより形成されるものよりも厚く頑丈であり、良好な反射面を提供する。また、このデバイスは、表面マイクロマシニング技術を用いて構築されたMEMS構造を含む。これにより、純粋にバルク・マイクロマシニングがなされたデバイスと比較して、より複雑なMEMS構造を製造することが可能になる。MEMSアレイのためにリンク 50

用フレームワークを含めることにより、全体的な一様性を向上させることができる。

【0015】

本発明の以上のような及びそれ以外の特徴及び効果は、以下の詳細な説明を添付の図面と共に読むことにより、当業者に明らかになるはずである。

【発明を実施するための最良の形態】

【0016】

ハイブリッド法

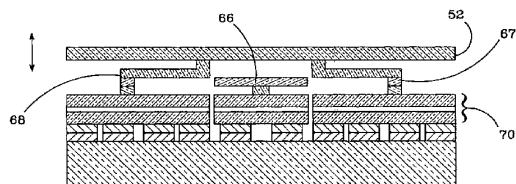

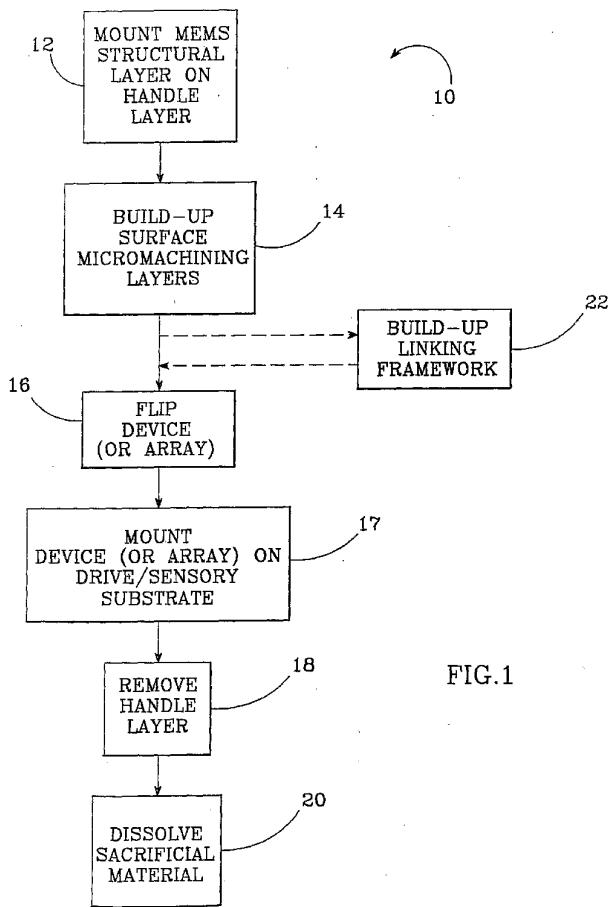

図1は、本発明によるMEMSデバイスを製造し单一のMEMSデバイス又は複数のMEMSデバイスのアレイを製造する新規なハイブリッド方法の流れ図10である。以下の説明では、主に、单一のMEMSデバイスを製造する新規な方法について述べるが、この方法は、複数のMEMSデバイスのアレイを製造する場合にも等しく適用可能である。

10

【0017】

最初のステップ12では、MEMS構造材料の層が、犠牲実装層／材料によって「ハンドル」層に実装される。このハンドル層は、多くの異なる材料を用いて作ることができ、MEMS構造層を、表面マイクロマシニング層がその上に構築される（後で述べる）間、保持及び保護するのに用いられる。このMEMS構造層は、例えば、光MEMSデバイスのためのミラー層でありうる。光MEMSアレイを製造する際には、多数のミラー層が用いられる。ハンドル層は、実装層／材料と共に、後述する製造ステップの間、ミラー層の表面を保持及び保護し、いったんハンドル及び酸化物層が取り除かれると、ミラーの反射面が現れる。これ以外の実施例では、複数のハンドル層及びMEMS構造材料が、单一のMEMSデバイスのために用いられることもありうる。次のステップ14では、表面マイクロマシニング層が、上述した表面マイクロマシニング技術を用いて、MEMS構造層の上に構築される。ポリシリコン／酸化物層の対が、様々なMEMS構造を構築するために積層される。光MEMSデバイスのためのセンサ、ギア、バネ及び電極を含む（限定例挙ではない）多くの異なる構造をこのプロセスを用いて構築することができ、このステップでは、上述の最近開発されたSUMMIT V5層表面マイクロマシニング・プロセスを用いることができる。反応炉成長など多くの標準的な成長プロセスを用いて層を構築することができ、また、多結晶シリコン、二酸化シリコン、シリコン・ゲルマニウム、シリコン・カーバイドなどの異なる材料をこれらの構築される層に用いることができる。

20

【0018】

次のステップ16では、ステップ14によるMEMS構造は反転（フリップ）され、ステップ17で、駆動及び／又は感知電子装置又はそのような電子装置への接続部を有する基板に実装される。接点をMEMS構造又は駆動／感知基板の上に含ませることも可能であり、これらのいずれかが、基板とMEMS構造との間の機械的及び電気的接続を提供する。これにより、構造にバイアスを与える、又は、構造からの信号を基板に与えることが可能になる。

30

【0019】

次のステップ18では、ハンドル層が取り除かれ、ハンドル層とMEMS構造層との間の実装層／材料が現れる。次に、酸化物材料を化学的なエッティングにより除去することができ、MEMS構造層の表面が現れる。あるいは、実装層／材料を最初にエッティングにより取り除き、ハンドル層をMEMS構造層からリフトすることもできる。

40

【0020】

最終のステップ20では、ポリシリコン／酸化物層の対における犠牲酸化物材料が溶解される。酸化物材料の溶解によって残った空間により、残っているポリシリコンMEMS構造が動くことが可能になり、また、複数の構造の間の機械的及び電気的分離が提供される。例えば、光MEMSデバイスにおいて、電極を、MEMSマイクロミラーを保持するバネ構造から、電気的にも機械的にも分離することができる。電極が静止している間にミラーがバネ構造の上で上下に動くように、バイアスを電極とミラーとの間に加えることができる。

50

【0021】

MEMSアレイを製造する際に、多数のデバイスをステップ12及び14を用いて構築することができ、リンク用レームワーク（結合用の枠）が、個々のMEMSデバイスをリンクさせるために含まれる。ステップ22では、フレームワークが、表面マイクロマシニング技術によって個々のMEMSデバイスのバネ及び駆動構造の上に構築され、これらをリンクさせる。フレームワークは、また、構造及び犠牲ポリシリコン／酸化物の対を含む。最終のステップ20では、フレームワークの犠牲酸化物材料は、構造の中の他の犠牲材料と共に溶解される。ステップ16で構造がセンサ／駆動電子装置に実装されるときには、フレームワークは、電子装置と表面マイクロマシニング層との間に配置される。MEMSデバイスに加えられたバイアスや、デバイスから基板に送られた信号は、リンク用フレームワークを通過する。

10

#### 光MEMSを製造するためのハイブリッド法

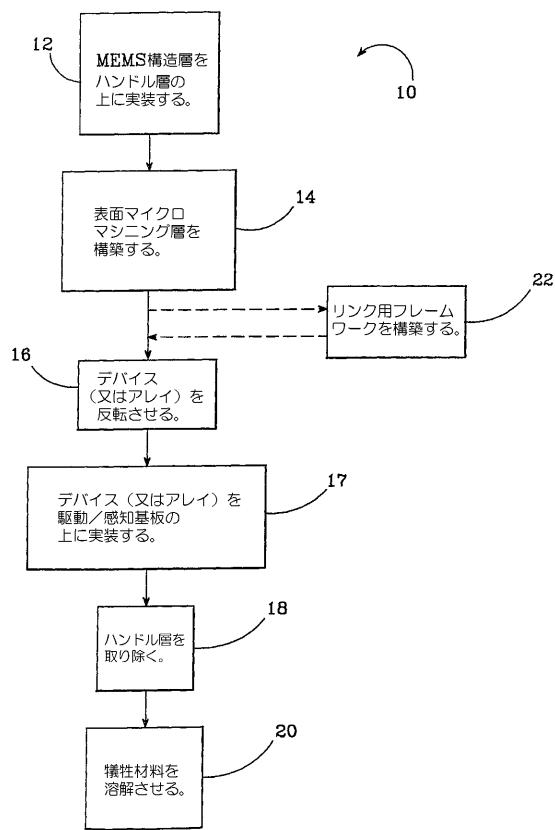

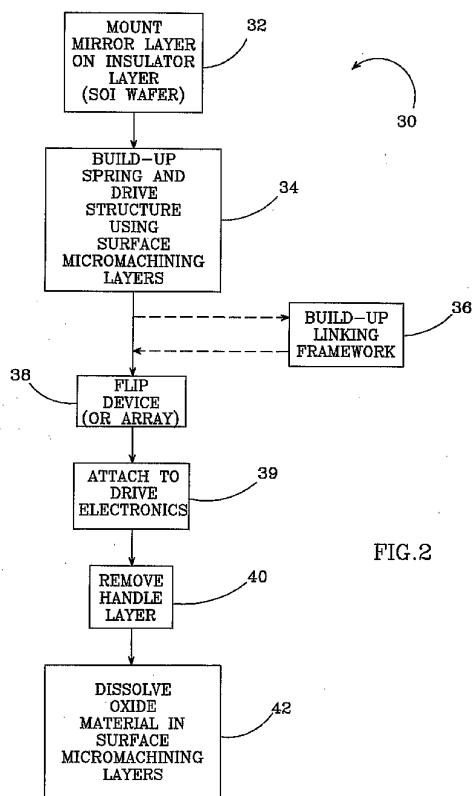

図2は、本発明による新規なハイブリッドな方法であるが、光MEMSデバイスを製造するのに用いられる場合である。既に述べたように、次の説明では、個々のMEMSデバイスの製造について主に述べるが、光MEMSアレイの製造にもこの方法は等しく適用可能である。

#### 【0022】

ステップ32では、MEMS構造層が、絶縁層の上に実装される。光MEMSデバイスでは、MEMS層は、デバイスのマイクロミラーとして機能し、高品質な反射面を提供する任意の材料でよいが、層がシリコン(Si)であることが好ましい。

#### 【0023】

このステップには、市販のシリコン・オン・インシュレータ(SOI)ウエハを用いることができるが、これは、多くの提供源から入手可能である。例えば、BCOテクノロジーズp1c、SEHアメリカInc、バージニア・セミコンダクタIncなどである。SOIウエハは、一般的に、薄いSi層とそれよりも厚いSiハンドル層とが絶縁酸化物材料を挟む構造を含んでいる。酸化物材料に隣接する薄いSi層は反射性のマイクロミラー表面として機能し、より厚いSi層と酸化物材料とはSiミラー層を保持及び保護するハンドル層として機能する。

#### 【0024】

ステップ34では、バネ及び駆動構造が、表面マイクロマシニング技術を用いてSOIウエハの上に構築され、ポリシリコン／酸化物層の対は、Siハンドル層とは反対の薄いSi層の表面上にある。これらの層の対は、ミラーを付勢する電極と、バイアスがMEMSデバイスに与えられるとミラーを動かしバイアスが除かれるとミラーを元に戻すバネ構造とを形成する。

20

#### 【0025】

オプションであるステップ36では、アレイの中の多数の光MEMSデバイスをリンクさせるフレームワークが、同じ表面マイクロマシニング技術を用いて、バネ及び駆動構造の上に構築される。フレームワークは、一般に、1つ又は2つのポリシリコン／酸化物層の対を用い、光MEMSデバイスのアレイの間に堅牢な結合を提供し、それによって、MEMSマイクロミラーの整列が改善され、結合応力に対する感度を低下させることができる。

30

#### 【0026】

ステップ38では、ステップ34（又は、ステップ36）によるMEMS構造が反転される。反転の前又は後に、金属製の接点を構造の底部層に積層させることができる。ステップ39では、構造が、フリップ・チップ結合技術を用いて駆動電子装置を用いて、機械的及び電気的に基板に取り付けられる。この取り付けのための最も容易で最も一般的な方法の1つとして、ハンダによるものがある。しかし、電気的接続に用いられる場合には、ハンダ・パッドをどの程度まで小さくできるかの限界が存在する。より小さな光MEMSデバイスの場合であれば、インジウム・コラムなど、他の取り付け方法を用いることもできる。

40

#### 【0027】

50

ステップ 140 では、この時点で構造の最上位の層であるハンドル（厚い Si）層が、取り除かれる。既に述べたように、別の除去方法を用いることもできるが、この実施例では、この層を下位にある酸化物層のレベルまで機械的に研磨し、酸化物層は化学的エッチングより溶解される。

【0028】

最終のステップ 42 では、バネ及び駆動構造における犠牲酸化物材料とリンク用フレームワークとが、MEMS 構造におけるポリシリコン又はシリコン材料を損傷することなく酸化物を溶解させる方法を用いて溶解される。適切な方法として、フッ化水素酸エッチングを用いる化学的エッチングがある。

【0029】

エッチング・プロセスが完了すると、ミラーとそのバネ構造は自由に動くことができ、駆動構造はバネ構造から機械的及び電気的に分離される。より詳しくは後述するが、ミラーと駆動構造との間にバイアスを加えることができ、これら 2 つの間に静電的な引力を生じさせることができ、これにより、バネ構造が圧縮される。バイアスが除去されると、静電的な引力も除去されて、バネ構造はミラーをその中立的な位置に自由に戻すことができる。

新規な方法を用いて製造される光MEMS デバイス

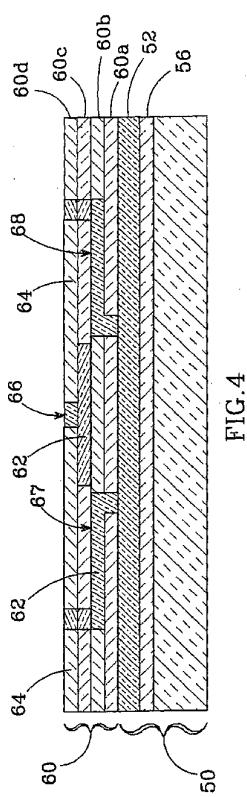

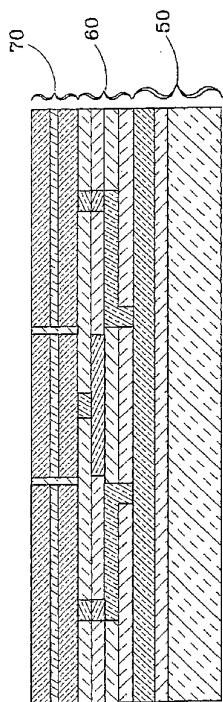

図 3 から図 9 は、上述した新規なハイブリッド法を用いて製造された新規な光MEMS デバイスを示している。図 3 は、上述したステップ 32 によって提供される SOI ウエハ 50 の断面図である。この SOI ウエハは、酸化物層 56 によってハンドル Si 層 54 に固定されている薄い Si 層 52 を有している。ハンドル層 54 は、Si 層 52 よりも厚いのが一般的であり、その適切な厚さは約 500 ミクロンである。Si 層 52 は、MEMS デバイスのマイクロミラーとして機能し、1 ミクロン未満でありうる。好ましい厚さの範囲は約 5 - 20 ミクロンである。しかし、これ以外の厚さでもかまわない。このマイクロミラーは、厚すぎると、迅速に動くには質量が大きすぎることになり、薄すぎると、その堅牢さが失われてしまう。

【0030】

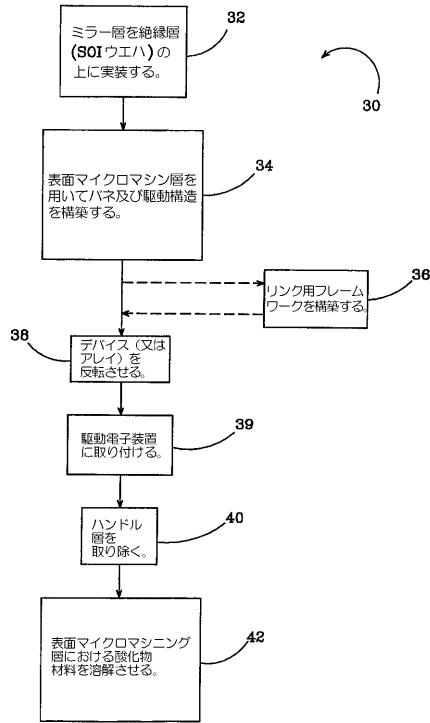

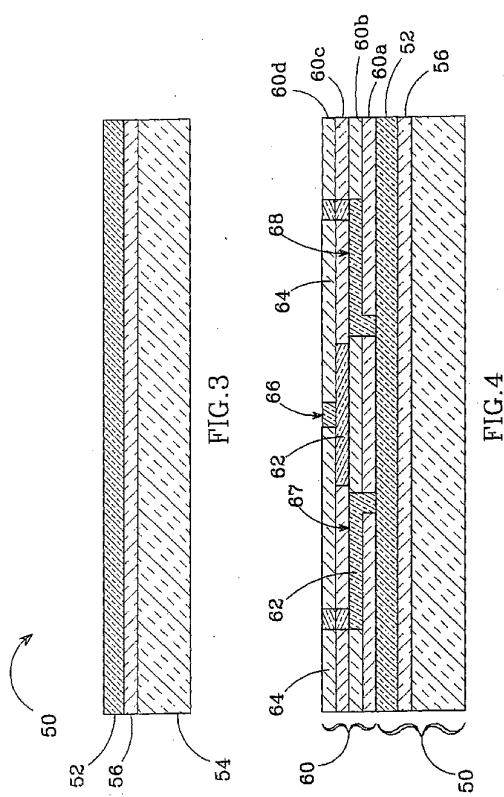

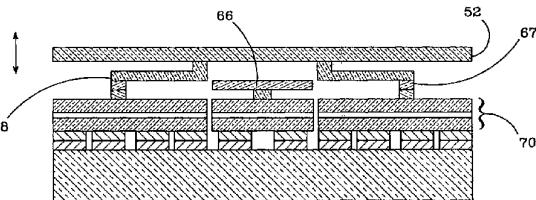

図 4 は、SOI ウエハ 50 の断面図であり、表面マイクロマシニング層 60 は、上述のステップ 34 により、ハンドル層 56 とは反対のシリコン層 52 の表面上に構築されている。2 つのポリシリコン / 酸化物の対に対応して、4 つの層 60a - d が存在している。4 つの層は、それぞれ、ポリシリコン構造材料 62 と酸化物犠牲材料 64 とを有している。これら 4 つの層はシリコン層 52 の上に構築されており、第 1 の層 60a は酸化物層であるのが一般的である。これは、様々な位置で切断され、それにより、ポリシリコンを、第 2 の層 60b と Si 層 52 との間の、又は、Si 層 52 への構造的な接続を提供するように含めることができる。第 2 の層 60b は一般にポリシリコン層であり、この層の積層の間、ポリシリコンが第 1 の層 60a の切断された領域に導かれる。この第 2 のポリシリコン層は、次の層 60c が積層されるときに犠牲酸化物が含まれるように、切断することができる。次の層 60c は酸化物であり、最終の層 60d はポリシリコンであり、これらは共に隣接する層からの材料を含むように切断することが可能である。

【0031】

これらの層は、構築される間に様々な態様での切断が可能であり、異なる機能を実行する構造が構築される。層 60a - d では、ポリシリコン材料 62 は、駆動電極 66 とバネ構造 67 及び 68 とを形成する。層は、用いられる層の対の数に応じて、異なる厚さを有することがありうる。SUMMIT V 表面マイクロマシニング技術を用いて添う 60a - d が積層される場合には、酸化物層の厚さは約 0.5 - 2.0 ミクロン、ポリシリコン層の厚さは約 0.3 - 2.5 ミクロンでありうる。

【0032】

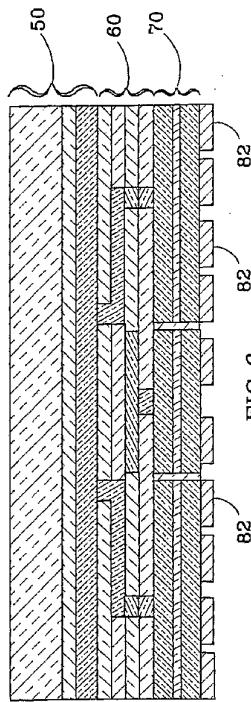

図 5 は、図 4 の構造であるが、上述したステップ 36 によりフレームワーク・リンク構造 70 がバネ及び駆動構造 60 の上に構築されたものを示している。リンク用フレームワークは、MEMS デバイスのアレイにわたる連続的な構造であり、それぞれのデバイスの上

10

20

30

40

50

にバネ及び駆動構造が構築された後でこれらのデバイスの上に構築される。また、構造 70 は、1つ又は2つのポリシリコン／酸化物層の対と共に表面マイクロマシニング技術を用いて製造される。構造 70 は、アレイの中の個々の光MEMSデバイスをリンクさせる。

【0033】

リンク用フレームワーク 70 に用いられる層の数は、電極及びバネ構造 60 に用いることができる層の数に直接的な影響を与える。リンク用フレームワーク 70 に層の対を2つ用いることによって、3つまでの層を、電極及びバネ構造 60 に用いることができる。層の対がただ1つ用いられる場合には、構造 60 のために4つまでの層を用いることができる。光MEMSデバイスがアレイにおいてリンクされない場合には、バネ及び駆動構造のために層の対を5つまで用いることができる。この構造の別の利点として、Siミラー層 52 が基板として機能できることがあり、それによって、5つの層すべてを表面マイクロマシニングに用いることができる。従来型の5層表面マイクロマシニングでは、最下部の層が基板として機能するのが一般的であり、4つの層だけしか残らなかった。

10

【0034】

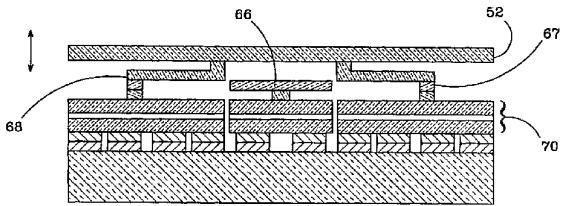

図6は、上述したステップ38によって反転された後の、図5の構造を示している。反転の前後のいずれにでも、既知のメタライゼーション・プロセスを用いて、接点 82 を、リンク用フレームワーク構造 70 の上に設けることができる。リンク用フレームワークが存在しない場合には、これらの接点は、電極及びバネ構造の上に設けられる。

20

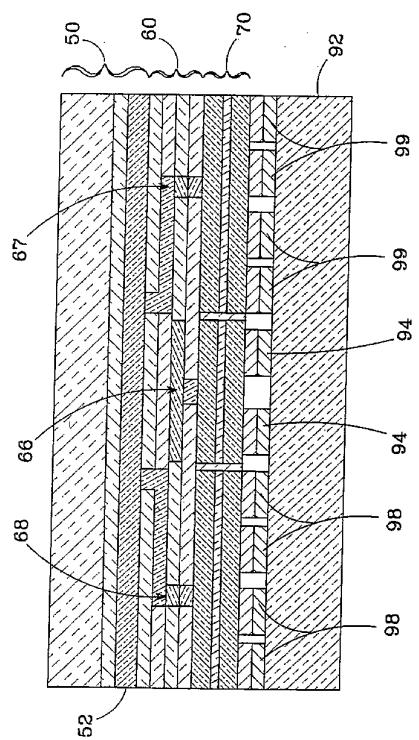

【0035】

図7は、駆動電子装置 92 を有する従来型の基板に実装された図6の構造を示している。基板 92 は、また、接点パッド 94、98 及び 99 を有しており、これらは、リンク用フレームワーク 70 の上の接点パッド 82 と整合されている。これらの整合された接点は、フレームワーク 70 と基板 92 との間の機械的及び電気的接続を提供する。動作の間には、接点パッド 94 に印加される電気信号は電極 66 に、接点 98 及び 99 に印加された電気信号はバネ構造 68 及び 67 に、それぞれ送られ、最終的にはマイクロミラー層 52 に至る。

【0036】

図7の構造は、構築プロセスが完了した後の光MEMSデバイスを示している。以下のステップでは、様々な層が除去又は溶解され、ミラーを露出させて、MEMS構造を自由に動き動作させる。

30

【0037】

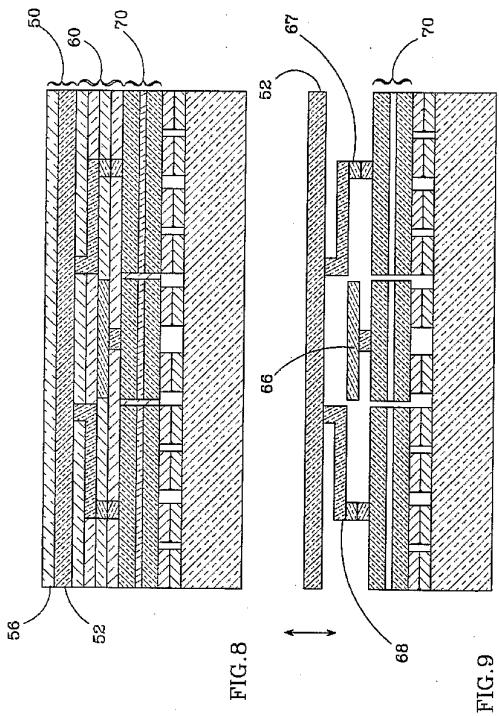

図8は、図7の構造を示しているが、上述のステップ39によってハンドル層 54 が取り除かれ、Siミラー層 52 の上に酸化物層 56 が残った状態になっている。上述の場合と同様に、ハンドル層は、研磨などの機械的な方法により取り除かれる。あるいは、酸化物層 56 を最初に化学的エッティングにより溶解させ、ハンドル層を解放することも可能である。

40

【0038】

最後に、図9は、上述のステップ40の化学的エッティングによる残りの酸化物犠牲材料が溶解された後の図8の構造を示している。この図は、更に、本発明による新規な方法を用いて製造された光MEMSデバイスの最終的な形態を示している。静電応力を生じさせるために、接点 94 と接点 98 及び 99 の両方又は一方との間に基板からバイアスが加えられる。接点 98 及び / 又は 99 のバイアスは、マイクロミラー 52 に至り、上述したように、このバイアスは、マイクロミラー 52 と電極 66 との間に静電応力を生じさせる。マイクロミラー 52 は、電極 66 の方向に下向きに引きつけられ、これにより、バネ構造 67 及び 68 が圧縮される。バイアスが取り除かれると、バネ構造 67 及び 68 はその中立的な位置に戻る。

【0039】

図10は、6要素アレイ 110 の中の新規な光MEMSデバイスを示している。MEMSデバイス 112 は、それぞれが、マイクロミラー 113 と、電極 114 と、バネ構造 11

50

6 及び 118 とを有している。単一のリンク用フレームワーク 120 は、アレイ 110 の全体にわたって伸張し、個々の MEMS デバイスを相互にリンクさせる。駆動電子装置 122 を有する基板がリンク用フレームワーク 120 に実装され、それにより、MEMS デバイスは、それぞれ、特定のデバイス 112 における電極 114 とマイクロミラー 113 との間のバイアスによって個別的に付勢されるようになる。

#### 【0040】

以上では、本発明を特定の好適な構成例を参照して相当詳細に説明したが、これ以外の様も可能である。例えば、ハンドル層と実装層／材料とが取り除かれた後で、MEMS 構造層をバルク・マイクロマシニング技術を用いて更に加工して、カンチレバー、ブリッジ、トレンチ、空乏、ノズル、膜などを層の中に形成することもできる。上述した方法におけるステップは、別の順序で生じたり、他のステップが含まれることもありうる。上述した光 MEMS デバイスは、本発明によって製造できる多くの異なるタイプの中の 1 つであり、それ以外のデバイスの一例として、付勢されると傾くミラーを有するものがある。従って、特許請求の範囲の精神及び範囲は、この明細書に記載された本発明の好適実施例に限定されることはない。

#### 【図面の簡単な説明】

#### 【0041】

【図 1】MEMS デバイスを製造するための新規でハイブリッドな方法の流れ図である。

【図 2】光 MEMS デバイスを製造するための新規でハイブリッドな方法の流れ図である。

【図 3】本発明による光 MEMS デバイスのための固定層の上のミラー層の断面図である。

【図 4】図 3 に示されているミラー層の上に構築された駆動及びバネ構造の断面図である。

【図 5】図 4 の構造の上に構築されたリンク用フレームワークの断面図である。

【図 6】フリップ・チップ実装のために反転（フリップ）した後の図 5 の構造の断面図である。

【図 7】駆動電子装置を有する基板の上に実装された図 6 の構造の断面図である。

【図 8】ハンドル層が取り除かれた図 7 の構造の断面図である。

【図 9】犠牲層が溶解された図 8 の構造の断面図である。

【図 10】本発明によるハイブリッドな製造プロセスを用いて製造された光 MEMS デバイスのアレイの全体図である。

10

20

30

【図1】

【図2】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

17 April 2003 (17.04.2003)

PCT

(10) International Publication Number

WO 03/031321 A2(51) International Patent Classification<sup>5</sup>: B81B 3/00, G02B 25/08

(74) Agents: HEYBL, Jaye, G. et al.; Koppel, Jacobs, Patrick &amp; Heybl, 555 S. Charles Drive, Suite 107, Thousand Oaks, CA 91360 (US).

(81) Designated State (national): JP.

(21) International Application Number: PCT/US02/22782

(22) International Filing Date: 17 July 2002 (17.07.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 09/911,818 24 July 2001 (24.07.2001) US

(71) Applicant: INNOVATIVE TECHNOLOGY LICENSING, LLC [US/US]; Mail Code A15, P.O. Box 1083, Thousand Oaks, CA 91358-0083 (US).

(72) Inventor: DE NATALE, Jeffrey, F.; 662 Whispering Oaks Place, Thousand Oaks, CA 91320 (US).

(84) Designated States (regional): European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR).

(Published:

without international search report and to be republished upon receipt of that report)

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: HYBRID MEMS FABRICATION METHOD AND NEW OPTICAL MEMS DEVICE

A2

WO 03/031321 A2

(57) Abstract: A new hybrid method of fabricating optical micro electro mechanical system (MEMS) devices is disclosed that uses both bulk and surface micromachining techniques, and a new optical MEMS device is also disclosed that is fabricated using the new method. The method includes the step of mounting a handle layer to one or more layers of MEMS structural material (12). Layers of structural and sacrificial material are then built up on the MEMS structural material using surface micromachining techniques (14). Drive electronics are mounted to the layers of structural and sacrificial material (17). The handle layer is removed (18) to reveal the MEMS structural layer and the sacrificial material within the various layers is dissolved (20). The new method is particularly applicable to fabricating optical MEMS devices, with the handle layer (54) being adjacent to a Si mirror layer (52). The surface micromachining layers form electrode (66) and spring structures (67, 68). Drive electronics (92) are then mounted on the layers of structural material, so that a bias can be applied to the MEMS structures. The handle layer (54) is removed from the mirror layer (52) to reveal the mirror's reflective surface, and the sacrificial material (64) is dissolved away, freeing the MEMS structures to operate. For optical or other MEMS arrays, a linking framework (70) can be included to attach the MEMS devices.

WO 03/031321

PCT/US02/22782

**HYBRID MEMS FABRICATION METHOD AND NEW OPTICAL MEMS DEVICE**

BACKGROUND OF THE INVENTION

5

Field of the Invention

This invention relates to micro electro mechanical system (MEMS) devices, and more particularly to hybrid 10 method for fabricating MEMS devices and an optical MEMS device fabricated using the new method.

Description of the Related Art

15 There has been a great deal of recent interest in the development of optical MEMS devices for applications such as projection devices, displays, fiber switches, sensors, beam steering and optical data storage devices. Often these 20 optical MEMS devices are fabricated in array configurations with each of the array elements having a micro-mirror that is individually controllable to reflect light in different directions.

One common process for manufacturing MEMS devices is by bulk micromachining using deep etch processing, which is 25 considered a subtractive fabrication technique because it involves etching away material from a single substrate layer to form the MEMS structure. One of the more common substrate materials is silicon (Si), which provides a good reflective surface for optical MEMS devices. The substrate 30 layer can be relatively thick, on the order of tens of microns, and the sophistication of this process allows for the micromachining of different structures in the substrate such as cantilevers, bridges, trenches, cavities, nozzles

and membranes. MEMS devices fabricated using this process are considered to be more robust compared to devices from other processes and they are less subject to the surface tension and forces that act upon MEMS devices during 5 processing. However, because only one layer of material is used, the complexity of the MEMS device is typically limited. Details for this process are discussed in J.K. Bhardwaj, H.J. Ashraf, Advanced Silicon Etching Using High Density Plasmas, Proc. SPIE, vol. 2639, Pg. 224 (1996 SPIE, 10 Bellingham, WA), and A.A. Aryon et al. Etching Characteristics and Profile Control in a Time Multiplexed Inductively Coupled Plasma Etcher, Solid State Sensor and Actuator Workshop, pg. 41 (June 1998, Hilton Head, SC)

The most common method of fabricating MEMS devices is 15 by surface micromachining techniques. It is considered an additive process because alternate structural layers and sacrificial spacer layers are "built-up" to construct the MEMS structure with the necessary mechanical and electrical characteristics. Polycrystalline silicon (polysilicon) is 20 the most commonly used structural material and silicon dioxide (oxide) glass is the most commonly used sacrificial material. In traditional micromachining processes, these layers are formed in polysilicon/oxide pairs on a silicon substrate isolated with a layer of silicon nitride. The 25 layers are patterned using photolithography technology to form intricate structures such as motors, gears, mirrors, and beams. As the layers are built up, cuts are made through the oxide layers and filled with polysilicon to anchor the upper structural layers to the substrate or to 30 the underlying structural layer. After the build-up process, the sacrificial (oxide) layers are removed using various techniques such as hydrofluoric acid release etching, which frees the device to move relative to the

substrate. [M.A. Michalicek, J.H. Comtois, and H.K. Schriner, Design and Fabrication of Optical MEMS Using a Four-level, Planarized, Surface Micromachined Polysilicon Process, Proc. SPIE Vol. 3276, pp. 48-55 (1998)].

5 MEMS devices fabricated using this process can be more complex than bulk micromachined devices, with the complexity of the devices determined by the number of polysilicon/oxide layer pairs. A single pair limits designers to simple sensors. Geared mechanisms require two

10 pairs wherein the polysilicon layer from the first pair is used to form the gears and the polysilicon layer from the second pair used to form the locking hub. Motorized mechanisms require a minimum of three independent layer pairs. More recently, a 5-level surface micromachining

15 technology has been developed, which allows for the fabrication of complex movable components on translatable stages that can engage and interact with other subassemblies. This technology is commonly referred to as the Sandia Ultra-planar Multi-level MEMS Technology V

20 (SUMMiT V). [M.S. Rogers and J.J. Sniegowski, Designing Microelectromechanical Systems-On-A-Chip in a 5-level Surface Micromachine Technology, 2<sup>nd</sup> Annual Int. Conf. on Engineering Design and Automation (August 1998), and M.S. Rogers and J.J. Sniegowski, 5-Level Polysilicon Surface

25 Micromachining Technology Application to Complex Mechanical Systems, Proc. 1998 Solid State Sensor and Actuator Workshop, pg. 144 (June 1998, Hilton Head, SC)]

One disadvantage of the use of the surface micromachining process for micro-mirror arrays is that the

30 thin polysilicon layers are typically used as the micro-mirrors and they can be extremely sensitive to residual stress. This can cause significant curvature in the micro-mirror, which degrades the optical quality of the

individual mirror and of the array. In addition, polysilicon micro-mirrors provide a poor reflective surface and to make them more reflective the mirror surface can be metalized with reflective thin films. However, this can 5 introduce additional film stresses that can cause further micro-mirror curvature. Also, using one of the polysilicon layers for the mirror reduces the number of available structural layers that can be used for actuators, electrodes, springs, etc., reducing the design flexibility 10 and ultimate device complexity.

Finally, the roughness of the polysilicon surface can degrade optical quality. This can be mitigated with surface polishing (as is used in SUMMIT V), or through flip-chip transfer processing. One recently developed optical MEMS 15 device has been fabricated using this flip-chip technique. [M.A. Michalicek et al., Micromirror Arrays Fabricated by Flip-Chip Assembly, SPIE vol. 3878, (20 September 1999)]. A silicon mirror is anchored to a silicon substrate by an oxide using commercial foundry processes and bonding pads 20 are deposited on it. A ceramic substrate is then patterned with gold wire and indium bonding pads to mate with the mirror pads. The mirror/substrate structure is then flip-chip mounted on the ceramic substrate and the mirror is released from the substrate by dissolving the oxide with a 25 hydrofluoric acid etch. The resulting silicon mirror surface is smooth, replicating the original substrate, but the mirror is very thin. If it is coated to make more reflective, the mirror can be stressed and deformed. Also, variations in bonding stresses can impair global micro- 30 mirror array uniformity.

Another type of optical MEMS array has been developed by first fabricating the array's drive electronics and then building micro-mirrors on the electronics. [L.J. Hornbeck,

Digital Light Processing and MEMS: Timely Convergence for a Bright Future, Plenary Session, SPIE Micromachining and Microfabrication, Vol. 2639, Pg. 2 (October 1995, Austin, TX)]. This fabrication process requires low temperatures and is strictly a surface micromachining process. This limits the flexibility in changing the process to fabricate different structures for different applications. Also, like the polysilicon micro-mirrors, these micro-mirrors are relatively thin and can be susceptible to deformation under stress. For instance, any coating placed on the mirror to increase its ability to reflect must be very thin or the mirror can deform. Also, by being so thin there is a danger that the mirrors can misregister, degrading the array's performance.

15

SUMMARY OF THE INVENTION

The present invention provides a new method for fabricating MEMS devices and a new optical MEMS device fabricated using the new method. The new method is a hybrid 20 that combines bulk deep-etch and surface micromachining fabrication techniques to include the advantages of both.

The new hybrid method includes the step of providing a layer of bulk micromachining material and then building 25 up layers of structural and sacrificial material on the bulk micromachining material using surface micromachining techniques. A substrate with drive electronics is then mounted to the layers of structural and sacrificial material. The bulk material is then micromachined and the sacrificial material within the various surface layers is 30 dissolved.

The new method is particularly applicable to fabricating optical MEMS devices, beginning with the step of mounting a handle layer to a mirror layer, to hold and

protect the mirror layer. Layers of structural and sacrificial materials are then built on the mirror layer using surface micromachining techniques, with the structural material forming electrode and spring structures. Drive electronics are then mounted on the layers of structural material so that a bias can be applied to the electrode and spring structures. The handle layer is removed from the mirror layer to reveal the mirror's reflective surface, and the sacrificial material is dissolved from the surface micromachining layers, freeing the electrode and spring structures to operate.

For optical or other MEMS device arrays, a linking framework can be included to link the individual MEMS elements to one another. In the above method, the linking framework is preferably built-up on the layers of structural and sacrificial material prior to mounting the drive electronics. The linking framework is also built up using the same surface micromachining techniques. The drive electronics are then mounted to the linking framework to provide mechanical and electrical interconnection with the MEMS structure.

The invention also provides a new optical MEMS device fabricated using a hybrid fabrication process including a mirror fabricated using bulk micromachining techniques and a substrate with drive electronics to activate the mirror. The device also includes a spring structure and an electrode fabricated using surface micromachining techniques. The spring structure is connected between the substrate and mirror, holding the mirror above the substrate. The electrode is mounted on the substrate between said mirror and said substrate. A bias applied across the mirror and electrode activates the device, causing the mirror to be drawn toward the electrode against

the action of the spring structure.

The new hybrid method and new optical MEMS device provide many advantages over conventional methods and devices. For optical MEMS devices the micro-mirror is 5 formed from the subtractive bulk deep etch process wherein the handle layer is removed from the Si layer. The resulting micro-mirror is thicker and more rugged than those formed from surface micromachining processes and provides a good reflective surface. The device also 10 includes MEMS structures that are built-up using surface micromachining techniques. This allows for the fabrication of more complex MEMS structures compared to purely bulk micromachined devices. By including a linking framework for MEMS arrays, global uniformity can be enhanced.

15 These and other further features and advantages of the invention will be apparent to those skilled in the art from the following detailed description, taken together with the accompanying drawings, in which:

20 BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a flow diagram for the new hybrid method of fabricating MEMS devices;

FIG. 2 is a flow diagram for the new hybrid method used to fabricate optical MEMS devices;

25 FIG. 3 is a sectional view of a mirror layer on an anchor layer for the new optical MEMS device;

FIG. 4 is a sectional view of the drive and spring structure built up on the mirror layer shown in FIG 3;

FIG. 5 is a sectional view of the linking framework 30 built up on the structure of FIG. 4;

FIG. 6 is a sectional view of the structure in FIG. 5 after flipping for flip-chip mounting;

FIG. 7 is a sectional view of the structure in FIG. 6

mounted on a substrate with drive electronics;

FIG. 8 is a sectional view of the structure in FIG. 7 with the handle layer removed;

FIG. 9 is a sectional view of the structure in FIG. 8 with the sacrificial layers dissolved; and

FIG. 10 is a perspective view of an array of optical MEMS devices fabricated using the new hybrid fabrication process.

10 DETAILED DESCRIPTION OF THE INVENTION

Hybrid Method

FIG. 1 is a flow diagram 10 for the new hybrid method of fabricating MEMS devices in accordance with the present 15 invention to fabricate a single MEMS device or an array of MEMS devices. The following primarily describes a new method for fabricating a single MEMS device but the method is equally applicable to fabricating an array of MEMS devices.

20 In the first step 12, a layer of MEMS structural material is mounted to a "handle" layer by a sacrificial mounting layer/material. The handle layer can be made of many different materials and are used to hold and protect the MEMS structural layer while the surface micromachining 25 layers are built upon it (see below). For example, the MEMS structural layer can be a mirror layer for an optical MEMS device. When fabricating an optical MEMS array, numerous mirror layers are used. The handle layer along with the mounting layer/material, hold and protect the surface of 30 the mirror layer during later fabrication steps, and once the handle and oxide layers are removed the reflective surface of the mirror is revealed. In other embodiments more than one handle layer and MEMS structural material can

be used for a single MEMS device.

In the next step 14, surface micromachining layers are built-up on the MEMS structural layer using the above-described surface micromachining techniques. 5 Polysilicon/oxide layer pairs are deposited to build-up various MEMS structures. Many different structures can be built-up using this process, including but not limited to sensors, gears, and springs and electrodes for optical MEMS devices, and this step can use the recently developed 10 SUMMiT V 5-layer surface micromachining process described above. Many standard growth processes, such as reaction furnace growth, can be used to build-up the layers and different materials can be used for the layers such as Polycrystalline silicon, silicon dioxide, silicon germanium 15 or silicon carbide.

In the next step 16, the MEMS structure from step 14 is flipped, and in step 17 it is mounted on a substrate having drive and/or sensory electronics or connection to the electronics. Contacts can be included on the MEMS 20 structure or the drive/sensory substrate, either of which provide mechanical and electrical connections between the substrate and the MEMS structure. This allows a bias to be applied to structure or a signal sent from the structure to the substrate.

25 In the next step 18, the handle layer is removed, revealing the mounting layer/material between the handle layer and the MEMS structural layer. The oxide material can then be chemically etched away, revealing the surface of the MEMS structural layer. Alternatively, the mounting 30 layer/material can be etched first and the handle layer lifted from the MEMS structural layer.

In the final step 20, the sacrificial oxide material in the polysilicon/oxide layer pairs is dissolved. The

spaces left by the dissolved oxide material allow the remaining polysilicon MEMS structures to move and also provides mechanical and electrical isolation between the structures. For instance, in optical MEMS devices an 5 electrode can be both electrically and mechanically isolated from spring structures that hold the MEMS micro-mirror. A bias can be applied across the electrode and mirror so that the mirror moves up and down on the spring structure while the electrode remains stationary.

10 When fabricating MEMS arrays, numerous devices are built-up using steps 12 and 14 and a linking framework is included to link the individual MEMS devices. In step 22 the framework is built up on the spring and drive structure of the individual MEMS devices by surface micromachining 15 techniques, linking them together. The framework also includes structural and sacrificial polysilicon/oxide pairs. In the final step 20, the framework's sacrificial oxide material is dissolved along with the other sacrificial materials in the structure. When the structure 20 is mounted to the sensor/drive electronics in step 16, the framework is arranged between the electronics and the surface micromachining layers. A bias applied to the MEMS devices, or a signal sent to the substrate from the devices, passes through the linking framework.

25

#### Hybrid Method for Fabricating Optical MEMS

FIG. 2 shows a flow diagram 30 for the new hybrid method in accordance with the present invention, used to fabricate an optical MEMS device. As above, the following 30 primarily describes fabrication of an individual MEMS device but it is equally applicable to fabricating optical MEMS arrays.

In step 32, the MEMS structural layer is mounted on an

insulator layer. For optical MEMS devices the MEMS layer serves as the devices' micro-mirror and it can be any material that provides a high-quality reflective surface, with the preferred layer being silicon (Si).

5 For this step, commercially available silicon on insulator (SOI) wafers can be used and are available from many sources such as: BCO Technologies, plc; SEH America, Inc.; and Virginia Semiconductor, Inc. SOI wafers commonly include a thin Si layer and a thicker Si handle layer

10 sandwiching an insulating oxide material. The surface of the thin Si layer adjacent to the oxide material serves as the reflective micro-mirror surface and the thicker Si layer and oxide material serve as a handle layer to hold and protect the Si mirror layer.

15 In step 34, the spring and drive structures are built on the SOI wafer using the surface micromachining techniques, with the polysilicon/cxide layer pairs being on the surface of the thin Si layer opposite the Si handle layer. The layer pairs form the electrode to activate the

20 mirror and the spring structure that allows the mirror to move when a bias is applied to the MEMS device and to return when the bias is removed.

25 In optional step 36, the framework to link a number of optical MEMS devices in an array is built on the spring and drive structure using the same surface micromachining techniques. The framework generally uses 1 or 2 polysilicon/oxide layer pairs and provides a rigid linkage between the array of optical MEMS devices so that the MEMS

30 micro-mirrors can be better aligned and less sensitive to bonding stress.

In step 38 the MEMS structure from step 34 (or alternatively step 36) is flipped. Metallic contacts can be deposited on its bottom layer of the structure before or

after flipping. In step 39, the structure is mechanically and electrically attached to substrate with drive electronics using flip-chip bonding techniques. One of the easiest and most common methods for attaching is by solder. 5 However, there is a limit to how small the solder pads can be when used for electrical connections. For smaller optical MEMS devices other attachment methods can be used such as Indium columns.

10 In step 40, the handle (thick Si) layer, which is now the top layer of the structure, is removed. As described above, different removal methods can be used but in this embodiment the layer is mechanically grinded down to the oxide layer below it and then the oxide layer is dissolved using a chemical etch.

15 In the final step 42, the sacrificial oxide material in the spring and drive structure and the linking framework is dissolved using a method that dissolves the oxide without damaging the polysilicon or silicon materials in the MEMS structure. A suitable method is chemical etching 20 using a hydrofluoric acid etch.

When the etching process is complete, the mirror and its spring structures are free to move and the drive structure is mechanically and electrically isolated from the spring structures. As more fully described below, a 25 bias can be applied across the mirror and drive structure, causing an electrostatic attraction between the two. This causes the mirror to be drawn toward the drive structure, which in turn compresses the spring structures. When the bias is removed the electrostatic force is also removed and 30 the spring structures are free to return the mirror to its neutral position.

Optical MEMS Device Fabricated Using New Method

FIGs. 3-9 show a new optical MEMS device fabricated using the new hybrid method described above. FIG. 3 shows 5 a sectional view of SOI wafer 50 provided in accordance with step 32 above. The SOI wafer has a thin Si layer 52 anchored to a handle Si layer 54 by an oxide layer 56. The handle layer 54 is generally thicker than the Si layer 52, with a suitable thickness being approximately 500 microns. 10 The Si layer 52 serves as the MEMS device's micro-mirror and can be less than 10 microns with the preferred range of thicknesses being approximately 5-20 microns, although other thicknesses will also work. If it is too thick, the micro-micro-mirror can have too great a mass to move 15 quickly and if it is too thin, it can lose its rigidity.

FIG. 4 shows a sectional view of the SOI wafer 50 with the surface micromachining layers 60 built on the surface of the silicon layer 52 opposite the handle layer 56, in accordance with step 34 above. There are four layers 60a-d 20 that correspond to two polysilicon/oxide pairs. Each of the four layers has polysilicon structural material 62 and oxide sacrificial material 64. The four layers are built-up on the silicon layer 52 and the first layer 60a is commonly an oxide layer. It is cut at various locations so that 25 polysilicon can be included to provide a structural connection between the second layer 60b and/or to the Si layer 52. The second layer 60b is commonly a polysilicon layer and during deposition of this layer, polysilicon is introduced into the cut areas of the first layer 60a. The 30 second polysilicon layer can also be cut so that sacrificial oxide can be included when the next layer 60c is deposited. The next layer 60c is an oxide and the final layer 60d is a polysilicon, both of which can also be cut

to include material from the adjacent layers.

The layers can be cut during build-up in various ways to construct structures that perform different functions. In layers 60a-d, the polysilicon material 62 forms a drive 5 electrode 66 and spring structures 67 and 68. The layers can have different thicknesses depending on the number of layer pairs used. If the SUMMiT V surface micromachining technique is used to deposit layers 60a-d, the thicknesses of the oxide layers can be in the range of approximately 10 0.5-2.0 microns and the polysilicon layers can be in the range of approximately 0.3-2.5 microns.

FIG. 5 shows the structure of FIG. 4 with a framework linking structure 70 built on the spring and drive structure 60, in accordance with step 36 above. The 15 linking framework is a continuous structure across the array of MEMS devices and is built-up on the devices after the spring and drive structures have been built-up on each of the devices. The structure 70 is also fabricated using surface micromachining techniques with 1 or 2 20 polysilicon/oxide layer pairs. The structure 70 links the individual optical MEMS devices in an array.

The number of layers used for the linking framework 70 directly impacts the number of layers that can be used for the electrode and spring structures 60. By using 2 layer 25 pairs for the linking framework 70, up to three layers can be used for the electrode and spring structure 60. If only 1 layer pair is used, up to four layers can be used for the structure 60. If the optical MEMS device is not to be linked in an array, up to five layer pairs can be used for 30 the spring and drive structures. Another advantage of this structure is that the Si mirror layer 52 can serve as the substrate so that all 5 of the layers can be used for surface micromachining. In conventional 5 layer surface

micromachining, the bottom layer commonly serves as the substrate, leaving only 4 layers.

FIG. 6 shows the structure of FIG. 5 after it is flipped in accordance with step 38 above. Contacts 82 can be deposited on the linking framework structure 70 using known metalization processes, either before or after flipping. If there is no linking framework then the contacts are deposited on the electrode and spring structures.

FIG. 7 shows the structure of FIG. 6 mounted to a conventional substrate with drive electronics 92. The substrate 92 also has contact pads 94, 98 and 99, which align with the contact pads 82 on the linking framework 70. The aligned contacts provide mechanical and electrical connection between the framework 70 and the substrate 92. During operation, a electrical signal that is applied across contact pads 94 passes to the electrode 66 and an electrical signal applied across contacts 98 and 99 passes to the spring structures 68 and 67 respectively, and on to the micro-mirror layer 52.

The structure in FIG. 7 shows the optical MEMS device after the build-up process is complete. In the steps that follow, various layers are removed or dissolved, exposing the mirror and freeing the MEMS structures to move and operate.

FIG. 8 shows the structure of FIG. 7 with the handle layer 54 removed in accordance with step 39 above, leaving the oxide layer 56 on the Si mirror layer 52. As above, the handle layer is removed by a mechanical method such as grinding. Alternatively, the oxide layer 56 can first be dissolved by chemical etching, thereby releasing the handle layer.

Finally, FIG. 9 shows the structure of FIG. 8 after

the remaining oxide sacrificial material has been dissolved by a chemical etch in accordance with step 40 above. This figure further illustrates the resulting new optical MEMS device fabricated using the new method. To create the 5 electrostatic tension, a bias is applied from the substrate 92 across contacts 94 and both or either of contacts 98 and 99. The bias at contacts 98 and/or 99 passes to the micro-mirror 52 and as described above, the bias creates an electrostatic tension between the micro-mirror 52 and the 10 electrode 66. The micro-mirror 52 is drawn down toward the electrode 66, which compresses the spring structures 67 and 68. When the bias is removed, the spring structures 67 and 68 return the mirror 52 to its neutral location.

FIG. 10 shows the new optical MEMS device in the six- 15 element array 110. Each of the MEMS devices 112 has its own micro-mirror 113, electrode 114 and spring structures 116, 118. A single linking framework 120 extends across the array 110, linking the individual MEMS devices to one another. The substrate with drive electronics 122 is 20 mounted to the linking framework 120 so that each of the MEMS devices can be separately actuated by a bias across the electrode 114 and micro-mirror 113 at the particular device 112.

Although the present invention has been described in 25 considerable detail with reference to certain preferred configurations thereof, other versions are possible. For instance, after the handle layer and mounting layer/material are removed, the MEMS structural layer(s) can be further processed using bulk micromachining 30 techniques to form cantilevers, bridges, trenches, cavities, nozzles or membranes in the layer(s). The steps in above methods can occur in a different order and other steps can be included. The above optical MEMS device is one

of the many different types that can be fabricated in accordance with this invention, with one example of an alternative device having mirrors that are tipped when actuated. Therefore, the spirit and scope of the appended 5 claims should not be limited to the preferred versions of the invention described in the specification.

**I CLAIM:**

1. A hybrid method (10) for fabricating micro electro mechanical system (MEMS) devices, comprising:

- 5        mounting a handle layer adjacent to a layer of MEMS structural material (12);

building up layers of structural and sacrificial material on said layer of MEMS structural material by surface micromachining (14);

- 10      mounting drive electronics to said layers of structural and sacrificial material (17);

removing said handle layer from said MEMS structural material (18); and

dissolving away said sacrificial material (20).

- 15      2. The method (10) of claim 1, wherein said handle layer is mounted to said layer of MEMS structural material (12) by a sacrificial mounting layer/material.

3. The method (10) of claim 1, wherein said handle layer is removed from said MEMS structural material (18) by grinding.

4. The method (10) of claim 2, wherein said handle layer is removed from said MEMS structural material (18) by dissolving said mounting layer/material with a chemical etch, freeing said handle layer.

- 5      5. The method of claim 1, wherein said drive electronics are mounted to said layers of structural and sacrificial material (17) by flip-chip mounting.

6. The method (10) of claim 1, wherein said sacrificial

material is dissolved (20) by chemical etching.

7. The method (10) of claim 1, wherein said MEMS device is in an array of MEMS devices, said method comprising the addition step of building up a linking framework (22) on said structural and sacrificial material of said MEMS devices before the mounting of said drive electronics.

8. A hybrid method of fabricating optical micro electro mechanical system (MEMS) devices, comprising:

mounting a handle layer (54) adjacent to a mirror layer (52), to hold and protect said mirror layer (52);

5 building up layers of structural and sacrificial materials (60) on said mirror layer (52) using surface micromachining, said structural material (66,67,68) forming MEMS structures;

mounting drive electronics (92) to said layers of 10 sacrificial and structural material (60), said drive electronics (92) mounted so that a bias can be applied to said MEMS structures;

removing said handle layer (54) from said mirror layer (52); and

15 dissolving away said sacrificial material (64), freeing said MEMS structures to operate under said bias.

9. The method of claim 8, wherein said mirror layer (52) and handle layer (54) are silicon (Si) that together form a silicon on insulator (SOI) substrate.

10. The method of claim 8, wherein said surface micromachining structural material (66,67,68) forms spring structures and an electrode.

11. The method of claim 10, wherein said bias is applied across said mirror (52) and said electrode (66), said spring structure (67,68) allowing said mirror layer (52) to move when said bias is applied and return when said bias is 5 removed.

12. The method of claim 10, wherein said spring structure (67,68) runs between said drive electronics (92) and said mirror (52) to hold said mirror (52) above said drive electronics (92) after said sacrificial material is 5 dissolved.

13. The method of claims 10, wherein said electrode (66) is in electrical connection with said drive electronics (92) and is arranged between said drive electronics (92) and said mirror (52). 5

14. The method of claim 11, wherein an electrostatic tension is created between said electrode (66) and said mirror (52) when a bias is applied across the two, said electrostatic tension drawing said mirror (52) toward said 5 drive electronics (92).

15. The method of claim 8, wherein said handle layer (54) is mounted to said mirror (52) by a sacrificial mounting layer/material (56).

16. The method of claim 8, wherein said handle layer (54) is removed from said mirror layer (52) by grinding.

17. The method of claim 15, wherein said handle layer (54) is removed from said mirror layer (52) by dissolving said mounting layer (56) with a chemical etch, freeing said

handle layer.

5

18. The method of claim 8, wherein said drive electronics (92) are mounted to said layers of structural and sacrificial (60) material by flip-chip mounting.

19. The method of claim 8, wherein said sacrificial material (56) in said layers of structural and sacrificial material (60) is dissolved by chemical etching.

20. The method of claim 8, wherein said optical MEMS device (112) is one of a plurality of MEMS devices in an array (110), said method comprising the addition step of building up a linking framework (120) on said layers of structural and sacrificial material before said step of mounting said drive electronics, said linking framework (120) arranged between said layers of structural and sacrificial material and said drive electronics.

21. The method of claim 20, wherein said linking framework (120) is formed by building up additional layers of structural and sacrificial materials.

22. An optical micro electro mechanical system (MEMS) device fabricated using a hybrid fabrication process, comprising:

5 a mirror (52) fabricated using bulk micromachining;

a substrate with drive electronics (92) to activate said mirror; and

a spring structure (67,68) and an electrode (66) fabricated using surface micromachining techniques, said spring structure (67,68) connected between said substrate (92) and mirror (52), and holding said mirror (52) above

10

15 said substrate, said electrode (66) mounted on said substrate (92) between said mirror (52) and said substrate (92), a bias across said mirror (52) and said electrode (66) causing said mirror (52) to be drawn toward said electrode (66).

23. The device of claim 22, further comprising a linking framework (70) between substrate (92) and said spring structure (67,68) and electrode (66), said framework (70) connecting said MEMS device to other MEMS devices in an array.

24. An array of optical micro electro mechanical system (MEMS) devices, comprising:

a plurality of optical MEMS devices (112), each comprising;

5 a mirror (113) fabricated using bulk micromachining;

10 a spring structure and an electrode (114) fabricated using surface micromachining techniques, said spring structure connected to said mirror (113);

a linking framework (120) attached to said optical MEMS devices (112) to link them adjacent to one another, each said spring structure and electrode (114) connected to said framework (120), said electrode (114) arranged between said framework (120) and said mirror (113); and

15 a substrate (122) with drive electronics mounted to said linking framework (120) to apply a bias across spring structure and electrode (114) causing said mirror (113) to be drawn toward said electrode (114).

25. A hybrid method for fabricating micro electro mechanical system (MEMS) devices, comprising:

building up layers of structural and sacrificial material on a layer of bulk micromachining material by 5 surface micromachining (14);

mounting drive electronics to said layers of structural and sacrificial material (17);

etch micromachining said layer of bulk micromachining material (18); and

10 dissolving away said sacrificial material (20).

26. The method of claim 25, wherein said bulk micromachining material comprises a handle layer (54) mounted to layer of MEMS structural material by a sacrificial mounting layer/material (56).

5

27. The method of claim 26, wherein said MEMS structural material is a micro mirror (52).

28. The method of claim 25, wherein said sacrificial material (56) is dissolved by chemical etching.

29. The method of claim 25, wherein said MEMS device is in an array (110) of MEMS devices (112), said method comprising the addition step of building up a linking framework (120) on said structural and sacrificial material 5 of said MEMS devices before the mounting of said drive electronics, said linking framework (120) attaching said MEMS devices.

WO 03/031321

PCT/US02/22782

1/7

FIG.1

WO 03/031321

PCT/US02/22782

3/7

FIG. 5

FIG. 6

FIG. 7

FIG.10

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

17 April 2003 (17.04.2003)

PCT

(10) International Publication Number

WO 03/031321 A3(51) International Patent Classification<sup>5</sup>: B81B 3/00, G02B 25/08

(74) Agents: HEYBL, Jaye, G. et al.; Koppel, Jacobs, Patrick &amp; Heybl, 555 S. Charles Drive, Suite 107, Thousand Oaks, CA 91360 (US).

(81) Designated State (national): JP.

(22) International Filing Date: 17 July 2002 (17.07.2002)

(84) Designated States (regional): European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR).

(25) Filing Language: English

(85) Publication Language: English

(30) Priority Data: 09/911,818 24 July 2001 (24.07.2001) US

(86) Date of publication of the international search report: 9 October 2003

(71) Applicant: INNOVATIVE TECHNOLOGY LICENSING, LLC [US/US]; Mail Code A15, P.O. Box 1083, Thousand Oaks, CA 91358-0083 (US).

(87) with international search report

— before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

(72) Inventor: DE NATALE, Jeffrey, F.; 662 Whispering Oaks Place, Thousand Oaks, CA 91320 (US).

(88) Date of publication of the international search report: 9 October 2003

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: HYBRID MEMS FABRICATION METHOD AND NEW OPTICAL MEMS DEVICE

WO 03/031321 A3

(57) Abstract: A new hybrid method of fabricating optical micro electro mechanical system (MEMS) devices is disclosed that uses both bulk and surface micromachining techniques, and a new optical MEMS device is also disclosed that is fabricated using the new method. The method includes the step of mounting a handle layer to one or more layers of MEMS structural material (12). Layers of structural and sacrificial material are then built up on the MEMS structural material using surface micromachining techniques (14). Drive electronics are mounted to the layers of structural and sacrificial material (17). The handle layer is removed (18) to reveal the MEMS structural layer and the sacrificial material within the various layers is dissolved (20). The new method is particularly applicable to fabricating optical MEMS devices, with the handle layer (54) being adjacent to a Si mirror layer (52). The surface micromachining layers form electrode (66) and spring structures (67, 68). Drive electronics (92) are then mounted on the layers of structural material, so that a bias can be applied to the MEMS structures. The handle layer (54) is removed from the mirror layer (52) to reveal the mirror's reflective surface, and the sacrificial material (64) is dissolved away, freeing the MEMS structures to operate. For optical or other MEMS arrays, a linking framework (70) can be included to attach the MEMS devices.

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                   | International Application No<br>PCT/US 02/22782                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 B81B3/00 602B26/08                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 B81B G02B                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, INSPEC, PAJ                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| Category *                                                                                                                                                                                                                                    | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                | Relevant to claim No.                                                          |

| X                                                                                                                                                                                                                                             | US 5 699 181 A (CHOI BUM-KYOO)<br>16 December 1997 (1997-12-16)<br>column 2, line 45 -column 4, line 12;<br>figures 3,4<br>---                                                                                                                                                                                                                                                                    | 1-21                                                                           |

| Y                                                                                                                                                                                                                                             | ---                                                                                                                                                                                                                                                                                                                                                                                               | 22-29                                                                          |

| Y                                                                                                                                                                                                                                             | SU G D J ET AL: "Surface-micromachined 2D optical scanners with optically flat single-crystalline silicon micromirrors", SILICON-BASED AND HYBRID OPTOELECTRONICS III, SAN JOSE, CA, USA, 23-24 JAN. 2001, PROCEEDINGS OF THE SPIE - THE INTERNATIONAL SOCIETY FOR OPTICAL ENGINEERING, 2001, SPIE-INT. SOC. OPT. ENG, USA, PAGE(S) 46 - 53, XP009013719<br>ISSN: 0277-786X<br>figures 3,6<br>--- | 22-29                                                                          |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                   | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents:                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| *A* document relating to a general state of the art which is not considered to be of particular relevance                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| *E* earlier document but published on or after the international filing date                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| *U* document which may throw doubt on priority, claims or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| *O* document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| *P* document published prior to the international filing date but later than the priority date claimed                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |