(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3553212号

(P3553212)

(45) 発行日 平成16年8月11日(2004.8.11)

(24) 登録日 平成16年5月14日(2004.5.14)

(51) Int.CI.<sup>7</sup>

F 1

H03K 7/08

H03K 7/08

F

H02M 3/155

H02M 3/155

P

請求項の数 2 (全 9 頁)

(21) 出願番号 特願平7-166312

(22) 出願日 平成7年6月30日(1995.6.30)

(65) 公開番号 特開平8-195659

(43) 公開日 平成8年7月30日(1996.7.30)

審査請求日 平成13年8月24日(2001.8.24)

(31) 優先権主張番号 08/347863

(32) 優先日 平成6年12月1日(1994.12.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 000002325

セイコーインスツルメンツ株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100079212

弁理士 松下 義治

(72) 発明者 柴田 公男

千葉県千葉市美浜区中瀬1丁目8番地 セイコー電子工業株式会社内

審査官 江嶋 清仁

(56) 参考文献 特開平02-100411 (JP, A)

(58) 調査した分野(Int.CI.<sup>7</sup>, DB名)

H03K 7/08

H02M 3/155

(54) 【発明の名称】パルス巾変調器及びパルス巾変調型スイッチング電源

## (57) 【特許請求の範囲】

## 【請求項1】

発振回路からの信号をゲートの入力とし、第1の電源はソースに接続された第1導電型の第1のMOSトランジスタと、

前記発振回路からの信号をゲートの入力とし、ドレインが前記第1のMOSトランジスタのドレインと接続された第2導電型の第2のMOSトランジスタと、

パルス巾変調器のDC入力としての電圧レベル可変の電圧をゲートの入力とし、ドレインが前記第2のMOSトランジスタのソースに接続され、ソースが第2の電源に接続された第2導電型の第3のMOSトランジスタと、

一端が前記第1の電源に接続され、他端が前記第1及び第2のトランジスタの前記ドレインに接続されたコンデンサと、

前記コンデンサの電圧と、基準電圧とを比較する比較回路とから構成され、

前記比較回路の出力と前記発振回路からの信号の反転信号との、反転論理和を出力とし、前記パルス巾変調器のDC入力によって、前記コンデンサの充電又は放電する電流値を制御することを特徴とするパルス巾変調器。

## 【請求項2】

請求項1のパルス巾変調器を有し、更に

出力電圧を分圧する抵抗分圧器と、

前記分圧器の出力電圧と前記基準電圧を比較・增幅し、前記パルス巾変調器に入力する演算增幅器と、

10

20

前記パルス巾変調器の出力を得て、電圧変換、整流、平滑化するスイッチング素子による請求項1記載のパルス巾変調器を用いたスイッチング電源。

【発明の詳細な説明】

【0001】

【産業上の利用分野】

この発明は、電子機器に使用するスイッチング電源のうちのパルス巾変調器およびこれを有するスイッチング電源、特に低電力のスイッチング電源に関する。

【0002】

【従来の技術】

従来、この種のパルス巾変調器は発振器からのランプ波形と直流電圧を比較する電圧比較器から構成されており、該電圧比較器のオフセット電圧すなわちランプのスタート電圧の不安定を補うためアナログ的調整手段が必要であった。

10

【0003】

【発明が解決しようとする課題】

既に説明したように、上記のパルス巾変調器はランプ波形を発生する発振器を必要とするが、該発振器は電子機器のシステムの発振器との同期をとるのが容易ではない。そのため、パルス巾（デューティー比）の制御が困難であった。

【0004】

また、上記発振器によるノイズのためにシステム全体のS/N比が悪かった。さらに、上記アナログ的調整手段は回路が複雑となり、上記電圧比較器はスイッチング動作時でない安定時でも電力を消費する構成なので消費電流を少なくすることが困難であった。

20

【0005】

また比較器の初段の差動増幅器はトランジスタとの特性の整合をとるために、ICの設計においては特別の配慮が必要であった。

本発明は上記課題を解消してパルス巾の細かい制御をし、低動作電圧、低消費電流、低雑音の、しかも小型のスイッチング電源を提供することを目的とする。

【0006】

【課題を解決するための手段】

本発明が上記目的を達成するために採用した手段は、発振器からのクロック信号の電位に応じてコンデンサの電荷を放電する第一の回路と、クロック信号の反転電位に応じてコンデンサに充電を開始する第二の回路と、入力電圧レベルに応じてコンデンサの充電電流を可変する第三の回路と、コンデンサに接続され、該コンデンサの電位があるしきい値を越えると出力が反転する第四の回路と、第四の回路の出力と、クロック信号を入力とする論理ゲートからなることを特徴とする。また、上記構成から成るパルス巾変調器を有し、出力電圧を分圧する抵抗分圧器の電圧と、基準電圧源の電圧を比較し増幅する演算増幅器と、パルス巾変調器の出力を得て、電圧変換、整流、平滑化するスイッチング電源回路素子からなることを特徴とする。

30

【0007】

【作用】

上記の構成であるので、本発明のパルス巾変調器及びパルス巾変調型スイッチング電源は、簡単な回路構成で、スイッチング動作時のパルスの、立ち上がり、立ち下がりの短時間とコンデンサの充電時間にのみ電力を消費するだけなので消費電力を少なくできる。また、コンデンサを内蔵できるので、小型の電源が実現できる。

40

【0008】

【実施例】

本発明の実施例を図に基づいて説明する。

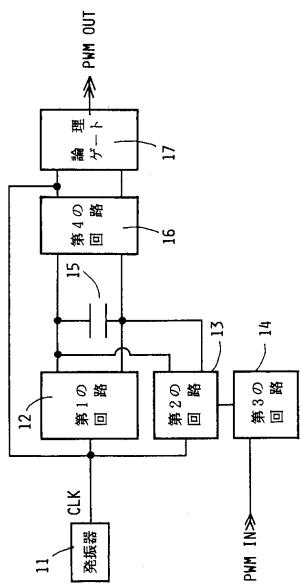

図1は本発明のパルス巾変調器のブロック図である。発振器11は第一の回路12及び第二の回路13に接続されており、該第二の回路13は、パルス巾変調器のDC入力（PWM IN）を入力とする第三の回路14に接続されている。第一の回路12と第四の回路16の間にはコンデンサ15が並列に接続されている。第四の回路16の出力は論理ゲー

50

ト17に接続され、さらに該論理ゲート17の入力は発振器11とも接続されている。論理ゲート17の出力がパルス巾変調器の出力(PWM OUT)となる。

【0009】

発振器11は上述のようにパルス巾変調器の内部に置く場合(以下内部発振器という)と、全体を構成する電子機器の発振器(以下外部発振器という)の信号を使う場合がある。従来のパルス巾変調器ではランプと矩形波の二つが必要なうえにさらにランプ電圧を調整しなければならないので、その対策の一つとして内部発振器を外部のトリガー信号(システムクロック)でランプ波形を発生し同期をとっていたが、同期できる周波数範囲が狭い欠点があった。

【0010】

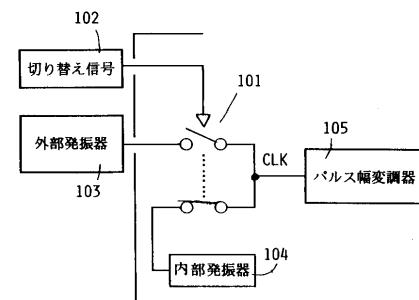

図10は内部発振器と外部発振器を切り換える実施例のブロック図で、切り替えスイッチ101が切り替え信号102によって切り換えられ外部発振器103か内部発振器104かを選択するし、パルス巾変調器105にクロック信号を送ることができる。

【0011】

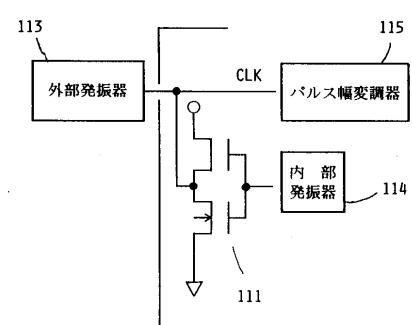

図11は内部発振器と外部発振器を切り換える他の実施例のブロック図で、外部発振器113と内部発振器114をインバータ111を介して接続すれば、外部発振器113の出力が内部発振器114の出力を強制的に打ち負かしてパルス巾変調器115に外部発振器113からのクロック信号を送る。一方、外部発振器113の信号を止めれば、内部発振器114からの信号をクロック信号としてパルス巾変調器に送ることができる。

【0012】

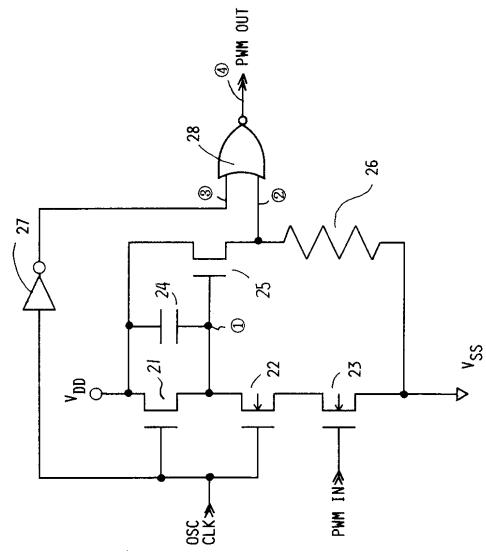

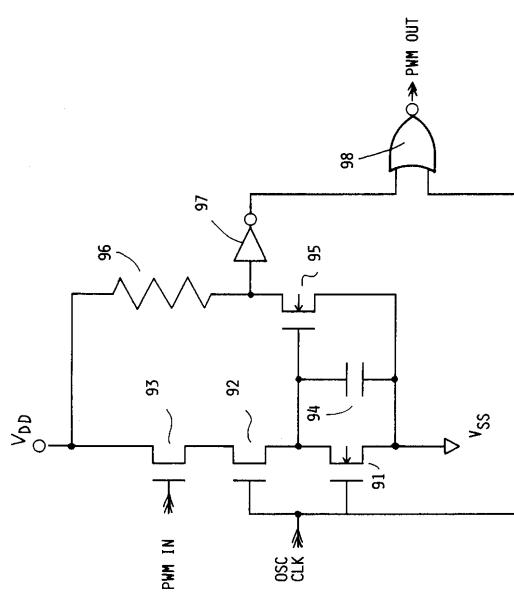

図2は図1のブロック図に実際の回路を当てはめた本発明のパルス巾変調器の回路図である。第一の回路12にはP型トランジスタ21、第二の回路13にはN MOSトランジスタ22をそれぞれ当てはめ図2のように相補型MOSトランジスタとして接続されている。該相補型MOSトランジスタの出力とVDDとの間にはコンデンサ24が接続されている。第三の回路14にはN MOSトランジスタ23を当てはめ、第四の回路16にはPMOSトランジスタ25と抵抗26が当てはめられている。論理ゲート17にはインバータ27とNOR回路28が当てはめられている。

【0013】

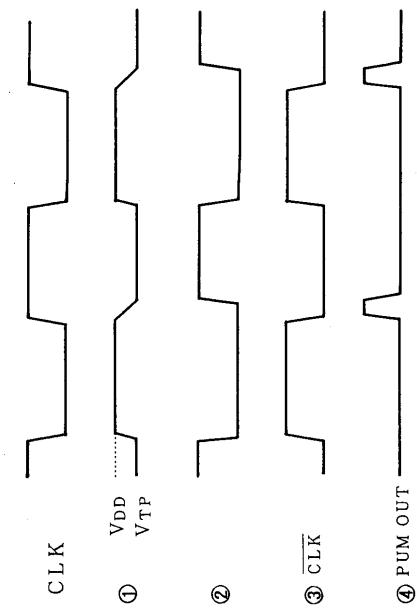

つぎに、本発明のパルス巾変調器の動作を図3のタイムチャート及び図2の回路図を参照して説明する。発振器からの出力OSC CLKがLowのとき、PMOSトランジスタ21はコンデンサ24を低インピーダンスで短絡させ、その電荷を放電させて、コンデンサ24の電圧1はVDDとなる。この状態からCLKがHighになった瞬間トランジスタ21はオフ、トランジスタ22がオンとなり、N MOSトランジスタ23のゲート電圧がしきい値電圧を越えたとき、該トランジスタのドレイン電流はN MOSトランジスタ22を通ってコンデンサ24に充電を開始する。コンデンサ24が充電されその電圧がPMOSトランジスタ25のしきい値電圧を越えたときトランジスタ25はオンになりその出力2はHighになる。また、上記CLKがHighになると、インバータ27の出力3はLowになり、この3と2を入力としてNOR回路28の出力4がパルス巾変調器の出力(PWM OUT)となる。

【0014】

N MOSトランジスタ23のドレイン電流IDは、そのゲート・ソース間電圧VGSとトランジスタのサイズW/Lで以下の式で与えられる。

$$0 < V_{DS} \leq (V_{GS} - V_T) \text{ のとき}$$

$$I_D = K_p (W/L) [(V_{GS} - V_T) - V_{DS}/2] V_{DS}$$

$$0 < (V_{GS} - V_T) \leq V_{DS} \text{ のとき}$$

$$I_D = K_p (W/L) (V_{GS} - V_T)$$

ここで、V<sub>DS</sub>はドレインソース電圧、V<sub>T</sub>はしきい値電圧、K<sub>p</sub>は製造プロセスによって与えられる定数、W/Lはトランジスタのゲートの巾/長さである。パルス巾を変

10

20

30

40

50

えるには PWM IN の電圧レベルを変えることによってトランジスタ 23 のドレイン電流が変化し、コンデンサ 24 に流れる充電電流が変化する。即ち、PWM IN の電圧レベルが増加するとコンデンサ 24 の充電時間が短くなり PWM OUT のパルス巾が短くなる。また、PWM IN の電圧レベルが減少すると、パルス巾は長くなり、トランジスタ 23 のしきい値以下まで減少すると、パルス巾は CLK の High 時間と同じになる。

#### 【0015】

コンデンサ 24 の充電時間  $t$  は以下のようになる。

$$t = (C) (V_{TP}) / I_D$$

ここで、C はコンデンサの容量、 $V_{TP}$  は PMOS トランジスタ 25 のしきい値電圧である。

10

#### 【0016】

このような構成にすることにより、短時間に於けるトランジスタ 25 のゲート電圧ードレイン電流特性は安定であるから、トランジスタ 25 のしきい値電圧を基準電圧と見なすことができ、パルス巾を制御できる。

実際に実現できたパルス巾は  $C = 2.5 \text{ pF}$ ,  $V_{TP} = 0.5 \text{ V}$  のとき

$I_D = 250 \mu\text{A}$  にすると 最小充電時間  $t$  は  $5 \text{ nsec}$

$I_D = 0.25 \mu\text{A}$  にすると 最大充電時間  $t$  は  $5 \mu\text{sec}$

となる。このことは、最小充電時間と最大充電時間の比は、図 3 の CLK のようにデューティ比が 50% の場合、1:1000 となり、デューティ比を 90% にすれば、1:1800 となる。即ち、1800 種類のパルス巾を安定して制御できる。

20

#### 【0017】

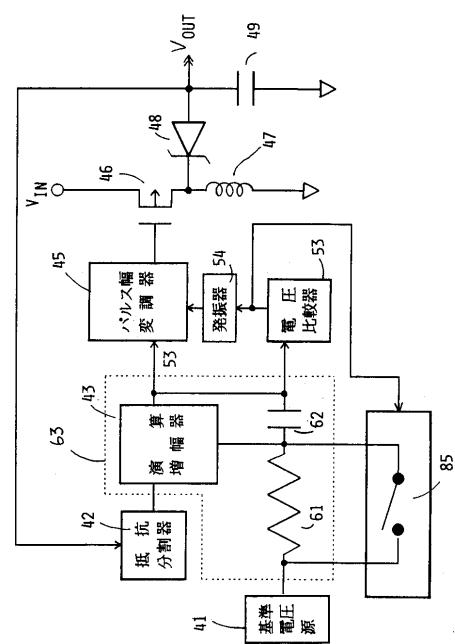

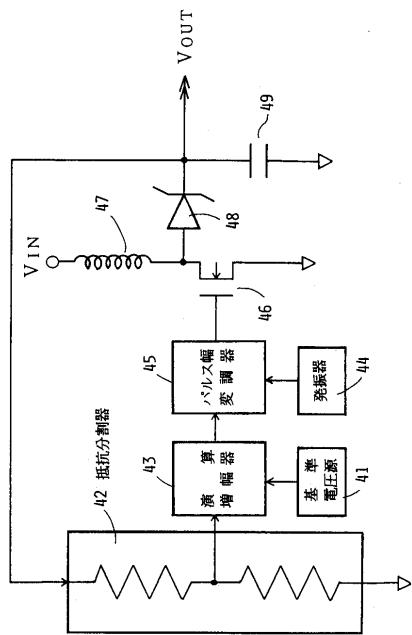

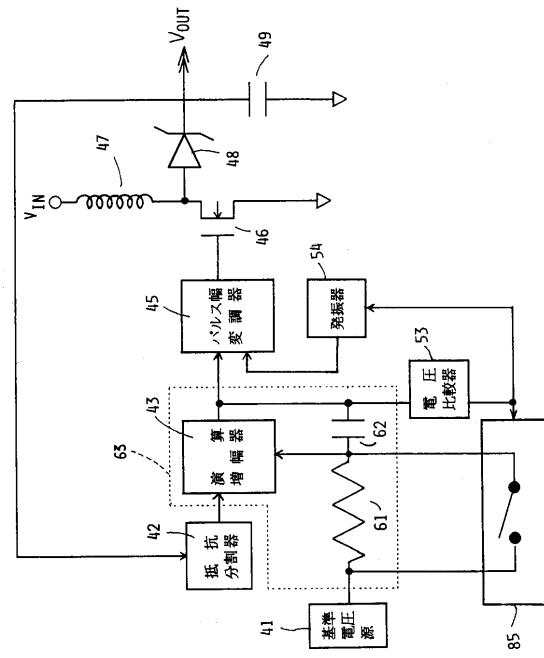

つぎに、上記パルス巾変調器を有するパルス巾変調型スイッチング電源について説明する。図 4 は本発明のスイッチング電源のブロック図である。抵抗分圧器 42 と基準電圧源 41 が演算増幅器 43 の入力側に接続され、該演算増幅器 43 の出力と発振器 44 がパルス巾変調器 45 の入力側に接続されている。該パルス巾変調器 45 の出力はトランジスタ 46 のゲートに接続され、スイッチング電源の入力端子とトランジスタ 46 のドレインの間にコイル 47 が接続されている。トランジスタ 46 のドレインにはダイオード 48 に接続され、該ダイオード 48 の他端は抵抗分圧器 42 に接続され、さらに一端を  $V_{SS}$  に接続されたコンデンサ 49 の他端に接続されこれが出力端子となっている。

#### 【0018】

30

つぎに、本発明のスイッチング電源の動作について説明する。演算増幅器 43 は出力電圧を分圧する抵抗分圧器 42 の出力電圧と、基準電圧源 41 の電圧を比較し増幅する。演算増幅器 43 の出力とクロック信号を発生する発振器 44 の出力を入力とする前述のパルス巾変調器 45 で入力に応じたパルス巾を作る。該パルス巾変調器 45 の出力をトランジスタ 46 が増幅しダイオード 48 で整流しコンデンサ 49 で平滑化する。このような構成により安定した定電圧を低消費電流で得ることができる。実際の使用例として、従来のスイッチング電源の消費電流が  $1.5 \text{ mA} \sim 4.5 \text{ mA}$  であるのに対し、本発明では  $10 \mu\text{A} \sim 20 \mu\text{A}$  が実現できた。

#### 【0019】

40

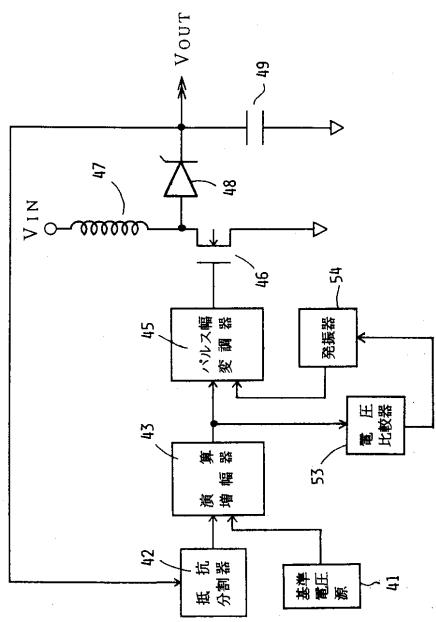

本発明のスイッチング電源の他の実施例を図 5 について説明する。図 5 は図 4 の実施例に電圧比較器 53 を加えたものであり、その動作は、演算増幅器 43 の出力電圧が上昇したとき電圧比較器 53 が反転出力を出力して発振器 54 の発振を停止させる。このような構成により、軽負荷時には発振器 54 及びこれに係わる回路の消費電流が削減されるのでスイッチング電源の変換効率の改善となる。本実施例は前述のパルス巾変調器が低消費電力を実現できたので、さらに有効となる。実際の使用例として本発明では  $2 \mu\text{A} \sim 4 \mu\text{A}$  の消費電流が実現できた。

#### 【0020】

50

また、このような構成のうちコイル 47 やコンデンサ 49 のような外付け部品以外の集積化された回路をテストするときに、正確なテスト用電源電圧を抵抗分圧器 42 に印加することによって発振器 54 の発振停止を観測して抵抗分圧器 42 の分圧精度または基準電圧

源 4 1 の値を間接的に測定できる。

【0021】

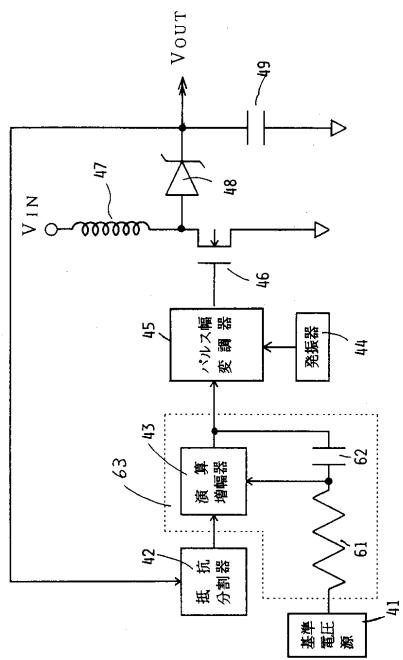

つぎに、本発明のスイッチング電源の他の実施例を図 6 について説明する。図 6 は図 4 の実施例に抵抗 6 1、コンデンサ 6 2 を加え演算増幅器 4 3 と共に積分器 6 3 を構成している。

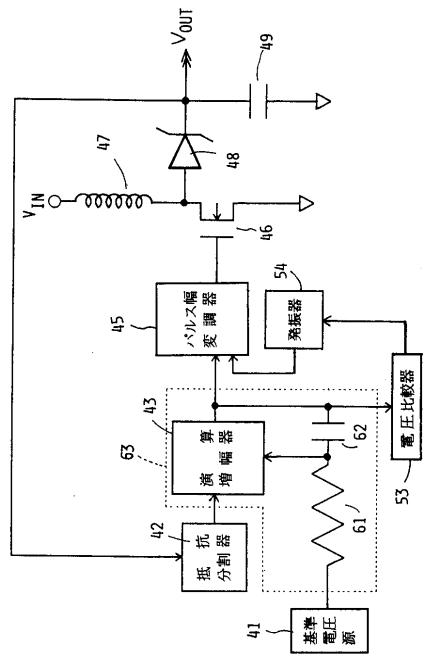

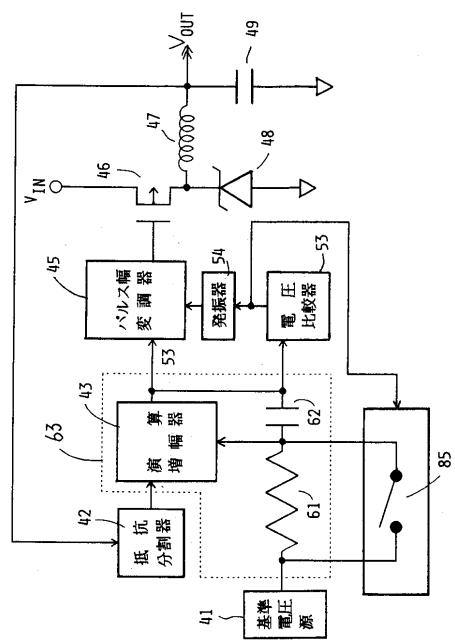

つぎに、本発明のスイッチング電源の他の実施例を図 7 について説明する。図 7 は図 6 の実施例に電圧比較器 5 3 を加えたものである。このように構成することにより、積分器 6 3 の安定した出力を得て電圧比較器 5 3 が発振器 5 4 の発振を停止し、軽負荷時の消費電流を削減することができる。

【0022】

10

さらに、本発明のスイッチング電源の他の実施例を図 8 について説明する。図 8 は図 7 の実施例にスイッチ 8 5 を抵抗 6 1 に平行に接続したものであり、このスイッチ 8 5 の開閉を行うための入力端子は電圧比較器 5 3 の出力と接続されている。このように構成することにより、スイッチング電源の負荷変動が発生した場合、その応答特性を改良するためにスイッチ 8 5 で積分器 6 3 の積分定数を小さくすることにより過渡応答時間を短くし、電源出力がほぼ平衡してから元の積分定数に戻すことができる。

【0023】

なお、図 2 の実施例で説明したパルス巾変調器のコンデンサ 2 4 の電圧基準を  $V_{DD}$  としたが、図 9 に示すようにコンデンサ 9 4 の電圧基準を  $V_{SS}$  とすることも可能である。この場合パルス巾変調器の入力部は PMOS トランジスタ 9 3 で構成することになり、その論理出力は図 3 と逆になる。また、上記説明した回路は全てバイポーラトランジスタ回路に置き換えることは言うまでもない。

20

【0024】

また、図 4 乃至図 8 では昇圧型のスイッチング電源を例として説明したが、本発明は図 1 2 のように降圧型、図 1 3 のように反転型のスイッチング電源にも有効であることは言うまでもない。

【0025】

30

【発明の効果】

以上説明したように、本発明によれば、パルス巾の可変範囲が最小パルス巾の 1800 倍まで安定に設定でき、通常の CMOS ロジック設計方法で設計した回路でも、動作電圧において 1V 以下で動作し、消費電流において数マイクロアンペア以下となり低消費電力化が実現できる。また、回路が集積化された場合、内部発振器と電子機器のシステム発振器が容易に切り換えるので、電子機器のシステム発振器と完全な同期がとれ、低雑音で小型のスイッチング電源の実現が可能になる。

【図面の簡単な説明】

【図 1】本発明のパルス巾変調器のブロック図である。

40

【図 2】本発明のパルス巾変調器の回路図である。

【図 3】図 2 の回路のタイムチャートである。

【図 4】本発明のパルス巾変調型スイッチング電源のブロック図である。

【図 5】本発明のパルス巾変調型スイッチング電源の他の実施例のブロック図である。

【図 6】本発明のパルス巾変調型スイッチング電源の他の実施例のブロック図である。

【図 7】本発明のパルス巾変調型スイッチング電源の他の実施例のブロック図である。

【図 8】本発明のパルス巾変調型スイッチング電源の他の実施例のブロック図である。

【図 9】本発明のパルス巾変調器の他の実施例の回路図である。

【図 10】本発明のパルス巾変調器の発振器を切り換える実施例のブロック図である。

【図 11】本発明のパルス巾変調器の発振器切り換えの他の実施例のブロック図である。

【図 12】本発明のパルス巾変調型スイッチング電源の降圧型のブロック図である。

【図 13】本発明のパルス巾変調型スイッチング電源の反転型のブロック図である。

【符号の説明】

11、44、54 発振器

50

- 8 5 スイッチ

1 2 第一の回路

1 3 第二の回路

1 4 第三の回路

1 5 コンデンサ

1 6 第四の回路

1 7 論理ゲート

4 1 基準電圧源

4 2 抵抗分圧器

4 3 演算増幅器

4 5 、 1 0 5 、 1 1 5 パルス巾変調器

4 6 トランジスタ

4 7 コイル

4 8 ダイオード

4 9 コンデンサ

5 3 電圧比較器

6 1 抵抗

6 2 コンデンサ

6 3 積分器

1 0 3 , 1 1 3 外部発振器

1 0 4 , 1 1 4 内部発振器

10

20

【図1】

【 义 2 】

### 【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】