(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4412027号

(P4412027)

(45) 発行日 平成22年2月10日(2010.2.10)

(24) 登録日 平成21年11月27日(2009.11.27)

(51) Int.Cl.

F 1

H03F 3/45 (2006.01)

H03F 3/34 (2006.01)H03F 3/45

H03F 3/34A

A

請求項の数 12 (全 20 頁)

(21) 出願番号 特願2004-96525 (P2004-96525)

(22) 出願日 平成16年3月29日 (2004.3.29)

(65) 公開番号 特開2005-286616 (P2005-286616A)

(43) 公開日 平成17年10月13日 (2005.10.13)

審査請求日 平成18年8月17日 (2006.8.17)

(73) 特許権者 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(74) 代理人 100080816

弁理士 加藤 朝道

(72) 発明者 土 弘

東京都港区芝五丁目7番1号 日本電気株

式会社内

審査官 儀同 孝信

最終頁に続く

(54) 【発明の名称】增幅回路及び表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

第1の電源に接続された負荷回路と、

前記負荷回路に共通に接続された第1及び第2の差動対と、

第1及び第2の差動対にそれぞれ電流を供給する第1及び第2の電流源と、

第1及び第2の差動対の共通接続された出力を受けて出力端子を駆動する増幅素子と、

前記第1の差動対の一方の入力と入力端子間に接続された第1のスイッチと、

前記第1の差動対の前記一方の入力と出力端子間に接続された第2のスイッチと、

前記第2の差動対の一方の入力と前記出力端子間に接続された第3のスイッチと、

前記第2の差動対の前記一方の入力に接続された容量素子と、

10 を備え、

前記第1の差動対の他方の入力と前記第2の差動対の他方の入力はともに前記入力端子に接続され、さらに、

前記第1の差動対と第2の電源間に、前記第1の電流源と直列形態に接続された第4のスイッチと、

を備えている、ことを特徴とする差動増幅回路。

## 【請求項2】

前記第2の差動対と第2の電源間に、前記第2の電流源と直列形態に接続された第5のスイッチと、

を備えている、ことを特徴とする請求項1記載の差動増幅回路。

20

**【請求項 3】**

データ出力期間が、第1の期間と第2の期間からなり、

前記第1の期間に、前記第1及び第3のスイッチがオン、前記第2のスイッチがオフとされ、

前記第2の期間に、前記第1及び第3のスイッチがオフ、前記第2のスイッチがオンとされ、

前記第4のスイッチは、前記第1の期間の開始の所定期間オフとされたのちオンとされる、ことを特徴とする請求項1記載の差動増幅回路。

**【請求項 4】**

第1の電源に接続された負荷回路と、

前記負荷回路に共通に接続された第1及び第2の差動対と、

第1及び第2の差動対にそれぞれ電流を供給する第1及び第2の電流源と、

第1及び第2の差動対の共通接続された出力を受けて出力端子を駆動する増幅素子と、

前記第1の差動対の一方の入力と入力端子間に接続された第1のスイッチと、

前記第1の差動対の前記一方の入力と出力端子間に接続された第2のスイッチと、

前記第2の差動対の一方の入力と前記出力端子間に接続された第3のスイッチと、

前記第2の差動対の前記一方の入力に接続された容量素子と、

を備え、

前記第1の差動対の他方の入力は前記入力端子に接続され、

前記第2の差動対の他方の入力は基準電圧入力端子に接続され、さらに、

前記第1の差動対と第2の電源間に、前記第1の電流源と直列形態に接続された第4のスイッチと、

前記第2の差動対と前記第2の電源間に、前記第2の電流源と直列形態に接続された第5のスイッチと、

を備えている、ことを特徴とする差動増幅回路。

**【請求項 5】**

データ出力期間が、第1の期間と第2の期間からなり、

前記第1の期間に、前記第1及び第3のスイッチがオン、前記第2のスイッチがオフとされ、

前記第2の期間に、前記第1及び第3のスイッチがオフ、前記第2のスイッチがオンとされ、

前記第4のスイッチは、前記第1の期間の開始の所定期間オフとしたのちオンとされ、

前記第5のスイッチは、前記第2の期間の開始の所定期間オフとされ、前記データ出力期間のうち前記第2の期間の開始の所定期間以外の期間オンとされる、ことを特徴とする請求項4記載の差動増幅回路。

**【請求項 6】**

第1の電源に接続された負荷回路と、

前記負荷回路に共通に接続された第1及び第2の差動対と、

第1及び第2の差動対にそれぞれ電流を供給する第1及び第2の電流源と、

第1及び第2の差動対の共通接続された出力を受けて出力端子を駆動する増幅素子と、

前記第1の差動対の一方の入力と入力端子間に接続された第1のスイッチと、

前記第1の差動対の前記一方の入力と出力端子間に接続された第2のスイッチと、

前記第2の差動対の一方の入力と前記出力端子間に接続された第3のスイッチと、

前記第2の差動対の前記一方の入力に接続された容量素子と、

を備え、

前記第1の差動対の他方の入力と前記第2の差動対の他方の入力は、ともに前記入力端子に接続され、さらに、

前記第2の差動対と第2の電源間に、第3の電流源と第4のスイッチとからなる直列回路が、前記第2の電流源と並列形態に接続されている、ことを特徴とする差動増幅回路。

**【請求項 7】**

10

20

30

40

50

データ出力期間が、第1の期間と第2の期間からなり、

前記第1の期間に、前記第1及び第3のスイッチがオン、前記第2のスイッチがオフとされ、

前記第2の期間に、前記第1及び第3のスイッチがオフ、前記第2のスイッチがオンとされ、

前記第4のスイッチは、前記第1の期間の開始の所定期間オンとされたのちオフとされる、ことを特徴とする請求項6記載の差動増幅回路。

#### 【請求項8】

第1の電源に接続された負荷回路と、

前記負荷回路に共通に接続された第1及び第2の差動対と、

10

第1及び第2の差動対にそれぞれ電流を供給する第1及び第2の電流源と、

第1及び第2の差動対の共通接続された出力を受けて出力端子を駆動する増幅素子と、

前記第1の差動対の一方の入力と入力端子間に接続された第1のスイッチと、

前記第1の差動対の前記一方の入力と出力端子間に接続された第2のスイッチと、

前記第2の差動対の一方の入力と前記出力端子間に接続された第3のスイッチと、

前記第2の差動対の前記一方の入力に接続された容量素子と、

を備え、

前記第1の差動対の他方の入力は前記入力端子に接続され、

前記第2の差動対の他方の入力は基準電圧入力端子に接続され、さらに、

20

前記第1の差動対と前記第2の電源間に、第3の電流源と第4のスイッチとからなる直列回路が、前記第1の電流源と並列形態に接続され、

前記第2の差動対と第2の電源間に、第4の電流源と第5のスイッチとからなる直列回路が、前記第2の電流源と並列形態に接続されている、ことを特徴とする差動増幅回路。

#### 【請求項9】

データ出力期間が、第1の期間と第2の期間からなり、

前記第1の期間に、前記第1及び第3のスイッチがオン、前記第2のスイッチがオフとされ、

前記第2の期間に、前記第1及び第3のスイッチがオフ、前記第2のスイッチがオンとされ、

前記第5のスイッチは、前記第1の期間の開始の所定期間、オンとされたのちオフとされ、

30

前記第4のスイッチは、前記第2の期間の開始の所定期間オンとされ、前記データ出力期間の前記第2の期間の開始の所定期間以外の期間はオフとされる、ことを特徴とする請求項8記載の差動増幅回路。

#### 【請求項10】

階調電圧を入力し、表示素子に接続されるデータ線を駆動する増幅回路を備えた表示装置において、

前記増幅回路として、請求項1乃至9のいずれか一に記載の差動増幅回路を有することを特徴とする表示装置。

#### 【請求項11】

第1の電源に接続された負荷回路と、

第1及び第2の差動対と、

40

第1及び第2の差動対にそれぞれ電流を供給する第1及び第2の電流源と、

前記負荷回路の出力を受けて出力端子を駆動する増幅素子と、

前記第1の差動対の一方の入力と入力端子間に接続された第1のスイッチと、

前記第1の差動対の前記一方の入力と出力端子間に接続された第2のスイッチと、

前記第2の差動対の一方の入力と前記出力端子間に接続された第3のスイッチと、

前記第2の差動対の前記一方の入力に接続された容量素子と、

を備え、

前記第1の差動対の他方の入力は前記入力端子に接続され、

50

前記第2の差動対の他方の入力は基準電圧入力端子に接続され、さらに、

前記第1の差動対の出力対と前記負荷回路間の導通／遮断を制御する第1のスイッチ群と

、

前記第2の差動対の出力対と前記負荷回路間の導通／遮断を制御する第2のスイッチ群と

と、

を備えている、ことを特徴とする差動增幅回路。

#### 【請求項12】

データ出力期間が、第1の期間と第2の期間からなり、

前記第1の期間に、前記第1及び第3のスイッチがオン、前記第2のスイッチがオフと

され、

10

前記第2の期間に、前記第1及び第3のスイッチがオフ、前記第2のスイッチがオンと

され、

前記第1のスイッチ群は、前記第1の期間の開始の所定期間オフとしたのちオンとされ

、

前記第2のスイッチ群は、前記第2の期間の開始の所定期間オフとされ、前記データ出

力期間のうち前記第2の期間の開始の所定期間以外の期間オンとされる、ことを特徴とす

る請求項11記載の差動增幅回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は增幅回路表示装置に関し、オフセットキャンセル機能を具備する増幅回路と該

增幅回路を有する表示装置に関する。

##### 【背景技術】

##### 【0002】

近時、液晶ディスプレイなどのフラットパネルディスプレイは世の中に広く普及し、そ

の多くはアクティブマトリックス型とされている。例えば、アクティブマトリックス駆動方

式を用いた液晶表示装置の表示部は、透明な画素電極及び薄膜トランジスタ(Thin Film

Transistor; TFT)を配置した半導体基板と、面全体に1つの透明な電極を形成した

対向基板と、これら2枚の基板を対向させて間に液晶を封入した構造からなり、スイッ

チング機能を持つTFTを制御することで各画素電極に所定の電圧を印加し各画素電極と対

向基板電極との間の電位差により液晶の透過率を変化させ、容量性を有する液晶がその電

位差及び透過率を所定の期間保持することにより、画像を表示させるものである。

30

##### 【0003】

半導体基板上には、各画素電極へ印加する複数のレベル電圧(階調電圧)を送るデータ

線と、TFTのスイッチング制御信号を送る走査線とが格子状に配線され、データ線は、

対向基板電極との間に挟まれる液晶の容量や各走査線との交差部に生じる容量などによる

容量性負荷となっている。

##### 【0004】

各画素電極への階調電圧の印加はデータ線を介して行われ、データ線につながる全ての

画素に対して1フレーム期間(1/60秒程度)に階調電圧の書き込みが行われる。このため、

データ線を駆動するデータ線駆動回路は、容量性負荷であるデータ線を、高い電圧精度で高速

度で駆動しなければならない。

40

##### 【0005】

そして、携帯機器用途については、データ線駆動回路には、データ線の高精度及び高速

駆動に加え、さらに、低消費電力であることが求められている。

##### 【0006】

また、データ線駆動回路は、多数のデータ線間で、駆動する階調電圧にばらつきなく駆

動することが求められている。すなわち、データ線駆動回路に用いられる出力增幅回路には、

高い出力電圧精度が求められている。

##### 【0007】

10

20

30

40

50

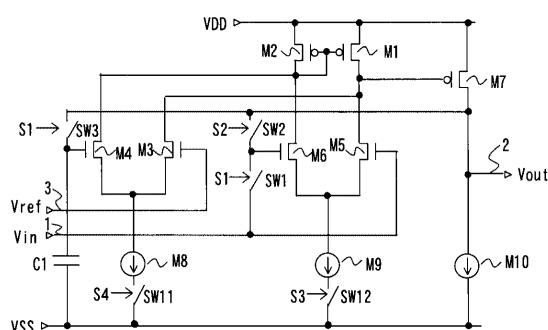

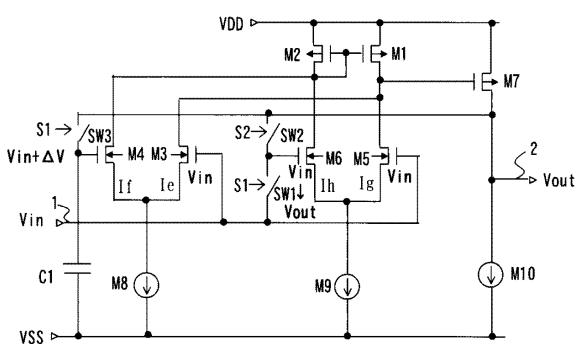

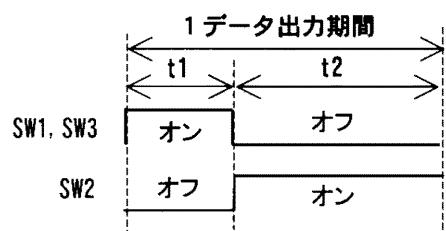

図13、図14は、高精度化を図る従来の増幅回路の構成及びタイミング動作の一例をそれぞれ示す図である（後記特許文献1参照）。

#### 【0008】

図13は、増幅回路を構成するトランジスタの素子ばらつきに起因する出力オフセットを抑制する機能を備えたオフセットキャンセルアンプの構成を示す図である。図13を参考すると、この回路は、共通接続されたソースが定電流源M8の一端に接続された差動対を構成するN MOSトランジスタM3、M4と、共通接続されたソースが定電流源M9の一端に接続された差動対を構成するN MOSトランジスタM5、M6と、を有し、N MOSトランジスタM3、M5のドレイン同士は接続され、PMOSトランジスタM1のドレインに接続され、N MOSトランジスタM4、M6のドレイン同士は接続され、PMOSトランジスタM2のドレインとゲートの接続点に接続され、PMOSトランジスタM1、M2のソースは高位側電源VDDに接続され、ゲートが共通接続されている。PMOSトランジスタM1、M2は、差動対（M3、M4）と差動対（M5、M6）の共通の能動負荷をなすカレントミラーを構成している。N MOSトランジスタM5とPMOSトランジスタM1の接続点は、ソースが電源VDDに接続され、ドレインが出力端子2に接続されたPMOSトランジスタM7のゲートに接続され、出力端子2と低位側電源VSS間には、電流源M10が接続されている。N MOSトランジスタM3、M5のゲートは、入力端子1に接続され、N MOSトランジスタM6のゲートは、スイッチSW1を介して入力端子1に接続され、スイッチSW2を介して出力端子2に接続されている。N MOSトランジスタM4のゲートは、一端が低位側電源VSSに接続された容量C1の他端に接続され、N MOSトランジスタM4のゲートと出力端子2間にはスイッチSW3が接続されている。10

#### 【0009】

図14のタイミングチャートを参考すると、図13に示す増幅回路は、1データ出力期間の期間t1に、スイッチSW1、SW3がオン、スイッチSW2がオフとされ、差動対（M3、M4）の入力対には、入力電圧Vinと出力電圧Voutが入力され、差動対（M5、M6）の入力対には入力電圧Vinが共通に入力される。このとき、出力電圧Voutは、オフセット電圧（ $V = V_f$ ；差動対の入力対に同電圧を印加したときの出力オフセット電圧）を含んだ電圧（ $V_{in} + V_f$ ）となっており、この電圧が容量素子C1に蓄積される。20

#### 【0010】

その後、期間t2に、スイッチSW1、SW3がオフし、スイッチSW2がオンとされ、その結果、差動対（M3、M4）の入力対には、入力電圧Vinと容量素子C1の端子電圧（ $V_{in} + V_f$ ）が差動入力され、差動対（M5、M6）の入力対には、入力電圧Vinと出力電圧Voutが差動入力される。このとき、差動対（M3、M4）には、期間t1と同じ電圧が、その入力対に入力されており、差動対（M5、M6）も、期間t1と同じ状態を保つように作用する。30

#### 【0011】

したがって、期間t2における出力電圧Voutは、入力電圧Vinと等しい電圧となって安定する。すなわち、図13に示した回路は、出力オフセットをキャンセルし、入力電圧と等しい電圧を増幅出力することができる。40

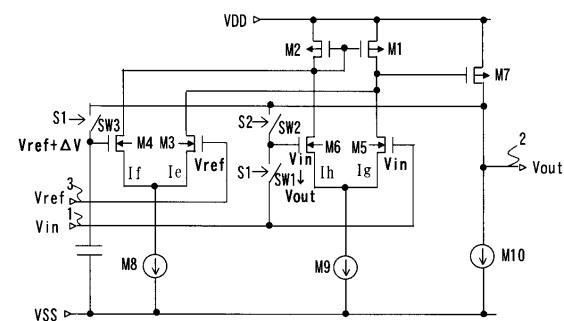

#### 【0012】

図15に示す構成は、図13に示した回路を変更したものである（後記特許文献2参照）。図15に示す構成が、図13に示した構成と相違している点は、図13に示す回路構成では、差動対をなすトランジスタM3のゲートに入力電圧Vinが入力されているのに対し、図15の例では、差動対をなすトランジスタM3のゲートに参照電圧Vrefを入力する構成としている。なお、図15の各スイッチを制御するタイミングチャートは、図14に示したものと同様である。

#### 【0013】

図15に示す増幅回路は、1データ出力期間の期間t1に、スイッチSW1、SW3が50

オンし、スイッチ SW2 はオフとされ、差動対 (M3, M4) の入力対には、入力電圧  $V_{in}$  と参照電圧  $V_{ref}$  が入力され、差動対 (M5, M6) の入力対には  $V_{in}$  が入力される。このとき、出力電圧  $V_{out}$  は、参照電圧  $V_{ref}$  に対してオフセット電圧  $V_f$  を含んだ電圧 ( $V_{ref} + V_f$ ) となっており、この電圧が容量素子 C1 の一端に印加される。その後、期間 t2 に、スイッチ SW1, SW3 がオフ、スイッチ SW2 がオンとされ、差動対 (M3, M4) の入力対には、入力電圧  $V_{ref}$  と容量素子 C1 の端子電圧 ( $V_{ref} + V_f$ ) が入力され、差動対 (M5, M6) の入力対には  $V_{in}$  と出力電圧  $V_{out}$  が入力される。このとき、差動対 (M3, M4) は、期間 t1 と同じ電圧が入力対に入力されており、差動対 (M5, M6) も、期間 t1 と同じ状態を保つように作用する。したがって、期間 t2 における出力電圧  $V_{out}$  は入力電圧  $V_{in}$  と等しい電圧となって安定する。すなわち、図 15 に示す回路は、出力オフセットをキャンセルし、入力電圧と等しい電圧を増幅出力することができる。

#### 【0014】

なお、参照電圧  $V_{ref}$  を、出力電圧範囲の中間電圧に設定すれば、期間 t1 での出力電圧  $V_{out}$  の電位変動量を、図 13 の構成よりも小さくすることができる。このため、期間 t1 を短縮して、高精度な駆動が行われる期間 t2 を長く取ることができる。

#### 【0015】

【特許文献 1】特開 2001-292041 公報 (第 3、4 頁、第 1 図)

【特許文献 2】特開 2003-168936 公報 (第 3、4 頁、第 1 図)

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0016】

近時、液晶表示装置は、表示部だけでなく、駆動回路も薄膜トランジスタで形成した駆動回路一体型の液晶表示装置が開発されている。しかし、駆動回路を形成する薄膜トランジスタは、単結晶シリコンで形成したトランジスタに比べて特性ばらつきが大きい。例えば閾値電圧は、100mV のオーダーでばらつく場合がある。

#### 【0017】

これに対して、図 13 や図 15 に示した従来のオフセットキャンセルアンプは、このような特性ばらつきの大きい薄膜トランジスタで形成しても有効であり、出力オフセットを抑制して高精度な電圧駆動を行うことができる。

#### 【0018】

しかしながら、本発明者による研究の結果、特性ばらつきの大きいトランジスタで形成した図 13 や図 15 に示した構成の従来のオフセットキャンセルアンプは、高い電圧精度は実現できるものの、特性ばらつきに起因したスルーレートのばらつきが発生することがわかった。液晶表示装置の駆動回路では、データ線間で同一の階調電圧に対するスルーレートがばらつくと、画素への書き込み電圧にも、ばらつきが出ることになる。このため、表示品質を低下させる要因となる。

#### 【0019】

したがって、本発明が解決しようとする課題は、特性ばらつきの大きいトランジスタで形成した増幅回路において、出力オフセットを抑制した高出力精度の実現とともに、スルーレートのばらつきも抑制するオフセットキャンセルアンプ、及び該アンプを具備する表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0020】

本願で開示される発明は、上記課題を解決するため、概略以下の構成とされる。

#### 【0021】

本発明の一つのアスペクトに係る差動増幅器は、共通の負荷回路と、第 1 及び第 2 の電流源との間にそれぞれ接続された第 1、第 2 の差動対を有し、第 1、第 2 の差動対の共通出力信号に応じて増幅作用を行う差動増幅器において、第 1、第 2 の電流源の少なくとも一方の活性、非活性を制御するための回路を設ける。

10

20

30

40

50

## 【0022】

本発明の他のアスペクトに係る差動増幅回路は、共通の負荷回路と、第1及び第2の電流源との間にそれぞれ接続された第1、第2の差動対を有し、第1、第2の差動対の共通出力信号に応じて増幅作用を行う差動増幅器において、第1、第2の差動対をそれぞれ駆動する電流源の電流値を変調制御するための回路を備えた構成としてもよい。

## 【0023】

本発明において、前記第1の差動対(M5、M6)の一方の入力と、差動増幅回路の入力端子(1)間に接続された第1のスイッチ(SW1)と、第1の差動対の前記一方の入力と、差動増幅回路の出力端子(2)間に接続された第2のスイッチ(SW2)と、前記第2の差動対(M3、M4)の一方の入力と出力端子(2)間に接続された第3のスイッチ(SW3)と、第2の差動対の一方の入力に接続された容量素子(C1)と、を備え、第1の差動対(M5、M6)の他方の入力は入力端子(1)に接続され、第2の差動対の他方の入力は、基準電圧入力端子(3)に接続されている。なお、括弧内の参照符号は、あくまで発明の理解の参考とするためのものであり、本発明を制限するものと解釈されるべきではない。10

## 【0024】

本発明に係る差動増幅回路は、その一態様として、入力端子と、出力端子と、第1の電源(VDD)に接続された負荷回路(M1、M2)と、前記負荷回路に共通に接続された第1、第2の差動対(M5、M6)、(M3、M4)と、第1、第2の差動対にそれぞれ電流を供給する第1、第2の電流源(M9、M8)と、第1、第2の差動対の共通接続された出力を受けて出力端子(2)を駆動する増幅素子(M7)と、前記第1の差動対(M5、M6)の一方の入力と入力端子(1)間に接続された第1のスイッチ(SW1)と、前記第1の差動対の前記一方の入力と出力端子(2)間に接続された第2のスイッチ(SW2)と、前記第2の差動対(M3、M4)の一方の入力と出力端子間に接続された第3のスイッチ(SW3)と、前記第2の差動対(M3、M4)の一方の入力に接続された容量素子(C1)と、を備え、前記第1の差動対(M5、M6)の他方の入力は前記入力端子(1)に接続され、前記第2の差動対(M3、M4)の他方の入力は基準電圧入力端子(3)に接続され、さらに、前記第1の差動対と第2の電源(VSS)間に、前記第1の電流源と直列形態に接続された第4のスイッチ(SW12)と、前記第2の差動対と前記第2の電源間に、前記第2の電流源と直列形態に接続された第5のスイッチ(SW11)と、を備えている。20

## 【0025】

データ出力期間が、第1の期間と第2の期間(t1、t2)からなり、第1の期間に、第1及び第3のスイッチ(SW1、SW3)がオン、第2のスイッチ(SW2)がオフとされ、第2の期間に、第1及び第3のスイッチ(SW1、SW3)がオフ、第2のスイッチ(SW2)がオンとされ、第4のスイッチ(SW12)は、第1の期間(t1)の開始の所定期間(ta)オフとされたのち、オンとされ、第5のスイッチ(SW11)は、第2の期間(t2)の開始の所定期間(tb)、オフとされ、それ以外の期間オンとされる。あるいは、第2の差動対(M3、M4)の他方の入力は、前記入力端子(1)に接続され、前記第1の差動対(M5、M6)と前記第2の電源間に、前記第1の電流源と直列形態に接続された第4のスイッチ(SW12)を備え、第5のスイッチ(SW11)を省略した構成としてもよい。40

## 【0026】

本発明に係る差動増幅回路は、その一態様として、入力端子と、出力端子と、第1の電源(VDD)に接続された負荷回路(M1、M2)と、前記負荷回路に共通に接続された第1、第2の差動対(M5、M6)、(M3、M4)と、第1、第2の差動対にそれぞれ電流を供給する第1、第2の電流源(M9、M8)と、第1、第2の差動対の共通接続された出力を受けて出力端子(2)を駆動する増幅素子(M7)と、前記第1の差動対(M5、M6)の一方の入力と入力端子(1)間に接続された第1のスイッチ(SW1)と、前記第1の差動対(M5、M6)の前記一方の入力と出力端子(2)間に接続された第250

のスイッチ (SW2) と、前記第2の差動対 (M3、M4) の一方の入力と出力端子間に接続された第3のスイッチ (SW3) と、前記第2の差動対 (M3、M4) の一方の入力に接続された容量素子 (C1) と、を備え、前記第1の差動対 (M5、M6) の他方の入力は前記入力端子 (1) に接続され、前記第2の差動対 (M3、M4) の他方の入力は基準電圧入力端子 (3) に接続され、さらに、前記第1の差動対 (M5、M6) と第2の電源 (VSS) 間に、第3の電流源 (M12) と第4のスイッチ (SW22) とからなる直列回路が、前記第1の電流源 (M9) と並列形態に接続され、前記第2の差動対 (M3、M4) と前記第2の電源 (VSS) 間に、第4の電流源 (M11) と第5のスイッチ (SW21) とからなる直列回路が、第2の電流源 (M8) と並列形態に接続されている。

## 【0027】

10

データ出力期間が、第1の期間と第2の期間 ( $t_1$ 、 $t_2$ ) からなり、第1の期間 ( $t_1$ ) に、第1及び第3のスイッチ (SW1、SW3) がオン、前記第2のスイッチ (SW2) がオフとされ、第2の期間 ( $t_2$ ) に、第1及び第3のスイッチ (SW1、SW3) がオフ、第2のスイッチ (SW2) がオンとされ、第5のスイッチ (SW21) は、第1の期間 ( $t_1$ ) の開始の所定期間 ( $t_a$ ) オンとされたのちオフとされ、第4のスイッチ (SW22) は、第2の期間 ( $t_2$ ) の開始の所定期間 ( $t_b$ ) オンとされ、それ以外の期間オフとされる。あるいは、前記第2の差動対 (M3、M4) の他方の入力は、前記入力端子 (1) に接続され、前記第2の差動対 (M3、M4) と前記第2の電源間に、前記第2の電流源 (M8) と並列形態に接続された前記第4の電流源 (M11) と前記第5のスイッチ (SW21) とからなる直列回路のみを備え、前記第3の電流源 (M12) と第4のスイッチ (SW22) からなる直列回路を省略した構成としてもよい。

## 【0028】

20

本発明の別のアスペクトに係る差動増幅回路は、第1及び第2の差動対 (M5、M6) 、(M3、M4) と、前記第1及び第2の差動対に共通接続された1つの負荷回路 (M1、M2) と、前記第1及び第2の差動対にそれぞれ電流を供給する第1及び第2の電流源 (M9、M8) と、を含み、前記第1及び第2の差動対の共通の出力信号に応じて増幅作用を行う差動増幅回路が、前記第1及び第2の差動対の少なくとも一方の活性 / 非活性を制御する回路を備えた構成としてもよい。

## 【発明の効果】

## 【0029】

30

本発明によれば、特性ばらつきの大きいトランジスタで形成した増幅回路において、出力オフセットを抑制するとともに、スルーレートのばらつきも抑制することができるという効果を奏する。

## &lt;発明の概要&gt;

## 【0030】

以下では、本発明の動作原理の前提として、従来技術におけるスルーレートばらつきに関する、本発明者による確認とその原因の考察を説述する。

## 【0031】

図10は、図15に示した構成の増幅回路 (Si基板上のCMOSプロセスによる増幅回路) を、薄膜トランジスタ (TFT) で構成した場合のシミュレーション対象の回路構成を示す図である。

40

## 【0032】

図10に示す構成では、出力を安定させるため、差動対の出力とPチャネルトランジスタM7の制御端の接続点と出力端子2との間に位相補償容量C2を設けている。特に、差動対の出力に、位相補償容量が直接接続される構成において、スルーレートばらつきが顕著となる。なお、定電流源M8、M9、M10は、ソースが低位側電源VSSに共通接続されたNチャネルトランジスタで構成し、ゲートには、バイアス電圧biasが共通に入力され、ドレインが差動対M3、M4、差動対M5、M6、出力端子2に接続されている。

## 【0033】

50

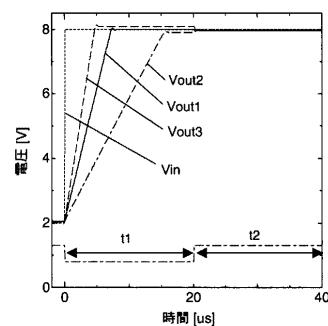

図11は、図10の回路において、参照電圧  $V_{ref} = 5V$ としたときの、入力電圧  $V_{in}$ に対する出力電圧波形（シミュレーション結果）を示している。

#### 【0034】

図11において、

出力電圧波形  $V_{out1}$  は、回路素子の特性ばらつきがない場合、

出力電圧波形  $V_{out2}$  は、NチャネルトランジスタM5、M6の閾値電圧  $V_{th5}$ 、 $V_{th6}$ が  $V_{th5} > V_{th6}$  の場合、

出力電圧波形  $V_{out3}$  は、 $V_{th5} < V_{th6}$  の場合である。

#### 【0035】

出力電圧波形  $V_{out2}$  および  $V_{out3}$  の期間  $t_1$ におけるオフセット電圧  $V_f$  を約 10 100mVとしている。

#### 【0036】

図11より、出力端子を参照電圧  $V_{ref}$  に駆動する期間  $t_1$ では、 $V_{out2}$ はスルーレートが  $V_{out1}$ より低く、オフセットが負となり、 $V_{out3}$ は、スルーレートが  $V_{out1}$ より高く、オフセットが正となっている。

#### 【0037】

一方、期間  $t_2$ では、逆に、 $V_{out2}$ はスルーレートが  $V_{out1}$ より高くなり、 $V_{out3}$ はスルーレートが  $V_{out1}$ より低くなっている。

#### 【0038】

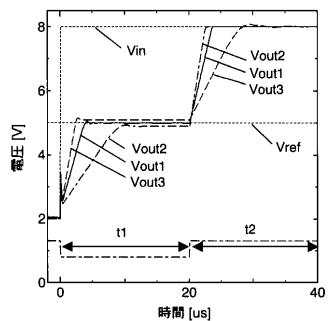

図12は、図10のシミュレーション対象の回路において、参照電圧  $V_{ref} = V_{in}$  20としたときの入力電圧  $V_{in}$ に対する出力電圧波形を示している。このとき、図10は、図13に示した構成と同じとなる。

#### 【0039】

差動対（M5，M6）の閾値電圧の関係を、図11の場合と、同様とすると、図12より、期間  $t_1$ では、 $V_{out2}$ はスルーレートが  $V_{out1}$ より低く、オフセットが負となり、 $V_{out3}$ はスルーレートが  $V_{out1}$ より高く、オフセットが正となっている。

#### 【0040】

以上のように、素子（特性）ばらつきが大きい場合には、素子ばらつきの条件により、スルーレートが大きく異なり、多出力の駆動回路では、出力間でスルーレートばらつきが生じる。

30

#### 【0041】

このようなスルーレートのばらつきは、図10において、差動対の出力信号によりPチャネルトランジスタM7の制御端を変化させる作用の強さが、薄膜トランジスタの特性ばらつきによって変動するためであることが分かった。

#### 【0042】

この作用について以下に説明する。なお、以下では、図10において、2つの差動対を構成するトランジスタM3、M4、M5、M6にそれぞれ流れる電流  $I_e$ 、 $I_f$ 、 $I_g$ 、 $I_h$ を、 $i_3$ 、 $i_4$ 、 $i_5$ 、 $i_6$ とし、電流源M8、M9の電流を、定電流  $I_8$ 、 $I_9$ とする。また説明を簡単にするため、差動対（M5，M6）以外の素子ばらつきはないものとする。

40

#### 【0043】

図10の構成において、差動対（M3，M4）、（M5，M6）は、それぞれ電流源M8、M9により駆動されているので、動作安定状態では、以下の関係が成り立つ。

#### 【0044】

$$i_3 + i_4 = I_8 \quad \dots (1)$$

$$i_5 + i_6 = I_9 \quad \dots (2)$$

#### 【0045】

また、M1、M2は、カレントミラーをなしているので、M1、M2に流れる電流は等しく、次式（3）が成り立つ。

$$i_4 + i_6 = i_3 + i_5 \quad \dots (3)$$

50

## 【0046】

上式(1)乃至(3)から、

$$i_3 + i_5 = (I_8 + I_9) / 2 \quad \dots (4)$$

$$i_4 + i_6 = (I_8 + I_9) / 2 \quad \dots (5)$$

となり、 $i_3$ と $i_5$ の和及び $i_4$ と $i_6$ の和は共に定数となる。

## 【0047】

ここで、図11の期間 $t_1$ における差動対の動作を考えると、期間 $t_1$ 開始直後、まず差動対( $M_5, M_6$ )の入力対には、スイッチ $SW_1$ がオン、スイッチ $SW_2$ がオフ状態であることから、入力電圧 $V_{in}$ が与えられ、これにより、電流 $i_5, i_6$ はそれぞれの閾値電圧に応じた定電流となる。一方、差動対( $M_3, M_4$ )の入力対には、スイッチ $SW_3$ がオン状態であることから、参照電圧 $V_{ref}$ と出力電圧 $V_{out}$ が与えられる。 $V_{out}$ は $V_{ref}$ よりも低い電位状態にあるため、 $i_3$ が増加、 $i_4$ が減少し、 $i_3$ の増加により、トランジスタ $M_7$ のゲート電位を引き下げ、トランジスタ $M_7$ に流れる電流が増加し、出力電圧 $V_{out}$ を上昇させるように作用する。このときの $i_3$ の電流増分量の大きさが、図11の期間 $t_1$ におけるスルーレートに影響する。

10

## 【0048】

上式(1)および上式(4)から、期間 $t_1$ における電流 $i_3$ の変化の幅は以下の範囲となる。

## 【0049】

$$I_8 - i_3 \{ (I_8 + I_9) / 2 \} - i_5 \quad \dots (6) \quad 20$$

## 【0050】

上式(6)において、電流 $i_3$ の範囲が広いほど、期間 $t_1$ における電流 $i_3$ の増分量が大きくなり、スルーレートが高くなる。

## 【0051】

ここで、差動対( $M_5, M_6$ )に素子ばらつきがある場合について考えると、トランジスタ $M_5, M_6$ の閾値電圧 $V_{th5}, V_{th6}$ が、 $V_{th5} > V_{th6}$ の場合、期間 $t_1$ において、電流の関係は $i_5 < i_6$ となる。このとき、上式(6)の電流 $i_3$ の範囲は狭くなり、したがって、スルーレートが低下する。

## 【0052】

一方、トランジスタ $M_5, M_6$ の閾値電圧の関係が、 $V_{th5} < V_{th6}$ の場合、期間 $t_1$ において電流の関係は $i_5 > i_6$ となる。このとき、上式(6)の電流 $i_3$ の範囲は広くなり、したがってスルーレートが高くなる。

30

## 【0053】

次に、図11の期間 $t_2$ における差動対の動作を考えると、期間 $t_2$ 開始直後、まず差動対( $M_3, M_4$ )の入力対には、参照電圧 $V_{ref}$ と参照電圧 $V_{ref}$ に対してオフセット電圧 $V_f$ を含んだ電圧( $V_{ref} + V_f$ )が与えられ、これにより、電流 $i_3, i_4$ は、それぞれ定電流となる。

## 【0054】

なお期間 $t_2$ の電流 $i_3, i_4$ の関係は、期間 $t_1$ の動作安定状態における電流 $i_3, i_4$ の関係が保持される。したがって、期間 $t_2$ の電流 $i_3, i_4$ の関係は、期間 $t_1$ の電流 $i_5, i_6$ の関係と、上式(3)によって定まり、トランジスタ $M_5, M_6$ の閾値電圧の関係が、

40

$V_{th5} > V_{th6}$ の場合、 $i_3 > i_4$ となり、

$V_{th5} < V_{th6}$ の場合、 $i_3 < i_4$ となる。

## 【0055】

一方、差動対( $M_5, M_6$ )の入力対には、入力電圧 $V_{in}$ と出力電圧 $V_{out}$ が与えられ、 $V_{out}$ は、 $V_{in}$ よりも低い電位状態にあるため、 $i_5$ が増加、 $i_6$ が減少し、 $i_5$ の増加により、トランジスタ $M_7$ のゲート電位を引き下げ、トランジスタ $M_7$ に流れる電流(ソース-ドレイン電流)が増大し、出力電圧 $V_{out}$ を上昇させるように作用する。このときの $i_5$ の電流増分量の大きさが、図11の期間 $t_2$ におけるスルーレートに

50

影響する。

**【0056】**

上式(2)および(4)から、期間 $t_2$ における電流 $i_5$ の変化の幅は以下の範囲となる。

**【0057】**

$$I_9 - i_5 \{ (I_8 + I_9) / 2 \} - i_3 \dots (7)$$

**【0058】**

上式(7)において、電流 $i_5$ の範囲が広いほど、期間 $t_2$ における電流 $i_5$ の増分量が大きくなり、スルーレートが高くなる。

**【0059】**

ここで、差動対(M5、M6)に素子ばらつきがある場合について考えると、トランジスタM5、M6の閾値電圧 $V_{th5}$ 、 $V_{th6}$ が、 $V_{th5} > V_{th6}$ の場合、電流 $i_3$ 、 $i_4$ の関係は、 $i_3 > i_4$ となるので、このとき、上式(7)の電流 $i_5$ の変化の範囲は広くなり、したがってスルーレートが高くなる。

10

**【0060】**

一方、トランジスタM5、M6の閾値電圧の関係が、 $V_{th5} < V_{th6}$ の場合、電流 $i_3$ 、 $i_4$ の関係は、 $i_3 < i_4$ となるので、このとき、上式(7)の電流 $i_5$ の変化の範囲は狭くなり、したがってスルーレートは低くなる。

**【0061】**

以上のような作用により、差動対(M5、M6)に、比較的大きな素子ばらつきがある場合、図11及び図12に示すようなスルーレートばらつきが発生する。同様に差動対(M3、M4)に素子ばらつきが生じた場合にもスルーレートばらつきが発生することは勿論である。

20

**【0062】**

本発明者による上記知見に基づき創案された本発明に係る差動増幅器は、共通の負荷回路(M1、M2)と、第1の電流源(M9)及び第2の電流源(M8)との間にそれぞれ接続された第1、第2の差動対(M5、M6)、(M3、M4)を有し、第1の差動対(M5、M6)の一方の入力と、差動増幅回路の入力端子(1)間に接続された第1のスイッチ(SW1)と、第1の差動対(M5、M6)の前記一方の入力と、差動増幅回路の出力端子(2)間に接続された第2のスイッチ(SW2)と、第2の差動対(M3、M4)の一方の入力と前記出力端子(2)間に接続された第3のスイッチ(SW3)と、第2の差動対(M3、M4)の一方の入力に接続された容量素子(C1)と、を備え、第1の差動対(M5、M6)の他方の入力は前記入力端子(1)に接続され、第2の差動対(M3、M4)の他方の入力は、入力端子(1)又は基準電圧入力端子(3)に接続され、2つの差動対の共通出力信号に応じて、増幅回路(M7)による増幅作用が行され、第1及び第2の電流源の少なくとも一方の活性、非活性を制御するための回路(SW11、SW12)を備えている。

30

**【0063】**

本発明の他の実施形態に係る差動増幅回路は、第1、第2の差動対をそれぞれ駆動する電流源の電流値を変調制御するための回路を備えた構成としてもよい。

40

**【0064】**

本発明の実施の形態によれば、特性ばらつきの大きいトランジスタで形成した増幅回路において、出力オフセットを抑制するとともに、スルーレートのばらつきも抑制することができる。

**【発明を実施するための最良の形態】**

**【0065】**

以下、本発明を実施するための最良の形態について図面を参照して詳細に説明する。

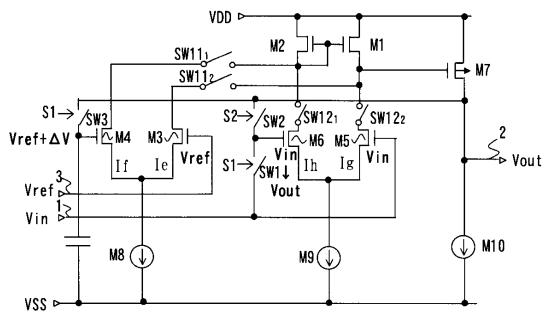

**【0066】**

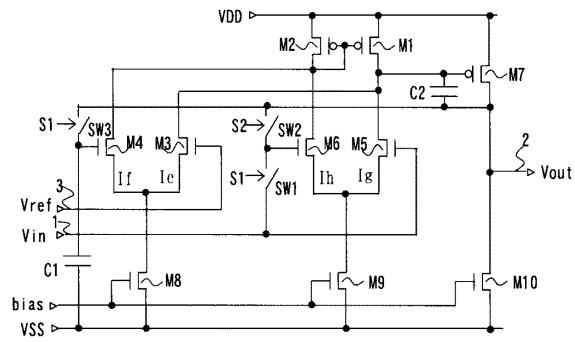

図1は、本発明を実施するための最良の一実施の形態の構成を示す図である。図1を参照すると、本発明の一実施形態の差動増幅回路は、図15に示したオフセットキャンセル

50

アンプにおいて、2つの電流源M8、M9の活性、非活性をそれぞれ制御するための回路を追加したものである。2つの電流源M8、M9の活性、非活性をそれぞれ制御するための回路として、電流源M8と直列形態で接続されるスイッチSW11と、電流源M9と直列形態で接続されるスイッチSW12を備えている。なお、図1の差動増幅回路は、TFTより構成される。また、図1を含む本願明細書添付図面の各々において、容量素子C1は一端が第2の差動対(M3, M4)の一方の入力に接続され、他端が低位側電源VSSに接続された構成が示されているが、容量素子C1の他端との接続は、低位側電源VSSの代わりに、高位側電源VDDもしくは任意の電源であってもよい。

#### 【0067】

前述した通り、図10に示した構成の場合、2つの差動対(M3, M4)、(M5, M6)のそれぞれのトランジスタに流れる電流は互いに影響しあうため、比較的大きな素子ばらつきがあると、スルーレートが変動する。10

#### 【0068】

これに対して、図1に示した実施例では、スイッチSW11、SW12により、2つの差動対(M3, M4)、(M5, M6)に流れる電流の相互作用を一時的になくすることにより、スルーレートの変動を抑えるものである。具体的な作用を以下に説明する。

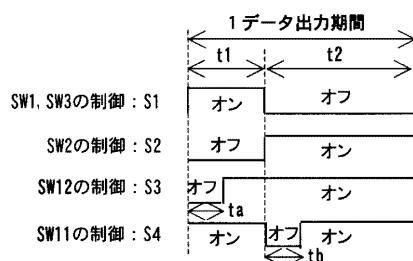

#### 【0069】

図2は、図1のスイッチSW1、SW3のオン・オフを制御する制御信号S1、スイッチSW2のオン・オフを制御する制御信号S2、スイッチSW12のオン・オフを制御する信号S3、及び、スイッチSW11のオン・オフを制御する信号S4のタイミングチャートを示している。本実施例において、制御信号S1、S2は、図14に示した例と同様である。以下、図2を参照して、スイッチSW11、SW12の作用を説明する。20

#### 【0070】

まず、期間t1の開始直後の期間taにおいて、制御信号S3により、スイッチSW12をオフとする。スイッチSW11は、期間t1を通じてオンのままする。

#### 【0071】

これにより、期間taにおいて、差動対(M5, M6)の電流が遮断され、差動対(M5, M6)の動作が停止される。このとき、差動対(M3, M4)に流れる電流i3, i4は、カレントミラー(M1, M2)によって決まり、カレントミラー(M1, M2)の素子ばらつきはないものとすると、動作安定状態で、以下の関係が成り立つ。30

#### 【0072】

$$i_3 = i_4 = I_8 / 2 \quad \dots (8)$$

#### 【0073】

これにより、期間taにおける電流i3の変化の幅は、以下の範囲となる。

#### 【0074】

$$I_8 - i_3 = I_8 / 2 \quad \dots (9)$$

#### 【0075】

なお上式(8)、(9)は、2つの差動対(M3, M4)、(M5, M6)の素子ばらつきに関係なく成り立ち、トランジスタM5の電流i5と無関係となる。

#### 【0076】

したがって、期間taでは、差動対(M3, M4)、(M5, M6)の素子ばらつきに関係なく、電流i3の増分量が一定となり、スルーレートも一定となる。40

#### 【0077】

本実施形態において、期間taは、期間t1において、出力電圧Voutが参照電圧Vref付近に到達する時間を目安に設定される。

#### 【0078】

そして、期間ta終了後、スイッチSW12をオンとし、残りの期間t1において、参照電圧Vrefに対して、オフセット電圧Vfを含んだ電圧(Vref + Vf)を容量素子C1に蓄積する。

#### 【0079】

10

20

30

40

50

次に、期間  $t_2$  の開始直後の期間  $t_b$ において、制御信号  $S_4$ により、スイッチ  $SW_{11}$ をオフとする。スイッチ  $SW_{12}$ は、期間  $t_2$ を通じてオンのまます。

#### 【0080】

これにより、期間  $t_b$ において、差動対 ( $M_3, M_4$ )の電流が遮断され、差動対 ( $M_3, M_4$ )の動作が停止される。

#### 【0081】

このときの差動対 ( $M_5, M_6$ )に流れる電流  $i_5, i_6$ は、カレントミラー ( $M_1, M_2$ )によって決まり、動作安定状態で以下の関係が成り立つ。

#### 【0082】

$$i_5 = i_6 = I_9 / 2 \quad \dots (10)$$

10

#### 【0083】

これにより、期間  $t_b$ における電流  $i_5$ の変化の幅は以下の範囲となる。

#### 【0084】

$$I_9 - i_5 = I_9 / 2 \quad \dots (11)$$

#### 【0085】

なお、上式 (10)、(11)は、2つの差動対 ( $M_3, M_4$ )、( $M_5, M_6$ )の素子ばらつきに関係なく成り立ち、電流  $i_3$ と無関係となる。

#### 【0086】

したがって、期間  $t_b$ では、差動対 ( $M_3, M_4$ )、( $M_5, M_6$ )の素子ばらつきに関係なく、電流  $i_5$ の増分量が一定となり、スルーレートも一定となる。

20

#### 【0087】

期間  $t_b$ は、期間  $t_2$ において、出力電圧  $V_{out}$ が入力電圧  $V_{in}$ 付近に到達する時間を目安に設定される。

#### 【0088】

そして、期間  $t_b$ 終了後、スイッチ  $SW_{11}$ をオンとし、残りの期間  $t_2$ において、出力電圧  $V_{out}$ は、オフセットがキャンセルされ、入力電圧  $V_{in}$ と等しい電圧に駆動される。

#### 【0089】

以上のように、図1に示した本実施形態では、差動対のテール電流を供給する電流源  $M_8, M_9$ の電流バスにそれぞれスイッチ  $SW_{11}, SW_{12}$ を挿入し、期間  $t_1$ および期間  $t_2$ にそれぞれ設けた期間  $t_a, t_b$ にスイッチ  $SW_{12}, SW_{11}$ をそれぞれ制御することにより、差動対 ( $M_3, M_4$ )、( $M_5, M_6$ )の素子ばらつきに依存せずに、出力電圧のスルーレートを一定に保つことができる。

30

#### 【0090】

なお、 $V_{ref} = V_{in}$ とする場合には、期間  $t_a$ に、出力電圧  $V_{out}$ が入力電圧  $V_{in}$ 付近まで駆動されるので、期間  $t_2$ において、出力電圧  $V_{out}$ が大きく変化することはない。したがって、期間  $t_2$ におけるスルーレートは考える必要がなく、この場合、スイッチ  $SW_{11}$ および期間  $t_b$ の制御は行わなくてよい。すなわち、期間  $t_a$ において、スイッチ  $SW_{12}$ をオフとするだけでよい。

#### 【0091】

40

また、図1に示す構成では、電流源  $M_8, M_9$ の活性、非活性を制御するための回路を、電流源  $M_8, M_9$ と直列形態で接続したスイッチ  $SW_{11}, SW_{12}$ で構成する例について説明したが、これ以外の構成であってもよいことは勿論である。

#### 【0092】

例えば、電流源  $M_8, M_9$ を、制御端にバイアス電圧を印加したトランジスタで形成し、バイアス電圧を変えることで電流源  $M_8, M_9$ の活性、非活性を制御してもよい。

#### 【0093】

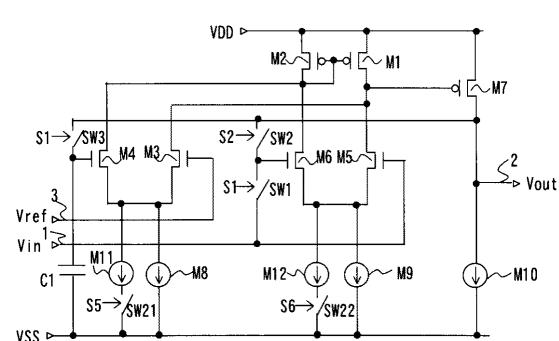

図3は、本発明の第2の実施形態の構成を示す図であり、図15に示したオフセットキャンセルアンプにおいて、差動対 ( $M_3, M_4$ )、( $M_5, M_6$ )を駆動する電流を変調するための回路を追加した構成を示したものである。図3を参照すると、直列形態で接続

50

された電流源M11とスイッチSW21を、電流源M8と並列に、差動対(M3、M4)の共通ソースと低位側電源VSS間に設け、直列形態で接続された電流源M12とスイッチSW22を、電流源M9と並列に、差動対(M5、M6)の共通ソースと低位側電源VSS間に備えている。

#### 【0094】

図3に示す実施形態は、2つの差動対(M3、M4)、(M5、M6)を駆動する電流を変調することにより、差動対の各トランジスタに流れる電流の相互作用を抑え、それによってスルーレートの変動を抑えるものである。具体的な作用を以下に説明する。

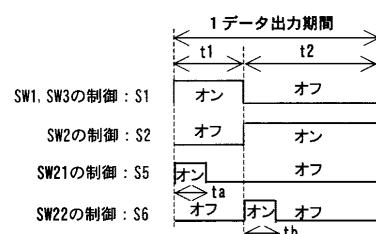

#### 【0095】

図4は、本発明の一実施例の各スイッチSW1、SW2、SW3、SW21、SW22のオン・オフ制御のタイミングチャートを示す図である。制御信号S1、S2は、図14と同様である。以下、図4を参照して、スイッチSW21、SW22の作用を説明する。

#### 【0096】

まず、期間t1の開始直後の期間taにおいて、制御信号S5により、スイッチSW21をオンとする。スイッチSW22は期間t1を通じてオフのままとする。

#### 【0097】

これにより、期間taにおいて、差動対(M3、M4)の電流が増加する。期間taにおける電流i3の変化の幅は、図10、図11と同様の原理で、上式(6)より以下の範囲となる。なお、電流源M11の電流を定電流I11とする。

#### 【0098】

$$I_8 + I_{11} - i_3 = \{ (I_8 + I_9 + I_{11}) / 2 \} - i_5 \quad \dots (12)$$

#### 【0099】

上式(12)より、電流i3の変化の幅は、電流I11の項が加わったことにより、差動対の素子ばらつきによって変動する電流i5の影響が小さくなる。したがって差動対の素子ばらつきによるスルーレートばらつきも小さくなる。

#### 【0100】

期間taは、期間t1において、出力電圧Voutが参照電圧Vref付近に到達する時間を目安に設定される。そして、期間ta終了後、スイッチSW21をオフとし、残りの期間t1において、参照電圧Vrefに対してオフセット電圧Vfを含んだ電圧(Vref + Vf)を容量素子C1に蓄積する。

#### 【0101】

次に、期間t2の開始直後の期間tbにおいて、制御信号S6により、スイッチSW22をオンとする。スイッチSW21は、期間t2を通じてオフのままとする。これにより、期間tbにおいて、差動対(M5、M6)の電流が増加する。

#### 【0102】

期間tbにおける電流i5の変化の幅は、図10、図11と同様の原理で、上式(7)より、以下の範囲となる。なお電流源M12の電流を定電流I12とする。

#### 【0103】

$$I_9 + I_{12} - i_5 = \{ (I_8 + I_9 + I_{12}) / 2 \} - i_3 \quad \dots (13)$$

#### 【0104】

上式(13)より、電流i5の変化の幅は、電流I12の項が加わったことにより、差動対の素子ばらつきによって変動する電流i3の影響が小さくなる。したがって、差動対の素子ばらつきによるスルーレートばらつきも小さくなる。

#### 【0105】

期間tbは、期間t2において、出力電圧Voutが入力電圧Vin付近に到達する時間を目安に設定される。そして、期間tb終了後、スイッチSW22をオフとし、残りの期間t2において、出力電圧Voutは、オフセットがキャンセルされ、入力電圧Vinと等しい電圧に駆動される。

#### 【0106】

以上のように、図3では、電流源M11、M12、スイッチSW21、SW22を設け

10

20

30

40

50

、期間 $t_1$ および期間 $t_2$ に設けた期間 $t_a$ 、 $t_b$ に、スイッチSW21、SW22をそれぞれ制御することにより、差動対(M3, M4)、(M5, M6)の素子ばらつきに対してスルーレート変動を抑制して、ほぼ一定に保つことができる。

#### 【0107】

なお、 $V_{ref} = V_{in}$ とする場合には、期間 $t_a$ に出力電圧 $V_{out}$ が入力電圧 $V_{in}$ 付近まで駆動されるので、期間 $t_2$ において出力電圧 $V_{out}$ が大きく変化することはない。したがって期間 $t_2$ におけるスルーレートは考える必要がなく、この場合には、電流源M12、スイッチSW22および期間 $t_b$ の制御はなくてよい。

#### 【0108】

また、図3は、差動対(M3, M4)、(M5, M6)を駆動する電流を変調するための回路の一例を示したもので、別の構成でもよいことはもちろんである。例えば、電流源M8、M9を、制御端にバイアス電圧を印加したトランジスタで形成し、バイアス電圧を変えることで電流源M8、M9の電流値を変調制御してもよい。

10

#### 【0109】

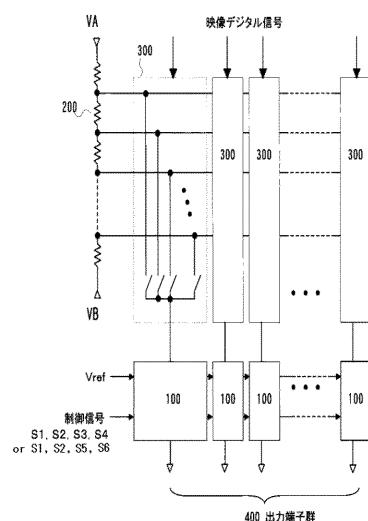

本発明に係る表示装置の実施例について説明する。図9は、本発明の実施例の構成を示す図である。表示装置のデータドライバの出力バッファ100に、図1や図3のオフセットキャンセルアンプを適用することにより、薄膜トランジスタで構成した表示装置のデータドライバ(多出力の駆動回路)において、高精度な電圧出力とともに、出力間のスルーレートばらつきも抑制されることにより、表示装置の表示品質を保つことができる。以下具体的な実施例について説明する。

20

#### 【実施例】

#### 【0110】

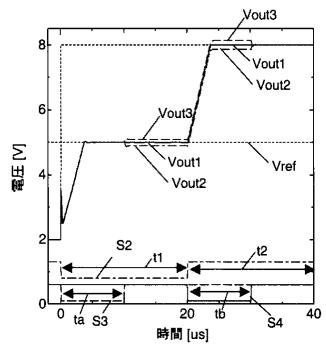

図5は、図1に示した実施形態の構成のシミュレーション結果を示す図である。シミュレーション対象回路は、図10に、スイッチSW11、SW12を付加した回路で行った。図5は、参照電圧 $V_{ref} = 5V$ としたときの入力電圧 $V_{in}$ に対する出力電圧波形を示している。

#### 【0111】

図5において、

出力電圧波形 $V_{out1}$ は、回路素子の特性ばらつきがない場合、

出力電圧波形 $V_{out2}$ は、NチャネルトランジスタM5、M6の閾値電圧 $V_{th5}$ 、 $V_{th6}$ が $V_{th5} > V_{th6}$ の場合、

30

出力電圧波形 $V_{out3}$ は、 $V_{th5} < V_{th6}$ の場合である。

#### 【0112】

閾値電圧 $V_{th5}$ 、 $V_{th6}$ のばらつきの幅は、図11の場合と同じである。図5より、 $V_{out2}$ 、 $V_{out3}$ において、期間 $t_a$ および期間 $t_b$ のスルーレートが $V_{out1}$ と同じであり、差動対(M5, M6)の素子ばらつきに対して、スルーレートばらつきを抑えることができることが示されている。

#### 【0113】

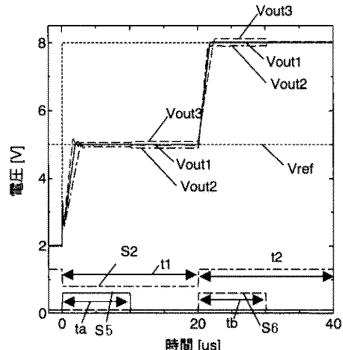

図6は、参照電圧 $V_{ref} = V_{in}$ としたときの入力電圧 $V_{in}$ に対する出力電圧波形を示している。なお、シミュレーション対象回路は、図10に、スイッチSW12のみを付加した回路で行った。

40

#### 【0114】

図6より、 $V_{out2}$ 、 $V_{out3}$ において、期間 $t_a$ のスルーレートが $V_{out1}$ と同じであり、差動対(M5, M6)の素子ばらつきに対してスルーレートばらつきを抑えることができることが示されている。

#### 【0115】

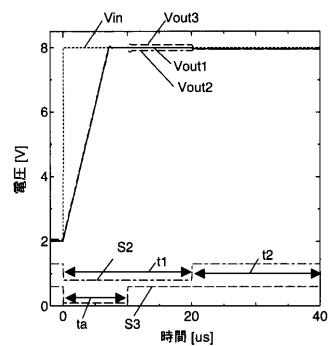

図7は、図3に示した実施形態の回路のシミュレーション結果である。シミュレーション回路は、図10に構成に、図3に示すような電流源M11、M12(NチャネルTFT)、スイッチSW21、SW22を付加した回路で行った。

#### 【0116】

50

図7は、参照電圧 $V_{ref} = 5V$ としたときの入力電圧 $V_{in}$ に対する出力電圧波形を示している。図7より、 $V_{out2}$ 、 $V_{out3}$ において、期間 $t_a$ および期間 $t_b$ のスルーレートが $V_{out1}$ に十分近く、差動対(M5, M6)の素子ばらつきに対してスルーレートばらつきを抑えることができる事が示されている。

#### 【0117】

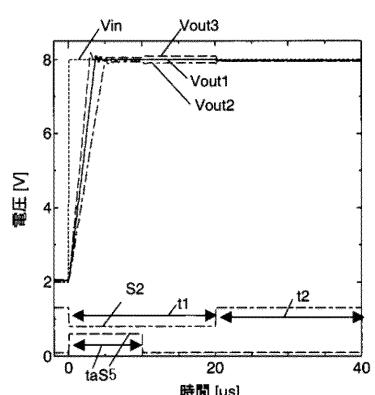

図8は、参照電圧 $V_{ref} = V_{in}$ としたときの入力電圧 $V_{in}$ に対する出力電圧波形を示している。なお、シミュレーション回路は、図10に、電流源M11とスイッチSW21のみを附加した回路で行った。図8より、 $V_{out2}$ 、 $V_{out3}$ において、期間 $t_a$ のスルーレートが $V_{out1}$ に十分近く、差動対(M5, M6)の素子ばらつきに対してスルーレートばらつきを抑えることができる事が示されている。なお、図5乃至図8は、差動対(M5, M6)に素子ばらつきがある場合の一例であるが、差動対(M3, M4)に素子ばらつきがある場合も、同様に、スルーレートばらつきを防ぐことができる。

#### 【0118】

なお、図1に示した構成は、差動対(M5, M6), (M3, M4)にそれぞれ定電流を供給する2つの電流源M8、M9の活性/非活性をそれぞれ制御するための回路を備えた構成である。ところで、電流源M8、M9の活性/非活性の制御は、すなわち差動対(M5, M6)、(M3, M4)の活性/非活性の制御と、実質的に等価である。したがって、本発明においては、差動対(M3, M4)、(M5, M6)の活性/非活性の制御を行う構成としてもよい。具体的には、図16に示す構成において、差動対(M3, M4)、(M5, M6)のそれぞれの出力対と、カレントミラー(M1, M2)との間にスイッチ群(SW111<sub>1</sub>、SW111<sub>2</sub>)、(SW121<sub>1</sub>、SW121<sub>2</sub>)を挿入し、スイッチ群の制御により、差動対(M3, M4)、(M5, M6)の活性(カレントミラー(M1, M2)との接続)、非活性(カレントミラー(M1, M2)との遮断)の制御を行う構成でもよい。なお、このとき、増幅トランジスタM7の制御端は、カレントミラー(M1, M2)の出力端と接続される。スイッチ(SW111<sub>1</sub>、SW111<sub>2</sub>)は、入力される制御信号に基づき、同時に連動してオン・オフし、スイッチ(SW121<sub>1</sub>、SW121<sub>2</sub>)は、入力される制御信号に基づき、同時に連動してオン・オフする。差動対(M5, M6)の出力対とカレントミラー(M1, M2)との間のスイッチ(SW121<sub>1</sub>、SW121<sub>2</sub>)による接続/遮断の制御は、例えば図2に示す制御信号S3を用いて行われ、制御信号S3がハイレベルで該スイッチ(SW121<sub>1</sub>、SW121<sub>2</sub>)がともにオンし、制御信号S3がロウレベルで該スイッチ(SW121<sub>1</sub>、SW121<sub>2</sub>)はともにオフする。差動対(M3, M4)の出力対とカレントミラー(M1, M2)との間のスイッチ(SW111<sub>1</sub>、SW111<sub>2</sub>)による接続/遮断の制御は、例えば図2に示す制御信号S4を用いて行われ、制御信号S4がハイレベルでスイッチ(SW111<sub>1</sub>、SW111<sub>2</sub>)がともにオンし、制御信号S4がロウレベルで該スイッチ(SW111<sub>1</sub>、SW111<sub>2</sub>)はオフする。1データ出力期間における制御信号S1、S2、S3、S4のタイミング波形は、図2に示した通りとされる。

#### 【0119】

以上本発明を上記実施例に即して説明したが、本発明は、上記実施例の構成にのみ限定されるものではなく、本発明の範囲内で当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

#### 【図面の簡単な説明】

#### 【0120】

【図1】本発明の一実施の形態の構成を示す図である。

【図2】本発明の一実施の形態のスイッチ制御の一例を示す図である。

【図3】本発明の他の実施の形態の構成を示す図である。

【図4】本発明の他の実施の形態のスイッチ制御の一例を示す図である。

【図5】本発明の一実施例のシミュレーション結果を示す図である。

【図6】本発明の一実施例のシミュレーション結果を示す図である。

【図7】本発明の第2の実施例のシミュレーション結果を示す図である。

10

20

30

40

50

【図8】本発明の第2の実施例のシミュレーション結果を示す図である。

【図9】本発明の表示装置の構成の一例を示す図である。

【図10】従来の回路のシミュレーション回路を示す図である。

【図11】図10の回路のシミュレーション結果を示す図である。

【図12】図10の回路のシミュレーション結果を示す図である。

【図13】従来の回路の構成を示す図である。

【図14】図13の従来の回路のスイッチ制御の一例を示す図である。

【図15】従来の回路の構成を示す図である。

【図16】本発明のさらに他の実施の形態の構成を示す図である。

【符号の説明】

10

【0121】

1 入力端子

2 出力端子

3 基準電圧端子

100 出力バッファ

200 階調電圧発生回路

300 デコーダ

400 出力端子群

C1 容量素子

M1、M2、M7 Pチャネルトランジスタ

20

M3～M6 Nチャネルトランジスタ

M8、M9、M10 電流源

SW1、SW2、SW11、SW12、SW111、SW112、SW121、SW22

スイッチ

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図 1 0】

【図 1 2】

【図 1 1】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

---

フロントページの続き

(56)参考文献 特開平11-186856(JP,A)

特開平01-284007(JP,A)

特開2000-174576(JP,A)

特開2001-168692(JP,A)

米国特許第6411240(US,B1)

特開2001-292041(JP,A)

特開2003-168936(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 - 3/45、3/50 - 3/52、

3/62 - 3/64、3/68 - 3/72、

H03G 1/00 - 3/34