(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6426379号

(P6426379)

(45) 発行日 平成30年11月21日(2018.11.21)

(24) 登録日 平成30年11月2日(2018.11.2)

(51) Int.Cl.

F 1

|             |           |      |       |      |

|-------------|-----------|------|-------|------|

| HO1L 21/336 | (2006.01) | HO1L | 29/78 | 616K |

| HO1L 29/786 | (2006.01) | HO1L | 29/78 | 616U |

| HO1L 21/28  | (2006.01) | HO1L | 29/78 | 616T |

| HO1L 29/417 | (2006.01) | HO1L | 29/78 | 616V |

| HO1L 21/304 | (2006.01) | HO1L | 29/78 | 618B |

請求項の数 8 (全 50 頁) 最終頁に続く

(21) 出願番号

特願2014-126434 (P2014-126434)

(22) 出願日

平成26年6月19日(2014.6.19)

(65) 公開番号

特開2015-26830 (P2015-26830A)

(43) 公開日

平成27年2月5日(2015.2.5)

審査請求日

平成29年5月22日(2017.5.22)

(31) 優先権主張番号

特願2013-128920 (P2013-128920)

(32) 優先日

平成25年6月19日(2013.6.19)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 島 行徳

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 神長 正美

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 中澤 安孝

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

酸化物半導体膜を有するトランジスタのソース電極及びドレイン電極を形成する工程は

、

前記酸化物半導体膜を覆うように、第1の導電膜を形成する工程と、

前記第1の導電膜上に、第2の導電膜を形成する工程と、

前記酸化物半導体膜と重なる領域の前記第2の導電膜を、選択的に除去する工程と、

前記第2の導電膜を覆い、かつ前記第2の導電膜から露出した前記第1の導電膜と接するように、第3の導電膜を形成する工程と、

前記酸化物半導体膜と重なる領域の前記第1の導電膜と前記第3の導電膜とを選択的に除去する工程と、

前記第1の導電膜と前記第3の導電膜とを選択的に除去した後、洗浄処理を行う工程と、

、を有することを特徴とする半導体装置の作製方法。

## 【請求項 2】

酸化物半導体膜を有するトランジスタのソース電極及びドレイン電極を形成する工程は

、

前記酸化物半導体膜を覆うように、第1の導電膜を形成する工程と、

前記第1の導電膜上に、第2の導電膜を形成する工程と、

前記酸化物半導体膜と重なる領域の前記第2の導電膜を、選択的に除去する工程と、

前記第2の導電膜を覆い、かつ前記第2の導電膜から露出した前記第1の導電膜と接

10

20

するように、第3の導電膜を形成する工程と、

前記酸化物半導体膜と重なる領域の前記第1の導電膜と前記第3の導電膜とを選択的に除去し、かつ前記酸化物半導体膜の上面を選択的に除去する工程と、

前記第1の導電膜と前記第3の導電膜とを選択的に除去し、かつ前記酸化物半導体膜の上面を選択的に除去した後、洗浄処理を行う工程と、を有することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項1または請求項2において、

前記第2の導電膜は、銅を含むことを特徴とする半導体装置の作製方法。

**【請求項4】**

10

請求項1乃至請求項3のいずれか一において、

前記第1の導電膜は、前記第2の導電膜よりも融点が高い材料を含み、

前記第3の導電膜は、前記第2の導電膜よりも融点が高い材料を含むことを特徴とする半導体装置の作製方法。

**【請求項5】**

請求項1乃至請求項4のいずれか一項において、

前記第1の導電膜は、タンゲステン、チタン、モリブデン、クロム、またはタンタルを含むことを特徴とする半導体装置の作製方法。

**【請求項6】**

20

請求項1乃至請求項5のいずれか一項において、

前記第3の導電膜は、タンゲステン、チタン、モリブデン、クロム、またはタンタルを含むことを特徴とする半導体装置の作製方法。

**【請求項7】**

請求項1乃至請求項6のいずれか一項において、

前記第3の導電膜は、金属窒化物または金属酸化物であることを特徴とする半導体装置の作製方法。

**【請求項8】**

請求項1乃至請求項7のいずれか一項において、

前記洗浄処理に、リン酸を含む溶液を用いることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

半導体装置及びその作製方法に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、発光表示装置、半導体回路、トランジスタ、および電子機器等は全て半導体装置といえる。

**【背景技術】**

**【0003】**

電気光学装置の1つである液晶表示装置や、発光表示装置に代表されるフラットパネルディスプレイの多くに用いられているトランジスタは、ガラス基板上に形成されたアモルファスシリコン、単結晶シリコンまたは多結晶シリコンなどのシリコン半導体によって構成されている。また、該シリコン半導体を用いたトランジスタは、集積回路（IC）などにも利用されている。

**【0004】**

また、フラットパネルディスプレイの大面積化及び高精細化に伴って、駆動周波数が高まると共に、配線の抵抗及び寄生容量が増大し、配線遅延が生じる。そのため、配線遅延を抑制するため、銅、アルミニウム、金、銀、亜鉛、モリブデン等の低抵抗材料を用いて配線を形成する技術が検討されている（特許文献1）。

**【0005】**

40

50

また、特許文献 2 では、ゲート配線を、シリコン (Si)、チタン (Ti)、タンタル (Ta)、タングステン (W)、またはモリブデン (Mo) で銅 (Cu) を包んだ構造とすることで、配線抵抗の低減と、配線の耐熱性の向上を実現する技術が開示されている。

#### 【0006】

また、特許文献 3 では、ゲート配線、ソース配線、またはドレイン配線を、タングステン (W)、モリブデン (Mo)、クロム (Cr) などで銅 (Cu) を包む構造とする技術が開示されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

10

【特許文献 1】特開 2004 - 133422 号公報

【特許文献 2】特開 2000 - 223716 号公報

【特許文献 3】特開 2007 - 165860 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

銅は、半導体装置の電気特性の不良原因となる不純物の一つであり、加工の途中において半導体層に拡散しやすい。特に、半導体層に接して形成されるソース配線およびドレイン配線に銅を含む材料を用いると、加工の途中において銅が半導体層へ拡散し、半導体装置の特性はらつきや、信頼性の低下を生じやすいという問題がある。

20

#### 【0009】

本発明の一態様は、半導体層の不純物濃度を低減することを課題の一とする。

#### 【0010】

本発明の一態様は、半導体装置の電気特性を向上させることを課題の一とする。

#### 【0011】

本発明の一態様は、半導体装置の信頼性を向上させることを課題の一とする。

#### 【課題を解決するための手段】

#### 【0012】

30

本発明の一態様は、酸化物半導体膜上に第 1 の導電膜を形成し、第 1 の導電膜上に第 2 の導電膜を形成し、第 2 の導電膜の一部を選択的に除去し、第 2 の導電膜を覆って第 3 の導電膜を形成し、第 1 の導電膜と、第 3 の導電膜の一部を選択的に除去した後、洗浄処理を行うことを特徴とする半導体装置の作製方法である。

#### 【0013】

第 1 の導電膜と第 3 の導電膜は、第 2 の導電膜よりも融点が高い材料を用いて形成することが好ましい。例えば、第 2 の導電膜に銅を含む材料を用いる場合、電極 106a および電極 106c は、タングステン、チタン、モリブデン、クロム、またはタンタルなどの銅よりも融点が高い金属元素を含む材料を用いて形成することが好ましい。

#### 【0014】

また、第 3 の導電膜に、金属窒化物または金属酸化物を用いてもよい。

#### 【0015】

40

洗浄処理は、例えば TM AH (Tetramethylammonium Hydroxide) 溶液などのアルカリ性の溶液、希フッ酸、シュウ酸、リン酸などの酸性の溶液、またはプラズマ処理（酸素プラズマ処理など）により行うことができる。

#### 【発明の効果】

#### 【0016】

本発明の一態様により、半導体層の不純物濃度を低減することができる。

#### 【0017】

本発明の一態様により、半導体装置の電気特性を向上させることができる。

#### 【0018】

本発明の一態様により、半導体装置の信頼性を向上させることができます。

50

**【図面の簡単な説明】****【0019】**

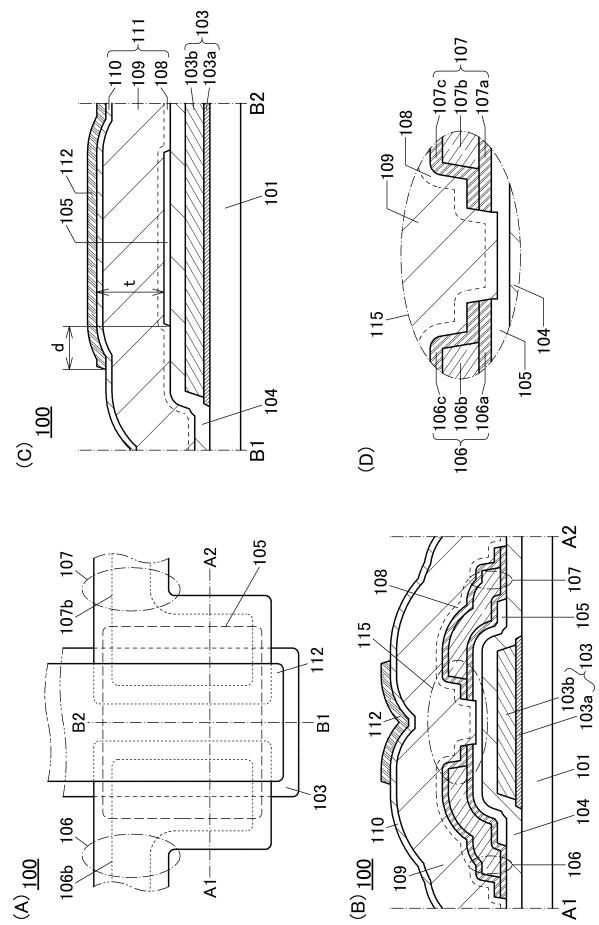

- 【図1】半導体装置の一形態を説明する上面図及び断面図。

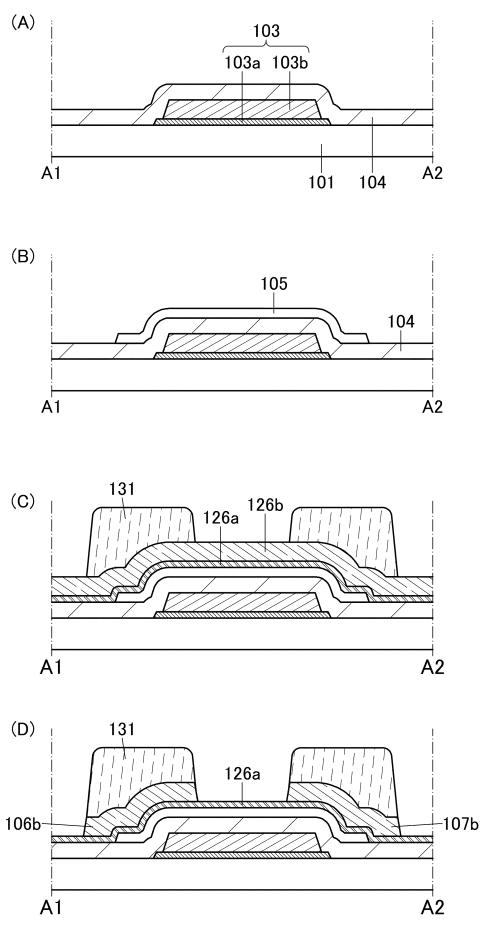

【図2】半導体装置の作製方法の一形態を説明する断面図。

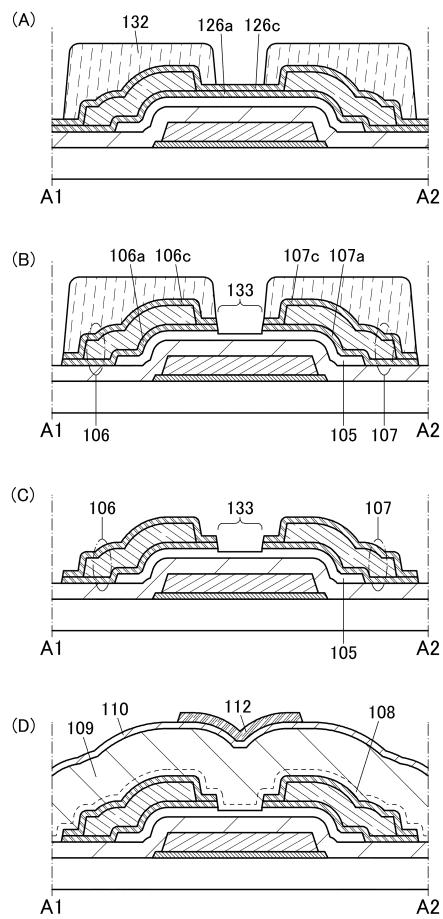

【図3】半導体装置の作製方法の一形態を説明する断面図。

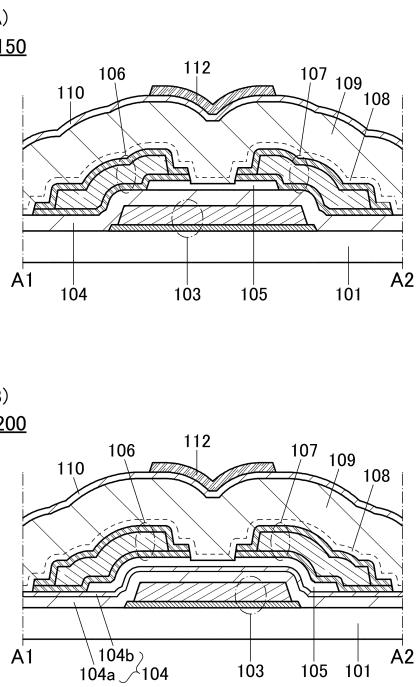

【図4】半導体装置の一形態を説明する断面図。

【図5】半導体装置の一形態を説明する上面図及び断面図。

【図6】半導体装置の一形態を説明するブロック図及び回路図。

【図7】半導体装置の一形態を説明する上面図。

【図8】半導体装置の一形態を説明する断面図。

【図9】半導体装置の一形態を説明する断面図。

- 10

【図10】半導体装置の作製方法の一形態を説明する断面図。

【図11】半導体装置の作製方法の一形態を説明する断面図。

【図12】半導体装置の作製方法の一形態を説明する断面図。

【図13】半導体装置の作製方法の一形態を説明する断面図。

【図14】半導体装置の作製方法の一形態を説明する断面図。

【図15】半導体装置の作製方法の一形態を説明する断面図。

【図16】半導体装置の作製方法の一形態を説明する断面図。

【図17】半導体装置の作製方法の一形態を説明する断面図。

【図18】半導体装置の作製方法の一形態を説明する断面図。

20

【図19】半導体装置の作製方法の一形態を説明する断面図。

【図20】半導体装置の作製方法の一形態を説明する断面図。

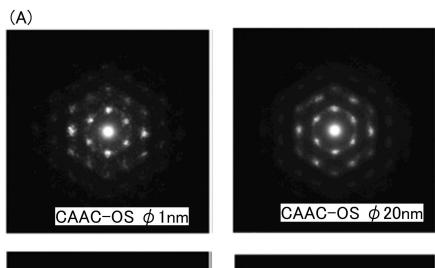

【図21】酸化物半導体膜のナノビーム電子線回折像を示す図。

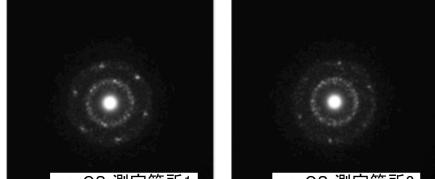

【図22】試料A乃至試料Dを説明する断面図および断面TEM観察像。

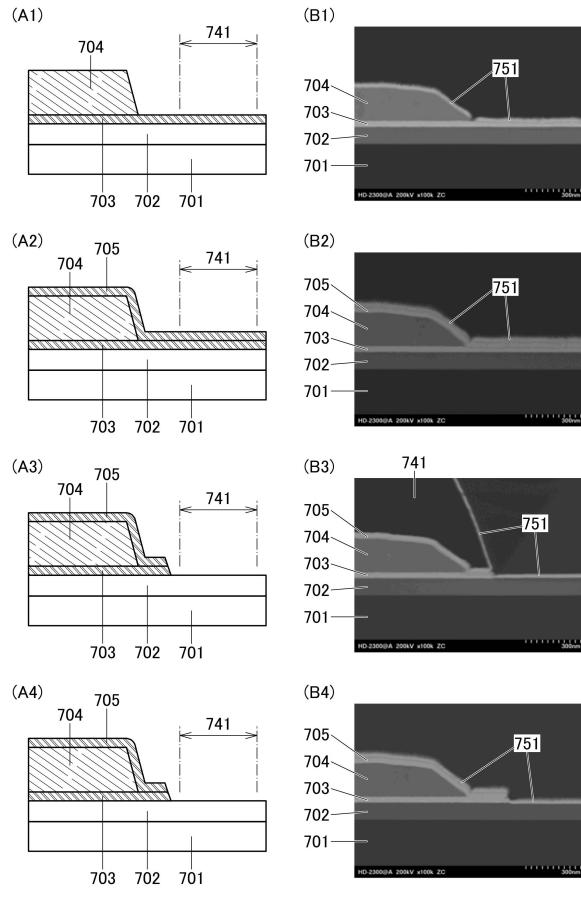

【図23】試料Aおよび試料BのSIMS分析結果を示す図。

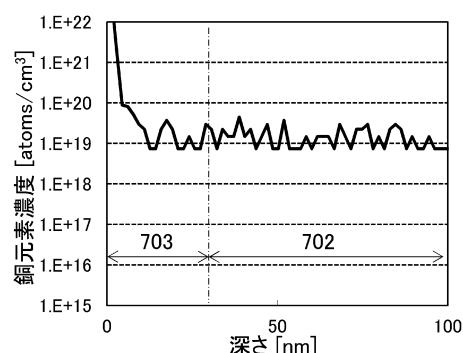

【図24】試料Cおよび試料DのSIMS分析結果を示す図。

【図25】電子機器の一例を説明する図。

**【発明を実施するための形態】****【0020】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態及び実施例において、同一部分または同様の機能を有する部分には、同一の符号または同一のハッチパターンを異なる図面間で共通して用い、その繰り返しの説明は省略する。

**【0021】**

本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

**【0022】**

また、図面等において示す各構成の、位置、大きさ、範囲などは、発明の理解を容易とするため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。例えば、実際の製造工程において、エッティングなどの処理によりレジストマスクなどが意図せず目に減りすることがあるが、理解を容易とするために省略して示すことがある。

**【0023】**

また、特に上面図（「平面図」ともいう。）において、図面をわかりやすくするために、一部の構成要素の記載を省略する場合がある。

**【0024】**

また、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるた

30

40

50

めに付するものであり、工程順または積層順など、なんらかの順番や順位を示すものではない。また、本明細書等において序数詞が付されていない用語であっても、構成要素の混同を避けるため、特許請求の範囲において序数詞が付される場合がある。

#### 【0025】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

#### 【0026】

また、ソースおよびドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合など、動作条件などによって互いに入れ替わるため、いずれがソースまたはドレインであるかを限定することが困難である。このため、本明細書においては、ソースおよびドレインの用語は、入れ替えて用いることができるものとする。

10

#### 【0027】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。よって、「電気的に接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

20

#### 【0028】

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が直上または直下で、かつ、直接接していることを限定するものではない。例えば、「絶縁層A上の電極B」の表現であれば、絶縁層Aの上に電極Bが直接接して形成されている必要はなく、絶縁層Aと電極Bとの間に他の構成要素を含むものを除外しない。

#### 【0029】

また、本明細書において、「平行」とは、二つの直線が - 10°以上 10°以下の角度で配置されている状態をいう。従って、- 5°以上 5°以下の場合も含まれる。また、「垂直」および「直交」とは、二つの直線が 80°以上 100°以下の角度で配置されている状態をいう。従って、85°以上 95°以下の場合も含まれる。

30

#### 【0030】

また、本明細書において、フォトリソグラフィ工程を行った後にエッチング工程を行う場合は、特段の説明がない限り、フォトリソグラフィ工程で形成したマスクは、エッチング工程終了後に除去するものとする。

#### 【0031】

##### (実施の形態1)

本実施の形態では、本発明の一態様である半導体装置及びその作製方法について図面を参照して説明する。

#### 【0032】

##### <半導体装置の構成例>

40

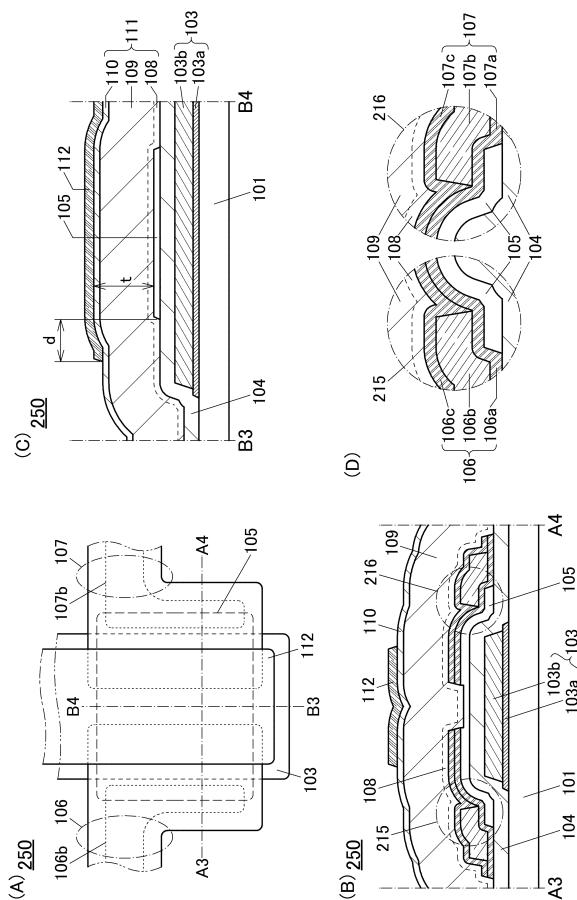

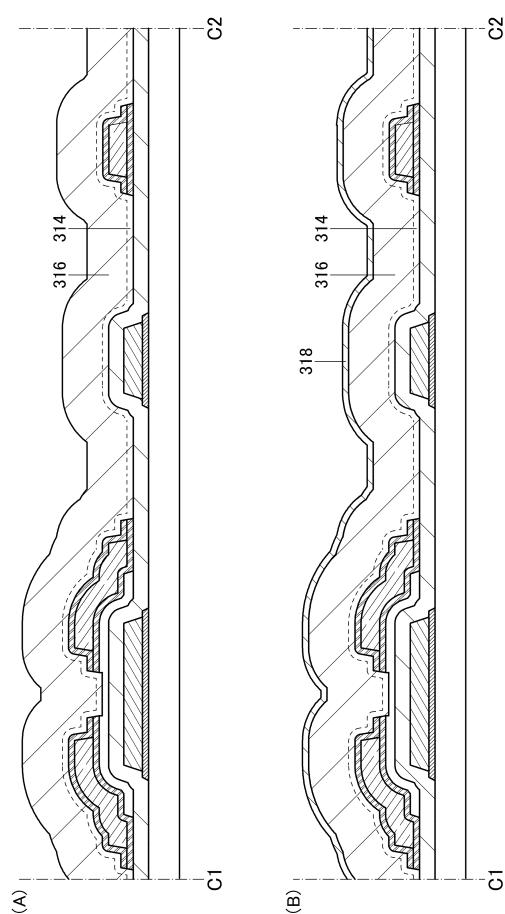

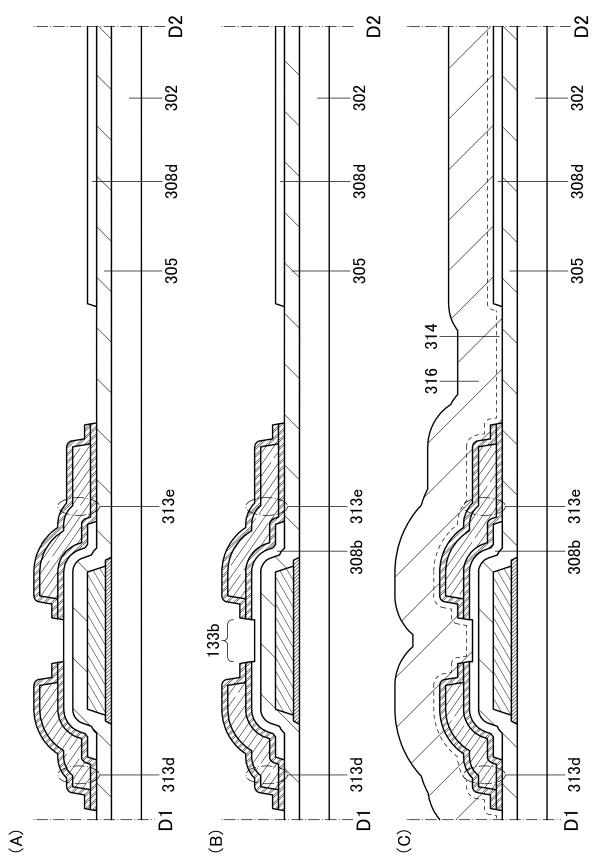

図1に、半導体装置の一例として、トランジスタ100の上面図及び断面図を示す。トランジスタ100は、チャネルエッチ型のトランジスタである。

#### 【0033】

図1(A)はトランジスタ100の上面図である。また、図1(B)は、図1(A)中の一点鎖線A1-A2で示す部位の断面図であり、図1(C)は、図1(A)中の一点鎖線B1-B2で示す部位の断面図である。また、図1(D)は、図1(B)に示す部位115の拡大図である。なお、図1(B)は、トランジスタ100のチャネル長方向の断面であり、図1(C)は、トランジスタ100のチャネル幅方向の断面である。

#### 【0034】

トランジスタ100は、基板101上に設けられるゲート電極103と、基板101及び

50

ゲート電極 103 上に形成されるゲート絶縁膜 104 と、ゲート絶縁膜 104 を介して、ゲート電極 103 と重なる酸化物半導体膜 105 と、酸化物半導体膜 105 に接する一対の電極 106、電極 107 を有する。また、ゲート絶縁膜 104、酸化物半導体膜 105、および一対の電極 106、電極 107 上には、酸化物絶縁膜 108、酸化物絶縁膜 109、及び窒化物絶縁膜 110 を含む保護膜 111 が形成される。また、窒化物絶縁膜 110 上に酸化物半導体膜 105 と重なるゲート電極 112 を有する。

#### 【0035】

トランジスタ 100 は、複数のゲート電極を有し、該電極の間に酸化物半導体膜 105 を有するデュアルゲート構造のトランジスタである。図 1 (C) に示すチャネル幅方向において、酸化物半導体膜 105 の外側にゲート電極 112 の端部が位置する。または、チャネル幅方向において、ゲート電極 112 は、保護膜 111 を介して酸化物半導体膜 105 の端部を超えて設けられている。また、チャネル幅方向において、酸化物半導体膜 105 の外側で、ゲート電極 103 およびゲート電極 112 は、ゲート絶縁膜 104、保護膜 111 を介して対向する。

10

#### 【0036】

図 1 (C) を用いて、ゲート電極 103、酸化物半導体膜 105、ゲート電極 112 の端部の位置について説明する。

#### 【0037】

ここで、酸化物半導体膜 105 の端部及びゲート電極 112 の端部の距離を  $d$  とし、保護膜 111 の厚さを  $t$  とすると、酸化物半導体膜 105 の端部及びゲート電極 112 の端部の距離  $d$  は、保護膜 111 の厚さ  $t$  以下であることが好ましい。酸化物半導体膜 105 の端部及びゲート電極 112 の端部の距離  $d$  を、保護膜 111 の厚さ  $t$  以下とすることで、酸化物半導体膜 105 の端部に、ゲート電極 112 の電界の影響を与えることが可能であり、酸化物半導体膜 105 の端部を含む全体をチャネルとして機能させることができる。

20

#### 【0038】

エッティング等で加工された酸化物半導体膜の端部は、加工におけるダメージにより欠陥が形成されると共に、不純物付着などにより汚染されるため、電界などのストレスが与えられることによって活性化しやすい。すなわち、エッティング等で加工された酸化物半導体膜の端部は、n型化（低抵抗化）されやすい。

#### 【0039】

30

このように意図せず n 型化された領域が、電極 106 および電極 107 と接すると、当該領域を介して電極 106 および電極 107 間に意図しない電流（「漏れ電流」または「リーケ電流」ともいう。）が流れてしまう。すなわち当該領域が寄生チャネルとして機能する。

#### 【0040】

しかしながら、図 1 (C) に示すように、酸化物半導体膜 105 の外側にゲート電極 112 の端部が位置することで、ゲート電極 112 の電界の影響により、酸化物半導体膜 105 の側面、または側面及びその近傍を含む端部における寄生チャネルの発生が抑制される。この結果、ゲート電圧がしきい値電圧を超えた時のドレイン電流の上昇が急峻となり、電気特性の優れたトランジスタとすることができる。

40

#### 【0041】

なお、ゲート電極 103 およびゲート電極 112 のどちらか一方を、単に「ゲート電極」という場合、他方を「バックゲート電極」という場合がある。また、ゲート電極 103 およびゲート電極 112 のどちらか一方を、「第 1 のゲート電極」といい、他方を「第 2 のゲート電極」という場合がある。

#### 【0042】

一般に、バックゲート電極は導電膜で形成され、ゲート電極とバックゲート電極で半導体層のチャネル形成領域を挟むように配置される。よって、バックゲート電極は、ゲート電極と同様に機能させることができる。バックゲート電極の電位は、ゲート電極と同電位としてもよく、GND 電位や、任意の電位としてもよい。バックゲート電極の電位を変化さ

50

ることで、トランジスタのしきい値電圧を変化させることができる。

**【0043】**

また、ゲート電極とバックゲート電極は導電膜で形成されるため、トランジスタの外部で生じる電界が、チャネルが形成される半導体層に作用しないようにする機能（特に静電気に対する静電遮蔽機能）も有する。

**【0044】**

また、バックゲート電極側から光が入射する場合に、バックゲート電極を、遮光性を有する導電膜で形成することで、バックゲート電極側から半導体層に光が入射することを防ぐことができる。よって、半導体層の光劣化を防ぎ、トランジスタのしきい値電圧がシフトするなどの電気特性の劣化を防ぐことができる。10

**【0045】**

酸化物半導体膜105を挟んでゲート電極103およびゲート電極112を設けることでの、更にはゲート電極103およびゲート電極112を同電位とすることで、酸化物半導体膜105においてキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタ100のオン電流が大きくなると共に、電界効果移動度が高くなる。

**【0046】**

また、ゲート電極103およびゲート電極112を有することで、それが外部からの電界を遮蔽する機能を有するため、基板101及びゲート電極103の間、ゲート電極112上に設けられる荷電粒子等の電荷が酸化物半導体膜105に影響しない。この結果、ストレス試験（例えば、ゲートに負の電荷を印加する - GBT (Gate Bias - Temperature) ストレス試験）の劣化が抑制されると共に、異なるドレイン電圧におけるオン電流の立ち上がり電圧の変動を抑制することができる。なお、この効果は、ゲート電極103及びゲート電極112が、同電位、または異なる電位の場合において生じる。20

**【0047】**

なお、BTストレス試験は加速試験の一種であり、長期間の使用によって起こるトランジスタの特性変化（即ち、経年変化）を、短時間で評価することができる。特に、BTストレス試験前後におけるトランジスタのしきい値電圧の変動量は、信頼性を調べるための重要な指標となる。BTストレス試験前後において、しきい値電圧の変動量が少ないほど、信頼性が高いトランジスタであるといえる。30

**【0048】**

また、ゲート電極103およびゲート電極112を有し、且つゲート電極103およびゲート電極112を同電位とすることで、しきい値電圧の変動量が低減される。このため、複数のトランジスタにおける電気特性のばらつきも同時に低減される。

**【0049】**

また、トランジスタ100は、ゲートに正の電荷を印加する + GBTストレス試験前後ににおけるしきい値電圧の変動が小さい。

**【0050】**

なお、本実施の形態においては、ゲート電極103およびゲート電極112が接続され、同電位であるが、ゲート電極103およびゲート電極112が接続されず、それぞれ異なる電位が印加されてもよい。40

**【0051】**

以下に、トランジスタ100の他の構成の詳細について説明する。

**【0052】**

基板101の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板101として用いてもよい。また、シリコンや炭化シリコンなどの材料を用いた単結晶半導体基板や多結晶半導体基板、シリコンゲルマニウムなどの材料を用いた化合物半導体基板、またはSOI基板などを適用することも可能であり、これらの50

基板上に半導体素子が設けられたものを、基板 101 として用いてもよい。なお、基板 101 として、ガラス基板を用いる場合、第 6 世代 ( $1500\text{mm} \times 1850\text{mm}$ )、第 7 世代 ( $1870\text{mm} \times 2200\text{mm}$ )、第 8 世代 ( $2200\text{mm} \times 2400\text{mm}$ )、第 9 世代 ( $2400\text{mm} \times 2800\text{mm}$ )、第 10 世代 ( $2950\text{mm} \times 3400\text{mm}$ ) 等の大面積基板を用いることで、大型の表示装置を作製することができる。

#### 【0053】

また、基板 101 として、可撓性基板を用い、可撓性基板上に直接、トランジスタ 100 を形成してもよい。または、基板 101 とトランジスタ 100 の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板 101 より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ 100 は耐熱性の劣る基板や可撓性の基板にも転載できる。10

#### 【0054】

ゲート電極 103 は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いてもよい。また、ゲート電極 103 は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。20

#### 【0055】

また、ゲート電極 103 は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。30

#### 【0056】

本実施の形態では、ゲート電極 103 をゲート電極 103a とゲート電極 103b の積層とする例を示している。ゲート電極 103a およびゲート電極 103b の厚さは、 $5\text{nm}$  以上  $500\text{nm}$  以下、より好ましくは  $10\text{nm}$  以上  $300\text{nm}$  以下、より好ましくは  $10\text{nm}$  以上  $200\text{nm}$  以下とするとよい。

#### 【0057】

ゲート絶縁膜 104 は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたは Ga - Zn 系金属酸化物、窒化シリコンなどを用いればよく、積層または単層で設ける。

#### 【0058】

また、ゲート絶縁膜 104 として、ハフニウムシリケート ( $\text{HfSiO}_x$ )、窒素が添加されたハフニウムシリケート ( $\text{HfSi}_x\text{O}_y\text{N}_z$ )、窒素が添加されたハフニウムアルミニート ( $\text{HfAl}_x\text{O}_y\text{N}_z$ )、酸化ハフニウム、酸化イットリウムなどの hig h-k 材料を用いることでトランジスタのゲートリークを低減できる。40

#### 【0059】

ゲート絶縁膜 104 の厚さは、 $5\text{nm}$  以上  $400\text{nm}$  以下、より好ましくは  $10\text{nm}$  以上  $300\text{nm}$  以下、より好ましくは  $50\text{nm}$  以上  $250\text{nm}$  以下とするとよい。

#### 【0060】

酸化物半導体膜 105 は、代表的には、In - Ga 酸化物、In - Zn 酸化物、In - M - Zn 酸化物 (M は Al、Ga、Y、Zr、La、Ce、または Nd) がある。50

## 【0061】

なお、酸化物半導体膜105がIn-M-Zn酸化物であるとき、InおよびMの和を100 atomic %とした場合のInとMの原子数比率は、好ましくは、Inが25 atomic %以上、Mが75 atomic %未満、さらに好ましくは、Inが34 atomic %以上、Mが66 atomic %未満とする。

## 【0062】

酸化物半導体膜105は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタのオフ電流を低減することができる。

## 【0063】

酸化物半導体膜105の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

## 【0064】

酸化物半導体膜105がIn-M-Zn酸化物(MはAl、Ga、Y、Zr、La、Ce、またはNd)の場合、In-M-Zn酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In>M、Zn>Mを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:M:Zn=1:1:1、In:M:Zn=3:1:2が好ましい。なお、成膜される酸化物半導体膜105の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。なお、酸化物半導体膜105に含まれるInの含有量が多いと、トランジスタのオン電流が増大し、電界効果移動度が高まる。このため、酸化物半導体膜105として、金属元素の原子数比がIn:M:Zn=3:1:2のIn-M-Zn酸化物のスパッタリングターゲットを用いて形成することで、電気特性の優れたトランジスタを作製することができる。

## 【0065】

酸化物半導体膜105としては、キャリア密度の低い酸化物半導体膜を用いる。例えば、酸化物半導体膜105は、キャリア密度が $1 \times 10^{17}$ 個/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ 個/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{13}$ 個/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{11}$ 個/cm<sup>3</sup>以下の酸化物半導体膜を用いる。

## 【0066】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性(電界効果移動度、しきい値電圧等)に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体膜105のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

## 【0067】

なお、酸化物半導体膜105として、不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を用いることで、さらに優れた電気特性を有するトランジスタを作製することができ好ましい。ここでは、不純物濃度が低く、欠陥準位密度の低い(酸素欠損の少ない)ことを「高純度真性」または「実質的に高純度真性」とよぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6$ μmでチャネル長Lが10μmの素子であっても、ソース電極とドレイン電極間の電圧(ドレイン電圧)が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$ A以下という特性を得ることができる。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジス

10

20

30

40

50

タは、電気特性の変動が小さく、信頼性の高いトランジスタとなる場合がある。なお、酸化物半導体膜のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

#### 【0068】

酸化物半導体膜に含まれる水素は金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。10

#### 【0069】

このため、酸化物半導体膜105は水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜105において、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる水素濃度を、 $2 \times 10^{20}$  atoms / cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>以下、 $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以下とする。20

#### 【0070】

酸化物半導体膜105において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体膜105において酸素欠損が増加し、n型化してしまう。このため、酸化物半導体膜105におけるシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms / cm<sup>3</sup>以下とする。

#### 【0071】

また、酸化物半導体膜105において、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜105のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。30

#### 【0072】

また、酸化物半導体膜105に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。従って、当該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下にすることが好ましい。40

#### 【0073】

また、酸化物半導体膜105は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、後述するC A A C - O S ( C Axis Aligned Crystalline Oxide Semiconductor)、多結晶構造、後述する微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、C A A C - O S は最も欠陥準位密度が低い。

#### 【0074】

酸化物半導体膜105は、例えば非晶質構造でもよい。非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。50

## 【0075】

なお、酸化物半導体膜105が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAC-O<sub>S</sub>の領域、単結晶構造の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAC-O<sub>S</sub>の領域、単結晶構造の領域のいずれか二種以上の領域を有する場合がある。また、混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAC-O<sub>S</sub>の領域、単結晶構造の領域のいずれか二種以上の領域の積層構造を有する場合がある。

## 【0076】

一対の電極106、電極107は、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タングステン膜上にアルミニウム膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造、タングステン膜上に銅膜を積層し、さらにその上にタングステン膜を形成する三層構造等がある。

## 【0077】

なお、インジウム錫酸化物、亜鉛酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの酸素を含む導電性材料、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を用いてもよい。また、前述した金属元素を含む材料と、酸素を含む導電性材料を組み合わせた積層構造とすることもできる。また、前述した金属元素を含む材料と、窒素を含む導電性材料を組み合わせた積層構造とすることもできる。また、前述した金属元素を含む材料、酸素を含む導電性材料、および窒素を含む導電性材料を組み合わせた積層構造とすることもできる。

## 【0078】

本実施の形態では、電極106を、電極106a、電極106b、および電極106cの積層とする例を示している。また、電極106bに銅を含む材料を用い、電極106bを電極106aと電極106cで包むことにより、銅が酸化物半導体膜105への拡散することを防ぐことができる。具体的に、本実施の形態に開示するトランジスタ100では、電極106aと電極106cが電極106bの端部を超えて延伸し、電極106bの外側で接する構成とすることで、電極106bを電極106aと電極106cで完全に包んでいる。

## 【0079】

電極106aおよび電極106cは、電極106bよりも融点が高い材料を用いて形成することが好ましい。例えば、電極106bに銅を含む材料を用いる場合、電極106aおよび電極106cは、タングステン、チタン、モリブデン、クロム、タンタルなどの銅よりも融点が高い金属元素を含む材料を用いて形成することが好ましい。

## 【0080】

電極106bに銅を含む材料を用いることにより電極106の抵抗を低減することができる。また、電極106と同一工程で同時に形成される他の電極および配線の抵抗も低減することができるため、信号のなまりが軽減され、電気特性の良好な半導体装置を実現することができる。また、電極106bを電極106aと電極106cで包むことで、銅の拡散を防ぎ、半導体装置の信頼性を向上することができる。

## 【0081】

10

20

30

40

50

電極 106a、電極 106b、および電極 106c の厚さは、それぞれ、5 nm 以上 500 nm 以下、より好ましくは 10 nm 以上 300 nm 以下、より好ましくは 10 nm 以上 200 nm 以下とするとよい。

#### 【0082】

また、本実施の形態では、電極 107 を、電極 107a、電極 107b、および電極 107c の積層とする例を示している。電極 107a、電極 107b、および電極 107c は、それぞれ、電極 106a、電極 106b、および電極 106c と同一工程で同時に作製することができる。

#### 【0083】

酸化物絶縁膜 108 は、酸素を透過する酸化物絶縁膜である。なお、酸化物絶縁膜 108 は、後に形成する酸化物絶縁膜 109 を形成する際の、酸化物半導体膜 105 へのダメージ緩和膜としても機能する。10

#### 【0084】

酸化物絶縁膜 108 としては、厚さが 5 nm 以上 150 nm 以下、好ましくは 5 nm 以上 50 nm 以下の酸化シリコン、酸化窒化シリコン等を用いることができる。なお、本明細書中において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

#### 【0085】

また、酸化物絶縁膜 108 は、欠陥量が少ないことが好ましく、代表的には、E S R 測定により、シリコンのダンギリングボンドに由来する  $g = 2.001$  に現れる信号のスピントン密度が  $3 \times 10^{17} \text{ spins/cm}^3$  以下であることが好ましい。これは、酸化物絶縁膜 108 に含まれる欠陥密度が多いと、当該欠陥に酸素が結合してしまい、酸化物絶縁膜 108 における酸素の透過量が減少してしまうためである。20

#### 【0086】

また、酸化物絶縁膜 108 と酸化物半導体膜 105との界面における欠陥量が少ないことが好ましく、代表的には、E S R 測定により、酸化物半導体膜 105 の欠陥に由来する  $g = 1.93$  に現れる信号のスピントン密度が  $1 \times 10^{17} \text{ spins/cm}^3$  以下、さらには検出下限以下であることが好ましい。

#### 【0087】

なお、酸化物絶縁膜 108 においては、外部から酸化物絶縁膜 108 に入った酸素が全て酸化物絶縁膜 108 の外部に移動せず、酸化物絶縁膜 108 にとどまる酸素もある。また、酸化物絶縁膜 108 に酸素が入ると共に、酸化物絶縁膜 108 に含まれる酸素が酸化物絶縁膜 108 の外部へ移動することで、酸化物絶縁膜 108 において酸素の移動が生じる場合もある。30

#### 【0088】

酸化物絶縁膜 108 として酸素を透過する酸化物絶縁膜を形成すると、酸化物絶縁膜 108 上に設けられる、酸化物絶縁膜 109 から脱離する酸素を、酸化物絶縁膜 108 を介して酸化物半導体膜 105 に移動させることができる。

#### 【0089】

酸化物絶縁膜 108 に接するように酸化物絶縁膜 109 が形成されている。酸化物絶縁膜 109 は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、T D S 分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18} \text{ atoms/m}^2 \text{ cm}^3$  以上、好ましくは  $3.0 \times 10^{20} \text{ atoms/m}^2 \text{ cm}^3$  以上である酸化物絶縁膜である。なお、上記 T D S 分析時における基板温度としては 100 以上 700 以下、または 100 以上 500 以下の範囲が好ましい。40

#### 【0090】

酸化物絶縁膜 109 としては、厚さが 30 nm 以上 500 nm 以下、好ましくは 50 nm 以下、または 100 以上 500 以下の範囲が好ましい。50

以上 400 nm 以下の、酸化シリコン、酸化窒化シリコン等を用いることができる。

**【0091】**

また、酸化物絶縁膜 109 は、欠陥量が少ないことが好ましく、代表的には、 ESR 測定により、シリコンのダンギリングボンドに由来する  $g = 2.001$  に現れる信号のスピニ密度が  $1.5 \times 10^{18} \text{ spins/cm}^3$  未満、更には  $1 \times 10^{18} \text{ spins/cm}^3$  以下であることが好ましい。なお、酸化物絶縁膜 109 は、酸化物絶縁膜 108 と比較して酸化物半導体膜 105 から離れているため、酸化物絶縁膜 108 より、欠陥密度が多くともよい。

**【0092】**

さらに、酸化物絶縁膜 109 上に、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する窒化物絶縁膜 110 を設けることで、酸化物半導体膜 105 からの酸素の外部への拡散と、外部から酸化物半導体膜 105 への水素、水等の侵入を防ぐことができる。窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する窒化物絶縁膜の代わりに、酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

**【0093】**

なお、保護膜 111 の構成は上記構成に限定されず、適宜酸化物絶縁膜または窒化物絶縁膜の単層、または積層とすることができる。または、2層、4層等の積層構造を適宜用いることができる。

**【0094】**

保護膜 111 上に形成するゲート電極 112 は、ゲート電極 103 と同様の材料および方法により形成することができる。

**【0095】**

<半導体装置の作製方法>

次に、図 1 に示すトランジスタ 100 の作製方法について、図 2 および図 3 を用いて説明する。なお、図 2 および図 3 は、図 1 (A) 中の一点鎖線 A1 - A2 で示す部位の断面に相当する。

**【0096】**

図 2 (A) に示すように、基板 101 上にゲート電極 103 を形成し、ゲート電極 103 上にゲート絶縁膜 104 を形成する。

**【0097】**

ここでは、基板 101 としてガラス基板を用いる。

**【0098】**

ゲート電極 103 の形成方法を以下に示す。はじめに、スパッタリング法、CVD 法、蒸着法等により、ゲート電極 103a およびゲート電極 103b となる導電膜を積層し、該導電膜上にフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いてゲート電極 103a およびゲート電極 103b となる導電膜の一部をエッチングして、ゲート電極 103a およびゲート電極 103b で構成されるゲート電極 103 を形成する。

**【0099】**

なお、ゲート電極 103 は、上記形成方法の代わりに、電解メッキ法、印刷法、インクジェット法等で形成してもよい。

**【0100】**

ここでは、厚さ 35 nm のチタン膜及び厚さ 200 nm の銅膜をスパッタリング法により順に形成する。次に、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて、銅膜の一部をウエットエッチング法により除去し、続いてチタン膜の一部をドライエッチング法により除去して、ゲート電極 103a およびゲート電極 103b を形成する。

10

20

30

40

50

この後、マスクを除去する。なお、ドライエッティング法によりエッティングを行った場合、マスクを除去する前にアッシング処理を行うと、剥離液を用いたマスクの除去を容易とすることができる。

#### 【0101】

また、ゲート電極103を、遮光性を有する導電性材料を用いて形成することで、バックライトなどの光源からの光が、ゲート電極103側から酸化物半導体膜105に到達しにくくすることができる。その結果、光照射によるトランジスタの電気特性の変動を抑制することができる。特に、ゲート電極103を、ゲート電極103の端部が酸化物半導体膜105の端部より外側に位置するように設けることで、光照射によるトランジスタの電気特性の変動をより抑制することができる。図4(A)に、ゲート電極103の端部が酸化物半導体膜105の端部より外側に位置するトランジスタ150の断面図を示す。10

#### 【0102】

ゲート絶縁膜104は、スパッタリング法、CVD法、蒸着法等で形成することができる。。

#### 【0103】

ゲート絶縁膜104として酸化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜を形成する場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。20

#### 【0104】

また、ゲート絶縁膜104は、窒化物絶縁膜と酸化物絶縁膜をゲート電極103側から順に積層する積層構造としてもよい。ゲート電極103側に窒化物絶縁膜を設けることで、ゲート電極103からの不純物、代表的には、水素、窒素、アルカリ金属、またはアルカリ土類金属等が酸化物半導体膜105に移動することを防ぐことができる。また、酸化物半導体膜105側に酸化物絶縁膜を設けることで、ゲート絶縁膜104及び酸化物半導体膜105界面における欠陥準位を低減することが可能である。この結果、電気特性の劣化の少ないトランジスタを得ることができる。なお、酸化物絶縁膜として、酸化物絶縁膜109と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成すると、ゲート絶縁膜104及び酸化物半導体膜105界面における欠陥準位をさらに低減することができるため好ましい。30

#### 【0105】

図4(B)に、トランジスタ100のゲート絶縁膜104を、ゲート絶縁膜104aとゲート絶縁膜104bの積層としたトランジスタ200の断面図を示す。例えば、ゲート電極103側に設けるゲート絶縁膜104aを窒化物絶縁膜とし、酸化物半導体膜105側に設けるゲート絶縁膜104bを酸化物絶縁膜とし、ゲート絶縁膜104bよりもゲート絶縁膜104aの膜厚を厚くする。

#### 【0106】

窒化物絶縁膜は酸化物絶縁膜よりも比誘電率が大きいため、ゲート絶縁膜104aの膜厚を厚くしても、ゲート電極103に生じる電界を効率よく酸化物半導体膜105に伝えることができる。また、ゲート絶縁膜104全体を厚くすることで、ゲート絶縁膜104の絶縁耐圧を高めることができる。よって、半導体装置の信頼性を高めることができる。40

#### 【0107】

また、ゲート絶縁膜104は、欠陥の少ない第1の窒化物絶縁膜と、水素プロッキング性の高い第2の窒化物絶縁膜と、酸化物絶縁膜とが、ゲート電極103側から順に積層される積層構造とすることができます。ゲート絶縁膜104に、欠陥の少ない第1の窒化物絶縁膜を用いることで、ゲート絶縁膜104の絶縁耐圧を向上させることができます。また、ゲート絶縁膜104に、水素プロッキング性の高い第2の窒化物絶縁膜を設けることで、ゲート電極103及び第1の窒化物絶縁膜に含まれる水素が酸化物半導体膜105に移動することを防ぐことができる。50

## 【0108】

第1の窒化物絶縁膜、第2の窒化物絶縁膜の作製方法の一例を以下に示す。はじめに、シラン、窒素、及びアンモニアの混合ガスを原料ガスとして用いたプラズマCVD法により、欠陥の少ない窒化シリコン膜を第1の窒化物絶縁膜として形成する。次に、原料ガスを、シラン及び窒素の混合ガスに切り替えて、水素濃度が少なく、且つ水素をブロッキングすることが可能な窒化シリコン膜を第2の窒化物絶縁膜として成膜する。このような形成方法により、欠陥が少なく、且つ水素のブロッキング性を有する窒化物絶縁膜が積層されたゲート絶縁膜104を形成することができる。

## 【0109】

また、ゲート絶縁膜104は、不純物のブロッキング性が高い第3の窒化物絶縁膜と、欠陥の少ない第1の窒化物絶縁膜と、水素ブロッキング性の高い第2の窒化物絶縁膜と、酸化物絶縁膜とが、ゲート電極103側から順に積層される積層構造とすることができます。ゲート絶縁膜104に、不純物のブロッキング性が高い第3の窒化物絶縁膜を設けることで、ゲート電極103からの不純物、代表的には、水素、窒素、アルカリ金属、またはアルカリ土類金属等が酸化物半導体膜105に移動することを防ぐことができる。

10

## 【0110】

第1の窒化物絶縁膜乃至第3の窒化物絶縁膜の作製方法の一例を以下に示す。はじめに、シラン、窒素、及びアンモニアの混合ガスを原料ガスとして用いたプラズマCVD法により、不純物のブロッキング性が高い窒化シリコン膜を第3の窒化物絶縁膜として形成する。次に、アンモニアの流量の増加させることで、欠陥の少ない窒化シリコン膜を第1の窒化物絶縁膜として形成する。次に、原料ガスを、シラン及び窒素の混合ガスに切り替えて、水素濃度が少なく、且つ水素をブロッキングすることが可能な窒化シリコン膜を第2の窒化物絶縁膜として成膜する。このような形成方法により、欠陥が少なく、且つ不純物のブロッキング性を有する窒化物絶縁膜が積層されたゲート絶縁膜104を形成することができる。

20

## 【0111】

また、ゲート絶縁膜104として酸化ガリウム膜を形成する場合、MOCVD (Meta l Organic Chemical Vapor Deposition) 法を用いて形成することができる。

## 【0112】

30

なお、必要に応じて、基板101及びゲート電極103の間に下地絶縁膜として機能する絶縁膜を設けることができる。該絶縁膜としては、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、該絶縁膜として、窒化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム等を用いることで、基板101から不純物、代表的にはアルカリ金属、水、水素等の酸化物半導体膜105への拡散を抑制することができる。

## 【0113】

下地絶縁膜として機能する絶縁膜は、スパッタリング法、CVD法等により形成することができる。

40

## 【0114】

次に、図2(B)に示すように、ゲート絶縁膜104上に酸化物半導体膜105を形成する。

## 【0115】

酸化物半導体膜105の形成方法について、以下に説明する。ゲート絶縁膜104上に、酸化物半導体膜105となる酸化物半導体膜を形成する。次に、酸化物半導体膜上にフォトリソグラフィ工程によりマスクを形成した後、該マスクを用いて酸化物半導体膜の一部をエッチングすることで、図2(B)に示すような、素子分離された酸化物半導体膜を形成する。

## 【0116】

50

酸化物半導体膜 105 となる酸化物半導体膜は、スパッタリング法、塗布法、パルスレーザー蒸着法、レーザーアブレーション法、CVD法等を用いて形成することができる。

#### 【0117】

なお、酸化物半導体膜を形成する場合、スパッタリング法でプラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。

#### 【0118】

スパッタリングガスは、希ガス（代表的にはアルゴン）雰囲気、酸素雰囲気、希ガス及び酸素の混合ガスを適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。

#### 【0119】

また、スパッタリングターゲットは、形成する酸化物半導体膜の組成にあわせて、適宜選択すればよい。

#### 【0120】

高純度真性または実質的に高純度真性である酸化物半導体膜を得るために、チャンバー内を高真空排氣するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が -40 以下、好ましくは -80 以下、より好ましくは -100 以下、より好ましくは -120 以下にまで高純度化したガスを用いることで酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

#### 【0121】

ここでは、酸化物半導体膜として、原子数比で In : Ga : Zn = 1 : 1 : 1 の In-Ga-Zn 酸化物ターゲットを用いたスパッタリング法により、厚さ 35 nm の In-Ga-Zn 酸化物膜を形成する。次に、該酸化物半導体膜上にマスクを形成し、該酸化物半導体膜の一部を選択的にエッチングすることで、酸化物半導体膜 105 を形成する。

#### 【0122】

こののち、第 1 の加熱処理を行ってもよい。第 1 の加熱処理によって、酸化物半導体膜 105 に含まれる水素、水等を脱離させ、酸化物半導体膜 105 に含まれる水素濃度及び水濃度を低減することができる。該加熱処理の温度は、代表的には、300 以上 400 以下、好ましくは 320 以上 370 以下とする。

#### 【0123】

第 1 の加熱処理は、電気炉、RTA 装置等を用いることができる。RTA 装置を用いることで、短時間に限り、基板の歪み点以上の温度で熱処理を行うことができる。そのため加熱処理時間を短縮することができる。

#### 【0124】

第 1 の加熱処理は、窒素、酸素、超乾燥空気（水の含有量が 20 ppm 以下、好ましくは 1 ppm 以下、好ましくは 10 ppb 以下の空気）、または希ガス（アルゴン、ヘリウム等）の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい。また、窒素または希ガス雰囲気で加熱処理した後、酸素または超乾燥空気雰囲気で加熱してもよい。この結果、酸化物半導体膜 105 中に含まれる水素、水等を脱離させると共に、酸化物半導体膜 105 中に酸素を供給することができる。この結果、酸化物半導体膜 105 中に含まれる酸素欠損量を低減することができる。

#### 【0125】

次に、図 2 (C) に示すように、電極 106a および電極 107a となる導電膜 126a と、電極 106b および電極 107b となる導電膜 126b を順に形成する。導電膜 126a および導電膜 126b は、スパッタリング法、CVD 法、蒸着法等を用いて形成する。

#### 【0126】

なお、電極 106a および電極 107a となる導電膜 126a は、タンゲステン、チタン、モリブデン、クロム、またはタンタル単体若しくはタンタル合金等の、酸素と結合しや

10

20

30

40

50

すい金属元素を含む導電材料を用いることが好ましい。この結果、酸化物半導体膜105に含まれる酸素と電極106aおよび電極107aを形成する導電材料とが結合し、酸化物半導体膜105において、酸素欠損領域が形成される。また、酸化物半導体膜105に電極106aおよび電極107aを形成する導電材料の構成元素の一部が混入する場合もある。これらの結果、酸化物半導体膜105中の、電極106aおよび電極107aと接する領域近傍に、低抵抗領域が形成される。低抵抗領域は、導電性が高いため、酸化物半導体膜105と電極106aおよび電極107aとの接触抵抗を低減することが可能であり、トランジスタのオン電流を増大させることが可能となる。

#### 【0127】

また、電極106aおよび電極107aを、上記酸素と結合しやすい導電材料と、窒化チタン、窒化タンタル、ルテニウム等の酸素と結合しにくい導電材料との積層構造としてもよい。

10

#### 【0128】

本実施の形態では、導電膜126aとして厚さ30nmのタンゲステン膜をスパッタリング法により形成する。また、導電膜126bとして厚さ200nmの銅膜をスパッタリング法により形成する。また、導電膜126b上に、フォトリソグラフィ工程によりマスク131を形成する。

#### 【0129】

次に、図2(D)に示すように、マスク131を用いて導電膜126bの一部をエッチングし、電極106bおよび電極107bを形成する。導電膜126bのエッチングは、ドライエッティング法でもウエットエッティング法でもよく、両方を用いてもよい。本実施の形態では、ウエットエッティング法により導電膜126bの一部を除去して、電極106bおよび電極107bを形成する。

20

#### 【0130】

電極106bおよび電極107bの形成工程において、エッティング溶液中に溶け出した導電膜126bを構成する金属元素の一部が導電膜126aに付着する場合がある。本実施の形態では、導電膜126bとして銅を含む材料を用いるため、導電膜126a上に銅が残留もしくは再付着する。しかしながら、導電膜126aがブロッキング層として機能し、該金属元素が酸化物半導体膜105に移動することを防ぐことができる。

#### 【0131】

30

次に、電極106b、電極107b、および導電膜126aを覆って、導電膜126cを形成する。導電膜126cは、導電膜126aと同様の材料を用いて形成してもよいし、異なる材料を用いて形成してもよい。本実施の形態では、導電膜126cとして厚さ30nmのタンゲステン膜をスパッタリング法により形成する。なお、前述した、導電膜126a上に付着した金属元素は、導電膜126aと導電膜126cの界面に残存する。

#### 【0132】

次に、図3(A)に示すように、導電膜126c上に、フォトリソグラフィ工程によりマスク132を形成する。マスク132は、電極106bおよび電極107bを完全に覆うように、電極106bおよび電極107bの端部を超えて形成する。

40

#### 【0133】

続いて、図3(B)に示すように、マスク132を用いて導電膜126aおよび導電膜126cの一部を選択的に除去する。導電膜126aおよび導電膜126cのエッティングは、ドライエッティング法でもウエットエッティング法でもよく、両方を用いてもよい。本実施の形態では、ドライエッティング法により導電膜126aおよび導電膜126cの一部を除去して、電極106a、電極106c、電極107a、および電極107cを形成する。

#### 【0134】

このようにして、電極106および電極107を形成することができる。また、電極106および電極107の形成により、酸化物半導体膜105の一部が露出する。図3(B)に、電極106および電極107の形成により露出された領域を、領域133として示す。

50

**【 0 1 3 5 】**

また、導電膜 126a と導電膜 126c のエッチングにより、導電膜 126a と導電膜 126c の界面に残っていた金属元素（本実施の形態では銅元素。）が領域 133 に付着し、領域 133 の表面および表面近傍が汚染される。

**【 0 1 3 6 】**

特に、ドライエッチング法により導電膜 126a と導電膜 126c をエッチングする場合は、エッチング条件によって導電膜 126a と導電膜 126c のみがエッチングされやすくなる。このため、導電膜 126a と導電膜 126c の界面に残っていた金属元素が、露出した酸化物半導体膜 105 表面に再付着しやすい。よって、導電膜 126a と導電膜 126c のエッチング後に、領域 133 に付着した該金属元素を除去するための洗浄処理を行なうことが好ましい。10

**【 0 1 3 7 】**

当該洗浄処理は、例えば TMAH (Tetramethylammonium Hydroxide) 溶液などのアルカリ性の溶液、希フッ酸、シュウ酸、リン酸などの酸性の溶液、またはプラズマ処理（酸素プラズマ処理など）により行なうことができる。本実施の形態では、リン酸を 0.85 wt % 含む水溶液を用いて、30 秒間の洗浄処理を行う。

**【 0 1 3 8 】**

なお、図 3 (C) に示すように、当該洗浄処理により領域 133 の酸化物半導体膜 105 の一部がエッチングされ、酸化物半導体膜 105 の他の部分よりも厚さが薄くなる場合がある。また、当該洗浄処理は、導電膜 126a と導電膜 126c のエッチング後であれば20、マスク 132 の除去前に行なってもよいし、除去後に行なってもよい。

**【 0 1 3 9 】**

また、当該洗浄処理の後、酸化物半導体膜 105 を酸素雰囲気で発生させたプラズマに曝し、酸化物半導体膜 105 に酸素を供給することができる。酸化雰囲気としては、酸素、オゾン、一酸化二窒素、二酸化窒素等の雰囲気がある。さらに、当該プラズマ処理において、基板 101 側にバイアスを印加しない状態で発生したプラズマに酸化物半導体膜 105 を曝すことが好ましい。この結果、酸化物半導体膜 105 にダメージを与えることなく、且つ酸素を供給することができる。また、エッチング処理により酸化物半導体膜 105 の表面に残存する不純物、例えば、フッ素、塩素等のハロゲン等を除去することができる。また、当該プラズマ処理を 300 以上で加熱しながら行なうことが好ましい。プラズマ中の酸素と酸化物半導体膜 105 に含まれる水素が結合し、水となる。基板が加熱されているため、当該水は酸化物半導体膜 105 から脱離する。この結果、酸化物半導体膜 105 に含まれる水素及び水の含有量を低減することができる。30

**【 0 1 4 0 】**

次に、図 3 (D) に示すように、酸化物半導体膜 105、電極 106、および電極 107 の上に、酸化物絶縁膜 108 を形成する。次に、酸化物絶縁膜 108 上に酸化物絶縁膜 109 を形成する。

**【 0 1 4 1 】**

なお、酸化物絶縁膜 108 を形成した後、大気に曝すことなく、連続的に酸化物絶縁膜 109 を形成することが好ましい。酸化物絶縁膜 108 を形成した後、大気開放せず、原料ガスの流量、圧力、高周波電力及び基板温度の一以上を調整して、酸化物絶縁膜 109 を連続的に形成することで、酸化物絶縁膜 108 及び酸化物絶縁膜 109 における界面の大気成分由来の不純物濃度を低減することができると共に、酸化物絶縁膜 109 に含まれる酸素を酸化物半導体膜 105 に移動させることができ、酸化物半導体膜 105 の酸素欠損量を低減することができる。40

**【 0 1 4 2 】**

酸化物絶縁膜 108 としては、酸化シリコン膜または酸化窒化シリコン膜を用いることが好ましい。酸化物絶縁膜 108 に用いる酸化シリコン膜または酸化窒化シリコン膜は、例えば、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 280 以上50

0.0 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を 2.0 Pa 以上 25.0 Pa 以下、さらに好ましくは 10.0 Pa 以上 25.0 Pa 以下とし、処理室内に設けられる電極に高周波電力を供給する条件により形成することができる。

【 0 1 4 3 】

酸化シリコン膜または酸化窒化シリコン膜を形成するための原料ガスとして、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

【 0 1 4 4 】

上記条件を用いることで、酸化物絶縁膜 108 として酸素を透過する酸化物絶縁膜を形成することができる。また、酸化物絶縁膜 108 を設けることで、酸化物絶縁膜 109 の形成工程における酸化物半導体膜 105 へのダメージを低減することが可能である。

【 0 1 4 5 】

当該成膜条件において、基板温度を上記温度とすることで、シリコン及び酸素の結合力が強くなる。この結果、酸化物絶縁膜 108 として、酸素が透過し、緻密であり、且つ硬い酸化物絶縁膜、代表的には、25 °C において 0.5 重量 % のフッ酸を用いた場合のエッチング速度が 10 nm / 分以下、好ましくは 8 nm / 分以下の酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

【 0 1 4 6 】

また、加熱をしながら酸化物絶縁膜 108 を形成することで、当該工程において酸化物半導体膜 105 に含まれる水素、水等を脱離させることができる。具体的には、基板 101 を 280 以上 400 以下に保持しながら酸化物絶縁膜 108 を形成することで、酸化物半導体膜 105 に含まれる水素、水等を脱離させることができる。酸化物半導体膜 105 に含まれる水素は、プラズマ中で発生した酸素ラジカルと結合し、水となる。酸化物絶縁膜 108 の成膜工程において基板が加熱されているため、酸素及び水素の結合により生成された水は、酸化物半導体膜から脱離する。即ち、プラズマ CVD 法によって酸化物絶縁膜 108 を形成することで、酸化物半導体膜に含まれる水及び水素の含有量を低減することができる。

【 0 1 4 7 】

また、酸化物絶縁膜 108 を形成する工程において加熱するため、酸化物半導体膜 105 が露出された状態での加熱時間が少なく、加熱処理による酸化物半導体膜からの酸素の脱離量を低減することができる。即ち、酸化物半導体膜中に含まれる酸素欠損量を低減することができる。

【 0 1 4 8 】

さらには、処理室の圧力を100Pa以上250Pa以下とすることで、酸化物絶縁膜108に含まれる水の含有量が少なくなるため、トランジスタ100の電気特性のばらつきを低減すると共に、しきい値電圧の変動を抑制することができる。

【 0 1 4 9 】

また、処理室の圧力を100Pa以上250Pa以下とすることで、酸化物絶縁膜108を成膜する際に、酸化物半導体膜105へのダメージを低減することが可能であり、酸化物半導体膜105に含まれる酸素欠損量を低減することができる。特に、酸化物絶縁膜108または後に形成される酸化物絶縁膜109の成膜温度を高くする、代表的には220より高い温度とすることで、酸化物半導体膜105に含まれる酸素の一部が脱離し、酸素欠損が形成されやすい。

〔 0 1 5 0 〕

また、トランジスタの信頼性を高めるため、後に形成する酸化物絶縁膜 109 を、膜中の欠陥量が少ない成膜条件を用いて形成すると、酸化物絶縁膜 109 からの酸素脱離量が低減しやすくなる。すると、酸化物絶縁膜 109 からの酸素供給により、酸化物半導体膜 105 の酸素欠損を補填することが困難となる場合がある。しかしながら、処理室の圧力を 100 Pa 以上 250 Pa 以下とし、酸化物絶縁膜 108 の成膜時における酸化物半導体

膜 105へのダメージを低減することで、酸化物絶縁膜109からの酸素供給量が少なくとも、酸化物半導体膜105中の酸素欠損を低減することが可能となる。

#### 【0151】

なお、シリコンを含む堆積性気体に対する酸化性気体量を100倍以上とすることで、酸化物絶縁膜108に含まれる水素含有量を低減することが可能である。この結果、酸化物半導体膜105に混入する水素量を低減できるため、トランジスタのしきい値電圧のマイナスシフトを抑制することができる。

#### 【0152】

本実施の形態では、酸化物絶縁膜108として、シラン及び一酸化二窒素を原料ガスとしたプラズマCVD法により、厚さ50nmの酸化窒化シリコン膜を形成する。当該条件により、酸素が透過する酸化窒化シリコン膜を形成することができる。10

#### 【0153】

酸化物絶縁膜109としては、酸化シリコン膜または酸化窒化シリコン膜を用いることが好ましい。酸化物絶縁膜109に用いる酸化シリコン膜または酸化窒化シリコン膜は、例えば、プラズマCVD装置の真空排気された処理室内に載置された基板を180以上280以下、さらに好ましくは200以上240以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm<sup>2</sup>以上0.5W/cm<sup>2</sup>以下、さらに好ましくは0.25W/cm<sup>2</sup>以上0.35W/cm<sup>2</sup>以下の高周波電力を供給する条件により形成することができる。20

#### 【0154】

酸化物絶縁膜109の成膜条件として、上記圧力の反応室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、酸化物絶縁膜109中における酸素含有量が化学量論比よりも多くなる。一方、基板温度が、上記温度で形成された膜では、シリコンと酸素の結合力が弱いため、後の工程の加熱処理により膜中の酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化物絶縁膜を形成することができる。また、酸化物半導体膜105上に酸化物絶縁膜108が設けられている。このため、酸化物絶縁膜109の形成工程において、酸化物絶縁膜108が酸化物半導体膜105の保護膜となる。この結果、酸化物半導体膜105へのダメージを低減しつつ、パワー密度の高い高周波電力を用いて酸化物絶縁膜109を形成することができる。30

#### 【0155】

なお、酸化物絶縁膜109の成膜条件において、酸化性気体に対するシリコンを含む堆積性気体の流量を増加することで、酸化物絶縁膜109の欠陥量を低減することが可能である。代表的には、ESR測定により、シリコンのダンギングボンドに由来するg=2.001に現れる信号のスピントン密度が6×10<sup>17</sup>spins/cm<sup>3</sup>未満、好ましくは3×10<sup>17</sup>spins/cm<sup>3</sup>以下、好ましくは1.5×10<sup>17</sup>spins/cm<sup>3</sup>以下である欠陥量の少ない酸化物絶縁膜を形成することができる。この結果トランジスタの信頼性を高めることができる。40

#### 【0156】

本実施の形態では、酸化物絶縁膜109として、シラン及び一酸化二窒素を原料ガスとしたプラズマCVD法により、厚さ400nmの酸化窒化シリコン膜を形成する。

#### 【0157】

次に、加熱処理を行う。該加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。

#### 【0158】

該加熱処理は、電気炉、RTA装置等を用いることができる。RTA装置を用いることでの短時間に限り、基板の歪み点以上の温度で熱処理を行うことができる。そのため加熱処理時間を短縮することができる。50

**【 0 1 5 9 】**

加熱処理は、窒素、酸素、超乾燥空気（水の含有量が 20 ppm 以下、好ましくは 1 ppm 以下、好ましくは 10 ppb 以下の空気）、または希ガス（アルゴン、ヘリウム等）の雰囲気下で行えればよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい。

**【 0 1 6 0 】**

当該加熱処理により、酸化物絶縁膜 109 に含まれる酸素の一部を酸化物半導体膜 105 に移動させ、酸化物半導体膜 105 に含まれる酸素欠損を補填することが可能である。この結果、酸化物半導体膜 105 に含まれる酸素欠損量をさらに低減することができる。

**【 0 1 6 1 】**

また、酸化物絶縁膜 108 及び酸化物絶縁膜 109 に水、水素等が含まる場合、水、水素等をブロッキングする機能を有する窒化物絶縁膜 110 を後に形成し、加熱処理を行うと、酸化物絶縁膜 108 及び酸化物絶縁膜 109 に含まれる水、水素等が、酸化物半導体膜 105 に移動し、酸化物半導体膜 105 に欠陥が生じてしまう。しかしながら、当該加熱により、酸化物絶縁膜 108 及び酸化物絶縁膜 109 に含まれる水、水素等を脱離させることができあり、トランジスタの電気特性のばらつきを低減すると共に、しきい値電圧の変動を抑制することができる。

10

**【 0 1 6 2 】**

なお、加熱しながら酸化物絶縁膜 109 を、酸化物絶縁膜 108 上に形成することで、酸化物半導体膜 105 に酸素を移動させ、酸化物半導体膜 105 に含まれる酸素欠損を補填することができるため、当該加熱処理を行わなくともよい。

20

**【 0 1 6 3 】**

ここでは、窒素及び酸素の混合ガス雰囲気で、350℃、1時間の加熱処理を行う。

**【 0 1 6 4 】**

また、一対の電極 106、電極 107 を形成する際、導電膜のエッチングによって、酸化物半導体膜 105 はダメージを受け、酸化物半導体膜 105 のバックチャネル（酸化物半導体膜 105 において、ゲート電極 103 と対向する面と反対側の面）側に酸素欠損が生じる。しかし、酸化物絶縁膜 109 に化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を適用することで、加熱処理によって当該バックチャネル側に生じた酸素欠損を修復することができる。これにより、酸化物半導体膜 105 に含まれる欠陥を低減することができるため、トランジスタ 100 の信頼性を向上させることができる。

30

**【 0 1 6 5 】**

次に、スパッタリング法、CVD 法等により、窒化物絶縁膜 110 を形成する。

**【 0 1 6 6 】**

なお、窒化物絶縁膜 110 をプラズマ CVD 法で形成する場合、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 300℃ 以上 400℃ 以下、さらに好ましくは 320℃ 以上 370℃ 以下にとすることで、緻密な窒化物絶縁膜を形成できるため好ましい。

**【 0 1 6 7 】**

窒化物絶縁膜 110 としてプラズマ CVD 法により形成した窒化シリコン膜を用いる場合、原料ガスとして、シリコンを含む堆積性気体、窒素、及びアンモニアを用いことが好ましい。原料ガスとして、窒素と比較して少量のアンモニアを用いることで、プラズマ中でアンモニアが解離し、活性種が発生する。当該活性種が、シリコンを含む堆積性気体に含まれるシリコン及び水素の結合、及び窒素の三重結合を切断する。この結果、シリコン及び窒素の結合が促進され、シリコン及び水素の結合が少なく、欠陥が少なく、緻密な窒化シリコン膜を形成することができる。一方、原料ガスにおいて、窒素に対するアンモニアの量が多いと、シリコンを含む堆積性気体及び窒素それぞれの分解が進まず、シリコン及び水素結合が残存して膜中の欠陥が増大し、且つ粗な窒化シリコン膜が形成されてしまう。このため、原料ガスにおいて、アンモニアに対する窒素の流量比を 5 以上 50 以下、好ましくは 10 以上 50 以下とすることが好ましい。

40

50

**【0168】**

本実施の形態では、シラン、窒素、及びアンモニアを原料ガスとしたプラズマCVD法により、厚さ100nmの窒化シリコン膜を形成する。

**【0169】**

以上の工程により、酸化物絶縁膜108、酸化物絶縁膜109、及び窒化物絶縁膜110で構成される保護膜111を形成することができる。

**【0170】**

次に、加熱処理を行ってもよい。該加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。

10

**【0171】**

ゲート電極103及び後に形成するゲート電極112を電気的に接続させる場合は、ここで、ゲート絶縁膜104、酸化物絶縁膜108、酸化物絶縁膜109、及び窒化物絶縁膜110に開口部を形成する。

**【0172】**

次に、ゲート電極112を形成する。ゲート電極112の形成方法を以下に示す。はじめに、スパッタリング法、CVD法、蒸着法等により導電膜を形成し、導電膜上にフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜の一部をエッチングして、ゲート電極112を形成する。

**【0173】**

なお、図1(C)に示すように、チャネル幅方向において、酸化物半導体膜105の外側にゲート電極112の端部が位置するように、ゲート電極112を形成する。

20

**【0174】**

本実施の形態では、厚さ100nmの酸化シリコンを有するITO膜をスパッタリング法により形成する。次に、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて酸化シリコンを有するITO膜をウエットエッチングして、ゲート電極112を形成する。この後、加熱処理を行ってもよい。

**【0175】**

以上の工程により、トランジスタ100を作製することができる。

**【0176】**

本実施の形態に示すトランジスタは、第1のゲート電極及び第2のゲート電極の間に酸化物半導体膜が設けられるデュアルゲート構造のトランジスタであって、トランジスタのチャネル幅方向において、第1のゲート電極及び第2のゲート電極の端部はそれぞれ、酸化物半導体膜の端部より外側に位置することで、酸化物半導体膜105の端部に、ゲート電極112の電界の影響を与えることが可能であり、酸化物半導体膜105の全体をチャネルとして機能させることができる。この結果、トランジスタのオン電流を増大させると共に、電界効果移動度を高めることができる。

30

**【0177】**

また、本実施の形態に示すトランジスタは、第1のゲート電極及び第2のゲート電極を有するため、それぞれのゲート電極が外部からの電界を遮蔽することができる。この結果、ストレス試験の劣化が抑制されると共に、異なるドレイン電圧におけるオン電流の立ち上がり電圧の変動を抑制することができる。この結果、電気特性の優れたトランジスタを有する半導体装置を得ることができる。また、信頼性の高い半導体装置を得ることができる。

40

**【0178】**

本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及び方法などと適宜組み合わせて用いることができる。

**【0179】**

(実施の形態2)

実施の形態1に半導体装置の一例として示したトランジスタ100と異なる構成を有する

50

トランジスタ 250 について図面を参照して説明する。

**【0180】**

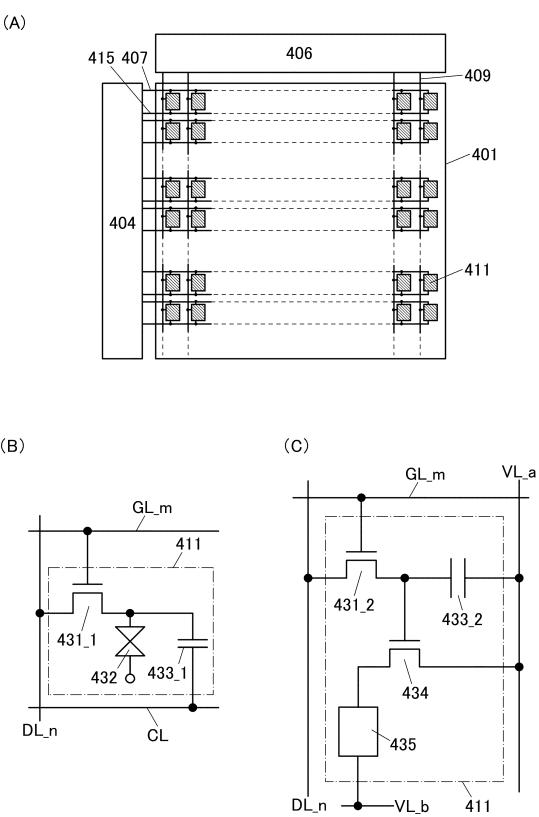

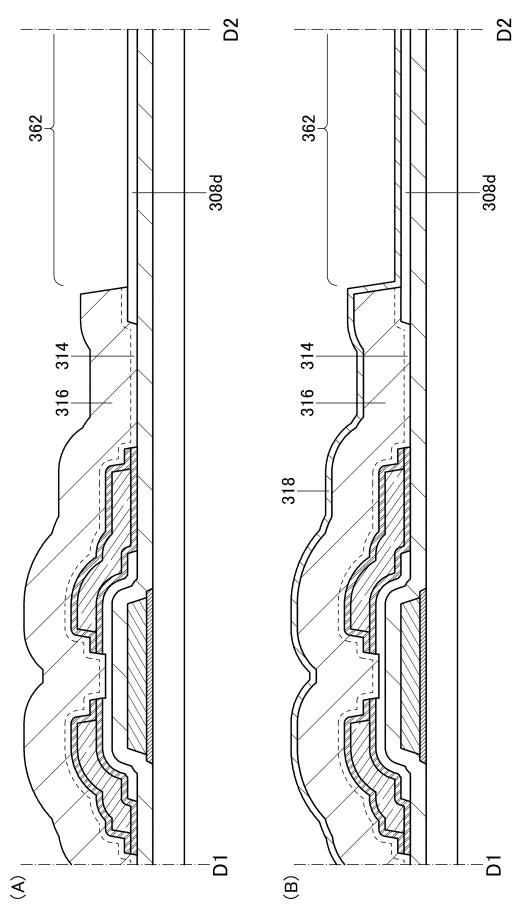

図5に、トランジスタ 250 の上面図及び断面図を示す。トランジスタ 250 は、チャネルエッチ型のトランジスタである。

**【0181】**

図5(A)はトランジスタ 250 の上面図である。また、図5(B)は、図5(A)中の一点鎖線 A3 - A4 で示す部位の断面図であり、図5(C)は、図5(A)中の一点鎖線 B3 - B4 で示す部位の断面図である。また、図5(D)は、図5(B)に示す部位 215 および部位 216 の拡大図である。なお、図5(B)は、トランジスタ 250 のチャネル長方向の断面であり、図5(C)は、トランジスタ 250 のチャネル幅方向の断面である。10

**【0182】**

トランジスタ 250 は、電極 106b および電極 107b の形状がトランジスタ 100 と異なる。トランジスタ 250 は、電極 106b および電極 107b を、ゲート電極 103 と重畠しないように形成することで段差を軽減し、上層に形成する絶縁膜や導電膜の被覆をより良好なものとすることができます。

**【0183】**

本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及び方法などと適宜組み合わせて用いることができる。

**【0184】**

(実施の形態 3)

本実施の形態では、本発明の一態様である半導体装置について、図面を用いて説明する。なお、本実施の形態では、表示装置を例にして本発明の一態様である半導体装置を説明する。また、本実施の形態では、半導体膜として酸化物半導体膜を用いて説明する。

**【0185】**

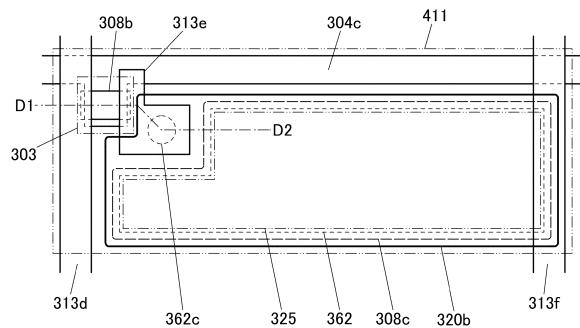

図6(A)に、半導体装置の一例を示す。図6(A)に示す半導体装置は、画素部 401 と、走査線駆動回路 404 と、信号線駆動回路 406 と、各々が平行または略平行に配設され、且つ走査線駆動回路 404 によって電位が制御される m 本の走査線 407 と、各々が平行または略平行に配設され、且つ信号線駆動回路 406 によって電位が制御される n 本の信号線 409 と、を有する。さらに、画素部 401 はマトリクス状に配設された複数の画素 411 を有する。また、走査線 407 に沿って、各々が平行または略平行に配設された容量線 415 を有する。なお、容量線 415 は、信号線 409 に沿って、各々が平行または略平行に配設されていてもよい。また、走査線駆動回路 404 及び信号線駆動回路 406 をまとめて駆動回路部という場合がある。30

**【0186】**

各走査線 407 は、画素部 401 において m 行 n 列に配設された画素 411 のうち、いずれかの行に配設された n 個の画素 411 と電気的に接続される。また、各信号線 409 は、m 行 n 列に配設された画素 411 のうち、いずれかの列に配設された m 個の画素 411 に電気的と接続される。m、n は、ともに 1 以上の整数である。また、各容量線 415 は、m 行 n 列に配設された画素 411 のうち、いずれかの行に配設された n 個の画素 411 と電気的に接続される。なお、容量線 415 が、信号線 409 に沿って、各々が平行または略平行に配設されている場合は、m 行 n 列に配設された画素 411 のうち、いずれかの列に配設された m 個の画素 411 に電気的と接続される。40

**【0187】**

図6(B)及び図6(C)は、図6(A)に示す表示装置の画素 411 に用いることができる回路構成を示している。

**【0188】**

図6(B)に示す画素 411 は、液晶素子 432 と、トランジスタ 431\_1 と、容量素子 433\_1 と、を有する。

**【0189】**

10

20

30

40

50

液晶素子432の一対の電極の一方の電位は、画素411の仕様に応じて適宜設定される。液晶素子432は、書き込まれるデータにより配向状態が設定される。なお、複数の画素411のそれぞれが有する液晶素子432の一対の電極の一方に共通の電位（コモン電位）を与えてもよい。また、各行の画素411毎の液晶素子432の一対の電極の一方に異なる電位を与えてよい。

#### 【0190】

例えば、液晶素子432を備える表示装置の駆動方法としては、TNモード、STNモード、VAモード、ASM(Axially Symmetric Aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(antiFerroelectric Liquid Crystal)モード、MVAモード、PVA(Patterned Vertical Alignment)モード、IPSモード、FFSモード、またはTBA(Transverse Bend Alignment)モードなどを用いてよい。

また、表示装置の駆動方法としては、上述した駆動方法の他、ECB(Electrically Controlled Birefringence)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、PNLC(Polymer Network Liquid Crystal)モード、ゲストホストモードなどがある。ただし、これに限定されず、液晶素子及びその駆動方式として様々なものを用いることができる。

20

#### 【0191】

また、ブルー相(Blue Phase)を示す液晶とカイラル剤とを含む液晶組成物により液晶素子を構成してもよい。ブルー相を示す液晶は、応答速度が1 msec以下と短く、光学的等方性であるため、配向処理が不要であり、かつ、視野角依存性が小さい。

#### 【0192】

m行n列目の画素411において、トランジスタ431\_1のソース電極及びドレイン電極の一方は、信号線DL\_nに電気的に接続され、他方は液晶素子432の一対の電極の他方に電気的に接続される。また、トランジスタ431\_1のゲート電極は、走査線GL\_mに電気的に接続される。トランジスタ431\_1は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

30

#### 【0193】

容量素子433\_1の一対の電極の一方は、電位が供給される配線（以下、容量線CL）に電気的に接続され、他方は、液晶素子432の一対の電極の他方に電気的に接続される。なお、容量線CLの電位の値は、画素411の仕様に応じて適宜設定される。容量素子433\_1は、書き込まれたデータを保持する保持容量としての機能を有する。

#### 【0194】

例えば、図6(B)の画素411を有する表示装置では、走査線駆動回路404により各行の画素411を順次選択し、トランジスタ431\_1をオン状態にしてデータ信号のデータを書き込む。

#### 【0195】

データが書き込まれた画素411は、トランジスタ431\_1がオフ状態になることで保持状態になる。これを行毎に順次行うことにより、画像を表示できる。

40

#### 【0196】

また、図6(C)に示す画素411は、トランジスタ431\_2と、容量素子433\_2と、トランジスタ434と、発光素子435と、を有する。

#### 【0197】

トランジスタ431\_2のソース電極及びドレイン電極の一方は、データ信号が与えられる配線（以下、信号線DL\_nという）に電気的に接続される。さらに、トランジスタ431\_2のゲート電極は、ゲート信号が与えられる配線（以下、走査線GL\_mという）に電気的に接続される。

50

**【0198】**

トランジスタ431\_2は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

**【0199】**

容量素子433\_2の一対の電極の一方は、電位が与えられる配線（以下、電位供給線VL\_aという）に電気的に接続され、他方は、トランジスタ431\_2のソース電極及びドレイン電極の他方に電気的に接続される。

**【0200】**

容量素子433\_2は、書き込まれたデータを保持する保持容量としての機能を有する。

**【0201】**

トランジスタ434のソース電極及びドレイン電極の一方は、電位供給線VL\_aに電気的に接続される。さらに、トランジスタ434のゲート電極は、トランジスタ431\_2のソース電極及びドレイン電極の他方に電気的に接続される。

**【0202】**

発光素子435のアノード及びカソードの一方は、電位供給線VL\_bに電気的に接続され、他方は、トランジスタ434のソース電極及びドレイン電極の他方に電気的に接続される。

**【0203】**

発光素子435としては、例えば有機エレクトロルミネセンス素子（有機EL素子ともいう）などを用いることができる。ただし、発光素子435としては、これに限定されず、無機材料からなる無機EL素子を用いても良い。

**【0204】**

なお、電位供給線VL\_a及び電位供給線VL\_bの一方には、高電源電位VDDが与えられ、他方には、低電源電位VSSが与えられる。

**【0205】**

図6(C)の画素411を有する表示装置では、走査線駆動回路404により各行の画素411を順次選択し、トランジスタ431\_2をオン状態にしてデータ信号のデータを書き込む。

**【0206】**

データが書き込まれた画素411は、トランジスタ431\_2がオフ状態になることで保持状態になる。さらに、書き込まれたデータ信号の電位に応じてトランジスタ434のソース電極とドレイン電極の間に流れる電流量が制御され、発光素子435は、流れる電流量に応じた輝度で発光する。これを行毎に順次行うことにより、画像を表示できる。

**【0207】**

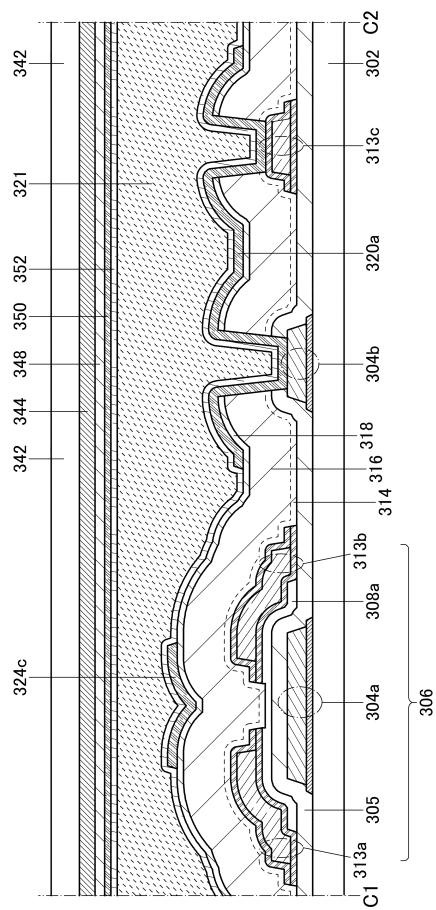

次いで、画素411に液晶素子を用いた液晶表示装置の具体的な例について説明する。ここでは、図6(B)に示す画素411の上面図を図7に示す。

**【0208】**

図7において、走査線として機能する電極304cは、信号線に略直交する方向（図中左右方向）に延伸して設けられている。信号線として機能する電極313dは、走査線に略直交する方向（図中上下方向）に延伸して設けられている。容量線として機能する電極313fは、信号線と平行方向に延伸して設けられている。なお、走査線として機能する電極304cは、走査線駆動回路404（図5(A)を参照。）と電気的に接続されており、信号線として機能する電極313d及び容量線として機能する電極313fは、信号線駆動回路406（図6(A)を参照。）に電気的に接続されている。

**【0209】**

トランジスタ303は、走査線及び信号線が交差する領域に設けられている。トランジスタ303は、ゲート電極として機能する電極304c、ゲート絶縁膜（図7に図示せず。）、ゲート絶縁膜上に形成されたチャネル領域が形成される酸化物半導体膜308b、ソース電極及びドレイン電極として機能する電極313d、電極313eにより構成される。なお、電極304cは、走査線としても機能し、酸化物半導体膜308bと重畠する領

10

20

30

40

50

域がトランジスタ 303 のゲート電極として機能する。また、電極 313d は、信号線としても機能し、酸化物半導体膜 308b と重畠する領域がトランジスタ 303 のソース電極またはドレイン電極として機能する。また、図 7において、電極 304c は、バックライトなどの光源からの光を遮る遮光膜として機能し、トランジスタに含まれる酸化物半導体膜 308b に光が照射されず、トランジスタの電気特性の変動を抑制することができる。さらに、電極 304c を、上面形状において端部が酸化物半導体膜 308b の端部より外側に位置するように配置すると、外部からの光が酸化物半導体膜 308b により到達にくくなるため、トランジスタの電気特性の変動をより抑制することができる。

#### 【0210】

また、電極 313e は、開口部 362c において、画素電極として機能する透光性を有する電極 320b と電気的に接続されている。 10

#### 【0211】

容量素子 325 は、開口部 362 において容量線として機能する電極 313f と接続されている。また、容量素子 325 は、ゲート絶縁膜上に形成される導電性を有する酸化物半導体膜 308c と、画素電極として機能する透光性を有する電極 320b と、トランジスタ 303 上に設けられる窒化物絶縁膜で形成される誘電体膜とで構成されている。ゲート絶縁膜上に形成される導電性を有する酸化物半導体膜 308c は透光性を有する。即ち、容量素子 325 は透光性を有する。

#### 【0212】

このように容量素子 325 は透光性を有するため、画素 411 内に容量素子 325 を大きく(大面積に)形成することができる。従って、開口率を高めつつ、代表的には 55% 以上、好ましくは 60% 以上とすることが可能であると共に、電荷容量を増大させた半導体装置を得ることができる。例えば、解像度の高い半導体装置、例えば液晶表示装置においては、画素の面積が小さくなり、容量素子の面積も小さくなる。このため、解像度の高い半導体装置において、容量素子に蓄積される電荷容量が小さくなる。しかしながら、本実施の形態に示す容量素子 325 は透光性を有するため、当該容量素子を画素に設けることで、各画素において十分な電荷容量を得つつ、開口率を高めることができる。代表的には、画素密度が 200ppi 以上、さらには 300ppi 以上である高解像度の半導体装置に好適に用いることができる。 20

#### 【0213】

また、図 7 に示す画素 411 は、電極 313d と平行な辺が、電極 304c と平行な辺よりも短い形状であり、且つ電極 313f が、電極 313d と平行な方向に延伸して設けられている。この結果、画素 411 に占める電極 313f の面積を低減することができるため、開口率を高めることができる。また、電極 313f が接続電極を用いず、直接導電性を有する酸化物半導体膜 308c と接するため、さらに開口率を高めることができる。 30

#### 【0214】

また、本発明の一態様は、高解像度の表示装置においても、開口率を高めることができるために、バックライトなどの光源の光を効率よく利用することができ、表示装置の消費電力を低減することができる。 40

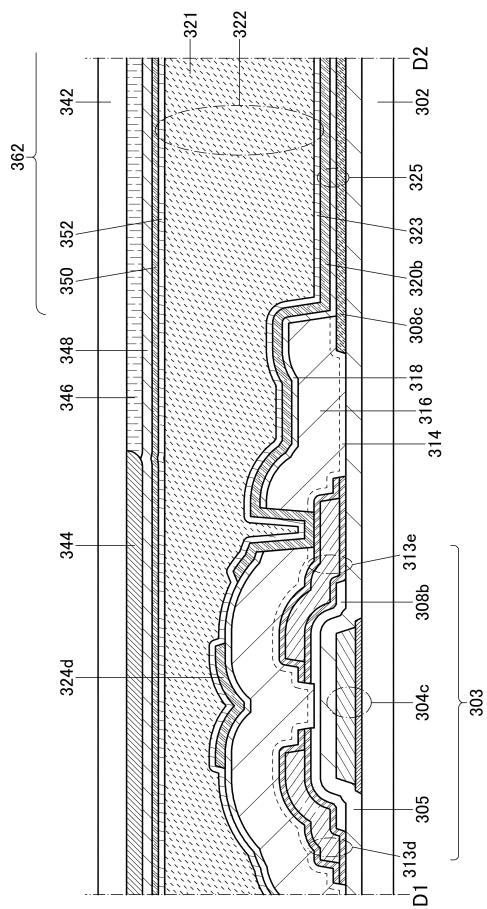

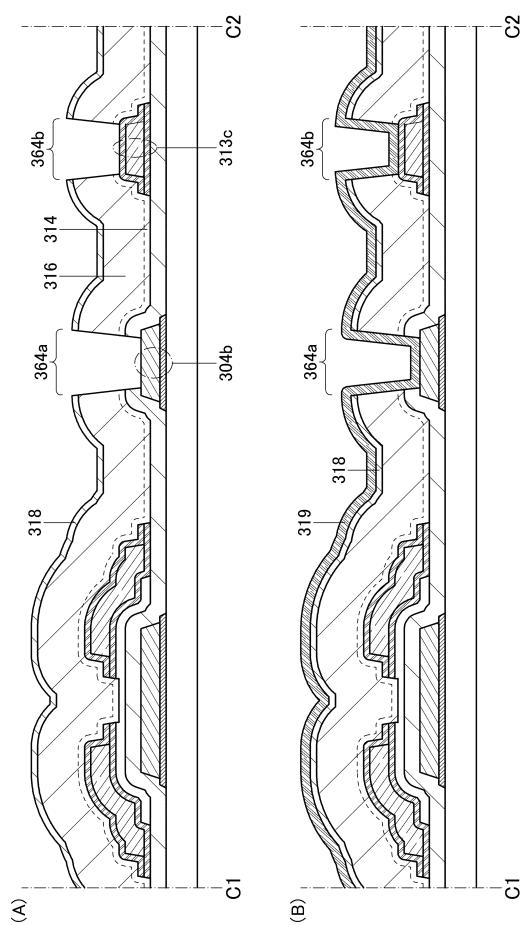

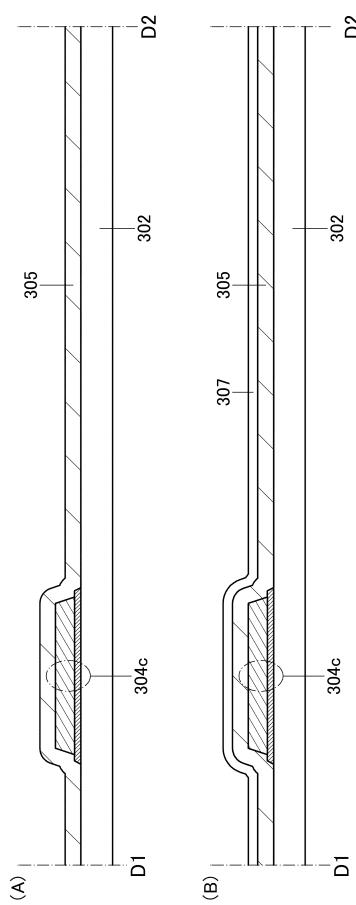

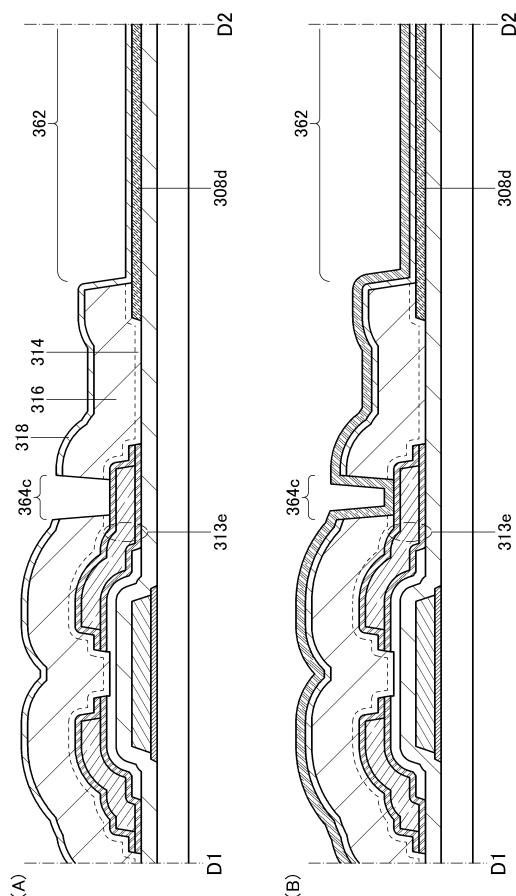

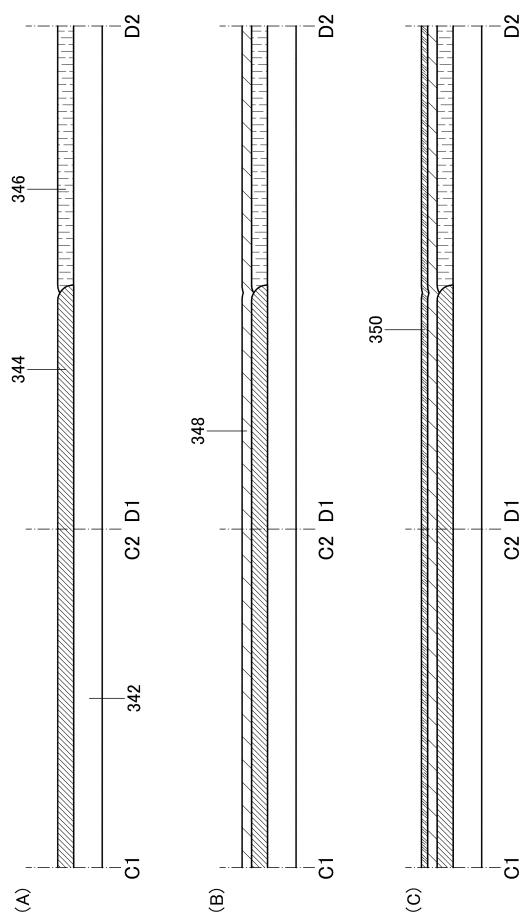

#### 【0215】

次いで、走査線駆動回路 404 及び信号線駆動回路 406 を含む駆動回路部(上面図を省略する。)の断面図を C1 - C2 として図 8 に示す。また、図 6 の一点鎖線 D1 - D2 間における断面図を図 9 に示す。また、本実施の形態においては、縦電界方式の液晶表示装置について説明する。

#### 【0216】

本実施の形態に示す表示装置は、一対の基板(基板 302 と基板 342)間に液晶素子 322 が挟持されている。

#### 【0217】

液晶素子 322 は、基板 302 の上方の透光性を有する電極 320b と、液晶層 321 と 50

、液晶層321の配向性を制御する膜（以下、配向膜323、配向膜352という）と、導電膜350と、を有する。なお、透光性を有する電極320bは、液晶素子322の一方の電極として機能し、導電膜350は、液晶素子322の他方の電極として機能する。

#### 【0218】

このように、液晶表示装置とは、液晶素子を有する装置のことをいう。なお、液晶表示装置は、複数の画素を駆動させる駆動回路等を含む。また、液晶表示装置は、別の基板上に配置された制御回路、電源回路、信号生成回路及びバックライトモジュール等を含み、液晶モジュールとよぶこともある。

#### 【0219】

駆動回路部において、トランジスタ306は、ゲート電極として機能する電極304a、ゲート絶縁膜として機能する絶縁膜305、チャネル領域が形成される酸化物半導体膜308a、ソース電極及びドレイン電極として機能する電極313a、および電極313bにより構成される。酸化物半導体膜308aは、ゲート絶縁膜として機能する絶縁膜305上に設けられる。10

#### 【0220】

画素部において、トランジスタ303は、ゲート電極として機能する電極304c、ゲート絶縁膜として機能する絶縁膜305、ゲート絶縁膜上に形成されたチャネル領域が形成される酸化物半導体膜308b、ソース電極及びドレイン電極として機能する電極313d、および電極313eにより構成される。酸化物半導体膜308bは、ゲート絶縁膜として機能する絶縁膜305上に設けられる。20

#### 【0221】

また、画素電極として機能する透光性を有する電極320bが、絶縁膜314、絶縁膜316、および絶縁膜318に設けられた開口部において、電極313eと電気的に接続する。

#### 【0222】

また、一方の電極として機能する導電性を有する酸化物半導体膜308c、誘電体膜として機能する絶縁膜318、他方の電極として機能する透光性を有する電極320bにより容量素子325を構成する。導電性を有する酸化物半導体膜308cは、絶縁膜305上に設けられる。

#### 【0223】

図9に示す電極304bは、電極304a、および電極304cと同時に形成される。また、図9に示す電極313cは、電極313a、電極313b、電極313d、電極313eと同時に形成される。駆動回路部において、電極304bと電極313cとは、透光性を有する電極320bと同時に形成された透光性を有する電極320aで電気的に接続される。30

#### 【0224】

電極304b及び透光性を有する電極320aは、絶縁膜305、絶縁膜314、絶縁膜316および絶縁膜318に設けられた開口部において電気的に接続する。また、電極313cと透光性を有する電極320aは、絶縁膜314、絶縁膜316および絶縁膜318に設けられた開口部において電気的に接続する。40

#### 【0225】

ここで、図8および図9に示す表示装置の構成要素について、以下に説明する。

#### 【0226】

基板302は、実施の形態1に示す基板101と同様の材料および作製方法を適宜用いて形成することができる。

#### 【0227】

電極304a、電極304b、電極304cは、実施の形態1に示すゲート電極103と同様の材料および作製方法を適宜用いて形成することができる。

#### 【0228】

絶縁膜305は、実施の形態1に示すゲート絶縁膜104と同様の材料および作製方法を50

適宜用いて形成することができる。

**【0229】**

酸化物半導体膜308aは、電極304aと重畳する位置に形成され、駆動回路部のトランジスタ306のチャネルが形成される半導体層として機能する。また、酸化物半導体膜308bは、電極304cと重畳する位置に形成され、画素部のトランジスタ301のチャネルが形成される半導体層として機能する。

**【0230】**

酸化物半導体膜308a、酸化物半導体膜308b、及び導電性を有する酸化物半導体膜308cは、実施の形態1に示す酸化物半導体膜105と同様の材料および作製方法を適宜用いて形成することができる。

10

**【0231】**

導電性を有する酸化物半導体膜308cは、酸化物半導体膜308a、酸化物半導体膜308bと同様の金属元素を有する膜であり、且つ不純物が含まれていることを特徴とする。不純物としては、水素がある。なお、水素の代わりに不純物として、ホウ素、リン、スズ、アンチモン、希ガス元素、アルカリ金属、アルカリ土類金属等が含まれていてもよい。

**【0232】**

酸化物半導体膜308a、酸化物半導体膜308b、及び導電性を有する酸化物半導体膜308cは共に、絶縁膜305上に形成されるが、不純物濃度が異なる。具体的には、酸化物半導体膜308a、および酸化物半導体膜308bよりも、導電性を有する酸化物半導体膜308cの不純物濃度が高い。例えば、酸化物半導体膜308a、および酸化物半導体膜308bに含まれる水素濃度は、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下であり、導電性を有する酸化物半導体膜308cに含まれる水素濃度は、 $8 \times 10^{19}$ 以上、好ましくは $1 \times 10^{20}$  atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{20}$ 以上である。また、酸化物半導体膜308a、308bと比較して、導電性を有する酸化物半導体膜308cに含まれる水素濃度は2倍、好ましくは10倍以上である。

20

**【0233】**

また、導電性を有する酸化物半導体膜308cは、酸化物半導体膜308aおよび酸化物半導体膜308bよりも抵抗率が低い。酸化物半導体膜308aおよび酸化物半導体膜308bの抵抗率は、導電性を有する酸化物半導体膜308cの抵抗率の $1 \times 10^1$ 倍以上 $1 \times 10^8$ 倍未満で有ることが好ましい。導電性を有する酸化物半導体膜308cの抵抗率は、代表的には $1 \times 10^{-3}$  cm以上 $1 \times 10^{-4}$  cm未満、さらに好ましくは、抵抗率が $1 \times 10^{-3}$  cm以上 $1 \times 10^{-1}$  cm未満であるとよい。

30

**【0234】**

導電性を有する酸化物半導体膜308cは、開口部362において絶縁膜318と接する。絶縁膜318は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、半導体膜へ拡散するのを防ぐ材料で形成される膜であり、更には水素を含む。

40

絶縁膜318の水素が、開口部362において酸化物半導体膜308aおよび酸化物半導体膜308bと同時に形成された半導体膜に拡散すると、該半導体膜において水素は酸素と結合し、キャリアである電子が生成される。

また、絶縁膜318をプラズマCVD法またはスパッタリング法で成膜すると、開口部362において酸化物半導体膜308aおよび酸化物半導体膜308bと同時に形成された半導体膜がプラズマに曝され、酸素欠損が生成される。当該酸素欠損に絶縁膜318に含まれる水素が入ることで、キャリアである電子が生成される。これらの結果、酸化物半導体膜308aおよび酸化物半導体膜308bと同時に形成された半導体膜は導電性が高くなり、導電性を有する酸化物半導体膜308cとなる。即ち、導電性を有する酸化物半導体膜308cは、導電性の高い酸化物半導体膜ともいえる。また、導電性を有する酸化物

50

半導体膜 308c は、導電性の高い金属酸化物膜ともいえる。

【0235】

ただし、本発明の実施形態の一態様は、これに限定されず、導電性を有する酸化物半導体膜 308c は、場合によっては、絶縁膜 318 と接していないことも可能である。

【0236】

また、本発明の実施形態の一態様は、これに限定されず、導電性を有する酸化物半導体膜 308c を、酸化物半導体膜 308a、または酸化物半導体膜 308b と別の工程で形成してもよい。その場合には、導電性を有する酸化物半導体膜 308c は、酸化物半導体膜 308a、酸化物半導体膜 308b と、異なる材質を有していても良い。例えば、導電性を有する酸化物半導体膜 308c は、インジウム錫酸化物酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを含むインジウム錫酸化物等を用いて形成してもよい。10

【0237】

本実施の形態に示す半導体装置は、トランジスタの半導体膜と同時に、容量素子の一方となる電極を形成する。また、画素電極として機能する透光性を有する導電膜を容量素子の他方の電極として用いる。よって、容量素子を形成するために、新たに導電膜を形成する工程が不要であり、半導体装置の作製工程を削減できる。また、容量素子を構成する一対の電極が透光性を有するため、容量素子は透光性を有する。この結果、容量素子の占有面積を大きくしつつ、画素の開口率を高めることができる。20

【0238】

電極 313a、電極 313b、電極 313c、電極 313d、電極 313e は、実施の形態 1 に示す一対の電極 106 および電極 107 と同様の材料および作製方法を適宜用いて形成することができる。

【0239】

絶縁膜 314 は、酸化物半導体膜 308a および酸化物半導体膜 308b との界面特性を向上させることができ可能な材料を用いることが好ましい。絶縁膜 314 は、実施の形態 1 に示す酸化物絶縁膜 108 と同様の材料及び作製方法を適宜用いて形成することができる。

【0240】

絶縁膜 316 は、実施の形態 1 に示す酸化物絶縁膜 109 と同様の材料及び作製方法を適宜用いて形成することができる。30

【0241】

絶縁膜 318 は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、半導体膜へ拡散するのを防ぐ材料を用いることが好ましく、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等の窒化絶縁膜を適宜用いることができる。絶縁膜 318 の厚さは、30 nm 以上 200 nm 以下、好ましくは 50 nm 以上 150 nm 以下とする。絶縁膜 318 は、スパッタリング法、CVD 法等を適宜用いて形成することができる。

【0242】

なお、電極 304b および電極 313c を直接接続する構造とするには、電極 313c を形成する前に、絶縁膜 305 に開口部を形成するためのマスクを形成する必要があるが、図 9 の接続構造であれば、当該マスクの形成が不要である。図 9 のように、透光性を有する電極 320a により、電極 304b 及び電極 313c を電気的に接続することで、電極 304b および電極 313c が直接接する接続部を作製する必要が無くなる。すなわち、電極 304b と電極 313c を直接接続する工程よりも、フォトマスクを 1 枚少なくすることができる。即ち、半導体装置の作製工程を削減することが可能である。40

【0243】

透光性を有する電極 320a、透光性を有する電極 320b としては、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、ITO、インジウム亜鉛

50

酸化物、酸化シリコンを含むインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

#### 【0244】

また、電極304a、酸化物半導体膜308aと重畳し、絶縁膜318上に形成された電極324cは、透光性を有する電極320aおよび透光性を有する電極320bと同時に形成することができる。また、電極324cは、トランジスタ306のバックゲート電極として機能することができる。電極324cを設けることで、トランジスタ306を、デュアルゲート型のトランジスタとすることができる。また、電極324cは、実施の形態1に示したゲート電極103と同様の材料及び作製方法を適宜用いて形成することもできる。

10

#### 【0245】

また、電極304c、酸化物半導体膜308bと重畳し、絶縁膜318上に形成された電極324dは、透光性を有する電極320aおよび透光性を有する電極320bと同時に形成することができる。また、電極324dは、トランジスタ303のバックゲート電極として機能することができる。電極324dを設けることで、トランジスタ303を、デュアルゲート型のトランジスタとすることができる。また、電極324dは、実施の形態1に示したゲート電極103と同様の材料及び作製方法を適宜用いて形成することもできる。

#### 【0246】

また、基板342上には、有色性を有する膜（以下、有色膜346という。）が形成されている。有色膜346は、カラーフィルタとしての機能を有する。また、有色膜346に隣接する遮光膜344が基板342上に形成される。遮光膜344は、ブラックマトリクスとして機能する。また、有色膜346は、必ずしも設ける必要はなく、例えば、表示装置が白黒の場合等によって、有色膜346を設けない構成としてもよい。

20

#### 【0247】

有色膜346としては、特定の波長帯域の光を透過する有色膜であればよく、例えば、赤色の波長帯域の光を透過する赤色（R）のカラーフィルタ、緑色の波長帯域の光を透過する緑色（G）のカラーフィルタ、青色の波長帯域の光を透過する青色（B）のカラーフィルタなどを用いることができる。

#### 【0248】

30

遮光膜344としては、特定の波長帯域の光を遮光する機能を有していればよく、金属膜または黒色顔料等を含んだ有機絶縁膜などを用いることができる。

#### 【0249】

また、有色膜346上には、絶縁膜348が形成されている。絶縁膜348は、平坦化層としての機能、または有色膜346が含有しうる不純物を液晶素子側へ拡散するのを抑制する機能を有する。

#### 【0250】

また、絶縁膜348上には、導電膜350が形成されている。導電膜350は、画素部の液晶素子が有する一対の電極の他方としての機能を有する。なお、透光性を有する電極320a、電極320b、及び導電膜350上に、配向膜としての機能を有する絶縁膜を別途形成してもよい。本実施の形態では、導電膜350上に配向膜352を形成している。

40

#### 【0251】

液晶層321は、シール材（図示しない）を用いて、基板302と基板342の間に封止されている。なお、シール材は、外部からの水分等の入り込みを抑制するために、無機材料と接触する構成が好ましい。

#### 【0252】

また、透光性を有する電極320bと導電膜350との間に、液晶層321の厚さ（セルギャップともいう）を維持するスペーサを設けてもよい。

#### 【0253】

図8および図9を用いて説明した半導体装置の作製方法について、図10乃至図19を用

50

いて説明する。

【0254】

まず、基板302を準備する。ここでは、基板302としてガラス基板を用いる。

【0255】

次に、基板302上に導電膜を形成し、該導電膜を所望の領域に加工することで、電極304a、電極304b、電極304cを形成する。なお、電極304a、電極304b、電極304cの形成は、所望の領域に第1のフォトリソグラフィ工程によるマスクの形成を行い、該マスクに覆われていない領域をエッティングすることで形成することができる(図10(A)、図15(A)参照。)。

【0256】

次に、基板302、及び電極304a、電極304b、電極304c上に、絶縁膜305を形成する(図10(A)、図15(A)参照。)。

【0257】

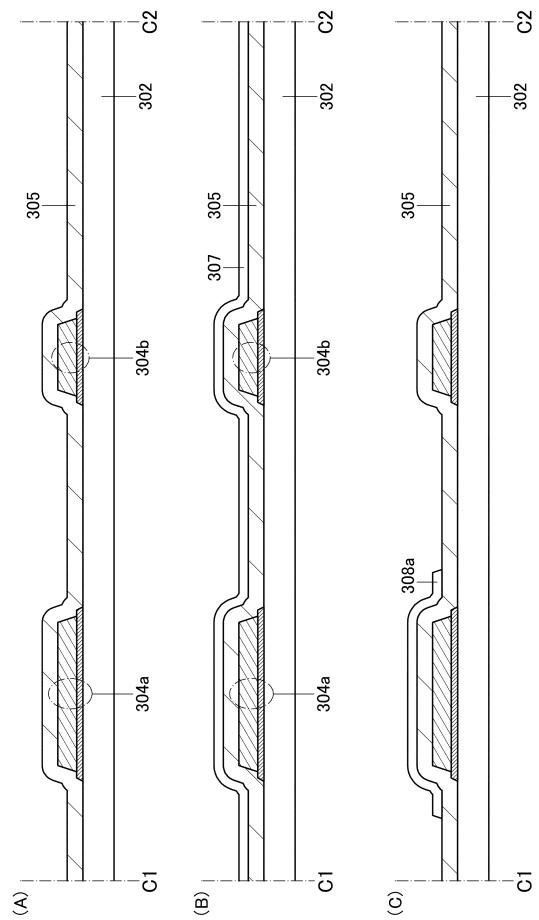

次に、絶縁膜305上に半導体膜307を形成する(図10(B)、図15(B)参照。)。

【0258】

次に、半導体膜307を所望の領域に加工することで、島状の酸化物半導体膜308a、酸化物半導体膜308b、酸化物半導体膜308dを形成する。なお、酸化物半導体膜308a、酸化物半導体膜308b、酸化物半導体膜308dの形成は、所望の領域に第2のフォトリソグラフィ工程によるマスクの形成を行い、該マスクに覆われていない領域をエッティングすることで形成することができる。エッティングとしては、ドライエッティング法、ウエットエッティング法、または双方を組み合わせたエッティング法を用いることができる(図10(C)、図15(C)参照。)。

【0259】

次に、第1の加熱処理を行ってもよい。第1の加熱処理は、実施の形態1に示す第1の加熱処理と同様の条件を用いる。第1の加熱処理によって、酸化物半導体膜308a、酸化物半導体膜308b、酸化物半導体膜308dに用いる酸化物半導体の結晶性を高め、さらに絶縁膜305、酸化物半導体膜308a、酸化物半導体膜308b、酸化物半導体膜308dから水素や水などの不純物を除去することができる。なお、酸化物半導体をエッティングする前に第1の加熱工程を行ってもよい。

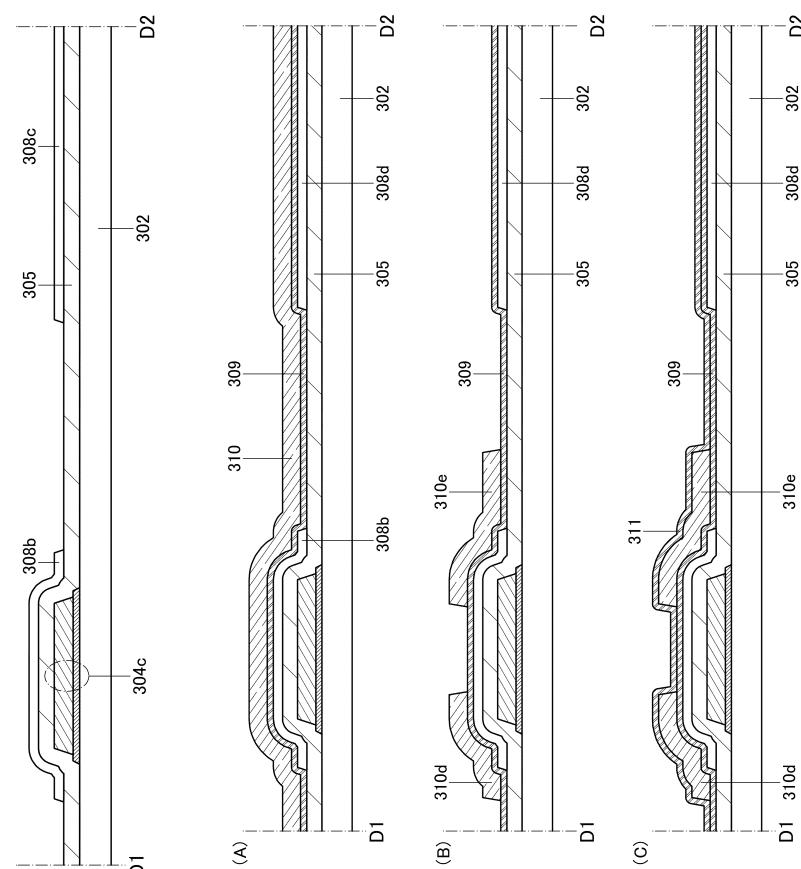

【0260】

次に、絶縁膜305、及び酸化物半導体膜308a、酸化物半導体膜308b、酸化物半導体膜308d上に、導電膜309および導電膜310を順に形成する(図11(A)、図16(A)参照。)。本実施の形態では、導電膜309としてタンゲステン膜を成膜し、導電膜310として銅膜を成膜する。

【0261】

次に、第3のフォトリソグラフィ工程により導電膜310上にマスクを形成し、導電膜310を所望の領域に加工することで、電極310a、電極310b、電極310c、電極310d、および電極310eを形成する(図11(B)、図16(B)参照。)。

【0262】

電極310a、電極310b、電極310c、電極310d、および電極310eの形成工程において、エッティング溶液中に溶け出した導電膜126bを構成する金属元素の一部が導電膜126aに付着する場合がある。本実施の形態では、導電膜310として銅を含む材料を用いるため、導電膜126a上に銅元素が残留もしくは再付着する。しかしながら、導電膜309がブロッキング層として機能し、該金属元素が酸化物半導体膜308a、酸化物半導体膜308b、酸化物半導体膜308dに移動することを防ぐことができる。

【0263】

次に、電極310a、電極310b、電極310c、電極310d、電極310e、および導電膜309上に、導電膜311を形成する(図11(C)、図16(C)参照。)。

10

20

30

40

50

本実施の形態では、導電膜 311 としてタンゲステン膜を成膜する。なお、前述した、導電膜 309 上に付着した銅元素は、導電膜 126a と導電膜 126c の界面に残存する。

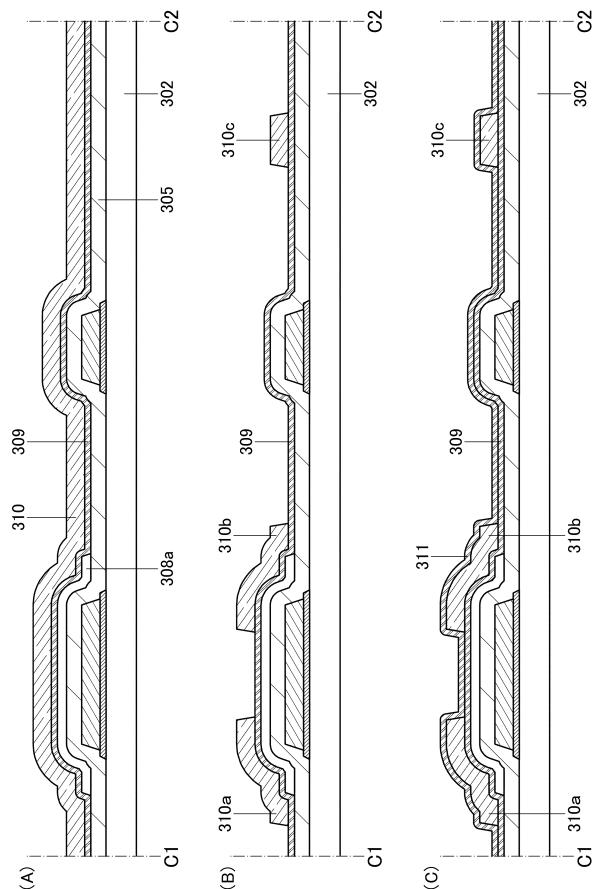

#### 【0264】

次に、第4のフォトリソグラフィ工程により導電膜 311 上にマスクを形成し、導電膜 311 と導電膜 309 の一部を選択的に除去する。この時、マスクが、電極 310a、電極 310b、電極 310c、電極 310d、および電極 310e を完全に覆うように、電極 310a、電極 310b、電極 310c、電極 310d、および電極 310e の端部を超えて形成する。

#### 【0265】

このようにして、電極 310a、電極 310b、電極 310c、電極 310d が金属層に完全に包まれた電極 313a、電極 313b、電極 313c、電極 313d、および電極 313e を形成することができる（図12（A）、図17（A）参照。）。

#### 【0266】

次に、導電膜 311 と導電膜 309 が除去された領域に付着した金属元素を除去するための洗浄処理を行う。本実施の形態では、導電膜 311 と導電膜 309 の界面に残留した銅元素が、エッチングにより試料表面に残留もしくは再付着するため、実施の形態 1 で説明した洗浄処理をおこなう。本実施の形態では、リン酸を 0.85wt% 含む水溶液を用いて、30秒間の洗浄処理を行う。また、当該洗浄処理は、導電膜 126a と導電膜 126c のエッチングであれば、マスク 132 の除去前に行ってもよいし、除去後に行ってもよい。

#### 【0267】

なお、当該洗浄処理により領域 133a として示す酸化物半導体膜 308a 表面の一部がエッチングされ、酸化物半導体膜 308a の他の部分よりも厚さが薄くなる場合がある。また、領域 133b として示す酸化物半導体膜 308b 表面の一部がエッチングされ、酸化物半導体膜 308b の他の部分よりも厚さが薄くなる場合がある。また、酸化物半導体膜 308d 表面もエッチングされ膜厚が減少する場合がある（図12（B）、図17（B）参照。）。

#### 【0268】

続いて、絶縁膜 314、絶縁膜 316 を順に形成する（図12（C）、図17（C）参照。）。

#### 【0269】

次に、第5のフォトリソグラフィ工程により絶縁膜 316 上にマスクを形成し、絶縁膜 314、および絶縁膜 316 の一部を選択的にエッチングして、酸化物半導体膜 308c 上に開口部 362 を形成する。この時、他の開口部も同時に形成する（図13（A）、図18（A）参照。）。絶縁膜 314、および絶縁膜 316 のエッチングは、ドライエッティング法、ウエットエッティング法、または双方を組み合わせたエッティング法を用いることができる。

#### 【0270】

この後、第2の加熱処理を行ってもよい。第2の加熱処理により、絶縁膜 316 に含まれる酸素の一部を酸化物半導体膜 308a、および酸化物半導体膜 308b に移動させ、酸化物半導体膜 308a、および酸化物半導体膜 308b に含まれる酸素欠損を低減することが可能である。

#### 【0271】

次に、絶縁膜 316 及び酸化物半導体膜 308d 上に絶縁膜 318 を形成する（図13（B）、図18（B）参照。）。

#### 【0272】

絶縁膜 318 としては、外部からの不純物、例えば、酸素、水素、水、アルカリ金属、アルカリ土類金属等が、多層膜へ拡散するのを防ぐ材料を用いることが好ましく、更には水素を含むことが好ましく、代表的には窒素を含む無機絶縁材料、例えば窒化物絶縁膜を用いることができる。絶縁膜 318 としては、例えば、CVD 法、スパッタリング法等を用

10

20

30

40

50

いて形成することができる。

#### 【0273】

絶縁膜318は、CVD法、スパッタリング法等を用いて形成すると、酸化物半導体膜308dがプラズマに曝され、酸化物半導体膜308dに酸素欠損が生成される。また、絶縁膜318は、外部からの不純物、例えば、水、アルカリ金属、アルカリ土類金属等が、半導体膜へ拡散するのを防ぐ材料で形成される膜であり、更には水素を含む。これらのため、絶縁膜318の水素が酸化物半導体膜308dに拡散すると、該酸化物半導体膜308dにおいて水素は酸素欠損と結合し、キャリアである電子が生成される。または、絶縁膜318の水素が酸化物半導体膜308dに拡散すると、該酸化物半導体膜308dにおいて水素は酸素と結合し、キャリアである電子が生成される。この結果、酸化物半導体膜308dは、導電性が高くなり、導電性を有する酸化物半導体膜308cとなる。10

#### 【0274】

また、上記窒化シリコン膜は、ブロック性を高めるために、高温で成膜されることが好ましく、例えば基板温度100以上基板の歪み点以下、より好ましくは300以上400以下の温度で加熱して成膜することが好ましい。また高温で成膜する場合は、酸化物半導体膜308a、酸化物半導体膜308bから酸素が脱離し、キャリア濃度が上昇する現象が発生するがあるため、このような現象が発生しない温度とする。

#### 【0275】

なお、絶縁膜318を形成する前に酸化物半導体膜308dを希ガス及び水素を含むプラズマに曝すことで、酸化物半導体膜308dに酸素欠損を形成するとともに、酸化物半導体膜308dに水素を添加することが可能である。この結果、酸化物半導体膜308dにおいてキャリアである電子をさらに増加させることができ、導電性を有する酸化物半導体膜308cの導電性をさらに高めることができる。20

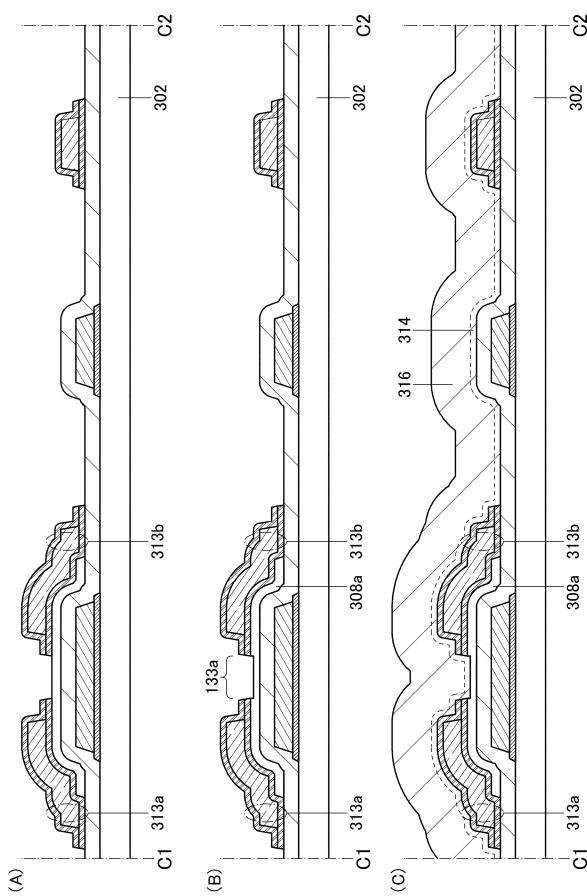

#### 【0276】

次に、絶縁膜305、絶縁膜314、絶縁膜316、絶縁膜318の一部を選択的にエッチングすることで、開口部364a、開口部364b、開口部364cを形成する。なお、開口部364a、開口部364b、開口部364cは、第6のフォトリソグラフィ工程によるマスクの形成を行い、該マスクに覆われていない領域をエッチングすることで形成することができる（図14（A）、図19（A）参照。）。

#### 【0277】

また、開口部364aは、電極304aの表面が露出するように形成する。また、開口部364bは、電極313cが露出するように形成する。また、開口部364cは、電極313eが露出するように形成する。30

#### 【0278】

なお、開口部364a、開口部364b、開口部364cの形成方法としては、例えば、ドライエッチング法を用いることができる。ただし、これに限定されず、ウェットエッチング法、またはドライエッチング法とウェットエッチング法を組み合わせた形成方法を用いてよい。

#### 【0279】

次に、開口部364a、開口部364b、開口部364cを覆い、絶縁膜318上に導電膜319を形成する（図14（B）、図19（B）参照。）。

#### 【0280】

次に、第7のフォトリソグラフィ工程によりマスクを形成し、導電膜319の一部を選択的にエッチングすることで、透光性を有する電極320a、電極320b、電極324c、電極320dを形成する（図8、図9参照。）。

#### 【0281】

以上の工程で、基板302上に、トランジスタを有する画素部及び駆動回路部を形成することができる。なお、本実施の形態に示す作製工程においては、第1乃至第6のパターニング、すなわち7枚のマスクでトランジスタ、及び容量素子を同時に形成することができる。40

**【0282】**

なお、本実施の形態では、絶縁膜318に含まれる水素を酸化物半導体膜308dに拡散させて、酸化物半導体膜308dの導電性を高めたが、酸化物半導体膜308a、酸化物半導体膜308bをマスクで覆い、酸化物半導体膜308dに不純物、代表的には、水素、ホウ素、リン、スズ、アンチモン、希ガス元素、アルカリ金属、アルカリ土類金属等を添加して、酸化物半導体膜308dの導電性を高めてよい。酸化物半導体膜308dに水素、ホウ素、リン、スズ、アンチモン、希ガス元素等を添加する方法としては、イオンドーピング法、イオン注入法等がある。一方、酸化物半導体膜308dにアルカリ金属、アルカリ土類金属等を添加する方法としては、該不純物を含む溶液を酸化物半導体膜308dに塗布する方法がある。

10

**【0283】**

次に、基板302に対向して設けられる基板342上に形成される構造について、以下説明を行う。

**【0284】**

まず、基板342を準備する。基板342としては、基板302と同様の材料を用いることができる。次に、基板342上に遮光膜344、有色膜346を形成する（図20（A）参照）。

**【0285】**

遮光膜344及び有色膜346は、様々な材料を用いて、印刷法、インクジェット法、フォトリソグラフィ法を用いて、それぞれ所望の位置に形成する。

20

**【0286】**

次に、遮光膜344、及び有色膜346上に絶縁膜348を形成する（図20（B）参照）。

**【0287】**

絶縁膜348としては、例えばアクリル樹脂、エポキシ樹脂、ポリイミド等の有機絶縁膜を用いることができる。絶縁膜348を形成することによって、例えば、有色膜346中に含まれる不純物等を液晶層321側に拡散することを抑制することができる。ただし、絶縁膜348は、必ずしも設ける必要はなく、絶縁膜348を形成しない構造としてもよい。

**【0288】**

30

次に、絶縁膜348上に導電膜350を形成する（図20（C）参照）。導電膜350としては、導電膜319と同様の材料および方法で形成することができる。

**【0289】**

以上の工程で基板342上に形成される構造を形成することができる。

**【0290】**

次に、基板302と基板342上、より詳しくは基板302上に形成された絶縁膜318、透光性を有する電極320a、電極320bと、基板342上に形成された導電膜350上に、それぞれ配向膜323と配向膜352を形成する。配向膜323、配向膜352は、ラビング法、光配向法等を用いて形成することができる。その後、基板302と、基板342との間に液晶層321を形成する。液晶層321の形成方法としては、ディスペンサ法（滴下法）や、基板302と基板342とを貼り合わせてから毛細管現象を用いて液晶を注入する注入法を用いることができる。

40

**【0291】**

以上の工程で、図8および図9に示す表示装置を作製することができる。

**【0292】**

本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及び方法などと適宜組み合わせて用いることができる。

**【0293】****(実施の形態4)**

本実施の形態では、上記実施の形態で説明した半導体装置に含まれているトランジスタに

50

おいて、チャネル領域が形成される酸化物半導体膜、および酸化物膜に適用可能な一態様について説明する。なお、ここでは、酸化物半導体膜を一例に用いて説明するが、酸化物膜も同様の構造とすることができます。

#### 【0294】

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、C AAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor ) 膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。ここでは、C AAC - OS 膜及び微結晶酸化物半導体膜について説明する。

#### 【0295】

まずは、C AAC - OS 膜について説明する。

#### 【0296】

C AAC - OS 膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一边が 100 nm 未満の立方体内に収まる大きさである。従って、C AAC - OS 膜に含まれる結晶部は、一边が 10 nm 未満、5 nm 未満または 3 nm 未満の立方体内に収まる大きさの場合も含まれる。

#### 【0297】

C AAC - OS 膜を透過型電子顕微鏡 ( TEM : Transmission Electron Microscope ) によって観察すると、明確な結晶部同士の境界、即ち結晶粒界 ( グレインバウンダリーともいう。 ) を確認することができない。そのため、C AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0298】

C AAC - OS 膜を、試料面と概略平行な方向から TEM によって観察 ( 断面 TEM 観察 ) すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C AAC - OS 膜の膜を形成する面 ( 被形成面ともいう。 ) または上面の凹凸を反映した形状であり、C AAC - OS 膜の被形成面または上面と平行に配列する。

#### 【0299】

一方、C AAC - OS 膜を、試料面と概略垂直な方向から TEM によって観察 ( 平面 TEM 観察 ) すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

#### 【0300】

なお、C AAC - OS 膜に対し、電子線回折を行うと、配向性を示すスポット ( 輝点 ) が観測される。

#### 【0301】

断面 TEM 観察および平面 TEM 観察より、C AAC - OS 膜の結晶部は配向性を有していることがわかる。

#### 【0302】

図 21 ( A ) に、厚さが 100 nm の C AAC - OS を 50 nm に薄膜化したサンプルに対し、表面側からナノビーム電子線回折を行った結果を示す。このとき、電子ビームのプローブ径は 1 nm ( 1 nm と表記 ) 、 10 nm ( 10 nm と表記 ) 、 20 nm ( 20 nm と表記 ) または 30 nm ( 30 nm と表記 ) とした。いずれの条件においても、特定の方向への配向性を確認することができた。また、プローブ径が小さいほど、配向性が高くなっていることがわかった。

#### 【0303】

C AAC - OS 膜に対し、X 線回折 ( XRD : X - Ray Diffraction ) 装置を用いて構造解析を行うと、例えば InGaZnO<sub>4</sub> の結晶を有する C AAC - OS 膜の out-of-plane 法による解析では、回折角 ( 2θ ) が 31° 近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (009) 面に帰属されることから、C AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概

10

20

30

40

50

略垂直な方向を向いていることが確認できる。

#### 【0304】

一方、 C A A C - O S 膜に対し、 c 軸に概略垂直な方向から X 線を入射させる i n - p l a n e 法による解析では、  $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、 I n G a Z n O<sub>4</sub> の結晶の (110) 面に帰属される。 I n G a Z n O<sub>4</sub> の単結晶酸化物半導体膜であれば、  $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、 (110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、 C A A C - O S 膜の場合は、  $2\theta$  を  $56^\circ$  近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

#### 【0305】

以上のことから、 C A A C - O S 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、 c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 T E M 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。

#### 【0306】

なお、結晶部は、 C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、 C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、 C A A C - O S 膜の形状をエッティングなどによって変化させた場合、結晶の c 軸が C A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

#### 【0307】

また、 C A A C - O S 膜中の結晶化度が均一でなくてもよい。例えば、 C A A C - O S 膜の結晶部が、 C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、 C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

#### 【0308】

なお、 I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S 膜の o u t - o f - p l a n e 法による解析では、  $2\theta$  が  $31^\circ$  近傍のピークの他に、  $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。  $2\theta$  が  $36^\circ$  近傍のピークは、 C A A C - O S 膜中的一部に、 c 軸配向性を有さない結晶が含まれることを示している。 C A A C - O S 膜は、  $2\theta$  が  $31^\circ$  近傍にピークを示し、  $2\theta$  が  $36^\circ$  近傍にピークを示さないことが嬉しい。

#### 【0309】

C A A C - O S 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

#### 【0310】

また、 C A A C - O S 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0311】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないので、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノー

10

20

30

40

50

マリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

#### 【0312】

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

10

#### 【0313】

次に、微結晶酸化物半導体膜について説明する。

#### 【0314】

微結晶酸化物半導体膜は、T E Mによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体膜に含まれる結晶部は、1 n m以上100 n m以下、または1 n m以上10 n m以下の大きさであることが多い。特に、1 n m以上10 n m以下、または1 n m以上3 n m以下の微結晶であるナノ結晶(n c : n a n o c r y s t a l )を有する酸化物半導体膜を、n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r )膜と呼ぶ。また、n c - O S 膜は、例えば、T E Mによる観察像では、結晶粒界を明確に確認できない場合がある。

20

#### 【0315】

n c - O S 膜は、微小な領域(例えば、1 n m以上10 n m以下の領域、特に1 n m以上3 n m以下の領域)において原子配列に周期性を有する。また、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。従って、n c - O S 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、n c - O S 膜に対し、結晶部よりも大きい径のX線を用いるX R D 装置を用いて構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、n c - O S 膜は、結晶部よりも大きいプローブ径(例えば50 n m以上)の電子線を用いる電子線回折(制限視野電子線回折ともいう。)を行うと、ハローパターンのような回折像が観測される。一方、n c - O S 膜は、結晶部の大きさと近いか結晶部より小さいプローブ径(例えば1 n m以上30 n m以下)の電子線を用いる電子線回折(ナノビーム電子線回折ともいう。)を行うと、スポットが観測される。また、n c - O S 膜のナノビーム電子線回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、n c - O S 膜のナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

30

#### 【0316】

図21(B)は、n c - O S 膜を有する試料に対し、測定箇所を変えてナノビーム電子線回折を行った例である。ここでは、試料を、n c - O S 膜の被形成面に垂直な方向に切断し、厚さが10 n m以下となるように薄片化する。また、ここでは、プローブ径が1 n mの電子線を、試料の切断面に垂直な方向から入射させる。図21より、n c - O S 膜を有する試料に対し、ナノビーム電子線回折を行うと、結晶面を示す回折パターンが得られるが、特定方向の結晶面への配向性は見られない。

40

#### 【0317】

n c - O S 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、n c - O S 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 膜は、C A A C - O S 膜と比べて欠陥準位密度が高くなる。

#### 【0318】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

50

**【0319】**

(実施の形態5)

本実施の形態では、半導体装置の一例として、上記実施の形態で説明した表示装置を搭載することのできる電子機器について説明する。

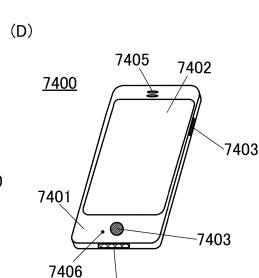

**【0320】**

電子機器として、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。これらの電子機器の具体例を図25に示す。

10

**【0321】**

図25(A)は、テレビジョン装置の一例を示している。テレビジョン装置7100は、筐体7101に表示部7103が組み込まれている。表示部7103により、映像を表示することが可能であり、上記実施の形態で説明した表示装置を表示部7103に用いることができる。また、ここでは、スタンド7105により筐体7101を支持した構成を示している。

**【0322】**

テレビジョン装置7100の操作は、筐体7101が備える操作スイッチや、別体のリモートコントローラ7110により行うことができる。リモートコントローラ7110が備える操作キー7109により、チャンネルや音量の操作を行うことができ、表示部7103に表示される映像を操作することができる。また、リモートコントローラ7110に、当該リモートコントローラから出力する情報を表示する表示部7107を設ける構成としてもよい。

20

**【0323】**

なお、テレビジョン装置7100は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

**【0324】**

図25(B)はコンピュータであり、本体7201、筐体7202、表示部7203、キーボード7204、外部接続ポート7205、ポインティングデバイス7206等を含む。なお、コンピュータは、上記実施の形態で説明した表示装置を表示部7203に用いることができる。

30

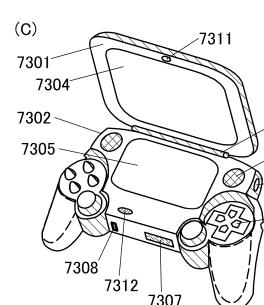

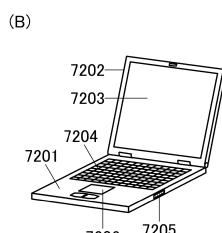

**【0325】**

図25(C)は携帯型遊技機であり、筐体7301と筐体7302の2つの筐体で構成されており、連結部7303により、開閉可能に連結されている。筐体7301には表示部7304が組み込まれ、筐体7302には表示部7305が組み込まれている。また、図25(C)に示す携帯型遊技機は、その他、スピーカ部7306、記録媒体挿入部7307、LEDランプ7308、入力手段（操作キー7309、接続端子7310、センサ7311（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、においまたは赤外線を測定する機能を含むもの）、マイクロfon7312）等を備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、少なくとも表示部7304および表示部7305の両方、または一方に上記実施の形態で説明した表示装置を用いていればよく、その他付属設備が適宜設けられた構成とすることができます。図25(C)に示す携帯型遊技機は、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図25(C)に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

40

**【0326】**

50

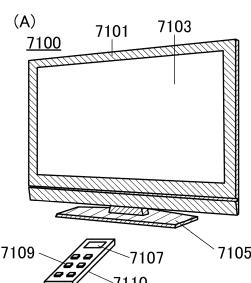

図25(D)は、携帯電話機の一例を示している。携帯電話機7400は、筐体7401に組み込まれた表示部7402の他、操作ボタン7403、外部接続ポート7404、スピーカ7405、マイク7406などを備えている。なお、携帯電話機7400は、上記実施の形態で説明した表示装置を表示部7402に用いることにより作製される。

#### 【0327】

図25(D)に示す携帯電話機7400は、表示部7402を指などで触ることで、情報を入力することができる。また、電話を掛ける、或いはメールを作成するなどの操作は、表示部7402を指などで触ることにより行うことができる。

#### 【0328】

表示部7402の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

10

#### 【0329】

例えば、電話を掛ける、或いはメールを作成する場合は、表示部7402を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部7402の画面のほとんどにキーボードまたは番号ボタンを表示させることが好みしい。

#### 【0330】

また、携帯電話機7400内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機7400の向き(縦か横か)を判断して、表示部7402の画面表示を自動的に切り替えるようにすることができる。

20

#### 【0331】

また、画面モードの切り替えは、表示部7402を触れること、または筐体7401の操作ボタン7403の操作により行われる。また、表示部7402に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

#### 【0332】

また、入力モードにおいて、表示部7402の光センサで検出される信号を検知し、表示部7402のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

30

#### 【0333】

表示部7402は、イメージセンサとして機能させることもできる。例えば、表示部7402に掌や指で触れ、掌紋、指紋等を撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

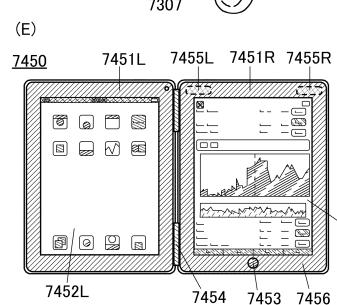

#### 【0334】

図25(E)は、折りたたみ式のコンピュータの一例を示している。折りたたみ式のコンピュータ7450は、ヒンジ7454で接続された筐体7451Lと筐体7451Rを備えている。また、操作ボタン7453、左側スピーカ7455Lおよび右側スピーカ7455Rの他、コンピュータ7450の側面には図示されていない外部接続ポート7456を備える。なお、筐体7451Lに設けられた表示部7452Lと、筐体7451Rに設けられた表示部7452Rが互いに対峙するようにヒンジ7454を折り畳むと、表示部を筐体で保護することができる。

40

#### 【0335】

表示部7452Lと表示部7452Rは、画像を表示する他、指などで触ると情報を入力できる。例えば、インストール済みのプログラムを示すアイコンを指でふれて選択し、プログラムを起動できる。または、表示された画像の二箇所に触れた指の間隔を変えて、画像を拡大または縮小できる。または、表示された画像の一箇所に触れた指を移動して画像を移動できる。また、キーボードの画像を表示して、表示された文字や記号を指で触れて選択し、情報を入力することもできる。

50

**【0336】**

また、コンピュータ7450に、ジャイロ、加速度センサ、GPS (Global Positioning System) 受信機、指紋センサ、ビデオカメラを搭載することができる。例えば、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、コンピュータ7450の向き（縦か横か）を判断して、表示する画面の向きを自動的に切り替えるようにすることができる。

**【0337】**

また、コンピュータ7450はネットワークに接続できる。コンピュータ7450はインターネット上の情報を表示できる他、ネットワークに接続された他の電子機器を遠隔から操作する端末として用いることができる。

10

**【0338】**

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

**【実施例1】****【0339】**

本実施例では、実施の形態1に示した電極106および電極107の作製工程中における、残留銅元素濃度の調査結果について説明する。

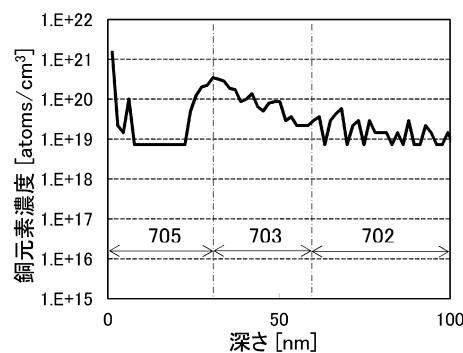

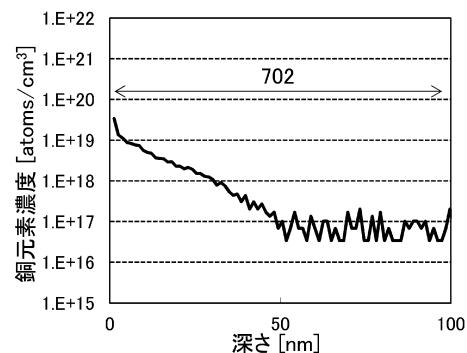

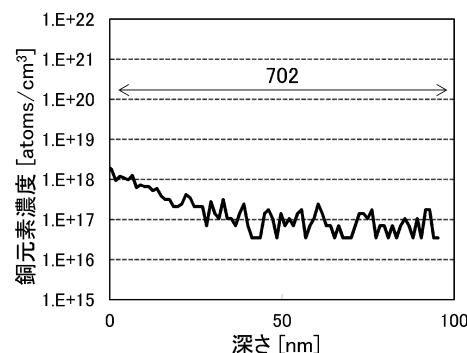

**【0340】**

以下に示す試料A乃至試料Dを作製し、銅が除去された領域の銅元素濃度を二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により測定した。

20

**【0341】**

<試料A乃至試料Dの構造および作製方法>

試料A乃至試料Dの構造および作製方法について説明する。また、試料A乃至試料Dの断面模式図を図22(A1)乃至図22(A4)に示す。

**【0342】**

また、試料A乃至試料Dの断面TEM観察像を図22(B1)乃至図22(B4)に示す。

なお、図22(B1)乃至図22(B4)は、Zコントラスト像である。また、TEM観察時のチャージアップを防ぐため、最上層に白金751が形成されている。また、図22(B1)乃至図22(B4)に示すTEM観察像は、同一試料のSIMS分析箇所とは異なる部位の観察像である。

30

**【0343】****[試料A]**

ガラス基板701上に、膜702として厚さ100nmのIn-Ga-Zn酸化物膜を形成し、次に膜703として厚さ30nmのタングステン膜を形成し、次に膜704として厚さ200nmの銅膜を形成し、次にフォトリソグラフィ法を用いてマスクを形成し、ウエットエッティング法により膜704の一部を選択的にエッティングして、試料Aを作製した(図22(A1)、図22(B1)参照。)。

**【0344】**

40

**[試料B]**

試料Aと同様の試料を作製し、その上に、膜705として厚さ30nmのタングステン膜を形成し、膜705により膜704が覆われた試料Bを作製した(図22(A2)、図22(B2)参照。)。

**【0345】****[試料C]**

試料Bと同様の試料を作製し、膜705上に、フォトリソグラフィ法を用いて膜704を覆ってマスクを形成し、マスクに覆われていない領域の、膜703と膜705をドライエッティング法によりエッティングし、膜702の一部を露出させて、試料Cを作製した(図22(A3)、図22(B3)参照。)。なお、図22(B3)は、該マスク(マスク74

50

2)を除去する前のTEM観察像である。

**【0346】**

**[試料D]**

試料Cを、リン酸を0.85wt%含む水溶液に室温で30秒間含浸して、試料Cを作製した(図22(A4)、図22(B4)参照。)。

**【0347】**

**<SIMS分析結果>**

SIMS分析法により、試料A乃至試料Dの領域741の、深さ方向の銅元素濃度を測定した。図23(A)、図23(B)、図24(A)、および図24(B)にSIMS分析結果を示す。図23(A)、図23(B)、図24(A)、および図24(B)の横軸は試料表面からの深さを示し、縦軸は特定の深さにおける銅元素濃度を示す。

10

**【0348】**

また、図23(A)、図23(B)、図24(A)、および図24(B)では、タンゲステンの二次イオン強度変化(図示せず)から推定した、各膜の境界位置を示している。

**【0349】**

なお、SIMS分析法における元素濃度の定量は、不純物濃度が既知の標準試料を用いて、SIMS分析により得られた二次イオン強度をもとに算出される。標準試料は主成分ごとに作製されるため、得られる定量値は、使用する標準試料と主成分が同様の材料中でのみ有効である。

20

**【0350】**

**[試料A]**

図23(A)に、試料AのSIMS分析結果を示す。図23(A)の銅元素濃度は、主成分がタンゲステンの標準試料を用いて定量化した値である。よって、図23(A)の銅元素濃度は、膜703中においてのみ有効である。

**【0351】**

図23(A)より、膜704のエッティング後において、露出した膜703の表面からバルク中にかけて、おおよそ $1 \times 10^{20}$ 乃至 $1 \times 10^{19}$ atoms/cm<sup>3</sup>の濃度で銅元素が検出されていることがわかる。

**【0352】**

**[試料B]**

30

図23(B)に、試料BのSIMS分析結果を示す。図23(B)の銅元素濃度は、主成分がタンゲステンの標準試料を用いて定量化した値である。よって、図23(B)の銅元素濃度は、膜703および膜705中においてのみ有効である。

**【0353】**

図23(B)より、膜703および膜705界面のから膜703のバルク中にかけて、おおよそ $1 \times 10^{20}$ 乃至 $1 \times 10^{19}$ atoms/cm<sup>3</sup>の濃度で銅元素が検出されていることがわかる。

**【0354】**

**[試料C]**

図24(A)に、試料CのSIMS分析結果を示す。図24(A)の銅元素濃度は、主成分がIn-Ga-Zn酸化物の標準試料を用いて定量化した値である。

40

**【0355】**

図24(A)より、露出した膜702の表面から深さ50nm程度までのバルク中において、おおよそ $1 \times 10^{19}$ 乃至 $1 \times 10^{17}$ atoms/cm<sup>3</sup>の濃度で銅元素が検出されていることがわかる。

**【0356】**

**[試料D]**

図24(B)に、試料DのSIMS分析結果を示す。図24(B)の銅元素濃度は、主成分がIn-Ga-Zn酸化物の標準試料を用いて定量化した値である。

**【0357】**

50

図24(B)より、露出した膜702の表面近傍の銅元素濃度が、およそ $1 \times 10^{-8}$  atoms/cm<sup>3</sup>以下の濃度に低減されていることがわかる。よって、洗浄処理を行うことにより、膜702の表面近傍の銅元素濃度を低減できることが確認された。

## 【符号の説明】

## 【0358】

|     |         |    |

|-----|---------|----|

| 100 | トランジスタ  |    |

| 101 | 基板      |    |

| 103 | ゲート電極   |    |

| 104 | ゲート絶縁膜  | 10 |

| 105 | 酸化物半導体膜 |    |

| 106 | 電極      |    |

| 107 | 電極      |    |

| 108 | 酸化物絶縁膜  |    |

| 109 | 酸化物絶縁膜  |    |

| 110 | 窒化物絶縁膜  |    |

| 111 | 保護膜     |    |

| 112 | ゲート電極   |    |

| 115 | 部位      |    |

| 131 | マスク     | 20 |

| 132 | マスク     |    |

| 133 | 領域      |    |

| 150 | トランジスタ  |    |

| 215 | 部位      |    |

| 216 | 部位      |    |

| 301 | トランジスタ  |    |

| 302 | 基板      |    |

| 303 | トランジスタ  |    |

| 305 | 絶縁膜     |    |

| 306 | トランジスタ  |    |

| 307 | 半導体膜    | 30 |

| 309 | 導電膜     |    |

| 310 | 導電膜     |    |

| 311 | 導電膜     |    |

| 314 | 絶縁膜     |    |

| 316 | 絶縁膜     |    |

| 318 | 絶縁膜     |    |

| 319 | 導電膜     |    |

| 321 | 液晶層     |    |

| 322 | 液晶素子    |    |

| 323 | 配向膜     | 40 |

| 325 | 容量素子    |    |

| 342 | 基板      |    |

| 344 | 遮光膜     |    |

| 346 | 有色膜     |    |

| 348 | 絶縁膜     |    |

| 350 | 導電膜     |    |

| 352 | 配向膜     |    |

| 362 | 開口部     |    |

| 401 | 画素部     |    |

| 404 | 走査線駆動回路 | 50 |

- 4 0 6 信号線駆動回路

4 0 7 走査線

4 0 9 信号線

4 1 1 画素

4 1 5 容量線

4 3 2 液晶素子

4 3 4 パンジスタ

4 3 5 発光素子

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

(B)

【図22】

【図23】

(A)

(B)

【図24】

(A)

(B)

【図25】

---

フロントページの続き

(51)Int.Cl.

F I

|         |        |         |

|---------|--------|---------|

| H 0 1 L | 21/28  | 3 0 1 B |

| H 0 1 L | 21/28  | 3 0 1 R |

| H 0 1 L | 29/50  | M       |

| H 0 1 L | 21/28  | B       |

| H 0 1 L | 21/304 | 6 4 7 Z |

(72)発明者 肥塚 純一

栃木県栃木市都賀町升塚161-2 アドバンスト フィルム ディバイス インク株式会社内

(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 高橋 宣博

(56)参考文献 特開2010-135766(JP,A)

特開2012-094853(JP,A)

特開2005-078087(JP,A)

特開2011-100994(JP,A)

特開2012-244145(JP,A)

特開2007-281459(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 1 / 2 8

H 0 1 L 2 1 / 3 0 4

H 0 1 L 2 9 / 4 1 7

H 0 1 L 2 9 / 7 8 6