(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 22 479 T2 2004.08.19

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 010 013 B1

(21) Deutsches Aktenzeichen: 698 22 479.5

(86) PCT-Aktenzeichen: PCT/US98/14846

(96) Europäisches Aktenzeichen: 98 935 769.4

(87) PCT-Veröffentlichungs-Nr.: WO 99/06845

(86) PCT-Anmeldetag: 17.07.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 11.02.1999

(97) Erstveröffentlichung durch das EPA: 21.06.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 17.03.2004

(47) Veröffentlichungstag im Patentblatt: 19.08.2004

(51) Int Cl.<sup>7</sup>: G01R 3/00

H03K 19/00

(30) Unionspriorität:

902345 29.07.1997 US

(84) Benannte Vertragsstaaten:

DE, FR, GB

(73) Patentinhaber:

Intel Corporation, Santa Clara, Calif., US

(72) Erfinder:

MOONEY, R., Stephen, Beaverton, US; HAYCOCK, B., Matthew, Beaverton, US; KENNEDY, T., Joseph, Beaverton, US

(74) Vertreter:

Patentanwälte Hauck, Graafls, Wehnert, Döring, Siemons, 80336 München

(54) Bezeichnung: IMPEDANZSTEUERUNGSSCHALTUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****STAND DER TECHNIK****1. Gebiet der Erfindung**

[0001] Die vorliegende Erfindung betrifft eine Impedanzregelungsschaltung und im Besonderen Regelungsschaltungen zur Anpassung der Impedanz eines Bauelements einer Schaltung zumindest teilweise auf der Basis der Impedanz einer externen Kopplung.

**2. Beschreibung des Stands der Technik**

[0002] Allgemein bekannt sind Schaltkreisanordnungen für eine Schnittstellenfunktion zwischen Baulementen bzw. Komponenten eines digitalen Systems, wie etwa für ein Mikroprozessorsystem oder ein Serversystem. Die zunehmenden Signalgeschwindigkeiten wie etwa im Bereich von Übertragungen mit 500 Megabit pro Sekunde haben diese Schnittstellenschaltungen zunehmend komplex gestaltet. Aufgrund der zunehmenden Signalgeschwindigkeiten kann es zum Beispiel wünschenswert sein, die Impedanzen zwischen den Systemkomponenten anzupassen, wie etwa zwischen einem sendenden Verstärker und einer geregelten Impedanzsignalkopplung in einem Serversystem, um das Ausmaß der möglichen Signalreflexion zu reduzieren.

[0003] Impedanzregelungsschaltungen gemäß der vorstehenden Beschreibung sind allgemein bekannt. Wünschenswert wäre jedoch eine wirtschaftliche Implementierung einer Rückkopplungsschaltung auf einem Chip, wobei die angepasste bzw. geregelte Schaltungsimpedanz auch dann aktualisiert werden kann, wenn digitale Signalabfragen über die Schnittstellenschaltkreisanordnung übertragen werden.

[0004] US-A-5.596.285 offenbart eine integrierte Schaltung, die eine Vorrichtung aufweist, die Impedanzen von Sendern und Empfängern an Impedanzen von Übertragungsleitungen anpasst, welche entsprechende Sender und Empfänger verbinden. Zwei entsprechende Impedanzanpassungsblöcke der Vorrichtung reproduzieren entsprechende Strukturen der Sender und Empfänger, wobei die Impedanz der Anpassungsblöcke durch einen Referenzwiderstand angepasst wird. Eine Regelvorrichtung reproduziert entsprechend die Anpassungsbedingungen der Anpassungsblöcke in den Sendern und Empfängern.

[0005] EP-A-0 520 687 offenbart die Regelung von Impedanzwerten in Anwendungen integrierter Schaltungen durch die digitale Regelung der effektiven Größe eines Transistors, der mit einem Ausgangsanschluss oder mit einem Eingangsanschluss einer integrierten Schaltung verbunden ist. Die digitale Regelung der effektiven Größe kann durch eine parallele Verbindung zwischen einer Mehrzahl von MOS-Transistoren erreicht werden.

[0006] US-A-5.134.311 offenbart eine selbsteinstel-

lende Impedanzanpassungs-Steuereinheit für eine digitale Schaltung. Eine Anordnung von Gattern bzw. Toren ist parallel jeweils mit einem Gatter zur Verbindung mit einem positiven Pol und mit einem Gatter zur Verbindung mit einem negativen Pol vorgesehen, wobei eine oder mehrere der Gatteranordnungen selektiv als Reaktion auf eine Schaltungseinrichtung freigegeben werden, welche eine Impedanzabstimmung zwischen einem Ausgang der Steuereinheit und einem durch die Steuereinheit gesteuerten Netzwerk überwacht.

**ZUSAMMENFASSUNG DER ERFINDUNG**

[0007] Vorgesehen ist gemäß einem ersten Aspekt der vorliegenden Erfindung eine digitale Rückkopplungsschaltung gemäß dem gegenständlichen Anspruch 1.

[0008] Vorgesehen ist gemäß einem zweiten Aspekt der vorliegenden Erfindung ein Verfahren gemäß dem gegenständlichen Anspruch 9.

**KURZE BESCHREIBUNG DER ZEICHNUNGEN**

[0009] Der Gegenstand der vorliegenden Erfindung ist in den abschließenden Abschnitten der Patentschrift im Besonderen und eindeutig ausgeführt. Die vorliegende Erfindung wird jedoch sowohl in Bezug auf den Aufbau als auch auf ihre Funktionsweise sowie in Bezug auf ihre Aufgaben, Merkmale und Vorteile am besten durch Verweis auf die folgende genaue Beschreibung deutlich, wenn diese in Verbindung mit den beigefügten Zeichnungen gelesen wird. Es zeigen:

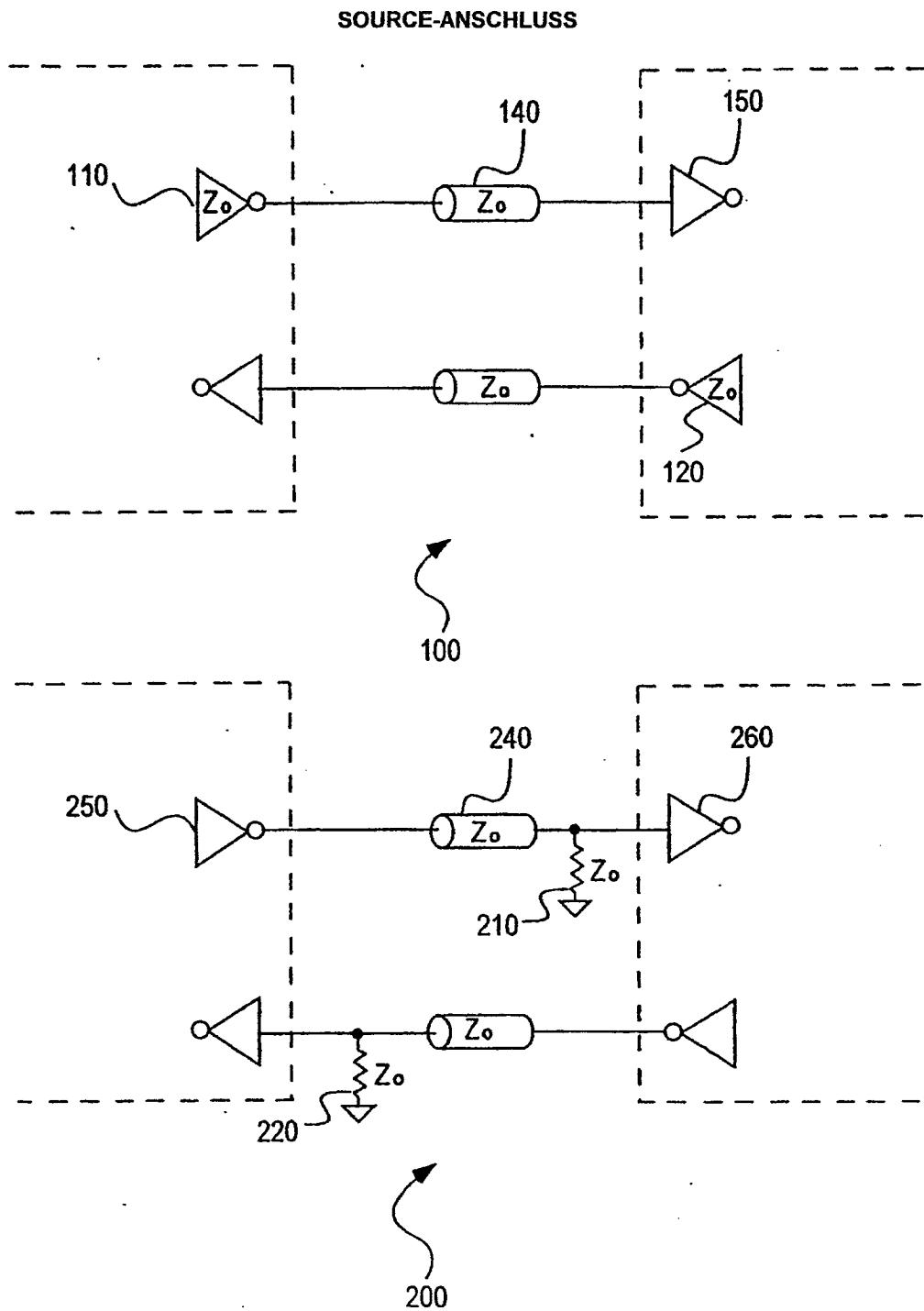

[0010] **Fig. 1** eine Prinzipskizze zweier alternativer Abschlussverfahren;

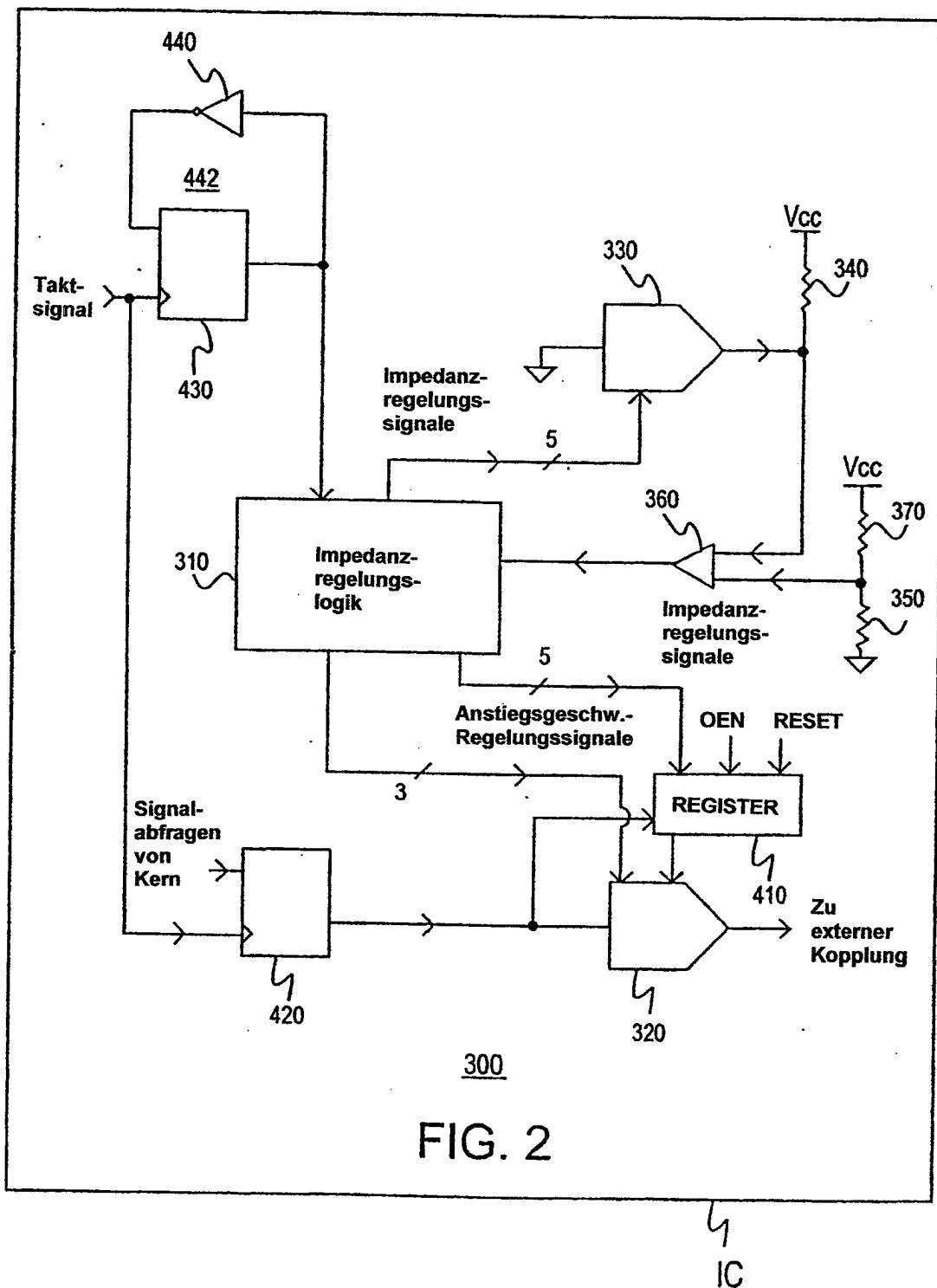

[0011] **Fig. 2** ein Blockdiagramm eines Ausführungsbeispiels einer Impedanzregelungsschaltung gemäß der vorliegenden Erfindung;

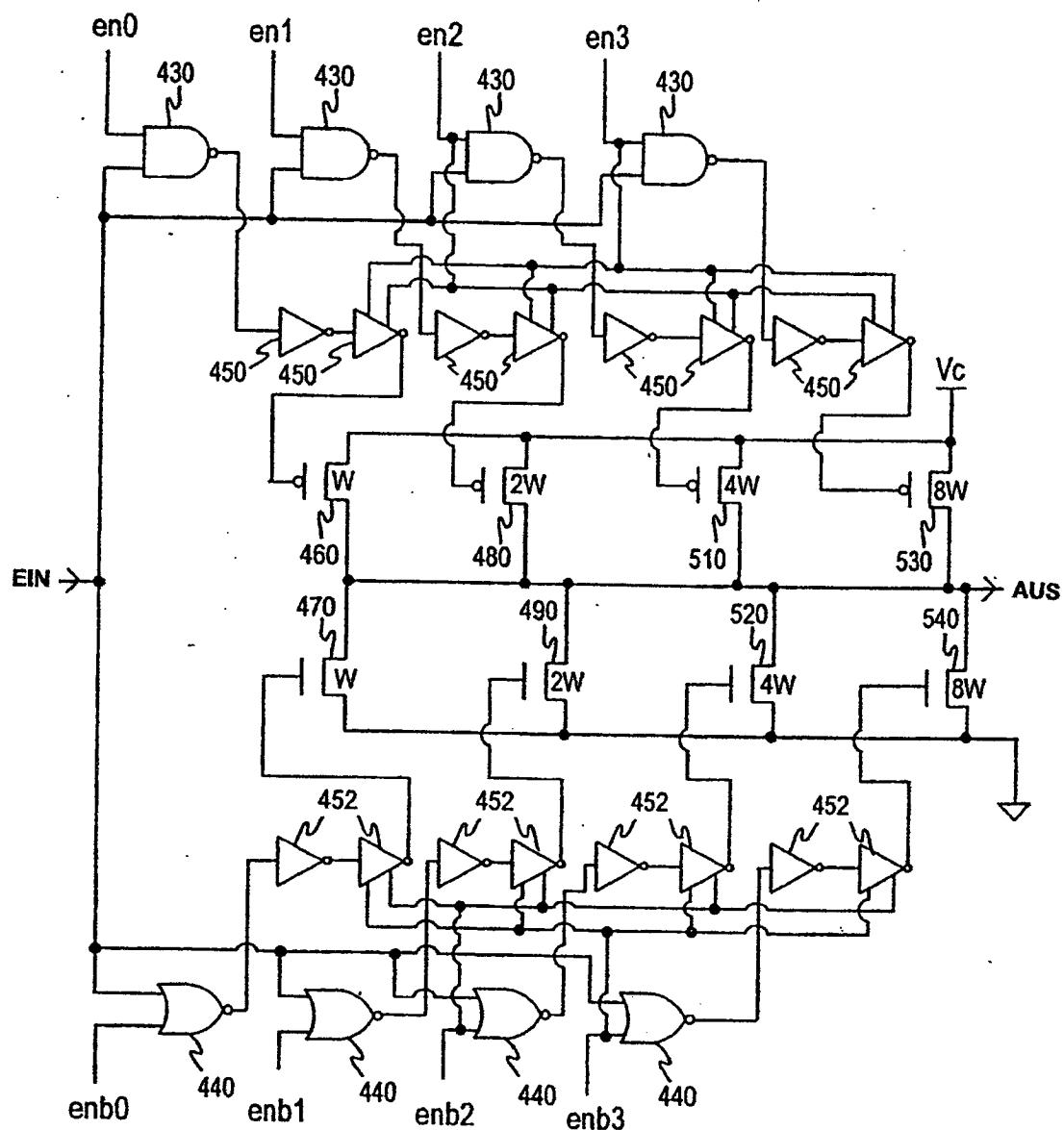

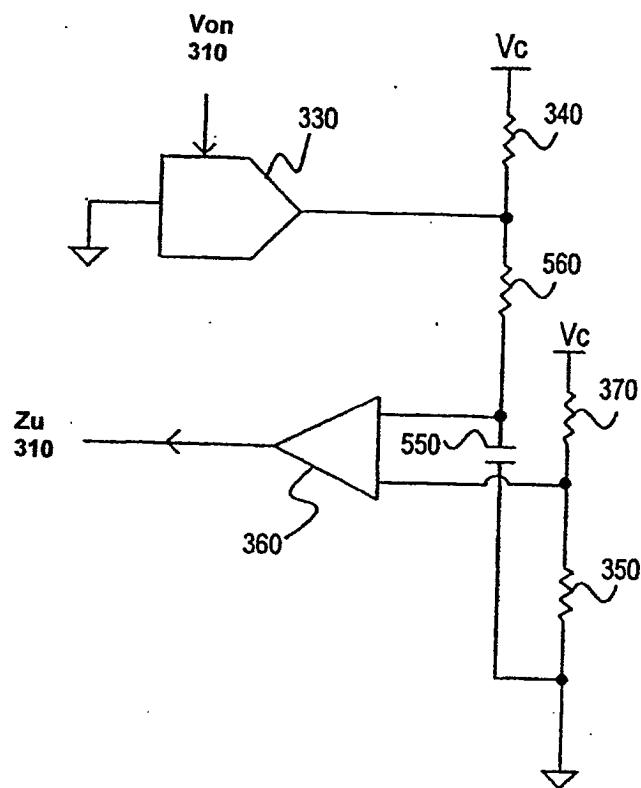

[0012] **Fig. 3** ein Schaltungsdiagramm, das den Ausgangspuffer aus **Fig. 2** in näheren Einzelheiten darstellt;

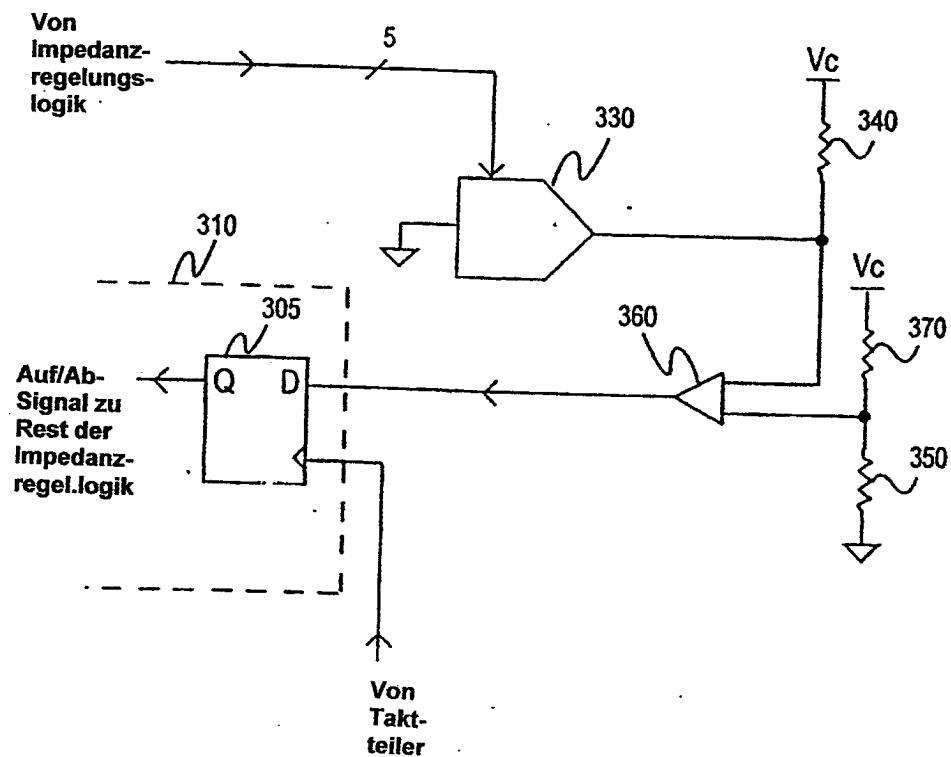

[0013] **Fig. 4** ein Blockdiagramm eines Abschnitts des Ausführungsbeispiels aus **Fig. 2** in näheren Einzelheiten;

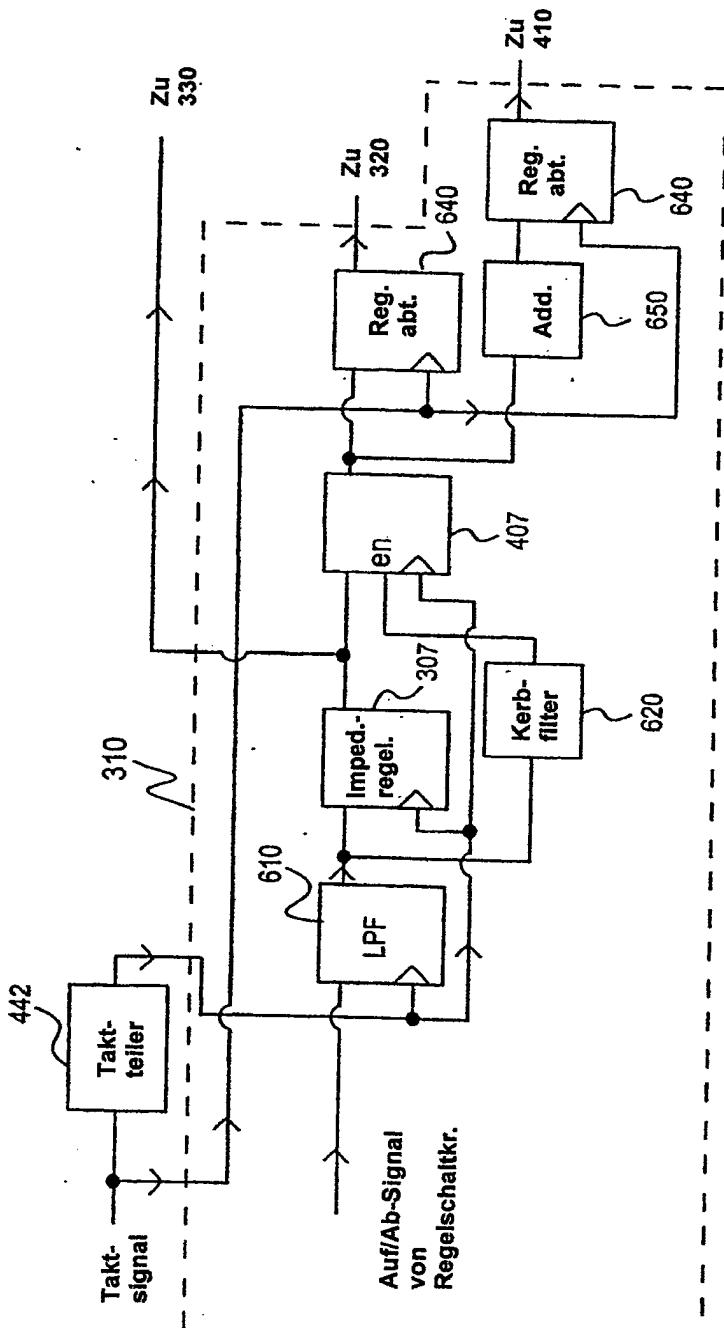

[0014] **Fig. 5** ein Blockdiagramm eines Abschnitts des Ausführungsbeispiels aus **Fig. 2** in näheren Einzelheiten;

[0015] **Fig. 6** ein Blockdiagramm eines Abschnitts des Ausführungsbeispiels aus **Fig. 2** in näheren Einzelheiten;

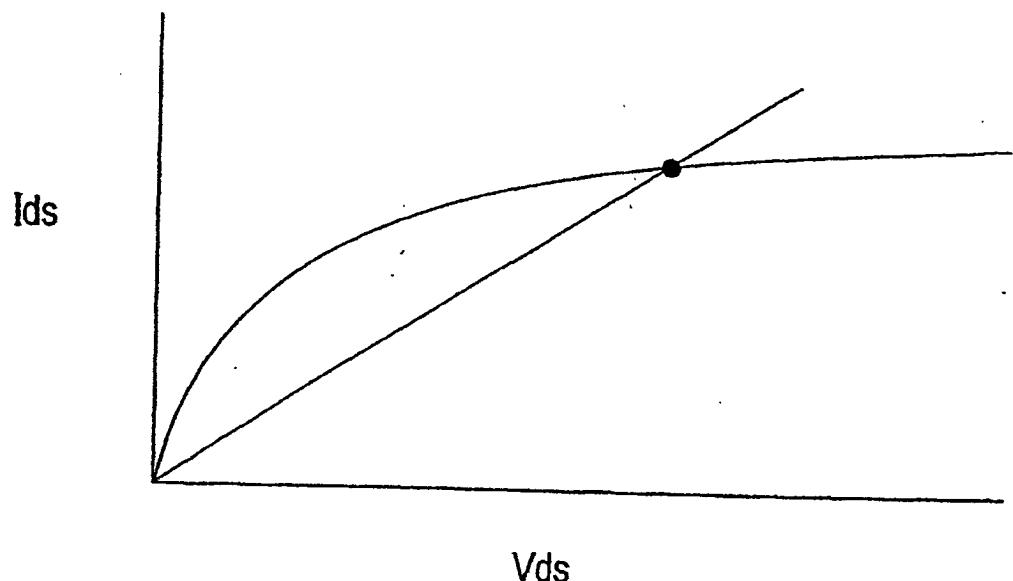

[0016] **Fig. 7** eine Darstellung, die Strom und Spannung (I/V) eines kennzeichnenden Metalloxid-Transistors (MOS-Transistors) gegenüberstellt; und

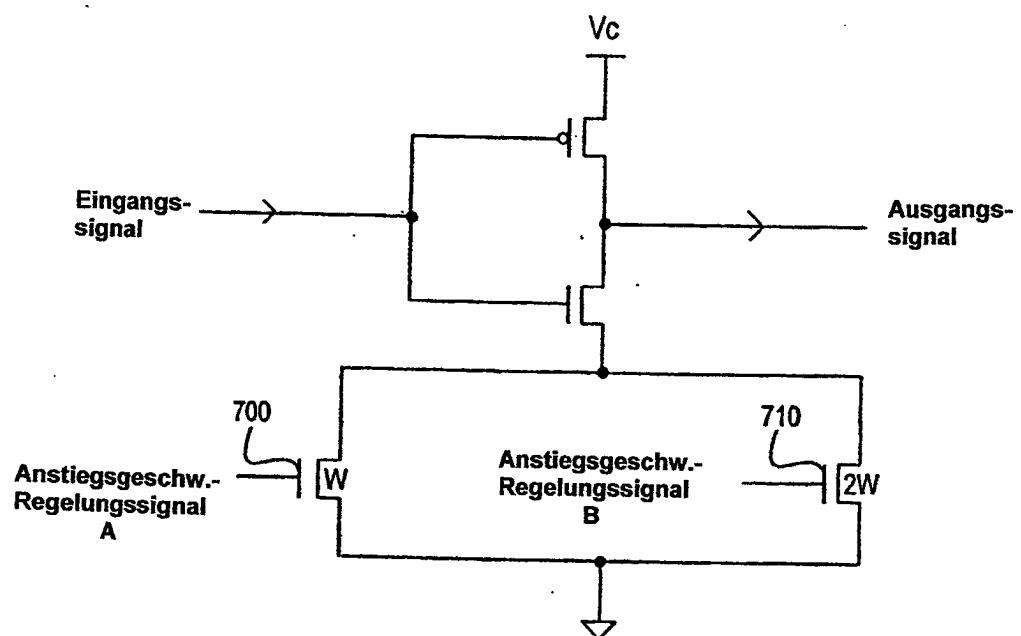

[0017] **Fig. 8** ein Schaltungsdiagramm eines Abschnitts des Ausführungsbeispiels aus **Fig. 3** in näheren Einzelheiten.

## GENAUE BESCHREIBUNG DER ERFINDUNG

[0018] In der folgenden genauen Beschreibung sind spezifische Einzelheiten ausgeführt, um ein umfassendes Verständnis der vorliegenden Erfindung vorzusehen. Der Fachmann auf dem jeweiligen Gebiet wird jedoch erkennen, dass die vorliegende Erfindung auch ohne diese spezifischen Details ausgeführt werden kann. In anderen Fällen wurde auf die Beschreibung allgemein bekannter Verfahren, Prozeduren, Komponenten und Schaltungen verzichtet, um die vorliegende Erfindung nicht unnötig zu verschleiern.

[0019] Im Zuge der Weiterentwicklung der Technologie der Siliziumverarbeitung nimmt die Geschwindigkeit der aus Silizium hergestellten Logikbauelemente weiter zu. Als Folge sind Hochgeschwindigkeits-Schnittstellenschaltkreisanordnungen für die Übertragung elektrischer Signale wünschenswert, wie etwa digitaler Signale, in und aus Chips integrierter Schaltungen, die auch bei diesen höheren Geschwindigkeiten funktionstüchtig sind. Für die Übermittlung elektrischer Hochgeschwindigkeitssignale mit Schnittstellenschaltkreisanordnungen ist der Einsatz einer ordnungsgemäß abgeschlossenen, geregelten Impedanzschaltung wünschenswert. Abschlusschaltungen oder Strukturen, um dies zu erreichen, können entweder auf Chips oder außerhalb von Chips implementiert werden; wobei allerdings im Besonderen Abschlusstechniken auf Chips Kosten- und Geschwindigkeitsvorteile gegenüber den Abschlusstechniken außerhalb von Chips aufweisen.

[0020] Die Abbildung aus **Fig. 1** zeigt eine Prinzipskizze von Ansätzen für einen Source- bzw. Ursprungsabschluss als auch einen parallelen Abschluss. Jeder Ansatz kann zur Implementierung eines Ausführungsbeispiels gemäß der vorliegenden Erfindung eingesetzt werden; jedoch wird das nachstehend beschriebene Ausführungsbeispiel als eine Source-Abschlusschaltung implementiert, um die Kosten- und Geschwindigkeitsvorteile zu nutzen, welche dieser Ansatz bietet. Wie dies in der Abbildung aus **Fig. 1** dargestellt ist, werden bei beiden Ansätzen elektrische Signale, wie etwa digitale Signale in dem vorliegenden speziellen Ausführungsbeispiel, von einer Ursprungssteuereinheit wie etwa 110 oder 250 zu einer Zielsteuereinheit wie etwa 150 oder 260 übermittelt. In ähnlicher Weise werden diese Signale über eine Kopplung wie etwa 140 oder 240 mit einem Widerstand  $Z_0$  übermittelt. Die Leistung kann im Verhältnis zu alternativen Ansätzen verbessert werden, wenn die allgemein bekannte Technik der Impedanzanpassung eingesetzt wird. Durch die Anpassung der Impedanz der Kopplung **140** bzw. **240** werden elektrische Signale, die von der Zielsteuereinheit reflektiert werden könnten, ordnungsgemäß abgeschlossen. In diesem Zusammenhang bedeutet dies, dass an dem Ursprungsende der Kopplung im Wesentlichen keine elektrischen Signalreflexionen auftreten.

[0021] Wie dies in der Abbildung aus **Fig. 1** dargestellt ist, kann ein Ansatz mit einem Ursprungsabschluss oder ein Ansatz mit einem parallelen Abschluss verwendet werden. Bei einem Ansatz mit Ursprungsabschluss wird die Impedanz der Kopplung wie etwa 140 durch die Impedanz der Ursprungssteuereinheit wie etwa 110 angepasst bzw. abgestimmt. Bei einem Ansatz mit parallelem Abschluss wird die Impedanz über eine Kopplung der abstimmenden Impedanz wie etwa 210 mit der Impedanz der abgestimmten Kopplung abgestimmt wie etwa 240.

[0022] Die Schnittstellenschaltkreisanordnung kann in Verbindung mit einem Signalbus eingesetzt werden, wie zum Beispiel für einen Betrieb in einem Desktop-Personalcomputer oder einer Serverkonfiguration, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist. Um die für Serveranwendungen wünschenswerten Geschwindigkeiten zu erreichen, kann zum Beispiel eine Impedanzabstimmung gemäß der vorstehenden Beschreibung eingesetzt werden. Wie dies jedoch bereits vorstehend im Text beschrieben worden ist, können Kosten- und Geschwindigkeitsfaktoren den Einsatz des Ansatzes eines parallelen Abschlusses auf einem Chip oder an einer anderen Position weniger wünschenswert machen als den Einsatz des Ansatzes mit Ursprungsabschluss. In dem vorliegenden speziellen Ausführungsbeispiel kann somit zum Beispiel die Impedanz einer Steuereinheit mit der Impedanz einer externen Kopplung mit einem Netzwerk abgestimmt werden, um zum Beispiel die gewünschten Signalgeschwindigkeiten zu erreichen.

[0023] Beim Einsatz von Metalloxidhalbleiter-Technologien (MOS) kann die Impedanzabstimmung die Abstimmung einer bestimmten Impedanz mit der Impedanz umfassen, die einem bestimmten Punkt auf einer nichtlinearen charakteristischen Strom-Spannungs-Kurve (I/V-Kurve) zugeordnet ist, welche den Betrieb eines MOS-Transistors darstellt. Eine derartige charakteristische Kurve ist einem MOS-Transistor zugeordnet, wobei der Drain-Source-Strom auf der Y-Achse dargestellt ist, während die Drain-Source-Spannung auf der X-Achse dargestellt ist, wie dies in der Abbildung aus **Fig. 7** veranschaulicht ist.

[0024] Für die Durchführung dieser Impedanzabstimmung können eine Vielzahl von Ansätzen eingesetzt werden, wobei der Umfang der vorliegenden Erfindung auf keinen bestimmten Ansatz beschränkt ist, wobei weder der Betriebsbereich eines MOS-Transistors beschränkt ist oder eine Schaltung eingesetzt wird, um den Betrieb eines MOS-Transistors zumindest näherungsweise zu linearisieren. In dem vorliegenden speziellen Ausführungsbeispiel jedoch wird die abzustimmende Impedanz aufgrund der einfachen Implementierung auf einen ausgesuchten Punkt auf der charakteristischen Strom-Spannungs-Kurve (IIV) des MOS-Transistors abgestimmt. Ein derartiger Ansatz ermöglicht den Einsatz eines invertierenden Komplementär-Metalloxid-Halbleiterpuffers (CMOS-Puffer) als Ausgangs-

puffer. Ein Nachteil ist es jedoch, dass Störquellen, die zu Übergängen auf andere Bereiche der I/V-Kurve führen, wie etwa dem Sättigungsbereich des Betriebs des Transistors, nicht ordnungsgemäß abgeschlossen werden und somit zu Interferenzen zwischen Symbolen beitragen können.

[0025] Für die Approximation der Impedanz der externen Kopplung durch die Impedanz eines CMOS-Ausgangspuffers gibt es eine Reihe von Möglichkeiten. Zum Beispiel können Kaskodenvorrichtungen oder eine in Reihe geschaltete Torsteuerung eingesetzt werden. Die Schaltungen können so implementiert werden, dass sie eine digitale oder eine analoge Regelung ermöglichen. Für das vorliegende spezielle Ausführungsbeispiel wird aufgrund der potenziell mit Störungen versehenen Umgebung für die elektronischen Signale ein digitaler Ansatz verwendet, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist.

[0026] In einem Ausführungsbeispiel kann eine Schaltung unter Verwendung von Kaskodenvorrichtungen implementiert werden, wobei ein primärer Ausgangsverstärker in Reihe angeschlossen ist, um die effektive Impedanz der Gesamtstruktur anzupassen oder zu regeln, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist. Die Kaskodenvorrichtungen können eine Mehrzahl paralleler Kopplungen aufweisen, die einzeln freigegeben werden können.

[0027] Die Gewichtung dieser Vorrichtungen zur Anpassung der effektiven Impedanz des Ausgangspuffers kann auf verschiedene Art und Weise erreicht werden, wobei der Umfang der vorliegenden Erfindung nicht auf einen bestimmten Ansatz beschränkt ist. Zwei häufig eingesetzte Ansätze sind eine binäre Gewichtung und eine lineare Gewichtung. Obwohl die Gesamtgröße der Vorrichtung den verfügbaren Impedanzbereich beeinflussen kann, der implementiert wird, kann die Auflösung der Impedanz zum Beispiel auch durch die Größe der kleinsten Vorrichtung beeinflusst werden, wie dies in der Abbildung aus **Fig. 3** dargestellt ist. Ein Vorteil der binären Gewichtung ist es, dass sie für eine bestimmte Auflösung einen größeren Impedanzbereich im Vergleich zu einer linearen Gewichtung zulässt, wobei dies jedoch Nachteile in Bezug auf die "fliegende" Aktualisierung der Impedanz aufweist, wie dies nachstehend im Text näher beschrieben wird.

[0028] Wie dies bereits vorstehend im Text beschrieben worden ist, kann bei einem alternativen Ansatz eine in Reihe geschaltete Torsteuerung oder Regelung der Impedanz des Ausgangspuffers eingesetzt werden. Dieser spezielle Ansatz wird in dem in der Abbildung aus **Fig. 3** veranschaulichten Ausführungsbeispiel eingesetzt, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen speziellen Ansatz beschränkt ist. Der spezielle zur Implementierung des Ausgangspuffers verwendete Ansatz kann weitere Aspekte der Implementierung beeinflussen, einschließlich der Größe des kleinsten

Zweigs, wie etwa durch die Empfindlichkeit der elektrostatischen Entladung (ESD) und ebenso die Fläche des Chips, welche der jeweilige Puffer belegt. Zum Beispiel verwendet ein Kaskodenansatz eine verhältnismäßig große Fläche im Vergleich zu dem Ansatz mit in Reihe geschalteter Torsteuerung.

[0029] Wie dies in der Abbildung aus **Fig. 3** dargestellt ist, handelt es sich bei dem Verstärker um eine Vorrichtung mit mehreren Zweigen, wobei das Eingangssignal durch Freigabesignale für die einzelnen Zweige gesteuert wird. In diesem Zusammenhang betrifft der Begriff Zweig die primären Transistoren, die zur Implementierung der Verstärkerkonfiguration (z. B. **460, 470, 480, 490, 510, 520, 530** und **540**) eingesetzt werden. Im Vergleich zu dem Kaskadenansatz ist die Größe des Verstärkers insgesamt kleiner. Da die vorgeschalteten Steuereinheiten wie etwa 430 oder 440 komplexer sind, kommt es jedoch zu Geschwindigkeitseinbußen, wodurch eine zusätzliche Verzögerung hinzugefügt wird.

[0030] Die Anstiegsgeschwindigkeit für die erzeugten elektronischen digitalen Signale kann ebenfalls angepasst bzw. geregelt werden. Es können wiederum verschiedene Techniken eingesetzt werden, einschließlich analoger Techniken und digitaler Techniken. Das in der Abbildung aus **Fig. 3** veranschaulichte Ausführungsbeispiel umfasst sowohl eine Anpassung der Impedanz als auch der Anstiegsgeschwindigkeit. In dem vorliegenden speziellen Ausführungsbeispiel wird eine Teilmenge der Impedanzregelungskopplungen zur Regelung der Anstiegsgeschwindigkeit eingesetzt. Dieser spezielle Ansatz reduziert die Regelungsschaltkreisanordnung und die Kopplung im Vergleich zu einem Ansatz, bei dem sowohl die Impedanzregelung als auch die Regelung der Anstiegsgeschwindigkeit in den gleichen Puffer gehen. In dem vorliegenden speziellen Ausführungsbeispiel wird ein 4-Bit-Regelungssystem mit einer 2-Bit-Anstiegsgeschwindigkeitsregelung der 4 Bits eingesetzt. Die Anpassung der Anstiegsgeschwindigkeit kann zum Beispiel unter Verwendung paralleler Zweige an der vorgeschalteten Steuereinheit für die Seite der Vorrichtung erreicht werden, die sich einschaltet oder das elektrische digitale Ausgangssignal erzeugt. Für eine vorgeschaltete PMOS-Steuereinheit weist die N-Vorrichtung zum Beispiel mehrere Zweige auf. Wie dies in der Abbildung aus **Fig. 8** dargestellt ist, die eine Detailansicht von **450** darstellt, wurden die Vorrichtungen **700** und **710** kaskodenartig mit der vorgeschalteten Steuereinheit der N-Typ MOS-Vorrichtung (NMOS) hinzugefügt. Die Inverter **452** können einen ähnlichen Ansatz unter Verwendung von PMOS-Vorrichtungen einsetzen. Die Vorrichtungen **700** und **710** aus **Fig. 8** werden zur Regelung der Impedanz der vorgeschalteten Steuereinheit in einem Ansatz verwendet, der dem Ansatz ähnlich ist, der zur Regelung als Impedanz des Ausgangspuffers mit den Vorrichtungen **460, 470**, etc. verwendet wird. Diese Impedanz, welche die Kapazität der Ausgangspuffer steuert, wie etwa über die Vorrich-

tungen **460**, **570**, etc. schränkt die Anstiegs geschwindigkeit des Ausgangspuffers ein. Nur die Anstiegsgeschwindigkeit des Einschaltens des Ausgangspuffers wird in diesem Ausführungsbeispiel ge regelt, da der Ausgangspuffer zur Verwendung in einer Konfiguration mit Ursprungsabschluss vorgesehen ist. Wenn alternativ ein Ausführungsbeispiel mit parallelem Abschluss eingesetzt wird, würde die Anstiegsgeschwindigkeit des Abschaltens ebenfalls ge regelt werden, und zwar zumindest teilweise auf grund des statischen Stroms der Kopplung.

[0031] In dem in der Abbildung aus **Fig. 3** veranschaulichten Ausführungsbeispiel eines Ausgangspuffers werden en3 und en2 für die Anpassung der Anstiegsgeschwindigkeit verwendet. Ein Versatzwert zwischen den nominalen Werten für die Impedanz anpassung und die Anpassung der Anstiegsgeschwindigkeit kann in der Regelungslogik eingesetzt werden, wie dies nachstehend im Text näher beschrieben ist. Wenn die Impedanz der vorgeschalteten Steuereinheit somit gut geregelt wird, kann auch die Anstiegsgeschwindigkeit der Steuereinheit innerhalb eines engen Rahmens gut geregelt werden.

[0032] Ein digitaler Regelkreis kann eingesetzt werden, um für einen digital regelbaren Puffer gemäß der vorstehenden Beschreibung zum Beispiel Schwan kungen in dem Verfahren und in der Umgebung aus zugleichen. Hiermit wird festgestellt, dass der Umfang der vorliegenden Erfindung nicht auf den vorstehend beschriebenen digital regelbaren Puffer be schränkt ist. Eingesetzt werden kann jeder digital regelbare Puffer sowie auch ein nicht digital regelbarer Puffer, der anderweitig regelbar ist. Da Rauschen bzw. Störungen an der in der Abbildung aus **Fig. 4** veranschaulichten Signalabtastschnittstelle vorhanden ist, ist es wünschenswert, die Bandbreite der Schleife bzw. des Kreises einzuschränken bzw. zu begrenzen, um die Empfindlichkeit in Bezug auf diese Störungen zu verringern. Ein Filter kann auf verschiedene Art und Weise implementiert werden, wie etwa als Abtaststift, in dem vorliegenden Ausführungsbeispiel die Schnittstelle von **330**, **340** und **360** oder in dem Block **310** der Regelungslogik, zur Begrenzung der Schleifenbandbreite. Ein weiterer Vor teil ist es, dass dies den Einsatz verhältnismäßig langsamer Schaltungskomponenten ebenso ermöglicht wie eine Reduzierung der Abtastrate, um eine Metastabilitäts-Ausregelzeit zu ermöglichen, wie dies nachstehend im Text beschrieben ist.

[0033] Die Prinzipskizze der Abbildung aus **Fig. 2** veranschaulicht ein Ausführungsbeispiel **300** eines Impedanzregelkreises gemäß der vorliegenden Erfindung, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf das spezielle vorliegende Ausführungsbeispiel beschränkt ist. Das Ausführungsbeispiel **300** ist als auf einem Chip einer integrierten Schaltung (IS) ausgeführt veranschaulicht, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist. Gemäß der Abbildung steuert ein abgeleitetes Takt signal den Regelkreis;

wobei es durch den Teiler **442** dividiert bzw. geteilt wird. Der Ausgangspuffer **330** umfasst einen Schnittstellenschaltungs-Ausgangspuffer, wobei der Ausgangspuffer **330** ein datenfreies Signal oder einen "leeren" bzw. blinden Ausgangspuffer umfasst. Eine Rückkopplungsschleife mit einem Verstärker **360** und einer Impedanzregelungslogik **310** ist so gekoppelt, dass sie die Impedanz des Ausgangspuffers **330** zumindest teilweise auf der Basis der Impedanz der externen Kopplung **340** anpasst. Die Rückkopplungsschaltung arbeitet in dem vorliegenden speziellen Ausführungsbeispiel so, dass sie die Impedanz des Puffers **330** ungefähr mit der Impedanz des externen Widerstands **340** abstimmt. Ebenso erzeugen die Widerstände **370** und **350** in dem vorliegenden Ausführungsbeispiel wirksam den Spannungssignal-Referenzwert für den Verstärker **360**. Die Impedanzregelungslogik **310** regelt zumindest teilweise auf der Basis des Ausgangssignals des Verstärkers **360**, ob die Impedanz des Puffers **330** nach oben oder nach unten angepasst werden soll, das heißt, ob die Pufferimpedanz erhöht oder reduziert werden soll. Die Regelungssignalinformationen werden ebenso dem Puffer **320** zugeführt. Die Rückkopplungsschaltung erzeugt ferner Regelungssignale zur Anpassung der Anstiegsgeschwindigkeit des Puffers **320** auf der Basis der Impedanzregelungssignale, die durch den Betrieb der Rückkopplungsschleife einschließlich des Puffers **330** erzeugt werden. Ebenso wird das Register **410** eingesetzt, so dass der Puffer **320** "fliegend" aktualisiert werden kann, wie dies nachstehend im Text näher erörtert wird.

[0034] Die Abbildung aus **Fig. 4** veranschaulicht einen Teil des Ausführungsbeispiels aus **Fig. 2**. Für den in der Abbildung aus **Fig. 4** veranschaulichten Teil des Ausführungsbeispiels ist ein externer Präzisionswiderstand **340** mit einem Ausgangsanschluss des datenfreien (blindem bzw. leeren) Ausgangspuffers **330** gekoppelt. Danach wird der für den Puffer **330** durch den Betrieb der vorstehend beschriebenen Rückkopplungsschaltung erhaltene Impedanzwert zur Anpassung der Impedanz des Ausgangspuffers **320** verwendet. Für die Rückkopplungsschaltung des vorliegenden Ausführungsbeispiels wird ein Referenzspannungs-Signalwert für den Verstärker **360** erzeugt. Dieser Referenzspannungs-Signalwert wird in dem vorliegenden Ausführungsbeispiel durch die Widerstände **350** und **370** aus der Abbildung aus **Fig. 4** implementiert. Dadurch wird der Grenzwert für den Verstärker **360** festgelegt. Dieser Referenzwert legt effektiv den Punkt auf der charakteristischen I/V-Kurve des MOS-Transistors fest, auf den die Impedanz des Puffers **330** abgestimmt wird. Der Widerstand **340** wird durch Approximation des nominalen Wertes der externen Kopplung mit dem Puffer **320** aus gewählt. Natürlich kann alternativ an Stelle des Widerstands **340** eine extern abgeleitete Kopplung eingesetzt werden, wobei aber auch ein anderer Ansatz eingesetzt werden kann.

[0035] Die Rückkopplungsschaltung arbeitet in dem

vorliegenden Ausführungsbeispiel wie folgt. Durch einen Eingangsspeicher **305** wird ein Abtastimpedanzsignalwert aufgenommen. Ein erster vorbestimmter Zeitraum läuft ab, um eine Ausregelung etwaiger Metastabilitäten in dem Signalspeicher zu ermöglichen. Auf der Basis des erhaltenen Signalabtastwertes und der Impedanz des Puffers **330** im Verhältnis zu dem Widerstand **340** wird bestimmt, in welche Richtung die Impedanz des Puffers **330** angepasst werden soll, das heißt, ob die Impedanz erhöht oder verringert wird. Dies kann zum Beispiel in **310** implementiert werden, indem der Wert eines Auf- und Abwärtszählers oder eines Schieberegisters auf die Regelung der Impedanz des Puffers **330** angepasst wird, wie dies nachstehend im Text erörtert wird. So mit erzeugt die Impedanzregelungslogik **310** dem Puffer **330** zugeführte Signale, um den nächsten Impedanzwert zu erzeugen. Ein zweiter vorbestimmter Zeitraum läuft ab, damit sich die Änderung des angepassten Impedanzwertes an dem Ausgangsanschluss des Puffers **330** ausregeln und durch den Eingangsverstärker **360** ausbreiten kann. Dieser Prozess wird wiederholt, bis die Impedanz, in dem speziellen vorliegenden Ausführungsbeispiel der Widerstand **340**, abgestimmt worden ist, wie dies gewünscht ist. An diesem Punkt führt der Regelkreis **310** bezüglich der Impedanz des Puffers **330** zu einer Erhöhung oder Reduzierung eines wertniedrigsten Steuerbits um einen gewünschten Impedanzwert.

[0036] Der Zeitraum für eine Metastabilitätsausregelung sowie für die Ausregelung des Übergangs des Ausgangspuffers **330** wird in dem vorliegenden Ausführungsbeispiel durch einen Takteiler vorgesehen, wie dies in der Abbildung aus **Fig. 4** dargestellt ist. Gemäß der Abbildung wird die Logik in dem Regelkreis durch das dividierte Taktignal getaktet. Es ist wünschenswert, den Takt oder die Abtastrate so festzulegen, dass durch die metastabilen Zustände in dem Eingangsspeicher **305** eine niedrige Abtastfehlerrate erreicht wird. Diese Metastabilitäten können durch Störungen an dem leeren bzw. blinden Stift zu jedem Zeitpunkt in Bezug auf den Takt auftreten, und somit gegen die Einstell- und Speicherbedingungen des Signalspeichers **305** verstößen. Die Berechnung des mittleren Zeitraums zwischen Fehlern eines Signalspeichers umfasst Parameter wie etwa die Verarbeitungstechnologie, die Bauweise des Signalspeichers, die zulässige Ausregelungszeit und die Wahrscheinlichkeitsverteilung der Datenflankenzeitsteuerung des Signalspeichers in Bezug auf den Takt. Unter Verwendung zulässiger Grenzen für diese Parameter und einer zulässigen Fehlerrate kann eine zulässige Ausregelzeit berechnet werden. Für einen Signalspeicher, der einheitlich verteilte asynchrone Datensignale mit einer Frequenz von ungefähr **433** Megahertz abtastet (und bestimmte vereinfachte Annahmen trifft), ist es wünschenswert, den Takt durch mindestens zwei erzeugte Abtasttaktpulse zu teilen, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt

ist. In dem vorliegenden Ausführungsbeispiel sieht der Teiler **442** somit eine zulässige Ausregelungszeit für die Zielverarbeitung vor, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist.

[0037] Ein weiterer Aspekt des vorliegenden Ausführungsbeispiels umfasst das Filtern von Frequenzen, die höher sind als die Hälfte der Abtastrate, um die Störquellen zu reduzieren, die auf oder oberhalb der Nyquist-Frequenz auftreten. Diese Frequenzen könnten ansonsten zu einem Treppeneffekt führen. Die Abbildung aus **Fig. 5** veranschaulicht den in dem vorliegenden Ausführungsbeispiel eingesetzten Filter, wobei der Umfang der vorliegenden Erfindung auch diesbezüglich nicht auf den Einsatz eines Filters oder auf das spezielle vorliegende Ausführungsbeispiel beschränkt ist. Ebenso ist es bei der Platzierung des Poles des Filters wünschenswert, Instabilitäten zu vermeiden. Somit ist es wünschenswert, die Impedanz auf einer niedrigeren Frequenz als der Bandbreite der Schleife zu aktualisieren, um eine Ausregelung der Schleifenzeit nach einer Aktualisierung zu ermöglichen. In dem vorliegenden speziellen Ausführungsbeispiel wird der Pol des analogen Filters niedriger als die Hälfte der Abtastfrequenz platziert, jedoch mindestens auf dem Zweifachen der Aktualisierungsrate, wobei die vorliegende Erfindung jedoch nicht auf diesen Aspekt beschränkt ist. In dem Frequenzbereich des Zeitbereichs erfolgt das nächste Abtastereignis somit nach der Aktualisierung der Impedanz nach zwei Filterzeitkonstanten. Natürlich kann vor dem nächsten Abtastereignis auch eine größere Anzahl von Filterzeitkonstanten eingesetzt werden, wobei dies jedoch die Sperrzeit der Regelschleife bzw. des Regelkreises erhöhen kann.

[0038] Durch den Betrieb des Regelkreises und eine Situation, bei der die Impedanz des Ausgangspuffers **320** nicht präzise übereinstimmt, sollte der Regelkreis mit einer Schwankung von einem Bit von dem Abstimmungspunkt sperren und somit oszillieren. Es ist wünschenswert, diese Oszillation aus dem tatsächlich durch den Puffer **320** erzeugten Ausgangssignal zu entfernen. Es kann ein einfacher digitaler Kerbfilter eingesetzt werden, obwohl dies auch auf verschiedene andere Arten möglich ist. Zum Beispiel kann auch eine einfache exklusive Oder-Schaltung eingesetzt werden. Wenn aufeinanderfolgende digitale Abtastwerte übereinstimmen, so wird eine Aktualisierung des Puffers **320** durchgeführt, wobei für den Fall, dass aufeinanderfolgende Abtastungen nicht übereinstimmen, die letzte Aktualisierung durch den Puffer **320** gespeichert wird. Dieses spezielle Ausführungsbeispiel ist in der Abbildung aus **Fig. 6** dargestellt. Wie dies dargestellt ist, sieht der Impedanzregelungsblock **310** Signale an den Ausgangspuffer **330** vor. Ebenso werden Ausgangssignale des Tiefpassfilters **610** an den Kerbfilter **620** vorgesehen. Der Kerbfilter **620** sieht ein Signal an den Block **407** vor. Abhängig von den an den Kerbfilter **620** vorgesehenen aufeinanderfolgenden Abtastwerten werden

die durch 310 erzeugten Impedanzregelungssignale durch den Block **407** auch an das Register **640** vorgesehen und somit an das Register **410** und letztendlich an den Puffer **320**.

[0039] Die Implementierung des Impedanzregelungsblocks **307** ist zumindest teilweise von der Gewichtung der Zweige der Ausgangspuffer abhängig. Wenn die Vorrichtungen zum Beispiel linear gewichtet sind, kann ein Schieberegister eingesetzt werden. Wenn sie jedoch binär gewichtet sind, kann dieser Block als ein Auf- und Abwärtszähler implementiert werden. Bei einem linear gewichteten Puffer würde sich bei jeder Impedanzaktualisierung ein Bit eines Schieberegisters verändern, wobei sich die Impedanz des Puffers in einem im Wesentlichen einheitlichen Ausmaß ändern würde. Bei einem binär gewichteten Puffer wird ein Zähler aktualisiert, wobei ein weiterer binärer digitaler Signalwert erzeugt wird, der die Pufferimpedanz regelt. Bei einem derartigen Ausführungsbeispiel können sich somit alle Bits des Zählers bei einer einzigen Impedanzaktualisierung ändern. Wie dies in der Abbildung aus **Fig. 6** dargestellt ist, wird ein Addierer **650** verwendet, um den nominalen Wert der Anstiegsgeschwindigkeit von dem nominalen Impedanzwert zu verändern. Dieser Versatzwert kann durch eine Vielzahl verschiedener Techniken intern oder extern festgelegt werden. Der Versatzwert kann zum Beispiel von einer externen Quelle in ein Register geladen werden, wobei der Wert alternativ auch mit Sicherungen implementiert werden kann. Wenn es zum Beispiel beabsichtigt ist, den gleichen Ausgangspuffer für die Abstimmung verschiedener alternativer Impedanzen zu verwenden, und wenn es gewünscht wird, eine im Wesentlichen konstante Anstiegsgeschwindigkeit zu erhalten, so wäre es wünschenswert, den Versatzwert modifizieren zu können.

[0040] Wie dies bereits vorstehend im Text beschrieben worden ist, weist das vorliegende Ausführungsbeispiel die Fähigkeit auf, die Impedanz des Ausgangspuffers anzupassen, während der Ausgangspuffer Datensignale übermittelt. Ein Problem in Bezug auf diese "fliegende" Aktualisierung ist es, dass für den Fall, dass die Aktualisierung zeitlich nahe einer ausgehenden Datensignalflanke erfolgt, dies zum Beispiel die Zeitsteuerung der Flanke verändern könnte. Dies kann zu der Erzeugung von unerwünschten Synchronisationsstörungen der Zeitsteuerung führen. Für einen binär gewichteten Ausgangspuffer mit fünf Zweigen kann zum Beispiel eine signifikante Änderung der Impedanz des Ausgangspuffers in einem einzigen Taktzyklus auftreten. Da sich bei einer linearen Codierung immer nur ein Bit gleichzeitig ändert, wird die Auswirkung dieses Effekts reduziert. Die lineare Codierung sieht allerdings einen geringeren Bereich von Impedanzwerten vor. Wenn eine Regelung der Anstiegsgeschwindigkeit eingesetzt wird, kann es ebenso zu einem weiteren Problem kommen, da sich nach einer großen Impedanzänderung bestimmte Ausgangspufferzweige

aufgrund der Regelung der Anstiegsgeschwindigkeit verhältnismäßig langsam einschalten können. Dies kann in dem vorliegenden Ausführungsbeispiel schnell erfolgen, da das "Abschalten" eines Zweiges bei Puffern mit Source-Abschluss bzw. mit Ursprungsabschluss schnell durchgeführt wird, während das "Einschalten" eines Zweiges für die Implementierung der Regelung der Anstiegsgeschwindigkeit langsam erfolgt. Zum Beispiel können sich die Signalwerte der Impedanzregelung von 310 bei einer einzigen Impedanzaktualisierung von 1000 zu 0111 ändern. Wenn sich das werthöchste Bit zuerst ändert, kann der Puffer unverzüglich drei Zustände ausführen. Wenn sich bei der Ausführung von drei Zuständen in dem Puffer in der Signalübertragungskopplung ein Strom von ungleich Null befand, wechselt die Leitung. Danach wechseln die verbleibenden Impedanzregelungsbits, wobei der Puffer wieder eingeschaltet wird und die Kopplung ungefähr wieder an ihren ursprünglichen Zustand zurückkehrt, allerdings nur langsam. Die Leitung weist somit eine Störung auf. Dies kann zu einer Verschlechterung der Leistung führen, wenn währenddessen der Ausgangspuffer Datensignale übermittelt.

[0041] In Bezug auf das in der Abbildung aus **Fig. 8** dargestellte Ausführungsbeispiel erfolgt die fliegende Aktualisierung durch eine Aktualisierung, während sich der Ausgangspuffer in dem dreifachen Zustand befindet oder die "ausgeschaltete" oder nicht übermittelnde Seite des CMOS-Ausgangspuffers aktualisiert (in dem vorliegenden Ausführungsbeispiel zum Beispiel die NMOS-Vorrichtungen, während das Ausgangssignal hoch ist und die PMOS-Vorrichtungen, während das Ausgangssignal niedrig ist). Für die Implementierung dieses Ansatzes werden in dem vorliegenden Ausführungsbeispiel zum Beispiel an jedem einzelnen Zweig des Ausgangspuffers unter Verwendung des Registers **410** aus **Fig. 2** Signalspeicher eingesetzt. Die in dem Register **410** verwendeten Register werden an jedem Signalausgangsanschluss repliziert; wobei diese Signalspeicher jedoch verhältnismäßig klein sein können.

[0042] In dem Ausführungsbeispiel aus **Fig. 2** werden die Signale RESET und OEn eingesetzt, so dass die "fliegende" Aktualisierung während einem Tri-State bzw. dreifachen Zustand oder einem Zurücksetzen erfolgt. In dem vorliegenden speziellen Ausführungsbeispiel erfolgt die fliegende Aktualisierung nur für die Impedanz des Ausgangspuffers, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist. Für eine Anwendung, bei der die Auflösung der Regelung der Anstiegsgeschwindigkeit verhältnismäßig grob ist, kann die Regelung der Anstiegsgeschwindigkeit zum Beispiel zur Entfernung von Verarbeitungsschwankungen nach dem Zurücksetzen über einige Taktzyklen betrieben werden, und wobei der Wert der Anstiegsgeschwindigkeit danach verriegelt werden kann. Alternativ kann ebenso eine fliegende Aktualisierung der Anstiegsgeschwindigkeit eingesetzt wer-

den, wobei dies jedoch auch Synchronisationsstörungen der Zeitsteuerung erzeugen kann.

[0043] Ein Ausführungsbeispiel eines Verfahrens zur Anpassung einer Impedanz eines Schnittstellenschaltungs-Ausgangspuffers, wie etwa des in der Abbildung aus **Fig. 2** veranschaulichten Ausgangspuffers **320**, kann wie folgt realisiert werden. Wie dies bereits vorstehend im Text beschrieben worden ist, kann die Impedanz eines datenfreien Signalausgangspuffers, wie etwa des Ausgangspuffers **330** aus **Fig. 2**, der mit einer externen Impedanz gekoppelt ist, wie etwa dem Widerstand **340** in der Abbildung aus **Fig. 2**, digital angepasst werden. Die Impedanz eines Schnittstellenschaltungs-Ausgangspuffers, wie etwa des Ausgangspuffers **320** aus **Fig. 2**, kann zumindest teilweise auf der Basis der digital angepassten Impedanz des datenfreien Signalausgangspuffers digital angepasst werden. Ebenso kann die Impedanz des Schnittstellenschaltungs-Ausgangspuffers zumindest teilweise auf der Basis der digitalen Anpassung der Impedanz des datenfreien Signalausgangspuffers digital angepasst werden. Auch dies wurde bereits vorstehend im Text in Bezug auf den Ausgangspuffer **320** beschrieben, wie dies in der Abbildung aus **Fig. 2** dargestellt ist. Ebenso kann die Impedanz des Schnittstellenschaltungs-Ausgangspuffers fliegend digital angepasst werden. In dem in der Abbildung aus **Fig. 2** veranschaulichten Ausführungsbeispiel kann zum Beispiel die Impedanz der nicht übermittelnden Seite des Schnittstellenschaltungs-Ausgangspuffers fliegend digital angepasst werden. Wie dies bereits vorstehend im Text beschrieben worden ist, umfasst die digitale Anpassung der Impedanz des datenfreien Signalausgangspuffers die ungefähre Abstimmung der Impedanz des datenfreien Signalausgangspuffers, wie etwa des Puffers **330** aus **Fig. 2**, mit der Impedanz einer externen Kopplung, wie etwa dem Widerstand **340** aus **Fig. 2**. In dem vorliegenden speziellen Ausführungsbeispiel wird die Impedanz des datenfreien Signalausgangspuffers ebenso digital angepasst, so dass die externe Impedanz an der Source abgeschlossen wird, wobei der Umfang der vorliegenden Erfindung jedoch nicht auf diesen Aspekt beschränkt ist. Ebenso umfasst die digitale Anpassung der Impedanz eines datenfreien Signalausgangspuffers, der mit einer externen Impedanz gekoppelt ist, die digitale Anpassung der Impedanz in binär gewichteten Inkrementen, wobei der Umfang der vorliegenden Erfindung wiederum nicht auf diesen Aspekt beschränkt ist.

[0044] In Bezug auf die vorstehend beschriebenen und veranschaulichten bestimmten Merkmale der vorliegenden Erfindung sind zahlreiche Modifikationen, Substitutionen, Änderungen und Äquivalente möglich, die für den Fachmann auf dem Gebiet offensichtlich sind. Hiermit wird somit festgestellt, dass die anhängigen Ansprüche alle derartigen Modifikationen und Änderungen gemäß dem Umfang der vorliegenden Erfindung umfassen.

## Patentansprüche

1. Integrierte Schaltung, die folgendes umfasst: eine digitale Rückkopplungsschaltung (**300**), die so angeordnet ist, um (a) einen Schnittstellenschaltungs-Ausgangspuffer (**320**) auf der Basis der Impedanz zumindest teilweise gemäß Regelungen der Impedanz eines datenfreien Signalausgangspuffers (**330**) zu regeln, der mit einer externen Impedanz (**340**) gekoppelt ist, und (b) die Anstiegsgeschwindigkeit des genannten Schnittstellenschaltungs-Ausgangspuffers (**320**) zu regeln.

2. Integrierte Schaltung nach Anspruch 1, wobei die genannte digitale Rückkopplungsschaltung (**300**) die Fähigkeit aufweist, die Impedanz des genannten Schnittstellenschaltungs-Ausgangspuffers fliegend zu regeln.

3. Integrierte Schaltung nach Anspruch 2, wobei die Fähigkeit zur fliegenden Regelung der Impedanz des genannten Schnittstellenschaltungs-Ausgangspuffers die Fähigkeit umfasst, die Impedanz der nicht übermittelnden Seite (**450**) des genannten Schnittstellenschaltungs-Ausgangspuffers fliegend zu regeln.

4. Integrierte Schaltung nach Anspruch 2, wobei die genannte digitale Rückkopplungsschaltung zur Regelung der Impedanz des genannten Schnittstellenschaltungs-Ausgangspuffers (**320**) eine digitale Rückkopplungsschaltung umfasst, um die Impedanz des genannten datenfreien Signalausgangspuffers (**330**) ungefähr an die Impedanz der externen Impedanz (**340**) anzupassen.

5. Integrierte Schaltung nach Anspruch 1, wobei die genannte externe Impedanz mindestens einen Widerstand (**340**) umfasst.

6. Integrierte Schaltung nach Anspruch 1, wobei die genannte digitale Rückkopplungsschaltung eine digitale Rückkopplungsschaltung (**140** und **110**) für einen Source-Abschluss umfasst.

7. Integrierte Schaltung nach Anspruch 1, wobei der genannte Schnittstellenschaltungs-Ausgangspuffer (**320**) einen Ausgangspuffer umfasst, wobei mindestens einige der Transistoren in Reihe torgesteuert sind.

8. Integrierte Schaltung nach Anspruch 1, wobei der genannte Schnittstellenschaltungs-Ausgangspuffer eine Verstärkerkonfiguration (**460**, **470**, **480**, **490**, **510**, **520**, **530** und **540**) mit einer Mehrzahl von Zweigen aufweist, wobei die genannten Zweige so bemessen sind, so dass deren Gewichtung zur Regelung der effektiven Impedanz des Ausgangspuffers im Wesentlichen binär ist.

9. Verfahren zur Regelung der Impedanz eines Schnittstellenschaltungs-Ausgangspuffers (**320**), wobei das Verfahren folgendes umfasst:

digitale Regelung der Impedanz eines datenfreien Signalausgangspuffers (**330**), der mit einer externen Impedanz (**340**) gekoppelt ist;

digitale Regelung der Impedanz des Schnittstellenschaltungs-Ausgangspuffers zumindest teilweise auf der Basis der digital geregelten Impedanz des datenfreien Signalausgangspuffers; und

digitale Regelung der Anstiegsgeschwindigkeit des Schnittstellenschaltungs-Ausgangspuffers.

10. Verfahren nach Anspruch 9, wobei die digitale Regelung der Impedanz des Schnittstellenschaltungs-Ausgangspuffers die fliegende digitale Regelung der Impedanz aufweist.

11. Verfahren nach Anspruch 10, wobei die fliegende digitale Regelung der Impedanz des Schnittstellenschaltungs-Ausgangspuffers die fliegende digitale Regelung der Impedanz der nicht übermittelnden Seite (**450**) des Schnittstellenschaltungspuffers umfasst.

12. Verfahren nach Anspruch 9, wobei die Regelung der Impedanz des datenfreien Signalausgangspuffers die Impedanz des datenfreien Signalausgangspuffers ungefähr an die Impedanz der externen Impedanz (**340**) anpasst.

13. Verfahren nach Anspruch 12, wobei die externe Impedanz mindestens einen Widerstand (**340**) umfasst.

14. Verfahren nach Anspruch 9, wobei die digitale Regelung der Impedanz eines datenfreien Signalausgangspuffers, der mit einer externen Impedanz gekoppelt ist, die digitale Regelung der Impedanz des datenfreien Signalausgangspuffers umfasst, so dass für die externe Impedanz ein Source-Abschluss (**110** und **140**) durchgeführt wird.

15. Verfahren nach Anspruch 9, wobei die digitale Regelung der Impedanz eines datenfreien Signalausgangspuffers, der mit einer externen Impedanz gekoppelt ist, die digitale Regelung der Impedanz in binär gewichteten Inkrementen (**450**, **700** und **710**) umfasst.

Es folgen 8 Blatt Zeichnungen

FIG. 1

FIG. 2

320

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7

450

FIG.8