(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5089139号

(P5089139)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

F 1

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>HO1L 29/786</b> | <b>(2006.01)</b> | HO1L 29/78 | 618B |

| <b>HO1L 21/336</b> | <b>(2006.01)</b> | HO1L 29/78 | 616U |

| <b>HO1L 29/417</b> | <b>(2006.01)</b> | HO1L 29/78 | 627C |

| <b>HO1L 21/28</b>  | <b>(2006.01)</b> | HO1L 29/78 | 616V |

|                    |                  | HO1L 29/50 | M    |

請求項の数 7 (全 31 頁) 最終頁に続く

(21) 出願番号

特願2006-304812 (P2006-304812)

(22) 出願日

平成18年11月10日 (2006.11.10)

(65) 公開番号

特開2007-165861 (P2007-165861A)

(43) 公開日

平成19年6月28日 (2007.6.28)

審査請求日

平成21年3月27日 (2009.3.27)

(31) 優先権主張番号

特願2005-329806 (P2005-329806)

(32) 優先日

平成17年11月15日 (2005.11.15)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 秋元 健吾

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 竹口 泰裕

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極を形成し、前記ゲート電極上に、珪素を主成分とするゲート絶縁膜を形成し、前記ゲート絶縁膜上に、A1又はA1合金を主成分とする第1の導電膜を形成し、前記第1の導電膜上に、酸化亜鉛を含み、n型又はp型の導電性を示す第2の導電膜を形成し、前記第1の導電膜をエッチングストッパーとして機能させて、前記第2の導電膜を島状にエッチングし、前記ゲート絶縁膜をエッチングストッパーとして機能させて、前記第1の導電膜を島状にエッチングし、島状の前記第2の導電膜及び前記ゲート絶縁膜上に酸化亜鉛を含む半導体膜を形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、前記第2の導電膜は、ホウ素、アルミニウム、ガリウム、リン、又は砒素を含むことを特徴とする半導体装置の作製方法。

## 【請求項 3】

請求項1または請求項2において、前記ゲート絶縁膜は、酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、窒化珪素膜のう

10

20

ちのいずれかからなる単層膜又は積層膜であることを特徴とする半導体装置の作製方法。

**【請求項 4】**

請求項 1乃至3のいずれか一において、

前記ゲート絶縁膜をエッティングストッパーとして機能させて、前記第1の導電膜を島状に

するエッティングは、ウェットエッティングであることを特徴とする半導体装置の作製方法

。

**【請求項 5】**

請求項 1乃至3のいずれか一において、

前記ゲート絶縁膜をエッティングストッパーとして機能させて、前記第1の導電膜を島状に

するエッティングは、フォトレジスト用の現像液を用いたウェットエッティングであることを

特徴とする半導体装置の作製方法。

10

**【請求項 6】**

請求項 1乃至3のいずれか一において、

前記ゲート絶縁膜をエッティングストッパーとして機能させて、前記第1の導電膜を島状に

するエッティングは、有機アルカリ系水溶液を用いたウェットエッティングであることを特徴

とする半導体装置の作製方法。

**【請求項 7】**

請求項 1乃至3のいずれか一において、

前記ゲート絶縁膜をエッティングストッパーとして機能させて、前記第1の導電膜を島状に

するエッティングは、TMAH（テトラメチルアンモニウムヒドロキシド）を用いたウエットエッティングであることを特徴とする半導体装置の作製方法。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、ZnO (Zinc Oxide 酸化亜鉛) を用いた半導体装置及びその作製方法に関する。

**【背景技術】**

**【0002】**

液晶表示装置やEL (Electroluminescence エレクトロルミネッセンス) 表示装置の表示パネルに用いられる半導体装置、例えば TFT (Thin Film Transistor 薄膜トランジスタ) の半導体部分は、通常、a-Si (アモルファスシリコン) やpoly-Si (多結晶シリコン) で形成されている。

30

**【0003】**

Si (シリコン) 材料は禁制帯幅 (バンドギャップ) が1.1eVであり、可視光を吸収する。この光の照射によってSi中に電子及び正孔 (キャリア) が形成される。Si膜をTFTのチャネル形成領域に用いると、オフ状態にあるときでも、光の照射によってチャネル形成領域にキャリアが生成され、ソース領域とドレイン領域との間に電流が流れれる。オフ状態のときに流れる電流は「オフリーク電流」と呼ばれ、この値が大きいと、表示パネルが正常に動作しない。このため、光がSi膜に照射されないように遮光膜を形成することが行われている。しかし、遮光膜を形成するには、堆積工程やフォトリソグラフィー工程、エッティング工程が必要になるため、工程が煩雑になる。

40

**【0004】**

このような問題を解決するため、バンドギャップが3.4eVとSiよりも大きい半導体である酸化亜鉛 (ZnO) を用いた透明トランジスタが注目されている。このような透明トランジスタでは、バンドギャップが可視光帯域の光エネルギーよりも大きく、可視光を吸収しない。したがって光の照射を受けてもオフリーク電流は増大しないという利点を有している。

**【0005】**

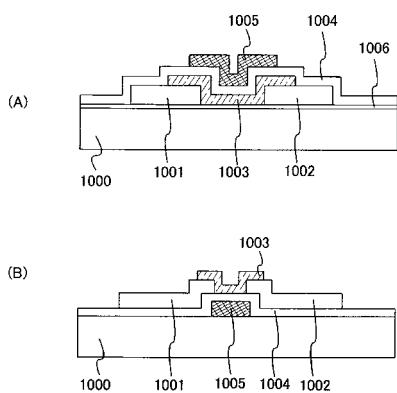

ZnOをチャネル形成領域に用いた半導体装置は、例えば、特許文献1に開示されている。図7(A)を参照しながら、ZnOを用いた半導体装置の構成を説明する。

50

**【0006】**

図7(A)の半導体装置は、ガラス基板等の絶縁性基板1000上に形成されたソース電極1001およびドレイン電極1002と、ソース電極1001及びドレイン電極1002に接触するように配置されたZnO層1003と、ZnO層1003に積層されたゲート絶縁層1004、ゲート電極1005とを備えている。

**【0007】**

ソース電極1001及びドレイン電極1002にはII族元素(B(ホウ素)、A1(アルミニウム)、Ga(ガリウム)、In(インジウム)、Tl(タリウム))、VII族元素(F(フッ素)、Cl(塩素)、Br(臭素)、I(ヨウ素))、I族元素(Li(リチウム)、Na(ナトリウム)、K(カリウム)、Rb(ルビジウム)、Cs(セシウム))、V族元素(N(窒素)、P(リン)、As(砒素)、Sb(アンチモン)、Bi(ビスマス))のいずれかをドープした導電性ZnOが用いられている。

10

【特許文献1】特開2000-150900号公報

**【発明の開示】****【発明が解決しようとする課題】****【0008】**

本発明者の検討によると、図7(A)に示されるトップゲート型半導体装置のソース電極1001及びドレイン電極1002を形成する際のエッチングによって基板1000がエッチングされる場合があることがわかった。基板1000上に酸化珪素膜や酸化窒化珪素膜からなる下地膜1006を形成した場合でも、この下地膜がエッチングされて基板1000の表面が露出する場合があることがわかった。また図7(B)に示されるボトムゲート型半導体装置においては、ソース電極1001及びドレイン電極1002を形成する際のエッチングによって酸化珪素膜や酸化窒化珪素膜からなるゲート絶縁膜1004がエッチングされることがわかった。

20

**【0009】**

トップゲート型半導体装置において、ガラス基板1000や酸化珪素膜や酸化窒化珪素膜からなる下地膜1006がエッチングされると、基板1000からナトリウムなどの不純物が半導体膜1003に拡散し、特性を劣化させてしまう。

**【0010】**

ボトムゲート型半導体装置(図7(B))において、ソース電極1001及びドレイン電極1002の形成の際のエッチングによりゲート絶縁膜1004がエッチングされてしまうと、特性が安定せず、不良の原因となる。

30

**【0011】**

本発明は、上記事情に鑑みてなされたものであり、その目的とするところは、チャネル形成領域にZnO半導体膜を用い、ソース電極及びドレイン電極にn型又はp型の不純物を添加したZnO膜を用いたときでも欠陥や不良が生じない半導体装置及びその作製方法を提供することにある。

**【課題を解決するための手段】****【0012】**

本発明の半導体装置は、酸化珪素膜又は酸化窒化珪素膜上のAl膜又はAl合金膜と、前記Al膜又はAl合金膜上のn型又はp型の不純物が添加されたZnO膜とを有することを特徴とする。なお、本明細書においては、酸化珪素膜、酸化窒化珪素膜、Al膜、Al合金膜、ZnO膜はそれぞれ酸化珪素を含む膜、酸化窒化珪素を含む膜、Alを含む膜、Al合金を含む膜、ZnOを含む膜を意味するものとする。

40

**【0013】**

本発明の半導体装置は、ゲート電極上の酸化珪素膜又は酸化窒化珪素膜からなるゲート絶縁膜と、前記ゲート絶縁膜上のAl膜又はAl合金膜と、前記Al膜又はAl合金膜上のn型又はp型の不純物が添加されたZnO膜と、前記n型又はp型の不純物が添加されたZnO膜及び前記ゲート絶縁膜上のZnO半導体膜とを有することを特徴とする。

**【0014】**

本発明の半導体装置は、酸化珪素膜又は酸化窒化珪素膜上のA1膜又はA1合金膜と、前記A1膜又はA1合金膜上のn型又はp型の不純物が添加されたZnO膜と、前記酸化珪素膜又は酸化窒化珪素膜上及び前記n型又はp型の不純物が添加されたZnO膜上のZnO半導体膜と、前記ZnO半導体膜上のゲート絶縁膜と、前記ゲート絶縁膜上のゲート電極とを有することを特徴とする。

## 【0015】

本発明の半導体装置の作製方法は、酸化珪素膜又は酸化窒化珪素膜を形成し、前記酸化珪素膜又は酸化窒化珪素膜上にA1膜又はA1合金膜を形成し、前記A1膜又はA1合金膜上にn型又はp型の不純物が添加されたZnO膜を形成し、前記n型又はp型の不純物が添加されたZnO膜を第1のエッティングによって島状にし、前記A1膜又はA1合金膜を第2のエッティングによって島状にすることを特徴とする。 10

## 【0016】

本発明の半導体装置の作製方法は、前記第2のエッティングをした後、前記n型又はp型の不純物が添加されたZnO膜及び前記酸化珪素膜又は酸化窒化珪素膜上にZnO半導体膜を形成することを特徴とする。

## 【0017】

ボトムゲート型の半導体装置の場合にはゲート電極を形成した後、前記ゲート電極上に前記酸化珪素膜又は酸化窒化珪素膜からなるゲート絶縁膜を形成することを特徴とする。

## 【0018】

トップゲート型の半導体装置の場合には前記ZnO半導体膜を形成した後、ゲート絶縁膜を形成し、ゲート電極を形成することを特徴とする。 20

## 【0019】

本発明の第1のエッティングはウェットエッティングでもよい。

## 【0020】

本発明の第1のエッティングはバッファードフッ酸を用いたウェットエッティングでもよい。

## 【0021】

本発明の第1のエッティングはドライエッティングでもよい。

## 【0022】

本発明の第1のエッティングはCH<sub>4</sub>(メタン)ガスを用いたドライエッティングでもよい。 30

## 【0023】

本発明の第2のエッティングはウェットエッティングでもよい。

## 【0024】

本発明の第2のエッティングはフォトレジスト用の現像液を用いたウェットエッティングでもよい。

## 【0025】

本発明の第2のエッティングは有機アルカリ系水溶液を用いたウェットエッティングでもよい。 40

## 【0026】

本発明の第2のエッティングはTMAH(tetramethylammonium hydroxide、テトラメチルアンモニウムヒドロキシド)を用いたウェットエッティングでもよい。

## 【0027】

また本発明の半導体装置は、ゲート電極上のゲート絶縁膜と、前記ゲート絶縁膜上の金属材料を有する第1の膜と、前記第1の膜上のn型又はp型の不純物が添加された透明半導体材料を有する第2の膜と、前記第2の膜上及び前記ゲート絶縁膜上の透明半導体を有する第3の膜とを有することを特徴とする。

## 【0028】

10

20

30

40

50

また本発明の半導体装置は、絶縁膜上の金属材料を有する第1の膜と、前記第1の膜上のn型又はp型の不純物が添加された透明半導体材料を有する第2の膜と、前記第1の膜上及び前記第2の膜上の透明半導体材料を有する第3の半導体膜と、前記第3の膜上のゲート絶縁膜と、前記ゲート絶縁膜上のゲート電極とを有することを特徴とする。

## 【0029】

また本発明の半導体装置の作製方法は、絶縁膜を形成し、前記絶縁膜上に金属材料を有する第1の膜を形成し、前記第1の膜上にn型又はp型の不純物が添加された透明半導体材料を有する第2の膜を形成し、前記第2の膜を第1のエッティングによって島状にし、前記第1の膜を第2のエッティングによって島状にすることを特徴とする。

## 【0030】

また本発明の半導体装置の作製方法は、ゲート電極を形成し、前記ゲート電極上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に金属材料を有する第1の膜を形成し、前記1の膜上にn型又はp型の不純物が添加された透明半導体材料を有する第2の膜を形成し、前記第2の膜を第1のエッティングによって島状にし、前記第1の膜を第2のエッティングによって島状にすることを特徴とする。

## 【発明の効果】

## 【0031】

トップゲート型半導体装置においては、ガラス基板や酸化珪素膜又は酸化窒化珪素膜からなる下地膜がエッティングされず、基板からナトリウムなどの不純物が半導体膜に拡散し、特性を劣化させることがない。

## 【0032】

ボトムゲート型半導体装置においては、ゲート絶縁膜がエッティングされず、特性が不安定になることがない。

## 【0033】

ソース電極及びドレイン電極の一部にA1を用いているので配線の低抵抗化を図ることができる。

## 【発明を実施するための最良の形態】

## 【0034】

以下、発明を実施するための最良の形態について図面を参照しながら説明する。但し、本発明は多くの異なる様様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は本実施形態の記載内容に限定して解釈されるものではない。

## 【0035】

## (実施形態1)

ここではボトムゲート型の半導体装置について説明する。

## 【0036】

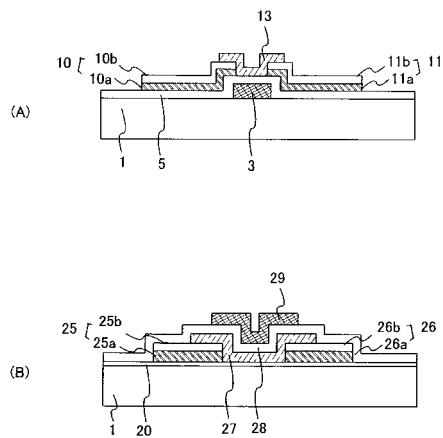

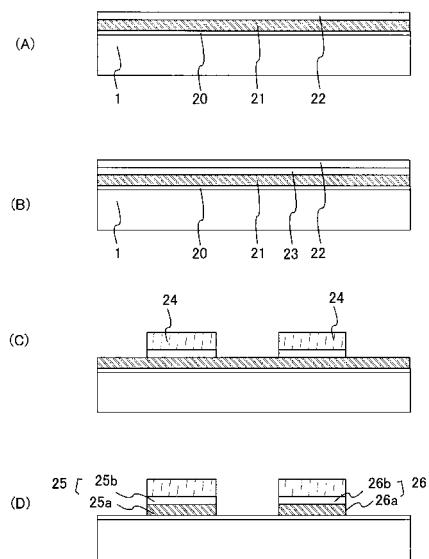

図1(A)は、本発明の実施形態の一例を示した断面図である。図1(A)において、1は基板、3はゲート電極、5はゲート絶縁膜、10はソース電極、10aは第1の導電膜、10bは第2の導電膜、11はドレイン電極、11aは第1の導電膜、11bは第2の導電膜、13は半導体膜を示している。半導体膜13上にパッシベーション用の絶縁膜や平坦化用の絶縁膜を形成してもよい。

## 【0037】

基板1上にゲート電極3が形成され、ゲート電極3上にゲート絶縁膜5が形成され、ゲート絶縁膜5上にソース電極10、ドレイン電極11が形成されている。ソース電極10は第1の導電膜10a及び第2の導電膜10bの積層膜によって形成され、ドレイン電極11は第1の導電膜11a及び第2の導電膜11bの積層膜によって形成されている。第1の導電膜10aと第2の導電膜10bとの間や、第1の導電膜11aと第2の導電膜11bとの間に第3の導電膜が形成されていてもよい。ソース電極10とドレイン電極11はそれぞれゲート絶縁膜5を介してゲート電極3と一部重なるように形成されていてもよい。ゲート絶縁膜5上であってソース電極10とドレイン電極11上に半導体膜13が

10

20

30

40

50

形成される構成になっている。

#### 【0038】

以下、各構成について説明する。

##### (1) 基板

ガラス基板、アルミナなど絶縁物質で形成される基板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板等を用いることができる。基板1にプラスチック基板を用いる場合、P C ( P o l y c a r b o n a t e ポリカーボネート)、P E S ( P o l y e t h e r s u l f o n e ポリエーテルサルファン)、P E T ( p o l y e t h y l e n e t e r e p h t h a l a t e ポリエチレンテレフタレート)もしくはP E N ( P o l y e t h y l e n e n a p h t h a l a t e ポリエチレンナフタレート)等を用いることができる。プラスチック基板の場合は、表面にガスバリア層として無機層または有機層を設けてもよい。プラスチック基板の作製時のゴミ等によって基板に突起が発生している場合は、C M Pなどを用いて基板を研磨し、基板の表面を平坦化させた後に使用してもよい。基板1の上には酸化珪素(S i O x )、窒化珪素(S i N x )、酸化窒化珪素(S i O x N y )(x > y)、窒化酸化珪素(S i N x O y )(x > y)など、基板側から不純物などの拡散を防止するための絶縁膜を形成しておいてもよい。10

#### 【0039】

##### (2) ゲート電極

A l (アルミニウム)膜、W (タンゲステン)膜、M o (モリブデン)膜、T a (タンタル)膜、C u (銅)膜、T i (チタン)膜、または前記元素を主成分とする合金材料(例えばA l 合金膜、M o W (モリブデンタンゲステン)合金膜)などを用いることができる。P (リン)等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。またゲート電極3は単層であっても2層以上積層させたものであってもよい。20

#### 【0040】

##### (3) ゲート絶縁膜

ゲート絶縁膜5は珪素を主成分とする絶縁膜、例えば酸化珪素膜、酸化窒化珪素膜で形成される。また単層であっても積層膜であってもよい。

#### 【0041】

##### (4) ソース電極、ドレイン電極

ソース電極10は第1の導電膜10a及び第2の導電膜10bの積層膜によって形成され、ドレイン電極11は第1の導電膜11a及び第2の導電膜11bの積層膜によって形成されている。30

#### 【0042】

第1の導電膜としてはA l 膜、A l N i (アルミニウムニッケル)膜やA l N d (アルミニウムネオジム)膜等のA l 合金膜を用いることができる。第2の導電膜としてはB (ホウ素)、A l (アルミニウム)、G a (ガリウム)、P (リン)、A s (砒素)などのp型又はn型の不純物が添加されたZ n O (酸化亜鉛)を用いることができる。第1の導電膜と第2の導電膜の間に第3の導電膜としてT i 膜などの金属膜を設けてもよい。

#### 【0043】

##### (5) 半導体膜

半導体膜としてはZ n O 膜を用いる。半導体膜と接するソース電極、ドレイン電極がp型又はn型の不純物が添加されたZ n O 膜を有しているので半導体膜と容易に電気的に接続させることができる。40

#### 【0044】

##### (6) 絶縁膜

図示しないが、半導体膜13上にはパッシベーション膜、平坦化膜などの絶縁膜を形成してもよい。酸化珪素(S i O x )、窒化珪素(S i N x )、酸化窒化珪素(S i O x N y )(x > y)、窒化酸化珪素(S i N x O y )(x > y)、S O G (s p i n - o n - g l a s s )膜、アクリルなどの有機樹脂膜またはこれらの積層膜を用いることができ50

る。

**【0045】**

上記のようなボトムゲート型半導体装置はその作製時にゲート絶縁膜がエッティングされず、特性が不安定になることがない。ソース電極及びドレイン電極の一部にA1を用いているため、配線の低抵抗化を図ることができる。

**【0046】**

(実施形態2)

ここではトップゲート型の半導体装置について説明する。

**【0047】**

図1(B)は、本発明の実施形態の一例を示した断面図である。図1(B)において、1は基板、20は絶縁膜、25はソース電極、25aは第1の導電膜、25bは第2の導電膜、26はドレイン電極、26aは第1の導電膜、26bは第2の導電膜、27は半導体膜、28はゲート絶縁膜、29はゲート電極を示している。ゲート電極上にパッシベーション用の絶縁膜や平坦化用の絶縁膜を形成してもよい。

10

**【0048】**

基板1上に絶縁膜20が形成され、絶縁膜20上にソース電極25、ドレイン電極26が形成されている。ソース電極25は第1の導電膜25a及び第2の導電膜25bの積層膜によって形成され、ドレイン電極26は第1の導電膜26a及び第2の導電膜26bの積層膜によって形成されている。第1の導電膜25aと第2の導電膜25bとの間、第1の導電膜26aと第2の導電膜26bとの間に第3の導電膜が形成されていてもよい。絶縁膜20上であって、ソース電極25とドレイン電極26上に半導体膜27が形成され、半導体膜27上にゲート絶縁膜28が形成され、ゲート絶縁膜28上にゲート電極29が形成されている。ゲート電極29はゲート絶縁膜28、半導体膜27を介してソース電極25とドレイン電極26のそれぞれと一部重なるように形成してもよい。

20

**【0049】**

以下、各構成について説明する。

**【0050】**

基板、ソース電極、ドレイン電極、半導体膜、ゲート電極は実施形態1において説明したもの用いることができる。

(1) 基板上の絶縁膜

30

基板1の上には基板側から不純物などの拡散を防止するための絶縁膜20として酸化珪素膜や酸化窒化珪素膜を形成する。また単層であっても積層膜であってもよい。

**【0051】**

(2) ゲート絶縁膜

ゲート絶縁膜28は珪素を主成分とする絶縁膜、例えば酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、窒化珪素膜で形成される。また単層であっても積層膜であってもよい。

。

**【0052】**

(3) ゲート電極上の絶縁膜

図示しないが、ゲート電極29上にはパッシベーション膜、平坦化膜などの層間絶縁膜を形成してもよい。SiO<sub>x</sub>膜、SiN<sub>x</sub>膜、SiON膜、SiNO膜、SOG(spin-on-glass)膜、アクリルなどの有機樹脂膜またはこれらの積層膜を用いることができる。

40

**【0053】**

上記のようなトップゲート型半導体装置においては、その作製時に基板や酸化珪素膜又は酸化窒化珪素膜からなる下地膜がエッティングされず、基板からナトリウムなどの不純物が半導体膜に拡散し、特性を劣化させることがない。ソース電極及びドレイン電極の一部にA1を用いているため、配線の低抵抗化を図ることができる。

**【0054】**

(実施形態3)

50

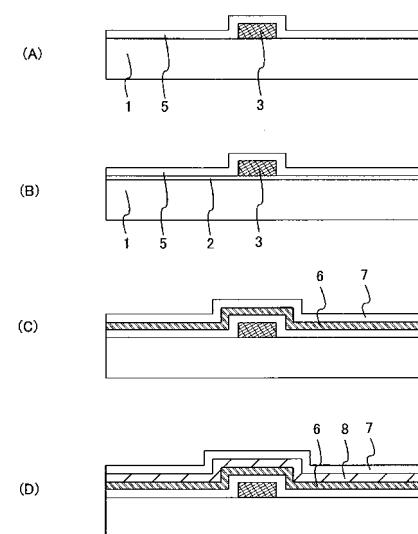

ここではボトムゲート型の半導体装置において、ゲート電極上にゲート絶縁膜として酸化珪素膜又は酸化窒化珪素膜を形成し、第1の導電膜としてAl膜又はAl合金膜を形成し、第2の導電膜としてn型又はp型の不純物が添加されたZnO膜を形成した後に、前記第2の導電膜を第1のエッティングによって島状にし、前記第1の導電膜を第2のエッティングによって島状にしてソース電極及びドレイン電極を形成し、ZnO半導体膜を形成する方法について説明する。

#### 【0055】

図2(A)に示すように、基板1上にゲート電極3を10nm～200nmの厚さで形成する。基板1としては実施形態1に示したもの用いる。ここではガラス基板を用いる。

10

#### 【0056】

基板1の上には酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiNx)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)など、基板側から不純物などの拡散を防止するための絶縁膜2をCVD法やスパッタ法により10nm～200nmの厚さで形成しておいてもよい(図2(B))。

#### 【0057】

絶縁膜2は基板1の表面を高密度プラズマによって処理することによって形成してもよい。高密度プラズマは例えば2.45GHzのマイクロ波を用いることによって生成され、電子密度が $1 \times 10^{11} \sim 1 \times 10^{13} / \text{cm}^3$ かつ電子温度が2eV以下のものであればよい。このような高密度プラズマは活性種の運動エネルギーが低く、従来のプラズマ処理と比較してプラズマによるダメージが少なく、欠陥の少ない膜を形成することができる。

20

#### 【0058】

窒化性雰囲気、例えば窒素と希ガスを含む雰囲気下、または窒素と水素と希ガスを含む雰囲気下、またはアンモニアと希ガスを含む雰囲気下において、上記高密度プラズマ処理を行うことによって基板1の表面を窒化することができる。基板1としてガラス基板などを用いた場合、上記高密度プラズマによる窒化処理を行った場合、基板1表面に形成される窒化膜は窒化珪素が主成分である絶縁膜2を形成することができる。この窒化膜の上に酸化珪素膜または酸化窒化珪素膜をプラズマCVD法により形成して複数層よりなる絶縁膜2としてもよい。

30

#### 【0059】

また絶縁膜2の表面に同様に高密度プラズマによる窒化処理を行うことによって、その表面に窒化膜を形成することができる。

#### 【0060】

高密度プラズマによる窒化処理によって形成された窒化膜は基板1からの不純物の拡散を抑制することができる。

#### 【0061】

ゲート電極3としては実施形態1に示したもの用いることができる。ここではAlNd(アルミニウムネオジム)膜を、AlNdターゲットを用いてスパッタ法により成膜し、島状に加工する。島状に加工するにはフォトリソグラフィー法を用い、ドライエッティングやウェットエッティング方法を用いる。

40

#### 【0062】

ゲート電極3の表面及び、基板1又は絶縁膜2の表面を洗浄した後、ゲート電極3上にゲート絶縁膜5を、公知のCVD法又はスパッタ法を用いて10nm～200nmの厚さで形成する(図2(A)、(B))。これら表面洗浄工程とゲート絶縁膜5の形成工程とは、大気にふれさせずに連続的に行ってもよい。ゲート電極3にAl膜を用いた場合にはゲート絶縁膜5を高温で形成すると、ヒロックが発生するため、500以下、好ましくは350以下の低温で形成することが望ましい。

#### 【0063】

ゲート絶縁膜5は実施形態1に示したもの用いることができる。ここでは酸化珪素

50

膜を形成する。なお、以下の図面において絶縁膜2は省略する。

#### 【0064】

ゲート絶縁膜5上にソース電極及びドレイン電極用の第1の導電膜6を膜厚10nm～200nmで形成する。第1の導電膜6としては実施形態1に示したもの用いることができる。ここではAlNi（アルミニウムニッケル）膜又はAlNd膜を用いる。第1の導電膜6はスパッタ法により形成でき、AlNiターゲット又はAlNdターゲットを用いてスパッタ法により形成することができる。またゲート絶縁膜5を形成した後、大気にさらすことなく、連続して第1の導電膜6を形成してもよい。

#### 【0065】

第1の導電膜6上に第2の導電膜7を膜厚10nm～200nmで形成する（図2（C））。第2の導電膜7としては実施形態1に示したもの用いることができる。ここではAl又はGaの不純物が添加されたZnO（酸化亜鉛）を用いる。これによって後に形成される半導体層であるZnO膜と容易にオーミック接続させることができる。第2の導電膜7はスパッタ法等により形成できる。例えばAlやGaを添加するには、AlやGaが1～10重量%添加されたZnOターゲットを用いてスパッタする方法や、ZnOターゲットにAlやGaのチップを載せて200～300でスパッタする方法によって形成することができる。

#### 【0066】

第1の導電膜6を形成した後、大気にさらすことなく、連続して第2の導電膜7を形成してもよい。したがってゲート絶縁膜5から第2の導電膜7までは大気にさらすことなく、連続形成してもよい。

#### 【0067】

第1の導電膜6と第2の導電膜7の間に第3の導電膜8を膜厚10nm～200nmで設けてもよい（図2（D））。作製工程における熱処理温度によって、第1の導電膜6と第2の導電膜7との間のコンタクト抵抗が上昇する場合がある。しかし、第3の導電膜8を形成することによって第1の導電膜6と第2の導電膜7との間のコンタクト抵抗を低くすることができる。第3の導電膜8はTi膜などの金属膜を用いることができ、スパッタ法等により形成することができる。

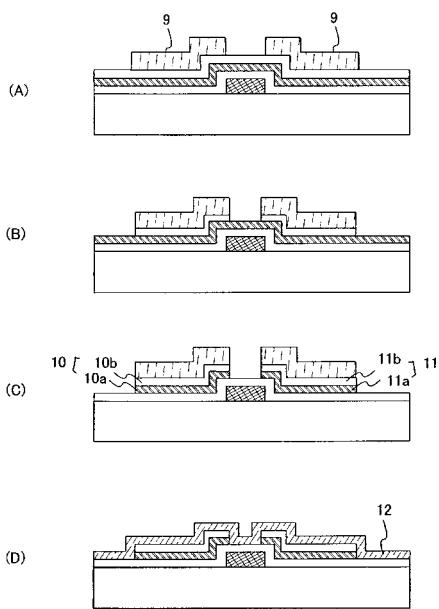

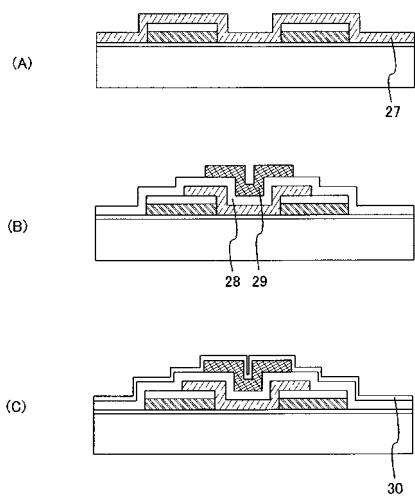

#### 【0068】

第2の導電膜7上にレジストマスク9を形成して第2の導電膜7をエッチングする（図3（A）、（B））。ウェットエッチング方法を用いる場合には、バッファードフッ酸（HF（フッ化水素酸）とNH<sub>4</sub>F（フッ化アンモニウム）とを混合したもの）、例えばHF:NH<sub>4</sub>F（重量比）=1:100～1:10の溶液を用いることができる。

#### 【0069】

ドライエッティング方法を用いる場合には、CH<sub>4</sub>ガスによる異方性プラズマエッティングを用いることができる。

#### 【0070】

第2の導電膜7の下には、第1の導電膜6が形成されている。したがって第2の導電膜7をエッティングする際に、第1の導電膜6がエッティングストッパーとなる。これによりゲート絶縁膜5をエッティングしてダメージを与えることなく、ソース電極及びドレイン電極を形成することができる。

#### 【0071】

また第2の導電膜7をエッティングするときに第1の導電膜6の一部をエッティングしてもよい。ただし第1の導電膜6をすべてエッティングしてしまうと、ゲート絶縁膜にダメージを与えることになるため注意を要することは言うまでもない。

#### 【0072】

次にレジストマスク9を用いて第1の導電膜6をエッティングしてソース電極10及びドレイン電極11を形成する（図3（C））。本発明ではフォトレジスト用の現像液、TMAH（tetramethylammonium hydroxide、テトラメチルアンモニウムヒドロキシド）に代表される有機アルカリ系水溶液を用いて第1の導電膜

10

20

30

40

50

6をエッティングする。

【0073】

例えば第1の導電膜6にAlNi膜を用い、エッティング液にTMAHを用いた場合、エッティング速度は30で約300nm/minである。一方、上述した材料を用いた第2の導電膜7やゲート絶縁膜5はTMAHによってエッティングされることはない。これによりゲート絶縁膜5にダメージを与えることなく、ソース電極10及びドレイン電極11を形成することができる。また島状の第2の導電膜10b、11bのサイズを縮小することもない。本発明では第1の導電膜6用に特殊なエッティング液を用いずにレジストマスクを形成する際の現像液を用いてエッティングすることができる。したがって低コスト化、高効率化につながる。

10

【0074】

ソース電極10及びドレイン電極11を形成した後、レジストマスク9を除去する。

【0075】

ソース電極10、ドレイン電極11及びゲート絶縁膜5上に半導体膜12としてZnO膜をスパッタ法にて膜厚20nm～200nmで形成する(図3(D))。例えばZnOターゲットを用い、酸素／アルゴンの流量比を30～20にし、200～300でスパッタすることによって形成できる。

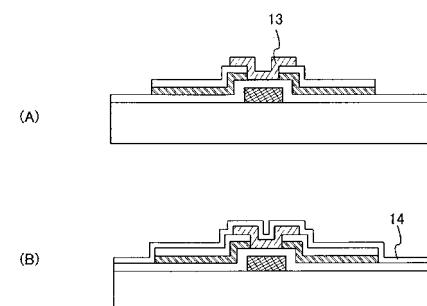

【0076】

半導体膜12を、フォトリソグラフィー法を用いてエッティングして島状の半導体膜13にする(図4(A))。エッティングにはバッファードフッ酸を用いたウエットエッティング方法やCH<sub>4</sub>ガスを用いた異方性ドライエッティング法を用いることができる。

20

【0077】

半導体膜12と第2の導電膜10b、11bとはZnOを用いている点で共通しており、十分なエッティング選択比を得ることは困難である。しかし第2の導電膜7は半導体膜12と接する部分に形成されればよいため、半導体膜12と接しない部分、例えば配線部分については第2の導電膜7がエッティングされてもよい。上記したエッティング方法では、第2の導電膜10b、11bがエッティングされても第1の導電膜10a、11aはエッティングされることはない。したがって第1の導電膜10a、11aが配線となり、半導体装置との電気的接続は確保される。

【0078】

30

半導体膜13上に絶縁膜14をCVD法やスパッタ法により膜厚50nm～1μmで形成する(図4(B))。絶縁膜14には珪素を主成分とする絶縁膜を用いることができる。珪素を含む絶縁膜の上に有機樹脂膜等を積層してもよい。絶縁膜14は平坦膜やパッセーペーション膜として機能する。ソース電極10、ドレイン電極11にはAlが含まれているため絶縁膜14を高温で形成すると、ヒロックが発生するため、500以下、好ましくは350以下の低温で形成することが望ましい。

【0079】

絶縁膜14にコンタクトホール形成して、ゲート電極3、ソース電極10、ドレイン電極11とコンタクトする導電膜を必要に応じて設ける。

【0080】

40

このように本発明によって、ゲート絶縁膜にダメージを与えることなく、半導体装置を形成することが可能である。第1の導電膜としてAlNi膜等のAl合金膜を用いているので、配線の低抵抗化を図ることができる。

【0081】

(実施形態4)

ここではトップゲート型の半導体装置において、酸化珪素膜又は酸化窒化珪素膜上に第1の導電膜としてAl膜又はAl合金膜を形成し、第2の導電膜としてn型又はp型の不純物が添加されたZnO膜を形成した後に、第2の導電膜を第1のエッティングによって島状にし、第1の導電膜を第2のエッティングによって島状にしてソース電極及びドレイン電極を形成し、ZnO半導体膜を形成し、ゲート絶縁膜を形成し、ゲート電極を形成する

50

方法について説明する。なお本実施形態に用いる材料、作製に用いる方法は実施形態1～3に記載したもの用いることができることはいうまでもない。

#### 【0082】

まず図5(A)に示すように、基板1上に絶縁膜20として酸化珪素膜(SiO<sub>x</sub>)をCVD法やスパッタ法により10nm～200nmの厚さで形成する。絶縁膜20は基板1側から不純物などの拡散を防止する。

#### 【0083】

絶縁膜20上にソース電極及びドレイン電極用の第1の導電膜21をスパッタ法又は蒸着法により10nm～200nm形成する。第1の導電膜21としては実施形態1に示したもの、AlNi(アルミニウムニッケル)膜等のAl合金膜を用いることができる。また絶縁膜20を形成した後、大気にさらすことなく、連続して第1の導電膜21を形成してもよい。

10

#### 【0084】

第1の導電膜21上に第2の導電膜22をスパッタ法により膜厚10nm～200nmで形成する(図5(A))。第2の導電膜22としてはB(ホウ素)、Al(アルミニウム)、Ga(ガリウム)、P(リン)、As(砒素)などのp型又はn型の不純物が添加されたZnO(酸化亜鉛)を用いることができる。また第1の導電膜21を形成した後、大気にさらすことなく、連続して第2の導電膜22を形成してもよい。したがって絶縁膜20から第2の導電膜22までは大気にさらすことなく、連続形成してもよい。

#### 【0085】

20

第1の導電膜21と第2の導電膜22との間のコンタクト抵抗を低くするために、第1の導電膜21と第2の導電膜22の間に、第3の導電膜23としてTi膜などの金属膜をスパッタ法により10nm～200nm設けてもよい(図5(B))。

#### 【0086】

第2の導電膜22上にレジストマスク24を形成して第2の導電膜22をエッチングする(図5(C))。エッチング方法はバッファードフッ酸を用いたウェットエッチング又はCH<sub>4</sub>ガスを用いたドライエッチングを用いることができる。

#### 【0087】

第2の導電膜22の下には、第1の導電膜21が形成されている。したがって第2の導電膜22をエッチングする際に、第1の導電膜21がエッチングストッパーとなる。これにより、絶縁膜20をエッチングして基板1を露出させることなく、ソース電極及びドレイン電極を形成することができる。

30

#### 【0088】

また第2の導電膜22をエッチングするときに第1の導電膜21の一部をエッチングしてもよい。ただし第1の導電膜21のすべてエッチングしてしまうと、絶縁膜20をエッチングして基板1が露出して基板1に含まれる不純物が拡散する可能性があるため注意を要する。

#### 【0089】

第1の導電膜21をエッチングしてソース電極25及びドレイン電極26を形成する(図5(D))。エッチング方法としてはフォトレジスト用の現像液、TMAHを用いたウェットエッチングを用いる。これにより絶縁膜20をエッチングすることなく、ソース電極25及びドレイン電極26を形成することができる。またZnO膜はTMAHによってエッチングされないため、島状の第2の導電膜25b、26bのサイズを縮小することもない。本発明では第1の導電膜21用に特殊なエッチング液を用いずにレジストマスクを形成する際の現像液を用いてエッチングすることができる。したがって低コスト化、高効率化につながる。

40

#### 【0090】

ソース電極25及びドレイン電極26を形成した後、レジストマスク24を除去する。

#### 【0091】

50

ソース電極 25、ドレイン電極 26、絶縁膜 20 上に半導体膜 27 として ZnO 膜をスパッタ法にて膜厚 20 nm ~ 200 nm で形成する(図 6(A))。

#### 【0092】

半導体膜 27 を、フォトリソグラフィー法を用いてエッチングして島状の半導体膜 27 にする。エッチングにはバッファードフッ酸を用いたウェットエッチング方法や CH<sub>4</sub> ガスを用いたドライエッチング法を用いることができる。

#### 【0093】

半導体膜 27 と第 2 の導電膜 25b、26b とは ZnO を用いている点で共通しており、十分なエッチング選択比を得ることは困難である。しかし第 2 の導電膜 22 はソース電極及びドレイン電極部に形成されなければよいため、半導体膜 27 と接しない部分、特に配線部分については第 2 の導電膜がエッチングされてもよいことは実施形態 3 と同様である。

10

#### 【0094】

半導体膜 27 上にゲート絶縁膜 28 を、CVD 法やスパッタ法を用いて 10 nm ~ 200 nm の厚さで形成する(図 6(B))。半導体膜 27 に上記実施形態で記載した高密度プラズマ処理を行ってゲート絶縁膜を形成してもよい。例えば窒化性雰囲気、例えば窒素と希ガスを含む雰囲気下、または窒素と水素と希ガスを含む雰囲気下、またはアンモニアと希ガスを含む雰囲気下において、上記高密度プラズマ処理を行うことによって半導体膜 27 の表面を窒化することができる。

#### 【0095】

20

ゲート絶縁膜 28 は珪素を主成分とする絶縁膜、例えば酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜などで形成してもよい。また単層であっても積層膜であってもよい。

#### 【0096】

ゲート絶縁膜 28 上にゲート電極 29 を形成する(図 6(B))。ゲート電極 29 としては上記実施形態に示した材料を用いることができ、単層であっても 2 層以上積層させたものであってもよい。膜形成方法には公知の CVD 法、スパッタ法、蒸着法等を用いることができる。また島状に加工するにはフォトリソグラフィー法を用い、ドライエッチングやウェットエッチング方法を用いることができる。

#### 【0097】

30

ゲート電極 29 及びゲート絶縁膜 28 上に絶縁膜 30 を CVD 法やスパッタ法により 50 nm ~ 1 μm 形成する(図 6(C))。絶縁膜 30 は珪素を含む絶縁膜を用いることができる。珪素を含む絶縁膜の上に有機樹脂膜等を積層してもよい。絶縁膜 30 は平坦化膜やパッシベーション膜として機能する。ソース電極 25、ドレイン電極 26 は Al を含んでいるためゲート絶縁膜 28、ゲート電極 29、絶縁膜 30 を高温で形成すると、ヒロツクが発生することがあるため、500 以下、好ましくは 350 以下の低温で形成することが望ましい。

#### 【0098】

このように本発明によって、基板 1 が露出することによる不純物の拡散を防止できる。第 1 の導電膜として AlNi 膜等の Al 合金膜を用いているので、配線の低抵抗化を図ることができる。

40

#### 【0099】

##### (実施形態 5)

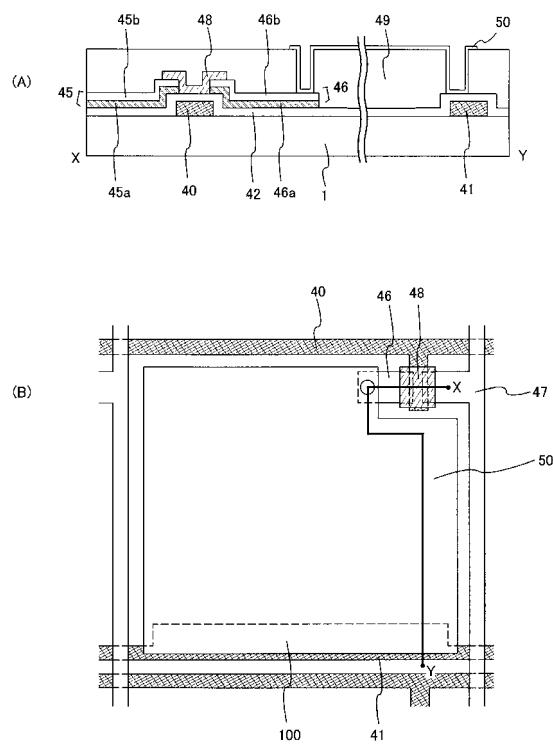

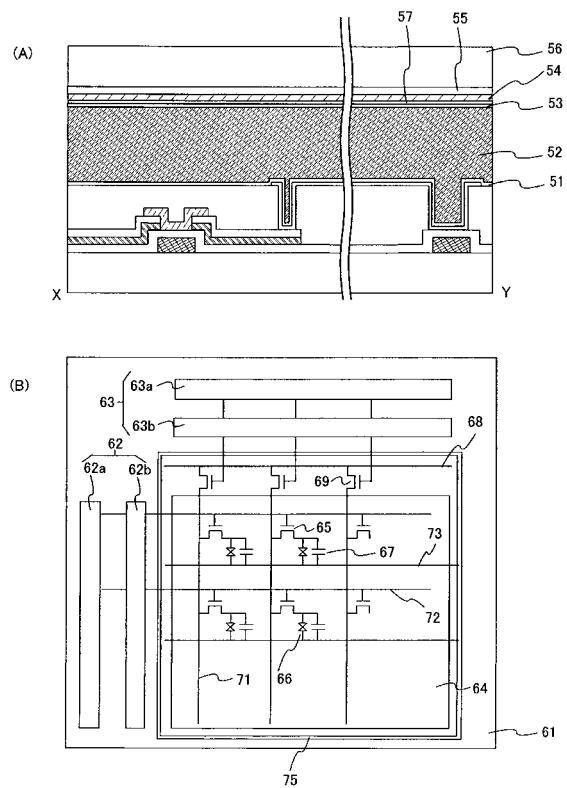

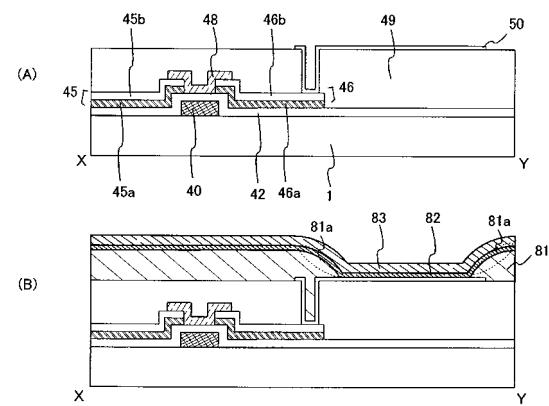

ここでは実施形態 1、3 で示したボトムゲート型の半導体装置を用いて液晶表示装置を作製する形態について図 8、9 を用いて説明する。なお実施形態 2、4 で示したトップゲート型の半導体装置を適用できることは言うまでもない。図 8(A)、図 9(A) は図 8(B) における X-Y の断面図を示す。

#### 【0100】

ガラス基板又はプラスチック基板 1 上にゲート配線 40 及び補助容量配線 41 を形成する。スパッタ法にて AlNd 膜を成膜し、その後公知のフォトリソグラフィー法及びエ

50

ツチング方法を用いて形成する。

【0101】

CVD法又はスパッタ法にて酸化珪素膜又は酸化窒素珪素膜からなるゲート絶縁膜42を形成する。

【0102】

ゲート絶縁膜42上に第1の導電膜としてスパッタ法にてAlNi膜を成膜する。第1の導電膜は後にソース電極45a、ドレイン電極46a及びソース配線47を形成する。

【0103】

第1の導電膜上に第2の導電膜としてAlが添加されたZnO(酸化亜鉛)をスパッタ法にて成膜する。第2の導電膜は後にソース電極45b、ドレイン電極46b及びソース配線47を形成する。10

【0104】

第2の導電膜上であって、後にソース電極部、ドレイン電極部、ソース配線部となる領域にレジストマスクを形成する(図示しない)。そして第2の導電膜をエッチングしてソース電極45b、ドレイン電極46b及びソース配線47を形成する。ここではバッファードフッ酸、HF:NH<sub>4</sub>F=1:100(重量比)の溶液を用いてエッチングする。

【0105】

次に第1の導電膜を、TMAH溶液を用いてエッチングしてソース電極45a、ドレイン電極46a、ソース配線47を形成する。その後レジストマスクを除去する。これによりゲート絶縁膜42にダメージを与えることなく、ソース電極45、ドレイン電極46及びソース配線47を形成することができる。またZnO膜はTMAHによってエッチングされないため、島状の第2の導電膜のサイズを縮小することもない。また第1の導電膜にAlNi膜を用いているのでソース配線の低抵抗化を図ることができる。20

【0106】

次に半導体膜48を形成する。スパッタ法にてZnO膜を成膜し、その後フォトリソグラフィー法及びエッチング方法を用いてZnO膜から成る半導体膜48を形成する。エッチングにはバッファードフッ酸を用いたウェットエッチングを用いる。このとき半導体膜48と接しない部分の第2の導電膜は一部除去されてもよい。配線となる部分には第1の導電膜が形成されているからである。30

【0107】

半導体膜48上に絶縁膜49をCVD法、スパッタ法、塗布法等により形成する。絶縁膜49は珪素を含む絶縁膜及び有機樹脂膜等の積層膜を用いることができる。絶縁膜49は表面の凹凸を平坦化する膜であればよい。

【0108】

絶縁膜49にフォトリソグラフィー法及びエッチング法を用いてドレイン電極46へのコンタクトホール及び補助容量用のコンタクトホールを形成する。

【0109】

透明導電膜をスパッタ法にて成膜し、その後フォトリソグラフィー法及びエッチング方法を用いて画素電極50を形成する。例えばITO(Indium Tin Oxide、インジウム錫酸化物)、ITSO(酸化珪素を含むインジウム錫酸化物)、IZO(Indium Zinc Oxide 酸化インジウム酸化亜鉛)を用いればよい。40

【0110】

反射型液晶表示装置の場合には透明電極でなく、Ag(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の光反射性を有する金属材料を形成する。

【0111】

画素電極50と補助容量配線41との重なった部分は、画素電極50、ゲート絶縁膜42及び補助容量配線41によって補助容量100を形成する(図8(A)(B))。

【0112】

50

配線や電極において、屈曲部や配線幅が変化する部位の角部をなめらかにして、丸みを付けてもよい。フォトマスクのパターンを用いてマスクパターンを作製し、当該マスクパターンを用いて形成することにより、角部を面取りした形状にすることができる。これにより以下の効果がある。凸部を面取りすることによって、プラズマを用いたドライエッティングを行う際、異常放電による微粉の発生を抑えることができる。また、凹部を面取りすることによって、微粉が発生した場合でも、洗浄のときに当該微粉が角に集まるのを防止し、当該微粉を洗い流すことができる。こうして、製造工程における塵や微粉の問題を解消し、歩留まりを向上させることができる。

## 【0113】

画素電極50を覆うように配向膜51を形成する。配向膜は液滴吐出法や印刷法等によって形成する。配向膜を形成した後、ラビング処理を行う。 10

## 【0114】

対向基板56には、着色層及び遮光層(ブラックマトリクス)によってカラーフィルター55を形成し、保護絶縁膜54を形成する。保護絶縁膜54上に透明電極57を形成し、配向膜53を形成する(図9(A))。配向膜にはラビング処理を行う。

## 【0115】

次いでシール材の閉パターン75を形成する(図9(B))。液滴吐出法等により形成することができる。このシール材で囲まれた領域に液晶組成物52が充填される(図9(A))。 20

## 【0116】

この閉パターン75内に液晶組成物52を滴下してから、対向基板56と半導体装置が形成された基板1を貼り合わせる。液晶組成物52を充填する際には開口部を有するシールパターンを基板1に設け、対向基板56と基板1とを貼り合わせた後に毛細管現象を用いて液晶を注入してもよい。

## 【0117】

液晶組成物52の配向モードとしては、液晶分子の配列が光の入射側から射出側に向かって90°ツイスト配向したTNモード、FLCモード、IPSモード、VAモードなどを用いることができる。ただしIPSモードの場合には電極パターンが図8(B)に示したものと異なり、櫛歯状になる。 30

## 【0118】

偏光板は半導体装置が形成されている基板1と対向基板56の両方に貼り付ける。また必要に応じて光学フィルムを貼り付けることができる。

## 【0119】

半導体装置が形成されている基板1と対向基板56との基板間隔は、球状のスペーサを散布する、樹脂からなる柱状のスペーサを形成する、シール材にフィラーを含ませることなどによって維持すればよい。上記柱状のスペーサは、アクリル、ポリイミド、ポリイミドアミド、エポキシの少なくとも1つを主成分とする有機樹脂材料、もしくは酸化珪素、窒化珪素、窒素を含む酸化珪素のいずれか一種の材料、或いはこれらの積層膜からなる無機材料を用いることができる。 40

## 【0120】

そして、異方性導電体層を介し、公知の技術を用いてFPC(Flexible Printed Circuit)を貼りつける。

## 【0121】

周辺駆動回路を基板上に形成してもよい。平面模式図を図9(B)に示す。

## 【0122】

ガラス等の基板61上にゲート配線駆動回路62、ソース配線駆動回路63、アクティブマトリクス部64が形成されている。ゲート配線駆動回路62は、少なくともシフトレジスタ62a及びバッファ62bから構成される。ソース配線駆動回路63は、少なくともシフトレジスタ63aと、バッファ63bと、ビデオライン68を通じて送られる信号のサンプリングを行うアナログスイッチ69とから構成される。アクティブマトリクス 50

部 6 4 には、ゲート配線駆動回路 6 2 から延びる複数の平行するゲート配線 7 2 が配されている。ソース配線駆動回路 6 3 からは複数のソース配線 7 1 がゲート配線 7 2 に直交して配設されている。また、ゲート配線 7 2 に平行して補助容量配線 7 3 が配設されている。そして、ゲート配線 7 2 、ソース配線 7 1 及び補助容量配線 7 3 に囲まれた領域には、半導体装置 6 5 、液晶部 6 6 、及び補助容量 6 7 が設けられている。

#### 【 0 1 2 3 】

ゲート配線駆動回路 6 2 、ソース配線駆動回路 6 3 、アナログスイッチ 6 9 にはそれぞれ半導体装置 6 5 と同じ作製方法によって同様の構造の半導体装置が形成されている。

#### 【 0 1 2 4 】

半導体装置 6 5 のゲート電極は、ゲート配線 7 2 に接続され、ソース電極はソース配線 7 1 に接続されている。半導体装置 6 5 のドレイン電極に接続された画素電極と、対向基板上の対向電極との間に液晶が封入され、液晶部 6 6 が構成されている。また補助容量配線 7 3 は対向電極と同じ電位の電極に接続されている。

#### 【 0 1 2 5 】

上記した液晶表示装置はゲート絶縁膜がエッティングされず、特性が不安定になることがなく信頼性が高い。またトップゲート型半導体装置を用いた場合にはガラス基板や酸化珪素膜や酸化窒化珪素膜からなる下地膜がエッティングされないため、基板からナトリウムなどの不純物が半導体膜に拡散し、特性を劣化させることがなく信頼性が高い。

#### 【 0 1 2 6 】

ソース電極及びドレイン電極の一部に A 1 を用いているため、配線の低抵抗化を図ることができる。

#### 【 0 1 2 7 】

##### ( 実施形態 6 )

ここでは実施形態 1 、 3 で示したボトムゲート型の半導体装置を用いて発光装置を作製する形態について図 1 0 、 1 1 を用いて説明する。なお実施形態 2 、 4 の半導体装置を適用できることは言うまでもない。

#### 【 0 1 2 8 】

上記実施形態の記載に基づいて半導体装置を作製し、図 1 0 ( A ) の形成までを行う。上記実施形態と同じものは同じ符号で表す。

#### 【 0 1 2 9 】

画素電極 5 0 は E L 表示装置において、陽極又は陰極として機能する。画素電極 5 0 の材料としてはアルミニウム ( A l ) 、銀 ( A g ) 、金 ( A u ) 、白金 ( P t ) 、ニッケル ( N i ) 、タンクステン ( W ) 、クロム ( C r ) 、モリブデン ( M o ) 、鉄 ( F e ) 、コバルト ( C o ) 、銅 ( C u ) 、パラジウム ( P d ) 、リチウム ( L i ) 、セシウム ( C s ) 、マグネシウム ( M g ) 、カルシウム ( C a ) 、ストロンチウム ( S r ) 、チタン ( T i ) などの導電性を有する金属、又はアルミニウム - シリコン ( A l - S i ) 、アルミニウム - チタン ( A l - T i ) 、アルミニウム - シリコン - 銅 ( A l - S i - C u ) 等の合金、または窒化チタン ( T i N ) 等の金属材料の窒化物、 I T O 、ケイ素を含有する I T O 、 I Z O 等の金属化合物などを形成することができる。

#### 【 0 1 3 0 】

E L 層からの発光を取り出す方の電極は透明性を有する導電膜により形成すれば良く、 I T O 、ケイ素を含有する I T O 、 I Z O などの金属化合物の他、 A l 、 A g 等金属の極薄膜を用いても良い。

#### 【 0 1 3 1 】

画素電極 5 0 と対向する電極の方から発光を取り出す場合、画素電極 5 0 は反射率の高い材料 ( A l 、 A g 等) を用いることができる。本実施形態では I T S O ( ケイ素を含む I T O ) を画素電極 5 0 として用いる ( 図 1 0 ( A ) ) 。

#### 【 0 1 3 2 】

次に絶縁膜 4 9 及び画素電極 5 0 を覆って有機材料もしくは無機材料からなる絶縁膜を形成する。続いて当該絶縁膜を画素電極 5 0 の一部が露出するように加工し、隔壁 8 1

10

20

30

40

50

を形成する。隔壁 8 1 の材料としては、感光性を有する有機材料（アクリル、ポリイミドなど）が好適に用いられるが、感光性を有さない有機材料や無機材料で形成してもかまわない。また、隔壁 8 1 の材料にチタンブラックやカーボンナイトライドなどの黒色顔料や染料を分散剤などを用いて分散し、隔壁 8 1 を黒くすることでブラックマトリクスとして用いても良い。隔壁 8 1 は、テーパー形状を示し、画素電極に向かう隔壁 8 1 の端面 8 1 a は曲率を有し、当該曲率が連続的に変化していることが望ましい（図 10（B））。

#### 【 0 1 3 3 】

次に、発光物質を含む層 8 2 を形成し、続いて発光物質を含む層 8 2 を覆う対向電極 8 3 を形成する。これによって画素電極 5 0 と対向電極 8 3との間に発光物質を含む層 8 2 を挟んでなる発光素子を作製することができ、画素電極 5 0 と対向電極 8 3 の間に電圧を印加することによって発光を得ることができる。10

#### 【 0 1 3 4 】

対向電極 8 3 の形成に用いられる電極材料としては画素電極に用いることのできる材料と同様の材料を用いることができる。本実施形態ではアルミニウムを第 2 の電極として用いる。

#### 【 0 1 3 5 】

発光物質を含む層 8 2 は、蒸着法、インクジェット法、スピンドルコート法、ディップコート法、ロールツーロール法、スパッタ法などによって形成される。

#### 【 0 1 3 6 】

有機エレクトロルミネッセンス表示装置の場合、発光物質を含む層 8 2 は正孔輸送、正孔注入、電子輸送、電子注入、発光など各機能を有する層の積層であっても良いし、発光層単層であっても良い。発光物質を含む層としては、単層の有機化合物層もしくは積層の有機化合物層を用いることができる。20

#### 【 0 1 3 7 】

正孔注入層は陽極と正孔輸送層の間に設けられる。正孔注入層としては有機化合物と金属酸化物の混合層を用いることができる。これによって画素電極 5 0 の表面に形成された凹凸や電極表面に残った異物の影響で画素電極 5 0 と対向電極 8 3 がショート（短絡）することを防ぐことができる。混合層の膜厚は 6 0 nm 以上あることが望ましい。また、1 2 0 nm 以上であるとなお良い。厚膜化しても発光素子の駆動電圧の上昇を招かないため、凹凸や異物の影響を充分にカバーできる膜厚を選ぶことができる。したがって本発明によって作製された発光装置は暗点を発生させることができない。また駆動電圧や消費電力の増加を招くことがない。30

#### 【 0 1 3 8 】

金属酸化物としては、遷移金属の酸化物や窒化物が望ましく、具体的には、酸化ジルコニアム、酸化ハフニウム、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンクス滕、酸化チタン、酸化マンガン、酸化レニウムが好適である。

#### 【 0 1 3 9 】

有機化合物としては 4 , 4' - ビス [ N - ( 1 - ナフチル ) - N - フェニルアミノ ] ビフェニル（略称：N P B）、4 , 4' - ビス [ N - ( 3 - メチルフェニル ) - N - フェニルアミノ ] ビフェニル（略称：T P D）、4 , 4' , 4'' - トリス ( N , N - ジフェニルアミノ ) トリフェニルアミン（略称：T D A T A）、4 , 4' , 4'' - トリス [ N - ( 3 - メチルフェニル ) - N - フェニルアミノ ] トリフェニルアミン（略称：M T D A T A）、4 , 4' - ビス { N - [ 4 - ( N , N - ジ - m - トリルアミノ ) フェニル ] - N - フェニルアミノ } ビフェニル（略称：D N T P D）、1 , 3 , 5 - トリス [ N , N - ジ ( m - トリル ) アミノ ] ベンゼン（略称：m - M T D A B）、4 , 4' , 4'' - トリス ( N - カルバゾリル ) トリフェニルアミン（略称：T C T A）等のアリールアミノ基を有する有機材料や、フタロシアニン（略称：H<sub>2</sub> P C）、銅フタロシアニン（略称：C u P C）、バナジルフタロシアニン（略称：V O P C）等も用いることができる。40

#### 【 0 1 4 0 】

正孔輸送層は陽極と発光層との間、正孔注入層が設けられる場合には正孔注入層と発光層との間に設けられる。正孔輸送層はホールを輸送する機能に優れた層、例えばN P BやT P D、T D A T A、M T D A T A、B S P Bなどの芳香族アミン（即ち、ベンゼン環-窒素の結合を有する）の化合物からなる層である。ここに述べた物質は、主に $1 \times 1 0^{-6} \sim 1 0 \text{ cm}^2 / \text{Vs}$ の正孔移動度を有する物質である。但し、電子よりも正孔の輸送性の高い物質であれば、これら以外のものを用いてもよい。なお、正孔輸送層は、単層のものだけでなく、上記物質からなる層が二層以上積層したものであってもよい。

#### 【0141】

発光層は陽極と陰極の間、正孔輸送層や電子輸送層が設けられる場合には、正孔輸送層と電子輸送層との間に設けられる。発光層について特に限定は無いが、発光層として機能する層には大きく分けて2つの態様ある。一つは発光中心となる発光材料（ドーパント材料）の有するエネルギー-ギャップよりも大きいエネルギー-ギャップを有する材料（ホスト材料）からなる層に発光材料を分散するホスト-ゲスト型の層と、もう一つは発光材料のみで発光層を構成する層である。前者は濃度消光が起こりにくく、好ましい構成である。発光中心となる発光物質としては、4-ジシアノメチレン-2-メチル-6-(1,1,7,7-テトラメチルジユロリジル-9-エニル)-4H-ピラン（略称：D C J T）、4-ジシアノメチレン-2-t-ブチル-6-(1,1,7,7-テトラメチルジユロリジル-9-エニル)-4H-ピラン、ペリフランテン、2,5-ジシアノ-1,4-ビス[2-(10-メトキシ-1,1,7,7-テトラメチルジユロリジン-9-イル)エテニル]ベンゼン、N,N'-ジメチルキナクリドン（略称：D M Q d）、クマリン6、クマリン545T、トリス(8-キノリノラト)アルミニウム（略称：A l q<sub>3</sub>）、9,9'-ビアントリル、9,10-ジフェニルアントラセン（略称：D P A）や9,10-ビス(2-ナフチル)アントラセン（略称：D N A）、2,5,8,11-テトラ-t-ブチルペリレン（略称：T B P）、P t O E P、I r (p p y)<sub>3</sub>、B t p<sub>2</sub>I r (a c a c)、F I r p i c 等が挙げられる。また、上記発光材料を分散してなる層を形成する場合に母体となるホスト材料としては、9,10-ジ(2-ナフチル)-2-t e r t -ブチルアントラセン（略称：t-B u D N A）等のアントラセン誘導体、4,4'-ビス(N-カルバゾリル)ビフェニル（略称：C B P）等のカルバゾール誘導体、トリス(8-キノリノラト)アルミニウム（略称：A l q<sub>3</sub>）、トリス(4-メチル-8-キノリノラト)アルミニウム（略称：A l m q<sub>3</sub>）、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム（略称：B e B q<sub>2</sub>）、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム（略称：B A l q）、ビス[2-(2-ヒドロキシフェニル)ビリジナト]亜鉛（略称：Z n p p<sub>2</sub>）、ビス[2-(2-ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛（略称：Z n B O X）などの金属錯体等を用いることができる。また、発光物質のみで発光層を構成することのできる材料としては、トリス(8-キノリノラト)アルミニウム（略称：A l q<sub>3</sub>）、9,10-ビス(2-ナフチル)アントラセン（略称：D N A）、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム（略称：B A l q）などがある。

#### 【0142】

電子輸送層は発光層と陰極との間、電子注入層が設けられる場合には、発光層と電子注入層との間に設けられる。電子輸送層は、電子を輸送する機能に優れた層、例えはトリス(8-キノリノラト)アルミニウム（略称：A l q<sub>3</sub>）、トリス(5-メチル-8-キノリノラト)アルミニウム（略称：A l m q<sub>3</sub>）、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム（略称：B e B q<sub>2</sub>）、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム（略称：B A l q）など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる層である。また、この他ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛（略称：Z n (B O X)<sub>2</sub>）、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛（略称：Z n (B T Z)<sub>2</sub>）などのオキサゾール系、チアゾール系配位子を有する金属錯体なども用いることができる。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-t e r t -ブ

10

20

30

30

40

50

チルフェニル) - 1 , 3 , 4 - オキサジアゾール(略称: PBD)や、1 , 3 - ビス[5 - (p - tert - ブチルフェニル) - 1 , 3 , 4 - オキサジアゾール - 2 - イル]ベンゼン(略称: OXD - 7)、3 - (4 - tert - ブチルフェニル) - 4 - フェニル - 5 - (4 - ピフェニリル) - 1 , 2 , 4 - トリアゾール(略称: TAZ)、3 - (4 - tert - ブチルフェニル) - 4 - (4 - エチルフェニル) - 5 - (4 - ピフェニリル) - 1 , 2 , 4 - トリアゾール(略称: p - EtTAZ)、パソフェナントロリン(略称: BP hen)、パソキュプロイン(略称: BCP)なども用いることができる。ここに述べた物質は、主に $1 \times 10^{-6} \sim 10 \text{ cm}^2 / \text{Vs}$ の電子移動度を有する物質である。なお、正孔よりも電子の輸送性の高い物質であれば、上記以外の物質を電子輸送層として用いても構わない。また、電子輸送層は、単層のものだけでなく、上記物質からなる層が二層以上積層したものとしてもよい。

#### 【0143】

電子注入層は陰極と電子輸送層との間に設けられる。電子注入層としては、フッ化リチウム(LiF)、フッ化セシウム(CsF)、フッ化カルシウム(CaF<sub>2</sub>)等のようなアルカリ金属又はアルカリ土類金属の化合物を用いることができる。また、この他、電子輸送性を有する物質にアルカリ金属又はアルカリ土類金属を含有させたもの、例えばAlq<sub>3</sub>中にマグネシウム(Mg)を含有させたもの等を用いることができる。

#### 【0144】

無機エレクトロルミネッセンス表示装置の場合、発光物質を含む層82には蛍光体粒子を分散剤に分散したものを用いることができる。

#### 【0145】

ZnSにCu(銅)とともにCl(塩素)、I(ヨウ素)、Al(アルミニウム)などのドナー性不純物を添加した蛍光体を用いることができる。

#### 【0146】

分散剤としては、シアノエチルセルロース系樹脂のように比較的誘電率の高いポリマー、ポリエチレン、ポリプロピレン、ポリスチレン系樹脂、シリコーン樹脂、エポキシ樹脂、フッ化ビニリデンなどの樹脂を用いることができる。これらの樹脂に、BaTiO<sub>3</sub>(チタン酸バリウム)やSrTiO<sub>3</sub>(チタン酸ストロンチウム)などの高誘電率の微粒子を適度に混合して誘電率を調整することもできる。分散手段としては、超音波分散機などを用いることができる。

#### 【0147】

発光物質を含む層82と電極との間には誘電体層を隣接してもよい。誘電体層は、誘電率と絶縁性が高く、且つ高い誘電破壊電圧を有する材料であれば任意のものが用いられる。これらは金属酸化物、窒化物から選択され、例えばTiO<sub>2</sub>、BaTiO<sub>3</sub>、SrTiO<sub>3</sub>、PbTiO<sub>3</sub>、KNbO<sub>3</sub>、PbNbO<sub>3</sub>、Ta<sub>2</sub>O<sub>3</sub>、BaTa<sub>2</sub>O<sub>6</sub>、LiTaO<sub>3</sub>、Y<sub>2</sub>O<sub>3</sub>、Al<sub>2</sub>O<sub>3</sub>、ZrO<sub>2</sub>、AlON、ZnSなどが用いられる。これらは均一な膜として設置されても良いし、また粒子構造を有する膜として用いても良い。

#### 【0148】

無機エレクトロルミネッセンス表示装置の場合、発光層を絶縁層で挟んだ二重絶縁構造としてもよい。発光層にはMn(マンガン)や希土類元素を含んだZnS(硫化亜鉛)などの2 - 6族化合物、絶縁層にはSi<sub>3</sub>N<sub>4</sub>、SiO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、TiO<sub>2</sub>などの酸化物、窒化物を用いることができる。

#### 【0149】

対向電極83上にプラズマCVD法により窒素を含む酸化ケイ素膜をパッシベーション膜として形成する(図示しない)。窒素を含む酸化ケイ素膜を用いる場合には、プラズマCVD法でSiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>から作製される酸化窒化ケイ素膜、またはSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化ケイ素膜、あるいはSiH<sub>4</sub>、N<sub>2</sub>OをArで希釈したガスから形成される酸化窒化ケイ素膜を形成すれば良い。

#### 【0150】

また、パッシベーション膜としてSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>から作製される酸化窒化水

10

20

30

40

50

素化ケイ素膜を適用しても良い。もちろんパッシベーション膜は上記したものに限定されるものではない。他のケイ素を主成分とする絶縁層を用いることもできる。また単層構造ではなく積層構造でもよい。また窒化炭素膜と窒化ケイ素膜の多層膜やスチレンポリマーの多層膜を用いてもよい。窒化ケイ素膜やダイヤモンドライクカーボン膜を形成してもよい。

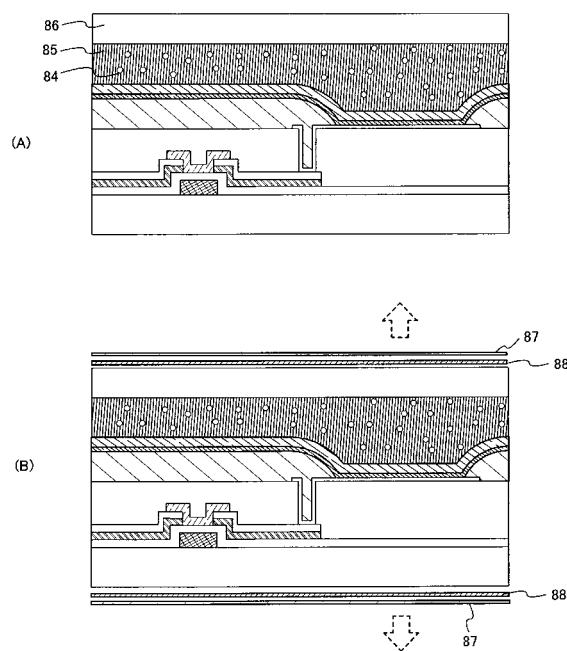

#### 【0151】

発光素子を水などの劣化を促進する物質から保護するために、表示部の封止を行う。対向基板そのものを封止に用いる場合は、絶縁性のシール材により、外部接続部が露出するように貼り合わせる。対向基板と素子基板との間の空間には乾燥した窒素などの不活性気体を充填しても良いし、シール材を画素部全面に形成し、そのシール材によって対向基板を貼り合わせても良い。シール材には紫外線硬化樹脂などを用いると好適である。シール材には乾燥剤や基板間のギャップを一定に保つための粒子を混入しておいても良い。続いて外部接続部にフレキシブル配線基板を貼り付けることによって、発光装置が完成する。

10

#### 【0152】

以上のように作製した発光装置の構成の1例について図11を参照しながら説明する。なお、形が異なっていても同様の機能を示す部分には同じ符号を付し、その説明を省略する部分もある。

#### 【0153】

図11(A)は画素電極50が透光性を有する導電膜により形成されており、基板1側に発光物質を含む層82より発せられた光が取り出される構造である。なお86は対向基板であり、発光素子が形成された後、シール材などを用い、基板1に固着される。対向基板86と素子との間に透光性を有する樹脂85等を充填し、封止する。これによって発光素子が水分により劣化することを防ぐ事ができる。また、樹脂85が吸湿性を有していることが望ましい。さらに樹脂85中に透光性の高い乾燥剤84を分散させるとさらに水分の影響を抑えることが可能になるためさらに望ましい形態である。

20

#### 【0154】

図11(B)は画素電極50と対向電極83の両方が透光性を有する導電膜により形成されている。よって基板1側及び対向基板86側の両方に点線の矢印で示すように光を取り出すことが可能な構成となっている。この構成では基板1と対向基板86の外側に偏光板88を設けることによって画面が透けてしまうことを防ぐことができ、視認性が向上する。偏光板88の外側には保護フィルム87を設けると良い。

30

#### 【0155】

なお、表示機能を有する本発明の発光装置には、アナログのビデオ信号、デジタルのビデオ信号のどちらを用いてもよい。デジタルのビデオ信号を用いる場合はそのビデオ信号が電圧を用いているものと、電流を用いているものとに分けられる。

#### 【0156】

発光素子の発光時において、画素に入力されるビデオ信号は、定電圧のものと、定電流のものがある。ビデオ信号が定電圧のものには、発光素子に印加される電圧が一定のものと、発光素子に流れる電流が一定のものとがある。

40

#### 【0157】

またビデオ信号が定電流のものには、発光素子に印加される電圧が一定のものと、発光素子に流れる電流が一定のものとがある。この発光素子に印加される電圧が一定のものは定電圧駆動であり、発光素子に流れる電流が一定のものは定電流駆動である。定電流駆動は、発光素子の抵抗変化によらず、一定の電流が流れる。本発明を用いて作製された発光装置及びその駆動方法には、上記したどの駆動方法を用いてもよい。

#### 【0158】

上記した発光装置はゲート絶縁膜がエッチングされず、特性が不安定になることがなく信頼性が高い。またトップゲート型半導体装置を用いた場合にはガラス基板や酸化珪素膜や酸化窒化珪素膜からなる下地膜がエッチングされないため、基板からナトリウムなど

50

の不純物が半導体膜に拡散し、特性を劣化させることなく信頼性が高い。

【0159】

ソース電極及びドレイン電極の一部にA1を用いているため、配線の低抵抗化を図ることができる。

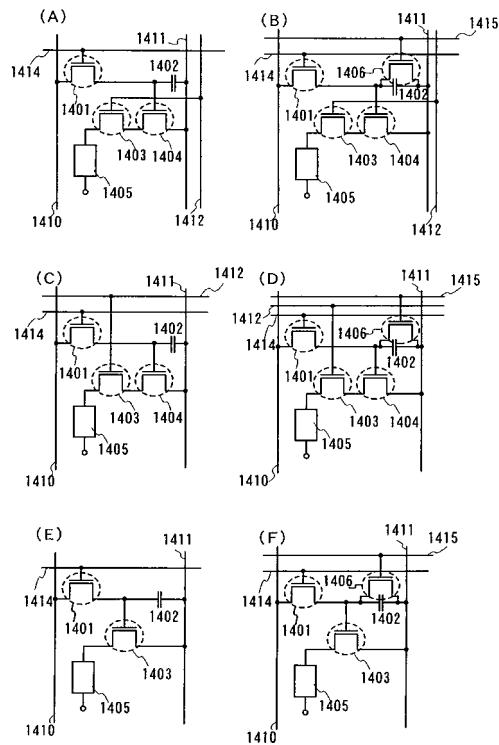

【0160】

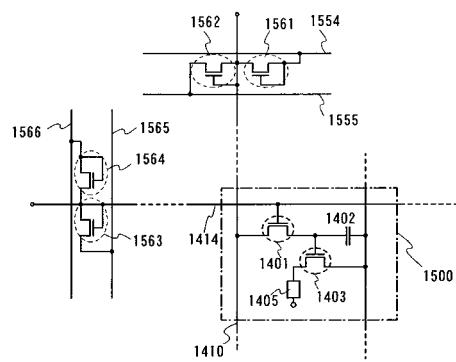

パネル、モジュールが有する画素回路、保護回路及びそれらの動作について図12、図13等を用いて説明する。図10、11に示した半導体装置は駆動用TFT1403の断面図となっている。スイッチング用TFT1401、電流制御用TFT1404、消去用TFT1406はすべて駆動用TFT1403と同時に作製され、駆動用TFT1403と同様の構成をしていても良い。

10

【0161】

図12(A)に示す画素は、列方向に信号線1410及び電源線1411、1412、行方向に走査線1414が配置される。また、スイッチング用TFT1401、駆動用TFT1403、電流制御用TFT1404、補助容量1402及び発光素子1405を有する。

【0162】

図12(C)に示す画素は、駆動用TFT1403のゲート電極が、行方向に配置された電源線1412に接続される点が異なっており、それ以外は図12(A)に示す画素と同じ構成である。つまり、図12(A)、(C)に示す両画素は、同じ等価回路図を示す。しかしながら、列方向に電源線1412が配置される場合(図12(A))と、行方向に電源線1412が配置される場合(図12(C))とでは、各電源線は異なるレイヤーの導電膜で形成される。ここでは、駆動用TFT1403のゲート電極が接続される配線に注目し、これらを作製するレイヤーが異なることを表すために、図12(A)、(C)として分けて記載する。

20

【0163】

図12(A)、(C)に示す画素の特徴として、画素内に駆動用TFT1403と電流制御用TFT1404が直列に接続されている。駆動用TFT1403のチャネル長L(1403)、チャネル幅W(1403)、電流制御用TFT1404のチャネル長L(1404)、チャネル幅W(1404)は、 $L(1403)/W(1403) : L(1404)/W(1404) = 5 \sim 6000 : 1$ を満たすように設定するとよい。

30

【0164】

なお、駆動用TFT1403は、飽和領域で動作し発光素子1405に流れる電流値を制御する役目を有する。電流制御用TFT1404は線形領域で動作し発光素子1405に対する電流の供給を制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましく、本実施形態ではnチャネル型TFTとして形成する。また駆動用TFT1403には、エンハンスマント型だけでなく、ディプリーション型のTFTを用いてもよい。上記構成を有する発光装置は、電流制御用TFT1404が線形領域で動作するために、電流制御用TFT1404のVgsの僅かな変動は、発光素子1405の電流値に影響を及ぼさない。つまり、発光素子1405の電流値は、飽和領域で動作する駆動用TFT1403により決定することができる。上記構成により、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた発光装置を提供することができる。

40

【0165】

図12(A)～(D)に示す画素において、スイッチング用TFT1401は、画素に対するビデオ信号の入力を制御するものであり、スイッチング用TFT1401がオンとなると、画素内にビデオ信号が入力される。すると、補助容量1402にそのビデオ信号の電圧が保持される。なお図12(A)、(C)には、補助容量1402を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などで可能な場合には、補助容量1402を設けなくてもよい。

【0166】

50

図12(B)に示す画素は、TFT1406と走査線1415を追加している以外は、図12(A)に示す画素構成と同じである。同様に、図12(D)に示す画素は、TFT1406と走査線1415を追加している以外は、図12(C)に示す画素構成と同じである。

#### 【0167】

TFT1406は、新たに配置された走査線1415によりオン又はオフが制御される。TFT1406がオンとなると、補助容量1402に保持された電荷は放電し、電流制御用TFT1404がオフとなる。つまり、TFT1406の配置により、強制的に発光素子1405に電流が流れない状態を作ることができる。そのためTFT1406を消去用TFTと呼ぶことができる。従って、図12(B)、(D)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時に点灯期間を開始することができるため、デューティ比を向上することが可能となる。10

#### 【0168】

図12(E)に示す画素は、列方向に信号線1410、電源線1411、行方向に走査線1414が配置される。また、スイッチング用TFT1401、駆動用TFT1403、補助容量1402及び発光素子1405を有する。図12(F)に示す画素は、TFT1406と走査線1415を追加している以外は、図12(E)に示す画素構成と同じである。なお、図12(F)の構成も、TFT1406の配置により、デューティ比を向上することが可能となる。20

#### 【0169】

このようなアクティブマトリクス型の発光装置は、画素密度が増えた場合、各画素にTFTが設けられているため低電圧駆動でき、有利であると考えられる。20

#### 【0170】

本実施形態では、一画素にTFTが設けられるアクティブマトリクス型の発光装置について説明したが、パッシブマトリクス型の発光装置を形成することもできる。パッシブマトリクス型の発光装置は、各画素にTFTが設けられていないため、高開口率となる。発光が発光積層体の両側へ射出する発光装置の場合、パッシブマトリクス型の発光装置を用いると透過率が高まる。

#### 【0171】

続いて、図12(E)に示す等価回路を用い、走査線及び信号線に保護回路としてダイオードを設ける場合について説明する。30

#### 【0172】

図13には、画素部1500にスイッチング用TFT1401、駆動用TFT1403、補助容量1402、発光素子1405が設けられている。信号線1410には、ダイオード1561と1562が設けられている。ダイオード1561と1562は、スイッチング用TFT1401又は駆動用TFT1403と同様に、上記実施形態に基づき作製され、ゲート電極、半導体層、ソース電極及びドレイン電極等を有する。ダイオード1561と1562は、ゲート電極と、ドレイン電極又はソース電極とを接続することによりダイオードとして動作させている。40

#### 【0173】

ダイオード1561、1562と接続する共通電位線1554、1555はゲート電極と同じレイヤーで形成している。従って、ダイオードのソース電極又はドレイン電極と接続するには、ゲート絶縁層にコンタクトホールを形成する必要がある。

#### 【0174】

走査線1414に設けられるダイオード1563、1564も同様な構成である。また共通電位線1565、1566も同様な構成である。

#### 【0175】

このように、本発明によれば、入力段に設けられる保護ダイオードを同時に形成することができる。なお、保護ダイオードを形成する位置は、これに限定されず、駆動回路と画素との間に設けることもできる。50

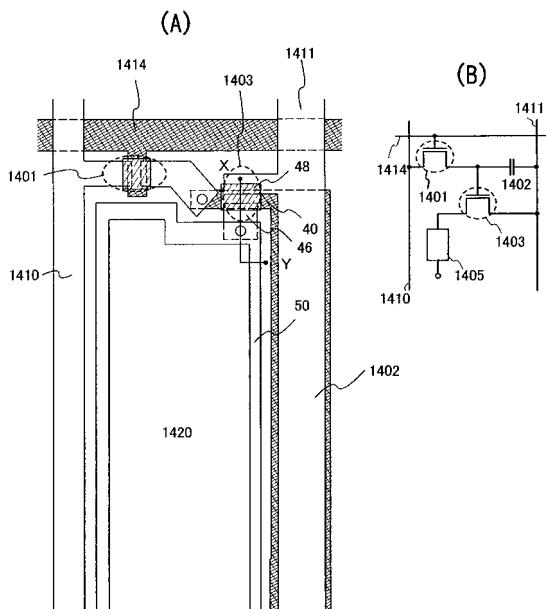

## 【0176】

図12(E)に示す等価回路を用いた場合の画素部分の上面図を図14(A)に示す。また図14(B)には図12(E)と同じ等価回路を示す。図10、11に示した半導体装置は駆動用TFT1403に対応する。図10、11は図14におけるX-Yの断面図を示している。電源線1411、信号線1410、スイッチング用TFT1401のソース電極、ドレイン電極、駆動用TFT1403のソース電極、ドレイン電極とは同じ導電膜、すなわち第1の導電膜及び第2の導電膜によって形成されている。

## 【0177】

スイッチング用TFT1401は駆動用TFT1403と同じ方法によって作製される。スイッチング用TFT1401のドレイン電極と駆動用TFT1403のゲート電極10 40はゲート絶縁膜42と同じ層の絶縁膜に形成されたコンタクトホールを介して電気的に接続されている。

## 【0178】

補助容量1402は駆動用TFT1403のゲート電極が延長した部分と、電源線1411と、ゲート絶縁膜42と同じ層の絶縁膜によって形成されている。

## 【0179】

発光領域1420は隔壁81の開口部に形成される。図示しないが発光領域1420の周辺には隔壁81が形成されている。発光領域1420は角部が丸みを帯びてもよい。隔壁81の開口部の角部に丸みを与えることによって発光領域1420の角部に丸みを与えることができる。角部に丸みを与えることによって、隔壁81の加工にプラズマを用いたドライエッティングを行う際、異常放電による微粉の発生を抑えることができる。20

## 【0180】

本実施形態は上記実施形態の適当な構成と適宜組み合わせて用いることができる。

## 【0181】

## (実施形態7)

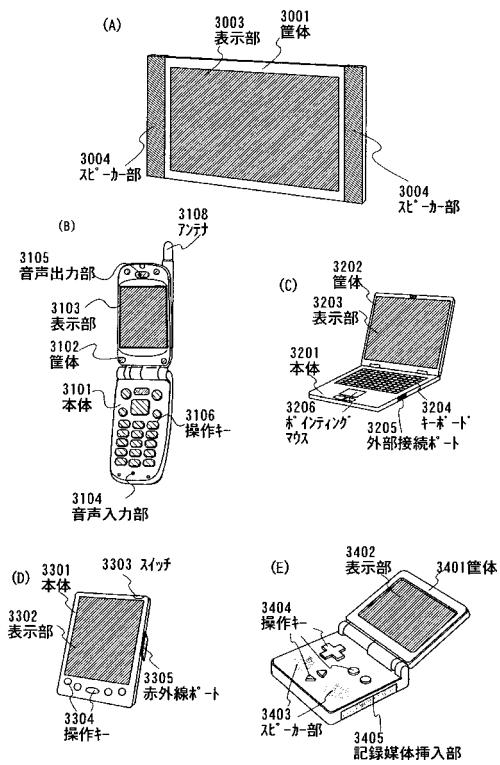

上記実施形態にその一例を示したようなモジュールを搭載した本発明の半導体装置を有する電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を図15、図16に示す。30

## 【0182】

図15(A)はテレビ受像器やパーソナルコンピュータのモニターなどである。筐体3001、表示部3003、スピーカー部3004等を含む。表示部3003にはアクティブマトリクス表示装置が設けられている。表示部3003は画素ごとに本発明の半導体装置を有している。これにより特性劣化が少ないテレビを得ることができる。

## 【0183】

図15(B)は携帯電話であり、本体3101、筐体3102、表示部3103、音声入力部3104、音声出力部3105、操作キー3106、アンテナ3108等を含む。表示部3103にはアクティブマトリクス表示装置が設けられている。表示部3103は画素ごとに本発明の半導体装置を有している。これにより特性劣化が少ない携帯電話を得ることができる。40

## 【0184】

図15(C)はコンピュータであり、本体3201、筐体3202、表示部3203、キーボード3204、外部接続ポート3205、ポインティングマウス3206等を含む。表示部3203にはアクティブマトリクス表示装置が設けられている。表示部3203は画素ごとに本発明の半導体装置を有している。これにより特性劣化が少ないコンピュータを得ることができる。50

## 【0185】

図15(D)はモバイルコンピュータであり、本体3301、表示部3302、スイッチ3303、操作キー3304、赤外線ポート3305等を含む。表示部3302にはアクティブマトリクス表示装置が設けられている。表示部3302は画素ごとに本発明の半導体装置を有している。これにより特性劣化が少ないモバイルコンピュータを得ることができる。

## 【0186】

図15(E)は携帯型のゲーム機であり、筐体3401、表示部3402、スピーカー部3403、操作キー3404、記録媒体挿入部3405等を含む。表示部3402にはアクティブマトリクス表示装置が設けられている。表示部3402は画素ごとに本発明の半導体装置を有している。これにより特性劣化が少ない携帯型ゲーム機を得ることができる。10

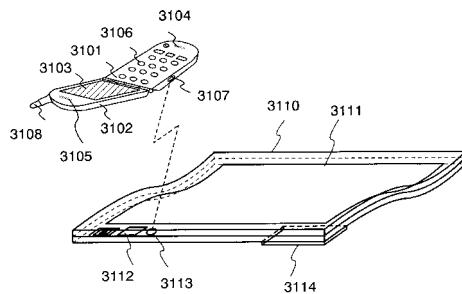

## 【0187】

図16はフレキシブルディスプレイであり、本体3110、画素部3111、ドライバIC3112、受信装置3113、フィルムバッテリー3114等を含む。受信装置では上記携帯電話の赤外線通信ポート3107からの信号を受信することができる。画素部3111にはアクティブマトリクス表示装置が設けられている。画素部3111は画素ごとに本発明の半導体装置を有している。これにより特性劣化が少ないフレキシブルディスプレイを得ることができる。

## 【0188】

以上のように、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。20

## 【図面の簡単な説明】

## 【0189】

【図1】本発明に係る半導体装置を説明する図。

【図2】本発明に係る半導体装置の作製工程を説明する図。

【図3】本発明に係る半導体装置の作製工程を説明する図。

【図4】本発明に係る半導体装置の作製工程を説明する図。

【図5】本発明に係る半導体装置の作製工程を説明する図。

【図6】本発明に係る半導体装置の作製工程を説明する図。30

【図7】従来例を説明する図。

【図8】液晶表示装置の作製工程を説明する図。

【図9】液晶表示装置の作製工程を説明する図。

【図10】発光装置の作製工程を説明する図。

【図11】発光装置の作製工程を説明する図。

【図12】発光装置の等価回路図。

【図13】発光装置の等価回路図。

【図14】発光装置の画素部の上面図と等価回路図。

【図15】本発明が適用される電子機器の例を示す図。

【図16】本発明が適用される電子機器の例を示す図。40

## 【符号の説明】

## 【0190】

1 基板

2 絶縁膜

3 ゲート電極

5 ゲート絶縁膜

6 第1の導電膜

7 第2の導電膜

8 第3の導電膜

9 レジストマスク

|       |               |    |

|-------|---------------|----|

| 1 0   | ソース電極         |    |

| 1 0 a | ソース電極、第1の導電膜  |    |

| 1 0 b | ソース電極、第2の導電膜  |    |

| 1 1   | ドレイン電極        |    |

| 1 1 a | ドレイン電極、第1の導電膜 |    |

| 1 1 b | ドレイン電極、第2の導電膜 |    |

| 1 2   | 半導体膜          |    |

| 1 3   | 島状の半導体膜       |    |

| 1 4   | 絶縁膜           | 10 |

| 2 0   | 絶縁膜           |    |

| 2 1   | 第1の導電膜        |    |

| 2 2   | 第2の導電膜        |    |

| 2 3   | 第3の導電膜        |    |

| 2 4   | レジストマスク       |    |

| 2 5   | ソース電極         |    |

| 2 5 a | ソース電極、第1の導電膜  |    |

| 2 5 b | ソース電極、第2の導電膜  |    |

| 2 6   | ドレイン電極        |    |

| 2 6 a | ドレイン電極、第1の導電膜 |    |

| 2 6 b | ドレイン電極、第2の導電膜 | 20 |

| 2 7   | 半導体膜          |    |

| 2 8   | ゲート絶縁膜        |    |

| 2 9   | ゲート電極         |    |

| 3 0   | 絶縁膜           |    |

| 4 0   | ゲート電極、ゲート配線   |    |

| 4 1   | 補助容量配線        |    |

| 4 2   | ゲート絶縁膜        |    |

| 4 5   | ソース電極         |    |

| 4 5 a | ソース電極         |    |

| 4 5 b | ソース電極         | 30 |

| 4 6   | ドレイン電極        |    |

| 4 6 a | ドレイン電極        |    |

| 4 6 b | ドレイン電極        |    |

| 4 7   | ソース配線         |    |

| 4 8   | 半導体膜          |    |

| 4 9   | 絶縁膜           |    |

| 5 0   | 画素電極          |    |

| 5 1   | 配向膜           |    |

| 5 2   | 液晶組成物         |    |

| 5 3   | 配向膜           | 40 |

| 5 4   | 保護絶縁膜         |    |

| 5 5   | カラーフィルター      |    |

| 5 6   | 対向基板          |    |

| 6 1   | 基板            |    |

| 6 2   | ゲート配線駆動回路     |    |

| 6 2 a | シフトレジスタ       |    |

| 6 2 b | バッファ          |    |

| 6 3   | ソース配線駆動回路     |    |

| 6 3 a | シフトレジスタ       |    |

| 6 3 b | バッファ          | 50 |

|         |             |    |

|---------|-------------|----|

| 6 4     | アクティブマトリクス部 |    |

| 6 5     | 半導体装置       |    |

| 6 6     | 液晶部         |    |

| 6 7     | 補助容量        |    |

| 6 8     | ビデオライン      |    |

| 6 9     | アナログスイッチ    |    |

| 7 1     | ソース配線       |    |

| 7 2     | ゲート配線       |    |

| 7 3     | 補助容量配線      |    |

| 7 5     | シール材        | 10 |

| 8 1     | 隔壁          |    |

| 8 1 a   | 端面          |    |

| 8 2     | 発光物質を含む層    |    |

| 8 3     | 対向電極        |    |

| 8 4     | 乾燥剤         |    |

| 8 5     | 樹脂          |    |

| 8 6     | 対向基板        |    |

| 8 7     | 保護フィルム      |    |

| 8 8     | 偏光板         |    |

| 1 0 0   | 補助容量        | 20 |

| 1 0 0 0 | 基板          |    |

| 1 0 0 1 | ソース電極       |    |

| 1 0 0 2 | ドレイン電極      |    |

| 1 0 0 3 | 半導体膜        |    |

| 1 0 0 4 | ゲート絶縁膜      |    |

| 1 0 0 5 | ゲート電極       |    |

| 1 0 0 6 | 下地膜         |    |

| 1 4 0 1 | スイッチング用 TFT |    |

| 1 4 0 2 | 補助容量        |    |

| 1 4 0 3 | 駆動用 TFT     | 30 |

| 1 4 0 4 | 電流制御用 TFT   |    |

| 1 4 0 5 | 発光素子        |    |

| 1 4 0 6 | TFT         |    |

| 1 4 1 0 | 信号線         |    |

| 1 4 1 1 | 電源線         |    |

| 1 4 1 2 | 電源線         |    |

| 1 4 1 4 | 走査線         |    |

| 1 4 1 5 | 走査線         |    |

| 1 4 2 0 | 発光領域        |    |

| 1 5 0 0 | 画素部         | 40 |

| 1 5 5 4 | 共通電位線       |    |

| 1 5 5 5 | 共通電位線       |    |

| 1 5 6 1 | ダイオード       |    |

| 1 5 6 2 | ダイオード       |    |

| 1 5 6 3 | ダイオード       |    |

| 1 5 6 4 | ダイオード       |    |

| 1 5 6 5 | 共通電位線       |    |

| 1 5 6 6 | 共通電位線       |    |

| 3 0 0 1 | 筐体          |    |

| 3 0 0 3 | 表示部         | 50 |

|         |            |    |

|---------|------------|----|

| 3 0 0 4 | スピーカー部     |    |

| 3 1 0 1 | 本体         |    |

| 3 1 0 2 | 筐体         |    |

| 3 1 0 3 | 表示部        |    |

| 3 1 0 4 | 音声入力部      |    |

| 3 1 0 5 | 音声出力部      |    |

| 3 1 0 6 | 操作キー       |    |

| 3 1 0 7 | 赤外線通信ポート   |    |

| 3 1 0 8 | アンテナ       |    |

| 3 1 1 0 | 本体         | 10 |

| 3 1 1 1 | 画素部        |    |

| 3 1 1 2 | ドライバ I C   |    |

| 3 1 1 3 | 受信装置       |    |

| 3 1 1 4 | フィルムバッテリー  |    |

| 3 2 0 1 | 本体         |    |

| 3 2 0 2 | 筐体         |    |

| 3 2 0 3 | 表示部        |    |

| 3 2 0 4 | キーボード      |    |

| 3 2 0 5 | 外部接続ポート    |    |

| 3 2 0 6 | ポインティングマウス | 20 |

| 3 3 0 1 | 本体         |    |

| 3 3 0 2 | 表示部        |    |

| 3 3 0 3 | スイッチ       |    |

| 3 3 0 4 | 操作キー       |    |

| 3 3 0 5 | 赤外線ポート     |    |

| 3 4 0 1 | 筐体         |    |

| 3 4 0 2 | 表示部        |    |

| 3 4 0 3 | スピーカー部     |    |

| 3 4 0 4 | 操作キー       |    |

| 3 4 0 5 | 記録媒体挿入部    | 30 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 21/28 301 R

(56)参考文献 国際公開第2004/038757 (WO, A1)

特開2003-037268 (JP, A)

特開昭62-252973 (JP, A)

特開平01-236655 (JP, A)

特開2005-077822 (JP, A)

特開平07-066417 (JP, A)

特開2003-086808 (JP, A)

特開2006-344849 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/33, 29/786