(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5554792号

(P5554792)

(45) 発行日 平成26年7月23日(2014.7.23)

(24) 登録日 平成26年6月6日(2014.6.6)

(51) Int.Cl.

H01L 33/20 (2010.01)

H01L 33/36 (2010.01)

F 1

H01L 33/00 170

H01L 33/00 200

請求項の数 1 (全 19 頁)

|              |                                                                   |

|--------------|-------------------------------------------------------------------|

| (21) 出願番号    | 特願2012-21079 (P2012-21079)                                        |

| (22) 出願日     | 平成24年2月2日(2012.2.2)                                               |

| (62) 分割の表示   | 特願2008-518038 (P2008-518038)<br>の分割<br>原出願日 平成18年6月22日(2006.6.22) |

| (65) 公開番号    | 特開2012-84933 (P2012-84933A)                                       |

| (43) 公開日     | 平成24年4月26日(2012.4.26)                                             |

| 審査請求日        | 平成24年2月2日(2012.2.2)                                               |

| (31) 優先権主張番号 | 10-2005-0053797                                                   |

| (32) 優先日     | 平成17年6月22日(2005.6.22)                                             |

| (33) 優先権主張国  | 韓国(KR)                                                            |

| (31) 優先権主張番号 | 10-2005-0055179                                                   |

| (32) 優先日     | 平成17年6月24日(2005.6.24)                                             |

| (33) 優先権主張国  | 韓国(KR)                                                            |

|           |                                                                                                                                      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 506029004<br>ソウル バイオシス カンパニー リミテッド<br>SEOUL VIOSYS CO., LTD.<br>大韓民国 425-851 ギョンギード<br>アンサンーシ ダンウォング ウォン<br>シードン 727-5 ブロック 1-3<br>6 |

| (74) 代理人  | 110000408<br>特許業務法人高橋・林アンドパートナーズ                                                                                                     |

| (72) 発明者  | イ, ジョンラン<br>790-751, 大韓民国, ギョンサンブ<br>クード, ボハンシ, ナング, ジゴクー<br>ドン, ギヨスアパート, 8-1403<br>最終頁に続く                                           |

(54) 【発明の名称】発光素子及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に複数の発光セルにそれぞれ対応させてn型半導体層、活性層、及びp型半導体層を順次に形成し、

前記複数の発光セルごとに水平面に対して勾配を有し且つ前記p型半導体層から前記活性層まで連続して形成された少なくとも一つの斜面を有するように前記p型半導体層及び前記活性層の一部をそれぞれ除去して前記n型半導体層の一部をそれぞれ露出させ、

前記p型半導体層の上部に反射層を形成し、

一方の前記発光セルの前記露出されたn型半導体層と、前記一方の前記発光セルに隣接する他方の前記発光セルの前記反射層とを、前記基板の一方の周縁に位置する前記発光セルの前記反射層及び前記基板の他方の周縁に位置する前記発光セルの前記露出されたn型半導体層を除いて、それぞれブリッジ配線を介して接続し、

前記複数の発光セルのうち、前記基板の一方の周縁に位置する前記発光セルの前記反射層上にp型金属バンプと、前記基板の一方の周縁に位置する前記発光セル以外の前記発光セルの前記反射層上にそれぞれバンピング用の金属バンプと、を形成し、

前記複数の発光セルのうち、前記基板の他方の周縁に位置する前記発光セルの前記露出された前記n型半導体層上にn型金属バンプを形成し、

サブマウント基板上に前記p型金属バンプ及び前記n型金属バンプにそれぞれ対応するp型ボンディングパッド及びn型ボンディングパッドと、前記バンピング用の金属バンプにそれぞれ対応するボンディング層と、を形成し、

10

20

前記 p 型金属バンプ及び前記 n 型金属バンプと、それぞれ対応する前記 p 型ボンディングパッド及び前記 n 型ボンディングパッドとがそれぞれ接続されるように、前記基板と前記サブマウント基板とをフリップチップボンディングし、

前記フリップチップボンディングされた前記基板と前記サブマウント基板を、前記プリッジ配線を介して接続された前記複数の発光セルを有する発光素子ごとに切り出すことを含み、

前記反射層は電気伝導性を有することを特徴とする発光素子の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

本発明は発光素子及びその製造方法に係り、さらに詳しくは、窒化物系の半導体発光素子における発光効率及び輝度を高めるための発光素子及びその製造方法に関する。

**【背景技術】**

**【0002】**

発光素子 (light emitting diode; LED) とは、半導体の p-n 接合構造を用いて注入された少数キャリア（電子または正孔）を作り、これらの再結合により所定の光を発する素子を言い、GaAs、AlGaAs、GaN、InGaN、AlGaN/Pなどの化合物半導体の材料を変えて発光源を構成することにより種々の色を実現することができる。例えば、赤色発光素子は GaAsPなどを用いて得ることができ、緑色発光素子は GaP、InGaNなどを用いて得ることができ、青色発光素子は InGaN/GaN ダブルヘテロ構造を用いて得ることができ、さらに、UV 発光素子は AlGaN/GaN または AlGaN/AlGaN 構造を用いて得ることができる。

20

**【0003】**

特に、GaN は、常温下で 3.4 eV の直接遷移型バンドギャップを有し、窒化インジウム (InN)、窒化アルミニウム (AlN) などの物質との組み合わせにより 1.9 eV (InN) から 3.4 eV (GaN)、6.2 eV (AlN) までの直接エネルギー bandwidth ギャップを有していて、可視光から紫外線域までの広い波長域が得られることから、光素子の応用可能性が極めて高い物質とされている。このように波長が調節できて短波長域における赤色、緑色及び青色発光素子によるフルカラーが実現可能になることから、ディスプレイ領域はもとより、一般の照明市場への波及効果は極めて大きくなると見込まれる。

30

**【0004】**

発光素子は、既存の電球または蛍光灯に比べて、消耗電力が低く、長寿命であり、手狭いスペースに取り付け可能である他、振動に強い、という特性を示している。この種の発光素子は表示素子及びバックライトとして用いられているが、消耗電力の削減と耐久性の面で優れた特性を有することから、近年、照明用途として採用するための研究が盛んになされできている。今後、大型 LCD-TV のバックライトや自動車のヘッドライト、一般照明にまでその応用が拡大していくと見込まれる中で、発光素子の発光効率の改善、放熱問題の解消及び発光素子の高輝度化・高出力化が解決課題として残されている。

**【0005】**

40

これまで発光素子の性能を高めるための数多くの技術が開発されている。発光素子の性能を示す指標としては、発光効率 (lm/W)、内部量子効率 (%)、外部量子効率 (%)、取出効率 (%) など種々あるが、取出効率は、発光素子に注入された電子と発光素子の外に発せられる光子との比により決まり、取出効率が高いほど発光素子が明るいことを意味する。発光素子の取出効率は、チップの形状や表面の形状、チップの構造、パッケージング方式に大きく影響されるため、発光素子を設計するに当たって細かい注意を払うことが必要である。

**【0006】**

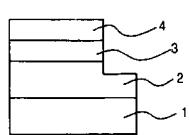

図 1 は、従来の水平構造の発光素子を示す断面図である。

図 1 を参照すれば、発光素子は、基板 1 と、基板 1 の上に形成された N 型半導体層 2 と、

50

該N型半導体層2の一部に形成された活性層3と、P型半導体層4と、を備えている。これは、前記基板1の上にN型半導体層2、活性層3、P型半導体層4を順次に形成した後、所定の領域のP型半導体層4と活性層3をエッティングしてN型半導体層2の一部を露出させ、その露出されたN型半導体層2の上面とP型半導体層2の上面にそれぞれ所定の電圧を印加するためのものである。

#### 【0007】

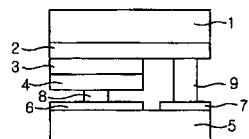

図2は、従来のフリップチップ構造の発光素子を示す断面図である。

図2を参照すれば、発光素子は、ベース基板1の上に順次に形成されたN型半導体層2と、活性層3及びP型半導体層4を備え、さらに、金属バンプ8、9を用いて前記ベース基板1をフリップチップボンディングしたサブマウント基板5を備えている。このために、所定の基板1の上にN型半導体層2と、活性層3及びP型半導体層4を順次に形成し、P型半導体層4と活性層3の一部をエッティングすることによりN型半導体層2を露出させて発光セルを形成する。また、別のサブマウント基板5を用意して第1及び第2の電極6、7を形成し、第1の電極6の上にはP型金属バンプ8を形成し、第2の電極7の上にはN型金属バンプ9を形成する。この後、前記発光セルを前記サブマウント基板5にボンディングするが、発光セルのP電極をP型金属バンプ8に、N電極をN型金属バンプ9にボンディングして発光素子を作製する。このような従来のフリップチップ構造の発光素子は、放熱効率が高く、且つ、光の遮蔽がほとんどないことから、光効率が既存の発光素子に比べて50%以上増大するという効果があり、発光素子の駆動のための金線が不要になることから、種々の小型パッケージへの応用も考えられている。

#### 【0008】

発光素子の発光層において生成された光はチップの全面から発せられ、光の取出効率は、通常、光の臨界角により決まる。しかしながら、従来の発光素子は、N型半導体層を露出させるためにエッティングを行うとき、P型半導体層と活性層の側面が垂直に加工されて、発光素子の内部において生成された光の一部が水平面から垂直に加工されたエッティング面において全反射されてしまう。

また、全反射される相当量の光は内部反射により外部に放出されないままで発光素子の内部において消滅されてしまう。すなわち、電気エネルギーが光エネルギーに変換されて素子の外部に抜け出る発光効率が低いという不都合がある。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

本発明は上記事情に鑑みてなされたものであり、その目的は、発光効率、外部量子効率、取出効率などの特性を高めると共に信頼性を確保することにより、高光度、高輝度の光を発光することのできる発光素子及びその製造方法を提供するところにある。

#### 【課題を解決するための手段】

#### 【0010】

上述した目的を達成するために、本発明は、基板の上にN型半導体層及び該N型半導体層の一部に形成されたP型半導体層を含む発光セルを多数備え、

前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層が接続され、前記発光セルのN型半導体層またはP型半導体層を含む側面が水平面から20~80°の勾配を有することを特徴とする発光素子を提供する。前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するための配線をさらに備えてもよい。前記P型半導体層の上に透明電極層をさらに備えてよく、前記P型半導体層及び前記N型半導体層の上にCrまたはAuを含むP型オーミック金属層及びN型オーミック金属層をそれぞれさらに備えてよい。

#### 【0011】

また、本発明は、N型半導体層及び該N型半導体層の上に形成されたP型半導体層を含む多数の発光セルが形成された基板と、前記基板がフリップチップボンディングされるサブマウント基板と、を備え、前記一方の発光セルのN型半導体層とそれに隣り合う他方の発

10

20

30

40

50

光セルのP型半導体層が接続され、前記発光セルの少なくともP型半導体層を含む側面が水平面から20～80°の勾配を有することを特徴とする発光素子を提供する。前記一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するための配線をさらに備えてよい。

#### 【0012】

本発明は、基板の上にN型半導体層及びP型半導体層を順次に形成するステップと、前記P型半導体層の上に側面が水平面から垂直ではなく所定の勾配を有するエッチングマスクパターンを形成するステップと、前記エッチングマスクパターンにより露出されたP型半導体層及び前記エッチングマスクパターンを除去するステップと、を含むことを特徴とする発光素子の製造方法を提供する。

10

#### 【0013】

前記P型半導体層の除去により露出されたN型半導体層の一部を除去して多数の発光セルを形成するステップと、導電性配線を介して一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するステップと、をさらに含んでいてよい。

#### 【0014】

また、前記P型半導体層及び前記エッチングマスクパターンを除去するステップ後に、前記基板を別のサブマウント基板にフリップチップボンディングするステップをさらに含んでいてよい。ここで、前記P型半導体層の除去により露出されたN型半導体層の一部を除去して多数の発光セルを形成するステップを含み、前記P型半導体層及び前記エッチングマスクパターンを除去するステップ後に、導電性配線を介して一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するステップをさらに含んでいてよい。

20

#### 【0015】

前記多数の発光セルを形成するステップは、前記P型半導体層の上に側面が水平面から垂直ではなく所定の勾配を有するエッチングマスクパターンを形成するステップと、前記エッチングマスクパターンにより露出されたP型半導体層及びN型半導体層を除去して多数の発光セルを形成するステップと、前記エッチングマスクパターンを除去するステップと、を含んでいてよい。

#### 【0016】

前記導電性配線は、ブリッジ工程またはステップカバレジ工程により一方の発光セルのN型半導体層とそれに隣り合う他方の発光セルのP型半導体層を接続するものであることを特徴とする。

30

#### 【0017】

前記エッチングマスクパターンを形成するステップにおいて、3～50μmの厚さの感光膜が用いられてもよい。前記エッチングマスクパターンを形成するステップは、前記P型半導体層の上に前記感光膜を塗布するステップと、所定のマスクパターンに応じて前記感光膜を露光するステップと、前記露光後に、ベーク工程を行うことなく現像を行うステップと、を含んでいてよい。また、前記エッチングマスクパターンを形成するステップは、前記P型半導体層の上に前記感光膜を塗布するステップと、所定のマスクパターンに応じて前記感光膜を露光するステップと、100～140°の温度下でハードベークを行うステップと、現像を行うステップと、を含んでいてよい。

40

#### 【0018】

前記P型半導体層及び前記エッチングマスクパターンを除去するステップ後に、前記基板の背面を所定の厚さだけ除去するステップと、前記基板の背面にAl、Ti、Ag、W、Ta、Ni、Ruまたはこれらの合金を蒸着するステップと、をさらに含んでいてよい。

#### 【発明の効果】

#### 【0019】

本発明による発光素子及びその製造方法によれば、水平面から垂直ではなく所定の勾配を有する半導体層の側面から発せられた光が全反射されずに発光素子の外部に放出されるこ

50

とから、さらに高い光取出効率、外部量子効率、発光効率などの特性が得られる。

**【図面の簡単な説明】**

**【0020】**

【図1】従来の発光素子を示す断面図。

【図2】従来の発光素子を示す断面図。

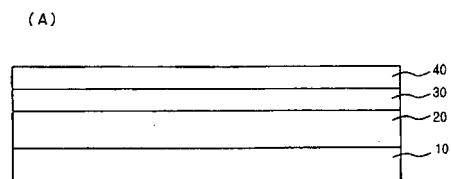

【図3】本発明による水平構造の発光素子を説明するための概念断面図。

【図4】A, Bは本発明による第1の実施形態の製造工程を説明するための断面図。

【図5】A～Dは本発明による第2の実施形態の製造工程を説明するための断面図。

【図6】A～Dは本発明による第3の実施形態の製造工程を説明するための断面図。

【図7】A～Dは本発明による第4の実施形態の製造工程を説明するための断面図。

10

【図8】本発明によるフリップチップ構造の発光素子を説明するための概念断面図。

【図9】A～Eは本発明による第5の実施形態の製造工程を説明するための断面図。

【図10】A～Eは本発明による第6の実施形態の製造工程を説明するための断面図。

【図11】本発明による第7の実施形態を示す断面図。

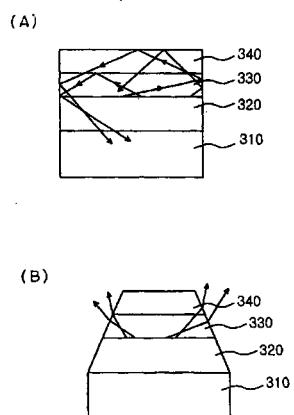

【図12】A, Bはそれぞれ従来の技術及び本発明による発光素子の効果を説明するための概念断面図。

**【発明を実施するための最良の形態】**

**【0021】**

以下、添付図面に基づき、本発明の好適な実施形態について詳細に説明する。しかし、本発明は後述する実施の形態に限定されるものではなく、相異なる形で実現可能であり、これららの実施の形態は、単に本発明の開示を完全たるものにし、且つ、この技術分野における通常の知識を持った者に発明の範疇を完全に報知するために提供されるものである。

20

**【0022】**

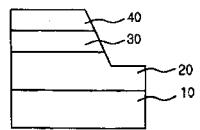

図3は、本発明による水平構造の発光素子を説明するための概念断面図である。

図3を参照すれば、発光素子は、基板10と、基板10の上に順次に形成されたN型半導体層20と、活性層30及びP型半導体層40を備えている。前記P型半導体層40と、活性層30及び所定の部分のN型半導体層20の側面は水平面から80～20°の勾配を有し、この側面から光の臨界角を変えて容易に光を取り出すことができるので、発光素子の発光効率を改善することができる。

**【0023】**

30

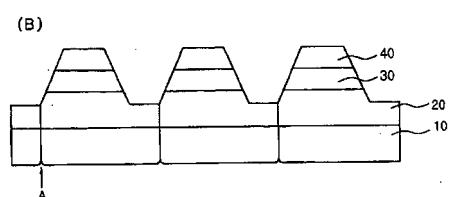

図4A及び図4Bは、本発明による第1の実施形態の製造工程を説明するための断面図である。

図4Aを参照すれば、基板10の上にN型半導体層20と、活性層30及びP型半導体層40を順次に形成する。

**【0024】**

基板10とは、発光素子を製作するための通常のウェーハを言い、Al<sub>2</sub>O<sub>3</sub>、SiC、ZnO、Si、GaAs、GaP、LiAl<sub>2</sub>O<sub>3</sub>、BN、AlN及びGaNのうち少なくともいずれか1種の基板10を用いる。この実施形態においては、サファイア製の結晶成長基板が用いられている。

**【0025】**

40

前記基板10の上に結晶を成長させるに際して基板10と後続層との間の格子不整合を低減するためのバッファ層(図示せず)をさらに形成してもよい。なお、バッファ層は、半導体材料としてのGaNまたはAlNを含めて形成してもよい。

**【0026】**

N型半導体層20は電子が生成される層であって、N型不純物が注入された窒化ガリウム(GaN)を用いることが好ましいが、本発明はこれに限定されるものではなく、種々の半導体性質を有する物質層が採用可能である。この実施形態においては、N型Al<sub>x</sub>Ga<sub>1-x</sub>N(0 < x < 1)を含むN型半導体層20を形成している。また、P型半導体層40は正孔が生成される層であって、P型不純物が注入された窒化ガリウム(GaN)を用いることが好ましいが、本発明はこれに限定されるものではなく、種々の半導体性質を有

50

する物質層が採用可能である。この実施形態においては、P型  $A_{1-x}G_{x}N$  ( $0 < x < 1$ ) を含むP型半導体層40を形成している。加えて、前記半導体層としてInGaNを用いてもよい。なお、上記のN型半導体層20及びP型半導体層40は多層膜であつてもよい。

#### 【0027】

活性層30は所定のバンドギャップを有し、且つ、量子井戸が形成されて電子及び正孔が再結合される領域であり、InGaNを含んでいてもよい。活性層30を構成する物質の種類に応じて、電子及び正孔が結合して得られる発光波長が変わる。このため、目標とする波長に応じて、活性層30に含まれる半導体材料を調節することが好ましい。

#### 【0028】

上述した物質層は、有機金属化学蒸着法(MOCVD: Metal Organic Chemical Vapor Deposition)、化学蒸着法(CVD: Chemical Vapor Deposition)、プラズマ化学蒸着法(PCVD: Plasma-enhanced Chemical Vapor Deposition)、分子線成長法(MBE: Molecular Beam Epitaxy)、水素化物気相成長法(HVPE: Hydride Vapor Phase Epitaxy)などをはじめとする種々の蒸着及び成長方法により形成される。

#### 【0029】

この後、所定のエッティング工程によりP型半導体層40及び活性層30の一部を除去してN型半導体層20の一部を露出させる。P型半導体層40の上にエッティングマスクパターンを形成した後、ドライまたはウェットエッティング工程を行うことによりP型半導体層40及び活性層30を除去してN型半導体層20を露出させる。

#### 【0030】

通常、前記エッティング工程を行うために、P型半導体層の上面に1~2μmの厚さにて感光膜を塗布した後、80~90℃の温度下でソフトベークを行う。次いで、所定のフォトマスクを介して紫外線(UV)領域の光を照射することにより、マスクの上に形成されたパターンを塗布された感光膜に転写するという露光工程を行う。この後、100~120℃の温度下でハードベークを行い、露光工程により相対的に結合が弱まっている個所の感光膜を溶剤を用いて溶け出すという現像工程を行う。これらの過程を経て前記P型半導体層40の上に所定のエッティングマスクパターンが形成される。

#### 【0031】

しかしながら、この実施形態においては、前記エッティングマスクパターンを形成するに当たって、従来に比べて厚目の3~50μmの厚さに感光膜を塗布し、ソフトベークを経て露光工程を行っている。その後、ハードベークを行うことなく直ちに現像すれば、残留している感光膜の現像された側面は水平面から垂直(90°)ではなく所定の勾配を有するような斜面を形成することになる。次いで、このような側面の勾配を有するエッティングマスクパターンを用いて露出された領域のP型半導体層40、活性層30、所定のN型半導体層20をエッティングすれば、エッティングされたP型半導体層40、活性層30、所定のN型半導体層20の側面は、上記と同様、水平面から垂直(90°)ではなく所定の勾配を有するような斜面が得られる。

#### 【0032】

すなわち、図4Aに示すP型半導体層40の上に3~50μmの厚さに感光膜を厚目に塗布して露光した後、ハードベークを行うことなく直ちに現像したエッティングマスクパターンを形成する。前記エッティングマスクパターンにより露出されたP型半導体層40、活性層30を誘導結合プラズマ(ICP: Inductive Coupled Plasma)またはドライエッティング工程により除去してN型半導体層20を露出させる。露出されたN型半導体層20の一部をさらに除去してもよい。この後、エッティングマスクパターンを除去すれば、図4Bに示すように、P型半導体層40、活性層30、一部のN型半導体層20の側面が水平面から垂直(90°)ではなく所定の勾配を有するような発光素子を製造することができる。

10

20

30

40

50

## 【0033】

また、図4Aに示すP型半導体層40の上に3～50μmの厚さに感光膜を厚目に塗布して露光した後、ハードベークを行う場合、ハードベークの温度を100～140にしてハードベークを行った後に現像を行うと、現像された感光膜の側面が水平面から80～20°の勾配を有するようにエッチングされた側面が得られる。例えば、100の温度下でハードベークを行う場合に、水平面から80°程度の勾配を有するエッチングマスクパターンが得られ、これを用いて、P型半導体層40、活性層30、一部のN型半導体層20の側面に水平面から80°程度の勾配を持たせることができる。さらに、140の温度下でハードベークを行う場合に、水平面から20°程度の勾配を有するエッチングマスクパターンが得られ、これを用いて、P型半導体層40、活性層30、一部のN型半導体層20の側面に水平面から20°程度の勾配を持たせることができる。10

## 【0034】

このようにして3～50μmの厚さの感光膜を露光した後、100～140の温度下でハードベークを行った後に現像したエッチングマスクパターンを用いることにより、エッチングされたP型半導体層40、活性層30、所定のN型半導体層20の側面が、上記と同様に、水平面から80～20°の勾配を有するようにエッチングされた側面が得られる。しかし、発光層の内部において生成された光は種々の勾配を有するようにエッチングされた側面に全反射されずに発光素子の外部に抜け出することになる。前記P型半導体層40の上部にP型半導体層40の抵抗を削減して透光率を高める目的で透明電極層をさらに形成してもよく、P型半導体層40または露出されたN型半導体層20の上部への電流の供給をスムーズに行うための別のオーミック金属層をさらに別設してもよい。前記透明電極層としては、ITO(Indium Tin Oxide)、ZnOまたは伝導性を有する透明金属が使用可能であり、前記オーミック金属層としては、Cr、Auが使用可能である。さらに、電圧を印加する目的で、P型半導体層40の上部にP型電極をさらに形成してもよく、N型半導体層20の上部にN型電極をさらに形成してもよい。20

## 【0035】

さらに、発光素子の放熱特性を高めるために、前記基板10の背面を所定の厚さだけ除去した後、Al、Ti、Ag、W、Ni、Ta、Ruまたはこれらの合金を基板10の背面に蒸着してもよい。

## 【0036】

図面から明らかなように、多数の発光素子を1枚の基板10の上に製作してもよく、この場合には、今後の使用に際し、多数の発光素子から個別の発光素子を切り出して用いる。このとき、図4BのA部はこれらの多数の発光素子から個別の発光素子を切り出すための切出部となる。

## 【0037】

これにより、P型半導体層40、活性層30、N型半導体層20の側面の一部が水平面から垂直ではなく所定の勾配を有するような発光素子を製造することが可能になる。

## 【0038】

上述した本発明の発光素子の製造工程は単なる例示に過ぎず、本発明はこれに限定されるものではなく、種々の工程及び製造方法が素子の特性及び工程の都合により変更または付加可能である。40

## 【0039】

図5Aから図5Dは、本発明による第2の実施形態の製造工程を説明するための断面図である。

本発明による第2の実施形態は、第1の実施形態とほとんど同様である。単に相違点があれば、第2の実施形態は、ウェーハのレベルで多数の発光セルを直列、並列または直並列など種々に接続して素子を小型化させ、適正な電圧及び電流に駆動して照明として使用可能である他、交流電源においても駆動可能な発光素子を提供するということである。以下では、上述した第1の実施形態と重なる部分の説明は省く。

## 【0040】

図5Aを参照すれば、有機金属化学蒸着法、化学蒸着法、プラズマ化学蒸着法、分子線成長法、水素化物気相成長法などの種々の蒸着方法により基板10の上にN型半導体層20、活性層30及びP型半導体層40を順次に形成する。前記基板10の上に結晶を成長させるに際して基板10と後続層との間の格子不整合を低減するためのバッファ層をさらに形成してもよい。

#### 【0041】

この後、所定のエッチング工程によりP型半導体層40及び活性層30の一部を除去してN型半導体層20の一部を露出させる。すなわち、図5Aに示すP型半導体層40の上に3～50μmの厚さに感光膜を厚目に塗布して露光した後、ハードベークを行うことなく直ちに現像してエッチングマスクパターンを形成する。前記エッチングマスクパターンにより露出されたP型半導体層40、活性層30を誘導結合プラズマまたはドライエッチング工程により除去してN型半導体層20を露出させる。露出されたN型半導体層20の一部をさらに除去してもよい。この後、エッチングマスクパターンを除去すれば、図5Bに示すように、P型半導体層40、活性層30、所定のN型半導体層20の側面が水平面から垂直(90°)ではなく所定の勾配を有するような斜面が得られる。

10

#### 【0042】

また、図5Aに示すP型半導体層40の上に3～50μmの厚さに感光膜を厚目に塗布して露光した後、100～140°の温度下でハードベークを行った後に現像してエッチングマスクパターンを形成してもよい。このエッチングマスクパターンにより露出されたP型半導体層40及び活性層30をエッチングした後、エッチングマスクパターンを除去してエッチングされたP型半導体層40及び活性層30の側面に80～20°の種々の勾配を持たせてもよい。

20

#### 【0043】

次いで、基板10の上に多数の発光セルを形成するために露出されたN型半導体層20の所定の領域を基板10が露出されるようにして除去する。このために、前記基板10が露出される所定の領域を除く全ての部分に所定のマスクパターンを形成した後、前記マスクパターンにより露出された領域のN型半導体層20をエッチングして、図5Cに示すように、多数の発光セルを電気的に絶縁する。このとき、上述した工程により側面が勾配を有するマスクパターンを形成してエッチングすることにより、多数の発光セルが分離されるN型半導体層20の側面が水平面から垂直ではなく種々の勾配を有するようにもできる。

30

#### 【0044】

図5Dを参照すれば、所定の配線形成工程により隣り合う発光セル間のN型半導体層20とP型半導体層40を接続する。すなわち、一方の発光セルの露出されたN型半導体層20とこれと隣り合う他方の発光セルのP型半導体層40を配線60を介して接続する。このとき、ブリッジ工程により隣り合う発光セルのN型半導体層20とP型半導体層40との間を電気的に接続する導電性配線60を形成する。

#### 【0045】

上述したブリッジ工程はエアブリッジ工程とも呼ばれ、互いに接続するチップ間にフォト工程を用いて感光液を塗布し且つ現像して感光膜パターンを形成し、先ずその上に金属などの物質を真空蒸着などの方法により薄膜として形成し、さらにその上に電気めっき、無電解めっきまたは金属蒸着などの方法により金を含む導電性物質を所定の厚さに塗布する。この後、ソルベントなどの溶液により感光膜パターンを除去すれば、導電性物質の下部は完全に除去されてブリッジ状の導電性物質のみが空間に形成される。

40

#### 【0046】

上記の配線60としては、金属に加えて、伝導性を有するあらゆる物質が使用可能である。もちろん、不純物によりドープされたシリコン化合物を用いることも可能である。

#### 【0047】

さらに、発光素子に外部より電圧を印加する目的で、一方の周縁に位置する発光セルのP型半導体層40にP型ボンディングパッド50を形成し、他方の周縁に位置する発光セルの露出されたN型半導体層20の上にN型ボンディングパッド55を形成する。

50

**【0048】**

上述した本発明の発光素子の製造工程は単なる例示に過ぎず、本発明はこれに限定されるものではなく、種々の変形及び種々の物質膜がさらに付加可能である。例えば、発光素子の放熱特性を高めるために、前記基板の背面を所定の厚さだけ除去した後、Al、Ti、Ag、W、Ta、Ni、Ruまたはこれらの合金を基板の背面に蒸着してもよい。

**【0049】**

これにより、P型半導体層40、活性層30、N型半導体層20の側面の一部が水平面から垂直ではなく所定の勾配を有するような発光セルが多数接続されてなる発光素子を製造することができる。

**【0050】**

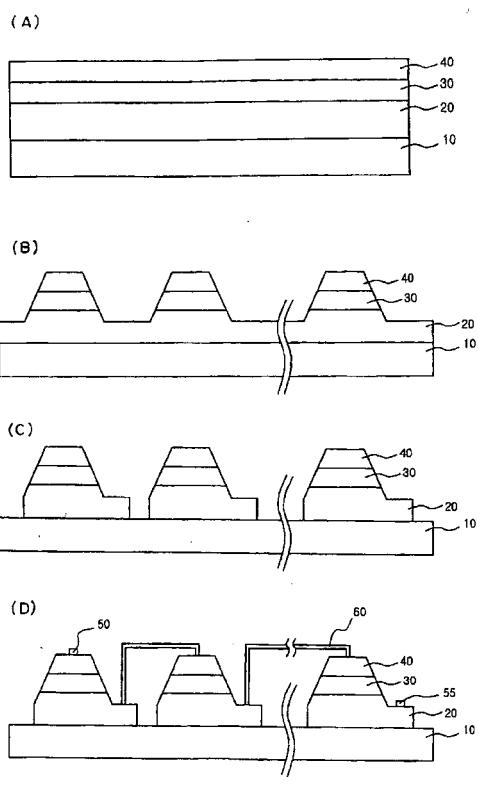

図6Aから図6Dは、本発明による第3の実施形態の製造方法を説明するための断面図である。

本発明による第3の実施形態は第2の実施形態とほとんど同様である。単に相違点があれば、第2の実施形態においては、先ず、N型半導体層20を露出させた後、発光セル間の分離のために露出されたN型半導体層20の一部を除去していたが、第3の実施形態においては、先ず、多数の発光セルを分離した後、N型半導体層20の一部を露出させているところにある。以下では、上記の第2の実施形態と重なる説明は省く。

**【0051】**

図6Aを参照すれば、基板10の上に順次に形成されたN型半導体層20、活性層30及びP型半導体層40の一部を除去して多数の発光セルを形成する。このために、P型半導体層40の上に3～50μmの厚さに感光膜を厚目に塗布して露光した後、ハードベークを行うことなく直ちに現像してエッチングマスクパターンを形成する。前記エッチングマスクパターンにより露出されたP型半導体層40、活性層30、所定のN型半導体層20と前記エッチングマスクパターンを除去して発光セルを分離する。そして、図面に示すように、P型半導体層40、活性層30、N型半導体層20の全ての側面が水平面から水平面から垂直(90°)ではなく所定の勾配を有するような斜面が得られる。また、P型半導体層40の上に3～50μmの厚さに感光膜を厚目に塗布して露光した後、100～140の温度下でハードベークを行った後に現像したエッチングマスクパターンを用いてP型半導体層40、活性層30、N型半導体層20を除去することにより、P型半導体層40、活性層30、N型半導体層20の全ての側面に80～20°の種々の勾配を持たせることもできる。

**【0052】**

この後、図6Bに示すように、所定のエッチング工程によりP型半導体層40及び活性層30の一部を除去してN型半導体層20の一部を露出させる。

**【0053】**

図6Cを参照すれば、ブリッジ工程により隣り合う発光セル間のN型半導体層20とP型半導体層40を接続する。

**【0054】**

また、発光素子に外部電圧を印加するために、一方の周縁に位置する発光セルのP型半導体層40にP型ボンディングパッド50を形成し、他方の周縁に位置する発光セルの露出されたN型半導体層20の上にN型ボンディングパッド55を形成する。

**【0055】**

上述した本発明の発光素子の製造工程は単なる例示に過ぎず、本発明はこれに限定されるものではなく、種々の変形及び物質膜がさらに付加可能である。例えば、発光素子の放熱特性を高めるために、前記基板の背面を所定の厚さだけ除去した後、Al、Ti、Ag、W、Ta、Ni、Ruまたはこれらの合金を基板の背面に蒸着させてよい。

**【0056】**

さらに、図6Aに示すように、側面が種々の勾配を有するようにエッチングして多数の発光セルを分離した後、N型半導体層20を露出させるためにエッチングする場合にも同じエッチング工程により発光素子を製造することができる。すなわち、図6Dに示すように

10

20

30

40

50

、N型半導体層20が露出されるようにエッティングされるP型半導体層40と活性層30の側面が種々の勾配を有するようになる。

**【0057】**

これにより、P型半導体層40、活性層30、N型半導体層20の全ての側面が水平面から垂直ではなく所定の勾配を有するような発光セルが多数接続されて得られる発光素子を製造することができる。

**【0058】**

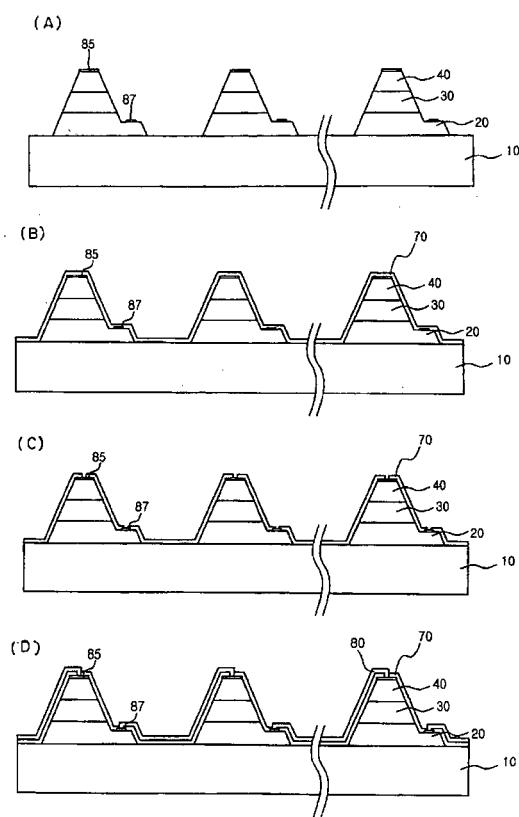

図7Aから図7Dは、本発明による第4の実施形態の製造方法を説明するための断面図である。

本発明による第4の実施形態は第3の実施形態とほとんど同様である。単に相違点があれば、第3の実施形態においては、ブリッジ工程により隣り合う発光セルのN型半導体層とP型半導体層を電気的に接続する導電性配線を形成していたが、第4の実施形態においては、ステップカバレジ工程により上記の導電性配線を形成するところにある。以下では、上記の第3の実施形態と重なる説明は省く。

**【0059】**

図7Aを参照すれば、上述した工程により側面が種々の勾配を有するようにエッティングして多数の発光セルを分離した後、N型半導体層20を露出させるためにエッティングする場合にも、N型半導体層20が露出されるようにエッティングされるP型半導体層40と活性層30の側面が種々の勾配を有するようにする。また、前記P型半導体層40の上部にP型半導体層40の抵抗を削減して透光率を高める目的で透明電極層85をさらに形成してもよく、P型半導体層40または露出されたN型半導体層20の上部への電流の供給をスムーズに行うための別のオーミック金属層87をさらに別設してもよい。前記透明電極層85としては、ITO、ZnOまたは伝導性を有する透明金属が使用可能であり、前記オーミック金属層87としては、Cr、Auが使用可能である。

**【0060】**

図7Bを参照すれば、多数の発光セルが形成された基板10の上面の全体に連続した絶縁層70を形成する。絶縁層70は、発光セルの側面及び上面を覆い、発光セル間の領域の基板10の上部を覆う。前記絶縁層70は、化学気相蒸着(CVD)技術を用いて、例えば、シリコン酸化膜から形成可能である。

**【0061】**

前記発光セルの側面が斜面となっているので、前記絶縁層70は発光セルの側面を容易に覆うことができる。N型半導体層20及び活性層30の全体の厚さが薄く、且つ、P型半導体層40間の空間が広いので、前記N型半導体層20の露出された領域に隣り合うP型半導体層40の側面も絶縁層70により容易に覆われる。

**【0062】**

図7Cを参照すれば、所定のエッティング工程により前記絶縁層70をパターニングして発光セルの露出されたN型半導体層20とP型半導体層40の上に開口部を形成する。同図に示すように、透明電極層85及び/またはオーミック金属層87を形成している場合、前記開口部により透明電極層85及び/またはオーミック金属層87が露出される。

**【0063】**

図7Dを参照すれば、前記開口部を有する絶縁層70の上に配線80が形成される。前記配線80は、前記開口部を介してN型半導体層20及びP型半導体層40に電気的に接続し、隣り合う発光セルのN型半導体層20とP型半導体層40をそれぞれ電気的に接続する。

**【0064】**

前記配線80はめっき技術により形成可能である。すなわち、前記絶縁層70の上に配線80領域を限定する開口部を有するエッティングマスクパターンを形成し、前記開口部内に金属層をめっきした後、前記エッティングマスクパターンを除去することにより、配線80を形成することができる。

**【0065】**

10

20

30

40

50

さらに、前記配線 80 は、化学気相蒸着または物理気相蒸着技術により形成されてもよい。すなわち、電子ビーム蒸着などの気相蒸着技術により金属層を形成した後、これを写真及びエッチング工程を用いてパターニングすることにより配線を形成することができる。前記発光セルの側面が斜面となっているので、金属層は発光セルの側面の上部に連設される。

#### 【 0 0 6 6 】

このような方法により配線 80 が形成された発光素子は、外圧により配線 80 が短線または短絡されることを防ぐことができ、配線 80 を形成する間に残存する金属などの導電性物質が発光セルを短絡させることを防止できるというメリットがある。

#### 【 0 0 6 7 】

これにより、P 型半導体層 40 、活性層 30 、N 型半導体層 20 の全ての側面が水平面から垂直ではなく所定の勾配を有するような発光セルが多数接続されて得られる発光素子を製造することができる。

#### 【 0 0 6 8 】

上述したように、本発明による発光素子は、P 型半導体層、活性層、N 型半導体層の一部側面が水平面から垂直ではなく所定の勾配を有することにより、従来の発光素子に比べて発光効率を高めることができる。これは、従来の平らな表面において反射されていた光子が様々な角の表面により反射されずに外部に抜け出るためである。

#### 【 0 0 6 9 】

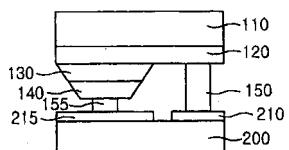

図 8 は、本発明によるフリップチップ構造の発光素子を説明するための概念断面図である。

図 8 を参照すれば、ベース基板 110 の上に順次に形成された発光層、すなわち、N 型半導体層 120 、活性層 130 及び P 型半導体層 140 を備え、さらに、金属バンプ 150 、155 を用いて前記発光層が形成されたベース基板 110 とフリップチップボンディングされるサブマウント基板 200 を備える。前記 P 型半導体層 140 、活性層 130 及び N 型半導体層 120 を備える発光層の側面は水平面から 20 ~ 80 ° の勾配を有し、この側面から光の臨界角を変えて容易に光を取り出すことができ、発光素子の発光効率を改善することができる。

#### 【 0 0 7 0 】

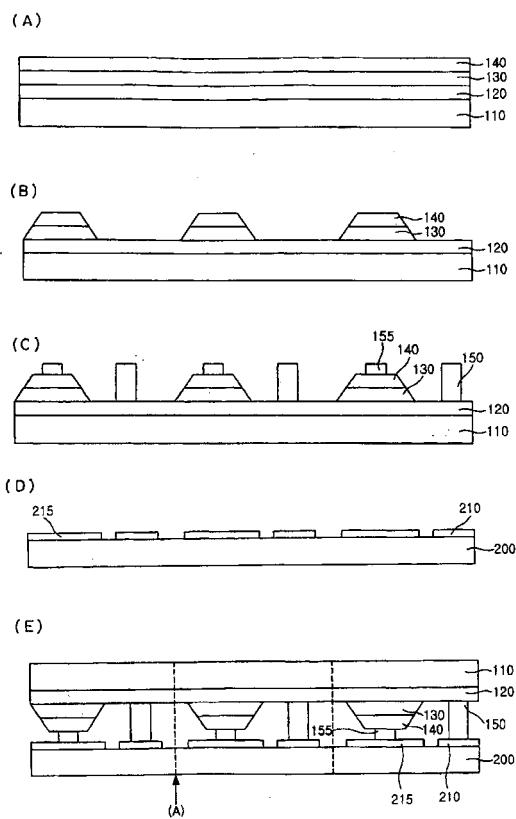

図 9A から図 9E は、本発明による第 5 の実施形態の製造工程を説明するための断面図である。

図 9A を参照すれば、ベース基板 110 の上に N 型半導体層 120 、活性層 130 及び P 型半導体層 140 を順次に形成する。

ベース基板 110 とは、発光素子を製作するための通常のウェーハを言い、Al<sub>2</sub>O<sub>3</sub> 、ZnO 、LiAl<sub>2</sub>O<sub>3</sub> などの透明基板を用いる。この実施形態においては、サファイア製の透明な結晶成長基板が用いられている。

#### 【 0 0 7 1 】

有機金属化学蒸着法、化学蒸着法、プラズマ化学蒸着法、分子線成長法、水素化物気相成長法などの種々の蒸着方法により前記ベース基板 110 の上に N 型半導体層 120 、活性層 130 及び P 型半導体層 140 を順次に形成する。前記基板 110 の上に結晶を成長させるに際して基板 110 と後続層との間の格子不整合を低減するためのバッファ層をさらに形成してもよい。これは上述した通りであるため、以下では重なる説明は省く。

#### 【 0 0 7 2 】

この後、所定のエッチング工程により P 型半導体層 140 及び活性層 130 の一部を除去して N 型半導体層 120 の一部を露出させる。これは、上述した実施形態と同様にして行う。

#### 【 0 0 7 3 】

すなわち、図 9A に示す P 型半導体層 140 の上に 3 ~ 50 μm の厚さに感光膜を厚目に塗布して露光した後、ハードベークを行うことなく直ちに現像してエッチングマスクパターンを形成する。前記エッチングマスクパターンにより露出された P 型半導体層 140 、

10

20

30

40

50

活性層 130 を誘導結合プラズマまたはドライエッチング工程により除去して N 型半導体層 120 を露出させる。この後、エッチングマスクパターンを除去すれば、図 9B に示すように、P 型半導体層 140 、活性層 130 の側面が垂直 (90°) ではなく所定の勾配を有するような斜面が得られる。

#### 【 0074 】

また、図 9A に示す P 型半導体層 140 の上に 3 ~ 50 μm の厚さに感光膜を厚目に塗布して露光した後、100 ~ 140 の温度下でハードベークを行った後に現像してエッチングマスクパターンを形成してもよい。このようなエッチングマスクパターンにより露出された P 型半導体層 140 及び活性層 130 をエッチングした後、エッチングマスクパターンを除去してエッチングされた P 型半導体層 140 及び活性層 130 の側面が水平面から 80 ~ 20° の種々の勾配を有するようにもできる。10

#### 【 0075 】

前記 P 型半導体層 140 の上部に光の反射のための反射層をさらに形成してもよく、P 型半導体層 140 または露出された N 型半導体層 120 の上部への電流の供給をスムーズに行うための別のオーミック金属層をさらに別設してもよい。前記オーミック金属層としては、Cr 、 Au が使用可能である。

#### 【 0076 】

さらに、図 9C に示すように、P 型半導体層 140 の上に P 型金属バンプ 155 を、N 型半導体層 120 の上に N 型金属バンプ 150 をバンピング用として形成する。P 型及び N 型金属バンプ 155 、 150 としては、Pb 、 Sn 、 Au 、 Ge 、 Cu 、 Bi 、 Cd 、 Zn 、 Ag 、 Ni 及び Ti のうち少なくともいずれか 1 種が使用可能であり、これらの合金も使用可能である。このために、全体の構造の上に感光膜を塗布した後、所定のマスクを用いた写真エッチング工程を行うことにより、P 型半導体層 140 と N 型半導体層 120 の一部を露出させた感光膜パターン（図示せず）を形成する。全体の構造の上に金属膜を蒸着した後、前記感光膜パターンにより露出された P 型半導体層 140 の上部に形成された金属膜と、N 型半導体層 120 の上部に形成された金属膜を除く残りの領域の金属膜及び前記感光膜パターンを除去する。これにより、P 型半導体層 140 の上には P 型金属バンプ 155 が形成され、N 型半導体層 120 の上には N 型金属バンプ 150 が形成される。20

#### 【 0077 】

次いで、図 9D を参照すれば、別のサブマウント基板 200 を設けて前記 P 型金属バンプ 155 及び N 型金属バンプ 150 にそれぞれ接続される P 型ボンディングパッド 215 及び N 型ボンディングパッド 210 を形成する。30

#### 【 0078 】

このとき、サブマウント基板 200 としては、熱伝導性に優れた種々の基板 200 を用いる。すなわち、SiC 、 Si 、 Ge 、 SiGe 、 AlN 、金属などを用いる。この実施形態においては、熱伝導性に優れ、且つ、絶縁性を有する AlN が用いられている。もちろん、本発明はこれに限定されるものではなく、熱伝導率が高く、且つ、電気伝導性に優れた金属性物質を用いることができる。この場合には、基板 200 の上に絶縁膜誘電体膜を形成して十分な絶縁を行わせる。誘電体膜としては、SiO<sub>2</sub> 、 MgO 及び SiN または絶縁性物質が使用可能である。また、前記 N 型ボンディングパッド 210 及び P 型ボンディングパッド 215 は、電気伝導性に優れた金属を用いて形成する。なお、これは、スクリーン印刷法により形成するか、あるいは、所定のマスクパターンを用いた蒸着工程により形成する。40

#### 【 0079 】

この後、前記サブマウント基板 200 及び前記発光層が形成されたベース基板 110 をフリップチップボンディングする。

#### 【 0080 】

図 9E を参照すれば、本発明の発光素子は、発光層の上部に形成された N 型及び P 型金属バンプ 150 、 155 とサブマウント基板 200 の N 型及び P 型ボンディングパッド 21 50

0、215が接続されるようにしてボンディングされる。このとき、熱及び超音波のいずれか一方、あるいは、これらの両方を用いてボンディングを行うことができる。金属バンプ150、155と下部ボンディングパッド210、215との接続は、種々のボンディング方法により行われる。

加えて、発光層の上部に必ずしもN型及びP型金属バンプ150、155が形成されるわけではなく、サブマウント基板200の上にそれぞれの金属バンプが形成されてもよい。

#### 【0081】

図面から明らかなように、多数の発光素子を1枚の基板の上に製作してもよく、この場合、今後の使用に際して多数の発光素子から個別の発光素子を切り出して用いる。このとき、図9EのA部は、これらの多数の発光素子から個別の発光素子を切り出すための切出部となる。10

#### 【0082】

上述した本発明の発光素子の製造工程は単なる例示に過ぎず、本発明はこれに限定されるものではなく、種々の工程と製造方法が素子の特性及び工程の都合に応じて変形あるいは付加可能である。例えば、上記と同じ工程において、図9Aに示すように、N型半導体層、活性層、P型半導体層が順次に形成されたベース基板を形成し、まず、基板が露出されるように前記P型半導体層、活性層、N型半導体層の一部を除去して多数の発光素子を個別に分離することができる。このとき、上述した工程によりエッチングされるP型半導体層、活性層、N型半導体層の側面を水平面から垂直ではなく所定の勾配を有するように形成してもよい。20

#### 【0083】

これにより、P型半導体層、活性層、N型半導体層側面の一部が水平面から垂直ではなく所定の勾配を有するようなフリップチップ構造の発光素子を製造することができる。

#### 【0084】

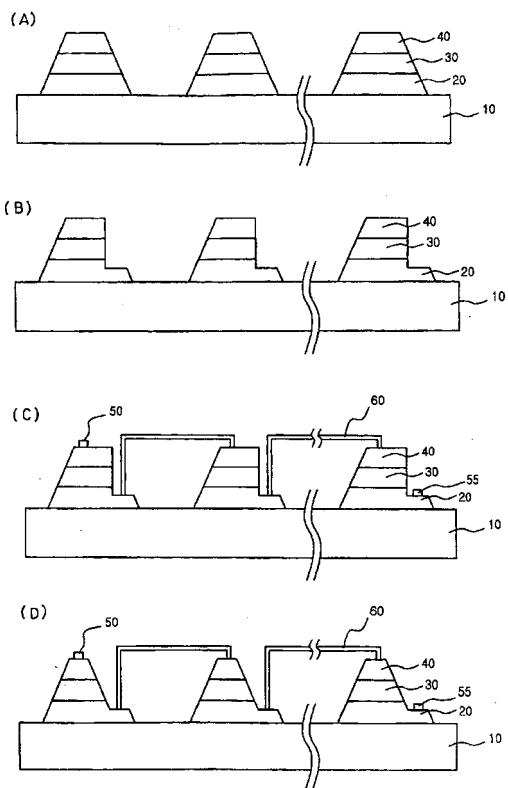

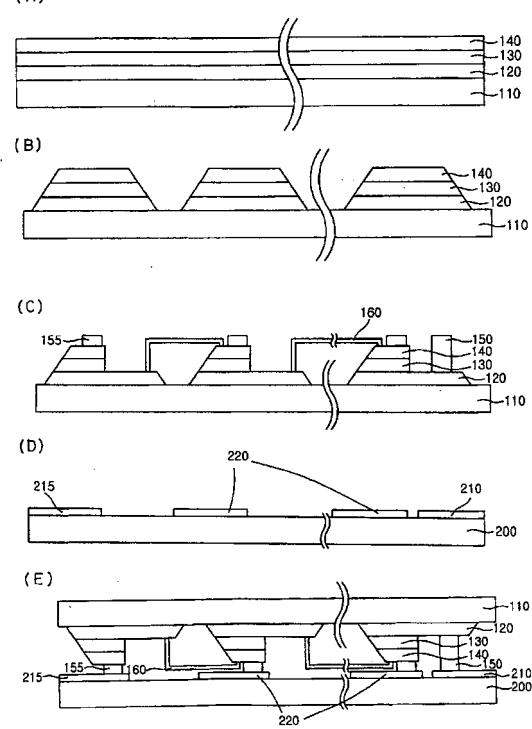

図10Aから図10Eは、本発明による第6の実施形態の製造工程を説明するための断面図である。

本発明による第6の実施形態は第5の実施形態とほとんど同様である。単に相違点があれば、第6の実施形態においては、ウェーハのレベルで多数の発光セルを直列、並列または直並列など種々に接続して素子を小型化させ、適正な電圧及び電流に駆動して照明として使用可能であり、交流電源においても駆動可能なフリップチップ構造の発光素子を提供することである。以下では、上述した実施形態と重なる説明は省く。30

#### 【0085】

図10Aを参照すれば、有機金属化学蒸着法、化学蒸着法、プラズマ化学蒸着法、分子線成長法、水素化物気相成長法などの種々の蒸着方法によりベース基板110の上にN型半導体層120、活性層130及びP型半導体層140を順次に形成する。前記ベース基板110の上に結晶を成長させるに際して基板110と後続層との間の格子不整合を低減するためのバッファ層をさらに形成してもよい。

#### 【0086】

この後、前記ベース基板110の上に順次に形成されたN型半導体層120、活性層130及びP型半導体層140の一部を除去して多数の発光セルを形成する。このために、図10Aに示すP型半導体層140の上に3～50μmの厚さに感光膜を厚目に塗布して露光した後、ハードベークを行うことなく直ちに現像してエッチングマスクパターンを形成する。前記エッチングマスクパターンにより露出されたP型半導体層140、活性層130、所定のN型半導体層120を誘導結合プラズマまたはドライエッチング工程により除去して発光セルを分離する。次いで、エッチングマスクパターンを除去すれば、図10Bに示すように、エッチングされたP型半導体層140、活性層130、N型半導体層120の全ての側面が水平面から垂直(90°)ではなく所定の勾配を有するような斜面が得られる。

#### 【0087】

また、図10Aに示すP型半導体層140の上に3～50μmの厚さに感光膜を厚目に塗50

布して露光した後、100～140の温度下でハードベークを行った後に現像してエッチングマスクパターンを形成してもよい。このようなエッチングマスクパターンにより露出されたP型半導体層140、活性層130、N型半導体層120をエッチングした後、エッチングマスクパターンを除去してエッチングされたP型半導体層140及び活性層130の側面に80～20°の種々の勾配を持たせることもできる。

#### 【0088】

次いで、図10Cに示すように、所定のエッチング工程によりP型半導体層140及び活性層130の一部を除去してN型半導体層120の一部を露出させる。所定の導電性配線を介して一方の発光セルの露出されたN型半導体層120と隣り合う他方の発光セルのP型半導体層140を接続する。このとき、ブリッジ配線160は導電性の物質を用いて形成するが、金属を用いて形成する。もちろん、不純物によりドープされたシリコン化合物を用いることもできる。前記ブリッジ配線160はブリッジ工程により形成される。

10

#### 【0089】

さらに、各発光セルの上部にバンピング用に多数の金属バンプを形成し、一方の周縁に位置する発光セルのP型半導体層140と他方の周縁に位置する発光セルのN型半導体層120の上にそれぞれP型金属バンプ155及びN型金属バンプ150をさらに形成する。

#### 【0090】

次いで、図10Dに示すように、別のサブマウント基板200を設けて、基板200の上部に多数のボンディング層220と、サブマウント基板200の一方の周縁に位置するP型ボンディングパッド215と、他方の周縁に位置するN型ボンディングパッド210と、を形成する。

20

#### 【0091】

この後、図10Eに示すように、上述した多数の発光セルが形成されたベース基板110とサブマウント基板200をフリップチップボンディングして発光素子を製作する。前記発光セルの上部に形成された金属バンプ150、155と前記サブマウント基板200に形成されたボンディング層220を介してボンディングを行う。サブマウント基板200の一方の周縁に位置するP型ボンディングパッド215は一方の周縁に位置する発光セルのP型金属バンプ155に接続され、他方の周縁に位置するN型ボンディングパッド210は他方の周縁に位置する発光セルのN型半導体層150に接続される。

30

#### 【0092】

上述した本発明の発光素子の製造方法はこれに限定されるものではなく、種々の工程と製造方法が素子の特性及び工程の都合に応じて変形または付加可能である。例えば、この実施形態においては、ブリッジ工程を介して隣り合う発光セルのN型半導体層とP型半導体層を電気的に接続する導電性配線を形成した後、サブマウント基板とフリップチップボンディングを行っているが、本発明はこれに限定されるものではなく、前記第4の実施形態と同じステップカバレジ工程により隣り合う発光セルのN型半導体層とP型半導体層を電気的に接続する導電性配線を形成してもよい。また、多数の発光セルとサブマウント基板のフリップチップボンディング時にサブマウント基板に電極層を形成し、金属バンプを介して隣り合う発光セルのN型半導体層とP型半導体層を電気的に接続してもよい。

40

#### 【0093】

これにより、発光層の側面が水平面から垂直ではなく所定の勾配を有するような多数のフリップチップ状の発光セルがサブマウント基板の上にアレイされた発光素子を製造することができる。前記発光セルは、目的に応じて、直列、並列または直並列など種々に種々に接続可能である。

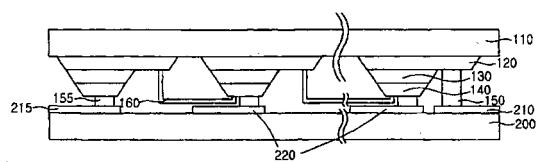

#### 【0094】

図11は、本発明による第7の実施形態を示す断面図である。

本発明による第7の実施形態は第6の実施形態とほとんど同様である。単に相違点があれば、第7の実施形態においては、図10Bに示すように、側面が種々の勾配を有するようにエッチングして多数の発光セルを分離した後、N型半導体層を露出させるためにエッチングする場合にも、同じエッチング工程を用いて発光素子を製造できることである。すな

50

わち、図11に示すように、N型半導体層120が露出されるようにエッティングされるP型半導体層140と活性層130の側面が種々の勾配を有するようになる。

#### 【0095】

これにより、発光層の全ての側面が水平面から垂直ではなく所定の勾配を有するような多数のフリップチップ状の発光セルがサブマウント基板の上にアレイされた発光素子を製造することができる。前記発光セルは、目的に応じて、直列、並列または直並列など種々に種々に接続可能である。

#### 【0096】

上述したように、本発明は、フリップチップ構造の発光素子において、発光層の一部の側面が水平面から垂直ではなく所定の勾配を有するようにすることにより、従来の発光素子に比べて発光効率を高めることができる。これは、従来の平らな表面において反射されていた光子が様々な角の表面により反射されずに外部に抜け出るためである。10

#### 【0097】

図12A及び図12Bは、それぞれ従来の技術及び本発明による発光素子の効果を説明するための概念断面図である。

#### 【0098】

発光素子の光効率は、内部量子効率と外部量子効率とに大別できるが、内部量子効率は、活性層の設計や品質により決まる。外部量子効率の場合、活性層において生成される光子が発光素子の外部に放出される量によって決まる。図12Aは、従来の技術による発光素子を示している。同図を参照すれば、半導体層の側面が水平面から垂直に形成される場合に、一部の光子が半導体層の側面を透過できずにそこから反射され、全反射された光は外部に透過できずに発光素子の内部において消滅してしまう。これに対し、本発明による発光素子を示している図12Bを参照すれば、半導体層の側面が水平面から垂直ではなく所定の勾配を有する場合に、所定の勾配を有する側面が光の臨界角を変えてより容易に光を取出可能に助長する。このため、活性層から発せられた光が全反射されずに発光素子の外部に放出される確率が高くなり、外部量子効率が格段に上がる結果となる。20

#### 【0099】

以上、本発明による発光素子及びその製造方法について説明したが、これは単なる例示的なものに過ぎず、本発明はこれらに限定されるものではない。なお、特許請求の範囲において請求するように、本発明の要旨を逸脱することなく、この技術分野における通常の知識を持った者であれば誰でも種々の変更実施が行える範囲まで本発明の技術的な精神があると言えるであろう。30

#### 【産業上の利用可能性】

#### 【0100】

以上説明したように、本発明による発光素子及びその製造方法によれば、水平面から垂直ではなく所定の勾配を有する半導体層の側面から発せられた光が全反射されずに発光素子の外部に放出されることから、さらに高い光取出効率、外部量子効率、発光効率などの特性が得られる。また、本発明の発光素子は、高光度、高輝度の光を発光するものであって、優れた光特性が求められる種々の製品分野に応用可能であるというメリットがある。

#### 【符号の説明】

#### 【0101】

- 10、110：基板、

- 20、120：N型半導体層、

- 30、130：活性層、

- 40、140：P型半導体層、

- 50、55：ボンディングパッド、

- 60、160：配線、

- 200：サブマウント基板、

- 210、215：金属バンプ、

- 220：ボンディング層

40

30

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(31)優先権主張番号 10-2006-0021801

(32)優先日 平成18年3月8日(2006.3.8)

(33)優先権主張国 韓国(KR)

前置審査

(72)発明者 イ , ジェホ

4 4 8 - 5 3 1 , 大韓民国 , ギヨンギ - ド , ヨンイン - シ , スジ - グ , ソンボク - ドン , エルジー -

3 チャビレッジアパート , 3 0 9 - 1 4 0 5

(72)発明者 ユン , ヨジン

4 2 6 - 7 3 8 , 大韓民国 , ギヨンギ - ド , アンサン - シ , サンノク - グ , サイル - ドン , ヨジン

スプソクアパート , 1 0 1 - 1 5 0 5

(72)発明者 フアン , ウイジン

4 2 9 - 8 5 6 , 大韓民国 , ギヨンギ - ド , シフン - シ , ジヨンワン - ドン , 1 5 6 9 - 7 - 3 0

3

(72)発明者 キム , デウォン

1 3 6 - 1 1 0 , 大韓民国 , ソウル ソンブク - グ , ギルウン - ドン , ギルウンニュータウン , 3

0 3 - 8 0 2

審査官 下村 一石

(56)参考文献 特開2001-168383(JP, A)

特開2003-347589(JP, A)

特開平06-318731(JP, A)

特開2003-031858(JP, A)

特開2001-217467(JP, A)

特開2005-079550(JP, A)

(58)調査した分野(Int.Cl. , DB名)

H 01 L 33 / 00 - 33 / 64