(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4836112号

(P4836112)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

(51) Int.Cl.

F 1

H01L 21/31 (2006.01)

H01L 21/31

B

C23C 16/44 (2006.01)

C23C 16/44

J

H01L 21/3065 (2006.01)

H01L 21/302

1 O 1 H

請求項の数 4 (全 11 頁)

(21) 出願番号

特願2004-374107 (P2004-374107)

(22) 出願日

平成16年12月24日 (2004.12.24)

(65) 公開番号

特開2006-179834 (P2006-179834A)

(43) 公開日

平成18年7月6日 (2006.7.6)

審査請求日

平成19年10月30日 (2007.10.30)

(73) 特許権者 504132272

国立大学法人京都大学

京都府京都市左京区吉田本町36番地1

(73) 特許権者 000231235

大陽日酸株式会社

東京都品川区小山一丁目3番26号

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100108578

弁理士 高橋 詔男

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100101465

弁理士 青山 正和

最終頁に続く

(54) 【発明の名称】半導体処理装置のクリーニング方法およびシリコン基板のエッティング方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物または付着物を除去する半導体処理装置のクリーニング方法であって、

酸素と、B C 1<sub>3</sub>とを混合させた混合ガスを、載置電極にバイアス電圧を印加しないプラズマ処理または加熱処理により活性化し、前記堆積物または付着物を除去することを特徴とする半導体処理装置のクリーニング方法。

## 【請求項2】

前記混合ガス中の酸素添加量が、1～10%であることを特徴とする請求項1記載の半導体処理装置のクリーニング方法。

10

## 【請求項3】

シリコン基板上に成膜した高誘電率酸化物をエッティングする方法であって、

酸素と、B C 1<sub>3</sub>とを混合させた混合ガスを、載置電極にバイアス電圧を印加しないプラズマ処理または加熱処理により活性化し、前記高誘電率酸化物をエッティングすることを特徴とするシリコン基板のエッティング方法。

## 【請求項4】

前記混合ガス中の酸素添加量が、1～10%であることを特徴とする請求項3記載のシリコン基板のエッティング方法。

## 【発明の詳細な説明】

## 【技術分野】

20

**【0001】**

本発明は、半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物または付着物を除去する半導体処理装置のクリーニング方法およびシリコン基板上に成膜した高誘電率酸化物をエッティングする方法に関するものである。

**【背景技術】****【0002】**

従来からの電界効果トランジスタのゲート絶縁膜としては、二酸化ケイ素(SiO<sub>2</sub>)、オキシ窒化ケイ素(SiON)、または窒化ケイ素(Si<sub>3</sub>N<sub>4</sub>)などが広く使用されてきた。しかしながら、デバイスの高性能化・高機能化により、デバイスの加工サイズの微細化が進み、それに伴いゲート絶縁膜の厚さを薄くして、一定のゲート容量を確保すると共に駆動電圧を低減して、トランジスタの高速化・高性能化・低消費電力化を図ろうとする試みがなされている。10

**【0003】**

現在、ゲート絶縁膜の膜厚は数ナノメートル以下になっており、絶縁性を保持する限界の膜厚になり、ゲートリーク電流増大といった重大な問題が生じている。このような問題の解決策として、従来からの酸化ケイ素よりも比誘電率の高い、高誘電率酸化物からなる膜をゲート絶縁膜に用いる試みがなされている。最近、開発された高誘電率酸化物からなる絶縁膜としては、HfO<sub>2</sub>、HfSi<sub>y</sub>O<sub>z</sub>、HfAl<sub>y</sub>O<sub>z</sub>、HfSiAl<sub>y</sub>O<sub>z</sub>などのハフニウムを含むものを挙げることができる。20

**【0004】**

これらの高誘電率酸化物は、化学気相堆積(CVD)法、原子層堆積(ALD)法により基板上に成膜される。この高誘電率酸化物は、処理室(チャンバー)の所定箇所に配置されている基板上にのみ成膜されるのが望ましいが、実際にはチャンバー内壁面や基板を載置する基板ホルダ周辺等に付着・堆積してしまう問題があった。

**【0005】**

その結果、この付着物・堆積物が、ガス流れ等による巻き上がりで剥離し、パーティクルとなって成膜中の基板上に付着し、デバイス製品の欠陥あるいは半導体処理装置の故障原因となるおそれがあった。

**【0006】**

これを防止するため、半導体処理装置のチャンバー内を周期的にクリーニングする必要がある。チャンバーをクリーニングする方法としては、機械的なクリーニングがあるが、手間と時間がかかるだけでなくチャンバー内壁面に損傷を与えてしまう可能性があり好ましくない。30

**【0007】**

そこで、塩素系ガスを使いプラズマ処理または加熱処理により、チャンバーを開放することなく、チャンバー内に付着・堆積したハフニウム等の遷移金属、アルミニウム等の第13族金属化合物を、化学的にドライクリーニングする方法が提案されている(例えば、特許文献1参照)。

**【0008】**

この特許文献1では、ハロゲン系ガスをメインに使用してクリーニングする際に、過剰の酸素を与えると、金属塩化物を金属酸化物へ転化させてしまうので、好ましいクリーニングが行なえないことが記載されている。40

**【0009】**

また、ゲートstackプロセスにおいては、ゲートstack形成後、コンタクト形成のために、トランジスタのソース・ドレイン領域上の上記高誘電率酸化物からなるゲート絶縁膜をエッティングにより除去する必要がある。高誘電率酸化物の厚さは数ナノメートル以下であるため、エッティング速度は問題とはならず、むしろ高誘電率酸化物の下地であるシリコン基板とのエッティングの選択性が重要となる。

**【0010】**

具体的には、高誘電率酸化物とシリコン基板との選択性(高誘電率酸化物/Si)が150

を超える高選択性のプロセスが求められている。ハロゲン系ガスのプラズマ処理によるエッティングが試みられているが、選択比が1を超えないのが現状である。

【特許文献1】特開2004-146787号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、特許文献1に係るクリーニング方法にあっては、チャンバー内壁を加熱処理するサーマルクリーニングの場合には、とりわけエッティング速度が小さく、また、バイアス電圧をかけないプラズマクリーニングやプラズマとサーマルの両方で操作するクリーニングの場合でも、エッティング速度を充分に大きくできない問題があった。

10

【0012】

また、特許文献1では、過剰の酸素を防止するため、酸素欠乏条件でクリーニングすることを奨めている。しかしながら、本発明者らの研究によれば、BCl<sub>3</sub>ガス単体でクリーニングすると、目的とする高誘電率酸化物は除去できても、BやSi等を含んだ他の化合物などがチャンバー内に堆積することがわかっている。したがって、酸素欠乏条件下でクリーニングするのが最適であるとは言えない。

【0013】

また、シリコン基板上に成膜した高誘電率酸化物をエッティングする場合、上述したように、高誘電率酸化物とシリコン基板との選択比が1を超えない問題があり、シリコン基板のエッティングを可能な限り抑えた高誘電率酸化物のエッティング方法が求められている。

。

20

【0014】

本発明は、上記従来技術の問題点に鑑み、半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物・付着物を高速で除去でき、かつ他の化合物による堆積物の生成を防止した半導体処理装置のクリーニング方法を提供することを目的とする。

【0015】

また、本発明は、シリコン基板上に成膜した高誘電率酸化物を、選択比が1を超える高い選択性をもってエッティング可能なシリコン基板のエッティング方法を提供することを目的とする。

【課題を解決するための手段】

30

【0016】

かかる課題を解決するため、

請求項1にかかる発明は、半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物または付着物を除去する半導体処理装置のクリーニング方法であって、酸素と、BCl<sub>3</sub>とを混合させた混合ガスを、載置電極にバイアス電圧を印加しないプラズマ処理または加熱処理により活性化し、前記堆積物または付着物を除去することを特徴とする半導体処理装置のクリーニング方法である。

【0017】

請求項2にかかる発明は、前記混合ガス中の酸素添加量が、1～10%であることを特徴とする請求項1記載の半導体処理装置のクリーニング方法である。

40

【0025】

請求項3にかかる発明は、シリコン基板上に成膜した高誘電率酸化物をエッティングする方法であって、酸素と、BCl<sub>3</sub>とを混合させた混合ガスを、載置電極にバイアス電圧を印加しないプラズマ処理または加熱処理により活性化し、前記高誘電率酸化物をエッティングすることを特徴とするシリコン基板のエッティング方法である。

請求項4にかかる発明は、前記混合ガス中の酸素添加量が、1～10%であることを特徴とする請求項8記載のシリコン基板のエッティング方法である。

【発明の効果】

【0026】

本発明のクリーニング方法によれば、酸素原子供与性ガスまたは酸化性ガスをハロゲン

50

系ガスに混合して使用することにより、半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物・付着物を高速で除去することができ、かつ他の化合物による堆積物の生成を防止することができる。

#### 【0027】

また、本発明のエッティング方法によれば、酸素原子供与性ガスまたは酸化性ガスをハロゲン系ガスに混合して使用することにより、バイアス電圧を印加することなく、シリコン基板上に成膜した高誘電率酸化物を、選択比が1を超える高い選択性をもってエッティングすることができる。

#### 【発明を実施するための最良の形態】

#### 【0028】

10

#### [クリーニング方法]

本発明に係る半導体処理装置のクリーニング方法とは、半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物または付着物を除去するものである。

#### 【0029】

このような高誘電率酸化物としては、 $HfO_z$ 、 $ZrO_z$ 、 $Al_yO_z$ 、 $HfSi_yO_z$ 、 $HfAl_yO_z$ 、 $HfSiAl_yO_z$ 、 $ZrSi_yO_z$ 、 $ZrAl_yO_z$ （yおよびzは、0より大きい整数または少数）などのハフニウム、アルミニウム、ジルコニウムを含む酸化物が挙げられる。そのなかでも、 $HfO_z$ 、 $ZrO_z$ 、 $Al_yO_z$ 、 $HfSi_yO_z$ 、 $HfAl_yO_z$ 、 $ZrSi_yO_z$ 、および $ZrAl_yO_z$ （yおよびzは、0より大きい整数または少数）からなる群から選択される一種以上の酸化物であるのが好ましい。ここで、yおよびzは、0より大きい整数または少数であり、上記高誘電率酸化物には、化学量論的組成のものだけでなく、非化学量論的組成のものも含まれる。

20

#### 【0030】

また、上記高誘電率酸化物が、さらに分子内に窒素を含有するものであってもよい。例えば、 $HfO_bN_c$ 、 $HfSi_aO_bN_c$ 、 $HfAl_aO_bN_c$ （a、b、およびcは、0より大きい整数または少数）などが挙げられる。

#### 【0031】

半導体処理装置のチャンバー内に生成した堆積物または付着物とは、これらの高誘電率酸化物を含有するものであり、さらにSiやCを含有する場合もある。

#### 【0032】

30

また、本発明に係る半導体処理装置のクリーニング方法とは、酸素原子供与性ガスまたは酸化性ガスのいずれかと、ハロゲン系ガスとを混合させたガスを、プラズマ処理または加熱処理により活性化し、上記堆積物または付着物を除去するものである。

#### 【0033】

このようなハロゲン系ガスとしては、高誘電率酸化物を揮発性の高い化合物に転化させやすいという性質を持つ点から、 $BCl_3$ 、 $HCl$ 、 $Cl_2$ 、 $SiCl_4$ 、 $HBr$ 、 $BBr_3$ 、 $SiBr_4$ 、および $Br_2$ からなる群から選択される一種以上のガスであるのが好ましい。そのなかでも、還元性あるいは酸素を引き抜く性質を持つ点から、 $BCl_3$ がより好ましい。ハロゲン系ガスを用いることにより、上記高誘電率酸化物からなる堆積物または付着物を、ハロゲン化物（ $HfCl_4$ 、 $HfBr_4$ 、 $AlCl_3$ 、 $AlBr_3$ 、 $ZrCl_4$ 、 $ZrBr_4$ 、 $SiCl_4$ 、 $SiBr_4$ など）に転化させることができ、これらのハロゲン化物は揮発性が高いため、チャンバー内からこれらを容易に除去することができる。

40

#### 【0034】

また、酸素原子供与性ガスとしては、 $O_2$ 、 $O_3$ 、 $H_2O$ 、 $H_2O_2$ 、 $CO_x$ 、 $SO_x$ 、および $NO_x$ （xは1以上の整数）からなる群から選択される一種以上のガスであるのが好ましい。そのなかでも、酸素ラジカルを生成しやすいという点から、 $O_2$ がより好ましい。また、酸化性ガスとしては、 $NF_3$ および/または $N_2O$ であるのが好ましい。

#### 【0035】

本発明では、上記酸素原子供与性ガスまたは酸化性ガスのいずれかと、ハロゲン系ガス

50

とを混合させたガスを用いる。混合割合は、混合ガス全体に対して、酸素原子供与性ガスまたは酸化性ガスを、1～50%添加するのが好ましい。また、この混合ガスを、アルゴンやヘリウム等の希ガスで希釈して使用してもよい。

#### 【0036】

クリーニングガスとして一般的なハロゲン系ガスに、酸化性の性質を有する酸素原子供与性ガスまたは酸化性ガスを混合して用いることにより、高誘電率酸化物からなる堆積物・付着物を容易に除去できると共に、BやSi等を含んだ他の化合物のチャンバー内への堆積を防止することができる。

#### 【0037】

また、この混合ガスに、さらにフッ素系ガスを添加するのが好ましい。<sup>10</sup> フッ素系ガスをさらに添加することにより、Siを含有する高誘電率酸化物からなる堆積物・付着物のクリーニングをより効率的に行うことができる。このようなフッ素系ガスとしては、CF<sub>4</sub>、C<sub>2</sub>F<sub>6</sub>、C<sub>3</sub>F<sub>8</sub>、C<sub>4</sub>F<sub>6</sub>、ClF<sub>3</sub>、F<sub>2</sub>、SF<sub>6</sub>、COF<sub>2</sub>からなる群から選択される一種以上のガスであるのがより好ましい。また、フッ素系ガスを添加する割合は、フッ素系ガスと混合ガスとの総量に対して、1～50%であるのが好ましい。

#### 【0038】

この混合ガスを活性化するには、半導体処理装置のチャンバー内に混合ガスを導入する前に、高周波(RF)またはマイクロ波源によるプラズマ処理を行い、この混合ガスを励起させる方法がある。また、チャンバー内にプラズマを発生させて、混合ガスを励起させてもよい。あるいは、混合ガスを加熱処理して励起させることができる。<sup>20</sup> プラズマ発生源として、電子サイクロトロン共鳴(ECR)、誘導結合型プラズマ(ICP)、ヘリコン波励起プラズマ(HWP)、電磁結合型プラズマ(TCP)、表面波励起プラズマ(SWP)、容量結合型プラズマ(CCP)等一般的に使用されている手段を用いて、プラズマを発生させることができる。

#### 【0039】

また、本発明における半導体処理装置とは、高誘電率酸化物を成膜するものであり、化学気相堆積(CVD)法、原子層堆積(ALD)法のいずれかの成膜法に用いられる装置または高誘電率酸化物をエッチングするエッチング装置であるのが好ましい。化学気相堆積法とは、気相中で化学反応を利用して薄膜を形成する方法である。具体的には、半導体処理装置のチャンバー内を排気してから、基板ホルダにシリコン基板を載置し、ヒーターでこの基板を450～600℃に加熱する。次いで、原料ガスであるHf(DPM)<sub>4</sub>、Hf(MMP)<sub>4</sub>などのHf原料と、ArとO<sub>2</sub>の混合ガスをチャンバー内に導入し、シリコン基板上に膜厚2～3nmのHfO<sub>2</sub>等の高誘電率酸化物を成膜する。<sup>30</sup> 成膜圧力は所定の値になるようにゲート弁を用いて調整する。

#### 【0040】

また、原子層堆積法とは、基板上に原料化合物の分子をモノレイヤごとに表面への吸着、反応による成膜、系内のリセットを繰り返し行うことによって、高膜質かつ段差被覆性の高い膜を形成させる方法である。具体的には、基板温度が熱CVD法の場合よりもやや低くなり、350～500℃にシリコン基板を加熱する。原料ガスとして、加水分解性の有機金属化合物(例えばアミン系の[(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf、塩化物系のHfCl<sub>4</sub>など)を使用し、水(H<sub>2</sub>O)と有機金属化合物とを交互にチャンバー内に供給して、一原子層ずつ成膜する。<sup>40</sup>

#### 【0041】

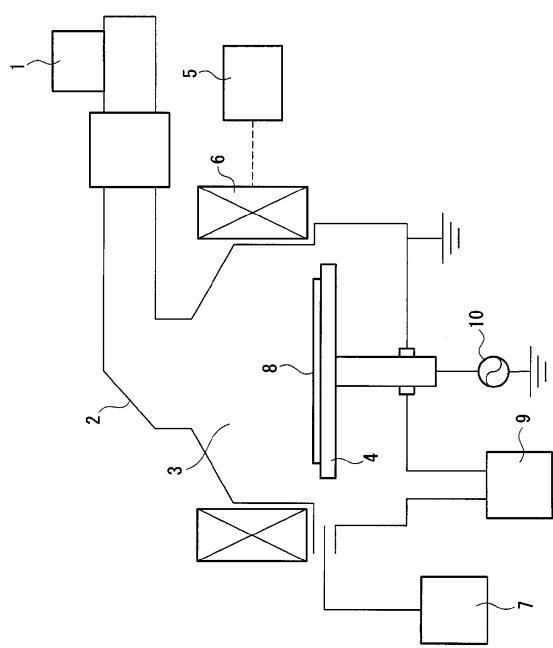

図1は、本発明における半導体処理装置の一例であるマイクロ波プラズマ装置を示す概略図である。この半導体処理装置は、マイクロ波を発振するマグネットロン1と、発振したマイクロ波をチャンバー3へと導入する導波管2と、クリーニングまたはエッチングを行うチャンバー3と、原料ガス及びクリーニングガス・エッチングガスを供給するガス供給装置7と、ガスを排気する真空排気装置9と、磁界を発生させるためチャンバー3の外側に設けられたソレノイドコイル6とから概略構成されている。この半導体処理装置では、クリーニングとエッチングの両方が行えるようになっている。<sup>50</sup>

## 【0042】

チャンバー3内には、高誘電率酸化物を成膜する下地となるシリコン基板8を載置する載置電極4が収容されている。この載置電極4には、シリコン基板8にバイアス電圧を印加するための高周波電源10が接続されている。また、ソレノイドコイル6には、直流電流を供給するための磁界発生用直流電源5が接続されている。

## 【0043】

マグネットロン1から発振した2.45GHzのマイクロ波は、導波管2を伝播しチャンバー3内に導かれる。チャンバー3の外側に設けられたソレノイドコイル6に、磁界発生用直流電源5から直流電流が供給されると、チャンバー3内に発生した875Gの磁界とマイクロ波電界によって、ガス供給装置7から供給したクリーニングガスまたはエッティングガスがプラズマ化される。このプラズマ化したガスにより、チャンバー3内に生成した高誘電率酸化物からなる堆積物・付着物のクリーニング、あるいはシリコン基板8上に成膜した高誘電率酸化物のエッティングを行うことができる。10

## 【0044】

具体的には、チャンバー3内を真空排気し、酸素原子供与性ガスまたは酸化性ガスと、ハロゲン系ガスとを混合させたガスを導入する。チャンバー3内の真空中度は、0.5~2Pa(3.8~15mTorr)であるのが好ましい。また、混合ガスの流量は、10~50sccmであるのが好ましい。次いで、600W、240mAのマイクロ波電力をマグネットロン1に印加してマイクロ波を発振し、プラズマを発生させる。クリーニングの場合、載置電極4には、高周波電源10から電力を供給しない。また、この時、載置電極4とチャンバー3の内壁温度は室温~350にするのが好ましい。20

## 【0045】

本発明のクリーニング方法によれば、酸素原子供与性ガスまたは酸化性ガスをハロゲン系ガスに混合して使用することにより、半導体処理装置のチャンバー内に生成した高誘電率酸化物からなる堆積物・付着物を高速で除去することができ、かつ他の化合物による堆積物の生成を防止することができる。また、クリーニングの速度が向上することにより、クリーニング時間が短縮でき、生産効率を向上させることができる。

## 【0046】

また、一例として、化学気相堆積(CVD)法の成膜法に用いられる装置、原子層堆積(ALD)法の成膜法に用いられる装置について記載したが、これ以外にも高誘電率酸化物をエッティングするエッティング装置内に堆積・蓄積した高誘電率酸化物を上記と同様のクリーニング方法により高速で除去することができる。30

## 【0047】

## [エッティング方法]

本発明に係るシリコン基板のエッティング方法とは、酸素原子供与性ガスまたは酸化性ガスのいずれかと、ハロゲン系ガスとを混合させたガスを、プラズマ処理または加熱処理により活性化し、シリコン基板上に成膜した高誘電率酸化物をエッティングするものである。

## 【0048】

高誘電率酸化物、混合ガス、プラズマ処理、加熱処理、これらを行う半導体処理装置については、上記クリーニング方法と同様であるので、その説明は省略する。クリーニング方法と異なるのは、エッティングの対象となるのがシリコン基板上に成膜した高誘電率酸化物である点である。40

## 【0049】

また、一般的に、エッティングを行う場合には、基板を載せた載置電極にバイアス電圧を印加して、プラズマ等により発生したイオンを加速して方向性を持たせて、これを基板上にたたきつける。この点が、クリーニングとは異なる。しかしながら、本発明に係るエッティング方法にあっては、バイアス電圧を印加する必要がない。ハロゲン系ガスに酸化性の性質を有する酸素原子供与性ガスまたは酸化性ガスを混合して用いることにより、バイアス電圧を印加することなく、高誘電率酸化物のエッティングを高速で行うことができる。

## 【0050】

10

20

30

40

50

具体的なエッティングの方法も、上記クリーニング方法と同様に行うことができる。この際、シリコン基板を250～300℃に加熱することにより、エッティング速度をより向上させることができる。

#### 【0051】

また、本発明に係るエッティング方法では、高誘電率酸化物のみが選択的にエッティングされ、シリコン基板はエッティングされない。そのため、高誘電率酸化物とシリコン基板との選択比が1を超える高い値となり、下地のシリコン基板に一切ダメージを与えないエッティングを行うことができる。

#### 【実施例】

##### 【0052】

以下、実施例により、本発明をさらに詳しく説明する。本発明は、下記実施例に何ら制限されるものではない。

10

##### 【0053】

###### [実験例1]

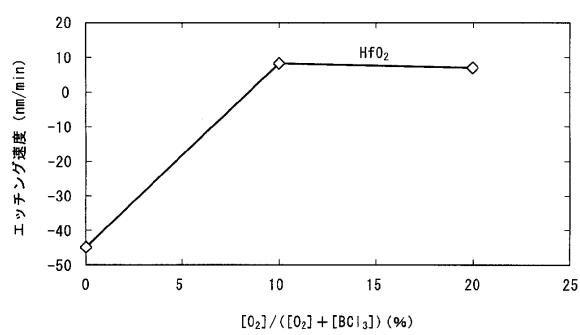

図1に示した半導体処理装置を用いて、シリコン基板上に成膜した厚さ100nmのHfO<sub>2</sub>膜のエッティングを行った。プラズマを発生させるには、2.45GHzのマイクロ波と875Gの磁界を用いた。載置電極には、高周波電源から電力を供給せずに、シリコン基板をプラズマに暴露した。エッティングガスにはBCl<sub>3</sub>とO<sub>2</sub>との混合ガスを用い、O<sub>2</sub>の添加量を、0%、10%、20%と変化させた。エッティングの条件を表1に示す。プラズマ暴露前後のHfO<sub>2</sub>膜の膜厚の差を段差計で測定し、エッティング速度を求めた。混合ガス中の酸素添加量を変化させた時のHfO<sub>2</sub>膜のエッティング速度との関係を図2のグラフに示す。

20

##### 【0054】

###### 【表1】

| クリーニング条件                                |                |

|-----------------------------------------|----------------|

| マイクロ波電力                                 | 600W, 200mA    |

| 載置電極高周波電力                               | 0W             |

| 真圧度                                     | 0.67Pa(5mTorr) |

| O <sub>2</sub> +BCl <sub>3</sub> トータル流量 | 40sccm         |

| 載置電極及びチャンバー壁温度                          | 室温             |

30

##### 【0055】

図2のグラフの結果から、酸素添加量が0%であるBCl<sub>3</sub>ガス単体を流した場合には、エッティングは起らず、エッティングガスに起因すると見られる堆積が観察された。しかし、酸素添加量が10%、20%の場合には、堆積物は生じず、良好なエッティング速度でエッティングされていることがわかった。

40

##### 【0056】

###### [実験例2]

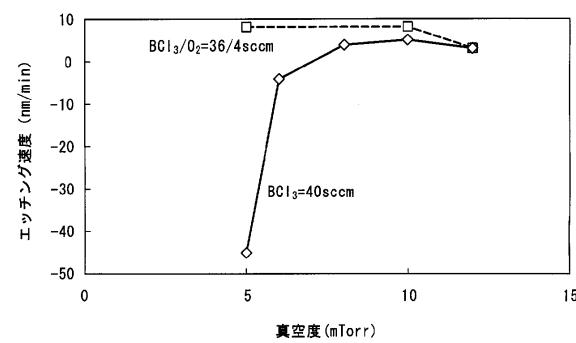

混合ガス中の酸素添加量を0%または10%とし、チャンバー内の真圧度を5、6、8、10、12mTorrと変化させた以外は、実験例1と同様にしてエッティングを行い、HfO<sub>2</sub>膜の膜厚の差を測定し、エッティング速度を求めた。エッティングの条件を表2に示す。混合ガス中の酸素添加量及び真圧度を変化させた時のHfO<sub>2</sub>膜のエッティング速度との関係を図3のグラフに示す。

##### 【0057】

50

## 【表2】

|                |                                                                      |

|----------------|----------------------------------------------------------------------|

| マイクロ波電力        | 600W, 240mA                                                          |

| 載置電極高周波電力      | 0W                                                                   |

| 真空度            | 0.67~1.6Pa(5~12mTorr)                                                |

| エッティングガス       | BCl <sub>3</sub> /O <sub>2</sub> =36/4sccm, BCl <sub>3</sub> =40sccm |

| 載置電極及びチャンバー壁温度 | 室温                                                                   |

10

## 【0058】

図3のグラフの結果から、酸素添加量が0%であるBCl<sub>3</sub>ガス単体を流した場合（実線）には、真空度が5mTorr及び6mTorrでは堆積が見られた。そして真空度が8mTorr以上になるとエッティングが観察された。しかし、酸素添加量が10%の場合（点線）では、堆積は一切観察されず、10mTorr以下の真空度では、BCl<sub>3</sub>ガス単体を流した場合よりもエッティング速度は大きいことがわかった。

20

## 【0059】

## [実験例3]

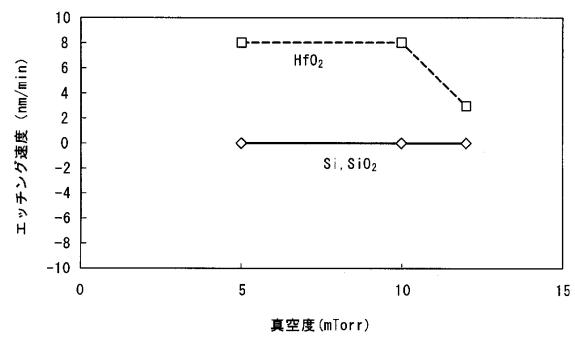

混合ガス中の酸素添加量を10%とし、チャンバー内の真空度を5、10、12mTorrに変化させた以外は、実験例2と同様にしてエッティングを行い、HfO<sub>2</sub>膜とシリコン基板の膜厚の差を測定し、エッティング速度を求めた。混合ガス中の真空度を変化させた時のHfO<sub>2</sub>膜及びシリコン基板のエッティング速度との関係を図4のグラフに示す。

20

## 【0060】

図4のグラフの結果から、シリコン基板のエッティングは観察されず、また堆積もなかった。HfO<sub>2</sub>膜については、良好なエッティング速度でエッティングされ、堆積は見られなかった。この場合の選択比は1を越える値であった。

30

## 【0061】

以上の結果から、本発明のエッティング方法によれば、酸素原子供与性ガスまたは酸化性ガスをハロゲン系ガスに混合して使用することにより、バイアス電圧を印加することなく、シリコン基板上に成膜した高誘電率酸化物を、選択比が1を超える高い選択性をもってエッティングできることが確認された。

## 【図面の簡単な説明】

## 【0062】

【図1】本発明における半導体処理装置の一例であるマイクロ波プラズマ装置を示す概略図である。

【図2】混合ガス中の酸素添加量を変化させた時のHfO<sub>2</sub>膜のエッティング速度との関係を示すグラフである。

40

【図3】混合ガス中の酸素添加量及び真空度を変化させた時のHfO<sub>2</sub>膜のエッティング速度との関係を示すグラフである。

【図4】混合ガス中の真空度を変化させた時のHfO<sub>2</sub>膜及びシリコン基板のエッティング速度との関係を示すグラフである。

## 【符号の説明】

## 【0063】

3 チャンバー

8 シリコン基板

50

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(74)代理人 100094400

弁理士 鈴木 三義

(74)代理人 100107836

弁理士 西 和哉

(74)代理人 100108453

弁理士 村山 靖彦

(72)発明者 斧 高一

京都府京都市左京区吉田本町 36 番地 1 京都大学大学院工学研究科内

(72)発明者 北川 智洋

京都府京都市左京区吉田本町 36 番地 1 京都大学大学院工学研究科内

(72)発明者 井上 實

東京都品川区小山一丁目 3 番 26 号 大陽日酸株式会社内

(72)発明者 大沢 正典

東京都品川区小山一丁目 3 番 26 号 大陽日酸株式会社内

審査官 宮本 靖史

(56)参考文献 特開2004-146787(JP,A)

特開平11-354505(JP,A)

特開2004-296477(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/31

C23C 16/44

H01L 21/3065