## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2017/0069726 A1 KYE et al.

Mar. 9, 2017 (43) **Pub. Date:**

## (54) SEMICONDUCTOR STRUCTURE AND METHOD FOR MANUFACTURING THE

(71) Applicant: SK hynix Inc., Gyeonggi-do (KR)

Inventors: **Jeong-Seob KYE**, Gyeonggi-do (KR); Jae-Sung KIM, Gyeonggi-do (KR); Tae-Kyum KIM, Gyeonggi-do (KR); Kun-Young LEE, Gyeonggi-do (KR)

Appl. No.: 15/048,236 (21)

(22)Filed: Feb. 19, 2016

#### (30)Foreign Application Priority Data

(KR) ..... 10-2015-0125570

### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | H01L 29/40  | (2006.01) |

|      | H01L 21/02  | (2006.01) |

|      | H01L 29/66  | (2006.01) |

|      | H01L 21/306 | (2006.01) |

|      | H01L 21/768 | (2006.01) |

|      | H01L 29/45  | (2006.01) |

|      | H01L 21/283 | (2006.01) |

### (52) U.S. Cl.

CPC ........... H01L 29/401 (2013.01); H01L 29/456 (2013.01); H01L 21/02532 (2013.01); H01L 21/02425 (2013.01); H01L 21/283 (2013.01); H01L 21/02694 (2013.01); H01L 21/30604 (2013.01); H01L 21/7682 (2013.01); H01L 29/66636 (2013.01); H01L 29/6656 (2013.01)

#### (57) ABSTRACT

A method for manufacturing a semiconductor structure includes preparing a semiconductor substrate which includes a memory cell region and a peripheral circuit region; forming a buried word line in the semiconductor substrate in the memory cell region; forming a bit line structure over the semiconductor substrate in the memory cell region; forming a dielectric layer in the peripheral circuit region and the memory cell region; forming a first opening in the dielectric layer in the memory cell region; filling a silicon filler in the first opening; forming a second opening in the dielectric layer in the peripheral circuit region; forming a sidewall spacer over a sidewall of the second opening; recessing the silicon filler to form a silicon plug, wherein the silicon plug fills a lower portion of the first opening; and forming a first metal silicide over a top surface of the silicon plug, and concurrently forming a second metal silicide in a lower portion of the second opening.

FIG. 1

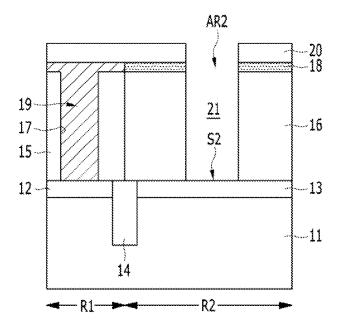

FIG. 2A

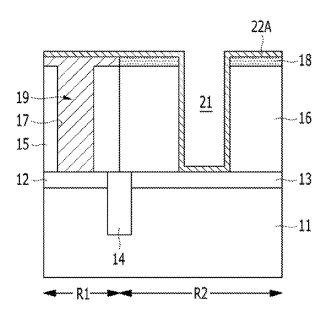

FIG. 2B

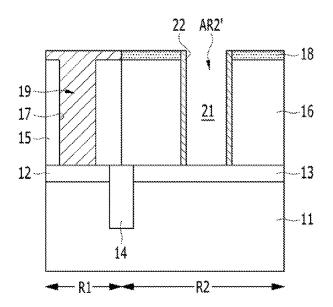

FIG. 2C

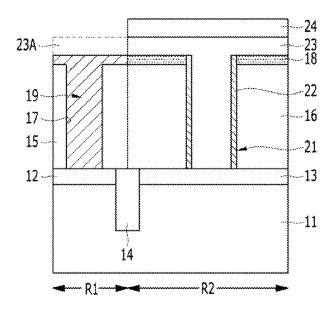

FIG. 2D

FIG. 2E

FIG. 2F

FIG. 2G

FIG. 2H

FIG. 2I

FIG. 2J

FIG. 2K

FIG. 2L

FIG. 2M

FIG. 2N

FIG. 3

FIG. 4A

FIG. 4B

FIG. 4D

-- R1----

-R2-

FIG. 4E

FIG. 4F

FIG. 4G

FIG. 4H

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 74

38 Ħ œ 504 526 333 요. \$10p 505 203 507p Š 23 304b 8 528 ක්. 'ක් 203 E. . 20. 20. 20. 23 Š 23 205

FIG. 7C

FIG. 7D

FIG. 84

FIG. 8B

<u>4</u> 48b 8 439 450 R20 4 4 33 2 ಹ . <del>1</del> 26 49C 48C

FIG. 8G

440

**4**

43

. <del>t</del>Ç

\$1 47C

3

42

43p

R20

R10

হ্ৰ| 28 82-96 485 AR2. 221 Œ, 63 ಹನ್ನ 8 72

ಜರಜ ಕ್ರಿ

382 65 882

99

FIG. 8I

700

99

ध्रक्षय हु

44P 71P 8 \$ 43p 485 **R**20 440 .63 448 ₹} 44A \$ 22 448 . tt 44B 42

# SEMICONDUCTOR STRUCTURE AND METHOD FOR MANUFACTURING THE SAME

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application claims priority under 35 U.S.C. \$119 to Korean Patent Application No. 10-2015-0125570 filed on Sep. 4, 2015, the disclosure of which is herein incorporated by reference in its entirety.

# TECHNICAL FIELD

[0002] Exemplary embodiments relate to a semiconductor structure, and more particularly, to a semiconductor structure including metal silicide and a method for manufacturing the same.

#### DISCUSSION OF THE RELATED ART

[0003] In the manufacture of a semiconductor structure, meta silicide is formed to suppress leakage current and contact resistance. In addition, a contact area reduces in conformity with miniaturization of a semiconductor device. [0004] Accordingly, it is necessary to sufficiently secure an area for forming metal silicide, to further decrease contact resistance.

### **SUMMARY**

[0005] Various embodiments are directed to a semiconductor structure capable of sufficiently securing an area of a metal silicide even though openings are miniaturized, and a method for manufacturing the same.

[0006] Also, various embodiments are directed to a semiconductor structure capable of concurrently forming metal silicides in openings having different aspect ratios, and a method for manufacturing the same.

[0007] Further, various embodiments are directed to a semiconductor structure capable of concurrently forming metal silicides in a memory cell, region and a peripheral circuit region, and a method for manufacturing the same.

[0008] In an embodiment, a method for manufacturing a semiconductor structure may include: preparing a substrate which includes a first doping region and a second doping region; forming a first opening which exposes the first doping region; forming a silicon region in a lower portion of the first opening; forming a second opening which exposes the second doping region; forming sidewall spacers in the second opening; forming a first metal-silicon region over the silicon region; and forming a second metal-silicon region over the second doping region. The forming of the silicon region in the lower of the first opening may include forming a silicon filler in the first opening; and recessing the silicon filler to forming the silicon region. The method may further include forming a first metal region over the first metalsilicon region, and concurrently forming a second metal region over the second metal-silicon region. The first opening has an aspect ratio larger than the second opening. The first opening and the second opening have the same height, and the first opening has a width smaller than the second opening. The forming of the first metal-silicon region and the second metal-silicon region may include forming a metal layer over the silicon region and the second doping region; forming the first metal-silicon region by reacting the silicon region and the metal layer; forming the second metal-silicon region by reacting the second doping region and the metal layer; and removing a non-reacted metal layer. The method may further include, before the forming of the first metalsilicon region and the second metal-silicon region, forming a first interface doping region over the silicon region; and forming a second interface doping region over the second doping region. The silicon region includes a polysilicon layer doped with a first dopant, and the forming of the first interface doping region may include doping an upper portion of the silicon region with a second dopant, wherein a doping concentration of the upper portion of the silicon region is higher than a lower portion of the silicon region; and performing a thermal processing to activate the second dopant in the upper portion of the silicon region to form the first interface doping region. The second doping region is formed by doping a third dopant, and the forming of the second interface doping region may include doping an upper portion of the second doping region with a fourth dopant, wherein the second interface doping region has a higher doping concentration than the second doping region; and performing a thermal processing to activate the fourth dopant in the second interface doping region. The first doping region may include a source/drain region of a first transistor, and the second doping region may include a source/drain region of a second transistor.

[0009] In an embodiment, a method for manufacturing a semiconductor structure, may include: preparing, a semiconductor substrate which includes a memory cell region and a peripheral circuit region; forming a buried word line in the semiconductor substrate in the memory cell region; forming a bit line structure over the semiconductor substrate in the memory cell region; forming a dielectric layer over the semiconductor substrate in the peripheral circuit region and the bit liner structure in the memory cell region; forming a first opening in the dielectric layer in the memory cell region; filling a silicon filler in the first opening; forming a second opening in the dielectric layer in the peripheral circuit region; forming a sidewall spacer over a sidewall of the second opening; recessing the silicon filler to form a silicon plug, wherein the silicon plug fills a lower portion of the first opening; and forming a first metal silicide over a top surface of the silicon plug, and concurrently forming a second metal silicide in a lower portion of the second opening. The method may further include forming a first metal plug and a second metal plug concurrently, the first metal plug fills the first opening and is provided over the first metal silicide, and the second metal plug fills the second opening and is provided over the second metal silicide. The method may further include before the forming of the first metal silicide and the second metal silicide, doping a first dopant into the top surface of the silicon plug to form a first interface doping region. The method may further include before the forming of the first metal silicide and the second metal silicide doping a second dopant into the semiconductor substrate exposed by the second opening to form a second interface doping region. The forming of the second opening and forming the sidewall spacer may include masking the memory cell region including the silicon filler; forming the second opening by etching the dielectric layer in the peripheral circuit region; forming a spacer layer to cover a sidewall and a bottom surface of the second opening; and etching back the spacer layer to form the sidewall spacer over the sidewall of the second opening. The forming of the silicon plug may include masking the peripheral circuit region including the second opening; etching back the silicon filler and forming the silicon plug; doping the top surface of the silicon plug with a dopant; and performing a thermal processing to activate the dopant. The forming of the dielectric layer over the semiconductor substrate in the peripheral circuit region and the bit line in memory cell region may include forming, a interlayer dielectric layer over the bit line in the memory cell region and the semiconductor substrate in peripheral circuit region; planarizing the interlayer dielectric layer such that a top surface of the bit line structure is exposed; forming plug isolation parts by partially etching portions of the interlayer dielectric layer; forming a plug isolation layer in the plug isolation parts; and removing the remaining interlayer dielectric layer from the memory cell region the interlayer dielectric layer remains in the peripheral circuit region, and the plug isolation layer is formed in the memory cell region. The method may further include forming a gate structure in the peripheral circuit region by using the same material as the bit line structure, and the gate structure is formed substantially at the same time when the bit line structure is formed. The method may further include forming a first spacer element over a sidewall of the bit line structure; and forming a second spacer element over a sidewall of the gate structure. The method may further include forming an air gap by removing a portion of the first spacer element; and capping the air gap.

[0010] In an embodiment, a semiconductor structure may include: a semiconductor substrate including a first doping region and a second doping region; a first dielectric layer having a first opening which exposes the first doping region; a second dielectric layer having a second opening which exposes the second doping region; a first contact structure filling the first opening, wherein the first contact structure includes a silicon region and a first metal-silicon region, wherein the silicon region contacts the first doping region, wherein the first metal-silicon region is formed over the silicon region; a second contact structure filling the second opening, wherein the second contact structure includes a second metal-silicon region, wherein the second metalsilicon region contacts the second doping region; and a sidewall spacer formed between the second contact structure and a sidewall of the second opening. The first contact structure and the second contact structure may further include a first metal region over the first metal-silicon region and a second metal region over the second metal-silicon region, respectively. The silicon region may include a doped polysilicon. Each of the first metal-silicon region and the second metal-silicon region may include metal silicide. The sidewall spacer may include dielectric material. The first dielectric layer and the second dielectric layer are different materials from each other. The first opening has an aspect ratio larger than the second opening. The first opening and the second opening have the same height, and the first opening has a width smaller than the second opening. The first doping region is a portion of a first transistor, and the second doping region is a portion of the second transistor. The first contact structure may further include a first interface doping region between the silicon region and the first metal-silicon region. The first, interface doping region may include a second dopant, and the first interface doping region has a higher doping concentration than the silicon region. The second contact structure may further include a second interface doping region formed between the second doping region and the second metal-silicon region.

[0011] In an embodiment, a semiconductor structure may include: a semiconductor substrate including a memory cell region and a peripheral circuit region, wherein the memory cell region includes a buried word line and a first doping region, wherein the peripheral circuit region includes a planar gate structure and a second doping region; a first dielectric layer formed over the semiconductor substrate in the memory cell region and having a first opening, wherein the first opening exposes the first doping region; a first contact structure formed in the first opening, wherein the first contact structure includes a silicon plug, a first metal silicide, and a first metal plug, wherein the silicon plug contacts the first doping region wherein the first metal silicide is formed over the silicon plug, wherein the first metal plug over the first metal silicide; a second dielectric layer formed over the semiconductor substrate in periphery circuit region and having a second opening, wherein the second opening exposes the second doping region and has an aspect ratio smaller than the first opening; a second contact structure formed in the second opening and including a second metal silicide and a second metal plug, wherein the second metal silicide contacts the second doping region, wherein the second metal plug is formed over the second metal silicide; and a sidewall spacer formed between the second contact structure and a sidewall of the second opening. The semiconductor structure may further include a bit line structure formed in the memory cell region; a spacer element provided over a sidewall of the bit line structure and formed in the memory cell region; and a memory element, formed in the memory cell region, the spacer element is provided between the bit line structure and the first contact structure, and the memory element is electrically coupled to the first contact structure. The spacer element may include an air gap. The semiconductor structure may further include a first interface doping region provided between the silicon plug and the first metal silicide. The semiconductor structure may further include a second interface doping region provided between the second doping region and the second metal silicide.

[0012] According to the embodiments, by forming a metal silicide in a spacer-free opening, it is possible to sufficiently secure an area for forming the metal silicide.

[0013] Also, according to the embodiments, it is possible to concurrently form metal silicide in an opening of a low aspect ratio and an opening of a high aspect ratio.

# BRIEF DESCRIPTION OF THE DRAWINGS

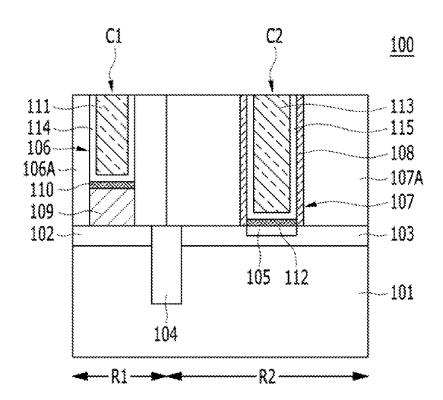

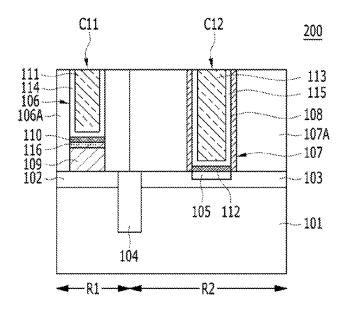

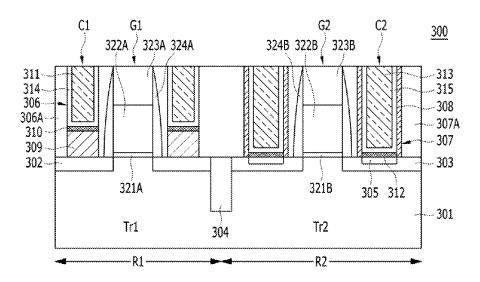

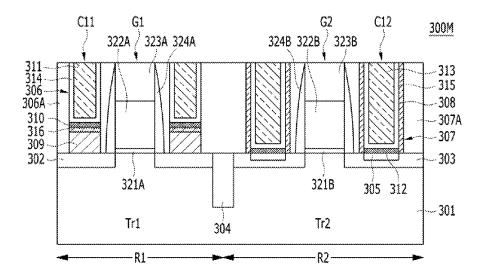

[0014] FIG. 1 is a view illustrating a semiconductor structure in accordance with a first embodiment.

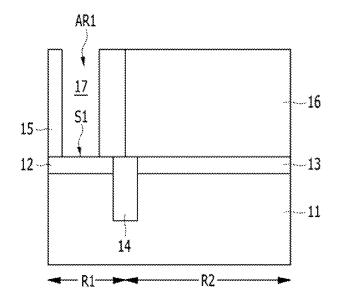

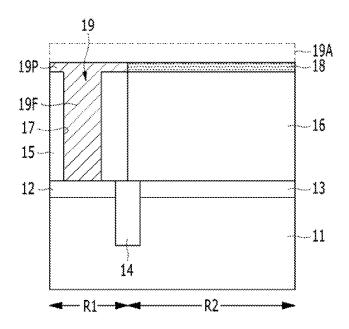

[0015] FIGS. 2A to 2N are views to assist in the explanation of a method for forming the semiconductor structure in accordance with the first embodiment.

[0016] FIG. 3 is a view illustrating a semiconductor structure in accordance with a second embodiment.

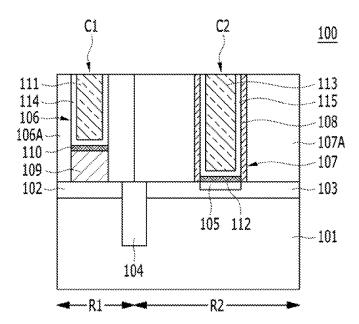

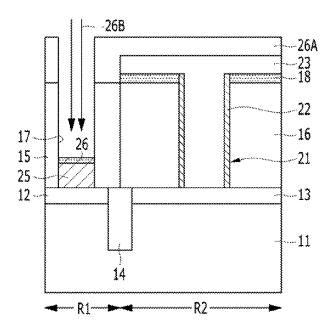

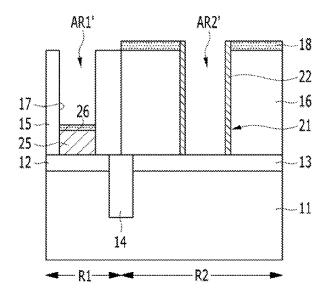

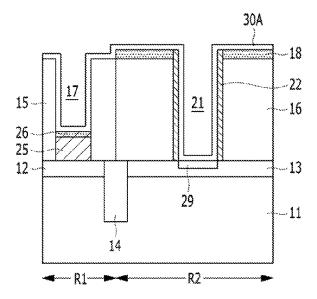

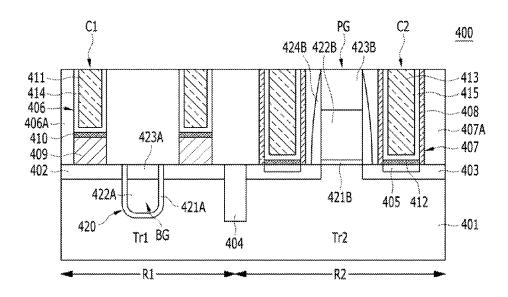

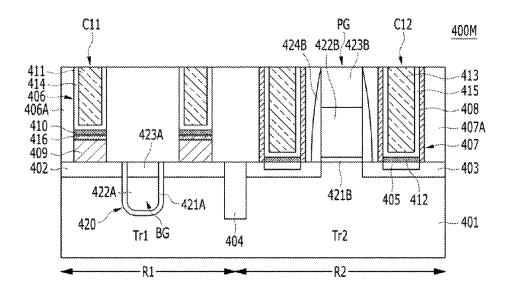

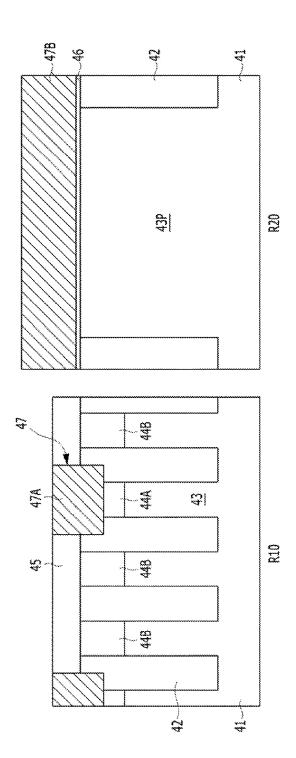

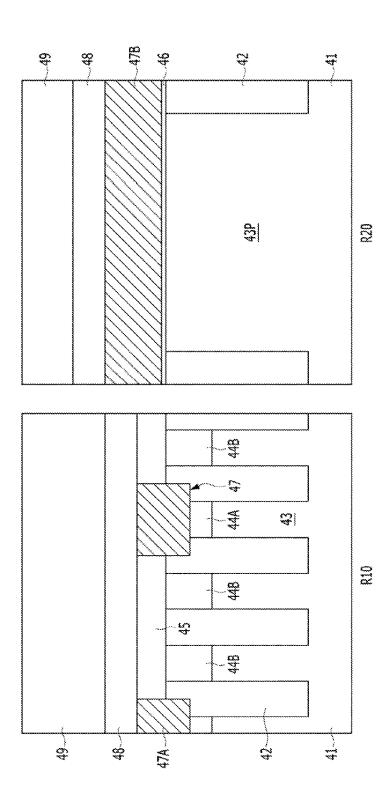

[0017] FIGS. 4A to 4H are representations a method for forming the semiconductor structure in accordance with the second embodiment.

[0018] FIGS. 5A and 5B are views illustrating semiconductor structures in accordance with a third embodiment and a modification thereof.

[0019] FIGS. 6A and 6B are views illustrating semiconductor structures in accordance with a fourth embodiment and a modification thereof.

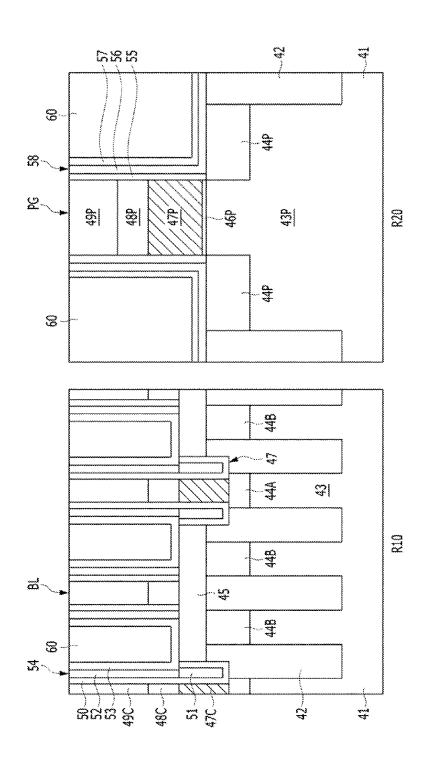

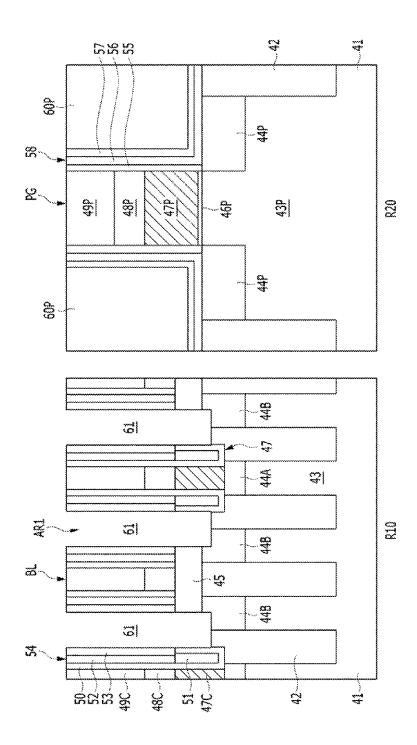

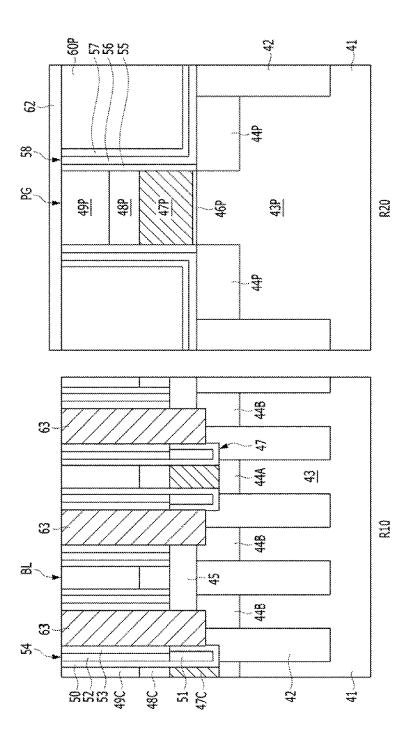

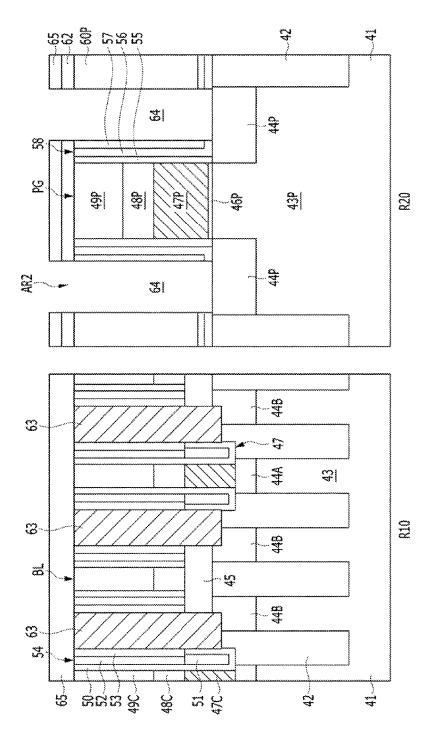

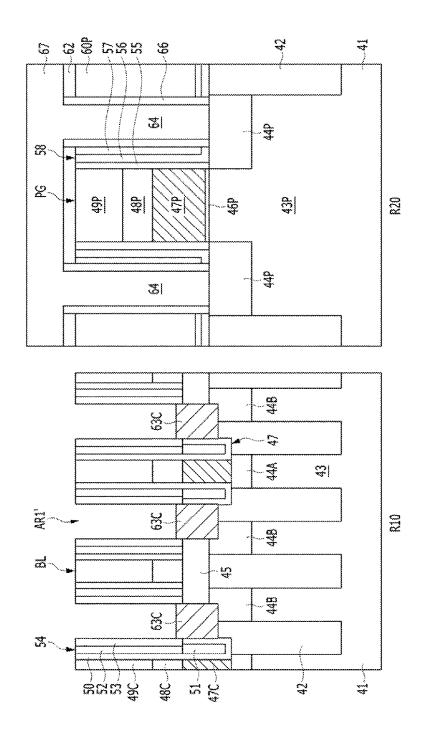

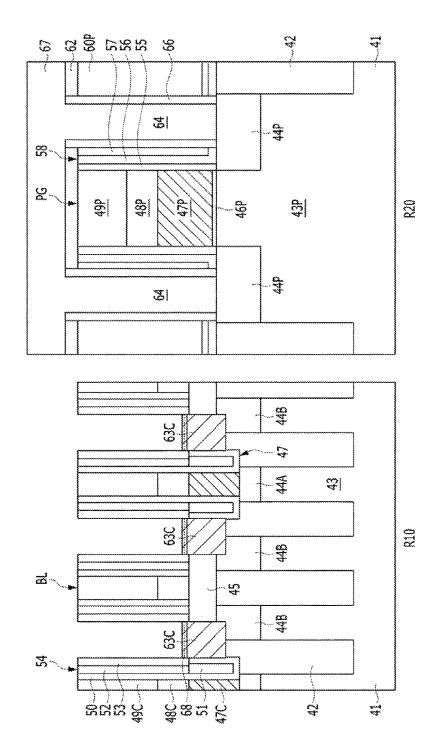

[0020] FIG. 7A is a view illustrating a semiconductor structure in accordance with a fifth embodiment.

[0021] FIG. 7B is a cross-sectional view taken along the lines A-A' and B-B' of FIG. 7A.

[0022] FIG. 7C is a cross-sectional view taken along the line C-C' of FIG. 7A.

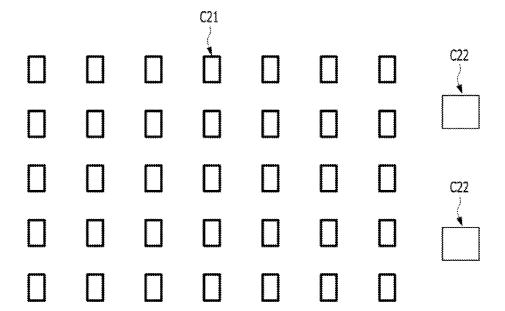

[0023] FIG. 7D is a view comparing a cell contact structure C21 and a peripheral contact structure C22.

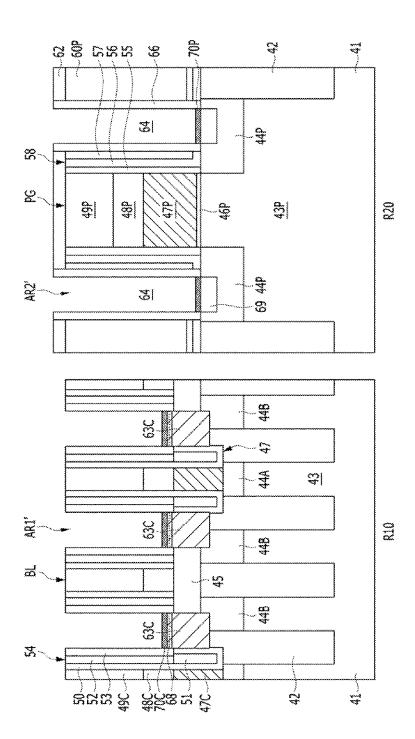

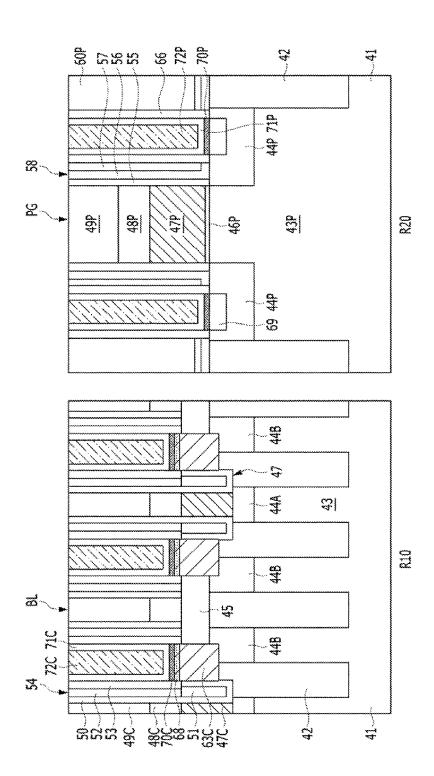

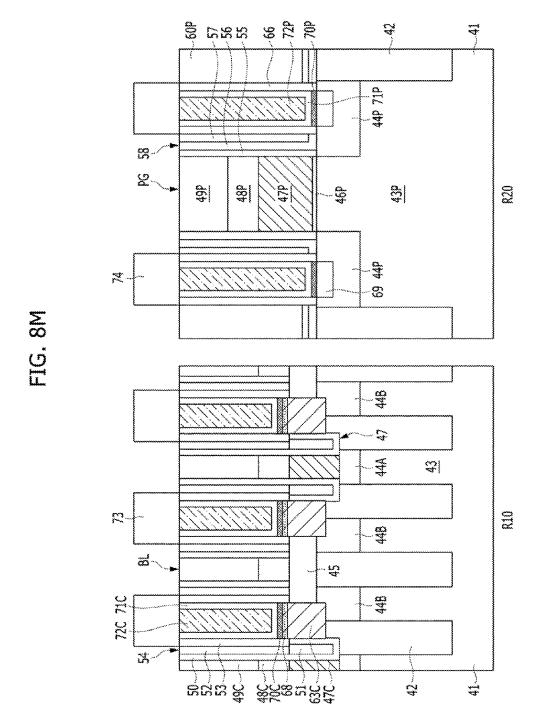

[0024] FIGS. 8A to 8M are illustrating a method for forming the semiconductor structure in accordance with the fifth embodiment.

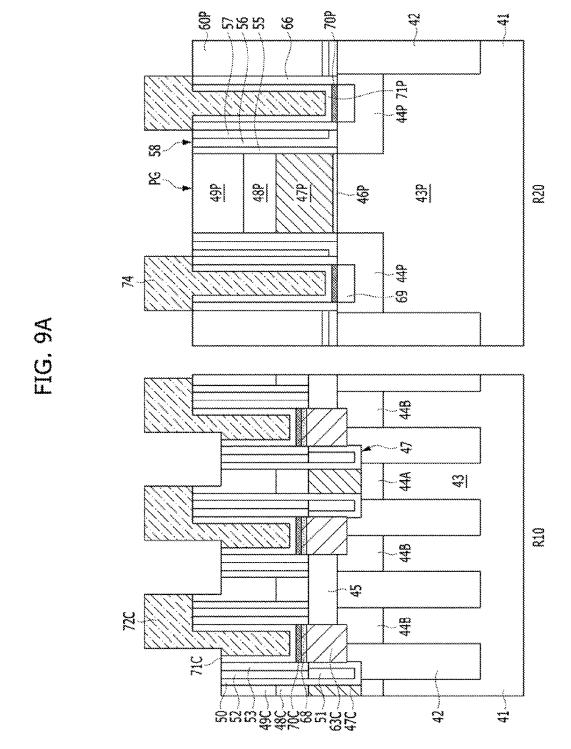

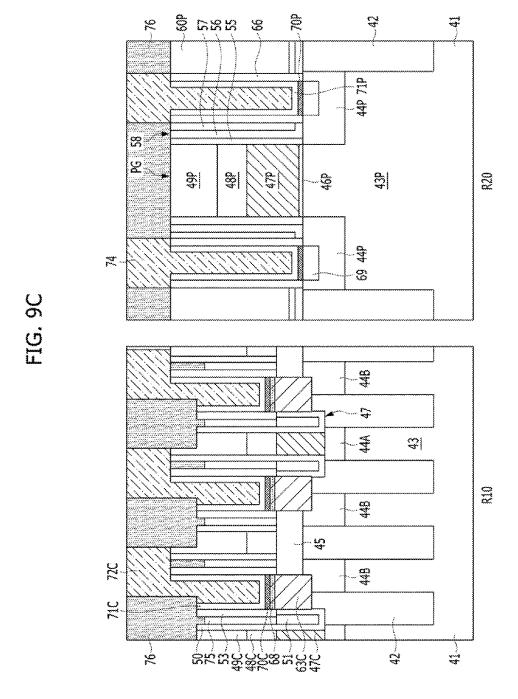

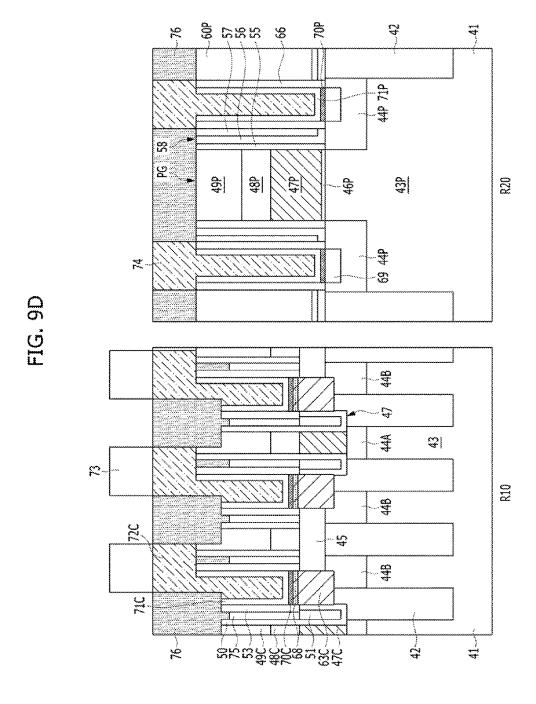

[0025] FIGS. 9A to 9D are illustrating a method for forming a semiconductor structure in accordance with a modification of the fifth embodiment.

#### DETAILED DESCRIPTION

[0026] Various embodiments will be described below in more detail with reference to the accompanying drawings. The present invention may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the present invention to those skilled in the art. Throughout the disclosure, like reference numerals refer to like parts throughout the various figures and embodiments of the present invention.

[0027] The drawings may not be necessarily to scale and in some instances, proportions may have been exaggerated in order to clearly illustrate features of the embodiments. When a first layer is referred to as being "on" a second layer or "on" a substrate, it not only refers to a case where the first layer is formed directly on the second layer or the substrate but also a case where a third layer exists between the first layer and the second layer or the substrate.

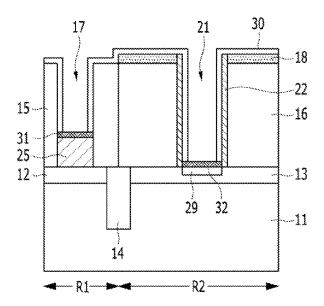

[0028] FIG. 1 is a view illustrating a semiconductor structure in accordance with a first embodiment.

[0029] Referring to FIG. 1, a semiconductor structure 100 in accordance with a first embodiment may include a first contact structure C1 and a second contact structure C2. The first contact structure C1 and the second contact structure C2 may have different aspect ratios. The aspect ratio refers to a ratio of a height with respect to a width of a given pattern. The given pattern may be a hole pattern or a pillar pattern. For example, the first contact structure C1 and the second contact structure C2 may have the same height as each other and different widths from each other.

[0030] The first contact structure C1 and the second contact structure. C2 may be formed on a semiconductor substrate 101. The semiconductor substrate 101 may include a first doping region 102 and a second doping region 103. The first doping region 102 may be formed in a first region R1, and the second doping region 103 may be formed in the second region R2. The first region R1 and the second region R2 may be isolated by an isolation layer 104.

[0031] A third doping region 105 may be additionally formed in the second doping region 103. The first doping region 102 and the second doping region 103 may be doped with the same dopant or different dopants. The third doping region 105 and the second doping region 103 may be doped with the same dopant or different dopants. The third doping region 105 may be doped to have a higher concentration than the second doping region 103. The third doping region 105 may be referred to as an interface doping region. The contact

resistance of the second contact structure  ${\rm C2}$  may be improved by the third doping region  ${\rm 105}.$

[0032] A first dielectric layer 106A and a second dielectric layer 107A may be formed on the semiconductor substrate 101. The first dielectric layer 106A may be formed in the first region R1, and the second dielectric layer 107A may be formed in the second region R2. The first dielectric layer 106A and the second dielectric layer 107A may be the same material or different materials.

[0033] The first dielectric layer 106A may have a first opening 106 which exposes a portion of the first doping region 102. The second dielectric layer 107A may have a second opening 107 which exposes a portion of the second do ping region 103. The first opening 106 may have an aspect ratio larger than the second opening 107. In the present embodiment, the second opening 107 and the first opening 106 may have the same height and different widths. For example, the second opening 107 may have a width larger than the first opening 106.

[0034] The first contact structure C1 may be formed in the first opening 106. The second contact structure C2 may be formed in the second opening 107. The second contact structure C2 may include sidewall spacers 108. The first contact structure C1 does not include spacers. That is, the first contact structure C1 may be a spacer-free structure, and the second contact structure C2 may be a spacer-embedded structure. The sidewall spacers 108 may be positioned on the sidewalls of the second opening 107.

[0035] The first contact structure C1 may include a silicon region 109, a first metal-silicon region 110, and a first metal region 111. The second contact structure C2 may include the sidewall spacers 108, a second metal-silicon region 112 and a second metal region 113. The first contact structure C1 may be coupled to the first doping region 102. The second contact structure C2 may be coupled to the second doping region 103. The contact resistance of the second contact structure C2 is improved by the third doping region 105. The silicon region 109 may include a polysilicon, in particular, a doped polysilicon. The first metal-silicon region 110 and the second metal-silicon region 112 may include a metal silicide such as a cobalt silicide. The first metal region 111 and the second metal region 113 may include a metal such as tungsten.

[0036] A first barrier 114 may be formed between the first metal-silicon region 110 and the first metal region 111. A second barrier 115 may be formed between the second metal-silicon region 112 and the second metal region 113. The first barrier 114 and the second barrier 115 may include a metallic material to reduce resistances of the first and second contact structures C1 and C2. The first barrier 114 and the second barrier 115 may include titanium, a titanium nitride or a combination thereof.

[0037] The semiconductor structure 100 may include a plurality of transistors. For example, a first transistor may be formed in the first region R1, and a second transistor may be formed in the second region R2. The first doping region 102 may be a portion of the first transistor. The second doping region 103 may be a portion of the second transistor. The first transistor and the second transistor may be formed to be isolated by the isolation layer 104.

[0038] FIGS. 2A to 2N are illustrating a method for forming the semiconductor structure in accordance with the first embodiment.

[0039] As shown in FIG. 2A, a substrate 11 is prepared. The substrate 11 may include a first region R1 and a second region R2. Structures which will be formed in the first region R1 and the second region R2 may be symmetrical or asymmetrical to each other. For example, the structures which will be formed in the first region R1 and the second region R2 may be the same as each other. In another embodiment, the structures which will be formed in the first region R1 and the second region R2 may be different from each other. In another embodiment, the first region R1 may be a region in which a high density structure is formed, and the second region R2 may be a region in which a low density structure is formed.

[0040] For example, a plurality of structures which are densely spaced apart from one another may be formed in the first region R1 with a high density. A plurality of structures which are coarsely spaced apart from one another when compared to the plurality of structures of the first region R1 may be formed in the second region R2 with a low density. A structure to be formed in the first region R1 may have a width smaller than a structure to be formed in the second region R2. In the first region R1, a first transistor may be formed. In the second region R2, a second transistor may be formed. The first region R1 may include a memory cell, and the second region R2 may include a peripheral circuit.

[0041] The substrate 11 may include suitable materials for semiconductor processing. The substrate 11 may include a semiconductor substrate. For example, the substrate 11 may include a silicon substrate, a silicon germanium (SiGe) substrate or an SOI (Silicon On Insulator) substrate. Also, the substrate 11 may include a dielectric material or a conductive material. For example, the substrate 11 may include a silicon oxide, a silicon nitride, a polysilicon, a metallic material, or a combination thereof. The substrate 11 may include a dielectric material which is formed on a semiconductor substrate.

[0042] A first doping region 12 may be formed in the first region R1. The first doping region 12 may be formed in the substrate 11. The first doping region 12 may be a portion of a transistor. In other words the first doping region 12 may be referred to as a source/drain region. The first doping region 12 may be doped with a dopant. The first doping region 12 may be formed by a doping technique such as implantation and plasma doping (PLAD). The first doping region 12 may be doped with an N type dopant or a P type dopant.

[0043] A second doping region 13 may be formed in the second region R2. The second doping region 13 may be formed in the substrate 11. The second doping region 13 may be a portion of a transistor. In other words, the second doping region 13 may be referred to as a source/drain region. The second doping region 13 may be doped with a dopant. The second doping region 13 may be formed by a doping technique such as implantation and plasma doping (PLAD). The second doping region 13 may be doped with an N type dopant or a P type dopant.

[0044] The first doping region 12 and the second doping region 13 may be formed to have a low concentration or a high concentration. In another embodiment, each of the first doping region 12 and the second doping region 13 may have a low concentration part and a high concentration part. The low concentration part may be referred to as an LDD.

[0045] The first region R1 and the second region R2 may be isolated from each other by an isolation layer 14. The isolation layer 14 may be an STI (shallow trench isolation)

region. The isolation layer 14 may include a silicon oxide, a silicon nitride, or a combination thereof.

[0046] Dielectric layers 15 and 16 may be formed on the substrate 11. The dielectric layers 15 and 16 may include a silicon oxide, a silicon nitride, a low-k material, or a combination thereof. For example, the dielectric layers 15 and 16 may include SiO<sub>2</sub>, TEOS, PSG, BPSG, BSG or SOD. Each of the dielectric layers 15 and 16 may be a single layer or multiple layers. The dielectric layers 15 and 16 may be formed through chemical vapor deposition (CVD) or other suitable techniques.

[0047] In the present embodiment, the first dielectric layer 15 may be formed in the first region R1, and the second dielectric layer 16 may be formed in the second dielectric layer 15 and the second dielectric layer 16 may be the same material or different materials. For example, the first dielectric layer 15 may be a silicon nitride, and the second dielectric layer 16 may be a silicon oxide. In another embodiment, each of the first dielectric layer 15 and the second dielectric layer 16 may be a silicon oxide or a silicon nitride. The first dielectric layer 15 may be multiple layers, and the second dielectric layer 16 may be a single layer. The first dielectric layer 15 may be formed as vertically stacked multiple layers, or a combination thereof.

[0048] Next, a first, opening 17 may be formed in the first dielectric layer 15. For example, a portion of the first dielectric layer 15 may be etched to form the first opening 17. The first opening 17 may have a first aspect ratio AR1. The first opening 17 may expose a first surface S1 of the substrate 11. When viewed from the top, the first opening 17 may have a circular shape, an elliptical shape or a rectangular shape. While forming the first opening 17 in the first region R1, the second dielectric layer 16 may be masked (not shown). The first surface S1 exposed by the first opening 17 may be a top surface of the first doping region 12. In another embodiment, the first surface S1 may be further recessed.

[0049] As shown in FIG. 2B, a filler 19 which fills the first opening 17 may be formed. The filler 19 may completely gapfill the first opening 17. The filler 19 may be formed of a conductive material. For example, the filler 19 may include a polysilicon. The filler 19 may include a doped polysilicon doped with a dopant. The filler 19 may be doped with phosphorus, arsenic or boron.

[0050] An example of forming the filler 19 is as follows. First, a protective layer 18 is formed on the second dielectric layer 16. The protective layer 18 may cover the second region R2 and expose the first region R1. The protective layer 18 may include a silicon nitride. Next, the first opening 17 is filled with a polysilicon layer 19A. As the polysilicon layer 19A, a seed layer, a doped polysilicon and an undoped polysilicon may be sequentially formed. The polysilicon layer 19A may be exposed to a subsequent thermal process. [0051] Then, a planarization process such as CMP (chemical mechanical polishing) may be performed. The CMP process for the polysilicon layer 19A may be performed until the surface of the protective layer 18 is exposed. As a result, a step between the first region R1 and the second region R2 may be removed. The filler 19 and the protective layer 18 may be coplanar to each other. The filler 19 may include a filler part 19F which fills the first opening 17 and a planar part 19P which is on the filler part 19F. The planar part 19P may cover the filler part 19F and the first dielectric layer 15.

The planar part 19P does not extend to the second region R2. In another embodiment, the filler 19 may include only the filler part 19F without the planar part 19P. In this way, by using the polysilicon layer 19A, it is possible to void-freely gapfill the first opening 17. In another embodiment, the gapfill and CMP processes for the polysilicon layer 19A may be performed without forming the protective layer 18.

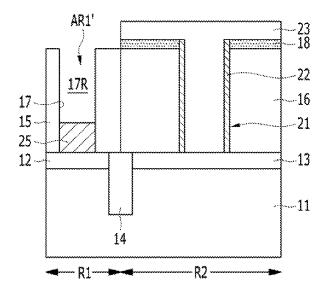

[0052] As shown in FIG. 2C, a second opening 21 may be formed. The second opening 21 may be formed in the second dielectric layer 16. For example, in order to form the second opening 21 the protective layer 18 and the second dielectric layer 16 may be etched by an etch process using a first mask layer 20. The second opening 21 may have a second aspect ratio AR2. The first aspect ratio AR1 and the second aspect ratio AR2 may be the same or different from each other.

[0053] For example, the first opening 17 and the second opening 21 may have the same height and different widths. The second opening 21 may have a width larger than the first opening 17. According to this fact, the first aspect ratio AR1 may be larger than the second aspect ratio AR2. The second opening 21 may expose a second surface S2 of the substrate 11. When viewed from the top, the second opening 21 may have a circular shape, an elliptical shape or a rectangular shape.

[0054] While forming the second opening 21 in the second region R2, the first region R1 may be protected by the first mask layer 20. The second surface S2 exposed by the second opening 21 may be a top surface of the second doping region 13. In another embodiment, the second surface S2 may be further recessed. The first mask layer 20 may include a photoresist pattern. In another embodiment, the first mask layer 20 may be a hard mask material such as an SOC (Spin On Carbon), TEOS and an amorphous carbon.

[0055] As shown in FIG. 2D, the first mask layer 20 may be removed. Then, a spacer layer 22A may be formed. The spacer layer 22A may be formed of a material which has an etching selectivity with respect to the second dielectric layer 16. For example, in the case where the second dielectric layer 16 is formed of a silicon oxide, the spacer layer 22A may be formed of a silicon nitride. When the second dielectric layer 16 is formed of a silicon nitride, the spacer layer 22A may be formed of a silicon oxide. The spacer layer 22A may prevent upper sidewalls of the second opening 21 from bending, bowing, or being distorted. In another embodiment, the spacer layer 22A may also be formed in the first region R1.

[0056] As shown in FIG. 2E sidewall spacers 22 may be formed in the second opening 21. In order to form the sidewall spacers 22, an etch-back process may be performed. In the etch-back process, the spacer layer 22A may be removed completely from the first region R1. Therefore, the sidewall spacers 22 may expose the bottom surface of the second opening 21 and be formed on only the sidewalls of the second opening 21. During the etching process for forming the sidewall spacers 22, the second surface S2 of the second doping region 13 may be recessed to a predetermined depth.

[0057] The sidewall spacers 22 may have a thickness of at least 30 Å. By this fact, it is possible to firmly form the sidewall spacers 22 without bowing. In the case where the thickness of the sidewall spacers 22 is thinner than 30 Å, the sidewall spacers 22 may be lost and bowing is likely to occur

in the upper sidewalls of the second opening 21. The bowing may cause bridging between neighboring second openings 21.

[0058] The second opening 21 may have a corrected second aspect ratio AR2' which is larger than the second aspect ratio AR2. The change in the aspect ratio is attributed to the sidewall spacers 22.

[0059] As shown in FIG. 2F, a blocking layer 23A may be formed. The blocking layer 23A may completely fill the second opening 21 on the sidewall spacers 22. The blocking layer 23A may also be formed in the first region R1. Namely, a portion of the blocking layer 23A may cover the filler 19. The blocking layer 23A may be formed of a carbon-containing material. The blocking layer 23A may be formed by Spin on Coating. Due to this fact it is possible to void-freely fill the blocking layer 23A in the second opening 21. The blocking layer 23A may include an SOC (Spin On Carbon). [0060] A second mask layer 24 may be formed on the blocking layer 23A. The second mask layer 24 may expose the first region R1 and cover the second region R2. The second mask layer 24 may include a photoresist pattern. The second mask layer 24 may also be referred to as a 'first region open mask.

[0061] By using the second mask layer 24 as an etch barrier, the blocking layer 23A is removed from the first region R1. Accordingly, a blocking pattern 23 may be formed in the second region R2. The blocking pattern 23 may fill the second opening 21 which is formed with the sidewall spacers 22.

[0062] As shown in FIG. 2G, the second mask layer 24 may be removed. Then, the filler 19 may be recessed so that a top surface of the filer 19 is located at a lower level than a top surface of the first dielectric layer 15. Thus, a silicon region 25 may be formed in the first opening 17. In order to recess the filler 19, an etch-back process may be performed. Meanwhile, during the etch-back process, the second region R2 may be protected by the blocking pattern 23. Since the filler 19 includes a poly silicon the silicon region 25 may be a polysilicon region. The silicon region 25 may be also referred to as a 'polysilicon plug.'

[0063] Due to the presence of the silicon region 25, the first opening 17 has a recess portion 17R. The recess portion 17R may have a corrected first aspect ratio AR1'. The corrected first aspect ratio AR1' may be smaller than the initial first aspect ratio AR1.

[0064] As shown in FIG. 2H, the blocking pattern 23 may be removed. The blocking pattern 23 may be removed by a strip process using oxygen plasma.

[0065] By the series of processes described above, the silicon region 25 may be formed in the first region R1, and the sidewall spacers 22 may be formed in the second region R2. That is, the silicon region 25 may be partially filled in the first opening 17, and the sidewall spacers 22 may be formed on the sidewalls of the second opening 21. As a result, the first opening 17 may be partially filled with the silicon region 25 with no sidewall spacer, that is, a spacer-free structure. Sidewall spacers do not exist in the first opening 17, and the sidewall spacers 22 exist in the second opening 21. This is referred to as an asymmetrical opening structure.

[0066] The first opening 17 may have the corrected first aspect ratio AR1' which is smaller than the first aspect ratio AR1. The reduction of the first aspect ratio is due to the silicon region 25. The second opening 21 may have the

corrected second aspect ratio AR2' which is larger than the second aspect ratio AR2. The change in the second aspect ratio is due to the sidewall spacers 22. The change between the corrected first aspect ratio AR1' and the original first aspect ratio AR1 may be larger than the change between the aspect ratio the corrected second aspect ratio AR2' and the original second aspect ratio AR2. Accordingly, the corrected first aspect ratio AR1' may be smaller than the corrected second aspect ratio AR2'.

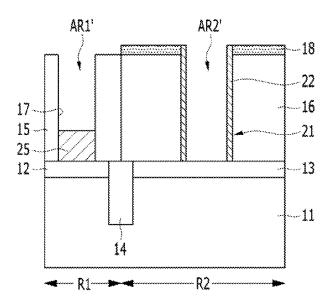

[0067] As shown in FIG. 2I, a third doping region 29 may be formed in the second region R2. The third doping region 29 may be formed in the second doping region 13. The third doping region 29 may be formed to decrease a contact resistance. The third doping region 29 may be referred to as an interface doping region. The third doping region 29 may be doped with a dopant. The third doping region 29 may be formed by a doping technique such as implantation and plasma doping (PLAD). The third doping region 29 may be doped with an N type dopant or a P type dopant. The second doping region 13 and the third doping region 29 may be doped with the same dopant or different dopants.

[0068] In order to form the third doping region 29, a doping process 28 using a third mask layer 27 may be performed. The third mask layer 27 may cover the first region R1. The third mask layer 27 may selectively expose the second opening 21 and cover the other portion of the second region R2.

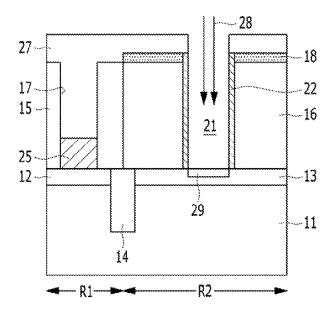

[0069] As shown in FIG. 23, the third mask layer 27 may be removed. Then, a metal layer 30A may be formed. The metal layer 30A may be formed on the entire surface including the silicon region 25 and the sidewall spacers 22. The metal layer 30A may be formed to a uniform thickness without filling the first opening 17 and the second opening 21. The metal layer 30A may be a silicidable material. For example, a metal contained in the metal layer 30A may react with the silicon region 25. Further, the metal contained in the metal layer 30A may react with the substrate 11, that is, the third doping region 29. In the present embodiment, the metal layer 30A may include cobalt. The metal layer 30A may be formed by a deposition method such as ALD (atomic layer deposition) and CVD (chemical vapor deposition).

[0070] Before forming the metal layer 30A, the surfaces of the silicon region 25 and the third doping region 29 are exposed. The surface of the third doping region 29 may include silicon, which is a portion of the substrate 11. Similarly to this the silicon region 25 may also include silicon. Therefore, portions of the metal layer 30A may be formed on surfaces in which silicon is contained, and the other portions of the metal layer 30A may be formed on the first dielectric layer 15, the protective layer 18 and the sidewall spacers 22. In another embodiment, the metal layer 30A may include a metal such as titanium and nickel, instead of cobalt.

[0071] As shown in FIG. 2K a thermal process may be performed. By the thermal process, metal-silicon regions 31 and 32 may be formed. The metal-silicon regions 31 and 32 may be concurrently formed in the first opening 17 and the second opening 21, respectively. For example, the metal-silicon regions 31 and 32 may be a metal silicide. The metal-silicon regions 31 and 32 may include a cobalt silicide.

[0072] The metal-silicon regions 31 and 32 may include a first metal-silicon region 31 and a second metal-silicon region 32. The first metal-silicon region 31 may be formed

in the first opening 17. The second metal-silicon region 32 may be formed in the second opening 21. The first metal-silicon region 31 may be formed on the silicon region 25. The second metal-silicon region 32 may be formed on the bottom surface of the second opening 21, that is, the third doping region 29. The first metal-silicon region 31 may be formed by reaction between silicon of the silicon region 25 and metal of the metal layer 30A. The second metal-silicon region 32 may be formed by reaction between metal of the metal layer 30A and silicon of the third doping region 29. After the thermal process, a non-reacted metal layer 30 may remain

[0073] The first metal-silicon region 31 and the second metal-silicon region 32 are not limited to a cobalt silicide. For example, by using another metal for example, such as titanium and nickel) capable of forming a silicide by reacting with silicon metal-silicon regions may be formed. When the first metal-silicon region 31, the second metal-silicon region 32, or both includes cobalt silicide, a leakage current can be significantly reduced since cobalt silicide has a low resistance.

[0074] As shown in FIG. 2L, the non-reacted metal layer 30 may be selectively removed. The silicon region 25 and the first metal-silicon region 31 may remain in the first opening 17. The second metal-silicon region 32 and the sidewall spacers 22 may remain in the second opening 21. The second metal-silicon region 32 may contact the third doping region 29. The first metal-silicon region 31 may contact the silicon region 25.

[0075] As shown in FIG. 2M, a conductive layer may be filled in the first opening 17 and the second opening 21. The conductive layer may be a material which has a resistance lower than the silicon region 25. For example, the conductive layer may be a metallic material. As the conductive layer, a first metallic layer 33 and a second metallic layer 34 may be sequentially formed. The first metallic layer 33 may include Ti, TIN or Ti/TiN. The second metallic layer 34 may include tungsten.

[0076] Since sidewall spacers do not exist in the first opening 17, it is possible to sufficiently gapfill the first metallic layer 33 and the second metallic layer 34. Due to this fact, by increasing the volume of a metal-based material, and a resistance may be decreased. As a comparative example, assuming that sidewall spacers exist in the first opening 17, a space in which the first metallic layer 33 and the second metallic layer 34 are to be formed may be insufficient or the first and second metallic layers 33 and 34 may not be formed. In some cases, the first metallic layer 33 and the second metallic layer 34 may not extend to either a bottom of the first opening 17 or a bottom of the second opening 21. This may result in a disconnection between the first metallic layer 33 and the first doping region 12 and between the second metallic layer 34 and the second doping region 13, causing a malfunction of the semiconductor device.

[0077] As shown in FIG. 2N, the first metallic layer 33 and the second metallic layer 34 may be planarized by CMP in such a manner that they remain only in the first opening 17 and the second opening 21. As a result, a first barrier 33A and a first metal region 34A may be formed in the first opening 17. A second barrier 33B and a second metal region 34B may be formed in the second opening 21. Since the first metal region 34A and the second metal region 34B are metal-based material, they may be also referred to as 'metal

plugs.' The first barrier 33A and the second barrier 33B may be concurrently formed, and the first metal region 34A and the second metal region 34B may also be concurrently formed. During the CMP process, the protective layer 18 may be removed.

[0078] According to the above descriptions, a first contact structure C1 may be formed in the first region R1 and a second contact structure C2 may be formed in the second region R2. The first contact structure C1 may include the silicon region 25, the first metal-silicon region 31, the first barrier 33A, and the first metal region 34A. The second contact structure C2 may include the second metal-silicon region 32, the second barrier 33B, and the second metal region 34B. The first contact structure C1 and the second contact structure C2 may include the first metal-silicon region 31 and the second metal-silicon region 32, respectively. Both the first contact structure C1 and the second contact structure C2 may include metallic materials, that is, the first barrier 33A, the second barrier 33B, the first metal region 34A and the second metal region 34B. The second metal region 34B and the second metal-silicon region 32 may include different metals. The first metal region 34A and the first metal-silicon region 31 may include different metals. In other words, the first metal region 34A and the second metal region 34B may include tungsten, and the first and second metal-silicon regions 31 and 32 may include cobalt. [0079] The first contact structure C1 and the second contact structure C2 may be asymmetrical to each other in structure. For example, the first contact structure C1 and the second contact structure C2 may become asymmetrical to each other due to the sidewall spacers 22 and the silicon region 25. The first contact structure C1 may be a spacer-free structure, and the second contact structure C2 may be a spacer-embedded structure in which the sidewall spacers 22 are embedded. The first contact structure C1 includes the silicon region 25 and the first metal region 34A while the second contact structure C2 includes only the second metal region 34B. The first contact structure C1 including the silicon region 25, which is a silicon-based material, and the first metal region 34A, which is a metal-based material, may also be referred to as a semi-metal plug (SMP) or a hybrid plug. The second contact structure C2 includes only a metal plug.

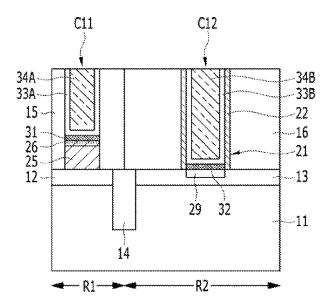

[0080] FIG. 3 is a view illustrating a semiconductor structure in accordance with a second embodiment. Referring to FIG. 3, a semiconductor structure 200 in accordance with a second embodiment may include a first contact structure C11 and a second contact structure C12. The first contact structure C11 and the second contact structure C12 may have different aspect ratios from each other. In the second embodiment, the first contact structure C11 may further include an interface doping region 116. The other construction may be the same as or similar to FIG. 1.

[0081] The first contact structure C11 according, to the second embodiment, which is a spacer-free structure, may include a silicon region 109, the interface doping region 116, a first metal-silicon region 110, and a first metal region 111. The interface doping region 116 improves a contact resistance between the silicon region 109 and the first metal-silicon region 110. The interface doping region 116 and the silicon region 109 may be the same material. The interface doping region 116 may have a higher concentration than the dopant doped into the silicon region 109. The interface doping region 116 and the silicon region 109 may be doped

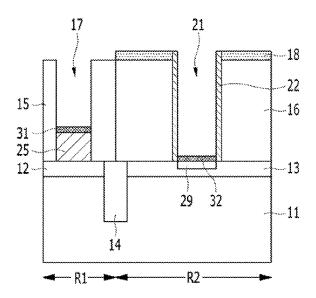

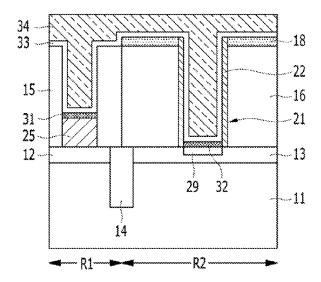

with the same dopant. The interface doping region 116 may include a polysilicon, in particular, a doped polysilicon. The silicon region 109 may include a doped polysilicon as well. [0082] FIGS. 4A to 4H illustrates a method for forming the semiconductor structure in accordance with the second embodiment. Except that the semiconductor structure in accordance with the second embodiment may include an interface doping region 26, the semiconductor structure may be the same as or similar to the first embodiment. For example, the silicon region 25 may be formed by the method shown in FIGS. 2A to 2G.

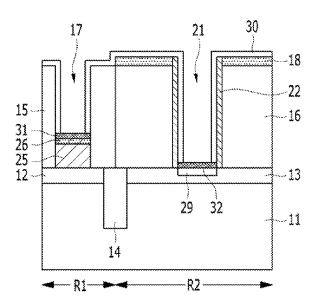

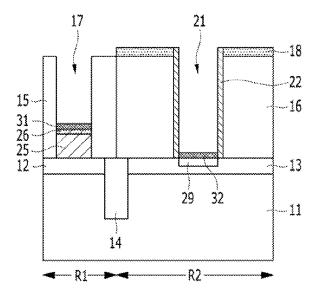

[0083] Next, as shown in FIG. 4A, a dopant may be doped into the silicon region 25. The dopant may be doped by a doping process 26B such as implantation and plasma doping (PLAD). For example, implantation may be performed at least 2 times. The doping process 26B may be performed by using an ion implantation mask layer 26A and the blocking pattern 23 as a barrier. The ion implantation mask layer 26A may selectively expose the first opening 17 and cover the other regions. Accordingly, due to the ion implantation mask layer 26A and the blocking pattern 23, a dopant is not doped into the second region R2.

[0084] Upon the doping process 26B, a top portion of the silicon region 25 may be converted into the interface doping region 26. An interfacial resistance may be reduced by the interface doping region 26. Namely, the interfacial resistance between the silicon region 25 and a first metal region 34A (see FIG. 4H) may be decreased. The interface doping region 26 and the silicon region 25 may be doped with the same dopant. The interface doping region 26 may be doped to a higher concentration than the silicon region 25 so that the interfacial resistance may be further improved.

[0085] As shown in FIG. 4B, the ion implantation mask layer 26A and the blocking pattern 23 may be removed. The ion implantation mask layer 26A may be removed by a strip process using oxygen plasma. The blocking pattern 23 may also be removed by oxygen plasma.

[0086] In order to activate the dopant implanted into the interface doping region 26, a thermal process may be performed. The thermal process may be performed at a temperature of 500° C. to 1100° C. by rapid thermal anneal (RTA).

[0087] By the series of processes described above, the silicon region 25 and the interface doping region 26 may be formed in the first region R1, and the sidewall spacers 22 may be formed in the second region R2. That is, the silicon region 25 and the interface doping region 26 may be partially filled in the first opening 17, and the sidewall spacers 22 may be formed on the sidewalls of the second opening 21. As a result, the first opening 17 may be partially filled with the silicon region 25 with no sidewall spacers, that is, a spacer-free structure. Sidewall spacers do not exist in the first opening 17, and the sidewall spacers 22 exist in the second opening 21. This is referred to as an asymmetrical opening structure.

[0088] The first opening 17 may have the corrected first aspect ratio AR1' which is smaller than the first aspect ratio AR1. The reduction of the first aspect ratio is due to the silicon region 25 and the interface doping region 26. The second opening 21 may have the corrected second aspect ratio AR2' which is larger than the second aspect ratio AR2. The change in the second aspect ratio is due to the sidewall spacers 22. The change between the corrected first aspect ratio AR1' and the original first aspect ratio AR1 may be

larger than the change the corrected second aspect ratio AR2' and the original second aspect ratio AR2. Accordingly, the corrected first aspect ratio AR1' may be smaller than the corrected second aspect ratio AR2'.

[0089] As shown in FIG. 4C, a third doping region 29 may be formed in the second region R2. The third doping region 29 may be formed in the second doping region 13. The third doping region 29 may be formed to decrease a contact resistance. The third doping region 29 may be referred to as an interface doping region. The third doping region 29 may be doped with a dopant. The third doping region 29 may be formed by a doping technique such as implantation and plasma doping (PLAD). The third doping region 29 may be doped with an N type dopant or a P type dopant. The second doping region 13 and the third doping region 29 may be doped with the same dopant or different dopants.

[0090] In order to form the third doping region 29, a doping process 28 using a third mask layer 27 may be performed. The third mask layer 27 may cover the first region R1. The third mask layer 27 may selectively expose the second opening 21 and cover the other portion of the second region R2.

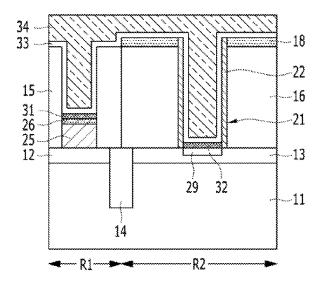

[0091] As shown in FIG. 4D, the third mask layer 27 may be removed. Then, a metal layer 30A may be formed. The metal layer 30A may be formed on the entire surface including the silicon region 25 and the sidewall spacers 22. The metal layer 30A may be conformally formed without filling the first opening 17 and the second opening 21. That is, the metal layer 30A is formed to a uniform thickness. The metal layer 30A may be a silicidable material. For example a metal contained in the metal layer 30A may react with the interface doping region 26. Further, the metal contained in the metal layer 30A may react with the substrate 11, that is, the third doping region 29. In the present embodiment, the metal layer 30A may include cobalt. The metal layer 30A may be formed by a deposition method such as ALD and CVD.

[0092] Before forming the metal layer 30A, the interface doping region 26 and the third doping region 29 are exposed. The third doping region 29 may be a portion of the substrate 11, and thus include silicon. Similarly, the interface doping region 26 may also include silicon. Therefore, portions of the metal layer 30A may be formed on surfaces in which silicon is contained, and the other portions of the metal layer 30A may be formed on the first dielectric layer 15, the protective layer 18 and the sidewall spacers 22. In another embodiment, the metal layer 30A may include a metal such as titanium and nickel, instead of cobalt.

[0093] As shown in FIG. 4E, a thermal process may be performed. By the thermal process, metal-silicon regions 31 and 32 may be formed. The metal-silicon regions 31 and 32 may be concurrently formed in the first opening 17 and the second opening 21, respectively. For example, the metal-silicon regions 31 and 32 may be metal silicide. The meta silicon regions 31 and 32 may include cobalt silicide.

[0094] The metal-silicon regions 31 and 32 may include a first metal-silicon region 31 and a second metal-silicon region 32. The first metal-silicon region 31 may be formed in the first opening 17. The second metal-silicon region 32 may be formed in the second opening 21. The first metal-silicon region 31 may be formed on the interface doping region 26. The second metal-silicon region 32 may be formed on the bottom surface of the second opening 21, that is, the third doping region 29. The first metal-silicon region

31 may be formed by reaction between silicon of the interface doping region 26 and metal of the metal layer 30A. The second metal-silicon region 32 may be formed by reaction between metal of the metal layer 30A and silicon of the third doping region 29.

[0095] After the thermal process, a non-reacted metal layer 30 may remain. The first metal-silicon region 31 and the second metal-si icon region 32 are not limited to cobalt silicide. For example, by using another metal, for example, such as titanium and nickel which is capable of forming silicide by reacting with silicon, metal-silicon regions may be formed. Due to the first metal-silicon region 31 and the second metal-silicon region 32, which may include cobalt silicide, a leakage current may be suppressed and a resistance may be reduced.

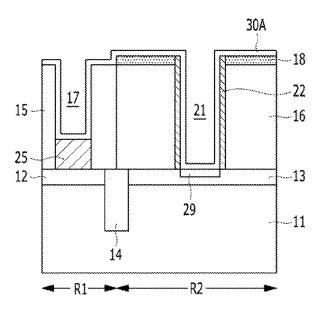

[0096] As shown in FIG. 4F, the non-reacted metal layer 30 may be selectively removed. Thus, the silicon region 25, the interface doping region 26 and the first metal-silicon region 31 may remain in the first opening 17. The second metal-silicon region 32 and the sidewall spacers 22 may remain in the second opening 21. The second metal-silicon region 32 may contact the third doping region 29. The first metal-silicon region 31 may contact the interface doping region 26.

[0097] As shown in FIG. 4G, a conductive layer may be filled in the first opening 17 and the second opening 21. The conductive layer may have a resistance lower than the silicon region 25 and the interface doping region 26. For example, the conductive layer may be a metallic material. As the conductive layer, a first metallic layer 33 and a second metallic layer 34 may be sequentially formed. The first metallic layer 33 may include Ti, TiN or Ti/TiN. The second metallic layer 34 may include tungsten.

[0098] Since sidewall spacers are not formed in the first opening 17, an opening defined by the first opening 17 may be relatively wide compared with when the sidewall spacers are formed. Thus, it is easy to completely gapfill the opening to form a stack of the first metallic layer 33 and the second metallic layer 34. Due to this fact, by increasing the volume of a metal-based material, a resistance may be reduced. As a comparative example, in the case where sidewall spacers exist in the first opening 17, an opening defined by the first opening 17 is relatively narrow. Thus, it is difficult to completely fill the first metallic layer 33 and the second metallic layer 34 in the narrow opening, causing void or a seam.

[0099] As shown in FIG. 4H, the first metallic layer 33 and the second metallic layer 34 may be planarized by CMP in such a manner that they remain only in the first opening 17 and the second opening 21. As a result, a first barrier 33A and a first metal region 34A may be formed in the first opening 17. A second barrier 33B and a second metal region 34B may be formed in the second opening 21. Since the first metal region 34A and the second metal region 34B are metal-based materials, they may be referred to as 'metal plugs.' The first barrier 33A and the second barrier 33B may be concurrently formed, and the first metal region 34A and the second metal region 34B may also be concurrently formed. During the CMP process, the protective layer 18 may be removed.

[0100] According to the above descriptions, a first contact structure C11 may be formed in the first region R1, and a second contact structure C12 may be formed in the second region R2. The first contact structure C11 may include the

silicon region 25, the interface doping region 26, the first metal-silicon region 31, the first barrier 33A, and the first metal region 34A. The second contact structure C12 may include the second metal-silicon region 32, the second barrier 33B, and the second metal region 34B. The first contact structure C11 and the second contact structure C12 may include the first metal-silicon region 31 and the second metal-silicon region 32, respectively. Both the first contact structure C11 and the second contact structure C12 may include metallic materials, that is, the first barrier 33A, the second barrier 33B, the first metal region 34A and the second metal region 34B.

[0101] The first contact structure C11 and the second contact structure C12 may be asymmetrical to each other in structure. For example, the first contact structure C11 and the second contact structure C12 may become asymmetrical structures due to a difference in the sidewall spacers 22 and the silicon region 25. The first contact structure C11 may be a spacer-free structure, and the second contact structure C12 may be a spacer-embedded structure in which the sidewall spacers 22 are embedded. The first contact structure C11 includes the silicon region 25 and the first metal region 34A whereas the second contact structure C12 includes only the second metal region 34B. The first contact structure C11 including the silicon region 25 which is silicon-based and the first metal region 34A which is metal-based may be referred to as a semi-metal plug (SMP) or a hybrid plug. The second contact structure C12 includes only a metal plug.

[0102] According to the first embodiment and the second embodiment described above, the first contact structures C1 and C11 and the second contact structures C2 and C12 are asymmetrical to each other in structure, and the first metal-silicon region 31 and the second metal-silicon region 32 may be concurrently formed. In particular, since sidewall spacers are not formed in the first opening 17, a wide area for forming the first metal-silicon region 31 may be secured. As a result, an ohmic contact characteristic may be improved. Since the sidewall spacers 22 are formed in the second opening 21, it is possible to substantially prevent a bowing profile on top sidewalls of the second opening 21.

[0103] FIG. 5A is a view illustrating a semiconductor structure in accordance with a third embodiment. FIG. 5B is a view illustrating a semiconductor structure in accordance with a modification of the third embodiment.

[0104] Referring to FIG. 5A, a semiconductor structure 300 in accordance with a third embodiment may include a first transistor Tr1, a second transistor Tr2, first contact structures C1 coupled to the first transistor Tr1, and second contact structures C2 coupled to the second transistor Tr2. [0105] The first transistor Tr1 may include a first planar gate structure G1 and pair of first doping regions 302. The pair of first doping regions 302 may be respectively positioned in a substrate 301 and at both sides of the first planar gate structure G1. The first contact structures C1 may be coupled to the pair of first doping regions 302, respectively. The first planar gate structure G1 may include a first gate dielectric layer 321A, a first gate electrode 322A, and a first gate cap layer 323A. First gate spacers 324A may be formed on both sidewalls of the first planar gate structure G1. The pair of first doping regions 302 may be source and drain regions of the first transistor Tr1.

[0106] The second transistor Tr2 may include a second planar gate structure G2 and a pair of second doping regions 303. The pair of second doping regions 303 may be respec-

tively positioned in the substrate 301 and at both sides of the second planar gate structure G2. The second contact structures C2 may be coupled to the pair of second doping regions 303, respectively. The second planar gate structure G2 may include a second gate dielectric layer 321B, a second gate electrode 322B, and a second gate cap layer 323B. Second gate spacers 324B may be formed on both sidewalls of the second planar gate structure G2. The pair of second doping regions 303 may be source and drain regions of the second transistor Tr2. Third doping regions 305 may be formed in the second doping regions 303. The third doping regions 305 and the second contact structures C2 may contact each other.

[0107] The first transistor Tr1 and the second transistor Tr2 may be isolated by an isolation layer 304. The first transistor Tr1 and the second transistor Tr2 may be the same type or different types. For example, both of the first transistor Tr1 and the second transistor Tr2 may be NMOSFETs or PMOSFETs. Further, any one transistor of the first transistor Tr1 and the second transistor Tr2 may be an NMOSFET, and the other transistor may be a PMOSFET. In the latter case, the first doping regions 302 and the second doping regions 303 may be doped with different dopants.

[0108] The first contact structures C1 may be the same as the first contact structure C1 according to the first embodiment. For example, each first contact structure C1 may be formed in a first opening 306 with no spacers. The first opening 306 may be formed in a first dielectric layer 306A and exposes a portion of the first doping region 302. Each first contact structure C1 may include a silicon region 309, a first metal-silicon region 310, a first barrier 314, and a first metal region 311.

[0109] The second contact structures C2 may be the same as the second contact structure C2 according to the first embodiment. For example, each second contact structure C2 may be formed in a second opening 307 including sidewall spacers 308. The second opening 307 may be formed in a second dielectric layer 307A and exposes a portion of the third doping region 305. Each second contact structure C2 may include a second metal-silicon region 312, a second barrier 315, and a second metal region 313.

[0110] Referring to FIG. 56, a semiconductor structure 300M in accordance with a modification of the third embodiment may include a first transistor Tr1, a second transistor Tr2, first contact structures C11 coupled to the first transistor Tr1, and second contact structures C12 coupled to the second transistor Tr2. The second contact structures C12 may be the same as the second contact structures C2 of FIG. 5A. The first contact structures C11 may be similar to the first contact structures C1 of FIG. 5A.

[0111] For example, each first contact structure C11 may be formed in a first opening 306 with no spacers. Each first contact structure C11 may include a silicon region 309, a first metal-silicon region 310, a first barrier 314, and a first metal region 311. Each first contact structure C11 may further include an interface doping region 316 between the silicon region 309 and the first metal-silicon region 310.

[0112] FIG. 6A is a view illustrating a semiconductor structure in accordance with a fourth embodiment. FIG. 6B is a view illustrating a semiconductor structure in accordance with a modification of the fourth embodiment.

[0113] Referring to FIG. 6A, a semiconductor structure 400 in accordance with a fourth embodiment may include a first transistor Tr1, a second transistor Tr2 first contact

structures C1 coupled to the first transistor Tr1, and second contact structures C2 coupled to the second transistor Tr2. [0114] The first transistor Tr1 may include a buried gate structure BG and a pair of first doping regions 402. The pair of first doping regions 402 may be respectively positioned in a substrate 401 and at both sides of the buried gate structure BG. The first contact structures C1 may be coupled to the pair of first doping regions 402, respectively. The buried gate structure BG may include a first gate dielectric layer 421A, a first gate electrode 422A, and a first gate cap layer 423A. The buried gate structure BG may be formed in a gate trench 420. The pair of first doping regions 402 may be source and drain regions of the first transistor Tr1.

[0115] The second transistor Tr2 may include a planar gate structure PG and a pair of second doping regions 403. The pair of second doping regions 403 may be respectively positioned in the substrate 401 and at both sides of the planar gate structure PG. The second contact structures C2 may be coupled to the pair of second doping regions 403, respectively. The planar gate structure PG may include a second gate dielectric layer 421B, a second gate electrode 422B, and a second gate cap layer 423B. Gate spacers 424B may be formed on both sidewalls of the planar gate structure PG. The pair of second doping regions 403 may be source and drain regions of the second transistor Tr2. Third doping regions 405 may be formed in the second doping regions 403. The third doping regions 405 and the second contact structures C2 may contact each other.

[0116] The first transistor Tr1 and the second transistor Tr2 may be isolated by an isolation layer 404. The first transistor Tr1 and the second transistor Tr2 may be the same type or different types. For example, both the first transistor Tr1 and the second transistor Tr2 may be NMOSFETs or PMOSFETs. Further, any one transistor of the first transistor Tr1 and the second transistor Tr2 may be an NMOSFET, and the other transistor may be a PMOSFET. When the transistors Tr1 and Tr2 have different polarity from each other, the first doping regions 402 and the second doping regions 403 may be doped with different dopants.

[0117] The first contact structures C1 may be the same as the first contact structure C1 according to the first embodiment. For example, each first contact structure C1 may be formed in a first opening 406 with no spacers. The first opening 406 may be formed in a first dielectric layer 406A and exposes a portion of the first doping region 402. Each first contact structure C1 may include a silicon region 409, a first metal-silicon region 410, a first barrier 414, and a first metal region 411.

[0118] The second contact structures C2 may be the same as the second contact structure C2 according to the first embodiment. For example, each second contact structure C2 may be formed in a second opening 407 including sidewall spacers 408. The second opening 407 may be formed in a second dielectric layer 407A and exposes a portion of the third doping region 405. Each second contact structure C2 may include a second metal-silicon region 412, a second barrier 415, and a second metal region 413.

[0119] Referring to FIG. 6B, semiconductor structure 400M in accordance with a modification of the fourth embodiment may include a first transistor Tr1, a second transistor Tr2 first contact structures C11 coupled to the first transistor Tr1, and second contact structures C12 coupled to the second transistor Tr2. The second contact structures C12 may be the same as the second contact structures C2 of FIG.

6A. The first contact structures C11 may be similar to the first contact structures C1 of FIG. 6A. For example, each first contact structure C11 may be formed in a first opening 406 with no spacers. Each first contact structure C11 may include a silicon region 409, a first metal-silicon region 410, a first barrier 414, and a first metal region 411. Each first contact structure C11 may further include an interface doping region 416 between the silicon region 409 and the first metal-silicon region 410.

**[0120]** The fourth embodiment and the modification thereof may be applied to a CMOS. For example, a first transistor including a buried gate structure may be formed in a first region, and a CMOS may be formed in a second region. In other words, a CMOS includes an NMOS and a PMOS, and each of the NMOS the PMOS include a planar gate structure and a second contact structure.

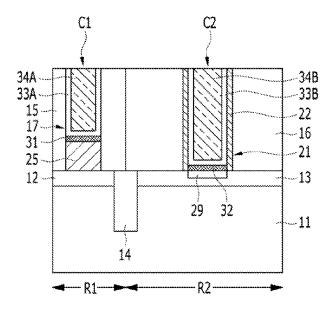

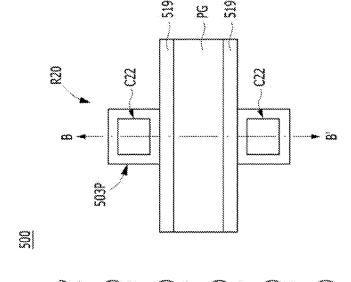

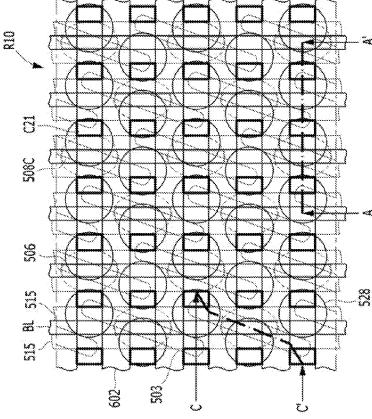

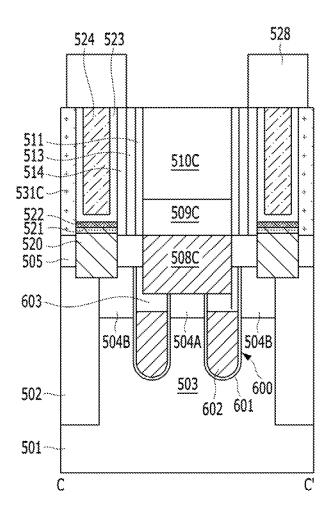

[0121] FIG. 7A is a view illustrating a semiconductor structure in accordance with a fifth embodiment. In the fifth embodiment, contact plugs are applied in a semiconductor device having memory cells, such as a DRAM. FIG. 7B is a cross-sectional view taken along the lines A-A' and B-B' of FIG. 7A. FIG. 7C is a cross-sectional view taken along the line C-C' of FIG. 7A. FIG. 7D is a view comparing a cell contact structure C21 and a peripheral contact structure C22. [0122] A semiconductor structure 500 may include a memory cell region R10 and a peripheral circuit region R20. A plurality of memory cells may be formed in the memory cell region R10. Each memory cell may include a buried word line 602, a bit line 509C, and a memory element 528. A transistor configuring a peripheral circuit (hereinafter, simply referred to as a 'peripheral, transistor') may be formed in the peripheral circuit region R20. The peripheral transistor may include a planar gate structure PG. The semiconductor structure 500 will be described below in detail.

[0123] An isolation layer 502 is formed in a substrate 501. A plurality of active regions 503 are defined in the memory cell region R10 by the isolation layer 502. An active region 503P may be defined in the peripheral circuit region R20 by the isolation layer 502.

[0124] Gate trenches 600 are formed in the memory cell region R10. A first gate dielectric layer 601 is formed on the surface of each gate trench 600. A buried word line 602 is formed on the first gate dielectric layer 601 to partially fill the gate trench 600. A sealing layer 603 is formed on the buried word line 602. The sealing layer 603 may extend up to the same level as an upper surface of the substrate 501. An upper surface of the buried word line 602 may be located at a level lower than the upper surface of the substrate 501.

[0125] A pair of first doping regions 504A and 504B may be formed in each active region 503. The first doping regions 504A and 504B may be separated from each other by the gate trench 600. The first doping regions 504A and 504B may be referred to as a source region and a drain region. The buried word line 602 and the first doping regions 504A and 504B may become a buried gate type transistor. The buried gate type transistor may improve a short channel effect by the buried word line 602.

[0126] A pair of second doping regions 504 may be formed in the active region 503P. The second doping regions 504 may include a low concentration source/drain region and a high concentration source/drain region, respectively. Third doping regions 504P may be formed in the second doping regions 504. The planar gate structure PG may be

formed on the active region 503P between the pair of second doping regions 504. The planar gate structure PG may include a second gate dielectric layer 507P, a silicon electrode 508P, a metal electrode 509P, and a gate cap layer 510P.

[0127] Bit line contact plugs 508C are formed on the substrate 501 in the memory cell region R10. Each bit line contact plug 508C may be coupled to any one first doping region 504A. Each bit line contact plug 508C is positioned in a first opening 506. The first opening 506 is formed in a hard mask layer 505. The hard mask layer 505 is formed on the substrate 501. The first opening 506 is a contact hole which exposes the first doping region 504A. The bottom surface of the bit line contact plug 508C may be located at a lower level than a top surface 501S of the substrate 501. The bit line contact plug 508C may be formed of polysilicon or metallic material. A portion of the bit line contact plug 508C may have a line width smaller than the diameter of the first opening 506. Thus, gaps G are formed on both sides of the bit line contact plug 508C. The gaps G are independently formed on both the sides of the bit line contact plug 508C. As a result, one bit line contact plug 508C and a pair of gaps G are positioned in each first opening **506**. The pair of gaps G is separated from each other by the bit fine contact plug 508C. The gaps G may be positioned between the bit line contact plug 508C and silicon plugs 520.

[0128] A bit line structure BL is formed on the bit line contact plug 508C. The bit line structure BL includes a bit line 509C and a bit line cap layer 510C which is on the bit line 509C. The bit line structure BL has a line shape which extends in a direction intersecting with the buried word line 602. A portion of the bit line 509C is coupled with the bit line contact plug 508C. When viewed from the cross-section taken along the line A-A', the bit line 509C and the bit line contact plug 508C may have the same line width. Therefore the bit line 509C may extend in any one direction while covering the bit line con tact plug 508C. The bit line 509C may include a metallic material. The bit line cap layer 510C may include a dielectric material. The bit line structure BL and the planar gate structure PG may be concurrently formed by using the same materials.

[0129] A cell contact structure C21 may be formed between neighboring bit line structures BL. The cell contact structure C21 is formed in a second opening 701. The cell contact structure C21 may be coupled to one of the pair of first doping regions 5048. The cell contact structure C21 may include the silicon plug 520 and a first metal plug 524. The first metal plug 524 may neighbor the bit line 509C. The silicon plug 520 may neighbor the bit line contact plug 508C.

[0130] A plug isolation layer 531C may be formed between neighboring cell contact structures C21. The plug isolation layer 531C may be formed between neighboring bit line structures BL and provide the second opening 701.

[0131] The cell contact structure C21 may include the silicon plug 520, an interface doping region 521, a first metal silicide 522, a first barrier 523, and the first metal plug 524. The silicon plug 520 may include a doped polysilicon, and the first metal plug 524 may include tungsten. The first metal silicide 522 is formed between the silicon plug 520 and the first metal plug 524. The first metal silicide 522 is an ohmic contact layer. A contact resistance is decreased by the first metal silicide 522. The contact resistance may be further improved by the interface doping region 521. The interface

doping region 521 may be a higher concentration than the dopant doped into the silicon plug 520. In another embodiment, the interface doping region 521 may be omitted.

[0132] Peripheral contact structures C22 may be formed in the peripheral circuit region R20. Each peripheral contact structure C22 may fill a third opening 702 in an interlayer dielectric layer 531. The peripheral contact structure C22 may include a second metal silicide 525, a second barrier 526, and a second metal plug 527. The second barrier 526 may be concurrently formed with the first barrier 523. The second metal plug 527 may be concurrently formed with the first metal plug 524. The second metal silicide 525 may be concurrently formed with the first metal silicide 522. A metal line 529 may be formed on the peripheral contact structure C22. The third opening 702 may include sidewall spacers 530. The second metal silicide 525 may be coupled to the third doping region 504P. In this structure, the contact resistance of the peripheral contact structure C22 may be improved.