(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6971538号

(P6971538)

(45) 発行日 令和3年11月24日(2021.11.24)

(24) 登録日 令和3年11月5日(2021.11.5)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| H04L 1/00  | (2006.01) | H04L 1/00  | A    |

| G06F 13/36 | (2006.01) | G06F 13/36 | 520Z |

| G06F 13/38 | (2006.01) | G06F 13/38 | 350  |

| G06F 11/10 | (2006.01) | G06F 11/10 | 632  |

請求項の数 17 (全 19 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2016-99930(P2016-99930)    |

| (22) 出願日  | 平成28年5月18日(2016.5.18)        |

| (65) 公開番号 | 特開2017-208710(P2017-208710A) |

| (43) 公開日  | 平成29年11月24日(2017.11.24)      |

| 審査請求日     | 令和1年5月20日(2019.5.20)         |

|           |                                                              |

|-----------|--------------------------------------------------------------|

| (73) 特許権者 | 316005926<br>ソニーセミコンダクタソリューションズ株<br>式会社<br>神奈川県厚木市旭町四丁目14番1号 |

| (74) 代理人  | 100121131<br>弁理士 西川 孝                                        |

| (74) 代理人  | 100082131<br>弁理士 稲本 義雄                                       |

| (72) 発明者  | 高橋 宏雄<br>神奈川県厚木市旭町四丁目14番1号 ソ<br>ニーセミコンダクタソリューションズ株式<br>会社内   |

最終頁に続く

(54) 【発明の名称】通信装置、通信方法、プログラム、および、通信システム

## (57) 【特許請求の範囲】

## 【請求項 1】

他の通信装置と信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信する送受信部と、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出するエラー検出部と

を備え、

前記プリアンブルの2ビット目は、前記他の通信装置によって駆動され、前記リードコマンドの受信の成功または失敗を示す信号であり、

前記エラー検出部は、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する

通信装置。

## 【請求項 2】

前記エラー検出部は、前記送受信部が受信したデータのうちの、奇数番目のビットから求められるパリティを偶数パリティとし、偶数番目のビットから求められるパリティを奇数パリティとする

請求項1に記載の通信装置。

10

20

**【請求項 3】**

前記エラー検出部は、前記送受信部が受信したデータのうちの、奇数番目のビットから求められるパリティを奇数パリティとし、偶数番目のビットから求められるパリティを偶数パリティとする

請求項 1 に記載の通信装置。

**【請求項 4】**

前記通信装置は、バスにおける制御の主導権を有する通信装置であり、前記他の通信装置は、前記通信装置による制御に従って通信を行う

請求項 1 に記載の通信装置。

**【請求項 5】**

前記送受信部により、前記プリアンブルが受信されて、そのプリアンブルに続いて受信された信号のビット列と、前記プリアンブルにより送信されることが指定されたタイプにおいて送信されるべきビット列とを比較することにより、エラーの発生を検出するエラー検出部と、

前記エラー検出部によりエラーの発生が検出された場合、前記プリアンブルに続いて所定ビット数に応じたクロックを送信するように、前記送受信部に対する指示を行うコンフリクト回避部と

をさらに備える請求項 1 に記載の通信装置。

**【請求項 6】**

前記送受信部から送信された信号を受信した前記他の通信装置から送信されてくる受信確認信号および非受信確認信号のいずれかを検出する確認信号検出部と、

前記確認信号検出部により前記非受信確認信号が検出されたとき、前記非受信確認信号に続く所定数のビットを無視するコンフリクト回避部と

をさらに備える請求項 1 に記載の通信装置。

**【請求項 7】**

前記送受信部は、前記他の通信装置から読み出されるリードデータを受信し、前記リードデータの後に送受信されるプリアンブルの 2 ビット目に対する駆動を常に行う

請求項 1 に記載の通信装置。

**【請求項 8】**

前記送受信部は、通常の転送レートでデータ通信を行うSDR ( Standard Data Rate ) モード、および、SDRモードよりも高い転送レートでデータ通信を行うHDR ( High Data Rate ) モードで、信号の送受信を行うことができる

請求項 1 に記載の通信装置。

**【請求項 9】**

前記エラー検出部は、前記HDRモードにおいて前記送受信部が受信したデータに対して前記パリティのチェックを実行する

請求項 8 に記載の通信装置。

**【請求項 10】**

前記送受信部は、1 ビットずつ逐次的にシリアルデータを伝送するデータ信号線、および、所定の周波数のシリアルクロックを伝送するクロック信号線の 2 本の信号線を介して通信を行う

請求項 1 に記載の通信装置。

**【請求項 11】**

前記送受信部、I3C ( Improved Inter Integrated Circuit ) の規格に準じた通信を行う

請求項 1 に記載の通信装置。

**【請求項 12】**

他の通信装置と信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信し、

受信したデータに対するパリティチェックを行うことでエラーの発生を検出し、

前記プリアンブルの 2 ビット目は、前記他の通信装置によって駆動され、前記リードコ

10

20

30

40

50

マンドの受信の成功または失敗を示す信号であり、

前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する

ステップを含む通信方法。

【請求項13】

他の通信装置と信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信し、

10

受信したデータに対するパリティチェックを行うことでエラーの発生を検出し、

前記プリアンブルの2ビット目は、前記他の通信装置によって駆動され、前記リードコマンドの受信の成功または失敗を示す信号であり、

前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する

ステップを含む通信処理をコンピュータに実行させるプログラム。

【請求項14】

20

バスにおける制御の主導権を有する第1の通信装置と、

前記第1の通信装置による制御に従って通信を行う第2の通信装置とを備え、

前記第1の通信装置が、

他の通信装置と信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信する送受信部と、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出するエラー検出部と

を有し、

前記プリアンブルの2ビット目は、前記他の通信装置によって駆動され、前記リードコマンドの受信の成功または失敗を示す信号であり、

30

前記エラー検出部は、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する

通信システム。

【請求項15】

前記エラー検出部は、前記送受信部が受信したデータのうちの、奇数番目のビットから求められるパリティを偶数パリティとし、偶数番目のビットから求められるパリティを奇数パリティとする

40

請求項14に記載の通信システム。

【請求項16】

前記エラー検出部は、前記送受信部が受信したデータのうちの、奇数番目のビットから求められるパリティを奇数パリティとし、偶数番目のビットから求められるパリティを偶数パリティとする

請求項14に記載の通信システム。

【請求項17】

前記送受信部により、前記プリアンブルが受信されて、そのプリアンブルに続いて受信された信号のビット列と、前記プリアンブルにより送信されることが指定されたタイプに

50

おいて送信されるべきビット列とを比較することにより、エラーの発生を検出するエラー検出部と、

前記エラー検出部によりエラーの発生が検出された場合、前記プリアンブルに続いて所定ビット数に応じたクロックを送信するように、前記送受信部に対する指示を行うコンフリクト回避部と

をさらに備える請求項1-4に記載の通信システム。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、通信装置、通信方法、プログラム、および、通信システムに関し、特に、より確実に通信を行うことができるようとした通信装置、通信方法、プログラム、および、通信システムに関する。 10

【背景技術】

【0002】

従来、複数のデバイスが実装されたボード内でバスを介したデバイス間の通信に用いられるバスIF(Interface)として、例えば、I2C(Inter-Integrated Circuit)が多く利用されている。

【0003】

また、近年、I2Cの高速化を実現することが求められており、次世代の規格としてI3C(Improved Inter Integrated Circuit)の規定が進行している。I3Cでは、マスタおよびスレーブは、2本の信号線を用いて双方向に通信を行うことができ、例えば、マスタからスレーブへのデータ転送(ライト転送)と、スレーブからマスタへのデータ転送(リード転送)とが行われる。 20

【0004】

例えば、特許文献1には、ホスト・プロセッサとサブシステム・コントローラとを、I2Cにより相互接続するディジタル・データ処理システムが開示されている。また、特許文献2には、標準I2Cプロトコルの上部に層状に配置された通信プロトコルを実現する方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000-99448号公報

【特許文献2】特開2002-175269号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、上述したようなI3Cでは、例えば、マスタおよびスレーブにおいて、パリティやCRC(Cyclic Redundancy Check)などによるエラー検出が行われることが規定されているが、そのようなエラー検出が用意されていない信号の送受信も行われる。そのため、エラー検出が用意されていない信号にエラーが発生したときに、マスタおよびスレーブのどちらもデータ信号線に対する駆動を行わない状態となることがあった。そのため、例えば、受信したデータが正しいものであるかを検出することが困難になり、正常な通信を行うことができなくなることが懸念される。 40

【0007】

本開示は、このような状況に鑑みてなされたものであり、より確実に通信を行うことができるようとするものである。

【課題を解決するための手段】

【0008】

本開示の第1の側面の通信装置は、他の通信装置と信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信する送受信部と、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出するエラー検出部とを備え、前記プリアンブルの2ビット目は、前記他の通信装置によって駆動され、前記リードコマンドの受信の成功または失敗を示す信号であり、前記エラー検出部は、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する。

#### 【0009】

本開示の第1の側面の通信方法またはプログラムは、他の通信装置と信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信し、受信したデータに対するパリティチェックを行うことでエラーの発生を検出し、前記プリアンブルの2ビット目は、前記他の通信装置によって駆動され、前記リードコマンドの受信の成功または失敗を示す信号であり、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する。

#### 【0010】

本開示の第1の側面においては、他の通信装置と信号の送受信が行われることによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータが受信され、受信したデータに対するパリティチェックを行うことでエラーの発生が検出される。そして、プリアンブルの2ビット目は、他の通信装置によって駆動され、リードコマンドの受信の成功または失敗を示す信号であり、データに含まれている2ビットのパリティのうち、一方が偶数パリティとされ、他方が奇数パリティとされてエラー検出が行われることで、データが全て1または0である場合であっても、そのデータが正しいものであるのか、プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかが判断される。

#### 【0011】

本開示の第2の側面の通信システムは、バスにおける制御の主導権を有する第1の通信装置と、前記第1の通信装置による制御に従って通信を行う第2の通信装置とを備え、前記第1の通信装置が、信号の送受信を行うことによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータを受信する送受信部と、前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出するエラー検出部とを有し、前記プリアンブルの2ビット目は、前記他の通信装置によって駆動され、前記リードコマンドの受信の成功または失敗を示す信号であり、前記エラー検出部は、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行うことで、前記データが全て1または0である場合であっても、そのデータが正しいものであるのか、前記プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する。

#### 【0012】

本開示の第2の側面においては、信号の送受信が行われることによって、リードコマンドの送信に続くプリアンブルの送受信の後にデータが受信され、受信したデータに対するパリティチェックを行うことでエラーの発生が検出される。そして、プリアンブルの2ビット目は、他の通信装置によって駆動され、リードコマンドの受信の成功または失敗を示す信号であり、データに含まれている2ビットのパリティのうち、一方が偶数パリティとされ、他方が奇数パリティとされてエラー検出が行われることで、データが全て1または0である場合であっても、そのデータが正しいものであるのか、プリアンブルの2ビット目に1ビットエラーが発生したことによってデータ信号線に対する駆動が行われない状態によるものであるのかを判断する。

10

20

30

40

50

によるものであるのかが判断される。

**【発明の効果】**

**【0013】**

本開示の第1および第2の側面によれば、より確実に通信を行うことができる。

**【図面の簡単な説明】**

**【0014】**

**【図1】**本技術を適用したバスIFの一実施の形態の構成例を示すブロック図である。

**【図2】**プリアンブルに発生するエラーについて説明する図である。

**【図3】**パリティによるエラー検出について説明する図である。

**【図4】**パリティによるエラー検出について説明する図である。

10

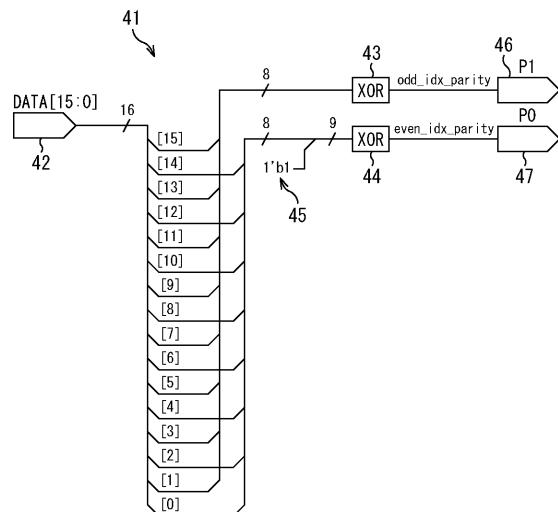

**【図5】**パリティエラー検出器の第1の構成例を示す図である。

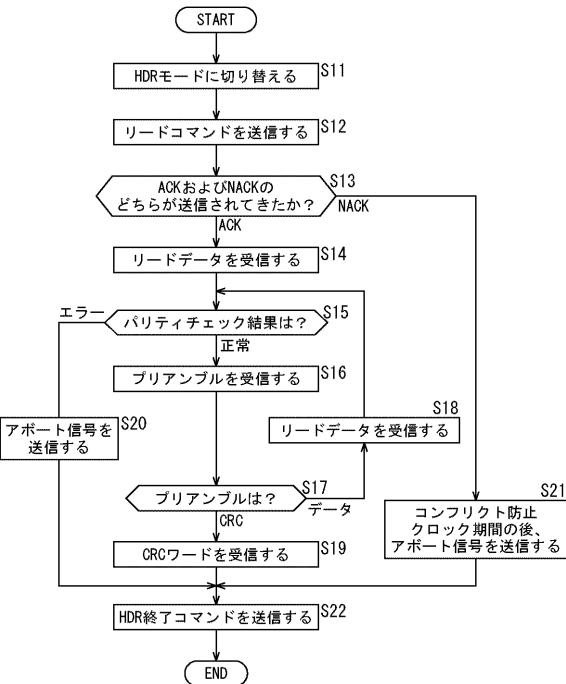

**【図6】**マスタのDDRモードでの通信処理を説明するフローチャートである。

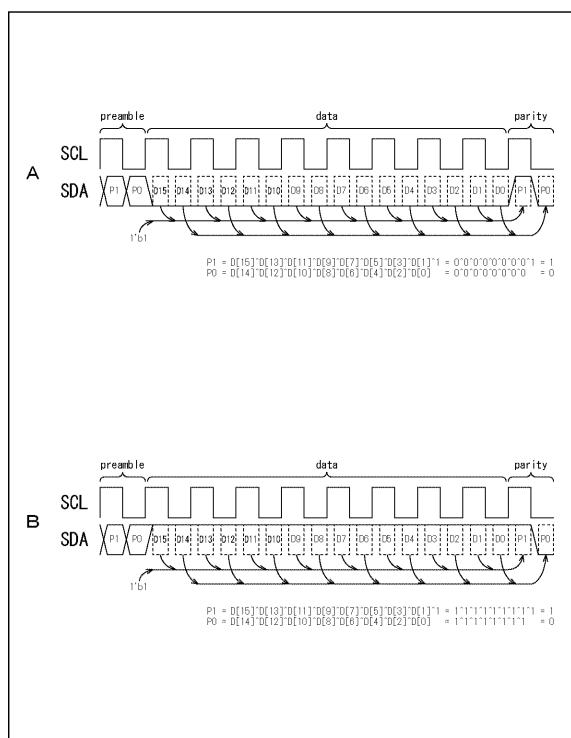

**【図7】**パリティによるエラー検出について説明する図である。

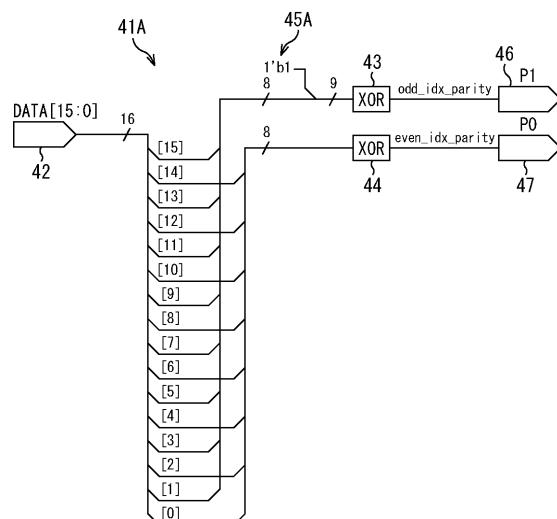

**【図8】**パリティエラー検出器の第2の構成例を示す図である。

**【図9】**本技術を適用したコンピュータの一実施の形態の構成例を示すブロック図である

。

**【発明を実施するための形態】**

**【0015】**

以下、本技術を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。

20

**【0016】**

<バスIFの構成例>

**【0017】**

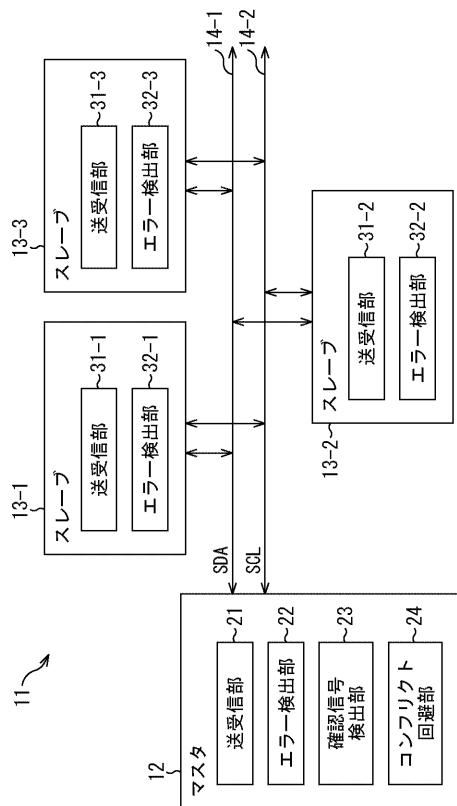

図1は、本技術を適用したバスIFの一実施の形態の構成例を示すブロック図である。

**【0018】**

図1に示されているバスIF11は、マスター12と3台のスレーブ13-1乃至13-3とが、データ信号線14-1およびクロック信号線14-2を介して接続されて構成される。

**【0019】**

マスター12は、バスIF11における制御の主導権を有しており、データ信号線14-1およびクロック信号線14-2を介して、スレーブ13-1乃至13-3と通信を行うことができる。

30

**【0020】**

スレーブ13-1乃至13-3は、マスター12による制御に従って、データ信号線14-1およびクロック信号線14-2を介して、マスター12と通信を行うことができる。なお、スレーブ13-1乃至13-3は、それぞれ同様に構成されており、以下、それらを区別する必要がない場合、単にスレーブ13と称し、スレーブ13を構成する各ブロックについても同様とする。

**【0021】**

データ信号線14-1およびクロック信号線14-2は、マスター12およびスレーブ13の間で信号を伝送するのに用いられる。例えば、バスIF11では、データ信号線14-1を介して、1ビットずつ逐次的にシリアルデータ( SDA : Serial Data )が伝送され、クロック信号線14-2を介して、所定の周波数のシリアルクロック( SCL : Serial Clock )が伝送される。

40

**【0022】**

また、バスIF11では、I3Cの規格に準じて、通信速度が異なる複数の伝送方式が規定されており、マスター12は、それらの伝送方式を切り替えることができる。例えば、バスIF11では、データの転送レートに応じて、通常の転送レートでデータ通信を行うSDR( Standard Data Rate )モード、および、SDRモードよりも高い転送レートでデータ通信を行うHDR( High Data Rate )モードが規定されている。また、HDRモードでは、DDR( Dou

50

ble Data Rate) モード、TSP(Ternary Symbol Pure-Bus)モード、および、TSL(Ternary Symbol Legacy-inclusive-Bus)モードの3つのモードが規格で定義されている。なお、バス I/F 1/1 では、通信を開始するときには SDR モードで通信を行うことが規定されている。

#### 【0023】

マスター 1/2 は、送受信部 2/1、エラー検出部 2/2、確認信号検出部 2/3、およびコンフリクト回避部 2/4 を備えて構成される。

#### 【0024】

送受信部 2/1 は、データ信号線 1/4 - 1 およびクロック信号線 1/4 - 2 を介して、スレーブ 1/3 と信号の送受信を行う。例えば、送受信部 2/1 は、クロック信号線 1/4 - 2 を駆動することにより送信するシリアルクロックのタイミングに合わせて、データ信号線 1/4 - 1 に対する駆動を行う（電位を H レベルまたは L レベルに切り替える）ことにより、スレーブ 1/3 に信号を送信する。また、送受信部 2/1 は、クロック信号線 1/4 - 2 のシリアルクロックのタイミングに合わせて、スレーブ 1/3 がデータ信号線 1/4 - 1 に対する駆動を行うことによって、スレーブ 1/3 から送信されてくる信号を受信する。なお、クロック信号線 1/4 - 2 に対する駆動は、常に、マスター 1/2 側により行われる。さらに、送受信部 2/1 は、スレーブ 1/3 に送信するデータに、後述するようなパリティを附加して送信を行う。

#### 【0025】

エラー検出部 2/2 は、送受信部 2/1 が受信した信号に発生しているエラーを検出する。例えば、エラー検出部 2/2 は、送受信部 2/1 が受信した信号に対するパリティチェックや巡回冗長検査 (CRC) などを行ったり、スレーブ 1/3 からマスター 1/2 へ送信権を移行する際に発行されるトークンを確認したりすることで、エラーを検出することができる。そして、エラー検出部 2/2 は、送受信部 2/1 が受信した信号にエラーが発生していることを検出した場合、例えば、送受信部 2/1 に対してスレーブ 1/3 との通信を最初からやり直すように指示することができる。

#### 【0026】

確認信号検出部 2/3 は、送受信部 2/1 から送信された信号を受信したスレーブ 1/3 から送信されてくる ACK (受信確認信号) または NACK (非受信確認信号) を検出することにより、スレーブ 1/3 がコマンドやデータなどの受信に成功したか否かを確認する。例えば、バス I/F 1/1 では、信号にエラーが発生せずに、スレーブ 1/3 がコマンドやデータなどの受信に成功したときには、スレーブ 1/3 からマスター 1/2 に ACK を送信するように規定されている。また、バス I/F 1/1 では、信号にエラーが発生して、スレーブ 1/3 がコマンドやデータなどの受信に失敗したときには、スレーブ 1/3 からマスター 1/2 に NACK を送信するように規定されている。

#### 【0027】

従って、確認信号検出部 2/3 は、マスター 1/2 から送信されるコマンドやデータなどに対して、スレーブ 1/3 から送信されてくる ACK を検出した場合には、スレーブ 1/3 がコマンドやデータなどを受信することに成功したと確認することができる。一方、確認信号検出部 2/3 は、マスター 1/2 から送信されるコマンドやデータなどに対して、スレーブ 1/3 から送信されてくる NACK を検出した場合には、スレーブ 1/3 がコマンドやデータなどを受信することに失敗したと確認することができる。

#### 【0028】

コンフリクト回避部 2/4 は、例えば、確認信号検出部 2/3 により NACK が検出された場合、NACK に続く所定数のビットを無視した後に、通信を途中で遮断することを指示するアボート信号を送信するように、送受信部 2/1 に対する指示を行う。これにより、コンフリクト回避部 2/4 は、例えば、スレーブ 1/3 から送信されるリードデータと、マスター 1/2 から送信される HDR 終了コマンドによりコンフリクトが発生することを回避することができる。なお、マスター アボートを確実に行うために、リードデータの後に送受信されるプリアンブルの 2 ビット目に対する駆動は、マスター 1/2 が常に行う。

10

20

30

40

50

**【0029】**

さらに、コンフリクト回避部24は、送受信部21により、CRCワードの送信を指示するプリアンブルが受信され、エラー検出部22により、そのプリアンブルに続いて受信された信号にトークンエラーまたはCRCエラーの発生が検出された場合、プリアンブルに続いて、CRCワードとリードデータとの差に対応するビット数に応じたクロックを送信した後に、通信を途中で遮断することを指示するアボート信号を送信するように、送受信部21に対する指示を行う。これにより、コンフリクト回避部24は、例えば、スレーブ13から送信されるリードデータと、マスタ12から送信されるHDR終了コマンドによりコンフリクトが発生することを回避することができる。

**【0030】**

スレーブ13は、送受信部31およびエラー検出部32を備えて構成される。

**【0031】**

送受信部31は、データ信号線14-1およびクロック信号線14-2を介して、マスタ12と信号の送受信を行う。例えば、送受信部31は、クロック信号線14-2のシリアルクロックのタイミングに合わせて、マスタ12がデータ信号線14-1に対する駆動を行うことによって、マスタ12から送信されてくる信号を受信する。また、送受信部31は、クロック信号線14-2のシリアルクロックのタイミングに合わせて、データ信号線14-1に対する駆動を行うことによって、マスタ12に信号を送信する。さらに、送受信部31は、マスタ12に送信するデータに、後述するようなパリティを附加して送信を行う。

**【0032】**

エラー検出部32は、マスタ12のエラー検出部22と同様に、送受信部31が受信した信号に発生しているエラーを検出する。そして、エラー検出部32は、送受信部31が受信した信号にエラーが発生していない場合、その信号により伝送されるコマンドやデータなどの受信に成功したことを伝えるACKを、送受信部31によりマスタ12に送信させる。一方、エラー検出部32は、送受信部31が受信した信号にエラーが発生していた場合、その信号により伝送されるコマンドやデータなどの受信に失敗したことを伝えるNACKを、送受信部31によりマスタ12に送信させる。

**【0033】**

さらに、エラー検出部32は、例えば、送受信部31が受信した信号にエラーが発生し、正常な通信を行うことができない場合には、その後の一切の通信を無視し、マスタ12に対する応答を停止してスレーブ13を待機状態とさせる。

**【0034】**

以上のようにバスIF11は構成されており、マスタ12およびスレーブ13は、データ信号線14-1およびクロック信号線14-2を介して信号を送受信することができる。

**【0035】**

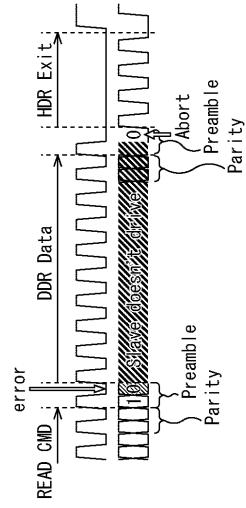

ところで、バスIF11では、DDRモード時において、プリアンブルと呼ばれる2ビットの信号を使用して、次に送信するデータのタイプを指定するように規定されている。しかしながら、プリアンブルには、パリティやCRCによるエラー検出が用意されていないため、プリアンブルにエラーが発生した場合には、そのエラーを検出することができない。

**【0036】**

例えば、マスタ12がスレーブ13にリードコマンドを送信したとき、リードコマンドに続いて送信されるプリアンブルでは、1ビット目はマスタ12により駆動され、2ビット目はスレーブ13により駆動される。例えば、マスタ12は、その1ビット目により、リードコマンドに続いてデータが送信されることを指定し、スレーブ13は、その2ビット目により、リードコマンドの受信に成功したか否かを送信することができる。例えば、スレーブ13は、リードコマンドに続くプリアンブルの2ビット目を0に駆動することによってリードコマンドの受信に成功したことを示すACKを送信し、その2ビット目を1に駆動することによってリードコマンドの受信に失敗したことを示すNACKを送信する。

10

20

30

40

50

**【 0 0 3 7 】**

しかしながら、このプリアンブルの2ビット目において、1ビットの値が反転する1ビットエラーが発生した場合、マスタ12は、エラーの発生を検出することができない。従って、スレーブ13が、リードコマンドの受信に失敗したことを伝えるNACKを送信したとき、そのNACKに1ビットエラーが発生すると、マスタ12は、スレーブ13からACKが送信されてきたと誤認識することになる。この場合、マスタ12は、スレーブ13からリードデータが送信されてくるのを待機する状態となるが、スレーブ13は、リードコマンドの受信に失敗しているため、リードデータの送信は行われない。

**【 0 0 3 8 】**

そのため、図2に示すように、リードコマンドに続くプリアンブルの2ビット目に1ビットエラーが発生すると、マスタ12およびスレーブ13のどちらもデータ信号線14-1に対する駆動を行わない状態となる。10

**【 0 0 3 9 】**

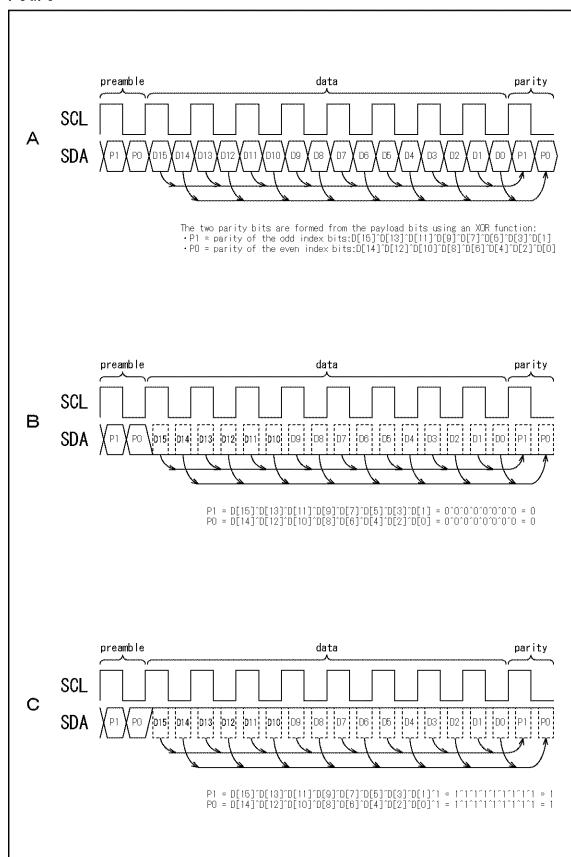

ここで、上述したように、マスタ12のエラー検出部22は、スレーブ13から送信されてくるリードデータに含まれるパリティビットを用いて、そのリードデータに発生するエラーを検出することができる。例えば、図3Aに示すように、エラー検出部22は、データの奇数ビットから求められるパリティビットP1と、データの偶数ビットから求められるパリティビットP0に基づいて、データにエラーが発生しているか否かを検出することができる。例えば、従来、パリティビットP1は、データの奇数ビットの論理和が偶数のとき0を取り、パリティビットP0は、データの偶数ビットの論理和が偶数のとき0を取りように設定されている。20

**【 0 0 4 0 】**

従って、図3Bに示すように、リードデータが全て0である場合、パリティビットP1およびP0はどちらも0となる。このため、データ信号線14-1に対するHレベル維持が行われない状態（即ち、データ信号線14-1がLレベル）で、マスタ12およびスレーブ13のいずれもデータ信号線14-1に対する駆動を行わない場合、リードデータは全て0となる。従って、この場合、実際に全て0のデータが送信してきたときと区別することができない。

**【 0 0 4 1 】**

同様に、図3Cに示すように、リードデータが全て1である場合、パリティビットP1およびP0はどちらも1となる。このため、データ信号線14-1に対するHレベル維持が行われる状態で、マスタ12およびスレーブ13のいずれもデータ信号線14-1に対する駆動を行わない場合、リードデータは全て1となる。従って、この場合、実際に全て1のデータが送信してきたときと区別することができない。30

**【 0 0 4 2 】**

そこで、マスタ12のエラー検出部22は、パリティビットP1は、データの奇数ビットの論理和が偶数のとき0を取り偶数パリティとし、パリティビットP0は、データの偶数ビットの論理和が奇数のとき0を取り奇数パリティとするように設定される。なお、以下では、マスタ12のエラー検出部22の構成について説明するが、スレーブ13のエラー検出部32も同様に構成されている。そして、送受信部21および送受信部31により、以下で説明するようなパリティが付加されてデータが送信される。40

**【 0 0 4 3 】**

これにより、例えば、図4Aに示すように、リードデータが全て0である場合、パリティビットP1は0となり、パリティビットP0は1となる。同様に、例えば、図4Bに示すように、リードデータが全て1である場合、パリティビットP1は0となり、パリティビットP0は1となる。このため、エラー検出部22は、マスタ12およびスレーブ13のいずれもデータ信号線14-1に対する駆動を行わない場合、パリティが一致しないことより、受信したデータは正確ではなく、エラーが発生していることを検出することができる。

**【 0 0 4 4 】**5020304050

< パリティエラー検出器の第 1 の構成例 >

**【 0 0 4 5 】**

マスター 12 のエラー検出部 22 は、図 5 に示すようなパリティエラー検出器 41 を有して構成される。

**【 0 0 4 6 】**

図 5 に示すように、パリティエラー検出器 41 は、入力端子 42、XOR ゲート 43 および 44、1 ビット付加部 45、並びに、出力端子 46 および 47 を備えて構成される。

**【 0 0 4 7 】**

パリティエラー検出器 41 の入力端子 42 には、データ信号線 14-1 を介して供給されるシリアルデータが入力される。そして、シリアルデータの奇数ビットは、XOR ゲート 43 に供給され、シリアルデータの偶数ビットは、XOR ゲート 44 に供給されるように、入力端子 42 が XOR ゲート 43 および 44 に接続される。10

**【 0 0 4 8 】**

そして、パリティエラー検出器 41 では、XOR ゲート 44 に対して 1 ビット付加部 45 から 1 の値の 1 ビットが付加される。これにより、パリティエラー検出器 41 は、出力端子 46 から出力されるパリティビット P1 は、データの奇数ビットの論理和が偶数のとき 0 を取り、出力端子 47 から出力されるパリティビット P0 は、データの奇数ビットの論理和が奇数のとき 0 を取るように構成される。

**【 0 0 4 9 】**

このように構成されるパリティエラー検出器 41 は、例えば、データ信号線 14-1 に対する H レベル維持が行われない状態（即ち、データ信号線 14-1 が L レベル）で、マスター 12 およびスレーブ 13 のいずれもデータ信号線 14-1 に対する駆動を行わない場合、データを正しく受信することができなかったと検出することができる。即ち、この場合、受信する信号は全て 0 となるが、パリティビット P1 は 0 となり、かつ、パリティビット P0 は 1 となるため、パリティが一致しないことよりエラーを検出すること（図 4A を参照）ができる。20

**【 0 0 5 0 】**

同様に、パリティエラー検出器 41 は、例えば、データ信号線 14-1 に対する H レベル維持が行われる状態で、マスター 12 およびスレーブ 13 のいずれもデータ信号線 14-1 に対する駆動を行わない場合、データを正しく受信することができなかったと検出することができる。即ち、この場合、受信する信号は全て 1 となるが、パリティビット P1 は 0 となり、かつ、パリティビット P0 は 1 となるため、パリティが一致しないことよりエラーを検出すること（図 4B を参照）ができる。30

**【 0 0 5 1 】**

また、パリティエラー検出器 41 では、パリティビット P1 を偶数パリティとし、パリティビット P0 を奇数パリティとすることで、例えば、マスター 12 がデータ信号線 14-1 を H レベルに維持し続ける場合を考慮すると、早期にエラーを検出することができる。即ち、マスター 12 がデータ信号線 14-1 を H レベルに維持し続ける場合にはデータが全て 1 となり、パリティビット P1 が 0 となることよりエラーを早く検出することができる。40

**【 0 0 5 2 】**

< パリティチェックを正常に行う通信方法 >

**【 0 0 5 3 】**

図 6 は、マスター 12 が、HDR モードのひとつである DDR モードでスレーブ 13 からデータを読み出す通信処理（DDR Read）を説明するフローチャートである。

**【 0 0 5 4 】**

ステップ S11において、マスター 12 は、通信を SDR モードから HDR モードに切り替える処理を行う。具体的には、マスター 12 では、送受信部 21 が、データ信号線 14-1 およびクロック信号線 14-2 を駆動して、SDR モードにおいて、バス IF 11 を構成する全てのスレーブ 13 を対象として一斉にコマンドを送信することを通知するプロードキャス50

トコマンド (0x7E+R/W=0) を送信する。その後、マスタ12では、ブロードキャストコマンドの受信が成功したことを確認するためにスレーブ13から送信されてくるACKを受信すると、送受信部21が、HDRモードに入るためのコモンコマンドコード (ENTHDR CCC(0x20)) を送信する。

【0055】

ステップS12において、マスタ12の送受信部21は、データ信号線14-1およびクロック信号線14-2を駆動して、リードコマンドを送信する。

【0056】

ステップS13において、送受信部21は、リードコマンドを送信した後のプリアンブルの2ビット目の値を検出し、スレーブ13からACKおよびNACKのどちらが送信されてきたかを判定する。即ち、送受信部21は、リードコマンドを送信した後のプリアンブルの2ビット目が0であることを検出した場合、スレーブ13からACKが送信されてきたと判定する。一方、送受信部21は、リードコマンドを送信した後のプリアンブルの2ビット目が1であることを検出した場合、スレーブ13からNACKが送信されてきたと判定する。

【0057】

ステップS13において、送受信部21が、スレーブ13からACKが送信されてきたと判定した場合、処理はステップS14に進む。

【0058】

ステップS14において、送受信部21は、スレーブ13から送信されてくるリードデータを受信する。

【0059】

ステップS15において、エラー検出部22は、ステップS14で送受信部21が受信したデータに対するパリティチェックを行って、データにエラーが発生しているか否かを判定する。このとき、図4を参照して上述したように、パリティビットP1は、データの奇数番目のビットの論理和が偶数のとき0を取り、パリティビットP1は、データの偶数番目のビットの論理和が奇数のとき0を取る。

【0060】

ステップS15において、エラー検出部22が、データにエラーが発生していない、即ち、データが正常であると判定した場合、処理はステップS16に進み、送受信部21は、データに続いて送信されてくるプリアンブルを受信する。

【0061】

ステップS17において、送受信部21は、ステップS16で受信したプリアンブルにより次に送信されることが指定されているのは、データおよびCRCワードのどちらであるかを判定する。

【0062】

ステップS17において、送受信部21が、次に送信されてくるのはデータであると判定した場合、処理はステップS18に進み、送受信部21はリードデータを受信した後、処理はステップS15に戻って、以下、同様の処理が繰り返される。

【0063】

一方、ステップS17において、送受信部21が、次に送信されてくるのはCRCワードであると判定した場合、処理はステップS19に進み、送受信部21はCRCワードを受信する。

【0064】

ステップS19の処理後、処理はステップS22に進む。または、ステップS15でパリティチェックの結果がエラーであると判定された場合、処理はステップS20に進み、スレーブ13に対して、処理を中断することを指示するアボート信号を送信した後、処理はステップS22に進む。また、ステップS13でNACKが送信されてきたと判定された場合、処理はステップS21に進み、所定のビット数のコンフリクト防止クロック期間の経過後、送受信部21は、スレーブ13に対して、処理を中断することを指示するアボート信号を送信して、処理はステップS22に進む。

10

20

30

40

50

**【 0 0 6 5 】**

ステップ S 2 2において、送受信部 2 1はHDR終了コマンドを送信し、これにより、マスタ 1 2がDDRモードでスレーブ 1 3からデータを読み出す通信処理(DDR Read)は終了される。

**【 0 0 6 6 】**

以上のように、バス I F 1 1では、例えば、マスタ 1 2がACKを受信したと判定したとき、そのACKがNACKの1ビットエラーであってデータ信号線 1 4 - 1に対する駆動を行わぬ状態が発生したとしても、エラー検出部 2 2がパリティチェックを行うことで、受信したデータが正しいものではないことを検出することができる。これにより、マスタ 1 2は、受信したデータが正しいものであるのか、データ信号線 1 4 - 1に対する駆動を行わぬ状態によるものであるのかを正確に判断して、より確実に通信を行うことができる。10

**【 0 0 6 7 】**

<パリティエラー検出器の第2の構成例>

**【 0 0 6 8 】**

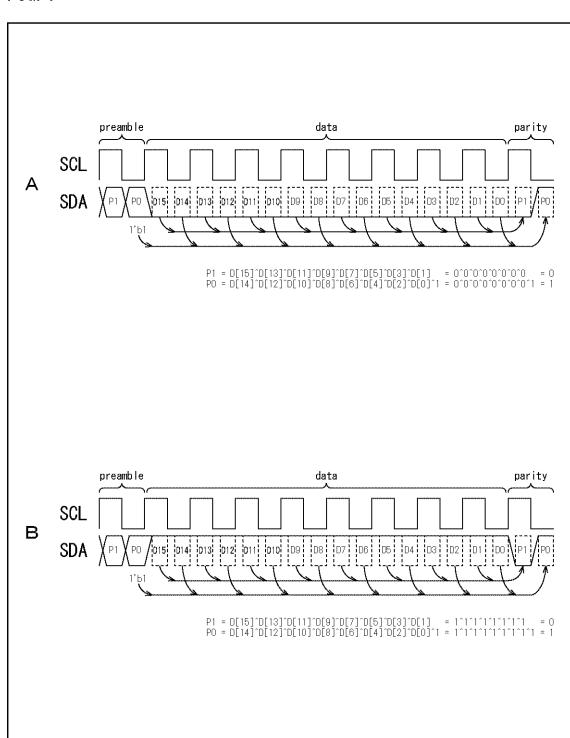

図 7 および図 8 を参照して、パリティエラー検出器 4 1 の第2の構成例について説明する。

**【 0 0 6 9 】**

上述の図 4 および図 5 を参照して説明したパリティエラー検出器 4 1 は、パリティビット P 1 は、データの奇数ビットの論理和が偶数のとき 0を取り、パリティビット P 0 は、データの偶数ビットの論理和が奇数のとき 0を取りるように構成されている。20

**【 0 0 7 0 】**

これに対し、図 7 および図 8 に示すように、パリティエラー検出器 4 1 A は、図 5 のパリティエラー検出器 4 1 とは逆に、パリティビット P 1 は、データの奇数ビットの論理和が偶数のとき 1を取り、パリティビット P 0 は、データの偶数ビットの論理和が奇数のとき 1を取りように構成されている。

**【 0 0 7 1 】**

このように構成されるパリティエラー検出器 4 1 A においても、例えば、データ信号線 1 4 - 1に対するHレベル維持が行わぬ状態(即ち、データ信号線 1 4 - 1がLレベル)で、マスタ 1 2およびスレーブ 1 3のいずれもデータ信号線 1 4 - 1に対する駆動を行わぬ場合、データを正しく受信することができなかつたと検出することができる。即ち、この場合、図 7 A に示すように、リードデータは全て 0となるが、パリティビット P 1 は 1となり、かつ、パリティビット P 0 は 0となるため、パリティが一致しないことよりエラーを検出することができる。30

**【 0 0 7 2 】**

同様に、パリティエラー検出器 4 1 A は、例えば、データ信号線 1 4 - 1に対するHレベル維持が行われる状態で、マスタ 1 2およびスレーブ 1 3のいずれもデータ信号線 1 4 - 1に対する駆動を行わぬ場合、データを正しく受信することができなかつたと検出することができる。即ち、この場合、図 7 B に示すように、リードデータは全て 1となるが、パリティビット P 1 は 1となり、かつ、パリティビット P 0 は 0となるため、パリティが一致しないことよりエラーを検出することができる。40

**【 0 0 7 3 】**

なお、本技術は、I3Cの規格に従ったバス I F 1 1に限定されることはなく、その他の規格に従ったバス I F 1 1に適用することができる。また、図 1 に示すバス I F 1 1では、スレーブ 1 3 - 1乃至 1 3 - 3が接続された構成例が示されているが、スレーブ 1 3は、例えば、1台または2台でもよく、あるいは、3台以上でもよい。

**【 0 0 7 4 】**

なお、上述のフローチャートを参照して説明した各処理は、必ずしもフローチャートとして記載された順序に沿って時系列に処理する必要はなく、並列的あるいは個別に実行される処理(例えば、並列処理あるいはオブジェクトによる処理)も含むものである。また50

、プログラムは、1のCPUにより処理されるものであっても良いし、複数のCPUによって分散処理されるものであっても良い。

【0075】

また、本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

【0076】

また、上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータなどに、プログラムが記録されたプログラム記録媒体からインストールされる。

【0077】

<ハードウェアの構成例>

【0078】

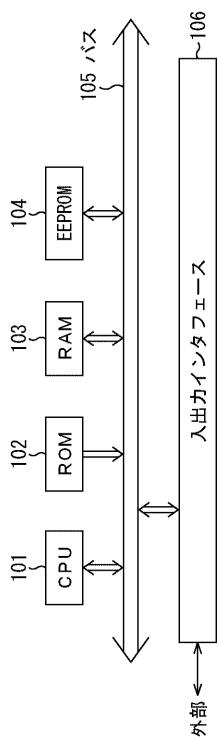

図9は、上述した一連の処理をプログラムにより実行するコンピュータのハードウェアの構成例を示すブロック図である。

【0079】

コンピュータにおいて、CPU(Central Processing Unit)101, ROM(Read Only Memory)102, RAM(Random Access Memory)103、およびEEPROM(Electronically Erasable and Programmable Read Only Memory)104は、バス105により相互に接続されている。バス105には、さらに、入出力インターフェース106が接続されており、入出力インターフェース106が外部(例えば、図1のデータ信号線14-1およびクロック信号線14-2)に接続される。

【0080】

以上のように構成されるコンピュータでは、CPU101が、例えば、ROM102およびEEPROM104に記憶されているプログラムを、バス105を介してRAM103にロードして実行することにより、上述した一連の処理が行われる。また、コンピュータ(CPU101)が実行するプログラムは、ROM102に予め書き込んでおく他、入出力インターフェース106を介して外部からEEPROM104にインストールしたり、更新したりすることができる。

【0081】

なお、本技術は以下のような構成も取ることができる。

(1)

他の通信装置と信号の送受信を行う送受信部と、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出するエラー検出部と

を備え、

前記エラー検出部は、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行う

を備える通信装置。

(2)

前記エラー検出部は、前記送受信部が受信したデータのうちの、奇数番目のビットから求められるパリティを偶数パリティとし、偶数番目のビットから求められるパリティを奇数パリティとする

上記(1)に記載の通信装置。

(3)

前記エラー検出部は、前記送受信部が受信したデータのうちの、奇数番目のビットから求められるパリティを奇数パリティとし、偶数番目のビットから求められるパリティを偶数パリティとする

10

20

30

40

50

上記(1)に記載の通信装置。

(4)

前記送受信部は、前記他の通信装置に送信するデータに付加する2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとする

上記(1)から(3)までのいずれかに記載の通信装置。

(5)

前記通信装置は、バスにおける制御の主導権を有する通信装置であり、前記他の通信装置は、前記通信装置による制御に従って通信を行う

上記(1)から(4)までのいずれかに記載の通信装置。

(6)

前記通信装置は、バスにおける制御の主導権を有する他の通信装置による制御に従って通信を行う

上記(1)から(5)までのいずれかに記載の通信装置。

(7)

前記送受信部により、次に送信するデータのタイプを指定するプリアンブルが受信されて、そのプリアンブルに続いて受信された信号のビット列と、前記プリアンブルにより送信されることが指定されたタイプにおいて送信されるべきビット列とを比較することにより、エラーの発生を検出するエラー検出部と、

前記エラー検出部によりエラーの発生が検出された場合、前記プリアンブルに続いて所定ビット数に応じたクロックを送信した後に、通信を途中で遮断することを指示するアボート信号を送信するように、前記送受信部に対する指示を行うコンフリクト回避部と

をさらに備える上記(1)から(6)までのいずれかに記載の通信装置。

(8)

前記送受信部から送信された信号を受信した前記他の通信装置から送信されてくる受信確認信号および非受信確認信号のいずれかを検出する確認信号検出部と、

前記確認信号検出部により前記非受信確認信号が検出されたとき、前記非受信確認信号に続く所定数のビットを無視した後に、通信を途中で遮断することを指示するアボート信号を送信するように、前記送受信部に対する指示を行うコンフリクト回避部と

をさらに備える上記(1)から(7)までのいずれかに記載の通信装置。

(9)

前記送受信部は、前記他の通信装置から読み出されるリードデータを受信し、前記リードデータの後に送受信されるプリアンブルの2ビット目に対する駆動を常に行う

上記(1)から(8)までのいずれかに記載の通信装置。

(10)

前記送受信部は、通常の転送レートでデータ通信を行うSDR(Standard Data Rate)モード、および、SDRモードよりも高い転送レートでデータ通信を行うHDR(High Data Rate)モードで、信号の送受信を行うことができる

上記(1)から(9)までのいずれかに記載の通信装置。

(11)

前記送受信部は、1ビットずつ逐次的にシリアルデータを伝送するデータ信号線、および、所定の周波数のシリアルクロックを伝送するクロック信号線の2本の信号線を介して通信を行う

上記(1)から(10)までのいずれかに記載の通信装置。

(12)

前記送受信部、I3C(Improved Inter Integrated Circuit)の規格に準じた通信を行う

上記(1)から(11)までのいずれかに記載の通信装置。

(13)

他の通信装置と信号の送受信を行い、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出し、

10

20

30

40

50

前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行う

ステップを含む通信方法。

(14)

他の通信装置と信号の送受信を行い、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出し、

前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行う

ステップを含む通信処理をコンピュータに実行させるプログラム。

10

(15)

バスにおける制御の主導権を有する第1の通信装置と、

前記第1の通信装置による制御に従って通信を行う第2の通信装置と

を備え、

前記第1の通信装置および前記第2の通信装置それぞれが、

他の通信装置と信号の送受信を行う送受信部と、

前記送受信部が受信したデータに対するパリティチェックを行うことでエラーの発生を検出するエラー検出部と

を有し、

前記エラー検出部は、前記データに含まれている2ビットのパリティのうち、一方を偶数パリティとし、他方を奇数パリティとしてエラー検出を行う

通信システム。

20

【0082】

なお、本実施の形態は、上述した実施の形態に限定されるものではなく、本開示の要旨を逸脱しない範囲において種々の変更が可能である。

【符号の説明】

【0083】

1 1 バスIF, 1 2 マスター, 1 3 スレーブ, 1 4 - 1 データ信号線,

1 4 - 2 クロック信号線, 2 1 送受信部, 2 2 エラー検出部, 2 3 確認信号検出部, 2 4 コンフリクト回避部, 3 1 送受信部, 3 2 エラー検出部,

4 1 パリティエラー検出器, 4 2 入力端子, 4 3 および 4 4 XORゲート, 4

5 1ビット付加部, 4 6 および 4 7 出力端子

30

【図1】

FIG.1

【図2】

FIG.2

High-Keeper (Nobody drives)

Slave doesn't drive

【図3】

FIG.3

【図4】

FIG.4

【図5】

FIG.5

【図6】

FIG.6

【図7】

FIG.7

【図8】

FIG.8

【図9】

FIG. 9

---

フロントページの続き

(72)発明者 横川 峰志

神奈川県厚木市旭町四丁目14番1号 ソニーセミコンダクタソリューションズ株式会社内

(72)発明者 李 惺薰

神奈川県厚木市旭町四丁目14番1号 ソニーセミコンダクタソリューションズ株式会社内

(72)発明者 越坂 直弘

神奈川県厚木市岡田四丁目16番1号 ソニーLSIデザイン株式会社内

審査官 川口 貴裕

(56)参考文献 特開平10-334044(JP,A)

米国特許第05566193(US,A)

米国特許第07865805(US,B1)

特開昭63-131738(JP,A)

特開2005-084791(JP,A)

特開2010-267259(JP,A)

特開2001-067310(JP,A)

国際公開第2015/195329(WO,A2)

米国特許出願公開第2006/0242348(US,A1)

米国特許出願公開第2011/0116331(US,A1)

MIPI Alliance Introduces Sensor Interface Specification for Mobile, Mobile-Influenced and Embedded-Systems Applications MIPI I3C Offers a Substantial Leap in Performance and Power Efficiency Compared to Existing Options[online], MIPI Alliance, 2014年, <https://www.mipi.org/content/mipi-alliance-introduces-sensor-interface-specification-mobile-mobile-influenced-and>

UM10204 I2C-bus specification and user manual Rev.6, NXP Semiconductors N.V., 2014年04月04日, <https://www.nxp.com/docs/en/user-guide/UM10204.pdf>

(58)調査した分野(Int.Cl., DB名)

H04L 1/00

G06F 11/10

G06F 13/36

G06F 13/38