(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

31 July 2008 (31.07.2008)

PCT

(10) International Publication Number

WO 2008/091504 A1

## (51) International Patent Classification:

C23C 16/40 (2006.01) C23C 16/54 (2006.01)

C23C 16/455 (2006.01)

## (21) International Application Number:

PCT/US2008/000466

## (22) International Filing Date: 14 January 2008 (14.01.2008)

## (25) Filing Language: English

## (26) Publication Language: English

(30) Priority Data:

11/627,525 26 January 2007 (26.01.2007) US

## (71) Applicant (for all designated States except US): EASTMAN KODAK COMPANY [US/US]; 343 State Street, Rochester, NY 14650-2201 (US).

## (72) Inventors; and

## (75) Inventors/Applicants (for US only): COWDERY-CORVAN, Peter, Jerome [US/US]; 558 Forest Lawn Road, Webster, NY 14580 (US). LEVY, David, Howard [US/US]; 114 Hampshire Drive, Rochester, NY 14618

(US). NELSON, Shelby, Forrester [US/US]; 8 Old Farm Circle, Pittsford, NY 14534 (US). FREEMAN, Diane, Carol [US/US]; 133 Woodleaf, Pittsford, NY 14534 (US). PAWLIK, Thomas, D. [DE/US]; 2154 Westfall Road, Rochester, NY 14618 (US).

## (74) Common Representative: EASTMAN KODAK COMPANY; 343 State Street, Rochester, NY 14650-2201 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BI, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

## (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH,

[Continued on next page]

## (54) Title: PROCESS FOR ATOMIC LAYER DEPOSITION

**(57) Abstract:** The present invention relates to a process of making a zinc-oxide-based thin film semiconductor, for use in a transistor, comprising thin film deposition onto a substrate comprising providing a plurality of gaseous materials comprising at least first, second, and third gaseous materials, wherein the first gaseous material is a zinc-containing volatile material and the second gaseous material is reactive therewith such that when one of the first or second gaseous materials are on the surface of the substrate the other of the first or second gaseous materials will react to deposit a layer of material on the substrate and wherein the third gaseous material is inert with respect to reacting with the first or second gaseous materials.

GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

- *with international search report*

- *before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments*

## **PROCESS FOR ATOMIC LAYER DEPOSITION**

### **FIELD OF THE INVENTION**

This invention generally relates to the deposition of thin-film materials and, more particularly, to a process for atomic layer deposition onto a substrate using a deposition device. In particular, the present invention relates to a process of making a film of a zinc-oxide-based semiconductor material for thin film transistors, which can be used in electronic devices, particularly in displays, the making of which at low temperature and near atmospheric pressure is advantageous.

### **BACKGROUND OF THE INVENTION**

Thin film transistors (TFTs) are widely used as switching elements in electronics, for example, in active-matrix liquid-crystal displays, smart cards, and a variety of other electronic devices and components thereof. The thin film transistor (TFT) is an example of a field effect transistor (FET). The best-known example of an FET is the MOSFET (Metal-Oxide-Semiconductor-FET), today's conventional switching element for high-speed applications. For applications in which a transistor needs to be applied to a substrate, a thin film transistor is typically used. A critical step in fabricating the thin film transistor involves the deposition of a semiconductor onto the substrate. Presently, most thin film devices are made using vacuum deposited amorphous silicon as the semiconductor.

Amorphous silicon as a semiconductor for use in TFTs still has its drawbacks. The deposition of amorphous silicon, during the manufacture of transistors, requires relatively difficult or complicated processes such as plasma enhanced chemical vapor deposition and high temperatures (typically 360°C) to achieve the electrical characteristics sufficient for display applications. Such high processing temperatures disallow deposition on substrates made of certain plastics that might otherwise be desirable for use in applications such as flexible displays.

There is a growing interest in depositing thin film semiconductors on plastic or flexible substrates, particularly because these supports would be more mechanically robust, lighter weight, and potentially lead to cheaper manufacturing by allowing roll-to-roll processing. A useful example of a flexible substrate is polyethylene terephthalate. Such plastics, however, limit device processing to

below 200°C.

There is also interest in utilizing processes for deposition that do not involve the expense associated with vacuum processing. In typical vacuum processing, a large metal chamber and sophisticated vacuum pumping systems are required in order to provide the necessary environment. These items increase the capital cost of systems and preclude the easy use of continuous web bases systems.

In the past decade, various materials have received attention as a potential alternative to amorphous silicon for use in semiconductor channels of thin film transistors. Semiconductor materials are desirable that are simpler to process, especially those that are capable of being applied to large areas by relatively simple processes. Semiconductor materials that can be deposited at lower temperatures would open up a wider range of substrate materials, including plastics, for flexible electronic devices.

Thus, thin film transistors made of easily deposited semiconductor materials can be viewed as a potential key technology for circuitry in various electronic devices or components such as display backplanes, portable computers, pagers, memory elements in transaction cards, and identification tags, where ease of fabrication, mechanical flexibility, and/or moderate operating temperatures are important considerations.

The discovery of practical inorganic semiconductors as a replacement for current silicon-based technologies has also been the subject of considerable research efforts. For example, metal oxide semiconductors are known that constitute zinc oxide, indium oxide, gallium indium zinc oxide, tin oxide, or cadmium oxide deposited with or without additional doping elements including metals such as aluminum. Such semiconductor materials, which are transparent, can have an additional advantage for certain applications, as discussed below.

A semiconductor material useful in a TFT displays several characteristics. In typical applications of a thin film transistor, the desire is for a switch that can control the flow of current through the device. As such, it is desired that when the switch is turned on a high current can flow through the device. The extent of current flow is related to the semiconductor charge carrier mobility. When the device is turned off, it is desired that the current flow be very small. This is related to the native charge carrier concentration. Furthermore, it is desired that

the device be weakly or not at all influenced by visible light to avoid a light-protection layer. In order for this to be true, the semiconductor band gap should be sufficiently large (> 3 eV) so that exposure to visible light does not cause an inter-band transition. Zinc oxide based materials are capable of delivering these 5 features. Furthermore, in a real high volume web based atmospheric manufacturing scheme, it is highly desirable that the chemistries used in the process be both cheap and of low toxicity, which can be satisfied also by the use of ZnO-based materials and the majority of its precursors.

The semiconductor films made according to the present method exhibit a 10 field effect electron mobility that is greater than  $0.01 \text{ cm}^2/\text{Vs}$ , preferably at least  $0.1 \text{ cm}^2/\text{Vs}$ , more preferably greater than  $1.0 \text{ cm}^2/\text{Vs}$ . In addition, n-channel semiconductor films made according to the present invention are capable of providing on/off ratios of at least  $10^4$ , advantageously at least  $10^6$ . The on/off ratio is measured by the ratio of the on current, defined as the drain current at a 15 gate voltage of 10 V in excess of the threshold voltage, to the off current, defined as the drain current at a gate voltage for which the transistor is in an off state.

High on/off ratios result when the device in its off state has very low current flow, often referred to as current leakage. There are many applications in which low leakage is essential. In display applications, low leakage is required 20 for the pixel select transistor. This select transistor is a switch that allows a charge to enter in and be stored in the pixel. In a perfect transistor without leakage, once the charge is stored in the pixel the transistor is switched to its off state and this charge cannot diminish by leakage through the select transistor. Too high of an off current in a transistor will cause a decay in stored charge in the pixel which 25 results in poor display performance.

Another transistor characteristic that is relevant for useful operation is the steepness of the transistor turn on, represented by the subthreshold slope. As the gate voltage of a transistor is varied, the transistor will start in an off state, characterized by low current flow, and transition to an on state, characterized by 30 high current flow. When the gate voltage reaches a point at which the transistor begins to turn on, there is a substantial increase in drain current with increasing gate voltage. This increase, called the subthreshold slope, is measured in volts of gate voltage per decade of drain current. This expression therefore represents the number of volts of gate voltage required to produce a 10 fold increase in drain

current. Lower values of the subthreshold slope indicate faster device turn on and are desirable.

Various processes for making zinc oxide films have been disclosed, both high temperature and low temperature processes, including radio frequency 5 magnetron sputtering or modified reactive planar magnetron sputtering.

Ohya et al (Japanese Journal of Applied Physics, Part 1, January 2001, vol. 40, no.1, pages 297-8) disclose a thin film transistor of ZnO fabricated by chemical solution deposition.

Transparent conducting oxides are reviewed in the August 2000 issue of 10 the Materials Research Bulletin, Volume 25 (8) 2000, devoted to materials and properties of transparent conducting oxide compounds.

One low temperature process for deposition of such oxide semiconductors are disclosed in US 2004/0127038 A1 to Garcia et al. This patent discloses a 15 semiconductor deposition process that uses magnetron sputtering of a metal oxide (ZnO, In<sub>2</sub>O<sub>3</sub>, SnO<sub>2</sub>, CdO) or metal (Zn, In, Sn, Cd) target in an atmosphere with a controlled partial pressure of oxygen in an inert gas. This is a low temperature process that is compatible with temperature sensitive substrates and components, for example, drive circuits for displays on flexible, polymer substrates. The field 20 effect transistors of Garcia et al. are based on a nominally undoped metal oxide semiconductor that should be deposited using physical vapor deposition or chemical vapor deposition, preferably rf (radio frequency) magnetron sputtering.

Japanese Kokai JP2004349583 A1 discloses a method of producing a thin 25 film transistor in which a dispersion of zinc-oxide nanoparticles is ink-jetted to form the semiconducting channel. No actual examples, however, are described relating to the preparation of the dispersion.

US 2004/0127038 discloses a method to produce high quality zinc-oxide thin film transistors using sputtering as a vacuum deposition method.

Steven K. Volkman et al., in "A novel transparent air-stable printable n-type semiconductor technology using ZnO nanoparticles," 2004 IEEE 30 International Electron Device meeting Technical Digest, pp. 769, 2004, disclose a method for producing thin film transistors using organically stabilized zinc-oxide nanoparticles. The disclosed process involves an exposure to a temperature of 400°C.

Although successful zinc oxide based devices have been made with sputtering techniques, it is clear that very precise control over the reactive gas composition (such as oxygen content) is required to produce good quality devices. Chemical vapor deposition (CVD) techniques, in which two reactive gasses are 5 mixed to form the desired film material, can be useful routes to achieving high quality film growth. Atomic layer deposition ("ALD") is yet an alternative film deposition technology that can provide improved thickness resolution and conformal capabilities, compared to its CVD predecessor. The ALD process segments the conventional thin-film deposition process of conventional CVD into 10 single atomic-layer deposition steps.

ALD can be used as a fabrication step for forming a number of types of thin-film electronic devices, including semiconductor devices and supporting electronic components such as resistors and capacitors, insulators, bus lines and other conductive structures. ALD is particularly suited for forming thin layers of 15 metal oxides in the components of electronic devices. General classes of functional materials that can be deposited with ALD include conductors, dielectrics or insulators, and semiconductors.

Examples of useful semiconducting materials are compound semiconductors such as gallium arsenide, gallium nitride, cadmium sulfide, zinc 20 oxide, and zinc sulfide.

A number of device structures can be made with the functional layers described above. A capacitor results from placing a dielectric between two conductors. A diode results from placing two semiconductors of complementary carrier type between two conducting electrodes. There may also be disposed 25 between the semiconductors of complementary carrier type a semiconductor region that is intrinsic, indicating that that region has low numbers of free charge carriers. A diode may also be constructed by placing a single semiconductor between two conductors, where one of the conductor/semiconductors interfaces produces a Schottky barrier that impedes current flow strongly in one direction. A 30 transistor results from placing upon a conductor (the gate) an insulating layer followed by a semiconducting layer. If two or more additional conductor electrodes (source and drain) are placed spaced apart in contact with the top semiconductor layer, a transistor can be formed. Any of the above devices can be created in various configurations as long as the critical interfaces are created.

Advantageously, ALD steps are self-terminating and can deposit precisely one atomic layer when conducted up to or beyond self-termination exposure times. An atomic layer typically ranges from 0.1 to 0.5 molecular monolayers, with typical dimensions on the order of no more than a few Angstroms. In ALD, 5 deposition of an atomic layer is the outcome of a chemical reaction between a reactive molecular precursor and the substrate. In each separate ALD reaction-deposition step, the net reaction deposits the desired atomic layer and substantially eliminates "extra" atoms originally included in the molecular precursor. In its most pure form, ALD involves the adsorption and reaction of each of the 10 precursors in the complete absence of the other precursor or precursors of the reaction. In practice in any process it is difficult to avoid some direct reaction of the different precursors leading to a small amount of chemical vapor deposition reaction. The goal of any process claiming to perform ALD is to obtain device performance and attributes commensurate with an ALD process while recognizing 15 that a small amount of CVD reaction can be tolerated.

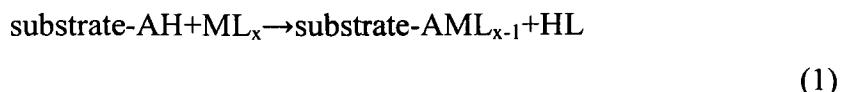

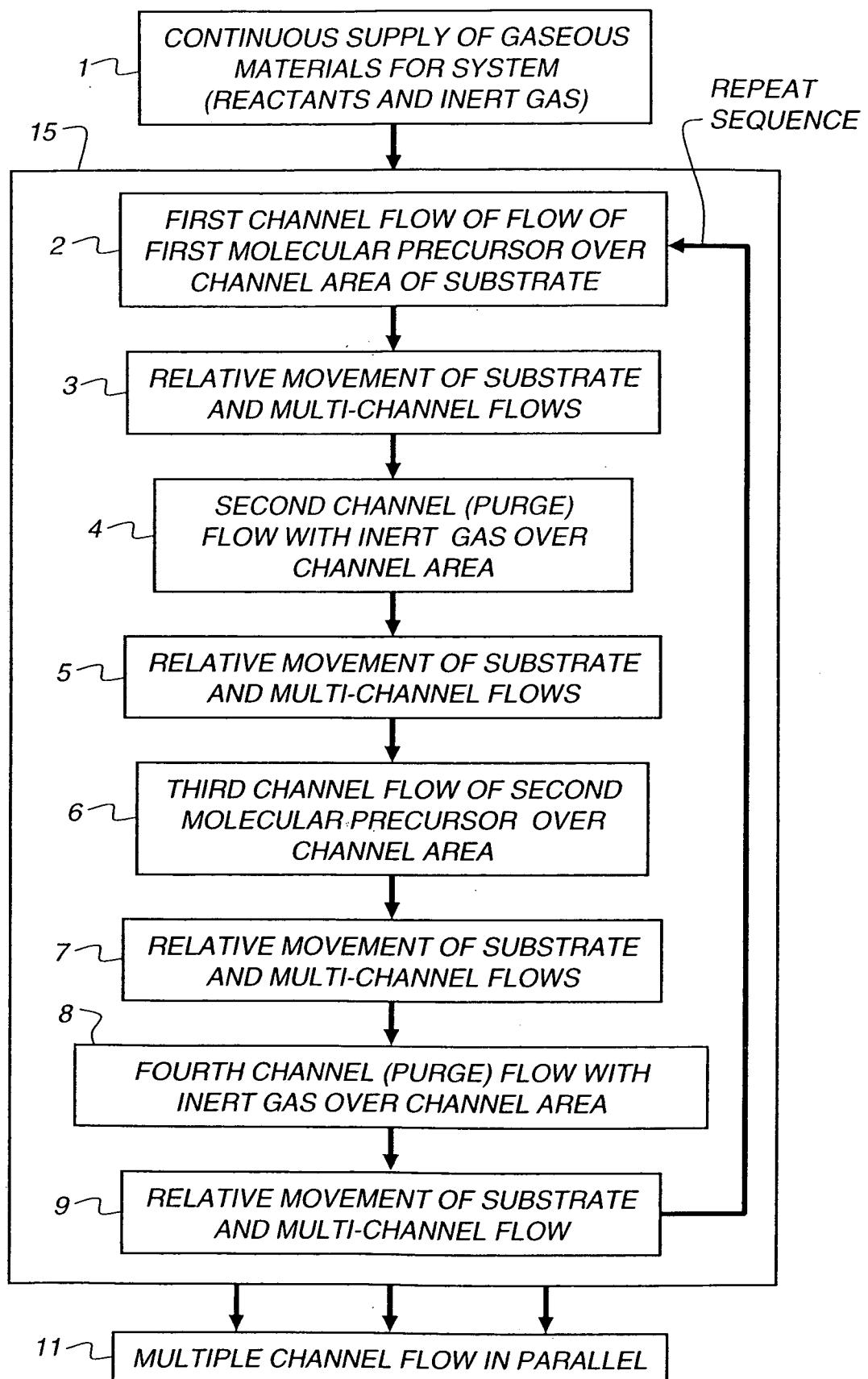

In ALD applications, typically two molecular precursors are introduced into the ALD reactor in separate stages. For example, a metal precursor molecule,  $ML_x$ , comprises a metal element, M that is bonded to an atomic or molecular ligand, L. For example, M could be, but would not be restricted to, Al, 20 W, Ta, Si, Zn, etc. The metal precursor reacts with the substrate, when the substrate surface is prepared to react directly with the molecular precursor. For example, the substrate surface typically is prepared to include hydrogen-containing ligands, AH or the like, that are reactive with the metal precursor. Sulfur (S), oxygen (O), and Nitrogen (N) are some typical A species. The gaseous 25 precursor molecule effectively reacts with all of the ligands on the substrate surface, resulting in deposition of a single atomic layer of the metal:

30 where HL is a reaction by-product. During the reaction, the initial surface ligands, AH, are consumed, and the surface becomes covered with  $AML_{x-1}$  ligands, which cannot further react with metal precursor  $ML_x$ . Therefore, the reaction self-terminates when all of the initial AH ligands on the surface are replaced with  $AML_{x-1}$  species. The reaction stage is typically followed by an inert-gas purge

stage that eliminates the excess metal precursor and the HL by-product species from the chamber prior to the separate introduction of the other precursor.

A second molecular precursor then is used to restore the surface reactivity of the substrate towards the metal precursor. This is done, for example, by

5 removing the L ligands and re-depositing AH ligands. In this case, the second precursor typically comprises the desired (usually nonmetallic) element A (i.e., O, N, S), and hydrogen (i.e., H<sub>2</sub>O, NH<sub>3</sub>, H<sub>2</sub>S). The next reaction is as follows:

10 This converts the surface back to its AH-covered state. (Here, for the sake of simplicity, the chemical reactions are not balanced.) The desired additional element, A, is incorporated into the film and the undesired ligands, L, are

eliminated as volatile by-products. Once again, the reaction consumes the reactive sites (this time, the L terminated sites) and self-terminates when the

15 reactive sites on the substrate are entirely depleted. The second molecular precursor then is removed from the deposition chamber by flowing inert purge-gas in a second purge stage.

In summary, then, an ALD process requires alternating in sequence the flux of chemicals to the substrate. The representative ALD process, as discussed 20 above, is a cycle having four different operational stages:

1. ML<sub>x</sub> reaction;

2. ML<sub>x</sub> purge;

3. AH<sub>y</sub> reaction; and

4. AH<sub>y</sub> purge, and then back to stage 1.

25 This repeated sequence of alternating surface reactions and precursor-removal that restores the substrate surface to its initial reactive state, with intervening purge operations, is a typical ALD deposition cycle. A key feature of ALD operation is the restoration of the substrate to its initial surface chemistry condition. Using this repeated set of steps, a film can be layered onto the substrate in equal metered layers that are all identical in chemical kinetics, deposition per cycle, composition, and thickness.

Self-saturating surface reactions make ALD insensitive to transport non-uniformities, which might otherwise impair surface uniformity, due either to

engineering tolerances and the limitations of the flow process or related to surface topography (that is, deposition into three dimensional, high aspect ratio structures). As a general rule, a non-uniform flux of chemicals in a reactive process generally results in different completion times at different areas.

5 However, with ALD, each of the reactions is allowed to complete on the entire substrate surface. Thus, differences in completion kinetics impose no penalty on uniformity. This is because the areas that are first to complete the reaction self-terminate the reaction; other areas are able to continue until the full treated surface undergoes the intended reaction.

10 Typically, an ALD process deposits 0.1 - 0.2 nm of a film in a single ALD cycle (with numbered steps 1 through 4 as listed earlier). A useful and economically feasible cycle time should be achieved in order to provide a uniform film thickness in a range of from 3 nm to 300 nm for many or most semiconductor applications, and even thicker films for other applications. Industry throughput 15 standards dictate that substrates be processed in 2 minutes to 3 minutes, which means that ALD cycle times should be in a range from 0.6 seconds to 6 seconds.

An ALD process should be able to execute this sequencing efficiently and reliably for many cycles in order to allow cost-effective coating of many substrates. In an effort to minimize the time that an ALD reaction needs to reach 20 self-termination, at any given reaction temperature, one approach has been to maximize the flux of chemicals flowing into the ALD reactor, using a so-called “pulsing” process. In the pulsed ALD process, a substrate sits in a chamber and is exposed to the above sequence of gases by allowing a first gas to enter the chamber, followed by a pumping cycle to remove that gas, followed by the 25 introduction of a second gas to the chamber, followed by a pumping cycle to remove the second gas. This sequence can be repeated at any frequency and variations in gas type and/or concentration. The net effect is that the entire chamber experiences a variation in gas composition with time, and thus this type of ALD can be referred to as time dependent ALD. The vast majority of existing 30 ALD processes are time dependent ALD.

In order to maximize the flux of chemicals into the ALD reactor, it is advantageous to introduce the molecular precursors into the ALD reactor with minimum dilution of inert gas and at high pressures. However, these measures work against the need to achieve short cycle times and the rapid removal of these

molecular precursors from the ALD reactor. Rapid removal in turn dictates that gas residence time in the ALD reactor be minimized.

Existing ALD approaches have been compromised with the trade-off between the need to shorten reaction times and improve chemical utilization 5 efficiency, and on the other hand, the need to minimize purge-gas residence and chemical removal times. One approach to overcome the inherent limitations of time depended ALD systems is to provide each reactant gas continuously and to move the substrate through each gas in succession. In these systems a relatively constant gas composition exists, but is located to specific areas or spaces of the 10 processing system. Therefore, these systems will be referred to as spatially dependent ALD systems.

For example, U.S. Patent No. 6,821,563 entitled “GAS DISTRIBUTION SYSTEM FOR CYCLICAL LAYER DEPOSITION” to Yudovsky describes 15 spatially dependent ALD processing system, under vacuum, having separate gas ports for precursor and purge gases, alternating with vacuum pump ports between each gas port. Each gas port directs its stream of gas vertically downward toward a substrate. The separate gas flows are separated by walls or partitions, with vacuum pumps for evacuating gas on both sides of each gas stream. A lower portion of each partition extends close to the substrate, for example, 0.5 mm or 20 greater from the substrate surface. In this manner, the lower portions of the partitions are separated from the substrate surface by a distance sufficient to allow the gas streams to flow around the lower portions toward the vacuum ports after the gas streams react with the substrate surface

A rotary turntable or other transport device is provided for holding one or 25 more substrate wafers. With this arrangement, the substrate is shuttled beneath the different gas streams, effecting ALD deposition thereby. In one embodiment, the substrate is moved in a linear path through a chamber, in which the substrate is passed back and forth a number of times.

Another approach using continuous gas flow spatially dependent ALD is 30 shown in U.S. Patent No. 4,413,022 entitled “METHOD FOR PERFORMING GROWTH OF COMPOUND THIN FILMS” to Suntola et al. A gas flow array is provided with alternating source gas openings, carrier gas openings, and vacuum exhaust openings. Reciprocating motion of the substrate over the array effects ALD deposition, again, without the need for pulsed operation. In the embodiment

of Figures 13 and 14, in particular, sequential interactions between a substrate surface and reactive vapors are made by a reciprocating motion of the substrate over a fixed array of source openings. Diffusion barriers are formed by a carrier gas opening between exhaust openings. Suntola et al. state that operation with 5 such an embodiment is possible even at atmospheric pressure, although little or no details of the process, or examples, are provided.

While processes such as those described in the '563 Yudovsky and '022 Suntola et al. disclosures may avoid some of the difficulties inherent to pulsed gas approaches, these processes have other drawbacks. For example, it would be very 10 difficult to maintain a uniform vacuum at different points in an array and to maintain synchronous gas flow and vacuum at complementary pressures, thus compromising the uniformity of gas flux that is provided to the substrate surface. Neither the gas flow delivery unit of the '563 Yudovsky disclosure nor the gas flow array of the '022 Suntola et al. disclosure can be used in closer proximity to 15 the substrate than 0.5 mm.

U.S. Patent Pub. No. 2005/0084610 to Selitser discloses an atmospheric pressure atomic layer chemical vapor deposition process. Selitser et al. state that extraordinary increases in reaction rates are obtained by changing the operating pressure to atmospheric pressure, which will involve orders of magnitude increase 20 in the concentration of reactants, with consequent enhancement of surface reactant rates. The embodiments of Selitser et al. involve separate chambers for each stage of the process, although Figure 10 shows an embodiment in which chamber walls are removed. A series of separated injectors are spaced around a rotating circular substrate holder track. Each injector incorporates independently operated 25 reactant, purging, and exhaust gas manifolds and controls and acts as one complete mono-layer deposition and reactant purge cycle for each substrate as it passes there under in the process. Little or no specific details of the gas injectors or manifolds are described by Selitser et al., although they state that spacing of the injectors is selected so that cross-contamination from adjacent injectors is 30 prevented by purging gas flows and exhaust manifolds incorporate in each injector.

A spatially dependent ALD process can be accomplished with other apparatus or systems described in more detail in commonly assigned US Application Serial Number 11/392,007, filed March 29, 2006 by Levy et al. and

entitled, "PROCESS FOR ATOMIC LAYER DEPOSITION;" US Application Serial Number 11/392,006, filed March 29, 2006 by Levy et al. and entitled "APPARATUS FOR ATOMIC LAYER DEPOSITION;" US Application Serial Number 11/620,744, filed January 08, 2007 by Levy and entitled "DEPOSITION SYSTEM AND METHOD USING A DELIVERY HEAD SEPARATED FROM A SUBSTRATE BY GAS PRESSURE;" and US Application Serial Number 11/620,740, filed January 08, 2007 by Nelson et al. and entitled "DELIVERY DEVICE COMPRISING GAS DIFFUSER FOR THIN FILM DEPOSITION." These systems attempt to overcome one of the difficult aspects of a spatial ALD system, which is undesired intermixing of the continuously flowing mutually reactive gases. In particular, USSN 11/392,007 employs a novel transverse flow pattern to prevent intermixing, while US Serial No. 11/620,744 and US Serial No. 11/620,740 employ a coating head partially levitated by the pressure of the reactive gases of the process to accomplish improved gas separation.

Despite the usefulness and ease of use of these spatially dependent ALD systems, they continue to be less capable than time dependent ALD systems in terms of separation of the mutually reactive gases. Thus, to render them industrially useful, chemistries should be considered that are more robust to unavoidable problems associated with gas intermixing.

A common approach to chemically modify the nature of a semiconductor is to include in the matrix of the semiconductor other atoms or molecules which vary the electrical properties of the semiconductor. These additional atoms typically operate by accepting or donating mobile charge to the system. In the case of a semiconductor like zinc oxide, acceptor dopants can be used to trap electrons, thus driving the semiconductor to have increased hole concentration and toward a p-type semiconductor. Alternatively, donor dopants can be used to release electrons, thus driving the semiconductor to have an increased electron concentration and toward a n-type semiconductor

A number of atoms exist that can be used as acceptor dopants in zinc oxide, among which are nitrogen, copper, phosphorus, and arsenic. In the existing prior art, the use of acceptor dopants in zinc oxide has been done with an attempt to produce p-type zinc oxide layers. Suitable p-type materials will in fact be driven to a sufficient hole concentration so as to render the materials somewhat conductive due to hole charge carrier movement.

For example, Sugihara et al. , US 2006/0244107 A1, disclose a method to prepare acceptor-doped ZnO-based layers . In their method, the films are prepared by using pulsed laser deposition, with a substrate temperature of 300°C and using nitric oxide as the N-dopant. Interestingly, the films require an adjacent 5 barrier layer to be effective.

C.Lee et al. (J.Vac. Sci. Technol. A 24(4) 2006) discusses N-doped ZnO-based semiconductor films grown by an ALD type process using ammonia gas to produce nitrogen doping. These films require annealing at 1000°C to convert them to p-type ZnO. They use a time dependent ALD process. The acceptor 10 doping is used to produce p-type materials.

Thus, there remains still a need to provide a spatially dependent ALD system to make a zinc-oxide based semiconductor film .

### **SUMMARY OF THE INVENTION**

The present invention relates to A process of making an n-type zinc-oxide-based thin film semiconductor, for use in a transistor by depositing a thin film 15 material on a substrate, comprising simultaneously directing a series of gas flows along elongated substantially parallel channels, and wherein the series of gas flows comprises, in order, at least a first reactive gaseous material, an inert purge gas, and a second reactive gaseous material, optionally repeated a plurality of 20 times, wherein the first reactive gaseous material is capable of reacting with a substrate surface treated with the second reactive gaseous material to form the zinc-oxide-based thin film semiconductor, wherein the first reactive gaseous material is a volatile organo-zinc precursor compound comprising both zinc and organic groups, a volatile acceptor dopant precursor is introduced into the first 25 reactive gaseous material, the second reactive gaseous material, in inert purge gas, or an additional gas flow of a supplemental gaseous material, and wherein the process is carried out substantially at or above atmospheric pressure and the temperature of the substrate during deposition is under 250°C. Accordingly, the acceptor dopant precursor reacts and is incorporated as an acceptor dopant in the 30 zinc-oxide-based thin film semiconductor film..

During the process, the substrate or deposition device for the gaseous materials, or both, is capable of providing relative movement between the output face of the deposition device and the substrate while maintaining close proximity.

In a preferred embodiment, the process can be operated with continuous movement of a substrate being subjected to thin film deposition, wherein the process is capable of conveying the support on or as a web past the deposition device, preferably in an unsealed environment to ambient at substantially atmospheric pressure.

5 In the material produced by a spatial ALD process, defects in the materials lead to two deleterious effects. First of all, such materials tend to have too high a concentration of native charge carrier, leading to high off currents. Secondly, such materials contain defect sites that can cause bulk charging effects, leading to 10 poor subthreshold slope. The present invention provides doping methods that permit zinc-oxide-based semiconductor material produced in a spatially dependent ALD system to not only effectively work in practice, but to perform well.

15 It is an advantage of the present invention that it provides an advantageous process for atomic layer deposition of a zinc-oxide-based n-type semiconductor onto a substrate, well suited to a number of different types of substrates and deposition environments.

20 It is yet a further advantage of the present invention that it is adaptable for deposition on a web or other moving substrate, including deposition onto a large area substrate.

It is a further advantage of the present invention that it allows operation, in preferred embodiments, under atmospheric pressure conditions.

25 It is still a further advantage of the present invention that it can be employed in low temperature processes at atmospheric pressures, which process may be practice in an unsealed environment, open to ambient atmosphere.

The invention is also directed to a transistor comprising a zinc-oxide-based semiconductor, preferably on a flexible substrate, made by the present process.

30 Semiconductor films made by the present method are capable of exhibiting, in the film form, excellent field-effect electron mobilities of greater than  $0.1 \text{ cm}^2/\text{Vs}$  and on-off ratios of greater than  $10^4$ , in which performance properties are sufficient for use in a variety of relevant technologies, including active matrix display backplanes.

A TFT structure includes, in addition to the zinc-oxide-based semiconductor, conducting electrodes, commonly referred to as a source and a drain, for injecting a current into the zinc-oxide-based semiconductor. The n-

channel semiconductor films made by the present invention can be used in thin film transistors each comprising spaced apart first and second contact means connected to an n-channel semiconductor film. A third contact means can be spaced from said semiconductor film by an insulator, and adapted for controlling, 5 by means of a voltage applied to the third contact means, a current between the first and second contact means through said film. The first, second, and third contact means can correspond to a drain, source, and gate electrode in a field effect transistor.

10 The objects, features, and advantages of the present invention will become apparent to those skilled in the art upon a reading of the following detailed description when taken in conjunction with the drawings wherein there is shown and described an illustrative embodiment of the invention.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

15 While the specification concludes with claims particularly pointing out and distinctly claiming the subject matter of the present invention, it is believed that the invention will be better understood from the following description when taken in conjunction with the accompanying drawings, wherein:

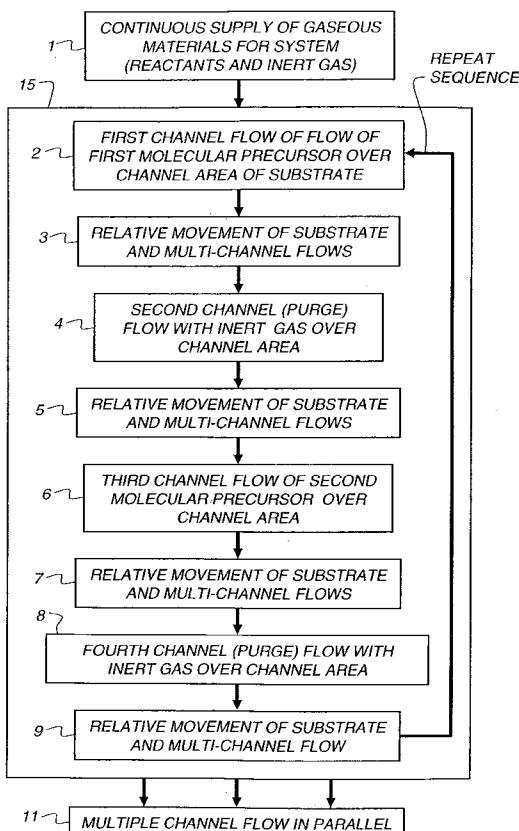

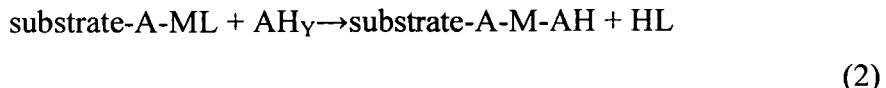

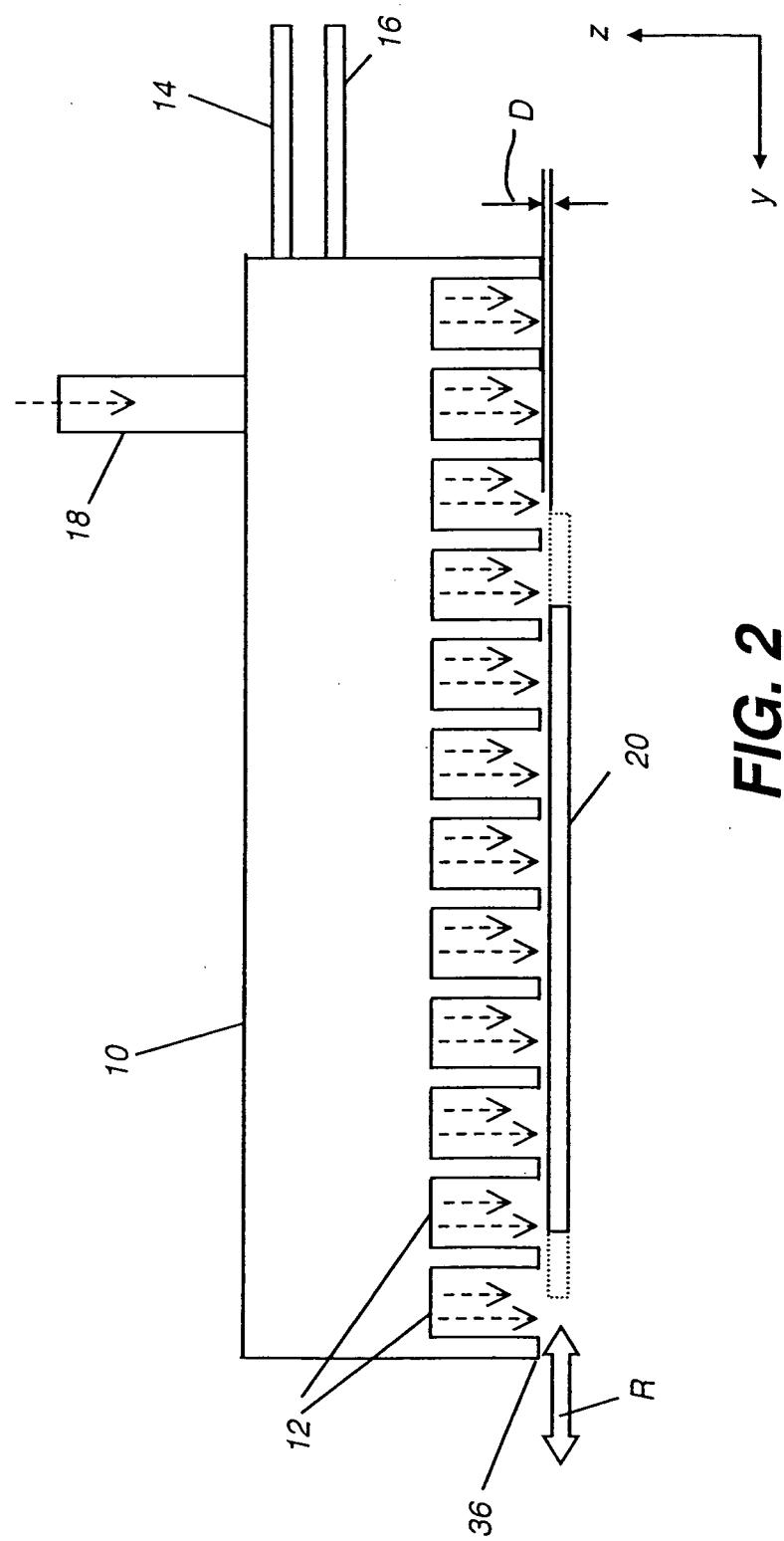

20 Figure 1 is a flow chart describing the steps of the present process; Figure 2 is a cross-sectional side view of one embodiment of a deposition device for atomic layer deposition that can be used in the present process;

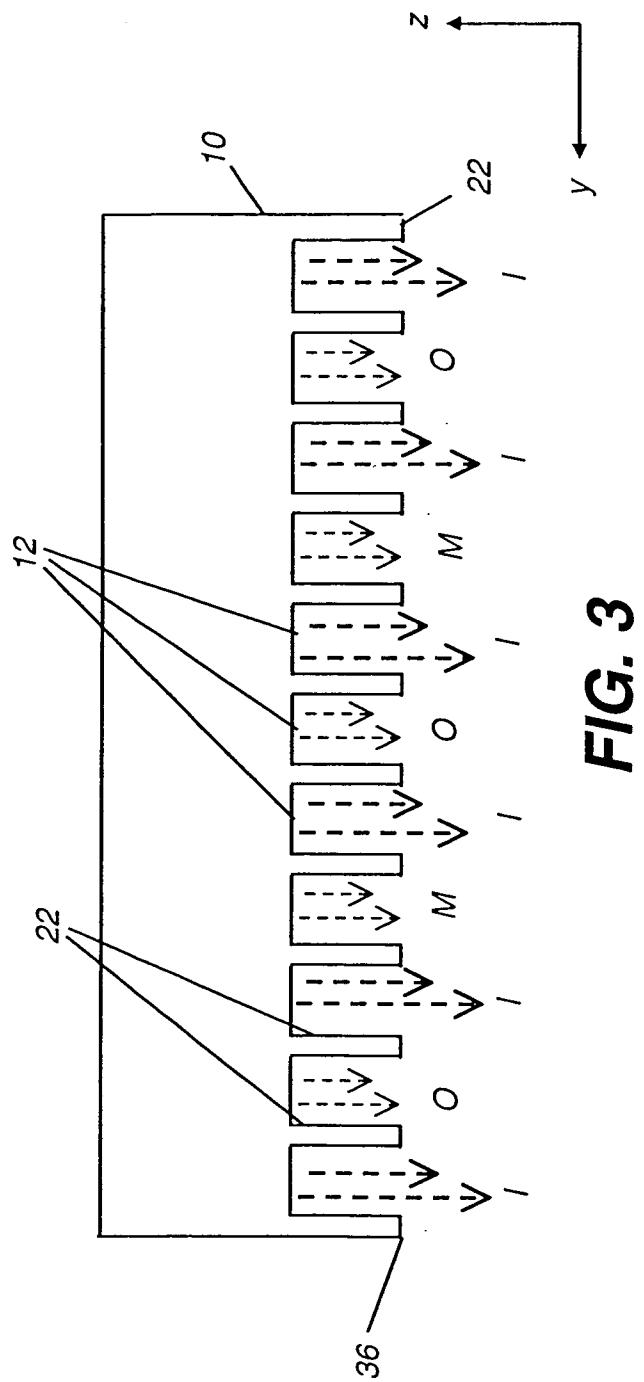

25 Figure 3 is a cross-sectional side view of an embodiment, for one exemplary system of gaseous materials, of the distribution of gaseous materials to a substrate that is subject to thin film deposition;

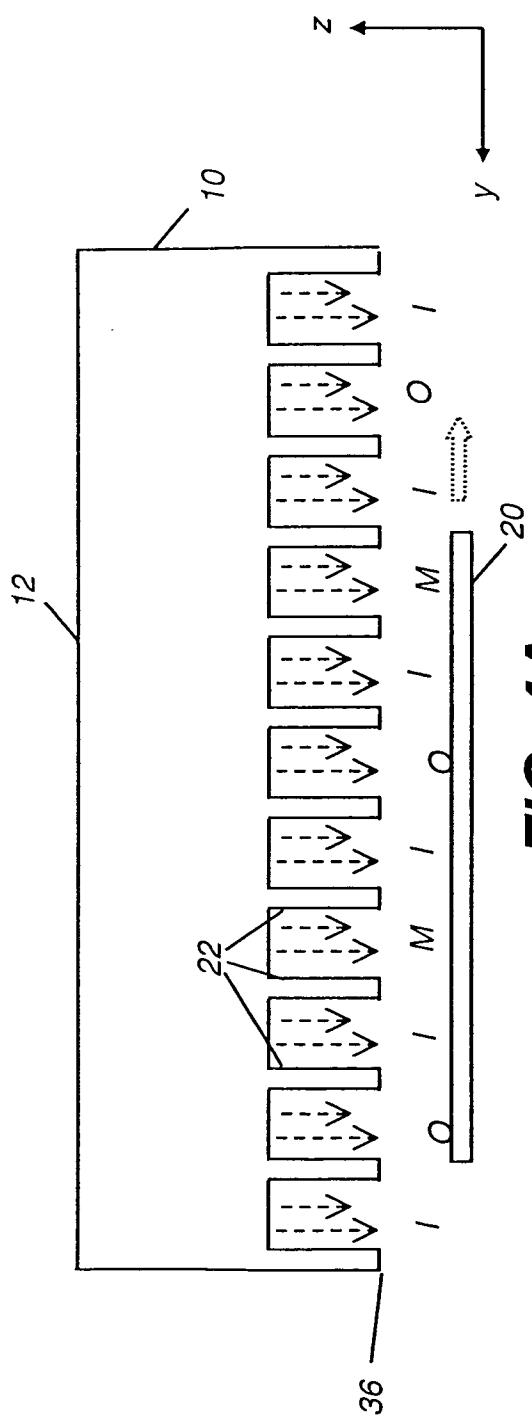

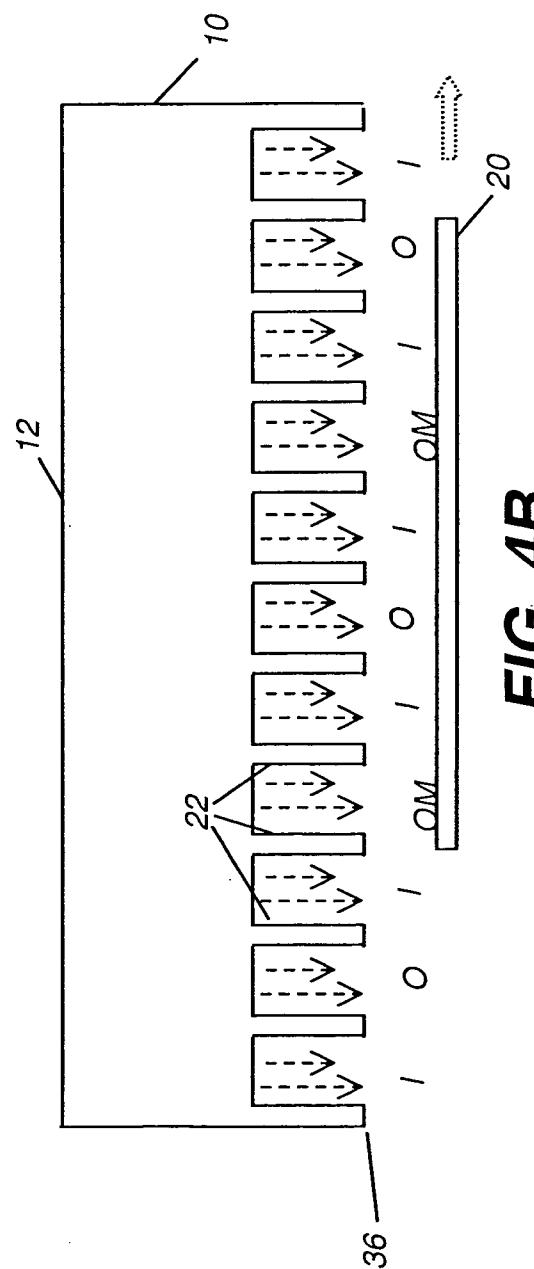

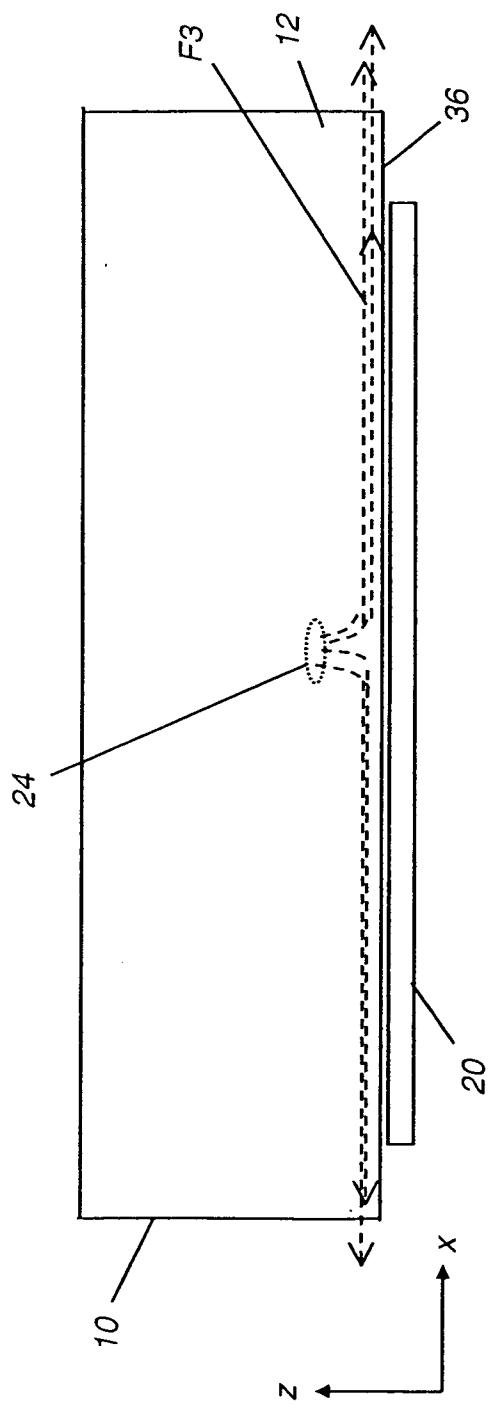

30 Figures 4A and 4B are cross-sectional side views of one embodiment of the distribution of a system of gaseous materials, schematically showing the accompanying deposition operation;

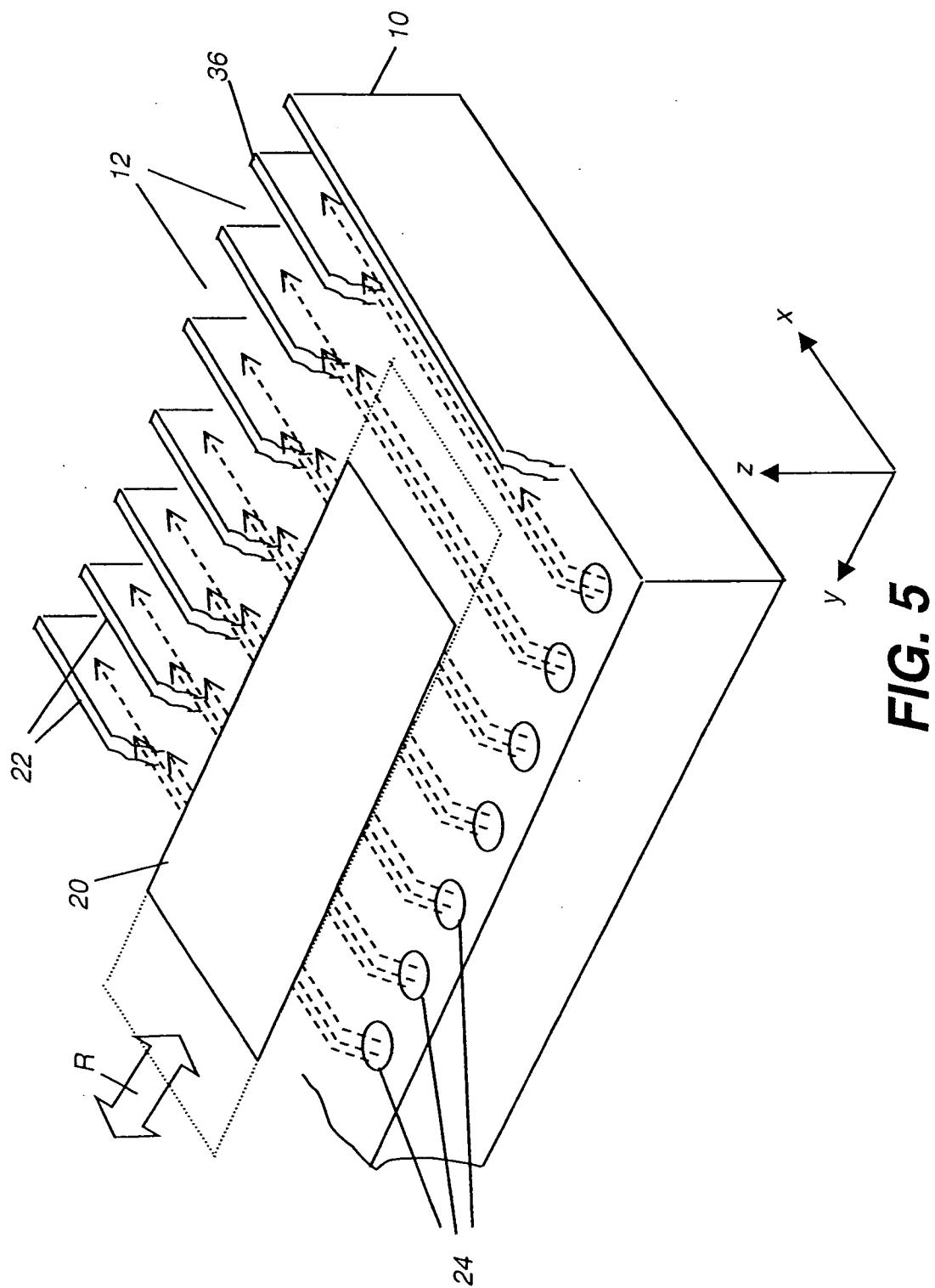

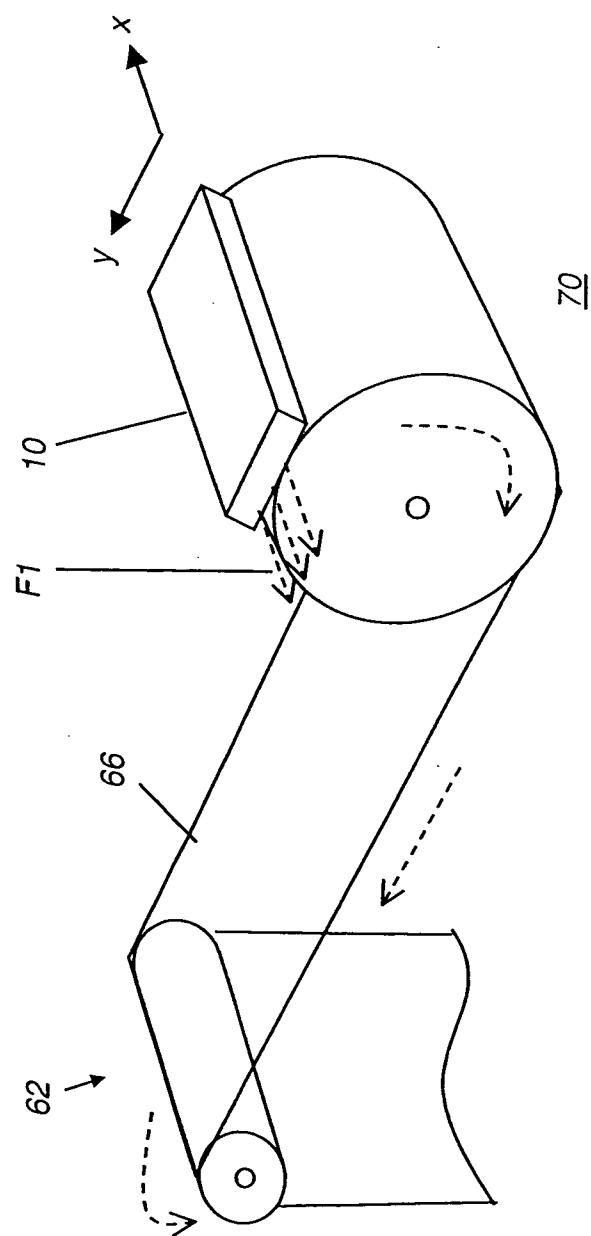

Figure 5 is a perspective view, from the output face side, of a portion of one embodiment of a deposition device, showing the orientation of output channels relative to the substrate and reciprocating motion, that can be used for 30 deposition on the substrate;

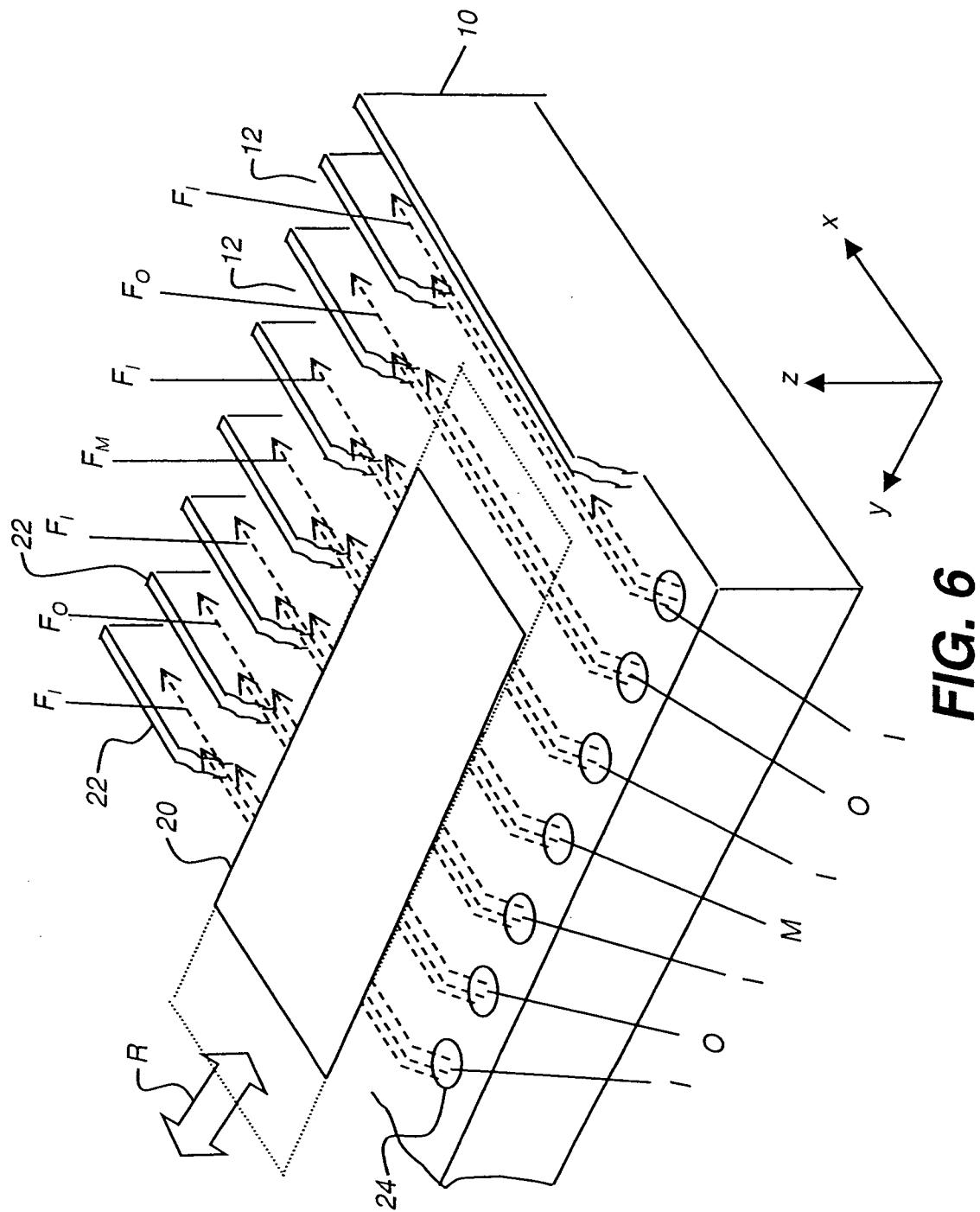

Figure 6 is a perspective view as in Figure 5, showing one exemplary arrangement of gas flow in the deposition device;

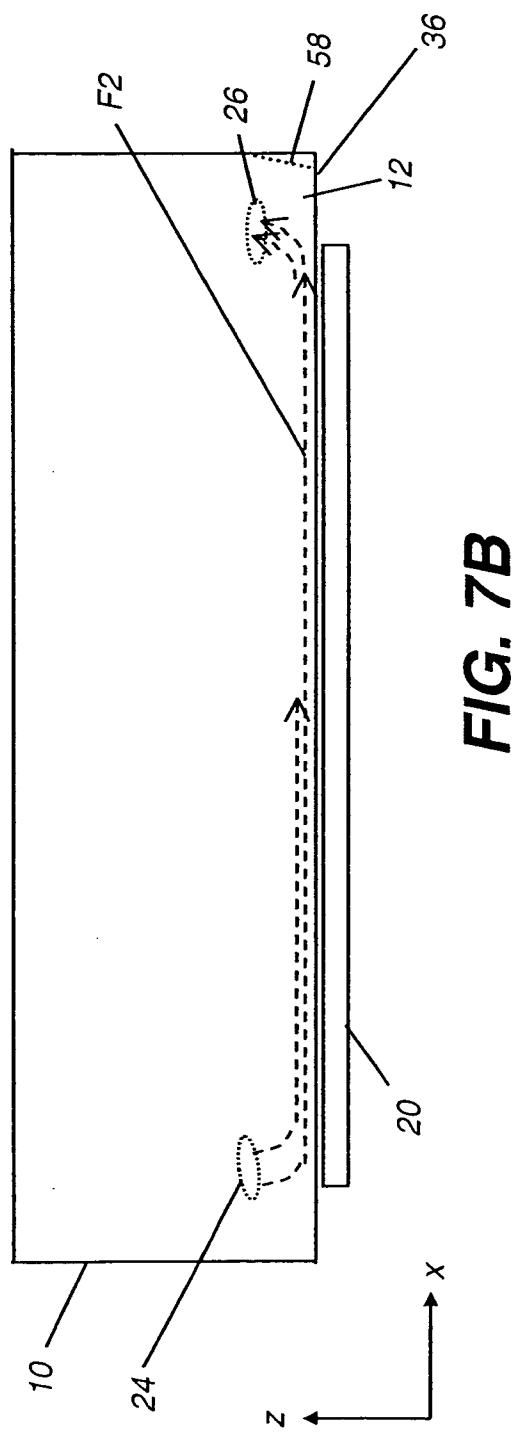

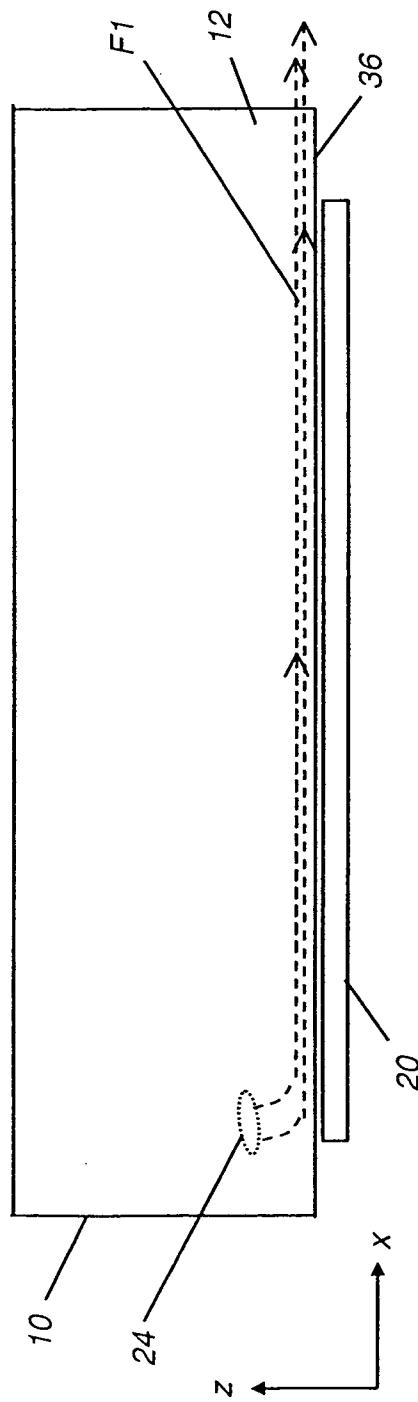

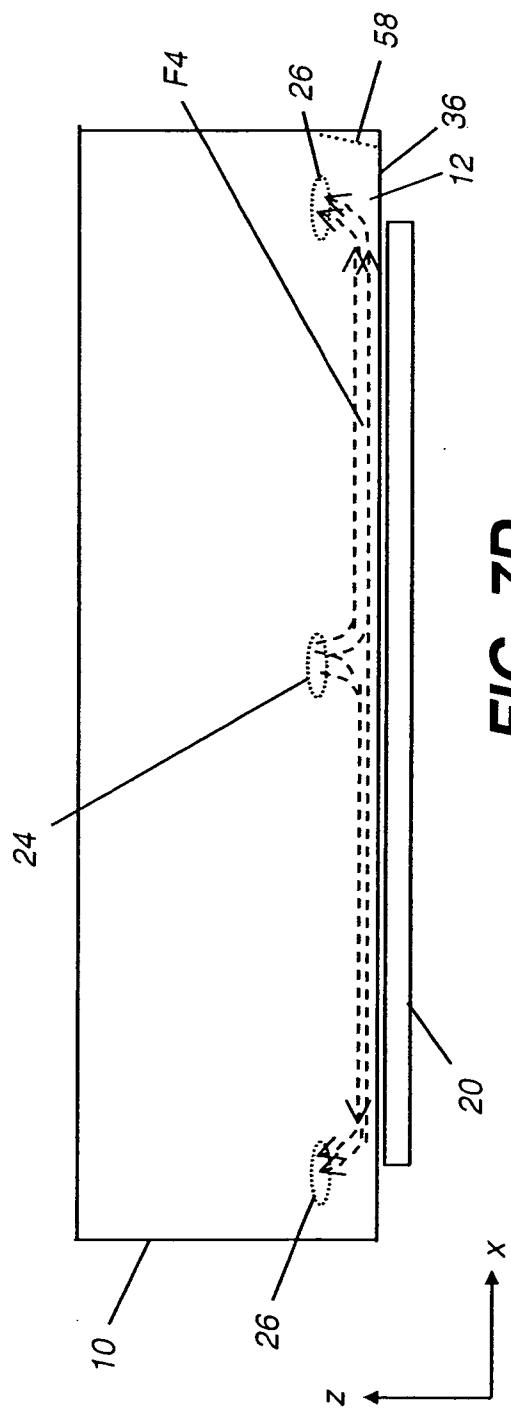

Figures 7A, 7B, 7C, and 7D are cross-sectional views taken orthogonally to the cross sectional views of previous Figures 2-4B, showing gas flow directions for output channels in various embodiments;

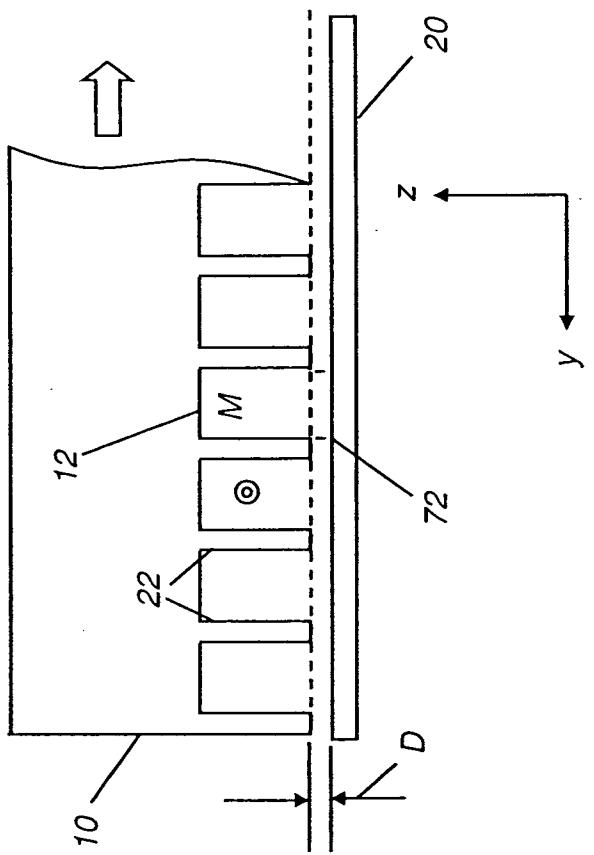

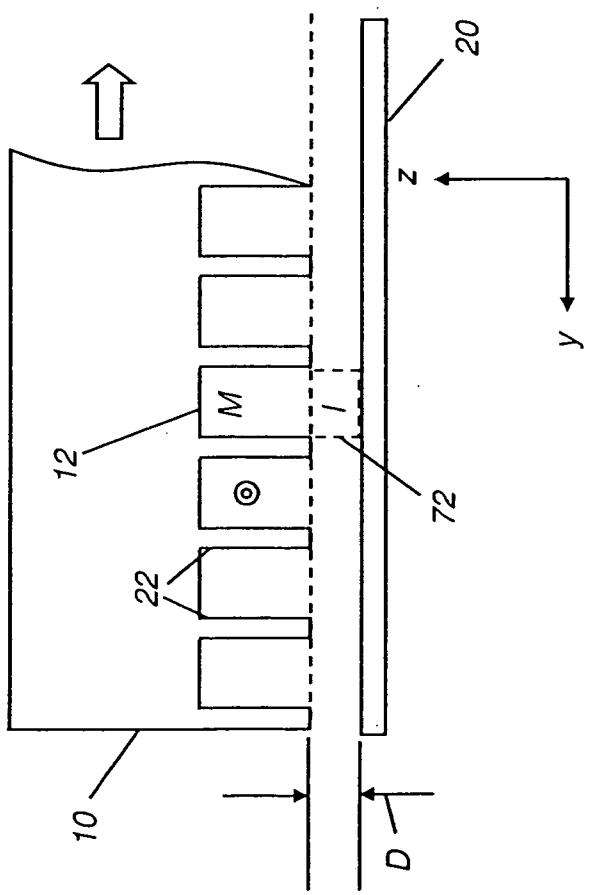

Figures 8A and 8B are cross-section views showing the impact of reduced 5 distance from the output face, of a deposition device for providing gaseous materials, to the substrate surface;

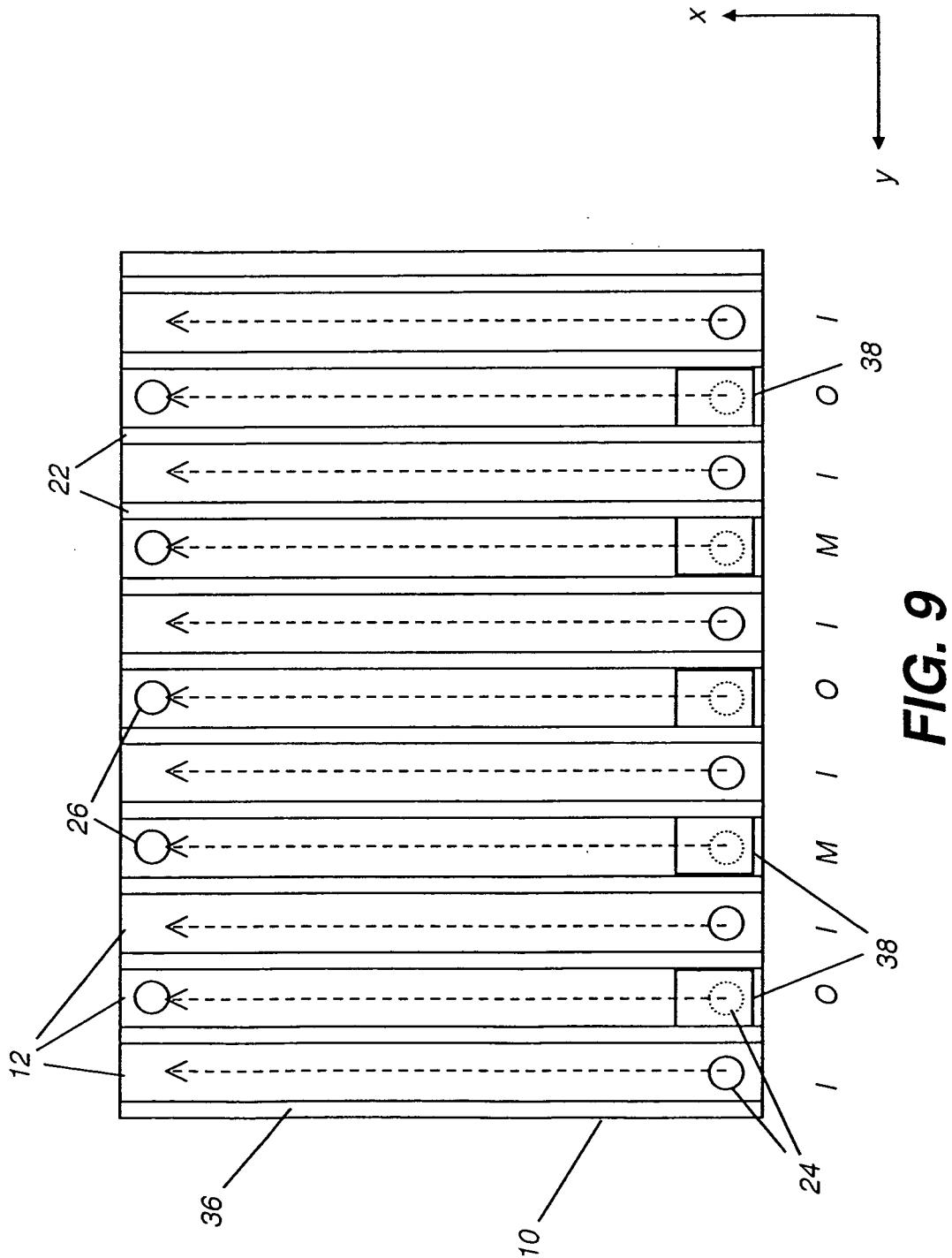

Figure 9 is a plan view of the output face of a deposition device such as shown in Figure 3 that can be used in the present process, showing movement of gaseous materials through an arrangement of output channels according to one 10 embodiment of the invention;

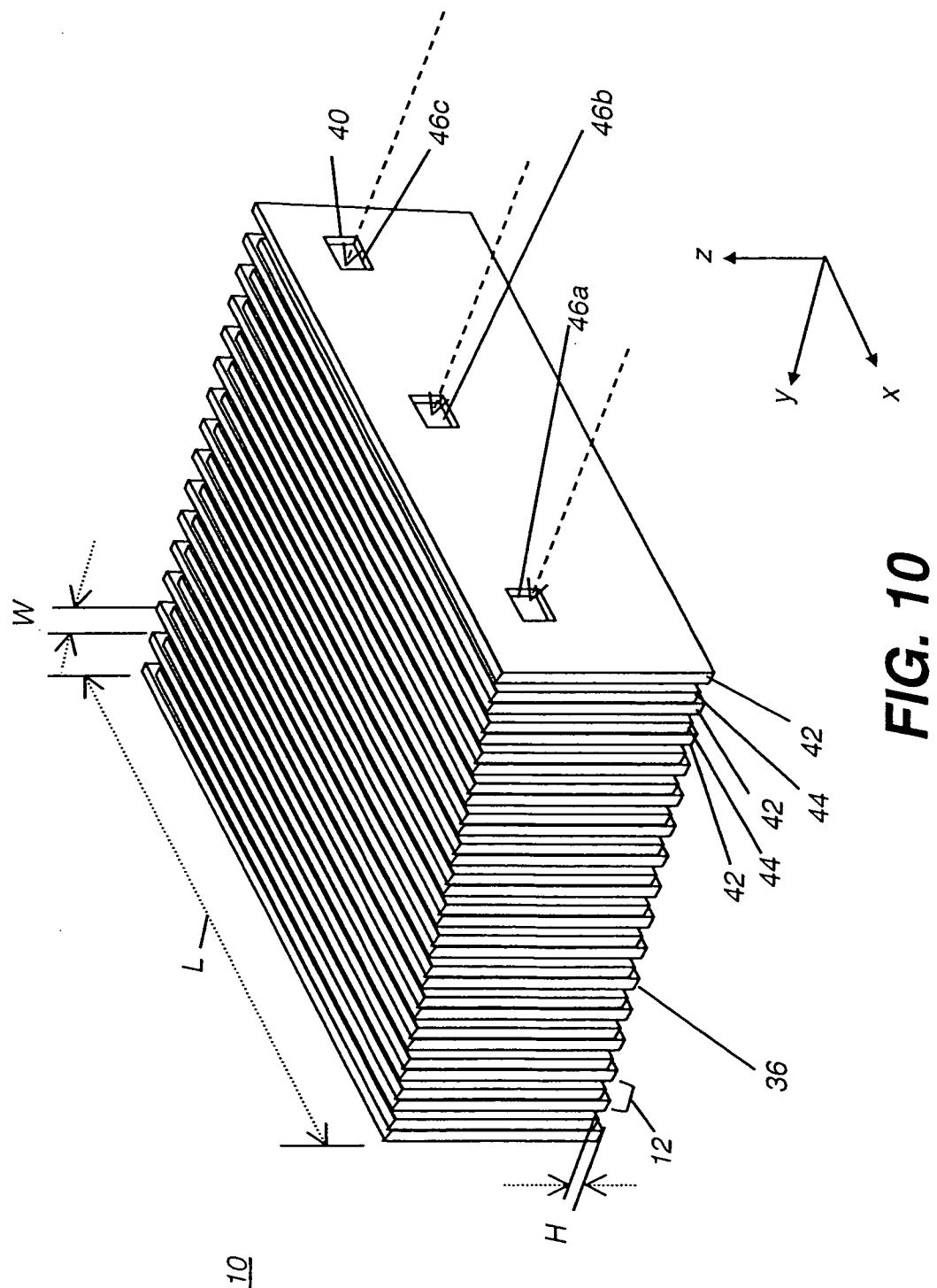

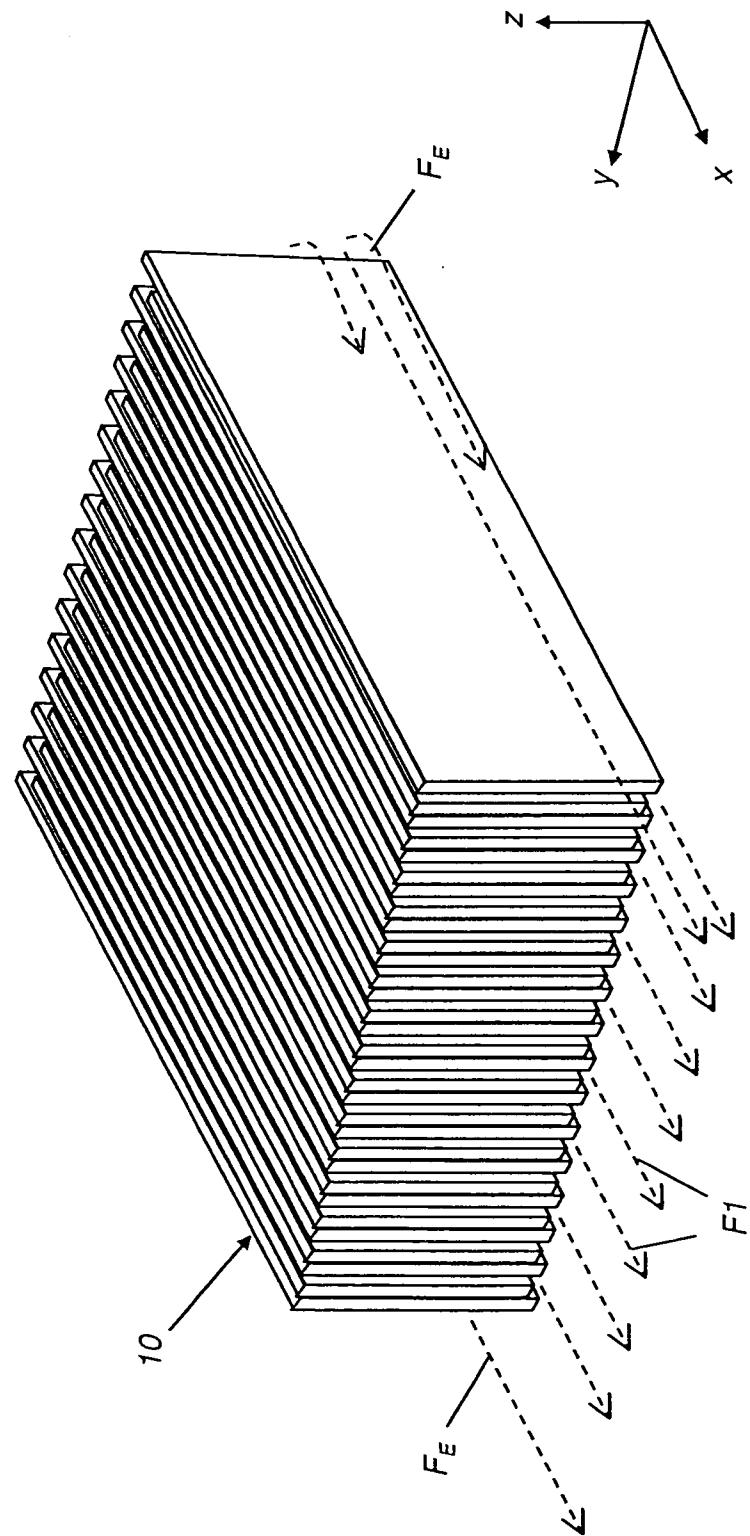

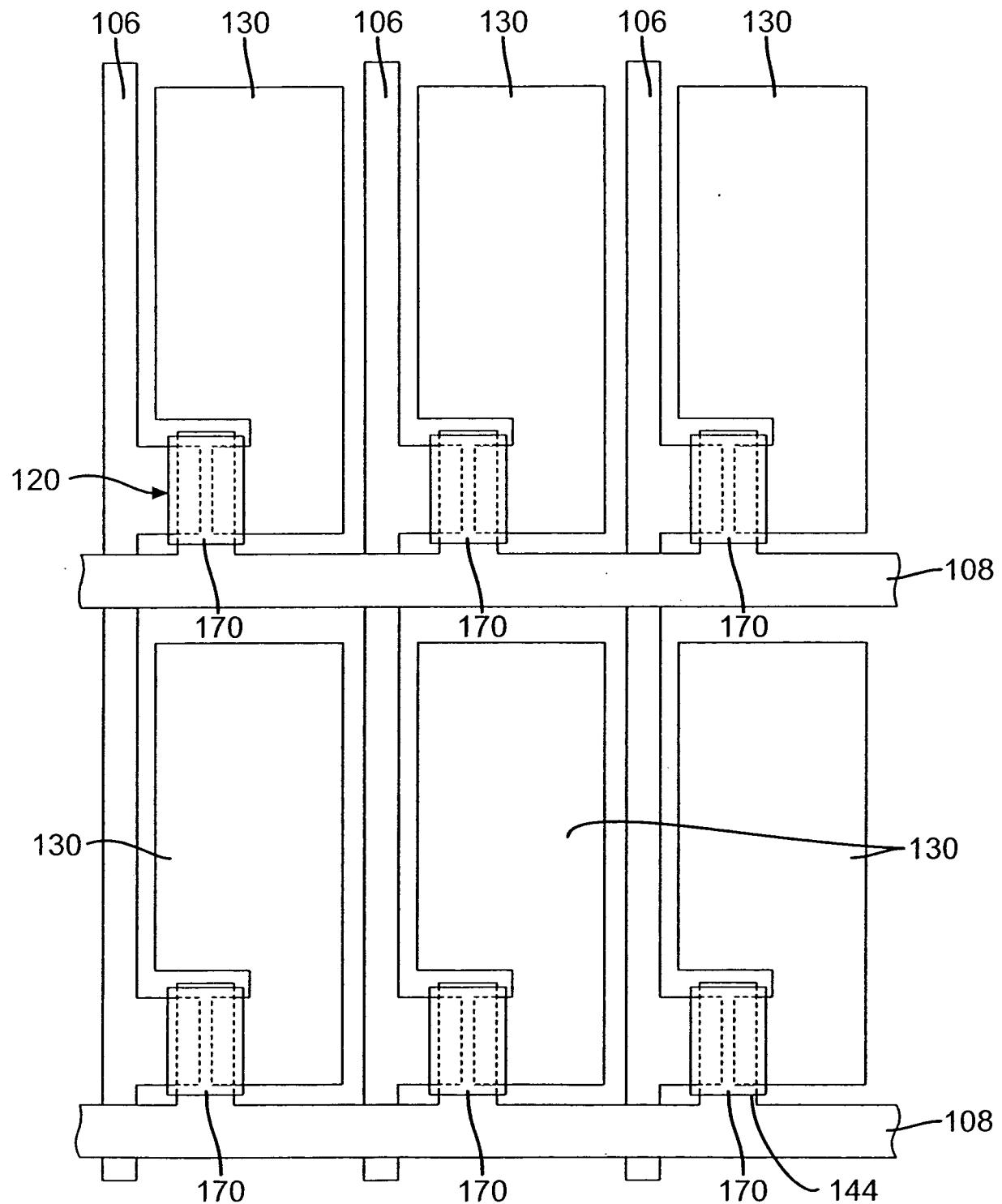

Figure 10 is a perspective view of one embodiment of a deposition device formed from stacked plates that can be used in the present process;

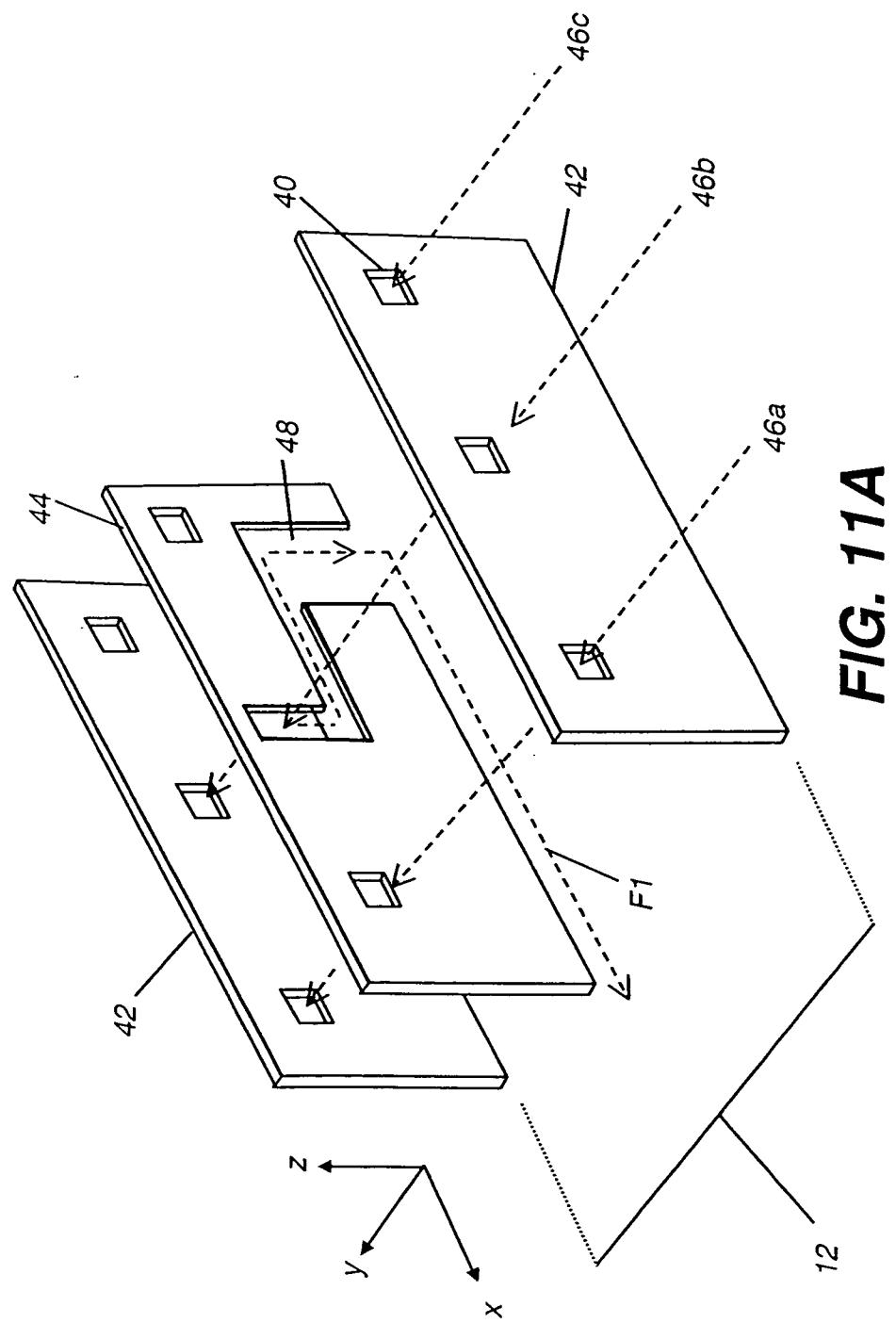

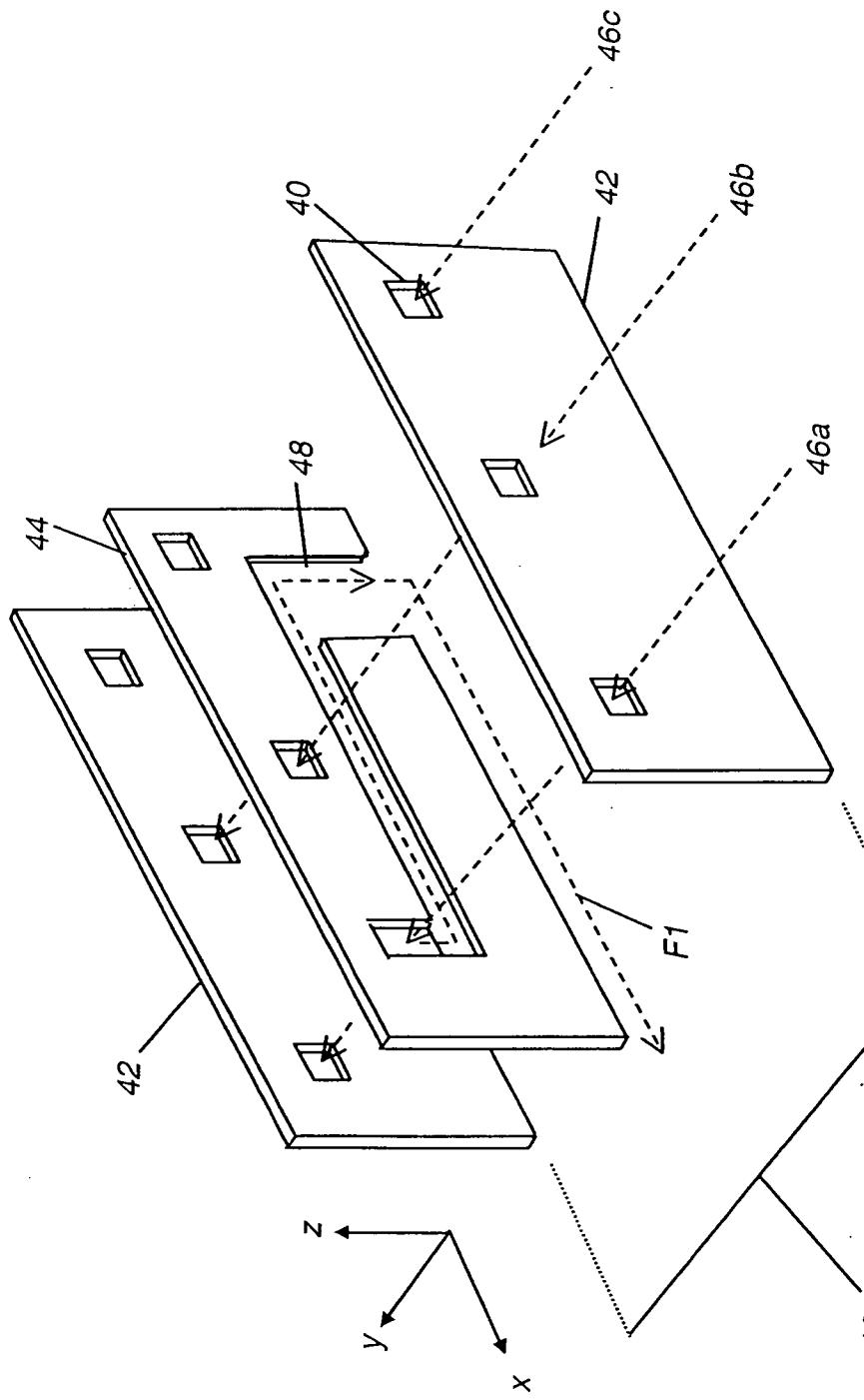

Figures 11A and 11B are exploded views of the construction of a deposition device that employs the stacked-plate structure shown in Figure 10, the 15 exploded views showing two different output channels for different gases used in the process;

Figure 12 is a perspective view showing an embodiment using an enveloping shroud of inert gas directed along the perimeter of the deposition device;

20 Figure 13 is a schematic diagram showing an alternative motion pattern for reciprocating and orthogonal movement;

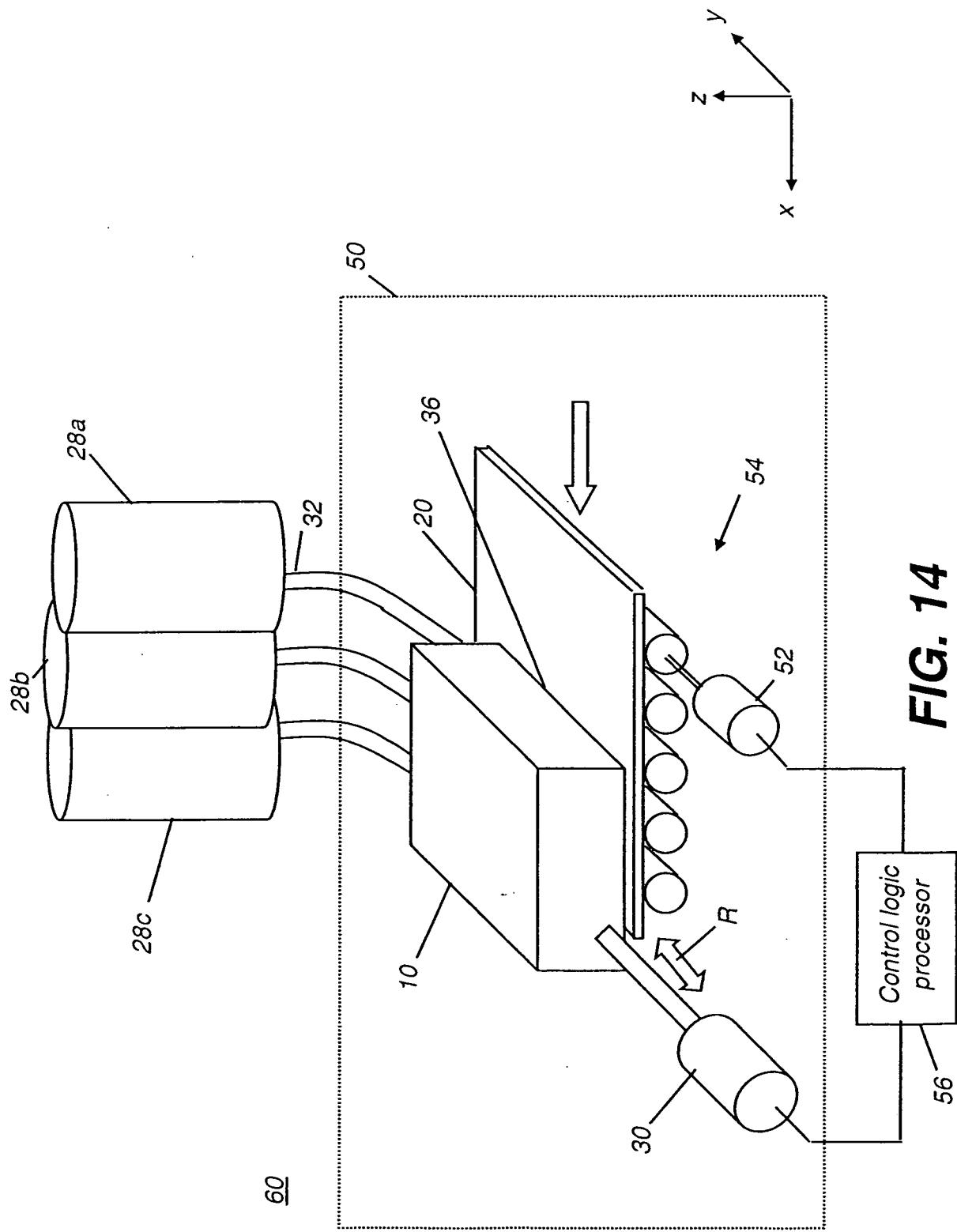

Figure 14 is a block diagram of one embodiment of a deposition system that uses the process according to the present invention;

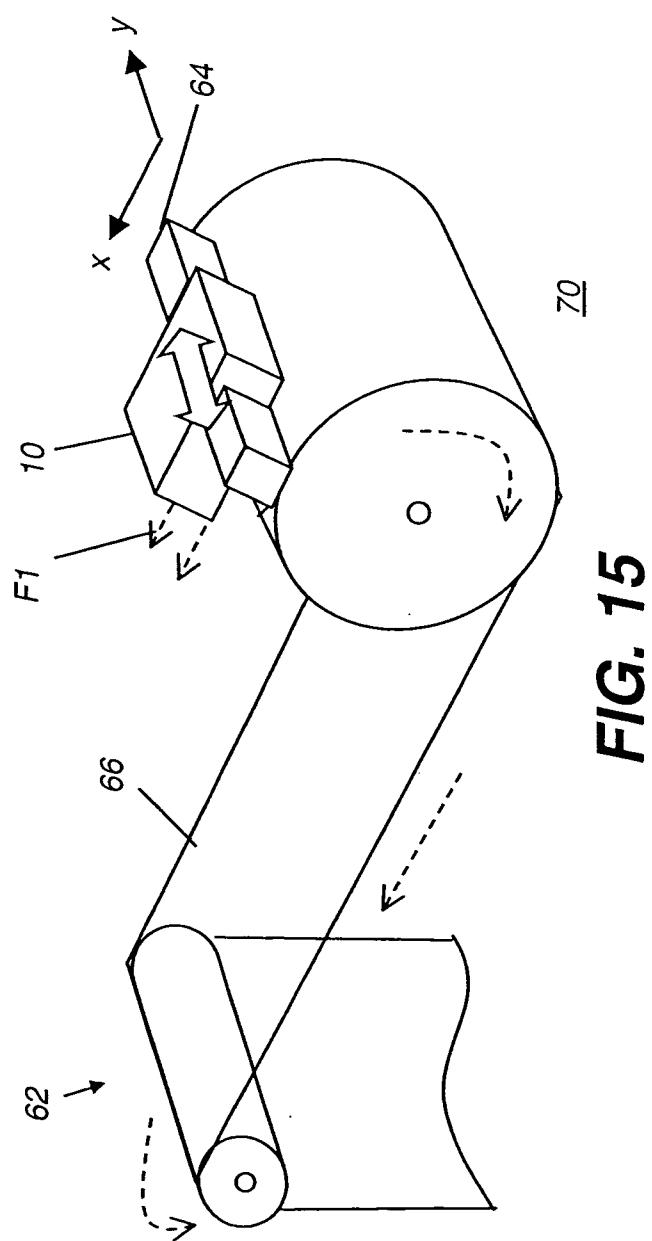

25 Figure 15 is a block diagram showing one embodiment of a deposition system applied to a moving web in accordance with the present process;

Figure 16 is a block diagram showing another embodiment of deposition system applied to a moving web in accordance with the present process, with the deposition device stationary;

30 Figure 17 is a cross-sectional side view of one embodiment of a deposition device with an output face having curvature that can be used in the present process;

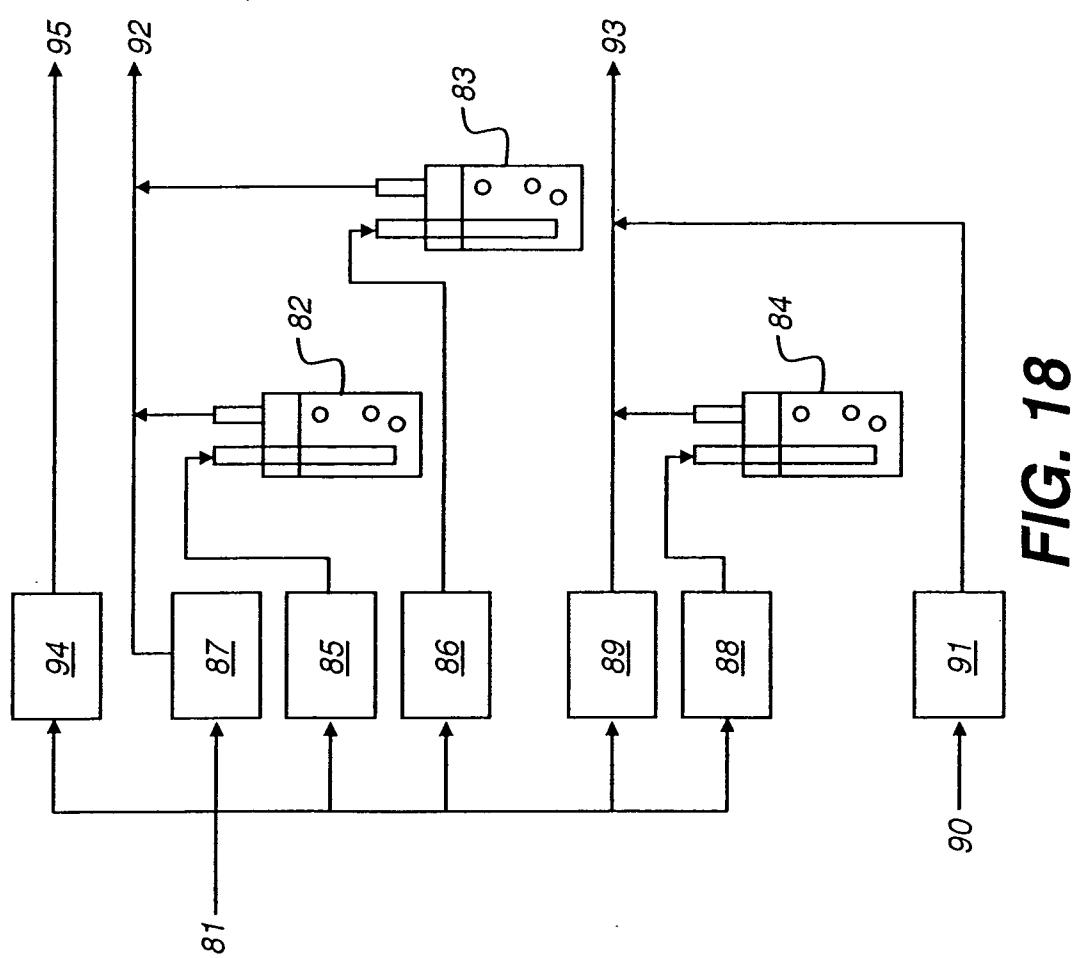

Figure 18 is a block diagram of the source materials for a thin film deposition process according to the Examples;

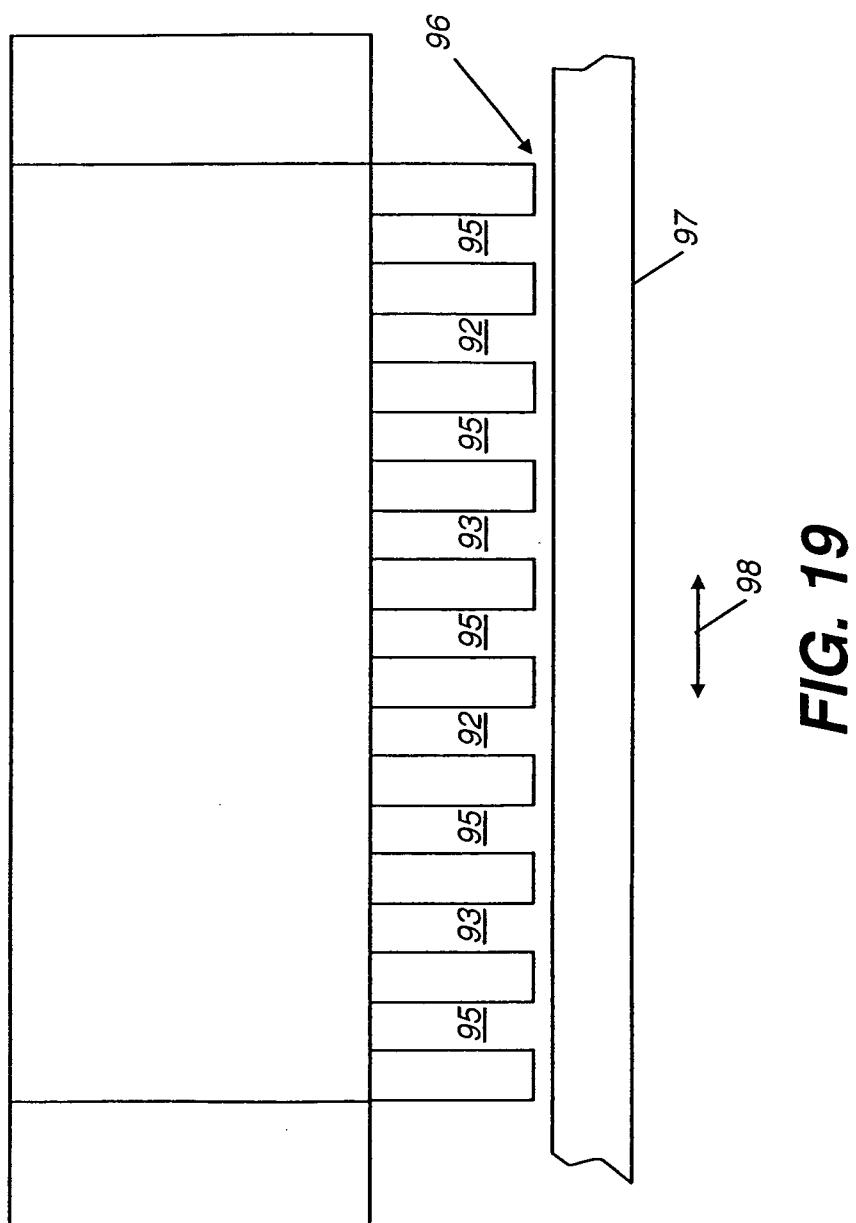

Figure 19 is a cross-sectional side view of the a deposition device used in the present process, showing the arrangement of gaseous materials provided to a substrate that is subject to thin film deposition process of the Examples;

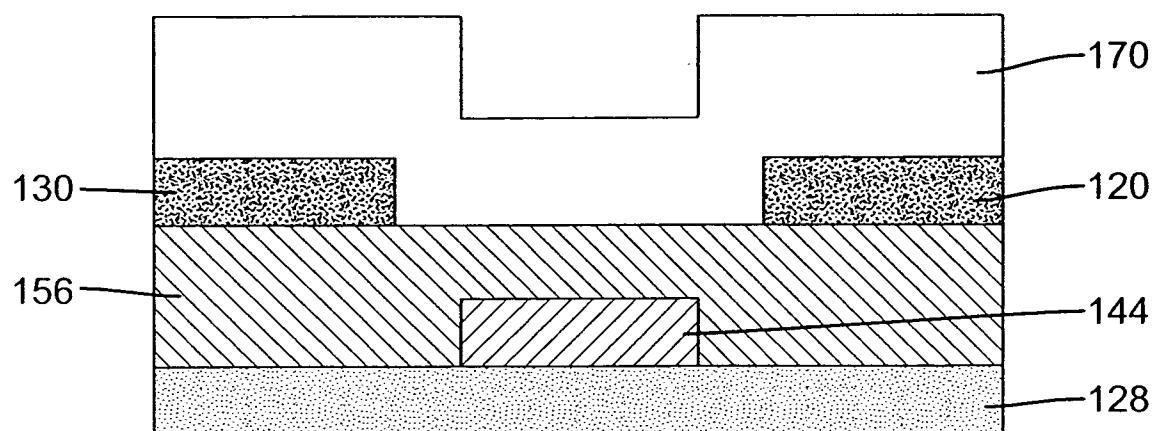

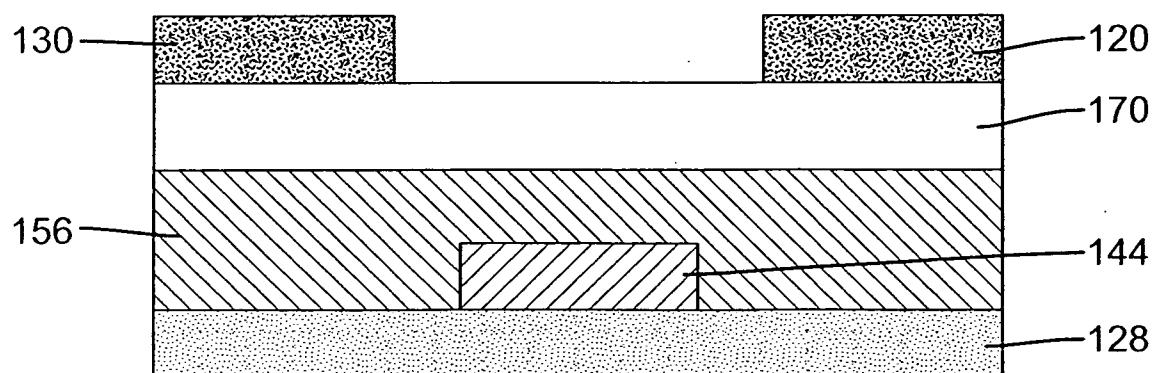

Fig. 20 illustrates a cross-sectional view of a typical thin film transistor

5 having a bottom-gate/bottom-contact configuration;

FIG. 21 illustrates a cross-sectional view of a typical thin film transistor

having a bottom-gate/top-contact configuration;

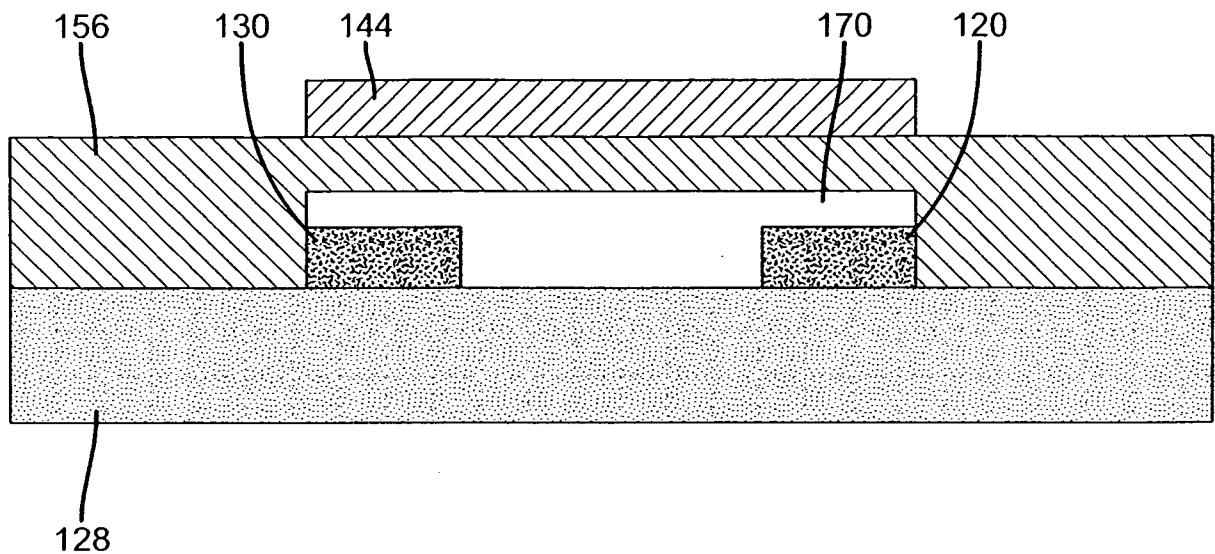

FIG. 22 illustrates a cross-sectional view of a typical thin film transistor

having a top-gate/bottom-contact structure;

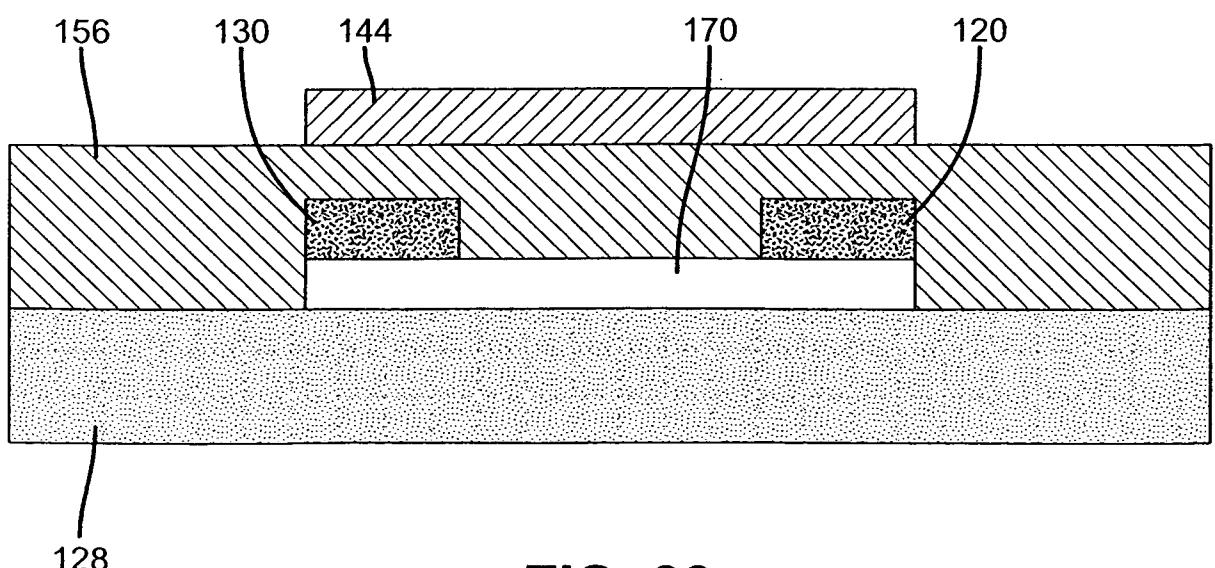

10 FIG. 23 illustrates a cross-sectional view of a typical thin film transistor

having a top-gate/top-contact structure;

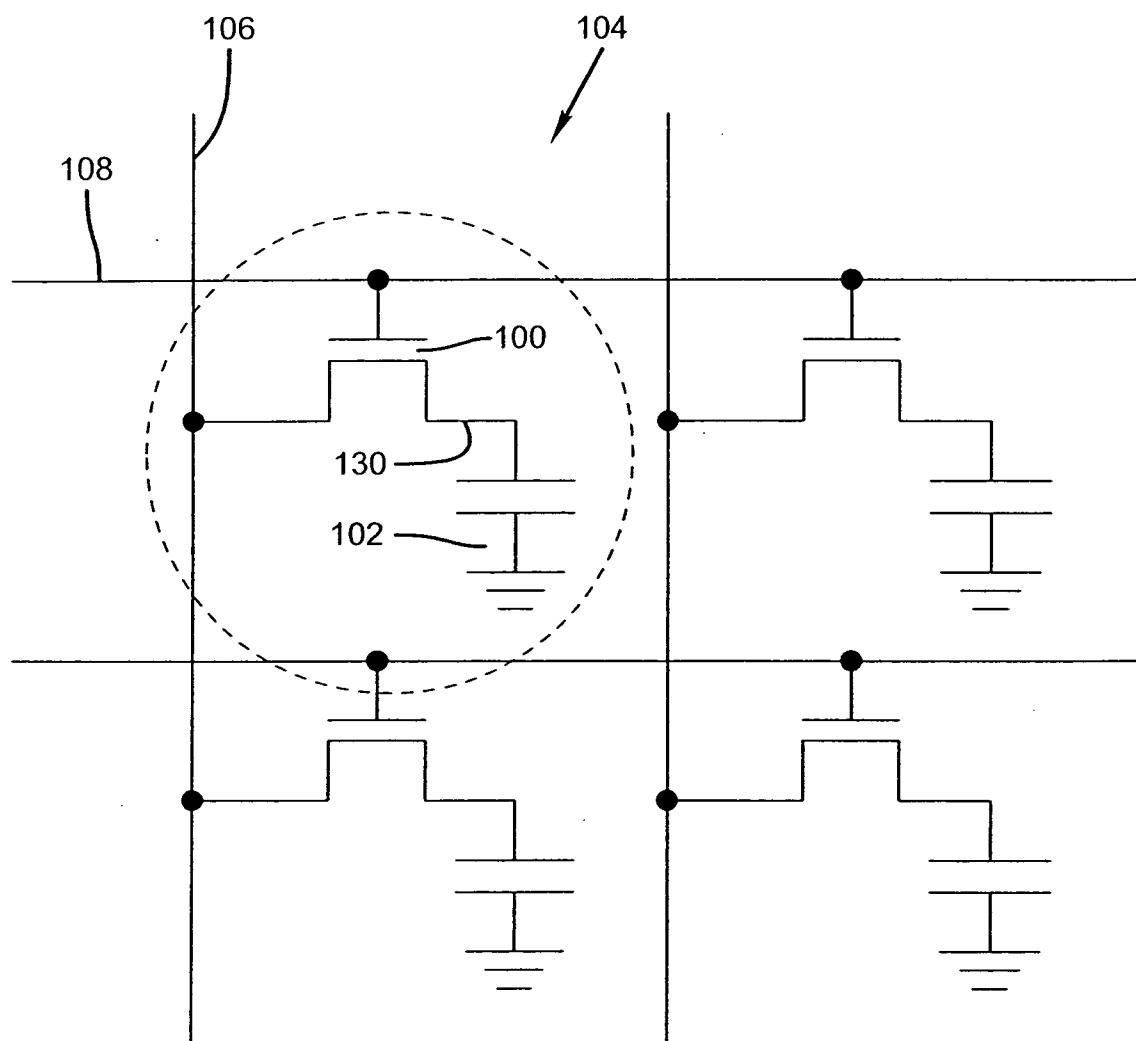

FIG. 24 illustrates a typical active matrix pixel design comprising a select

transistor and capacitor representing the capacitance due to display design;

15 FIG. 25 illustrates a typical pixel layout comprising data lines, control

lines, thin film transistors, and pixel conductor pads;

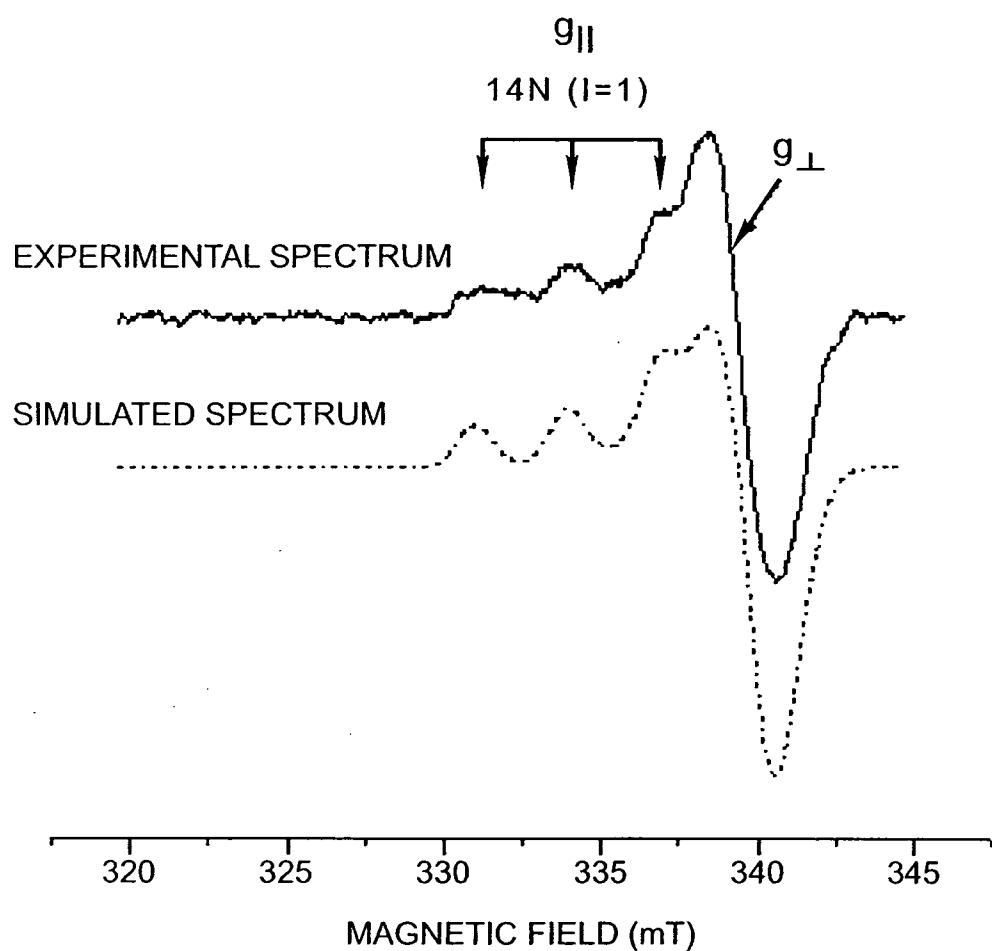

FIG. 26 shows, for Example 5 below, a typical EPR spectrum of the

doped sample (solid line) and a calculated EPR line-shape using the given

parameters of the spin-Hamiltonian; and

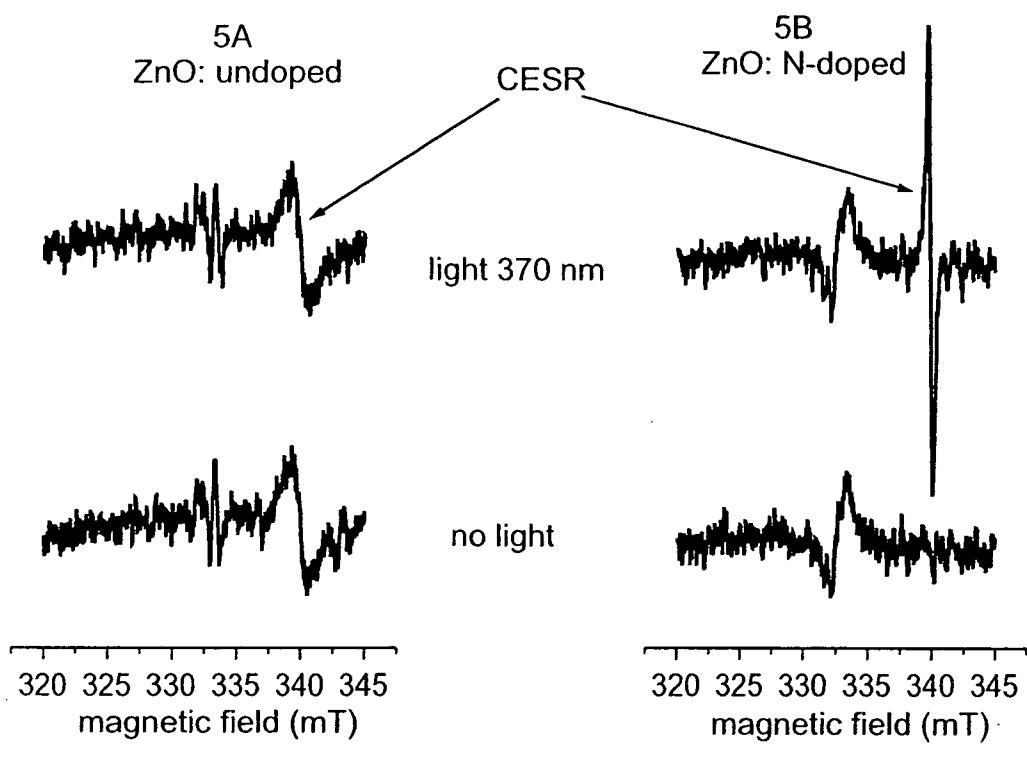

20 FIG. 27 shows, for Example 5, a comparison of EPR spectra of an

undoped and nitrogen-doped thin film of ZnO.

#### **DETAILED DESCRIPTION OF THE INVENTION**

The semiconductor films made according to the present method exhibit a field effect electron mobility that is greater than  $0.01 \text{ cm}^2/\text{Vs}$ , preferably at least  $0.1 \text{ cm}^2/\text{Vs}$ , more preferably greater than  $1 \text{ cm}^2/\text{Vs}$ . In addition, n-channel

25 semiconductor devices made according to the present invention are capable of providing on/off ratios of at least  $10^4$ , advantageously at least  $10^5$  or  $10^6$ .

Furthermore, it is desired that the device be weakly or not at all influenced by visible light. In order for this to be true, the semiconductor band gap should be sufficiently large ( $> 3 \text{ eV}$ ) so that exposure to visible light does not cause an inter-

30 band transition.

Zinc-oxide based materials are capable of yielding a high mobility, low carrier concentration, and high band gap. Furthermore, in a real high volume web based atmospheric manufacturing scheme, it is highly desirable that the

chemistries used in the process be both cheap and of low toxicity, which can be satisfied by the use of ZnO-based materials and the majority of its precursors.

The zinc-oxide-based semiconductor material can contain minor amounts of other metals capable of forming semiconducting oxides such as indium, tin, or 5 cadmium, and combinations thereof. For example, Chiang, H.Q. et al., "High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer," *Applied Physics Letters* **86**, 013503 (2005) discloses zinc tin oxide materials.

Accordingly, the term "zinc-oxide-based" refers to a composition 10 comprising mostly zinc oxide, preferably at least 80 percent, but allowing additives or mixtures with minor amounts of other metal oxides, which semiconductor compositions are known to the skilled artisan.

Nominally undoped zinc oxide shows n-type conductivity because of the presence of shallow donors. Lattice imperfections due to a deviation from 15 stoichiometry are thought to play a role in the creation of shallow donor states, although unintentionally incorporated hydrogen is also considered as a source of shallow donor states. See D. C. Look, J. R. Sizelove and J. W. Hemsky, *Phys. Rev. Lett.* **82**, 2552 - 2555 (1999); C. G. Van de Walle, *Phys. Rev. Lett.* **85** 1012 (2000). These shallow donors have in common that they introduce occupied 20 energy levels that are less than 100 meV below the conduction band edge of zinc oxide. Electrons occupying these shallow donor states can be promoted into the conduction band via thermal excitation and lead to intrinsic conductivity.

In order to improve off currents, the zinc oxide based semiconductor should have low numbers of native charge carriers, leading to a high resistivity. 25 According to the present invention, the resistivity of the ZnO is enhanced by substitutional doping with an acceptor dopant made from a volatile organic compound, for example, volatile compounds comprising an acceptor dopant such as N, P, As, Li, Na, K, Cu, Ag, or mixtures thereof. Preferably, the acceptor dopant comprises a Group V element, more preferably nitrogen, for example, 30 using an acceptor dopant precursor comprises nitrogen in the form of NO, N<sub>2</sub>O, NO<sub>2</sub>, or ammonia.

Typically, the acceptor dopant has fewer valence electrons than the atom it replaces, whether a Group (V) element substituting for oxygen or a Group (I) or (IB) element substituting for zinc.

In preferred embodiments of the invention, the on-off ratio of the 5 semiconductor without the acceptor dopant is less than  $1.0 \times 10^6$ . Also, the presence of the acceptor dopant provides an increase in resistivity of at least  $10^2$  wherein the resistivity of the semiconductor without the acceptor dopant is less than 500 ohm\*cm. In especially preferred embodiments, the presence of the acceptor dopant also provides an increase in mobility of at least 25 percent, more 10 preferably at least 50 percent.

Volatile compounds are defined as compounds that can exist to some extent in the vapor phase at room temperature, so that they may be delivered to a reaction chamber in the form of a gas. In order for such a gas to contain sufficient volatile materials to usefully affect the deposition process, the volatile compound 15 should have a vapor pressure at room temperature of greater than 0.1 mmHg, preferably greater than 1 mmHg. Such dopants are preferably present in the final semiconductor in the amount of 0.001% to 5%, more preferably 0.01% to 1%.

An acceptor dopant in the scope of this invention is an impurity that introduces an energy level within the band-gap of ZnO-based materials that is 20 below the energy level of shallow donors and is able to accept an electron. Such an acceptor dopant can be an impurity atom that has fewer valence electrons than the atom it replaces. Examples for ZnO-based materials are group (V) elements substituting for oxygen, e.g., nitrogen, phosphorous or arsenic or Group (I) and (IB) elements substituting for zinc, e.g. lithium, sodium, potassium, copper or 25 silver. See Ü. Özgür, Ya. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Doan, V. Avrutin, S.-J. Cho, and H. Morkoç, J. Appl. Phys. **98** 041301 (2001).

In addition, minor amounts of various optional conventional dopants known to the skilled artisan, preferably less than 10 weight percent, can also be included in the zinc-oxide-based semiconductor during or after deposition. The 30 thickness of the channel layer may vary, and according to particular examples it can range from 5 nm to 500 nm, 10 nm to 50 nm.

The length and width of the channel is determined by the pixel size and the design rules of the system under construction. Typically, the channel width may

vary from 10 to 1000  $\mu\text{m}$ . The channel length may vary, and according to particular examples it can range from 1 to 100  $\mu\text{m}$ .

The entire process of making the thin film transistor or electronic device of the present invention, or at least the production of the thin film semiconductor, 5 can be carried out below a maximum support temperature of 300° C, more preferably below 250° C, or even at temperatures around room temperature (25° C to 70°C). The temperature selection generally depends on the support and processing parameters known in the art, once one is armed with the knowledge of the present invention contained herein. These temperatures are well below 10 traditional integrated circuit and semiconductor processing temperatures, which enables the use of any of a variety of relatively inexpensive supports, such as flexible polymeric supports. Thus, the invention enables production of relatively inexpensive circuits containing thin film transistors with significantly improved performance.

15 For the description that follows, the term “gas” or “gaseous material” is used in a broad sense to encompass any of a range of vaporized or gaseous elements, compounds, or materials. Other terms used herein, such as: reactant, precursor, vacuum, and inert gas, for example, all have their conventional meanings as would be well understood by those skilled in the materials deposition 20 art. The figures provided are not drawn to scale but are intended to show overall function and the structural arrangement of some embodiments of the present invention.

The process of the present invention offers a significant departure from conventional approaches to making a film of zinc-oxide-based n-type 25 semiconductor, employing a system for delivery of gaseous materials to a substrate surface that can be adaptable to deposition on larger and web-based substrates and capable of achieving a highly uniform thin-film deposition at improved throughput speeds. The process of the present invention employs a continuous spatially dependent ALD (as opposed to pulsed or time dependent 30 ALD) gaseous material distribution. The process of the present invention allows operation at atmospheric or near-atmospheric pressures and is capable of operating in an unsealed or open-air environment.

Figure 1 is a generalized step diagram of one embodiment of a process for making a film of zinc-oxide-based n-type semiconductor according to an embodiment of the present invention, in which two reactive gases are used, a first molecular precursor and a second molecular precursor. Gases are supplied from a 5 gas source and can be delivered to the substrate, for example, via a deposition device. Metering and valving apparatus for providing gaseous materials to the a deposition device can be used.

As shown in Step 1, a continuous supply of gaseous materials for the system is provided for depositing a thin film of material on a substrate. The Steps 10 in Sequence 15 are sequentially applied. In Step 2, with respect to a given area of the substrate (referred to as the channel area), a first molecular precursor or reactive gaseous material is directed to flow in a first channel over the channel area of the substrate and reacts therewith. In Step 3 relative movement of the substrate and the multi-channel flows in the system occurs, which sets the stage 15 for Step 4, in which second channel (purge) flow with inert gas occurs over the given channel area. Then, in Step 5, relative movement of the substrate and the multi-channel flows sets the stage for Step 6, in which the given channel area is subjected to atomic layer deposition in which a second molecular precursor now (in this particular embodiment, transversely and substantially parallel to the 20 surface of the substrate) over the given channel area of the substrate and reacts with the previous layer on the substrate to produce (theoretically) a monolayer of a desired material. A first molecular precursor is a zinc-containing compound in gas form, and the material deposited is a zinc-containing compound, for example, an organozinc compound such as diethylzinc. In such an embodiment, the second 25 molecular precursor can be, for example, a non-metallic oxidizing compound. A volatile acceptor doping compound can be supplied to the system in any way in which allows it to react to sites in the growing film. Thus it can be delivered with the first or second molecular precursors, or with the purge gas. Preferably the volatile acceptor is delivered in common with the oxidizing molecular precursor.

30 In Step 7, relative movement of the substrate and the multi-channel flows then sets the stage for Step 8 in which again an inert gas is used, this time to sweep excess second molecular precursor from the given channel area from the previous Step 6. In Step 9, relative movement of the substrate and the multi-channels occurs again, which sets the stage for a repeat sequence, back to Step 2.

The cycle is repeated as many times as is necessary to establish a desired film. In the present embodiment of the process, the steps are repeated with respect to a given channel area of the substrate, corresponding to the area covered by a flow channel. Meanwhile the various channels are being supplied with the necessary 5 gaseous materials in Step 1. Simultaneous with the sequence of box 15 in Figure 1, other adjacent channel areas are being processed, which results in Multiple channel flows in parallel, as indicated in overall Step 11. Parallel flow can be either substantially orthogonal or substantially parallel to the output face of the deposition device.

10 The primary purpose of the second molecular precursor is to condition the substrate surface back toward reactivity with the first molecular precursor. The second molecular precursor also provides material from the molecular gas to combine with metal at the surface, forming an oxide with the freshly deposited zinc-containing precursor.

15 This particular embodiment does not need to use a vacuum purge to remove a molecular precursor after applying it to the substrate. Purge steps are expected by most researchers to be the most significant throughput-limiting step in ALD processes.

Assuming that, for the two reactant gases in Figure 1, AX and BY are 20 used, for example. When the reaction gas AX flow is supplied and flowed over a given substrate area, atoms of the reaction gas AX are chemically adsorbed on a substrate, resulting in a layer of A and a surface of ligand X (associative chemisorptions) (Step 2). Then, the remaining reaction gas AX is purged with an inert gas (Step 4). Then, the flow of reaction gas BY, and a chemical reaction 25 between AX (surface) and BY (gas) occurs, resulting in a molecular layer of AB on the substrate (dissociative chemisorptions) (Step 6). The remaining gas BY and by-products of the reaction are purged (Step 8). The thickness of the thin film can be increased by repeating the process cycle (steps 2-9) many times.

Because the film can be deposited one monolayer at a time it tends to be 30 conformal and have uniform thickness.

Oxides that can be made using the process of the present invention include, but are not limited to: ZnO, indium oxide, tin oxide. Mixed structure oxides that can be made using the process of the present invention can include, for example, InZnO and InGaZnO. Doped materials that can be made using the

process of the present invention can include, for example, ZnO:Al, GaInZnO, Mg<sub>x</sub>Zn<sub>1-x</sub>O, and LiZnO.

It will be apparent to the skilled artisan that alloys of two, three or more metals may be deposited, compounds may be deposited with two, three or more 5 constituents, and such things as graded films and nano-laminates may be produced as well.

These variations are simply variants using particular embodiments of the invention in alternating cycles.

For various volatile zinc-containing precursors, precursor combinations, 10 and reactants useful in ALD thin film processes, reference is made to the Handbook of Thin Film Process Technology, Vol. 1, edited by Glocker and Shah, Institute of Physics (IOP) Publishing, Philadelphia 1995, pages B1.5:1 to B1.5:16; and Handbook of Thin Film Materials, edited by Nalwa, Vol.1, pages 103 to 159.

15 Although oxide substrates provide groups for ALD deposition, plastic substrates can be used by suitable surface treatment.

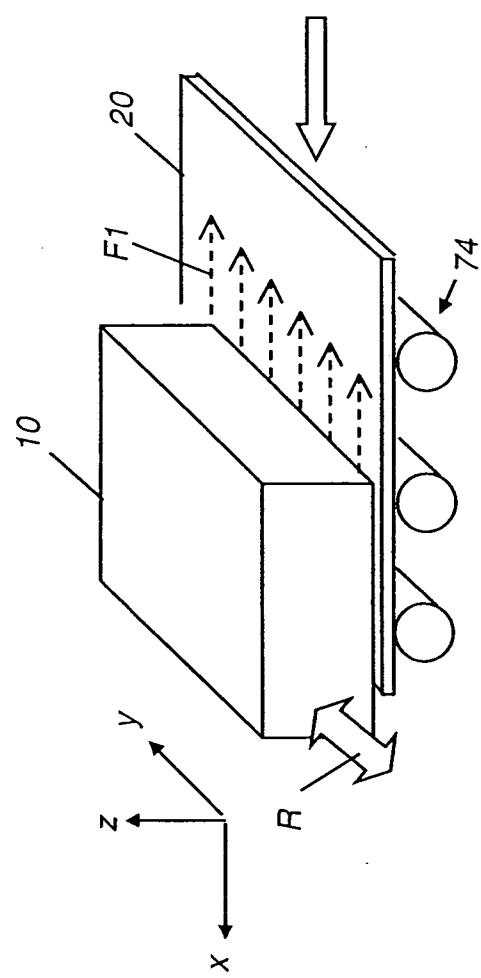

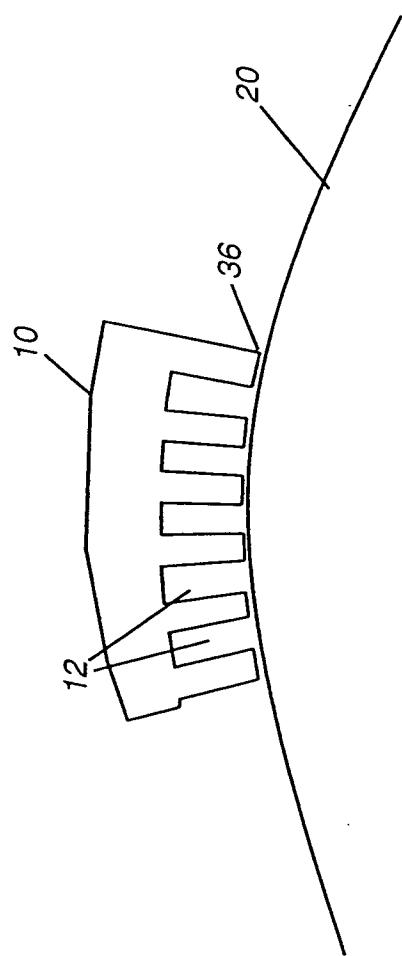

Referring now to Figure 2, there is shown a cross-sectional side view of one embodiment of a deposition device 10 that can be used in the present process for atomic layer deposition of a zinc-oxide-based semiconductor onto a substrate 20 according to the present invention. Deposition device 10 has a gas inlet port 14 20 for accepting a first gaseous material, a gas inlet port 16 for accepting a second gaseous material, and a gas inlet port 18 for accepting a third gaseous material. These gases are emitted at an output face 36 via output channels 12, having a structural arrangement described subsequently. The arrows in Figure 2 and 25 subsequent Figures 3-4B refer to the diffusive transport of the gaseous material, and not the flow, received from an output channel. In this particular embodiment, the flow is substantially directed out of the page of the figure, as described further below.

In one embodiment, gas inlet ports 14 and 16 are adapted to accept first 30 and second gases that react sequentially on the substrate surface to effect ALD deposition, and gas inlet port 18 receives a purge gas that is inert with respect to the first and second gases. Deposition device 10 is spaced a distance D from substrate 20, provided on a substrate support, as described in more detail subsequently. Reciprocating motion can be provided between substrate 20 and deposition device 10, either by movement of substrate 20, by movement of

deposition device 10, or by movement of both substrate 20 and deposition device 10. In the particular embodiment shown in Figure 2, substrate 20 is moved across output face 36 in reciprocating fashion, as indicated by the arrow R and by phantom outlines to the right and left of substrate 20 in Figure 2. It should be 5 noted that reciprocating motion is not always required for thin-film deposition using deposition device 10. Other types of relative motion between substrate 20 and deposition device 10 could also be provided, such as movement of either substrate 20 or deposition device 10 in one or more directions, as described in more detail subsequently.

10 The cross-sectional view of Figure 3 shows gas flows emitted over a portion of output face 36 of deposition device 10. In this particular arrangement, each output channel 12, separated by partitions 22, is in gaseous flow communication with one of gas inlet ports 14, 16 or 18 seen in Figure 2. Each output channel 12 delivers typically a first reactant gaseous material O, or a 15 second reactant gaseous material M, or a third inert gaseous material I.

Figure 3 shows a relatively basic or simple arrangement of gases. It is envisioned that a plurality of non-metal deposition precursors (like material O) or a plurality of metal-containing precursor materials, including at least a zinc-containing precursor (like material M) may be delivered sequentially at various 20 ports in a thin-film single deposition. Alternately, a mixture of reactant gases, for example, a mixture of metal precursor materials or a mixture of metal and non-metal precursors may be applied at a single output channel when making complex thin film materials, for example, having alternate layers of metals or having lesser amounts of dopants admixed in a metal oxide material. The inter-stream labeled I 25 separates any reactant channels in which the gases are likely to react with each other. First and second reactant gaseous materials O and M react with each other to effect ALD deposition, but neither reactant gaseous material O nor M reacts with inert gaseous material I. The nomenclature used in Figure 3 and following suggests some typical types of reactant gases. For example, first reactant gaseous 30 material O could be an oxidizing gaseous material; second reactant gaseous material M would be a metallic zinc-containing compound. Inert gaseous material I could be nitrogen, argon, helium, or other gases commonly used as purge gases in ALD processes. Inert gaseous material I is inert with respect to first or second reactant gaseous materials O and M. Reaction between first and second reactant

gaseous materials would form a metal oxide or other binary compound, such as zinc oxide ZnO, in one embodiment. Reactions between more than two reactant gaseous materials could form other zinc-oxide based materials such as a ternary compound, for example, ZnAlO.

5 The cross-sectional views of Figures 4A and 4B show, in simplified schematic form, the ALD coating operation performed as substrate 20 passes along output face 36 of deposition device 10 when delivering reactant gaseous materials O and M. In Figure 4A, the surface of substrate 20 first receives an oxidizing material from output channels 12 designated as delivering first reactant

10 gaseous material O. The surface of the substrate now contains a partially reacted form of material O, which is susceptible to reaction with material M. Then, as substrate 20 passes into the path of the metal compound of second reactant gaseous material M, the reaction with M takes place, forming a metallic oxide or some other thin film material that can be formed from two reactant gaseous

15 materials.

As Figures 4A and 4B show, inert gaseous material I is provided in every alternate output channel 12, between the flows of first and second reactant gaseous materials O and M. Sequential output channels 12 are adjacent, that is, share a common boundary, formed by partitions 22 in the embodiments shown.

20 Here, output channels 12 are defined and separated from each other by partitions 22 that extend at a perpendicular to the surface of substrate 20.

As mentioned above, in this particular embodiment, there are no vacuum channels interspersed between the output channels 12, that is, no vacuum channels on either side of a channel delivering gaseous materials to draw the gaseous

25 materials around the partitions. This advantageous, compact arrangement is possible because of the innovative gas flow that is used. Unlike gas delivery arrays of earlier processes that apply substantially vertical (that is, perpendicular) gas flows against the substrate and should then draw off spent gases in the opposite vertical direction, deposition device 10 directs a gas flow (preferably

30 substantially laminar in one embodiment) along the surface for each reactant and inert gas and handles spent gases and reaction by-products in a different manner, as described subsequently. The gas flow used in the present invention is directed along and generally parallel to the plane of the substrate surface. In other words,

the flow of gases is substantially transverse to the plane of a substrate rather than perpendicular to the substrate being treated.

Figures 5 and 6 show perspective views of one embodiment of a deposition device 10 that can be used in the present process, from the output face 5 36 (that is, from the underside with respect to Figures 2 - 4B). Partitions 22 that define and separate the adjacent output channels 12 in this embodiment are represented as partially cut away, to allow better visibility for the gas flows flowing from gas outlet ports 24. Figures 5 and 6 also show reference  $x, y, z$  coordinate axis assignments used in the figures of this disclosure. Output 10 channels 12 are substantially in parallel and extend in a length direction that corresponds to the  $x$  coordinate axis. Reciprocating motion of substrate 20, or motion relative to substrate 20, is in the  $y$  coordinate direction, using this coordinate assignment.

Figure 6 shows the gas flows  $F_I$ ,  $F_O$ , and  $F_M$  for the various gaseous 15 materials delivered from deposition device 10 with this embodiment. Gas flows  $F_I$ ,  $F_O$ , and  $F_M$  are in the  $x$ -direction, that is, along the length of elongated output channels 12.

The cross-sectional views of Figures 7A, 7B, 7C, and 7D are taken orthogonally to the cross-sections of Figures 2 – 4B and show gas flows in one 20 direction from this view. Within each output channel 12, the corresponding gaseous material flows from a gas output port 24, shown in phantom in the views of Figures 7A, 7B, 7C, and 7D. In the embodiment of Figure 7A, gas flow  $F_1$  directs the gaseous material along the length of output channel 12 and across substrate 20, as was described with reference to Figures 5 and 6. Flow  $F_1$  25 continues past the edge of deposition device 10 in this arrangement, flowing outward into the environment or, if desirable, to a gas collection manifold (not shown). Figure 7B shows an alternative embodiment for gas flow  $F_2$  in which output channel 12 also provides an exhaust port 26 for redirection or drawing off of the gas flow. Figure 7C shows an alternative embodiment for gas flow  $F_3$ , in 30 which gas output port 24 is centrally located within output channel 12 and directs gaseous material in gas flows along the channel in both directions. Figure 7D shows an alternate embodiment for gas flow  $F_4$ , in which gas output port 24 is also centrally positioned, with multiple exhaust ports 26 suitably placed near the extreme ends of output channel 12. Although unidirectional flows are preferred,

some degree of mixing can occur and even may be beneficial to some extent, depending on the flow rates and other circumstances involved in a particular application.

A particular deposition device 10 may use output channels 12 configured 5 using any one of the gas flow configurations or combinations thereof, either the F1 flow of Figure 7A, the F2 flow of Figure 7B, the F3 flow of Figure 7C, the F4 flow of Figure 7D, or some other variation in which gaseous material is directed to flow across substrate 20 along output channel 12, preferably in a substantially laminar or smooth fashion with controlled mixing. In one embodiment, one or 10 more exhaust ports 26 are provided for each output channel 12 that delivers a reactant gaseous material. For example, referring to Figure 6, output channels 12 for first and second reactant gaseous materials, labeled O and M, are configured with exhaust ports 26 to vent or draw off the reactant substances, following the pattern of flow F2 (Figure 7B). This allows some recycle of materials and 15 prevents undesirable mixing and reaction near the end of the manifold. Output channels 12 for inert gaseous material, labeled I, do not use exhaust ports 26 and thus follow the pattern of flow F1 (Figure 7A). Although laminar flows are preferred in some embodiments, some degree of mixing can occur and even may be beneficial to some extent, depending on the flow rates and other circumstances 20 involved in a particular application.

Exhaust port 26 is not a vacuum port, in the conventional sense, but is simply provided to draw off the gaseous flow in its corresponding output channel 12, thus facilitating a uniform gas flow pattern within the channel. A negative draw, just slightly less than the opposite of the gas pressure at gas output port 24, 25 can help to facilitate an orderly gas flow. The negative draw can, for example, operate at a pressure of between 0.9 and 1.0 atmosphere, whereas a typical vacuum is, for example, below 0.1 atmosphere. An optional baffle 58, as shown in dotted outline in Figures 7B and 7D may be provided to redirect the flow pattern into exhaust port 26.

Because no gas flow around partition 22 to a vacuum exhaust is needed, 30 output face 36 can be positioned very closely, to within 1 mil (approximately 0.025 mm) of the substrate surface. By comparison, an earlier approach such as that described in the US Patent No. 6,821,563 to Yudovsky, cited earlier, required gas flow around the edges of channel sidewalls and was thus limited to 0.5 mm or

greater distance to the substrate surface. Positioning the deposition device 10 closer to the substrate surface is preferred in the present invention. In a preferred embodiment, distance D from the surface of the substrate can be 0.4 mm or less, preferably within 0.3 mm, more preferably within 0.25 mm of the output face of 5 the deposition device or the bottom of the guide walls that provide the flow channels.

The cross-sectional views of Figures 8A and 8B show why it is desirable that the distance D is relatively small, consistent with the operation used in the invention. In these figures, deposition device 10 is moving over substrate 20 from 10 left to right, as the arrow indicates. As output channel 12 carrying a reactive gaseous material M moves to the right over an area, it encounters a diffusion layer 72 from the next adjacent (previous-in-time) output channel that is primarily inert gaseous material I. In order to react on the surface of substrate 20, reactive gaseous material M should diffuse through diffusion layer 72, which has a 15 thickness proportional to distance D. By comparison, Figure 8B shows what happens when distance D is reduced: diffusion layer 72 is reduced proportionately. Diffusion through diffusion layer 72 happens more quickly and more efficiently, allowing less waste and reducing the overall amount of time needed for reaction on the surface of substrate 20. The lower partition walls 22 20 also prevent less gas to remain from the previous-in time output channel gas. It should be noted that the flow of the gases in the channels are perpendicular to the page of the Figures 8A and 8B, as shown by the back of the arrow, which flow maintains a concentration gradient that aids the diffusion through the thin diffusion layer 72 to the surface of the substrate. The surface is exposed to the gas 25 flow of M for sufficient time for diffusion and any mixing to replace the previous-in-time output channel gas. In this particular embodiment, the flow of gas is across the surface rather than directly into the surface it limits the undesirable mixing of reactant gases between outlet channels, which might otherwise be exacerbated by relative oscillation of the manifold and/or substrate.

30 In order to provide smooth flow along the length of output channel 12, gas output port 24 may be inclined at an angle away from normal, as indicated in Figures 7A and 7B. Optionally, some type of gas flow redirecting structure may also be employed to redirect a downward flow from gas output port 24 so that it forms a gas flow that runs substantially in parallel to output face 36.

The plan view of Figure 9 shows output face 36 of a portion of a deposition device 10 that can be used in one embodiment. For optimizing directional gas flow in this particular embodiment, redirecting plates 38 may be positioned in each of the output channels 12 for directing reactant gaseous materials. In the embodiment shown, only output channels 12 that deliver reactant gaseous materials are provided with redirecting plates 38 and exhaust ports 26. This particular arrangement may be advantageous in some applications, where it is advantageous to surround deposition device 10 with inert gas, such as to reduce unwanted intake of ambient gases. However, redirecting plates 38 could be used on all output channels 12. Also, exhaust ports 26 could be used on some or all output channels 12. In another possible embodiment, redirecting plates can be used on all channels, but the outlet edge of the redirecting plate may be at a different x-axis position depending upon which channel is considered. In particular, it may be desirable to have the outlet edge position of the baffles for the inert flows to be at lower x-axis positions than those of the reactant gases so that the inert purge flows can serve as mentioned above to isolate the various channels.

Figure 9 also shows the pattern of output channels in one embodiment. Here, it has been found to be particularly advantageous to provide inert gas channels I as the outermost channels of deposition device 10. Oxidation channels with first reactant gaseous material O are next to the outermost channels, since these condition the surface for ALD reaction with the metallic component of second reactant gaseous material M.

Figure 10 shows one embodiment of a deposition device 10 that can be used in the present process in which the channels of width W, length L, and height H are formed from stacked metal plates 42 and 44 having apertures 40 forming ducts 46a,b,c. Figure 11A shows an exploded view of a single output channel 12 section of deposition device 10 formed in this way, showing an arrangement of apertures 40 in alternating partition plates 42 and delivery plates 44. Figure 11B shows a similar exploded view for an adjacent output channel 12. Ducts 46a, 46b, and 46c, formed by alignment of apertures 40, extend through deposition device 10 and provide input conduits for gaseous flow communication, accepting the different reactant and inert gaseous materials from external sources and providing the redirecting structures that provide gas flows along output face 36 described earlier. Baffles and other redirecting structures are not shown in these figures, but

could be provided using stacked plates suitably structured, or applied after the device is assembled.

The exploded views of Figures 11A and 11B each show a single output channel 12 formed from stacked plates 42 and 44. In the example of Figure 11A, 5 output channel 12 shown provides gaseous material provided from duct 46b. Ducts 46a and 46c conduct other gases past this channel in the embodiment shown in Figure 11A. Delivery plate 44, dimensioned and apertured differently than the partition plates 42 that bound output channel 12, contains a redirecting chamber 48 that redirects a portion of the gas in duct 46b into gas flow F1. In the example 10 of Figure 11B, output channel 12 shown provides gaseous material provided from duct 46a. Ducts 46b and 46c conduct other gases past this channel in the embodiment shown in Figure 11B. Plates 42 and 44 should be of a suitable metal for conducting the reactive gaseous materials, such as stainless steel or other metal for example.

15 It is desirable that when a large number of plates are assembled for such an embodiment, the gas flow delivered to the substrate is uniform across all of the channels delivering a particle flow (I, M, or O). This can be accomplished by proper design of the plates, such as having restrictions in some part of the flow pattern for each plate which are accurately machined to provide a reproducible 20 pressure drop for each channel.

Although the method of stacking plates is a particularly useful way of constructing a deposition device for use in this invention, there are a number of other methods to build such structures and may be useful in alternate embodiments of deposition devices that can be used in the present process. For 25 example, the deposition device for use in the present process may be constructed by direct machining of a metal block, or of several metal blocks adhered together. Furthermore, molding techniques involving internal mold features can be employed, as will be understood by the skilled artisan. A deposition device can also be constructed using any of a number stereolithography techniques.

30 As can be seen from the example embodiment of Figures 10, 11A, and 11B, deposition device 10 can be constructed of very small size, with each output channel 12 having the width of a sheet of metal plating. For example, in one embodiment using the arrangement of Figures 10, 11A, and 11B, output channel 12 is 0.034 inches (0.86 mm) in width W. Output channels 12 for different

materials could be fabricated at different thicknesses to obtain width W ranges, preferably from 0.01 inches (0.25 mm) to 0.1 inches (2.5 mm) for a compact arrangement. The length L of output channel 12 can vary, depending on the needed uniformity and desired gas pressure. In one embodiment, output channel 5 length L is 3 inches (75 mm). The height H of output channels 12 formed from extending portions of stacked plates 42 is 0.1 inches in one embodiment.

Because gas flow can inadvertently draw ambient gases, due to low-pressure zones that are created, it may be useful to provide additional protection barrier from an inert layer. Referring to Figure 12, there is shown an envelopment 10 gas flow  $F_E$  by which an additional flow of inert gas is used on one or more sides of deposition device 10 to prevent ambient gases from contaminating the process gases.

As was particularly described with reference to Figures 4A and 4B, deposition device 10 requires movement relative to the surface of substrate 20 in 15 order to perform its deposition function. This relative movement can be obtained in a number of ways, including movement of either or both deposition device 10 and substrate 20, such as by movement of a process that provides a substrate support. Movement can be oscillating or reciprocating or could be continuous movement, depending on how many deposition cycles are needed. Rotation of a 20 substrate can also be used, particularly in a batch process, although continuous processes are preferred.

Typically, ALD requires multiple deposition cycles, building up a controlled film depth with each cycle. Using the nomenclature for types of gaseous materials given earlier, a single cycle can, for example in a simple design, 25 provide one application of first reactant gaseous material O and one application of second reactant gaseous material M.

The distance between output channels for O and M reactant gaseous materials determines the needed distance for reciprocating movement to complete each cycle. For the example deposition device 10 of Figure 9, having a nominal 30 channel width of 0.034 inches in width W for each output channel 12, reciprocating motion (along the y axis as used herein) of at least 0.20 inches would be required. For this example, an area of substrate 20 would be exposed to both first reactant gaseous material O and second reactant gaseous material M with movement over this distance. In some cases, consideration for uniformity

may require a measure of randomness to the amount of reciprocating motion in each cycle, such as to reduce edge effects or build-up along the extremes of reciprocation travel.

A deposition device 10 may have only enough output channels 12 to 5 provide a single cycle. Alternately, deposition device 10 may have an arrangement of multiple cycles, enabling it to cover a larger deposition area or enabling its reciprocating motion over a distance that allows two or more deposition cycles in one traversal of the reciprocating motion distance.

In one embodiment, a given area of the substrate is exposed to a gas flow 10 in a channel for less than 500 milliseconds, preferably less than 100 milliseconds. The relative movement of the substrate to a channel during oscillation is at a speed at least 0.1 cm/sec, and the gas flow in the channels is at least 1 cm/sec. Preferably, the temperature of the substrate during deposition is under 300°C, more preferably under 250°C.

15 For example, in one particular application, it was found that each O-M cycle formed a layer of one atomic diameter over ¼ of the treated surface. Thus, four cycles, in this case, are needed to form a uniform layer of 1 atomic diameter over the treated surface. Similarly, to form a uniform layer of 10 atomic diameters in this case, then, 40 cycles would be required.