## **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6:

H04J 4/00

A1

(11) International Publication Number:

WO 00/18052

(43) International Publication Date:

30 March 2000 (30.03.00)

(21) International Application Number:

PCT/US99/20587

(22) International Filing Date:

8 September 1999 (08.09.99)

(30) Priority Data:

09/159,734

24 September 1998 (24.09.98) US

(71) Applicant: OMNIPOINT CORPORATION [US/US]; 3 Bethesda Metro Center, Suite 400, Bethesda, MD 20814 (US).

(72) Inventor: WADE, Roy; 3885 Highview Drive, Colorado Springs, CO 80908 (US).

(74) Agent: LYON & LYON LLP; Hemminger, Steven, D., Suite 4700, 633 West Fifth Street, Los Angeles, CA 90071–2066 (US). (81) Designated States: AE, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CR, CU, CZ, DE, DK, DM, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, UA, UG, UZ, VN, YU, ZA, ZW, ARIPO patent (GH, GM, KE, LS, MW, SD, SL, SZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

#### **Published**

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

### (54) Title: MANAGEMENT OF TIME SLOT OPERATIONS FOR WIRELESS COMMUNICATION

### (57) Abstract

A user station includes a control system for managing time slot operations for a system using aspects of TDMA/TDD and FDMA/FDD, to allow the user station to communicate periodically with a base station. The control system comprises an over-the-air driver for interfacing with upper layer protocol functions, and a slot manager for interfacing with the hardware to handle slot-related functions. The slot manager maintains a list or queue of slot objects, each defining a group of one or more time slots forming a logical communication channel. The slot manager configures the hardware to process each time slot at the appropriate time within a time frame. Different slot objects may be created for voice, signalling or other data traffic, and each slot object may cause the user station to communicate with the base station in one or more time slots of the time frame. The over-the-air driver instructs the slot manager to add, modify or delete slot objects based on requests from upper layer protocol functions. The control system may include service routines for performing data transfers in response to interrupts generated by a hardware controller (such as a control ASIC). The user station hardware may include a set of direct access data channels controlled through the use of interrupts to a peripheral event controller (PEC). The user station control system may also comprise components for radio reconfiguration, ARQ processing and power control processing.

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AL            | Albania                  | ES | Spain               | LS | Lesotho               | SI   | Slovenia                 |

|---------------|--------------------------|----|---------------------|----|-----------------------|------|--------------------------|

| AM            | Armenia                  | FI | Finland             | LT | Lithuania             | SK   | Slovakia                 |

| AT            | Austria                  | FR | France              | LU | Luxembourg            | SN   | Senegal                  |

| AU            | Australia                | GA | Gabon               | LV | Latvia                | SZ   | Swaziland                |

| AZ            | Azerbaijan               | GB | United Kingdom      | MC | Monaco                | TD   | Chad                     |

| BA            | Bosnia and Herzegovina   | GE | Georgia             | MD | Republic of Moldova   | TG   | Togo                     |

| BB            | Barbados                 | GH | Ghana               | MG | Madagascar            | TJ   | Tajikistan               |

| BE            | Belgium                  | GN | Guinea              | MK | The former Yugoslav   | TM   | Turkmenistan             |

| BF            | Burkina Faso             | GR | Greece              |    | Republic of Macedonia | TR   | Turkey                   |

| BG            | Bulgaria                 | HU | Hungary             | ML | Mali                  | TT   | Trinidad and Tobago      |

| BJ            | Benin                    | IE | Ireland             | MN | Mongolia              | UA   | Ukraine                  |

| BR            | Brazil                   | IL | Israel              | MR | Mauritania            | · UG | Uganda                   |

| BY            | Belarus                  | IS | Iceland             | MW | Malawi                | US   | United States of America |

| CA            | Canada                   | IT | Italy               | MX | Mexico                | UZ   | Uzbekistan               |

| CF            | Central African Republic | JP | Japan               | NE | Niger                 | VN   | Viet Nam                 |

| CG            | Congo                    | KE | Kenya               | NL | Netherlands           | YU   | Yugoslavia               |

| CH            | Switzerland              | KG | Kyrgyzstan          | NO | Norway                | zw   | Zimbabwe                 |

| CI            | Côte d'Ivoire            | KP | Democratic People's | NZ | New Zealand           |      |                          |

| CM            | Cameroon                 |    | Republic of Korea   | PL | Poland                |      |                          |

| CN            | China                    | KR | Republic of Korea   | PT | Portugal              |      |                          |

| CU            | Cuba                     | KZ | Kazakstan           | RO | Romania               |      |                          |

| $\mathbf{CZ}$ | Czech Republic           | LC | Saint Lucia         | RU | Russian Federation    |      |                          |

| DE            | Germany                  | LI | Liechtenstein       | SD | Sudan                 |      |                          |

| DK            | Denmark                  | LK | Sri Lanka           | SE | Sweden                |      |                          |

| EE            | Estonia                  | LR | Liberia             | SG | Singapore             |      |                          |

|               |                          |    |                     |    |                       |      |                          |

PCT/US99/20587

1

### **DESCRIPTION**

# Management Of Time Slot Operations For Wireless Communication

### Background Of The Invention

### 5 1. Field Of The Invention

The field of the present invention relates to methods and apparatus for managing and controlling time slot operations within a system for multiple access communication.

### 2. Background

10

15

20

25

30

A variety of techniques are known for allowing multiple users to communicate with one or more fixed stations (i.e., base stations) by making use of shared communication resources. Examples of multiple access communication systems include various types of cellular telephone networks and local wireless communication systems, such as wireless private branch exchange (PBX) networks. In such multiple access communication systems, transmissions from different sources may be distinguished in a variety of manners, such as on the basis of different frequencies, time slots, and/or codes, for example.

As referred to herein, a communication system in which transmissions are distinguished according to the transmission frequency may be referred to as a frequency division multiple access (FDMA) communication system. A communication system in which a forward link transmission over one frequency is paired with a reverse link transmission over a different frequency may be referred to as a frequency division duplex (FDD) communication system.

A communication system in which transmissions are distinguished according to the relative timing of the transmission (i.e., by use of time slots) may be referred to as a time division multiple access (TDMA) communication system. A communication system in which a forward link transmission during one time slot (or time segment) is paired with a reverse link transmission occurring during a different time slot (or time segment) may be referred to as a time division duplex (TDD) communication system.

A communication system in which transmissions are distinguished according to which code is used to encode the transmission may be referred to as a code division multiple access (CDMA) communication system. In a CDMA communication system, the data to be transmitted is generally encoded in some fashion, in a manner which causes the signal to be "spread" over a broader frequency range and also typically causes the signal

15

20

25

30

35

power to decrease as the frequency bandwidth is spread. At the receiver, the signal is decoded, which causes it to be "despread" and allows the original data to be recovered. Distinct codes can be used to distinguish transmissions, thereby allowing multiple simultaneous communication, albeit over a broader frequency band and generally at a lower power level than "narrowband" FDMA or TDMA systems. Different users may thereby transmit simultaneously over the same frequency without necessarily interfering with one another.

Various "hybrid" communication systems incorporating aspects of more than one multiple access communication technique have been developed or proposed. For example, a GSM system may be viewed as a "hybrid" communication system utilizing aspects of both FDD and TDMA.

In communication systems employing aspects of TDMA or TDD, including "hybrid" type systems, management of slot-related operations and forward and reverse links by a user station can be challenging, due in part to timing and synchronization constraints. For example, the user station may need to precisely control its reception frame window and its transmission frame window in relation to the time frame established by the base station. The user station may also need to process received data (for, e.g., decoding or correcting/processing) while at the same time, or immediately thereafter, having to transmit data in return to the base station.

In addition, the bursty nature of packetized TDMA or TDD communications may lead to particular difficulties at the user station in handling data. For example, bearer or voice data may need to be broken into a number of data packets to be transmitted over several or possibly many time frames, depending on the amount of data to be transmitted, and similarly may need to be reconstructed from data packets received from the base station over several or possibly many time frames. The data may also need to be processed by encoding or decoding algorithms (e.g., vocoding) after being received or before being transmitted, as well as processed for errors, therefore adding to the complexity of control operations at the user station.

In addition to various timing and environmental constraints, a user station may need to have provision for handling different message types, such as signalling (i.e., control) traffic messages as well as normal bearer traffic messages. For example, the user station may need the ability to exchange signalling traffic messages in order to establish communication or handoff to another base station. The user station hardware interface may need to respond rapidly and efficiently to instructions reveled through signalling messages from the base station. Also, it may be desirable to support advanced protocol features, such as super-rate or sub-rate communication, at the user station.

15

20

25

30

35

In communication systems employing aspects of FDMA or FDD (in addition to TDMA or TDD), further difficulties may be encountered. For example, the radio at the user station may need to be reconfigured periodically to switch between receive and transmit frequencies. The radio reconfiguration may need to occur simultaneous with processing of data just received or about to be transmitted. The user station may also need to control the radio as to allow monitoring of neighboring base stations and handover when needed.

It would therefore be advantageous to provide apparatus and methods for managing time slot operations within a communication system having aspects of TDMA or TDD. It would further be advantageous to provide apparatus and methods which can handle multiple simultaneous or near simultaneous tasks necessary to manage and communicate in time slots within a multiple access communication system. It would further be advantageous to provide a user station capable of processing data received from a base station while also being capable of preparing to transmit information to the base station, and doing so efficiently with a minimal chance of losing or missing data. It would further be advantageous to provide a user station having the ability to dynamically reconfigure its radio to transmit and/or receive on different frequencies (and/or using different codes) between time slots, so as to perform FDMA or FDD (and/or CDMA) communication. It would, in addition, be advantageous to provide such a user station having advanced protocol capabilities, and having, for example, the ability to transmit and/or receive at super-rates or sub-rates. It would also be advantageous to provide a user station control system capable of managing time slots and peripheral activities associated with communication in a TDMA or TDD environment, in addition to dynamic radio reconfiguration to support different communication environments and protocols (e.g., FDD or FDMA) and to support handover between base stations.

### **Summary Of The Invention**

The invention provides in one aspect methods and apparatus for managing time slot operations in a wireless communication system, and especially suited for use in a communication system employing aspects of FDMA or FDD as well as TDMA or TDD.

In one embodiment, a user station control system comprises an event-driven architecture utilizing interrupts to communicate with and/or to initiate action by a microcontroller. The microcontroller responds to such interrupts by transferring data to or from various hardware components, such as transmit and receive frame memory buffers, a digital signal processor (DSP) and vocoder, and a radio channel. In one embodiment, the microcontroller responds to a variety of interrupts, each of which requests the transfer of a

10

15

20

25

30

35

4

discrete amount (e.g., a single byte) of data. Dedicated counters keep track of the total number of bytes to transfer, and interrupt routines activate the microcontroller to enact each data transfer, or to inform the microcontroller that a data transfer has occurred, until the appropriate counter reaches a predefined count value or until otherwise disabled.

In another embodiment, a user station control system comprises a variety of software components for managing and controlling time slot operations. The user station control system may comprise a slot manager for setting up time slots, and for maintaining active time slots in a list or queue format. The user station control system may further comprise an over-the-air (OTA) driver for interfacing with various hardware components (e.g., a DSP/vocoder) and also for instructing the slot manager when to add, update or delete active time slots from the time slot list or queue. The slot manager and OTA driver may communicate via slot message queues. The user station control system also preferably comprises a variety of direct memory access data transfer tasks, which allow access to hardware registers and transference of data between various hardware sources and destinations. In addition, the user station control system may comprise components for radio reconfiguration, ARQ processing and power control processing.

In another embodiment, a microcontroller is programmed in accordance with algorithms for controlling and managing time slot operations in a user station. A control ASIC interfaces with the microcontroller, and provides an interface to various hardware components including, for example, a program memory, random-access memory, DSP/vocoder, linearizer and radio. The microcontroller may comprise a peripheral event controller which responds to interrupts received from the control ASIC. The microcontroller may instruct the control ASIC as to a predefined amount of data (e.g., number of bytes) to be transferred between hardware components, and the control ASIC may then, for each byte to be transferred, interrupt the peripheral event controller of the microcontroller to initiate a direct transfer of the data.

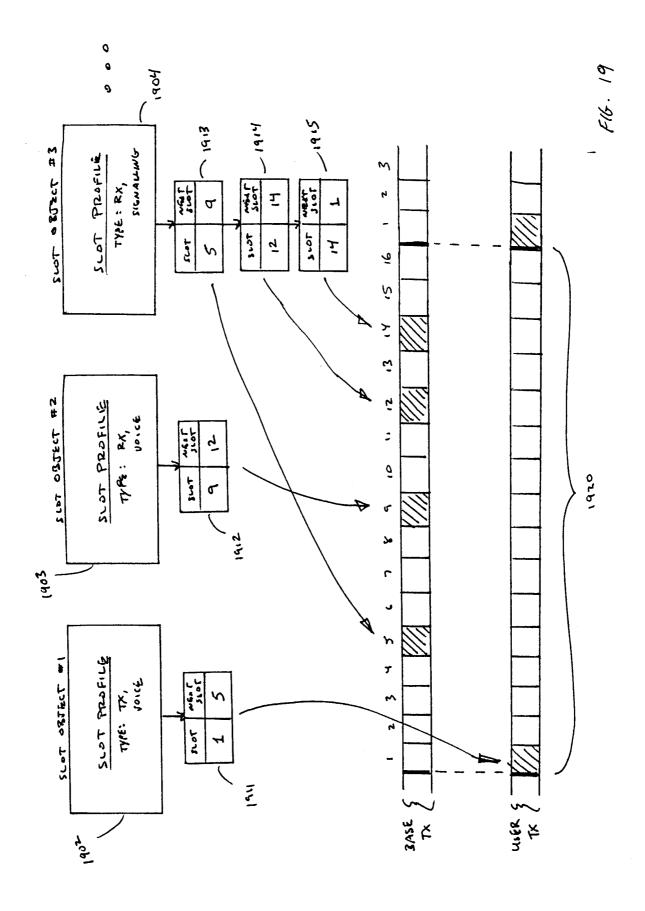

In another embodiment, a user station control system is provided to manage time slot operations, wherein a user station is capable of communicating with more than one base station at the same time. The user station control system preferably maintains, in the form of a slot object, a discrete data profile for each time slot or related group of time slots, and dynamically re-configures the user station radio (including its operative frequency, if applicable) to transmit or receive according to the data profile for the current time slot. When processing for the current time slot is finished, the control and/or configuration parameters for the next time slot are loaded. Each time slot preferably includes within its data profile an indicator (i.e., pointer) identifying the next active time slot. A slot object may be added for each active communication channel (whether

10

15

20

25

30

signalling, voice or other data), and may be deleted when the communication channel is closed down. In one aspect, the user station control system provides a capability for the user station to handoff from one base station to another, or monitor nearby base stations, by providing the ability for the user station to communicate contemporaneously (in different time slots of the same time frame) with different base stations.

In another embodiment, a user station control system for managing time slot operations within a TDMA or TDD communication system (and/or FDD or FDMA communication system) provides GSM functionality by interfacing with a subscriber identity module (SIM) card located within the user station. The user station control system may comprise a control ASIC which provides an interface between a microcontroller and the SIM card.

Further embodiments, modifications, variations and enhancements of the invention are also disclosed herein.

### **Brief Description Of The Drawings**

Fig. 1 is a diagram of a cellular system.

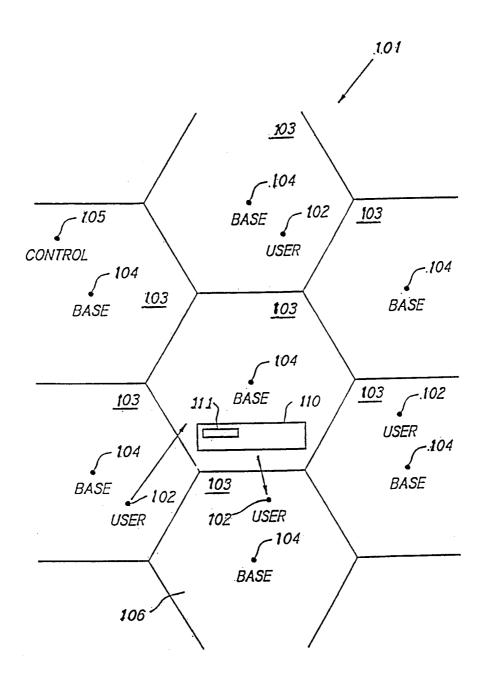

Fig. 2 is an abstract diagram of components of a preferred software system and their associated interfaces, in accordance with various aspects of the present invention.

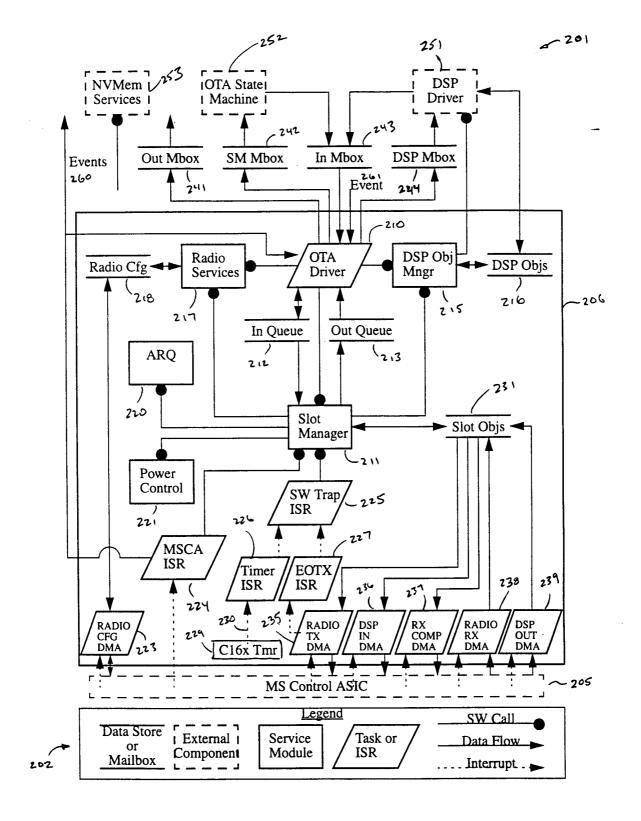

Fig. 3 is a block diagram of a user station or handset in which the invention may be employed.

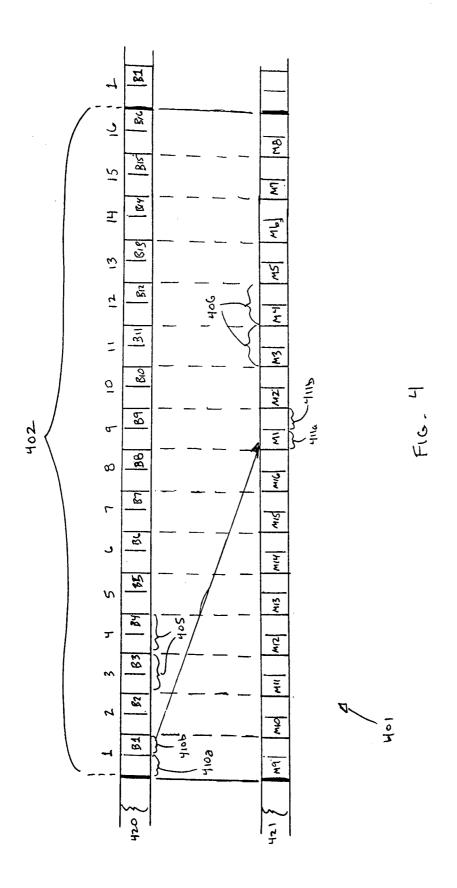

Fig. 4 is a diagram of a frame structure for FDD communication between a base station and multiple user stations.

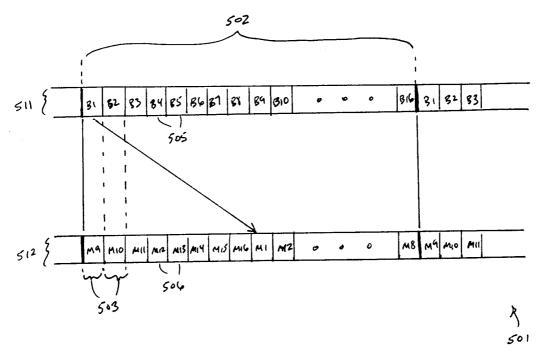

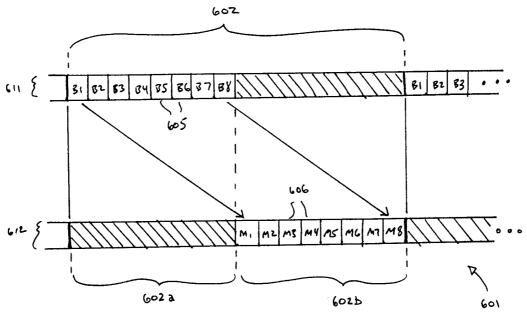

Figs. 5 and 6 are diagrams of alternative frame structures for FDD communication between a base station and multiple user stations.

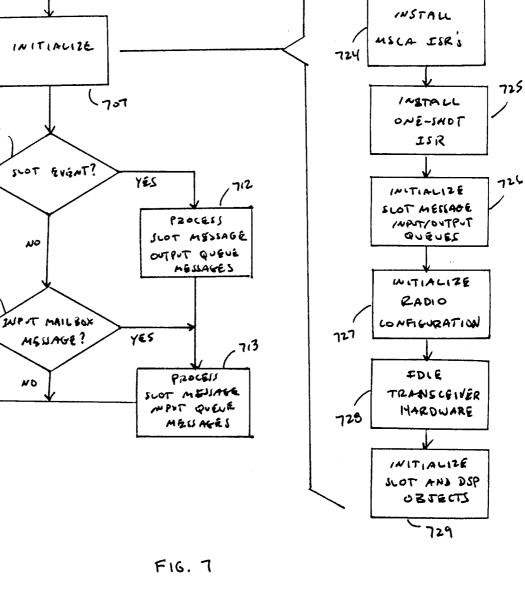

Fig. 7 is a diagram of a process flow for controlling a user station.

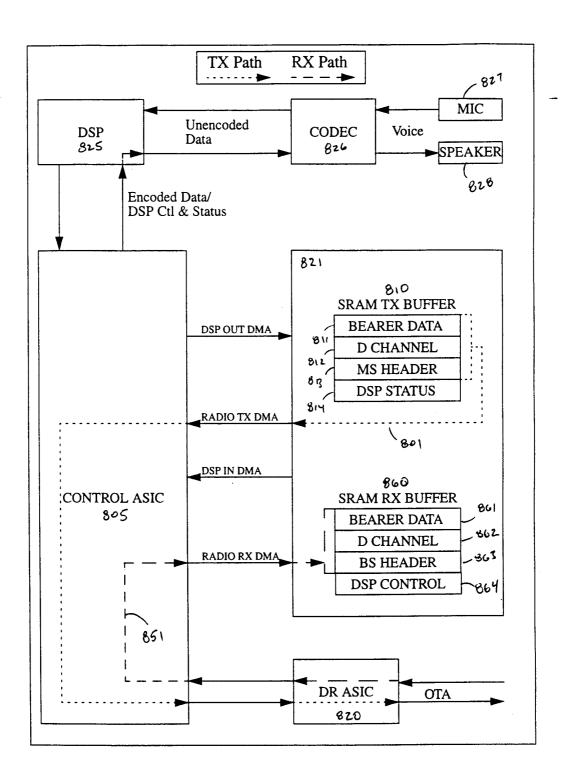

Fig. 8 is a data path diagram illustrating the flow of signalling traffic in accordance with a preferred embodiment of a user station.

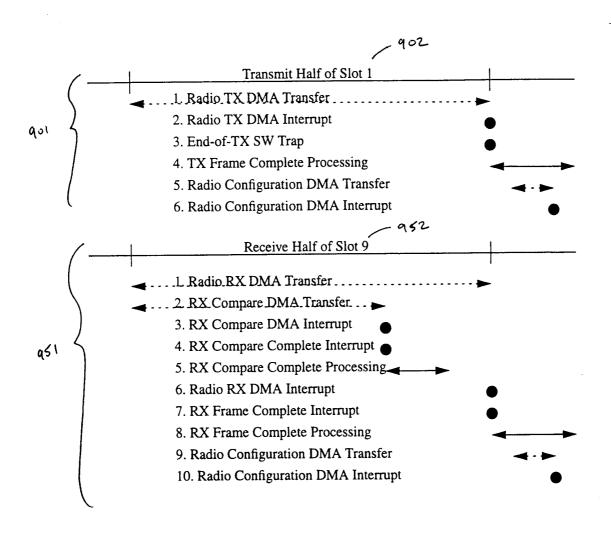

Fig. 9 is a timing diagram illustrating timing and sequencing for signalling traffic.

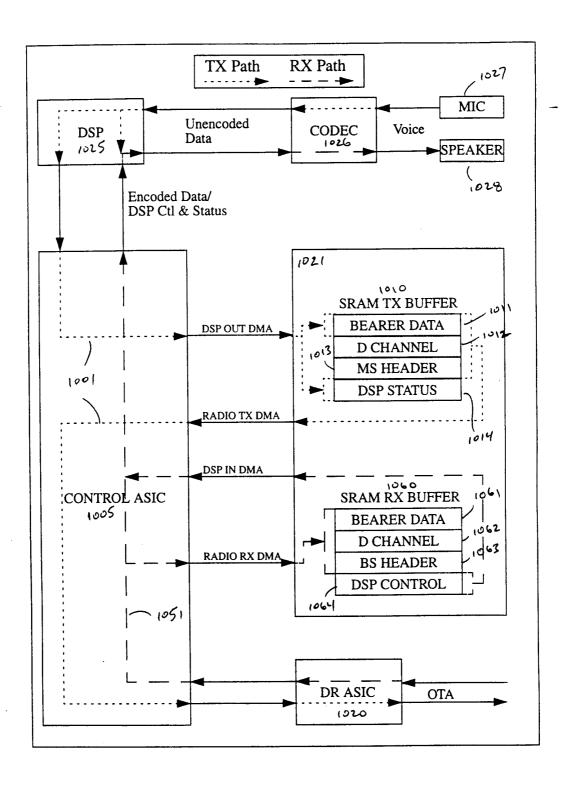

Fig. 10 is a data path diagram illustrating the flow of voice or bearer traffic in accordance with a preferred embodiment of a user station.

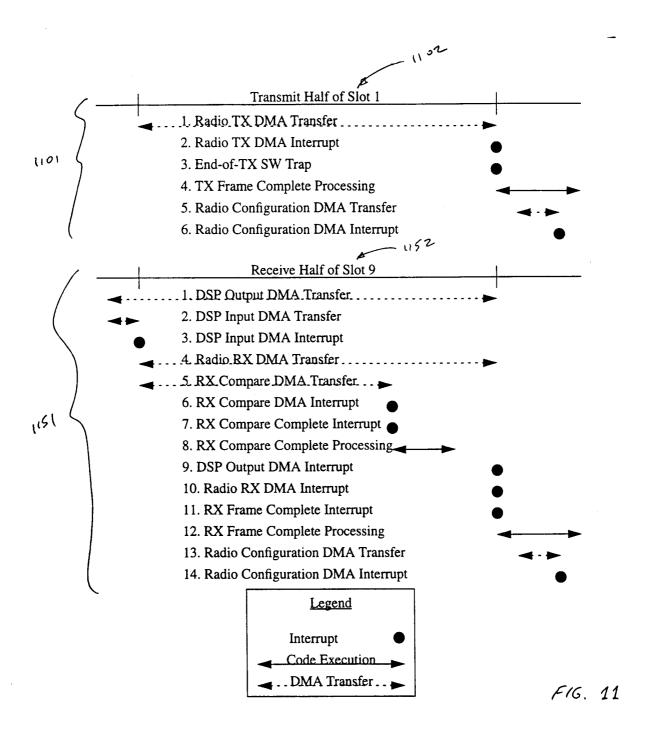

Fig. 11 is a timing diagram illustrating timing and sequencing for voice or bearer traffic.

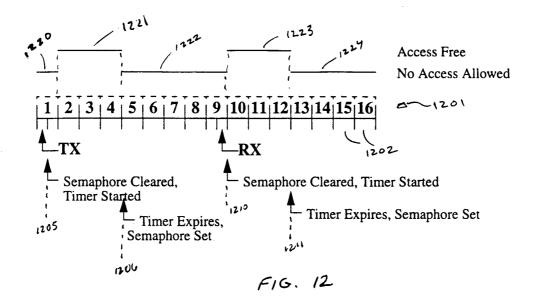

Fig. 12 is a timing diagram illustrating slot object access control.

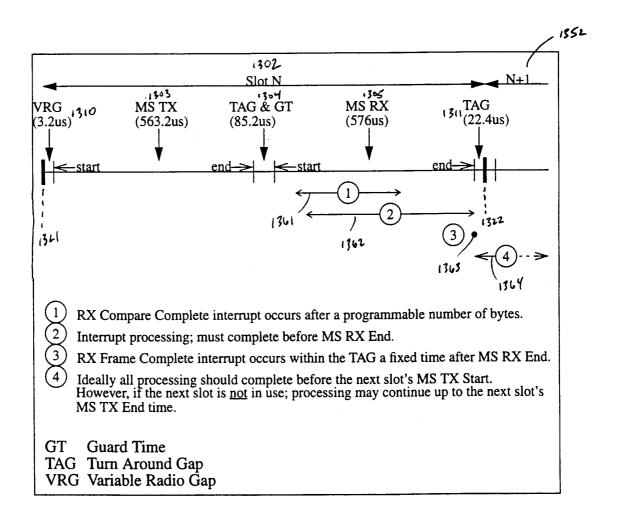

Fig. 13 is a timing diagram depicting a slot interrupt sequence.

Fig. 14 is a table diagram for automatic repeat request (ARQ) states.

10

15

20

25

30

35

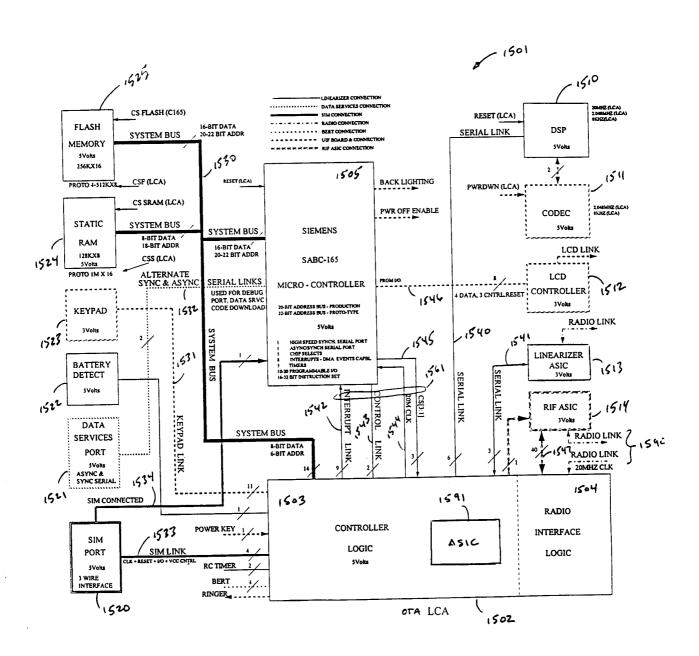

Fig. 15 is a top-level system diagram of a preferred control section for a user station in accordance with certain aspects of the invention as described herein.

Fig. 16 is a diagram of a preferred system memory map.

Fig. 17 is a diagram of a memory map for volatile memory space.

Fig. 18 is a diagram of a transmit/receive frame memory structure.

Fig. 19 is an example illustrating a relationship between slot objects and time slots.

### **Detailed Description Of Preferred Embodiments**

Figure 1 is a diagram of a cellular communication system 101 having base stations and user stations. In Fig. 1, a communication system 101 for communication among a plurality of user stations 102 includes a plurality of cells 103, each with a base station 104, typically located at or near the center of the cell 103. Each station (both the base stations 104 and the user stations 102) may generally comprise a receiver and a transmitter. The user stations 102 and base stations 104 preferably communicate using frequency division duplex (FDD) techniques as further described herein, in which base stations 104 communicate over one frequency band and user stations 102 communicate over another frequency band. Communication is also preferably conducted such that different user stations 102 transmit at different times (i.e., during different time slots), as further described herein.

As further shown in Fig. 1, the communication system 101 may also comprise a base station controller 105 which connects to the base stations 104 in a particular geographic region. The base station controller 105 aggregates inputs from multiple base stations 104 and relays information from the base stations 104 to a mobile switching center (MSC) (not shown) and ultimately to a public switched telephone network (PSTN, or "network") (not shown). The base station controller 105 also relays information from the network to the individual base stations 104. The base station controller 105 may, if necessary, perform conversion of signalling messages relating to, e.g., mobility management and call control, to make the signalling messages compatible with the communication protocol used by the base stations 104.

In a preferred embodiment, a wireless communication system includes a frame structure according to which transmissions to and from user stations are distinguished based on time (i.e., TDMA or TDD), and according to which base station transmissions are transmitted on a different frequency band than user station transmissions (i.e., FDMA or FDD). An exemplary frame structure which may be utilized in such a wireless communication system is shown in Fig. 4, and described below. Examples of alternative frame structures are shown in Figs. 5 and 6, and are described hereinafter. However, other

frame structures besides those shown in Figs. 4, 5 and 6 can be used in conjunction with the inventive features described herein.

In the frame structure 401 shown in Fig. 4, a repeating time frame 402 comprises a plurality of time slots 403, each of the time slots 403 having a first time segment 417 and a second time segment 418. The time slots 403 can be defined on multiple frequency bands 411, 412, in order to effectuate FDD or FDMA communication. Accordingly, the time slots 403 can be broken down into base transmit time slots 405 with respect to a base transmission frequency band 411, and user transmit time slots 406 with respect to a user transmission frequency band 412. Each of the base transmit time slots 405 is preferably paired with a corresponding one of the user transmit time slots 406, with such a pair defining a duplex channel for communication (up to N total duplex channels). The N duplex channels may be assigned, on demand, to user stations 102.

In a preferred embodiment, the number of time slots 403 in a time frame 402 is sixteen, and the number of base transmit time slots 405 and user transmit time slots 406 is likewise sixteen. Also in a preferred embodiment, the pairing between base transmit time slots 405 and user transmit time slots 406 is made such that each user transmit time slot 406 is paired with a base transmit time slot 405 that occurs eight time slots later (i.e., one-half of time frame 402). The user stations 102 preferably transmit in the first time segment 417 of the user transmit time slots 406, while the base station 104 preferably transmits in the second time segment 418 of the base transmit time slots 405. In other words, during the first time segment 417 of a user time slot 406, a user station 102 to which the duplex channel is assigned transmits a user station message to the base station 104, and during the second time segment 418 of the corresponding base transmit time slot 405, the base station 104 transmits a base station message to the user station 102 to which the duplex channel is assigned.

The frame structure 401 is designed in one regard to allow relatively convenient adaptation of TDD equipment to perform FDD functionality. Consequently, the base station messages and user station messages are separated in time (i.e., user stations 102 transmit during the first time segments 417 of time slots 403 while the base station 104 transmits in the second time segments 418 of time slots 403) even though time separation would not be necessary to avoid interference because the base station messages and user station messages are also separated by frequency. The frame structure 401 is advantageous when converting a TDD base station using a single frequency band for both base and user transmissions to a base station employing FDD, because the adapted base station can maintain the same relative timing between user transmit time segments and base transmit time segments in each time slot while having only to switch frequencies

PCT/US99/20587

5

10

15

20

25

30

35

between the first time segment 417 and the second time segment 418 in each time slot 403. Consequently, for the frame structure 401 of Fig. 4, the base station 104 need not have the capability of transmitting and receiving simultaneously over two different frequency bands, and does not need, for example, a diplexer.

While preferred embodiments of the invention are described below in relation to the frame structure 401 shown in Fig. 4, alternative frame structures are introduced here which could also be used in conjunction with the inventive features and processes disclosed herein. In particular, alternative frame structures are illustrated in Figs. 5 and 6. For the frame structure 501 shown in Fig. 5, a repeating time frame 502 comprises a plurality of time slots 503, which may be broken down, similar to Fig. 4, as base transmit time slots 505 with respect to a base transmission frequency band 511 and user transmit time slots 506 with respect to a user transmission frequency band 512. Each of the base transmit time slots 505 is preferably paired with a corresponding one of the user transmit time slots 506, with such a pair defining a duplex channel for communication (up to N total duplex channels). However, unlike the frame structure of Fig. 4, the time slots 503 are not divided into a first time segment and second time segment. Rather, during each user transmit time slot 506, the user station 102 to which the duplex channel is assigned transmits a user station message to the base station 104 over the user transmission frequency band 512, and during each base transmit time slot 505, the base station 104 transmits a base transmit message to the user station 102 to which the duplex channel is assigned over the base transmission frequency band 511. The base station 104 thereby carries out multiple access communication with a plurality of user stations 102. Generally, the base station 104 communicates with up to N user stations 102 in the N time slots 503 of time frame 502, unless more than one of the time slots (user time slots 506 or base time slots 505, or both) are aggregated to a single user station 102, or else more than one user station 102 is assigned to share a single time slot 503 by communicating during alternate time frames 502. In one aspect, the frame structure 501 is advantageous in that it can support twice as many user stations 102 as the frame structure 401, all other things being equal, but requires that the base station 104 be able to transmit and receive simultaneously over two different frequency bands 511, 512, unlike the frame structure 401 of Fig. 4.

The alternative frame structure 602 shown in Fig. 6 is, like that of Fig. 4, one in which the base station 104 need not be able to transmit and receive simultaneously over two different frequency bands. For the frame structure 601 shown in Fig. 6, a repeating time frame 602 comprises a plurality of base transmit time slots 605 and a plurality of user transmit time slots 606. Each of the base transmit time slots 605 is preferably paired with a corresponding one of the user transmit time slots 606, with such a pair defining a duplex

channel for communication (up to N total duplex channels). During the first half 602a of the time frame 602, the base station 104 transmits over a base transmission frequency band 611 in each of the base transmit time slot 605 in succession. With respect to the user transmission frequency band 612, the first half 602a of the time frame 602 is "dark" or unused. During the second half 602b of the time frame 602, the user stations 102 transmit in succession over the user transmission frequency band 612. With regard to the base transmission frequency band 611, the second half 602b of the time frame 602 is "dark" or unused. Preferably, the base transmit time slots 605 are paired with user transmit time slots 606 in the same relative sequential order, so that the first base transmit time slot 605 is paired with the first user transmit time slot 606, the second base transmit time slot 605 is paired with the second user transmit time slot 606, and so on. In such a preferred embodiment, each base transmit time slot 605 is paired with a user transmit time slot 606 separated from it by one-half of the time frame 602.

10

15

20

25

30

35

In the embodiments disclosed herein, communication may be established between a base station 104 and a user station 102 by any suitable means, including the methods and techniques described in, for example, U.S. Patent Application Ser. No. 08/284,053 filed August 30, 1994, assigned to the assignee of the present invention, and hereby incorporated by reference as if set forth fully herein. According to one technique described more fully in Ser. No. 08/284,053, a base station 104 transmits a "general poll" message in each time slot which is available for communication. A user station 102 desiring to establish communication with the base station 104 responds to one of the general poll messages by transmitting a general response message to the base station 104, preferably in the same time slot (or the user transmit time slot corresponding to the base transmit time slot) in which the general poll message was transmitted. As part of the general response message, the user station 102 transmits a user station identifier. Upon receipt of the general response message, the base station 104 transmits a specific poll message to the user station 102, preferably in the same time slot as the general poll message was transmitted. Upon receipt of the specific poll message, the user station 102 may transmit a specific response message, or else may commence communication in the appropriate time slot.

In one embodiment, a user station 102 may handoff communication to a base station 104 by first establishing communication with a new base station 104, requesting a circuit switch to the new base station 104, and then relinquishing the original link. The user station 102 may monitor the quality of signals received from other local base stations 104 and, when it appears that a handoff is desirable, establish a communication link with a new base station 104 by responding to a general poll message in an available time slot at

the new base station 104. Once the new communication link is established, the user station 104 instructs the old base station 104 to switch over the circuits for the call, and then terminates the communication link with the old base station 104. Until the old link is relinquished, the user station 102 maintains two separate links in two separate time slots, and potentially on different frequencies and/or with different code sets.

Certain features of the invention are conveniently described with reference to a preferred user station 301 (e.g., a handset) as shown in Fig. 3. As shown in Fig. 3, the user station 301 includes a radio transceiver 305 (comprising a transmitter 315 and a receiver 316), an antenna 306 connected to the radio transceiver 305, and an over-the-air controller 310 also connected to the radio transceiver 305. The over-the-air controller 310 is connected to a memory buffer 311. The over-the-air controller 310 manages the retrieval of information from the memory buffer 311 by the radio transceiver 305 for transmission to the base station 104 with which the user station 301 communicates, and the storage of information into the memory buffer 311 by the radio transceiver 305 when such information is received from the base station 104.

The memory buffer 311 is connected to an analog-to-digital (A/D) converter 331 and a digital-to-analog (D/A) converter 332. Both the A/D converter 331 and the D/A converter 332 are connected to a vocoder 335, which is connected to a speaker/microphone 336. Information received from the base station 104 and stored in the memory buffer 311 is converted from a digital format to an analog format by D/A converter 332. The vocoder 335 then processes the analog formatted information and sends a signal to speaker/microphone 336 to generate audible voice or other sounds to the user/listener. The speaker/microphone 336 also picks up audible voice or other sounds from the user, and relays an analog data signal to the vocoder 335. The vocoder 335 processes the analog data signal, and sends the processed analog data signal to A/D converter 331 for conversion to a digital format. The digital formatted data is then stored in the memory buffer 311, and made available for transmission to the base station 104 in the appropriate time slot.

Figure 3 also shows further details of the over-the-air controller 310. As shown therein, the over-the-air controller 310 comprises a clock 320 connected to a time frame counter 321 and a time slot counter 322. The time frame counter 321 and time slot counter 322 are connected to control logic 323, which uses outputs from the time frame counter 321 and time slot counter 322 to format messages for over-the-air communication. Under control of the over-the-air controller 310, the radio transceiver 305 stores and removes information from the memory buffer 311. The radio transceiver 305 further comprises a transmit/receive (T/R) switch 317 to allow selection between a transmission

10

15

mode and a reception mode. The control logic 323 of the over-the-air controller 310 controls the T/R switch 317, and thereby selects between the transmission mode and reception mode based, for example, upon the current portion of a time frame (such as time frame 401 described elsewhere herein). When in a transmission mode, the over-the-air controller 310 selects the user transmit frequency (e.g., user transmission frequency band 412), and when in a reception mode the over-the-air controller 310 selects the base transmit frequency (e.g., base transmission frequency band 411).

In a preferred embodiment, the control logic 323 comprises a microcontroller or microprocessor 327 (such as a Siemens C163/C165 processor) and a control ASIC 328 (referred to herein occasionally as the "MSCA"). The MSCA 328 may provide an interface between the microprocessor 327 and many of the other hardware components in the user station 301, including the radio transceiver 305 and the speaker/microphone 336, as well as a coder/decoder (CODEC) and digital signal processing circuitry. The MSCA 328 may comprise a variety of general and special purpose registers in order to facilitate performance of its various functions. Examples of such registers may include the following:

- Unencoded Receive Data Register

- Encoded Transmit Data Register

- Slot Map Pointer Register

- Test Register

- General Status Register

- Interrupt Control Register

- Compare Input Register

- Compare Count Register

- DSP Data/Control Bytes Register

- DSP Source Register

- Receive Source Register

- Transmit Destination Register

- Sleep Control Register

- Receive Status Register

- RSSI Byte I & 2 Register

- RC Count Register

- Protocol Control Register

- Radio Configuration/Slot Map Data Register

- Radio Configuration Code Register

- General Purpose Register (write)

12

### General Status Register

5

10

15

20

25

30

35

In a preferred embodiment, the microcontroller comprises a peripheral event controller (PEC), which receives occasional interrupts from the MSCA 328 for data transfer or similar tasks. A radio transceiver control process preferably provides coordinated updates of all registers of the MSCA 328 and signals that are involved in over-the-air or slot-dependent operations.

Further details of what may generally be termed a "control section" 1501 of a user station or handset in accordance with a preferred embodiment are shown in Fig. 15. As shown in the embodiment illustrated in Fig. 15, the control section 1501 comprises an over-the-air line card assembly (OTA LCA) 1502 comprising controller logic 1503 and radio interface logic 1504. The controller logic 1503 may comprise a control ASIC 1591 (similar in general function to control ASIC 328 of Fig. 3). The OTA LCA 1502 is connected to a microcontroller 1505 (e.g., a Siemens SABC-165 microcontroller). In a preferred embodiment, the microcontroller 1505 comprises, among other things, a microprocessor and one or more serial ports (at least one of which is a high speed synchronous serial port). The OTA LCA 1502 and microcontroller 1505 are connected by a set of control lines 1561, including an interrupt link 1542, a control link 1543, a clock signal line 1544, and a set of chip select (CS) lines 1545. In one aspect, the OTA LCA 1502 provides a control interface between the radio transceiver 305 (see Fig. 3) and the microcontroller 1505. The microcontroller 1505 can move data to and from the OTA LCA 1502, read the status of the OCA LCA 1502, and/or issue commands to the OTA LCA 1502 instructing it to perform certain predefined actions.

In addition to the control lines 1561, a system bus 1530 connects the OTA LCA 1502 to the microcontroller 1505. The system bus is also connected to a static RAM (SRAM) 1524 and a flash memory 1525. The SRAM 1524 may, for example, be 128k in size (8-bit words), and the flash memory 1525 may, for example, be 256k in size (16-bit words).

As further shown in Fig. 15, the controller logic 1503 of the OTA LCA 1502 is connected to a keypad 1523, a battery monitor 1522, a digital signal processor/vocoder (DSP/vocoder) 1510 and a linearizer ASIC 1513. Both the controller logic 1503 and the radio interface logic 1504 are connected to a radio interface ASIC 1514, and thereby to the radio transceiver (such as radio transceiver 305 shown in Fig. 3). The controller logic 1503 of the OTA LCA 1502 is also preferably connected via a SIM link 1533 to a SIM port 1520, which is coupled to a subscriber identity module (SIM) card (not shown). In a preferred embodiment, the SIM card is utilized to perform a number of GSM-related and user environment functions. Examples of such include provision of system security and

13

storage of subscriber-specific information, including such things as subscriber authentication information and subscriber-specific data. The SIM port 1520 is also connected over a status signal line 1534 to the microcontroller 1505.

The microcontroller 1505 is additionally connected to a liquid crystal display (LCD) controller 1512, which acts as the interface between the microcontroller 1505 and a visual display (not shown). The microcontroller 1505 is further connected to a data services port 1521, which can be used for downloading software, or testing and debugging. The data services port 1521 may comprise an asynchronous/synchronous serial interface port operable in two different modes, and which may be alternately connected to an RS232 port for code download, or directly to the asynchronous USART port of the microcontroller 1505.

5

10

15

20

25

30

35

Figure 16 depicts a system memory map associated with the control section 1501 shown in Fig. 15. As illustrated in Fig. 16, the system memory 1601 is divided into an imaged memory portion 1602 and a non-imaged memory portion 1603. The entirety of the imaged memory portion 1602 may be contained within the same segment of the system memory 1601 (e.g., segment 0). In the embodiment shown in Fig. 16, the imaged memory portion 1602 comprises one or more flash memory sections 1611, 1612 and 1613 (associated with the flash memory 1525 shown in Fig. 15), an SRAM section 1614 (associated with SRAM 1524 shown in Fig. 15), an internal RAM section 1627 (associated with a random-access memory or cache internal to the microcontroller 1505 shown in Fig. 15), and a peripheral/LCA register section 1616 (associated with the OTA LCA 1502 shown in Fig. 15 and various peripheral devices), as well as various unused sections 1615, if any. The "boot up" code for the microcontroller 1505 may be located in the first (i.e., lowest) flash memory section 1611. In addition, memory needed in certain direct memory access (DMA) operations is preferably imaged into segment 0 according to the above structure. The imaged memory portion 1603 in the embodiment shown in Fig. 16 comprises a flash memory section 1618, an SRAM section 1619, a prototype SRAM section 1620 and a prototype flash memory section 1621. The prototype SRAM section 1620 and prototype flash memory section 1621 are intended to assist in code development, and may require the use of additional chip select signal lines.

Figure 17 is a diagram further detailing the SRAM memory map 1701. As shown in Fig. 17, the SRAM is divided into a plurality of general software regions 1702, 1709 and 1710, a base/frequency map 1703, and a plurality of various buffers including a command buffer 1704, SIM buffer 1705, receive buffer 1706, transmit buffer 1707, and linearizer buffer 1708. The transmit buffer 1707 and receive buffer 1706 are generally utilized by the radio transceiver 305 (see Fig. 3), the linearizer buffer 1708 is generally

14

utilized by the linearizer ASIC 1513, and the SIM buffer is generally utilized by the SIM card (connected via SIM port 1520).

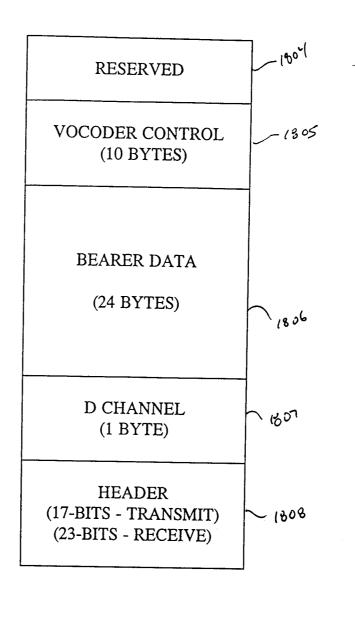

Data may be stored in the SRAM transmit buffer 1707 or receive buffer 1706 according to the format depicted in Fig. 18. According to that data format, a data message storage block 1801 comprises a header field 1808, a D-channel field 1807, a bearer data field 1806, and a vocoder control field 1805, and may also comprise a reserved portion 1804. In a preferred embodiment, the header field 1808 comprises 17 bits (for a message to be transmitted) or 23 bits (for a received message) of information, the D-channel field 1807 comprises one byte of information, the bearer data field 1806 comprises 24 bytes of information, and the vocoder control field 1805 comprises ten bytes of information.

5

10

15

20

25

30

35

In one aspect, the control section 1501 provides an interrupt-driven architecture for controlling communication transactions. Events which occur external to the microcontroller 1505 are known as peripheral events, and may cause interrupts. These interrupts are typically generated by the OTA LCA 1502 and coupled to the microcontroller 1505 across the interrupt link 1542. The microcontroller 1505 preferably includes internal circuitry, specifically a peripheral event controller (PEC) for handling such interrupts. The interrupts caused by peripheral events may cause the peripheral event controller to initiate data moves. Specifically, the peripheral event controller may respond to an interrupt by performing a DMA-type byte transfer over the system bus 1530. Different applications may require more than one byte of data. In one embodiment, a separate interrupt is used for each byte of data to be transferred (e.g., 20 bytes of data requires 20 individual interrupt requests). The number of data transfers needed for a particular application (and hence the number of interrupts) is preferably known in advance by the software and is based on the type of interrupt. After the required number of bytes have been moved, the microcontroller 1505 vectors to the appropriate interrupt service routine.

In addition to PEC interrupts, standard interrupts may also be generated from other hardware or software sources. The priority level of PEC interrupts and standard interrupts may be set by the software. The OTA LCA 1502 may include an interrupt state machine for handling event signals and generating interrupts as necessary. If the microcontroller 1505 is asleep or in a power down mode when an interrupt occurs, the interrupt state machine may instruct the clock circuit (for a sleep or power down mode) and/or reset circuit (for a power down mode) to revive the microcontroller 1505. Once the interrupt state machine sees a response from the reset and/or clock circuit indicating that the microcontroller 1505 is fully operational, the interrupt state machine applies the interrupt to the microcontroller 1505. At such a time, the interrupt state machine will present all the

30

35

interrupts that have been thus far requested. For example, if an initial PEC interrupt request originates from a SIM receive process while the microcontroller 1505 was asleep or in power down, and during the time that the microcontroller 1505 is being revived another PEC interrupt request is received from a different source, both interrupt requests are presented to the microcontroller 1505 at the same time. As each interrupt request is serviced, the request is cleared. Only when all interrupt requests presented to the microcontroller 1505 have been serviced is the state machine able to process a new request.

In one embodiment, the types of peripheral event interrupts are given by Table 1-1 below.

Table 1-1

**INTERRUPT SOURCE** DESTINATION **SRAM Transmit Buffer** Transmitter 15 2 Receiver SRAM Receive Buffer 3 **DSP** Encoded Data SRAM Transmit Buffer 4 SRAM SIM Buffer / SIM SIM Transmitter Receiver 5 Linearizer SRAM Buffer Linearizer Data/Control 20 Linearizer Data/Control Linearizer SRAM Buffer 6 SRAM Command Buffer Command Compare 7 SRAM Receive Buffer Receive DSP Data/Control 8 FLASH Radio Config. / Slot Map Data 25 9 **OTA LCA Error** General Status

The peripheral event interrupts may be asserted by application of a high pulse to an assigned input pin of the microcontroller 1505 (e.g., pins EX0IN - EX7IN and pin T2IN of the Siemens SABC-165 microcontroller).

The functions of the peripheral event interrupts may be explained in more detail as follows. When the OTA LCA 1502 is in need of data to transmit, it asserts a type 1 interrupt (according to Table 1-1), and the microcontroller 1505 responds with an operation including the steps of reading data from the SRAM transmit buffer 1707 (see Fig. 17) and writing the data to the OTA LCA transmit register (0E010H). The data is

16

thereafter transferred to the radio transceiver 305 (see Fig. 3) at the appropriate time for transmission.

For the reception of data, the OTA LCA 1502 asserts a type 2 interrupt (according to Table 1-1) to request that data in the OTA LCA receive register (0E011H) be placed into the receive SRAM receive buffer 1706 (see Fig. 17). The microcontroller 1505 responds with an operation including the steps reading the data from the OTA LCA receive register and writing the data to the SRAM receive buffer 1706.

A type 3 interrupt and type 7 interrupt (according to Table 1-1) are used in conjunction with various actions performed by or in relation to the DSP/vocoder 1510. The DSP/vocoder 1510, as described below, encodes data to be transmitted and decodes received data. For the transmit process, encoded data is transferred from the DSP/vocoder 1510 to the OTA LCA 1502 at certain time intervals. When a type 3 interrupt is asserted, the microcontroller 1510 transfers the data from the OTA LCA encoded data register (0E012H) to the SRAM transmit buffer 1707 for transmission at a later time. A type 7 interrupt is used in conjunction with the receipt of data and the transfer of that data to the DSP/vocoder 1510. The DSP/vocoder 1510 expects control information to follow the transmission of bearer information. When data is received from the radio transceiver 305 and stored in the SRAM receive buffer 1706 (see Fig. 17), the OTA LCA 1502 asserts a type 7 interrupt. In response, the microcontroller 1505 writes a byte of DSP/vocoder data or control information from the SRAM receive buffer 1706 to the DSP data/control bytes register (0E013H). This process may be repeated as necessary until all the pertinent data has been transferred to the DSP/vocoder 1510.

10

15

20

25

30

35

A type 4 interrupt is used in conjunction with activities performed by or in relation to the SIM card connected to the SIM port 1520. To transfer data to the SIM card, data is moved from the SIM buffer 1705 in the SRAM 1701 to the SIM transmit register (0E006H) within the OTA LCA 1502 in response to assertion of a type 4 interrupt. As data is needed, the OTA LCA 1502 asserts the type 4 interrupt to ensure a continuous flow of data to the SIM card. Once the SIM card receives all of its command and data information, it responds with output data for further processing by the microcontroller 1505. The SIM output data is moved from the SIM transmit register (0E006H) to the SIM buffer 1705 also through a type 4 interrupt. The microcontroller 1505 preferably takes account of the current state of the SIM card to determine the source and destination of data, as the type 4 interrupt can have more than one effect depending upon the state of the SIM card.

A type 5 interrupt may be used to send commands to the linearizer ASIC 1513. The microcontroller 1505 sends a command to the linearizer ASIC 1513 by writing a

17

command word to the linearizer command/data location (address 0E019H) in the peripheral address map. When the write is complete, the linearizer state machine will begin to transfer data to the linearizer ASIC 1513. In addition, the linearizer state machine will make supplementary requests for data as each byte is sent out. The microcontroller 1505 may keep track of the number of bytes sent to the linearizer ASIC 1513.

5

10

15

20

25

30

35

A type 6 interrupt is utilized during the course of receiving data, to pre-validate and/or pre-process the received data prior to the completion of an entire frame of data. To initiate this process, the microcontroller 1505 constructs a set of command templates and masks, placed in the SRAM command buffer 1704, for the information it expects to see with each reception. A compare state machine within the OTA LCA 1502 asserts the type 6 interrupt twice for each comparison operation, a first time to retrieve a byte of the command template from the SRAM command buffer 1704 and a second time to retrieve a corresponding mask byte from the SRAM command buffer 1704. With each incoming command byte from the receive frame, the compare state machine retrieves a command template byte and mask byte (i.e., a command/mask pair) from the SRAM command buffer 1704, and attempts to validate the incoming command. Further details of this process are described later herein.

A type 8 interrupt allows the microcontroller 1505 to change operative radio frequencies. The radio configuration data (e.g., frequency and code set, if applicable) is stored in the flash memory 1525, and is transferred to the RIF ASIC 1514 by transfer of a special command code (referred to as RFLOAD) written by the microcontroller 1505 to the radio configuration/slot map data register (0E002H) of the OTA LCA 1502. The RFLOAD command code governs what type of radio configuration data is to be transferred to the RIF ASIC 1514. When the OTA LCA 1502 receives the RFLOAD command, it asserts a type 8 interrupt to initiate transfer of the radio configuration data to the RIF ASIC 1514.

A type 9 interrupt is used by the OTA LCA 1502 to inform the microcontroller 1505 of an error of the end of the operation. The microcontroller 1505 responds to a type 9 interrupt by reading the general status register to determine the source of the error, if any.

In operation, the control section 1501 assists in the transmission and reception of data by a user station 102 or 301 within a multiple access communication system. The control section 1501 preferably operates according to a frame structure such as disclosed in Figs. 4, 5 or 6 herein, but may also be useful with a wide variety of alternative frame structures. Information is passed to and from the radio transceiver 305 (see Fig. 3) across the radio link 1590 shown in Fig. 15. The information is processed, as hereafter described,

by the RIF ASIC 1514 and OTA LCA 1502, under control of the microcontroller 1505, and transferred to and from the DSP/vocoder 1510 and the CODEC 1511. The DSP/vocoder 1510 may incorporate vocoder functionality, and may provide voice data to and remove voice data from the CODEC 1511 according to an applicable sub-rate speech coder algorithm. Voice data may be formatted as 64K  $\mu$ -law pulse-coded modulated (PCM) data.

5

10

15

20

25

30

35

The CODEC 1511 provides an interface between the digital circuitry of the control section 1501 and the analog circuitry of the end application (e.g., speaker/microphone 336, as shown in Fig. 3). The CODEC 1511 may operate at any suitable frequency, such as 2.048 MHz, and may be synchronized to the master radio clock at an 8 KHz rate. A frame sync clock may also be provided to the CODEC 1511. The frame sync clock may be any suitable frequency, such as 8 KHz, and may also be synchronized to the master radio clock. A presently preferred CODEC 1511 is commercially available from Texas Instruments, under the product name TLV320AC36IPT. A presently preferred DSP/vocoder 1510 is also commercially available from Texas Instruments, under the product name TMS320LC53SPZ57.

The compressed data created by the DSP/vocoder 1510 is stored, via the OTA LCA 1502, in the SRAM transmit buffer 1707 prior to transmission to the base station 104. At a time prior to the start of the transmit frame, the OTA LCA 1502 begins requesting data from the DSP/vocoder 1510, which responds with a serial stream of data over the serial link 1540. The DSP/vocoder 1510 may provide a single byte per request from the OTA LCA 1502, and when the data is received by the OTA LCA 1502, a PEC interrupt (i.e., a type 3 interrupt as defined herein) is asserted by the OTA LCA 1502. In response, the microcontroller 1505 writes the data to the SRAM transmit buffer 1707. In a preferred embodiment, an entire frame of data, including bearer (e.g., voice) data and status bytes, will be moved from the DSP/vocoder 1510 into the SRAM transmit buffer 1707 before the transmit frame starts.

After the transmit frame starts, the OTA LCA 1502 asserts a type 1 interrupt (as defined later herein) to request a byte of encoded data from the SRAM transmit buffer 1707. In response, the microcontroller 1505 transfers the encoded (voice) data from the SRAM transmit buffer 1707 to the OTA LCA 1502. The OTA LCA 1502 continues to request encoded data in the same manner until the entire transmit frame is sent.

Received data in compressed form is sent, via the OTA LCA 1502, to the DSP/vocoder 1510 for decompression. The received data is first stored in the SRAM receive buffer 1706, then transferred out of the receive buffer 1706 by the OTA LCA 1502. Prior to receiving the first byte of compressed bearer (e.g., voice) data, the OTA

LCA 1502 writes the sync bytes to the DSP/vocoder 1510. The sync bytes may be stored within the OTA LCA 1502 and transferred to the DSP/vocoder 1510 without intervention by the microcontroller 1505. As data is received over the radio link 1590 from the radio transceiver 305 (see Fig. 3), it is stored temporarily in the OTA LCA 1502. For each byte of data received a PEC interrupt (i.e., type 2 interrupt as defined herein) is asserted by the OTA LCA 1502. In response, the microcontroller 1505 transfers the byte of data in the SRAM receive buffer 1706. After each byte of bearer (e.g., voice) data is received and stored in the SRAM receive buffer 1706, it is serialized by the OTA LCA 1502 and sent to the DSP/vocoder 1510. After receipt of the bearer data is complete, the OTA LCA 1502 generates an interrupt to the microcontroller 1505 requesting the receipt of control bytes for the DSP/vocoder 1510. In response to the interrupt, the microcontroller 1505 transfers the control data to the OTA LCA 1502, which transfers the control data serially to the DSP/vocoder 1510.

10

15

20

25

30

35

During the course of receiving data, it may be desirable to begin validation and pre-processing before receipt of an entire frame of data. To initiate this process, the microcontroller 1505 constructs a set of command templates and masks for those commands that it expects to see with each receive frame. The set of command templates and masks are temporarily stored in the SRAM command buffer 1704. If the user station 301 is monitoring more than one time slot, then a separate area may be set up within the SRAM command buffer 1704 for each time slot that the user station 301 is monitoring.

A single command template and mask together comprise a command/mask pair. The command template of the command/mask pair represents a command (or data) that the microcontroller 1505 expects to see in the next receive frame. The command template is compared against one or more command bytes after they are received as part of the receive frame. The number of command bytes to compare is controlled by a compare count command communicated to the OTA LCA 1502 from the microcontroller 1505. The mask of the command/mask pair provides the ability to ignore certain selected bits of the command template in the comparison operation. For example, in one embodiment, any mask bit of the mask that contains a logical "0" causes the corresponding bit of the command template to be excluded from the compare operation and not affect the outcome.

Once the microcontroller 1505 has built up the set of command/mask pairs in the SRAM command buffer 1604, the microcontroller 1505 then writes a compare count value to the Compare Count register within the OTA LCA 1502. The compare count value indicates how many control bytes are to be compared, including header bytes. The compare count value consequently will ordinarily be equal to at least the number of header bytes (e.g., three bytes, in a preferred embodiment). A compare state machine within the

OTA LCA 1502 reads the compare count value and loads it into a decrementing register in preparation for the series of command compares. The compare state machine then asserts an interrupt (i.e., a type 6 interrupt as defined herein) twice for each comparison operation, once to retrieve a command template byte from the SRAM command buffer 1704 and a second time to retrieve a corresponding mask byte from the SRAM command buffer 1704. With each incoming command byte from the receive frame, the compare state machine uses two interrupts to retrieve a command template byte and mask byte (i.e., a command/mask pair) from the SRAM command buffer 1704.

With each comparison between the unmasked portion of the command template byte and the incoming command byte, the decrementing register (i.e., the Compare Counter) in the OTA LCA 1502 is decremented. Once the receive process has started, each command byte will be compared until the count in the Compare Counter reaches zero, or else a bad comparison is made (i.e., the unmasked portion of the command template byte and the incoming command byte do not match), the compare process terminates; however, the Compare Counter continues to decrement with each received byte. When the Compare Counter reaches zero, the interrupt control register is tested to determine if an interrupt should be issued; if so, a general interrupt may be issued and the compare complete bit will be set. Interrupts may be set to issue at the end of a receive frame and/or at the end of a compare operation.

Once a compare sequence progresses beyond the first byte (i.e., the Compare Counter is decremented at least once), the OTA LCA 1502 will proceed with transferring data to the DSP/vocoder 1510 and SRAM 1524. During this process, RSSI information is preferably generated regardless of when an interrupt is issued and regardless of the outcome of the compare sequence, so as to allow the user station 301 to search for better time slots or a better base station 104 for communication based on signal strength measurements. If a bad comparison with the compare/mask pair occurs after the first byte but before the Compare Counter reaches zero, the PEC interrupts used for storing data in the SRAM command buffer 1704 are discontinued to save power. When the Compare Counter reaches zero, the entire receive frame is stored in the SRAM receive buffer 1706.

If the receive frame from the base station 104 comprises a general poll message or specific poll message (both of which may be used in establishing communication between a base station 104 and a user station, as described previously herein), then the above process may be altered somewhat. In a preferred embodiment, a message from the base station 104 comprises a first header byte comprising a field indicating the packet type (e.g., general poll message, specific poll message, or other type of message). If it is determined that the packet type indicates receipt of a general poll message or a specific

poll message, the compare state machine performs the compare/mask operation using the current command template to see whether a general poll message or specific poll message is a command type that is expected. If so, then the comparison process continues as described above. However, if the receive frame comprises a general poll message or specific poll message but the command template does not indicate that either such message is expected, then the compare state machine will not decrement the Compare Counter, will not store the header byte in the SRAM receive buffer 1706, and will not indicate an error. Instead, the OTA LCA 1502 ignores the remainder of the incoming message (although it may continue to generate RSSI information). At the beginning of the next receive frame, the OTA LCA 1502 makes a similar test for a general poll message or specific poll message, and responds in a similar way, and repeats this process until a general poll message or specific poll message is received or else a time-out occurs (which causes the microcontroller 1505 to reset the compare operation). The result of this special case is that, when the user station 301 is looking for a general poll message or specific poll message, the microcontroller 1505 is only interrupted/awakened on a valid general poll message or specific poll message, which results in a power savings.

5

10

15

20

25

30

35

The OTA LCA 1502 preferably supports a SIM interface that is compliant with the ISA/IEC 7816-3 interface standard. The SIM interface may be managed by the microcontroller 1505 through various interface registers in the OTA LCA 1502. The microcontroller 1505 is responsible for managing the setup of the SIM port 1520 over the SIM interface. The SIM port 1520 may, if desired, include the capability of inverting or not inverting data, under instruction of the microcontroller 1505. The SIM port 1520 may also include the capability of rearranging data prior to transmission and after reception to conform to a most-significant-byte (MSB) first or least-significant-byte (LSB) first format, so that fewer operations for formatting data are required by the microcontroller 1505.

To transmit data to the SIM card, the microcontroller 1505 writes the data to be transmitted in the SRAM SIM buffer 1705, prior to enabling the SIM interface. Once the data is in the SRAM SIM buffer 1705, the microcontroller 1505 writes the number of bytes of data to a SIM transmit counter, thereby enabling the SIM interface. The OTA LCA 1502 asserts a PEC interrupt (i.e., a type 4 interrupt as defined herein) to obtain the first byte of data from the SRAM SIM buffer 1705, and does so for each byte of data to be transmitted thereafter. With each byte of data retrieved, the SIM transmit counter is decremented until it reaches zero, at which point the transmit process is complete.

In case of a parity error, the SIM interface preferably re-transmits the data autonomously, without the need for intervention by the microcontroller 1505. The SIM interface does not make another transmit request (via a PEC interrupt) until the previous

byte has been transmitted successfully, or a reset from the microcontroller 1505 occurs. If an attempted transmission fails for a predefined number of times (e.g., 3 times), then the General Status register is set to indicate a SIM transmit error and the microcontroller 1505 may issue a reset to the SIM control circuitry via the General Purpose register.

The SIM port 1520 is placed in a receive mode (to receive data from the SIM card) upon power-up, or after a successful transmission sequence to the SIM card has been completed, or when an external SIM reset is performed. After each byte of data is received at the SIM port 1520 from the SIM card, the OTA LCA 1502 asserts an interrupt (i.e., a type 4 interrupt as defined herein) to move the data out of the OTA LCA 1502 and into the SRAM SIM buffer 1705. The microcontroller 1505 preferably keeps track of how many bytes have been transferred (as the hardware does not know how many bytes are to be received), and when the desired number of bytes have been received it resets the SIM state machine. During the receive operation, the microcontroller 1505 may perform a watchdog function to ensure that the SIM card is not disconnected or does not fail during the process.

In addition to providing an interface between the microcontroller 1505 and the SIM port 1520, the OTA LCA 1502 also provides an interface between the microcontroller 1505 and the linearizer ASIC 1513. The linearizer ASIC 1513 is connected to the OTA LCA 1502 over a bi-directional, serial interface 1541 which is used for transporting both commands and data. The OTA LCA 1502 comprises a linearizer interface which may be instructed by the microcontroller 1505 to serialize and transmit data to the linearizer ASIC 1513, or to receive data from the linearizer ASIC 1513. The linearizer interface may also be placed in an autonomous special function mode whereby it periodically loads a temperature compensation instruction in a register accessible to the linearizer ASIC 1513 without requiring intervention by the microcontroller 1505.

The user station 301 may include provisions for power reduction by selectively deactivating circuitry at times when the full processing potential of the device is not needed. When the microcontroller 1505 determines that a power reduction mode is appropriate, it instructs the OTA LCA 1502 to enter the power reduction mode by writing a command to a Sleep Control register. If the microcontroller 1505 is to shut itself completely off, it first stores information in the Interrupt Control register (0E016H) to indicate which events will cause interrupts and return the microcontroller 1505 to full operation. If the microcontroller 1505 desires to save some power but will not be inactive for a long period of time, it may choose to place itself in standby mode with the microcontroller 1505 reduced to its minimum frequency. To enter the standby mode, the microcontroller 1505 writes an appropriate command to the Sleep Control register of the

10

15

20

25

30

35

OTA LCA 1502. The OTA LCA 1502 responds by reducing the frequency of the master clock to the minimum allowable frequency (e.g., 1 MHz). The microcontroller 1505 restores itself to full speed prior to performing an operation by requesting an interrupt which is handled by the OTA LCA 1502. The microcontroller 1505 may also selectively place any or all of the DSP/vocoder 1510, CODEC 1511, digital radio ASIC, and linearizer ASIC 1513 into a power reduction mode, and to selectively restore any device from a power reduction mode to full operation, by issuing commands to the OTA LCA 1502.

Features of the software-based control system for user station 301 will now be described in more detail, with particular reference to Fig. 2 as well as occasionally with reference to features shown in the user station diagram of Fig. 3 and the control section diagram of Fig. 15. While reference is made to the preferred user station configurations illustrated in Figs. 3 and 15, it is to be understood that the inventive concepts and features relating to Fig. 2 are independent of those particular embodiments and will find applicability in systems having a variety of other configurations.

In Fig. 2, a software control system 201 (sometimes referred to herein as the radio-transceiver component of the software, or RTRX) generally comprises the components shown in solid lines, while components to which the control system 201 interfaces are generally shown in dotted lines. In addition to the components shown in Fig. 2, the software control system 201 also comprises a real-time operating system (RTOS) not shown in Fig. 2, which provides a software platform that facilitates interaction or operation of the components shown in Fig. 2. A number of the components of Fig. 2 are described individually below, followed by a description of a preferred interaction and operation of the various components to manage communications of a user station 301.

Two principal components of the software control system 201 include the over-the-air (OTA) driver 210 and the slot manager 211. The OTA driver 210 preferably controls transmit and receive operations for the user station 301, while the slot manager 211 preferably manages slot object-related operations. The OTA driver 210 and slot manager 211 communicate using message queues 212, 213, as further described herein.

The software control system 201 also comprises a variety of interrupt service routines (ISRs), including an MSCA ISR 224, software trap ISR 225, a timer ISR 226, and an end-of-transmit ISR 227, to handle various conditions and events requiring service. In addition, a peripheral event controller (PEC) ISR (not shown) is included in the software control system 201, to handle interrupts generated in conjunction with PEC related direct memory access (DMA) transfers.

As further shown in Fig. 2, the software control system 201 comprises a radio services module 217, which can be accessed by both the OTA driver 210 and the slot manager 211 and provides a common interface to a digital ASIC (hereinafter digital radio ASIC, or DRA) in the radio transceiver 305. The software control system 201 further comprises a digital signal processor (DSP) object manager 215 which, like the radio services module 217, can be accessed by both the OTA driver 210 and the slot manager 211. The general purpose of the DSP object manager 215 is to define and coordinate updates to the DSP/vocoder objects 216. Other parts of the software control system 201 include an automatic repeat request (ARQ) module 220 and a power control module 221, both of which are accessible to the slot manager 211. The ARQ module 220 is involved in processing header information for automatic repeat requests, and the power control module 221 processes power control commands received from the base station 104.

The software control system 201 communicates with other system components through a variety of mailboxes 241, 242, 243 and 244, each preferably having specific assigned functions, as further detailed herein. The OTA driver 210 may, for example, communicate with the OTA state machine 252 through a Slot Message (SM) mailbox 242 (designated SM Mbox in Fig. 2), or with a Digital Signal Processor (DSP) driver 251 through a DSP mailbox 244 (designated DSP Mbox in Fig. 2). The slot manager 211 of the software control system 201 can access various memory locations (including special-purpose registers) through a variety of direct memory access (DMA) interface components 235, 236, 237, 238 and 239, as further detailed herein.

The slot manager 211 is, in one aspect, the heart of the software control system 201. The slot manager 211 may define slot objects 231 and perform slot object related operations. Such operations may include the ability to create, delete, update and query a slot object 231. In addition, the slot manager 211 may carry out all slot operations which must be executed in response to hardware slot synchronous events (e.g., interrupts). The slot manager 211 may utilize its inherent knowledge of interrupts to manage the operations of slot objects 231, to synchronize DSP control and status updates, and to synchronize radio configuration updates.

The slot manager 211 also functions as a service module to the OTA driver 210 and the slot-related interrupt service routines (ISRs). The slot manager 211 may be invoked by the OTA driver 210 to initialize, create, update, query or delete a slot object 231. If a request cannot be serviced due to potential interrupt conflicts, as determined by the slot manager 211, then the OTA driver 210 may queue the request in the slot message input queue 212 for subsequent interrupt-synchronous processing. As part of its interrupt-related processing, the slot manager 211 may process messages that are queued in the slot

message input queue 212, and then queue corresponding responses in the slot message output queue 213. Slot event messages may also be queued in the slot message output queue 213. Slot event messages serve as "unsolicited" notification to the OTA driver 210 that a slot has complete a set of transmit and/or receive transactions. In one aspect, the slot event messages provide a snapshot of the most recent transaction status, including, for example, transmit status, RSSI values, and receive data.

5

10

15

20

25

30

35

During its various processes, the slot manager 211 may use service functions to set up hardware, configure ISRs, set up PEC DMA paths, and to update slot objects 231. The slot manager 211 may, for example, invoke the DSP object manager 215 to create and initialize DSP objects 216, to commit DSP control updates, or to update DSP status. The slot manager 211 may invoke the radio services module 217 to commit configuration updates, synchronize the radio transceiver to time slots, switch between receive and transmit frequencies, read RSSI values, or set the transmit power level. The slot manager 211 may invoke the ARQ module 220 to control error detection and recovery processing on OTA packets. In addition, the slot manager 211 may invoke the power control module 221 to control the transmit power level of the radio transceiver 305 (see Fig. 3). The slot manager 211 also may use power-on/self-test functions to set up the various PEC DMA paths.

The MSCA ISR 224 handles the general status interrupts that are from time to time generated by the MSCA 1591. Non-slot related interrupts are sensed, then signalled externally to the OTA driver 210 through the external event interface 261. Slot-related interrupts (e.g., interrupts occurring when the radio transceiver 305 receives data on an active slot) are handled by invoking the associated function(s) of the slot manager 211.

The software trap ISR 225 handles software interrupts generated by the software control system 201. The software trap ISR 225 invokes the appropriate function(s) of the slot manager 211 based upon the source of the interrupt. The software trap ISR 225 may be invoked, for example, upon an end-of-transmit interrupt or a one-shot timer interrupt.

The end-of-transmit (EOTX) ISR 227 handles an interrupt generated upon completion of the transmit portion of a slot. The EOTX ISR 227 sets a flag and generates a software trap (thus invoking the software trap ISR 225) to perform end-of-transmit processing. The peripheral event controller of the OTA LCA 1502 invokes the EOTX ISR 227 upon completion of a DMA transfer of transmit data from the SRAM 1524 to the radio transceiver 305.

The timer ISR 226 handles an interrupt generated upon expiration of a local oneshot timer 229. To perform timer expiration processing, the timer ISR 226 may, for example, update a semaphore or set a flag.

The peripheral event controller (PEC) ISRs (not shown in Fig. 2) handle interrupts generated upon completion of PEC-controlled DMA transfers. The PEC ISRs are triggered upon completion of DMA data transfers requested by the OTA LCA 1502 through the associated PEC channel.

5

10

15

20

25

30

35