(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5735984号

(P5735984)

(45) 発行日 平成27年6月17日(2015.6.17)

(24) 登録日 平成27年4月24日(2015.4.24)

|              |                |

|--------------|----------------|

| (51) Int.Cl. | F 1            |

| HO1L 33/14   | (2010.01)      |

| HO1L 33/32   | (2010.01)      |

| HO1L 33/06   | (2010.01)      |

| HO1L 33/04   | (2010.01)      |

|              | HO1L 33/00 150 |

|              | HO1L 33/00 186 |

|              | HO1L 33/00 112 |

|              | HO1L 33/00 110 |

請求項の数 12 (全 14 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-546427 (P2012-546427)  |

| (86) (22) 出願日 | 平成22年12月27日(2010.12.27)       |

| (65) 公表番号     | 特表2013-516751 (P2013-516751A) |

| (43) 公表日      | 平成25年5月13日(2013.5.13)         |

| (86) 國際出願番号   | PCT/EP2010/070761             |

| (87) 國際公開番号   | W02011/080249                 |

| (87) 國際公開日    | 平成23年7月7日(2011.7.7)           |

| 審査請求日         | 平成25年12月25日(2013.12.25)       |

| (31) 優先権主張番号  | 102009060747.1                |

| (32) 優先日      | 平成21年12月30日(2009.12.30)       |

| (33) 優先権主張国   | ドイツ(DE)                       |

|           |                                                                                                                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 599133716<br>オスラム オプト セミコンダクターズ<br>ゲゼルシャフト ミット ベシュレンクテ<br>ル ハフツング<br>Osram Opto Semiconduc<br>tors GmbH<br>ドイツ連邦共和国、93055 レーゲン<br>スブルグ、ライプニッツシュトラーゼ 4<br>Leibnizstrasse 4, D<br>-93055 Regensburg,<br>Germany<br>(74) 代理人 100105050<br>弁理士 驚田 公一 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】発光半導体チップ

## (57) 【特許請求の範囲】

## 【請求項 1】

- 半導体積層体を有する半導体ボディ(2)を備えた半導体チップ(1)であつて、

- 前記半導体積層体が、n型導電多層構造(21)と、p型導電半導体層(22)と、放射を生成するための活性領域(20)と、を備えており、前記活性領域が前記n型導電多層構造と前記p型導電半導体層との間に配置されており、

- 前記n型導電多層構造が、複数の井戸層(211)を有する量子構造を備えており、前記複数の井戸層が、障壁層(212)の間に配置されており、

- 少なくとも1つのドーピングピーク(4)を備えたドーピングプロファイルが、前記n型導電多層構造に形成されており、

- 前記n型導電多層構造が、前記ドーピングピークに隣接する領域を備えており、前記ドーピングピークに隣接する前記領域においては、前記井戸層と前記井戸層に隣接する障壁層とが低濃度にドープされており、

- 前記ドーピングプロファイルがさらなるドーピングピーク(41)を備えており、前記n型導電多層構造の少なくとも1層の井戸層が、前記ドーピングピークと前記さらなるドーピングピークとの間に配置されており、

- 前記n型導電多層構造の前記量子構造のサブ領域(216)が、前記さらなるドーピングピーク(41)によって高いドーピング濃度を備えている、

半導体チップ(1)。

## 【請求項 2】

10

20

前記少なくとも 1 つのドーピングピークにおけるドーピング濃度が、前記 n 型導電多層構造の、n 型導電性に低濃度にドープされた領域（45）、におけるドーピング濃度の少なくとも 5 倍である、

請求項 1 に記載の半導体チップ。

**【請求項 3】**

前記少なくとも 1 つのドーピングピークにおけるドーピング濃度が少なくとも  $4 \times 10^{18} / \text{cm}^3$  であり、n 型導電性に低濃度にドープされた前記領域におけるドーピング濃度が最大で  $8 \times 10^{17} / \text{cm}^3$  である、

請求項 2 に記載の半導体チップ。

**【請求項 4】**

前記ドーピングピークの垂直方向の大きさが、1 nm ~ 30 nm の範囲内（両端値を含む）である、

請求項 1 から請求項 3 のいずれかに記載の半導体チップ。

**【請求項 5】**

前記ドーピングピークの垂直方向の大きさが、5 nm ~ 20 nm の範囲内（両端値を含む）である、

請求項 1 から請求項 4 のいずれかに記載の半導体チップ。

**【請求項 6】**

前記活性領域から前記ドーピングピークまでの距離が、2 nm ~ 20 nm の範囲内（両端値を含む）である、

請求項 1 から請求項 5 のいずれかに記載の半導体チップ。

**【請求項 7】**

前記活性領域が複数の井戸層（201）を備えており、前記ドーピングピークが、前記 n 型導電多層構造の前記井戸層のうち前記活性領域に最も近い前記井戸層と、前記活性領域の前記井戸層のうち前記 n 型導電多層構造に最も近い前記井戸層との間に配置されている、

請求項 1 から請求項 6 のいずれかに記載の半導体チップ。

**【請求項 8】**

前記 n 型導電多層構造の前記井戸層のバンドギャップが、前記活性領域の前記井戸層（201）のバンドギャップと少なくとも同じ大きさである、

請求項 7 に記載の半導体チップ。

**【請求項 9】**

前記活性領域が窒化物化合物半導体材料をベースとする、

請求項 1 から請求項 8 のいずれかに記載の半導体チップ。

**【請求項 10】**

前記 n 型導電多層構造の結晶構造が、V 形状の凹部を備えている、

請求項 1 から請求項 9 のいずれかに記載の半導体チップ。

**【請求項 11】**

前記半導体積層体の成長基板が前記半導体ボディから除去されている、

請求項 1 から請求項 10 のいずれかに記載の半導体チップ。

**【請求項 12】**

- 前記少なくとも 1 つのドーピングピークにおけるドーピング濃度が、前記ドーピングピークに隣接している、前記 n 型導電多層構造の領域、におけるドーピング濃度の少なくとも 5 倍であり、

- 前記活性領域が、少なくとも 1 層の井戸層（201）を有する量子構造、を備えている、

- 前記 n 型導電多層構造の前記井戸層のバンドギャップが、前記活性領域の前記井戸層のバンドギャップよりも大きい、

請求項 1 に記載の半導体チップ。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本出願は、放射を生成するための半導体チップに関する。

**【背景技術】****【0002】**

L E D 半導体チップは、放射を生成するための活性領域として、複数の量子井戸を有する活性領域を備えている場合がしばしばある。

**【0003】**

活性領域に I n G a N 量子井戸が存在するとき、放出される放射出力は、電流密度の増大に対して線形的には大きくならないことが判明している。この原因の 1 つとして、電荷キャリアが量子井戸に効率的に注入されない場合がしばしばある。10

**【先行技術文献】****【非特許文献】****【0004】**

【非特許文献 1】I. Schnitzer et al., Appl. Phys. Lett. 63 (16), 18 October 1993, 2174 - 2176

**【発明の概要】****【0005】**

本発明の 1 つの目的は、電荷キャリアが活性領域に効率的に注入される半導体チップを提供することである。20

**【0006】**

この目的は、独立請求項 1 の主題によって達成される。従属請求項は、さらなる構造形態およびさらなる発展形態に関する。

**【0007】**

一実施形態においては、半導体チップは、半導体積層体を有する半導体ボディを備えており、この半導体積層体は、n 型導電多層構造と、p 型導電半導体層と、放射を生成するための活性領域と、を備えている。活性領域は、n 型導電多層構造と p 型導電半導体層との間に配置されている。n 型導電多層構造には、少なくとも 1 つのドーピングピーク (doping peak) を備えたドーピングプロファイルが形成されている。

**【0008】**

ドーピングプロファイルは、特に、垂直方向、したがって半導体ボディの半導体積層体の堆積方向における、ドーピングの分布である。言い換えれば、ドーピングプロファイルは、半導体ボディの半導体積層体の半導体層の主延在面に垂直な方向に延びている。

**【0009】**

本出願において、ドーピングピークとは、半導体材料の領域のうち、自身に隣接する少なくとも 1 つの領域と比較して高いドーピング濃度を有する領域を意味するものと理解されたい。ドーピングピークを囲む（好ましくは両側の）半導体材料は、低濃度にドープされている、ドープされていない、または真性であることが好ましい。

**【0010】**

高いドーピング濃度とは、特に、少なくとも  $2 \times 10^{18} / \text{cm}^3$  の濃度を意味するものと理解されたい。40

**【0011】**

低いドーピング濃度とは、特に、少なくとも  $1 \times 10^{16} / \text{cm}^3$ 、最大で  $1 \times 10^{18} / \text{cm}^3$  の濃度を意味するものと理解されたい。

**【0012】**

特に、ドーピングピークが、n 型導電多層構造の残りの部分と比較して、薄くかつ高濃度にドープされていることによって、半導体チップの活性領域への電荷キャリアの注入が改善されることが判明した。n 型導電多層構造は、ドーピングピークの領域において、高濃度のドーピングの結果として横断方向の導電率が比較的高くなり（すなわち横方向における高い導電率）、したがって、横方向において特に均一に電荷キャリアを活性領域に注50

入することができる。逆方向（すなわち活性領域の非導通方向）においても、少なくとも1つのドーピングピークによって、横方向における均一な電流フローが得られる。このようにすることで、半導体チップは、静電放電（E S D）に対する低い感受性を示す。

#### 【0013】

好ましい構造形態においては、n型導電多層構造は、ドーピングピークによる高濃度にドープされた少なくとも1つの領域と、n型導電性に低濃度にドープされた1つの領域とを備えている。少なくとも1つのドーピングピークにおけるドーピング濃度は、n型導電多層構造の、n型導電性に低濃度にドープされた領域のドーピング濃度の、好ましくは少なくとも5倍、特に好ましくは少なくとも8倍、例えば10倍である。

#### 【0014】

n型導電性に低濃度にドープされた領域は、特に、ドーピングピークに隣接している。

#### 【0015】

ドーピングピークにおけるドーピング濃度は、少なくとも $4 \times 10^{18} / \text{cm}^3$ であることが好ましい。高いドーピング濃度の結果として、高い導電率を達成することができる。

#### 【0016】

さらには、ドーピングピークにおけるドーピング濃度は、好ましくは最大で $1 \times 10^{20} / \text{cm}^3$ 、特に好ましくは最大で $3 \times 10^{19} / \text{cm}^3$ である。

#### 【0017】

さらには、n型導電性に低濃度にドープされた隣接する領域におけるドーピング濃度は、好ましくは最大で $5 \times 10^{17} / \text{cm}^3$ 、特に好ましくは最大で $2 \times 10^{17} / \text{cm}^3$ である。

#### 【0018】

好ましい構造形態においては、少なくとも1つのドーピングピークにおけるドーピング濃度は、少なくとも $4 \times 10^{18} / \text{cm}^3$ であり、n型導電性に低濃度にドープされた領域におけるドーピング濃度は、最大で $8 \times 10^{17} / \text{cm}^3$ である。

#### 【0019】

ドーピングピークの垂直方向の大きさは、1nm～30nmの範囲内（両端値を含む）、特に好ましくは2nm～20nmの範囲内（両端値を含む）である。特に、ドーピングピークの垂直方向の大きさは、7nm～10nmの範囲内（両端値を含む）である。

#### 【0020】

n型導電多層構造は、特に、半導体チップの動作時に活性領域に電子を注入する役割を果たす。この目的において、n型導電多層構造は、必ずしも全体がn型導電性にドープされている必要はない。n型導電多層構造は、ドープされていないかまたは真性である1層または複数の層を備えていることもできる。

#### 【0021】

p型導電半導体層は、特に、活性領域に正孔を注入することを目的とする。p型導電半導体層は、多層構造とすることもでき、その場合、個々の層は、ドーピングもしくは結晶組成またはその両方に關して異なっていることができる。

#### 【0022】

半導体ボディは、化合物半導体、特に、窒化物化合物半導体をベースとすることが好ましい。

#### 【0023】

「窒化物化合物半導体をベースとする」とは、本明細書においては、活性エピタキシャル積層体（active epitaxial layer sequence）またはその少なくとも1層が、I I I / V族窒化物化合物半導体材料、好ましくは $\text{Al}_y\text{Ga}_{1-x-y}\text{In}_x\text{N}$ （0 < x < 1、0 < y < 1、x + y = 1）を含んでいることを意味する。この材料は、上の化学式による数学的に正確な組成を必ずしも有する必要はない。この材料は、例えば、1種類または複数のドーパントと、 $\text{Al}_y\text{Ga}_{1-x-y}\text{In}_x\text{N}$ 材料の特徴的な物理特性を実質的に変化させることのない追加の構成成分を含んでいることができる。しかしながら、説明を簡

10

20

30

40

50

潔にする目的で、上の化学式は、結晶格子の基本的な構成成分（すなわち A l、G a、I n、N）を含んでいるのみであり、これらの構成成分は、一部分を少量の別の物質によって置き換えることができる。

**【 0 0 2 4 】**

活性領域は、複数の井戸層を備えていることが好ましい。井戸層は、障壁層の間に配置されていることが好ましい。井戸層および障壁層は、量子構造を形成している。

**【 0 0 2 5 】**

本出願において、用語「量子構造」は、特に、包み込み（「閉じ込め」）によって電荷キャリアにおいてエネルギー状態の量子化が起こる任意の構造を包含する。特に、量子構造という表現は、量子化の次元について何らかの指定を行うものではない。したがって、量子構造には、特に、量子井戸、量子細線、および量子ドットと、これらの構造の任意の組合せとが含まれる。10

**【 0 0 2 6 】**

好ましい構造形態においては、n型導電多層構造は、量子構造を備えている。この量子構造は、複数の井戸層を備えていることができる。

**【 0 0 2 7 】**

用語「量子構造」は、多重量子井戸構造（MQW）としての構造と、超格子としての構造の両方を意味するものと理解されたい。超格子においては、多重量子井戸構造とは異なり、隣り合う井戸層の間の距離が小さく、隣り合う井戸層の電子状態によって量子が機械的にまとまって、共通の電子状態が形成される。20

**【 0 0 2 8 】**

障壁層は、例えば、超格子の井戸層の間に形成することができ、5nm以下の厚さ、例えば2nmの厚さを有する。

**【 0 0 2 9 】**

好ましい構造形態においては、n型導電多層構造の井戸層のバンドギャップは、活性領域の井戸層のバンドギャップと少なくとも同じ大きさである。特に好ましくは、多層構造の井戸層のバンドギャップは、活性領域の井戸層のバンドギャップより大きい。例えば、窒化物化合物半導体材料をベースとする半導体チップの場合、n型導電多層構造の井戸層は、活性領域の井戸層よりも低いインジウム含有量xを有することができる。

**【 0 0 3 0 】**

n型導電多層構造の井戸層は、活性領域の井戸層とは異なり、放射の生成を目的とするのではなく、特に、活性領域に電子を効率的に注入する役割を果たし、電子と正孔の再結合によって放射が放出される。30

**【 0 0 3 1 】**

活性領域の井戸層は、真性である、またはドープされていないことが好ましい。

**【 0 0 3 2 】**

さらなる好ましい構造形態においては、ドーピングピークは、n型導電多層構造の井戸層のうち活性領域に最も近い井戸層と、活性領域の井戸層のうちn型導電多層構造に最も近い井戸層との間に配置されている。したがって、活性領域の近傍において横方向の良好な電流分散が確保される。40

**【 0 0 3 3 】**

さらには、活性領域からドーピングピークまでの距離、特に、活性領域の井戸層のうちn型導電多層構造に最も近い井戸層から、ドーピングピークまでの距離は、1nm～30nmの範囲内（両端値を含む）、特に好ましくは2nm～20nmの範囲内（両端値を含む）、特に、7nm～10nmの範囲内（両端値を含む）である。

**【 0 0 3 4 】**

活性領域の近傍における、この高濃度にドープされたドーピングピークによって、活性領域への電荷キャリアの注入が、特に効率的に、かつ特に横方向に均一に行われる。さらに、半導体ボディのn型導電領域にドーピングピークが含まれていない半導体チップと比較したとき、少なくとも1つのドーピングピークによって、横方向の導電率が高いことで50

、電荷キャリアの多数の経路の使用が改善され、これにより E S D 損傷の危険性が減少する。

#### 【0035】

少なくとも 1 つのドーピングピークは、ドーピングプロファイルにおいてドーピング濃度が低濃度から高濃度、および高濃度から低濃度に急激に変化するように、構成されていることが好ましい。このことは、本半導体チップを製造するとき、低い成長速度（例えば、 $20 \text{ nm/h}$  ~  $500 \text{ nm/h}$  の範囲内の速度）によって達成することができる。堆積は、エピタキシャルに（例えば MOCVD によって）行うことが好ましい。

#### 【0036】

さらなる好ましい発展形態においては、n 型導電多層構造の結晶構造は、V 形状の凹部（V-shaped indentations）を備えている。このような凹部（半導体層の堆積時に、特に、転位線に沿って形成されることがある）は、「V ピット」としても知られている。このような V 形状の凹部は、特に、半導体材料の比較的低い堆積温度（例えば 950 以下）において形成されうる。これらの V 形状の凹部によって、非導通方向における半導体チップの挙動を改善することができる。

10

#### 【0037】

さらなる好ましい構造形態においては、ドーピングプロファイルは、少なくとも 1 つのさらなるドーピングピークを備えていることができる。特に、n 型導電多層構造の少なくとも 1 層の井戸層を、ドーピングピークと、さらなるドーピングピークとの間に配置することができる。言い換えれば、n 型導電多層構造の井戸層の一部が高濃度に n 型導電性にドープされており、井戸層の残りの部分が、これと比較して低濃度に n 型導電性にドープされているように、ドーピングプロファイルを構成することができる。

20

#### 【0038】

ドーピングプロファイルは、3 つ以上のドーピングピーク、特に、1 ~ 5 つの範囲内（両端値を含む）のドーピングピーク、好ましくは 1 ~ 3 つの範囲内（両端値を含む）のドーピングピークを備えていることもできる。

#### 【0039】

本半導体チップの好ましい構造形態においては、半導体ボディの半導体積層体の成長基板が、完全に、または少なくとも部分的に除去されている。このような半導体チップは、薄膜半導体チップとしても知られている。

30

#### 【0040】

本発明の目的において、薄膜半導体チップ、例えば薄膜発光ダイオードチップは、以下の特徴的な形状構造の少なくとも 1 つによって、さらに区別することができる。

- 活性領域を有する半導体積層体（特にエピタキシャル積層体）を備えた半導体ボディの第 1 の正面（キャリア要素の側の面）に、ミラー層が堆積または形成されており（例えば、ブラックミラーとして半導体層に組み込まれている）、このミラー層は、半導体積層体において生成された放射の少なくとも一部分を反射して半導体積層体に戻す。

- 半導体積層体の厚さは、 $20 \mu\text{m}$  以下の範囲、特に  $10 \mu\text{m}$  以下の範囲である。

- 半導体積層体は、少なくとも一面が混合構造（intermixing structure）である少なくとも 1 層の半導体層を含んでおり、この混合構造によって、理想的には半導体積層体における近似的に光のエルゴード分布につながり、すなわち、この混合構造は、実質的にエルゴード的確率過程である散乱挙動を示す。

40

#### 【0041】

薄膜発光ダイオードチップの基本的な原理は、例えば非特許文献 1 に記載されており、この点に関するこの文書の開示内容は、参照によって本出願に組み込まれている。

#### 【0042】

以下では、本発明のさらなる特徴、構造形態、有利な態様について、例示的な実施形態に基づいて図面を参照しながら説明する。

#### 【図面の簡単な説明】

#### 【0043】

50

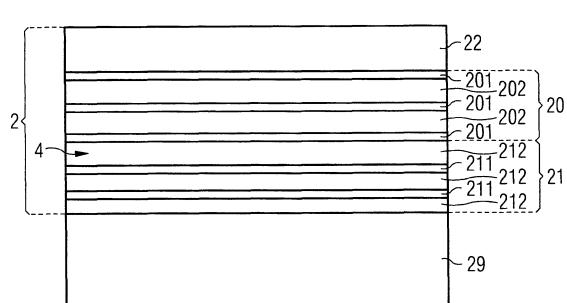

【図1A】半導体積層体を有する半導体ボディの例示的な実施形態の概略的な断面図である。

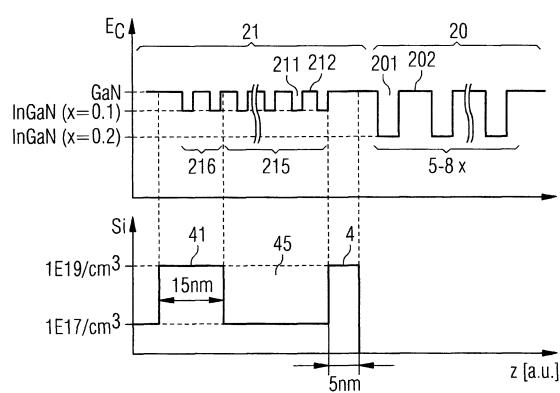

【図1B】第2の例示的な実施形態による半導体ボディの一部分の、堆積方向zにおける伝導帯端プロファイルE<sub>c</sub>およびドーピングプロファイルの概略図を示している。

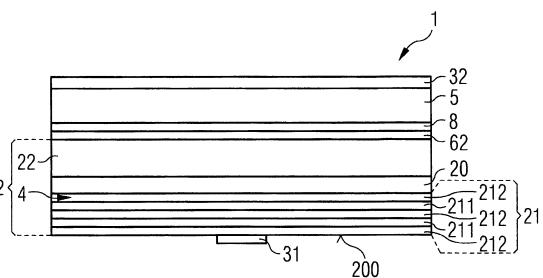

【図2】半導体チップの第1の例示的な実施形態の概略的な断面図である。

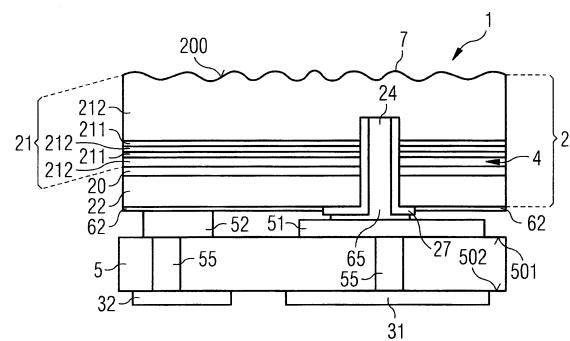

【図3】半導体チップの第2の例示的な実施形態の概略的な断面図である。

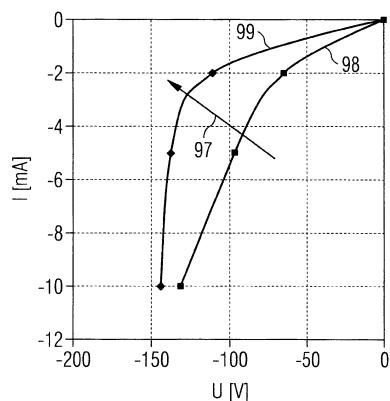

【図4】逆方向に印加された電圧Uの関数としての電流Iの測定結果を示している。

【発明を実施するための形態】

【0044】

図面において、同じ要素、類似する要素、または機能が同じである要素には、同じ参照数字を付してある。 10

【0045】

各図は概略的に描いてあり、したがって必ずしも正しい縮尺ではない。むしろ図を明確にする目的で、比較的小さい要素、特に層の厚さは、誇張した大きさで示してある。

【0046】

図1Aは、半導体チップの半導体ボディの第1の例示的な実施形態を概略的な断面図として示している。半導体ボディ2は、半導体積層体によって形成されている。半導体積層体は、放射を生成するための活性領域20を備えており、活性領域20は、n型導電多層構造21とp型導電半導体層22との間に配置されている。半導体ボディの半導体積層体は、成長基板29の上にエピタキシャルに（特に、MBEまたはMOCVDによって）堆積されていることが好ましい。窒化物化合物半導体材料をベースとする半導体ボディの成長基板として適する材料の例は、サファイア、炭化ケイ素、シリコン、窒化ガリウムである。n型導電多層構造21と成長基板との間にバッファ層を形成することができ、このバッファ層は、特に、結晶品質を高める目的で設けることができる（明示的には示していない）。 20

【0047】

活性領域20は量子構造を備えており、量子構造は、複数の井戸層201と、これら井戸層の間に配置されている複数の障壁層202とによって形成されている。この実施形態では、活性領域は、単なる一例として3層の井戸層を有する量子構造を備えている。しかしながら、このバリエーションとして、別の数の井戸層（例えば1層のみ、2層、または4層以上、例えば最大で20層、例えば5～8層の井戸層）を設けることもできる。 30

【0048】

p型導電半導体層22も多層構造とすることができます、この場合、個々の層は、特に、材料組成もしくはドーピングまたはその両方に關して互いに異なっていることができる。

【0049】

n型導電多層構造21は、複数の井戸層211を有する量子構造を備えており、井戸層211は障壁層212の間に配置されている。

【0050】

矢印は、垂直方向（すなわち半導体ボディ2の半導体層の主延在面に垂直な方向）における、ドーピングピーク4の位置を、概略的に示している。ドーピングピークは、n型導電多層構造21の中、特に、n型導電多層構造の井戸層211のうち活性領域に最も近い井戸層211と、活性領域20の井戸層201のうちn型導電多層構造に最も近い井戸層201との間に、位置している。ドーピングピーク4に隣接する、n型導電多層構造の領域においては、井戸層211と、井戸層に隣接する障壁層が、低濃度にドープされている。 40

【0051】

ドーピングピーク4によって、活性領域20への電子の効率的な注入を行うことができる。同様に、逆の方向においては、ドーピングピークによって、電流の拡散が改善され、これにより、半導体積層体によって形成されている半導体チップのESD損傷の危険性が減少する。したがって半導体積層体を堆積させる時点で早々とESD感受性の減少が達成 50

されるため、以降の製造ステップにおいて半導体チップが損傷する危険性が減少する。

**【0052】**

図1Bは、半導体チップの半導体ボディの第2の例示的な実施形態における、伝導帯端プロファイル $E_c$ と、シリコンドーピングのプロファイルを、z方向における関数として概略的に示している。z方向は、半導体ボディ2の半導体層の堆積方向に一致し、半導体ボディ2の半導体層の主延在面に垂直である。

**【0053】**

この第2の例示的な実施形態は、図1Aを参照しながら説明した、半導体ボディの第1の例示的な実施形態と実質的に同じである。第1の例示的な実施形態と異なる点として、第2の例示的な実施形態では、さらなるドーピングピーク41が設けられている。

10

**【0054】**

さらなるドーピングピーク41は、n型導電多層構造21の量子構造における高濃度にドープされたサブ領域を形成している。さらなるドーピングピークとドーピングピーク4との間には、n型導電性に低濃度にドープされた量子構造の領域45が設けられている。

**【0055】**

半導体ボディ2、特に、活性領域20は、この例示的な実施形態においては、窒化物化合物半導体材料をベースとしている。

**【0056】**

活性領域20は、複数の井戸層201を備えている。この例示的な実施形態においては、活性領域は、青色スペクトル領域の放射を生成することを目的としている。そのため、井戸層それぞれは、インジウム含有量 $x = 0.2$ を含んでいる。しかしながら、別のスペクトル領域の放射を放出するように活性領域を構成することもできる。インジウム含有量が高いほど、バンドギャップ（したがって活性領域において生成可能な光子のエネルギー）が小さくなる。このようにインジウム含有量は、広い範囲の中で変化させることができる。例えば、インジウム含有量 $x = 0.10$ の井戸層は、動作時に紫外線スペクトル領域の放射を放出し、インジウム含有量 $x = 0.40$ の井戸層は、緑色のスペクトル領域の放射を放送出する。井戸層の間にはGaNの障壁層202が配置されている。

20

**【0057】**

n型導電多層構造21のドーピングプロファイルは、この例示的な実施形態においては、シリコンドーピングによって形成される。しかしながら、別のドーパントを使用することもできる。

30

**【0058】**

ドーピングプロファイルは、ドーピングピーク4を備えている。ドーピングピーク4の幅は、この例示的な実施形態においては、約5nmである。ドーピングピーク4の領域におけるドーピング濃度は $1 \times 10^{19} / \text{cm}^3$ であるのに対して、ドーピングピーク4に隣接する、n型導電性に低濃度にドープされた領域45におけるドーピング濃度は、 $1 \times 10^{17} / \text{cm}^3$ である。さらに、ドーピングプロファイルは、幅15nmのさらなるドーピングピーク41を備えており、この領域のn型導電多層構造は、 $1 \times 10^{19} / \text{cm}^3$ のドーピング濃度でn型にドープされている。

**【0059】**

40

ドーピングピークによって、横方向において特に均一な電荷キャリアの注入を達成することができる。したがって、特に、活性領域の井戸層201のすぐ下において、効率的な電流拡散が生じる。

**【0060】**

n型導電多層構造21は、図1Aに関連して説明したように、複数の井戸層211（それぞれ障壁層212の間に配置されている）を有する量子構造を備えている。ドーピングプロファイルの結果として、低濃度にドープされた量子構造のサブ領域215と、高濃度にドープされた量子構造のサブ領域216とが生じる。これらの領域の中では、井戸層もしくは障壁層またはその両方を、それぞれドープすることができる。少なくとも1つのドーピングピークの領域において、井戸層および障壁層が高濃度にドープされていることが

50

好ましい。

**【0061】**

このように、n型導電多層構造21は、低濃度にドープされた量子構造のサブ領域と、高濃度にドープされた量子構造のサブ領域とを備えている。低濃度にドープされた量子構造のサブ領域215は、この実施形態では、ドーピングピーク4とドーピングピーク41との間に存在しており、半導体チップの動作時に電子の貯蔵領域となる。量子構造の低濃度にドープされたサブ領域においては、井戸層211と障壁層212とが低濃度にドープされている。n型導電多層構造21から活性領域20の井戸層への電荷キャリアの注入は、ドーピングピーク4によって、特に効率的かつ横方向に均一に行われる。

**【0062】**

この例示的な実施形態においては、n型導電多層構造21の井戸層は、一例としてインジウム含有量 $x = 0.1$ を含んでいる。しかしながら、インジウム含有量として別の値を選択することもできる。インジウム含有量は、活性領域における井戸層のインジウム含有量を超えないことが好ましく、したがって、n型導電多層構造21の井戸層のバンドギャップは、活性領域20における井戸層のバンドギャップより大きい、または、活性領域における井戸層のバンドギャップと同じである。

**【0063】**

n型導電多層構造の量子構造は、特に、量子井戸構造または超格子の形をとることができ、例えば、厚さが5nm未満（例えば約2nm）の障壁層を有する。

**【0064】**

これによって、活性領域への電荷キャリアの効率的な注入が単純に達成される。

**【0065】**

当然ながら、活性領域20およびn型導電多層構造21の材料組成と、ドーピングプロファイルは、説明した例示的な実施形態とは異なるものとすることができる。

**【0066】**

少なくとも1つのドーピングピーク4におけるドーピング濃度は、少なくとも $4 \times 10^{18} / \text{cm}^3$ であることが好ましい。さらには、ドーピングピークにおけるドーピング濃度は、好ましくは最大で $1 \times 10^{20} / \text{cm}^3$ 、特に好ましく最大で $3 \times 10^{19} / \text{cm}^3$ である。

**【0067】**

n型導電性に低濃度にドープされた領域45においては、ドーピング濃度は、好ましくは最大で $5 \times 10^{17} / \text{cm}^3$ 、特に好ましく最大で $2 \times 10^{17} / \text{cm}^3$ である。

**【0068】**

少なくとも1つのドーピングピークにおけるドーピング濃度は、n型導電多層構造の、n型導電性に低濃度にドープされた領域のドーピング濃度の好ましくは少なくとも5倍、特に好ましくは少なくとも8倍である。

**【0069】**

ドーピングピーク4もしくはさらなるドーピングピーク41またはその両方の厚さ（すなわち垂直方向の大きさ）は、好ましくは1nm～30nmの範囲内（両端値を含む）、特に好ましくは2nm～20nmの範囲内（両端値を含む）、最も好ましくは7nm～10nmの範囲内（両端値を含む）である。

**【0070】**

ドーピングピーク4は、活性領域20から小さい距離にあり、特に好ましくは最大で30nm、特に、1nm～30nmの範囲内（両端値を含む）、好ましくは2nm～20nmの範囲内（両端値を含む）、最も好ましくは7nm～10nmの範囲内（両端値を含む）の距離にあることが好ましい。

**【0071】**

さらには、説明した例示的な実施形態のバリエーションとして、3つ以上のドーピングピーク（例えば、1～5つの範囲内（両端値を含む）のドーピングピーク）を形成することもできる。

10

20

30

40

50

## 【0072】

さらには、説明した例示的な実施形態のバリエーションとして、n型導電性にドープされた多層構造21は、ドープされていない層またはサブ層、あるいは真性の層またはサブ層を備えていることもできる。この場合、ドープされていない層または真性の層は、n型導電多層構造21における堆積方向の電子の伝導性が十分に高いように、十分に薄いことが有利である。

## 【0073】

ドーピングピーク4,41の領域におけるドーピングプロファイルをできる限り方形とする目的で、堆積は、低い成長速度（例えば20nm/時～500nm/時の範囲内（両端値を含む）の速度）で行なうことが好ましい。

10

## 【0074】

さらには、n型導電多層構造の結晶構造は、V形状の凹部を備えていることが好ましく、V形状の凹部は、特に、低い堆積温度（例えば950以下）において、転位に沿って多数形成される。非導通方向に電圧が印加されたときの半導体チップの挙動を、これらのV形状の凹部によって改善することができる。

## 【0075】

図2は、半導体チップ1の第1の例示的な実施形態を示しており、半導体ボディ2は、一例として、図1Aに関連して説明した構造を有する。

## 【0076】

この実施形態においては、半導体チップ1は薄膜LED半導体チップの形をとり、半導体ボディ2の半導体積層体の成長基板29（図1A）は除去されている。活性領域20は、動作時にインコヒーレントな放射を生成するようにされている。

20

## 【0077】

半導体ボディ2は、キャリア5の上に配置されている。キャリア5は、特に、半導体ボディの機械的な安定性を高める役割を果たし、したがって、機械的な安定性のための成長基板は必要ない。

## 【0078】

キャリアの材料としては、半導体材料（例：シリコン、ガリウムヒ素、ゲルマニウム）、あるいはセラミック（例：窒化アルミニウム）が適している。

30

## 【0079】

キャリア5は、半導体ボディに、接合層8によって、機械的に安定的に導電接続されている。

## 【0080】

好適な接合層は、例えば、はんだ、または導電性接着剤である。

## 【0081】

ミラー層62は、キャリア5と半導体ボディ2との間に形成されている。半導体ボディ2の動作時、活性領域20において生成されてキャリア5の方向に放出される放射は、ミラー層によって放射出口面200の方向に反射され、半導体チップから放出される。

## 【0082】

半導体ボディ2は、キャリア5とは反対側の面に第1のコンタクト31を備えている。これとは反対側の半導体チップの面（すなわち半導体ボディ2とは反対側のキャリア5の面）には、第2のコンタクト32が形成されている。

40

## 【0083】

第1のコンタクトもしくは第2のコンタクトまたはその両方は、金属、例えば、金、銀、白金、アルミニウム、ニッケル、クロム、または銅、あるいはこれらの材料の少なくとも1種類との合金、を含んでいることが好ましい。

## 【0084】

半導体チップ1の動作時、第1のコンタクト31および第2のコンタクト32によって、異なる側から活性領域20に電荷キャリアを注入することができ、活性領域20内で電荷キャリアが再結合して放射が放出される。

50

## 【0085】

第1のコンタクト31を介して注入された電子は、n型導電多層構造21において少なくとも1つのドーピングピーク4の領域内で横方向に効果的に分散し、活性領域20の井戸層201に均一に取り込まれる。

## 【0086】

ミラー層62は、金属性であることが好ましく、活性領域において生成される放射に対して高い反射率を示すことがさらに好ましい。ミラー層に適する材料の例は、金属、例えば、アルミニウム、銀、金、パラジウム、またはロジウム、あるいはこれらの材料の少なくとも1種類との金属合金である。

## 【0087】

図3は、半導体チップ1の第2の例示的な実施形態を、概略的な断面図として示している。この場合も、半導体ボディ2は、図1Aに関連して説明した構造を有する。図2に関連して説明した第1の例示的な実施形態による半導体チップと異なる点として、半導体ボディ2は凹部24を備えており、この凹部24は、キャリア5の側の面から、p型導電半導体層22および活性領域20を通って、n型導電多層構造21に達している。この場合、凹部は、n型導電多層構造の井戸層211を貫通している。凹部の側面は絶縁層27によって覆われており、絶縁層27は、活性領域20の短絡から半導体ボディ2を保護する。

## 【0088】

凹部24の中にはコンタクト層65が形成されており、コンタクト層65は、p型導電半導体層22とは反対側の活性領域の面から、活性領域に電気的に接触する役割を果たす。

## 【0089】

キャリア5は、第1のランド51および第2のランド52を備えており、この場合、第1のランド51は、コンタクト層65を介してn型導電多層構造21に導電接続されており、第2のランド52は、ミラー層62を介してp型導電半導体層22に導電接続されている。第1のランド51および第2のランド52は、キャリア5の同じ面に配置されている。

## 【0090】

キャリア5とは反対側の活性領域20の面に配置されているn型導電多層構造21には、凹部24によって電気的に接触することができ、したがって、外部との電気コンタクトが放射出口面200に存在しないようにすることができる。これにより、放射透過性ではないコンタクトによって放射出口面が覆われることがない。

## 【0091】

キャリア5は開口部55を備えており、これらの開口部55は、半導体ボディ2の側のキャリアの第1の主面501から、この第1の主面とは反対側の第2の主面502に達している。これらの開口部によって、第1のランド51が第1のコンタクト31に導電接続されており、第2のランド52が第2のコンタクト32に導電接続されており、したがって、放射出口面200とは反対側の半導体チップの底面から、半導体チップ1に外部から電気的に接触することができる。

## 【0092】

さらには、半導体ボディ2は、放射出口面200の面にパターニング7を備えている。このパターニングは、半導体チップの中の活性領域において生成された放射の全反射を低減することで放射取り出し効率を高める役割を果たす。当然ながら、このようなパターニングは、図2に関連して説明した半導体チップの第1の例示的な実施形態においても設けることができる。

## 【0093】

図4は、逆電流Iの挙動を、逆方向（すなわち活性領域20の非導通方向）の電圧の関数として示している。曲線99は、半導体積層体（この積層体から以降の工程によって本発明の半導体チップの半導体ボディが得られる）における測定値を示している。半導体積

10

20

30

40

50

層体は、図1Bに関連して説明した構造を有する。

【0094】

これに対して、曲線98は、ドーピングピークを含んでいない従来のn型導電領域を使用した半導体積層体における測定値を示している。

【0095】

矢印97は、n型導電多層構造21の上述した構造によって電流プロファイルが変化する様子を示しており、すなわち、最初に低い電圧ではゆっくりと増大し、非常に高い電圧で急激に増大するようになる。測定曲線は、より強く湾曲したプロファイルを示している。

【0096】

本明細書では、例示的な実施形態について、LED半導体チップに基づいて説明したが、これは一例にすぎない。n型導電多層構造21の上述した構造と、少なくとも1つのドーピングピーク4を有する上述したドーピングプロファイルは、コヒーレントな放射、または少なくとも部分的にコヒーレントな放射を放出する部品（例えば、面発光型または端面発光型の半導体レーザチップや、RCLED（空洞共振型発光ダイオード））においても使用することができる。

【0097】

ここまで、本発明について例示的な実施形態に基づいて説明してきたが、本発明はこれらの実施形態に限定されない。本発明は、任意の新規の特徴および特徴の任意の組合せを包含しており、特に、請求項における特徴の任意の組合せを含んでいる。これらの特徴または特徴の組合せは、それ自体が請求項あるいは例示的な実施形態に明示的に記載されていない場合であっても、本発明に含まれる。

【0098】

関連出願

本特許出願は、独国特許出願第102009060747.1号の優先権を主張し、この文書の開示内容は参照によって本出願に組み込まれている。

【図1A】

【図2】

【図1B】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ペーター マティアス

ドイツ国 93055 レーゲンスブルク ディーベンブロックシュトラーセ 1

(72)発明者 マイヤー トビアス

ドイツ国 93346 イルラーシュタイン グロンンドルフ ヴェーク 25

(72)発明者 ワルター アレクサンダー

ドイツ国 93164 バーバー ヴァインベルクウェグ 9

(72)発明者 瀧 哲也

神奈川県横浜市港北区新羽町790

(72)発明者 オフ ユルゲン

ドイツ国 93059 レーゲンスブルク リーブルシュトラーセ 47

(72)発明者 ブーテンダイヒ ライナー

ドイツ国 93059 レーゲンスブルク セント - ヨーゼフ - シュトラーセ 10

(72)発明者 エルトコルン ヨアヒム

ドイツ国 93087 アルテグロフスハイム ビショフ - ケッテラー - シュトラーセ 21ア-

審査官 高椋 健司

(56)参考文献 米国特許出願公開第2008/0149918(US, A1)

特開2000-244013(JP, A)

特開平11-330554(JP, A)

特開平10-335757(JP, A)

特開平11-274644(JP, A)

国際公開第2009/106063(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64