(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication : 2 728 390

(à n'utiliser que pour les commandes de reproduction)

(21) N° d'enregistrement national : 94 15630

(51) Int Cl<sup>6</sup> : H 01 L 21/336, 21/324

**CETTE PAGE ANNULE ET REMPLACE LA PRECEDENTE**

(12) **DEMANDE DE BREVET D'INVENTION** A1

(22) Date de dépôt : 19.12.94.

(30) Priorité :

(71) Demandeur(s) : ELECTRONICS AND TELECOMMUNICATIONS RESEARCH INSTITUTE — KR.

(43) Date de la mise à disposition du public de la demande : 21.06.96 Bulletin 96/25.

(56) Liste des documents cités dans le rapport de recherche préliminaire : Se reporter à la fin du présent fascicule.

(60) Références à d'autres documents nationaux apparentés :

(72) Inventeur(s) : SONG YOON HO, PARK KYUNG HO et NAM KEE SOO.

(73) Titulaire(s) :

(74) Mandataire : CABINET MORELLE ET BARDOU.

(54) **PROCEDE DE FORMATION D'UN TRANSISTOR A FILM MINCE.**

(57) Procédé de formation d'un transistor à film mince qui peut être appliqué utilement à un affichage à cristaux liquides à matrice active à haute qualité d'image. En particulier, un procédé de formation d'un transition à film mince en polysilicium amélioré est décrit. Dans le procédé de formation d'un transistor à film mince en polysilicium, la cristallisation en phase solide de silicium non cristallin est effectuée sous atmosphère d'oxygène à haute pression et la durée de la cristallisation en phase solide de silicium non cristallin est donc raccourcie, de sorte à augmenter la productivité, et la taille des grains du polysilicium est rendue uniforme, de manière à améliorer les caractéristiques électriques du TFT (transistor à film mince).

FR 2 728 390 - A1

## PROCEDE DE FORMATION D'UN TRANSISTOR A FILM MINCE

La présente invention concerne un procédé de formation d'un transistor à film mince qui peut être appliqué utilement à un affichage à cristaux liquides à matrice active à haute qualité d'image. En particulier, la présente invention concerne un procédé de formation d'un transistor à film mince en polysilicium amélioré.

Généralement, le transistor à film mince en polysilicium est utilisé comme circuit intégré de pilotage de périphérique ou comme commutateur de pixels d'un panneau dans un affichage à cristaux liquides à matrice active à haute qualité d'image.

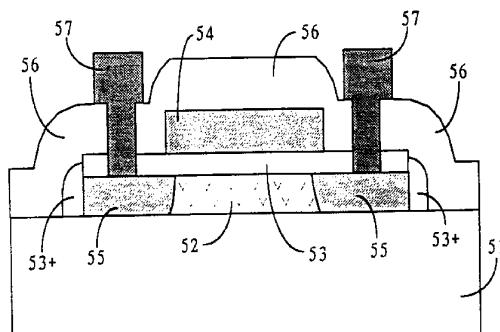

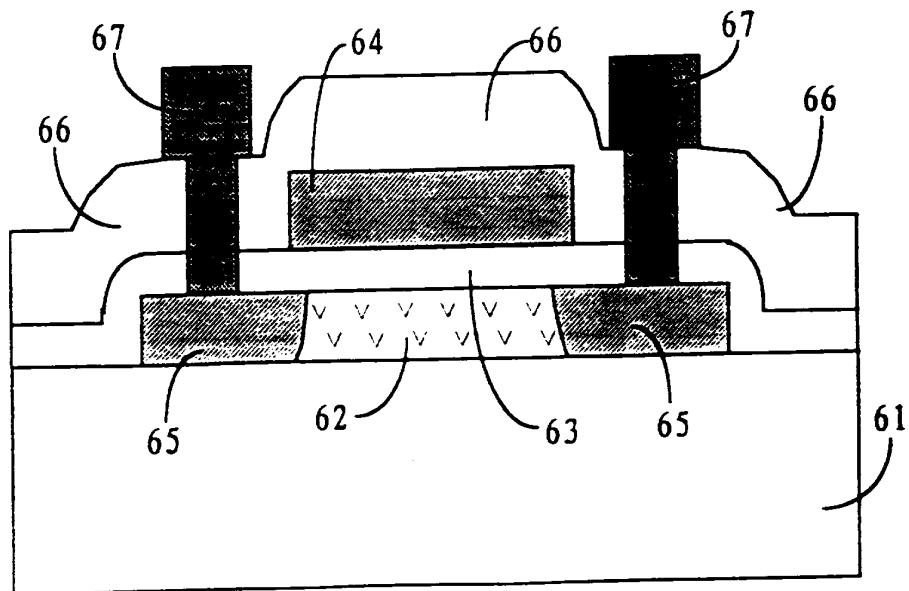

La figure 1 est une vue en coupe du transistor à film mince de polysilicium coplanaire du type général qui est fabriqué par la technique conventionnelle.

Ce transistor à film mince va être brièvement décrit en se référant à la figure 1.

Un gaz de SiH<sub>4</sub> ou Si<sub>2</sub>H<sub>6</sub> est d'abord utilisé pour déposer une couche de silicium non cristallin a-Si sur un substrat transparent 11 (composé de verre ou de quartz) en appliquant un procédé de dépôt chimique en phase vapeur amélioré par plasma (PECVD) ou en appliquant un procédé de dépôt chimique en phase vapeur à basse pression (LPCVD). Puis une cristallisation en phase solide ou en phase liquide est effectuée afin de former une couche de polysilicium.

Un procédé de photolithographie est alors appliqué pour former un motif sur la couche de polysilicium afin de définir une région de canal 12 et une région de source/drain.

La technique générale d'autoréglage est alors appliquée pour former une couche d'oxyde de grille 13, une électrode de grille 14, une source/drain 15, et une couche d'oxyde de protection 16, des électrodes métalliques 17,

formant de la sorte un transistor à film mince en polysilicium.

Dans le transistor à film mince coplanaire décrit ci-dessus, un courant de fuite pendant un état hors conduction 5 devient un problème.

Dans une tentative visant à surmonter le problème du courant de fuite, les techniques suivantes ont été proposées.

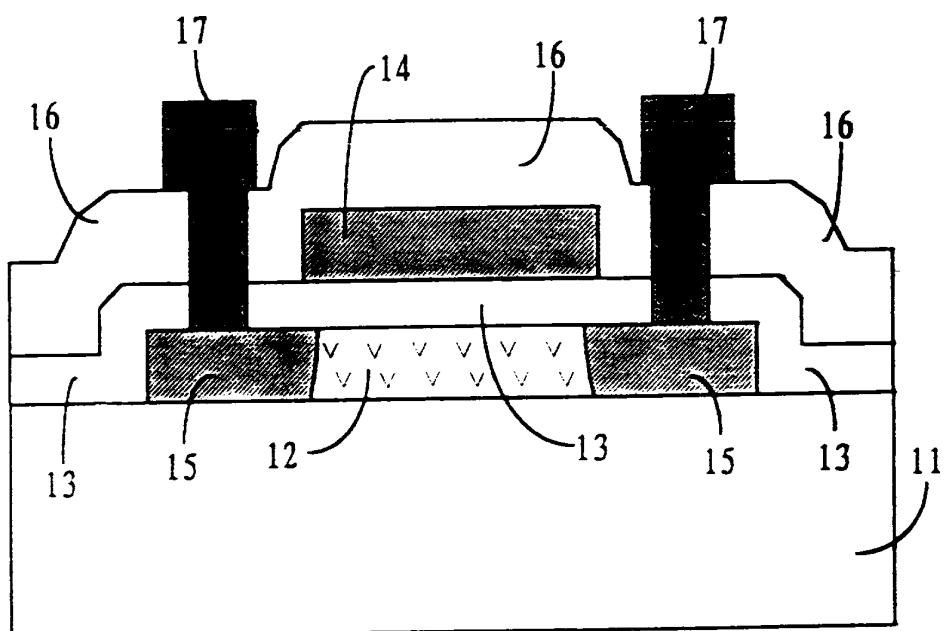

La figure 2 montre un transistor à film mince en 10 polysilicium de type à décalage, dans lequel une électrode 24 et une région 25 de source/drain ne se chevauchent pas verticalement.

Cette technique est décrite dans le brevet japonais Sho-60-251667.

15 Ce procédé est similaire à celui de la figure 1, mais un procédé de formation d'une région décalée est ajouté.

Dans le transistor à film mince de type à décalage décrit ci-dessus, de la région source/drain, seule la 20 région de drain peut être formée selon le type à décalage.

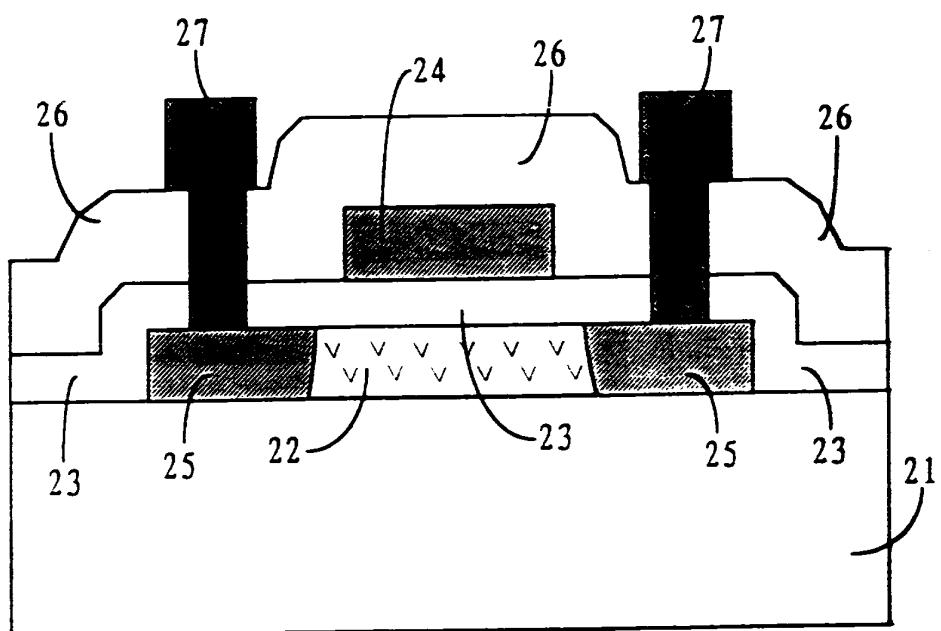

La figure 3 montre un transistor à film mince en 25 polysilicium dans lequel une région LDD (drain légèrement dopé) 35- est prévue sur un côté d'une région 35 de source/drain fortement dopée.

Cette technique a été proposée dans "Lightly Doped Drain TFT Structure for Poly-Si LCDs" par Nakazawa et al., (SID 90 Digest).

Cette technique est également similaire à celle de la 30 figure 1, sauf que le procédé de formation de la région LDD 35- est ajouté.

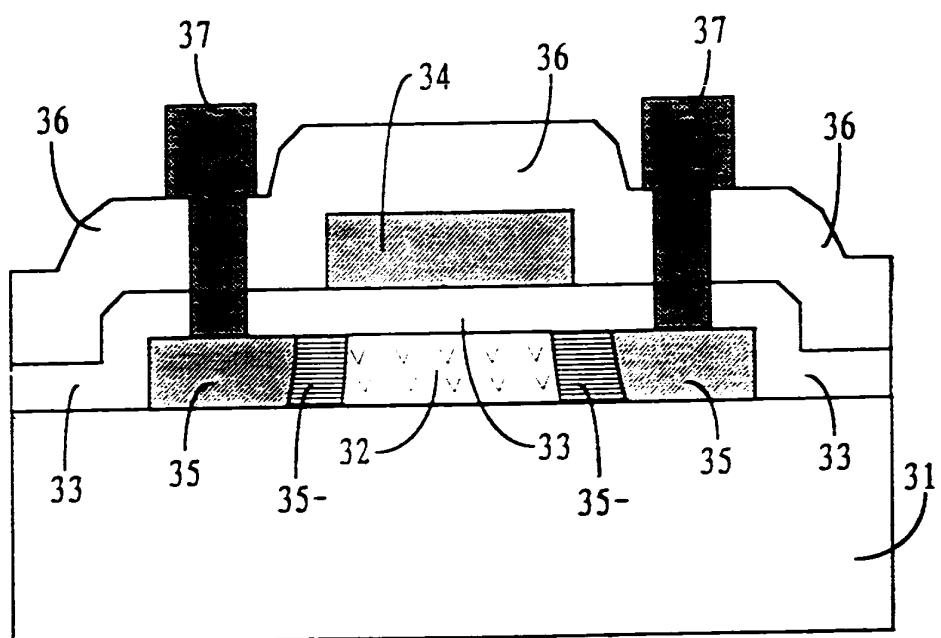

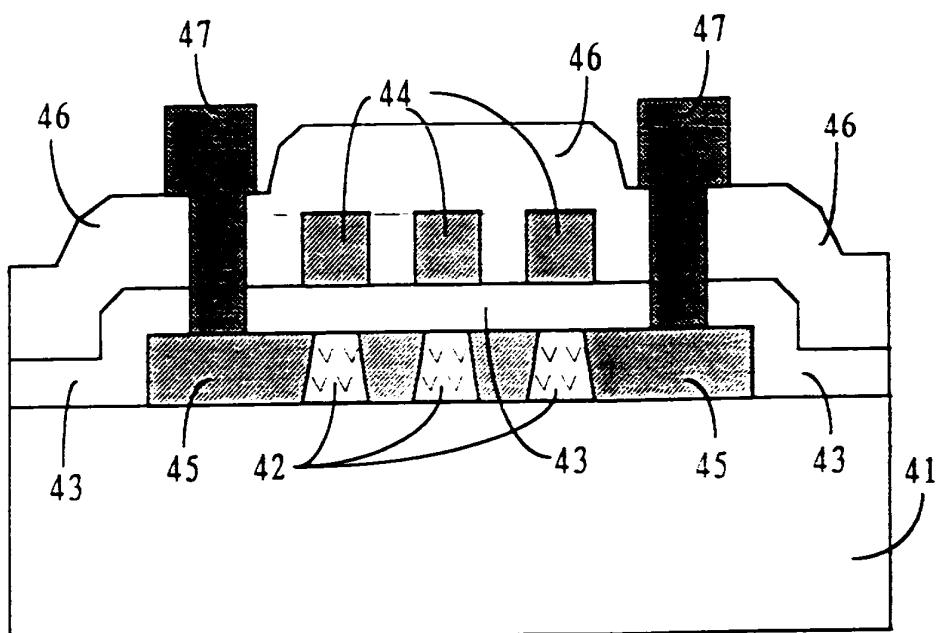

La figure 4 est une vue en coupe d'un transistor à 35 film mince en polysilicium dans lequel des électrodes 44 à grilles multiples sont prévues. Cette technique a été décrite dans "Development and Electrical Properties of Undoped Poly-Si TFTs" par Proano et al. (Proc. of SID, vol. 30/2).

Les différentes grilles sont reliées électriquement entre elles.

Dans ce procédé, si seul le masque de formation d'électrode de grille est remplacé, alors il peut être 5 fabriqué de la même manière que celui de la figure 1.

Dans les divers transistors à film mince en polysilicium décrits ci-dessus, les caractéristiques électriques sont déterminées par les états des joints entre les couches 13, 23, 33 et 43 d'oxyde de grille et les 10 couches 12, 22, 32 et 42 de polysilicium, qui sont des régions de canal.

De plus, des phénomènes désavantageux apparaissent fondamentalement au cours de la formation de la couche de polysilicium.

15 Comme décrit ci-dessus, dans le transistor à film mince, la couche de polysilicium est formée par cristallisation de silicium non cristallin.

Le silicium non cristallin est fabriqué par dépôt de type LPCVD ou PECVD à une température inférieure à 580°C. 20 Il peut également être fabriqué de telle manière qu'un polysilicium fabriqué par dépôt à une température de plus de 600°C soit converti en une forme non cristalline par un procédé d'auto-implantation ionique de Si.

25 Le procédé de cristallisation comprend: une cristallisation en phase solide basée sur un recuit en étuve ou un recuit thermique rapide; et une cristallisation en phase liquide basée sur un recuit par laser.

C'est-à-dire que, dans le procédé de formation conventionnel, la couche de polysilicium, qui est une 30 couche active, est principalement formée de la manière suivante. On applique un procédé de cristallisation en phase solide dans lequel du silicium non cristallin est traité thermiquement pendant plus de 20 heures au-dessous de la pression normale sous une atmosphère de gaz inerte.

35 Le polysilicium qui est fabriqué de cette manière a

des grains de très grande taille, mais il présente l'inconvénient que des défauts sont fréquents à l'intérieur de tels grains, et que le traitement thermique de recristallisation dure trop longtemps.

5 La longueur de la durée de cristallisation entraîne que les durées de germination et de croissance granulaire deviennent variées. En conséquence, les tailles des grains du polysilicium finalement obtenues sont très peu uniformes.

10 Les caractéristiques des joints entre la couche de polysilicium et la couche d'oxyde de grille sont donc dégradées.

15 En conséquence, dans le cas où un transistor à film mince est fabriqué en utilisant le polysilicium basé sur les procédés décrits ci-dessus, la productivité devient faible, les caractéristiques électriques du transistor sont dégradées, et un obstacle est rencontré sur la voie de la réalisation d'un transistor à film mince de haute densité.

20 La présente invention vise à surmonter les désavantages des techniques conventionnelles décrits ci-dessus.

25 L'objectif de la présente invention est donc de fournir un procédé de formation d'un transistor à film mince en polysilicium, dans lequel la durée de cristallisation en phase solide pour un silicium non cristallin est raccourcie afin d'améliorer la productivité, et la taille des grains du polysilicium est rendue plus uniforme afin d'améliorer les caractéristiques électriques du TFT (transistor à film mince).

30 Pour atteindre l'objectif ci-dessus, un premier mode de réalisation du procédé selon la présente invention comprend les étapes consistant à:

- a) déposer une couche de silicium non cristallin intrinsèque sur un substrat isolant transparent;

- 35 b) traiter thermiquement la couche de silicium non

cristallin sous une atmosphère d'oxygène ( $O_2$ ) sous pression élevée dans un four électrique, afin de procéder à une cristallisation en phase solide et à une oxydation pour former une bonne couche de polysilicium et une couche d'oxyde;

5 c) former un motif sur la couche de polysilicium et la couche d'oxyde pour définir une couche d'oxyde de grille et une région active du transistor;

10 d) former des couches d'oxyde de paroi latérale sur les parois latérales de la couche d'oxyde de grille et sur les parois latérales de la couche de polysilicium de la région active définie ci-dessus;

15 e) former une électrode de grille en un emplacement approprié de la couche d'oxyde de grille, et procéder à une implantation ionique en utilisant l'électrode de grille comme masque pour former une région de source/drain sur la région active; et

f) effectuer une métallisation pour former des électrodes métalliques.

20 Dans un autre aspect de la présente invention, un deuxième mode de réalisation du procédé de formation d'un transistor à film mince en polysilicium selon la présente invention comprend les étapes consistant à:

25 a) déposer une couche de silicium non cristallin intrinsèque sur un substrat isolant transparent;

b) traiter thermiquement la couche de silicium non cristallin sous une atmosphère d'oxygène ( $O_2$ ) sous pression élevée dans un four électrique, afin de procéder à une cristallisation en phase solide et à une oxydation pour former une bonne couche de polysilicium et une couche d'oxyde;

30 c) former un motif sur la couche de polysilicium et la couche d'oxyde pour définir une région active du transistor, puis éliminer la couche d'oxyde;

d) déposer une couche d'oxyde de grille sur toute la

surface du substrat sur laquelle la région active est définie;

5 e) former une électrode de grille en un emplacement approprié de la couche d'oxyde de grille, et procéder à une implantation ionique en utilisant l'électrode de grille comme masque pour former une région de source/drain sur la région active; et

f) effectuer une métallisation pour former des électrodes métalliques.

10 Selon la présente invention, la durée du procédé de formation est raccourcie, de sorte que la productivité sera améliorée. De plus, la taille des grains est rendue plus uniforme, de sorte qu'un meilleur polysilicium peut être obtenu.

15 En particulier, selon le premier mode de réalisation de la présente invention, la couche d'isolation de grille est formée par croissance par oxydation thermique du silicium non cristallin et, ainsi, la propriété d'isolation et les caractéristiques des joints du polysilicium sont 20 améliorées.

Selon le deuxième mode de réalisation de la présente invention, la limitation d'épaisseur de la couche d'isolation de grille est éliminée, de sorte que la couche d'isolation de grille peut être utilisée pour une tension 25 élevée.

L'objectif ci-dessus et d'autres avantages de la présente invention apparaîtront plus clairement en décrivant en détail le mode de réalisation préféré de la présente invention en se référant aux dessins annexés, dans 30 lesquels:

La figure 1 est une vue en coupe du transistor à film mince en polysilicium coplanaire général;

La figure 2 est une vue en coupe du transistor à film mince en polysilicium conventionnel du type à décalage;

35 La figure 3 est une vue en coupe d'un transistor à

film mince en polysilicium ayant la région LDD conventionnelle;

La figure 4 est une vue en coupe d'un transistor à film mince en polysilicium ayant les grilles multiples 5 conventionnelles;

Les figures 5a à 5f sont des vues en coupe montrant le procédé de formation du premier mode de réalisation du transistor à film mince en polysilicium selon la présente invention;

10 Les figures 6a à 6f sont des vues en coupe montrant le procédé de formation du deuxième mode de réalisation du transistor à film mince en polysilicium selon la présente invention;

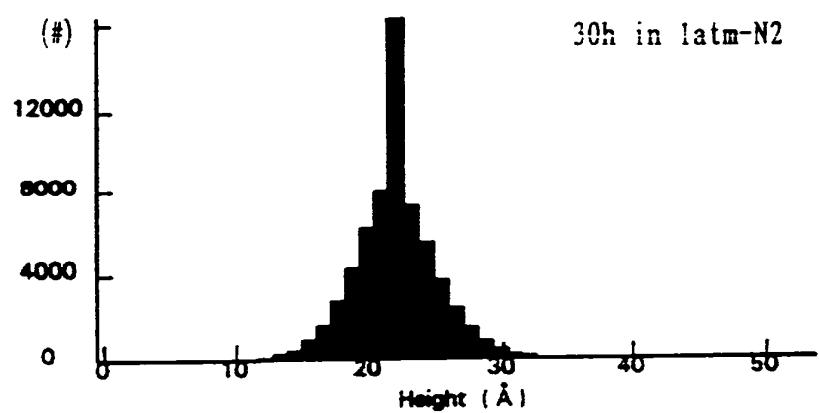

15 La figure 7a est un histogramme montrant la distribution de hauteur des irrégularités de la surface du polysilicium qui est formé selon un procédé conventionnel; et

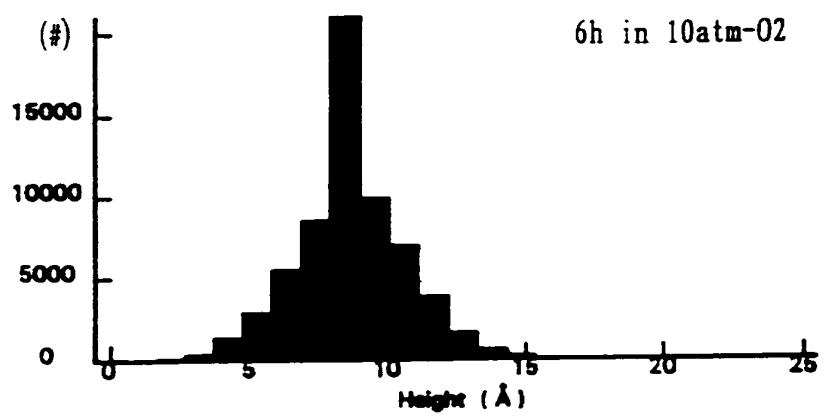

20 La figure 7b est un histogramme montrant la distribution de hauteur des irrégularités de la surface du polysilicium qui est formé selon la présente invention.

La figure 5 montre le procédé de formation d'un premier mode de réalisation du transistor à film mince au polysilicium selon la présente invention, et la figure 6 montre le procédé de formation d'un deuxième mode de 25 réalisation du transistor à film mince au polysilicium selon la présente invention.

Pour faciliter la description, les mêmes éléments dans l'art antérieur et dans différents modes de réalisation de la présente invention sont référencés avec des codes de référence dans lesquels le dernier chiffre est le même. De plus, des descriptions des parties se chevauchant sont 30 omises.

Le premier mode de réalisation de la présente invention va maintenant être décrit en se référant aux 35 figures 5a à 5f.

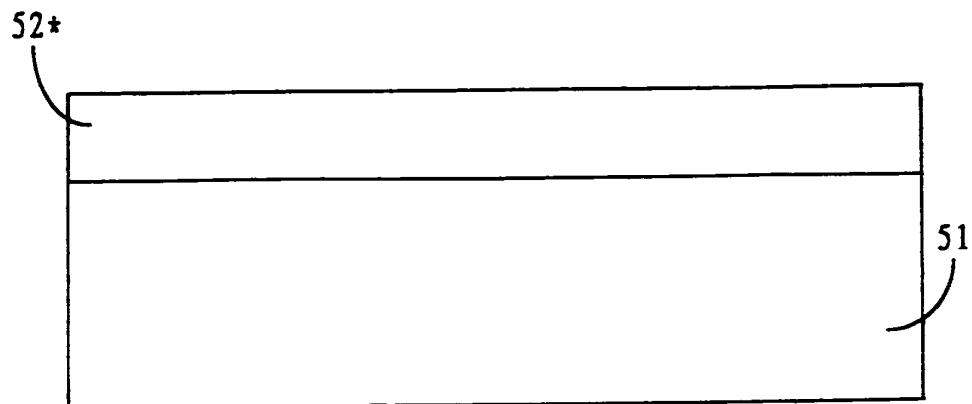

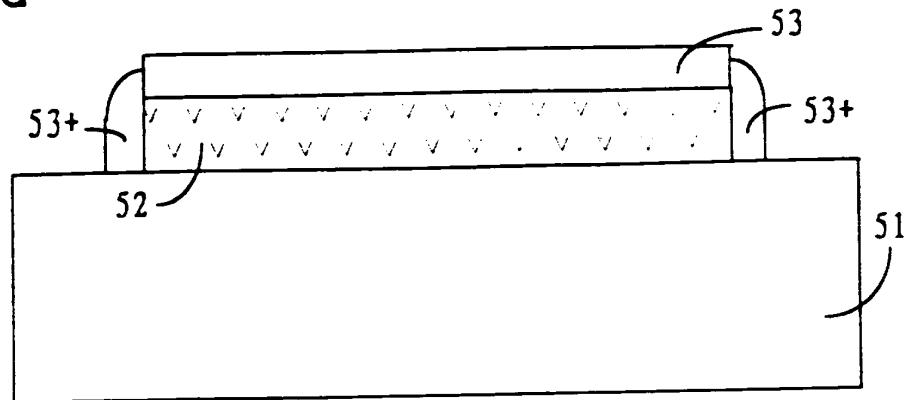

Se référant à la figure 5a, une première étape consiste à déposer une couche 52\* de silicium non cristallin intrinsèque sur un substrat isolant transparent 51.

5 Le substrat isolant transparent est composé de verre ou de quartz.

La couche 52\* de silicium non cristallin est formée avec une épaisseur de 200 - 1500 Å en utilisant un gaz de SiH<sub>4</sub> ou de Si<sub>2</sub>H<sub>6</sub> et en appliquant un procédé de LPCVD ou de PECVD.

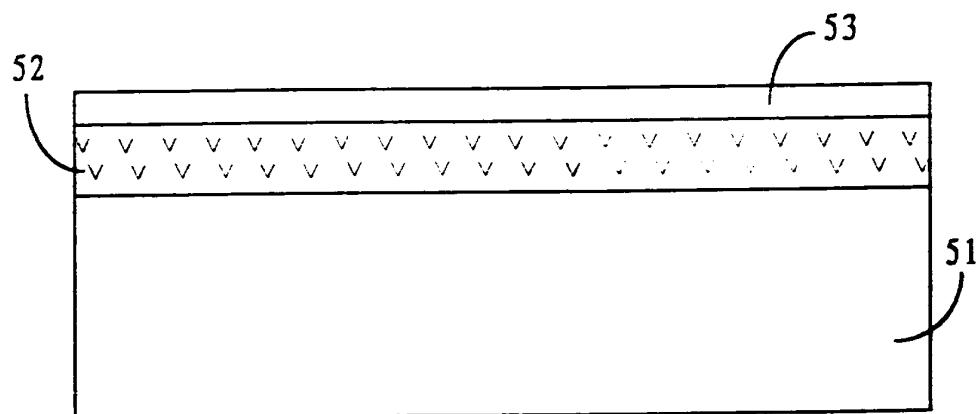

10 Une deuxième étape consiste à traiter thermiquement la couche 52\* de silicium non cristallin à une pression élevée sous atmosphère d'oxygène dans un four électrique, de manière à former une couche de polysilicium 52 et une 15 couche d'oxyde 53.

15 Comme le montre la figure 5b, le silicium non cristallin est soumis à une cristallisation en phase solide et à une oxydation en l'oxydant de manière continue à une température de moins de 600°C à une pression supérieure à 20 la normale, par exemple 100 atm sous atmosphère de O<sub>2</sub> dans un four électrique, formant ainsi une couche 52 de polysilicium et une couche 53 d'oxyde de grille.

25 La couche 53 d'oxyde de grille qui est formée de la manière décrite ci-dessus présente des propriétés d'isolation supérieures, et son épaisseur peut être contrôlée à un grand niveau de minceur. Cependant, son utilisation est interdite pour une tension élevée, pour laquelle une épaisseur de plus de 500 Å est requise.

30 Comme le montre la figure 5c, une troisième étape consiste à former un motif sur la couche de polysilicium 52 et la couche d'oxyde 53 en appliquant un procédé de photolithographie, et ainsi une région active du TFT est définie.

35 Comme le montre la figure 5d, une quatrième étape consiste à former des couches d'oxyde 53<sup>+</sup> de paroi latérale

sur les parois latérales de la couche 53 d'oxyde de grille et sur les parois latérales de la couche de polysilicium 52, sur lesquelles un motif a été formé de la manière décrite ci-dessus.

5 La couche 53<sup>+</sup> d'oxyde de paroi latérale est formée par un procédé d'oxydation sous pression élevée à une température de 600 °C.

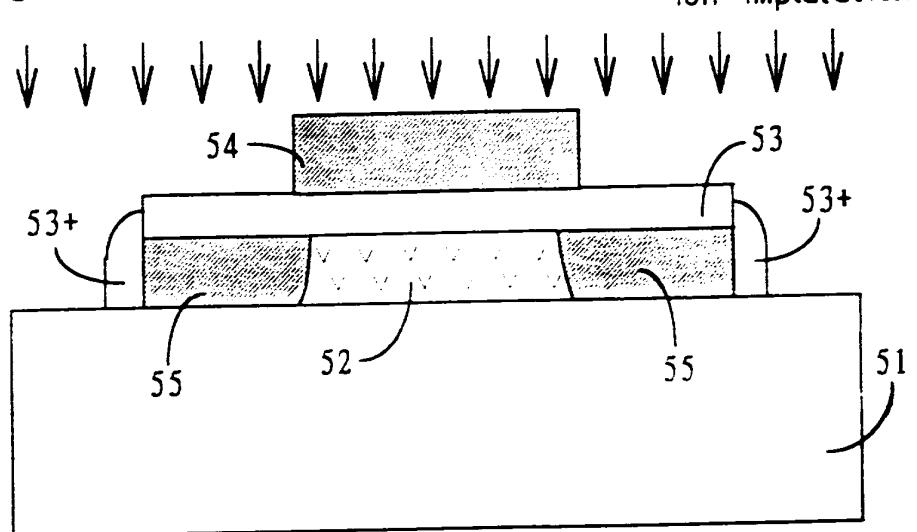

Une cinquième étape consiste à former une région de grille et une région de source/drain.

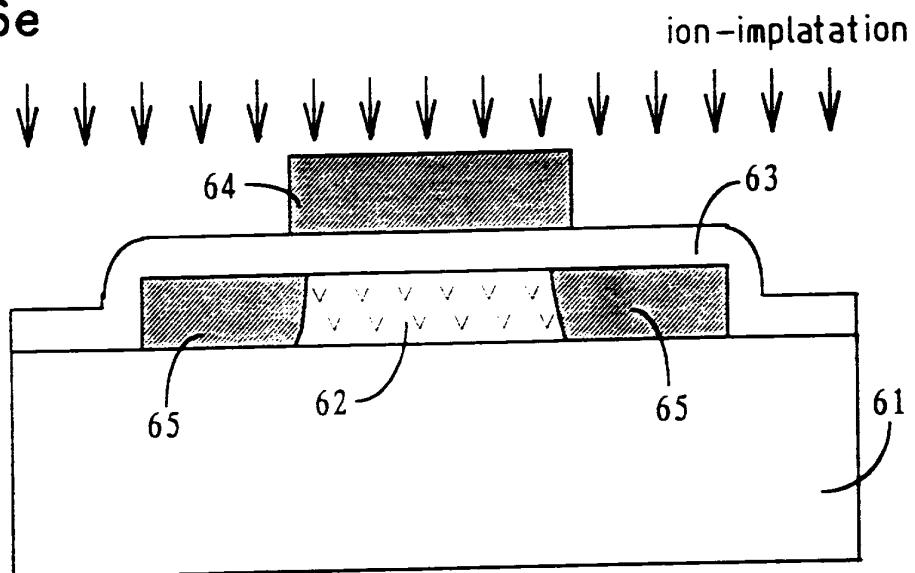

10 Comme le montre la figure 5e, une couche de polysilicium est débord déposée avec une épaisseur de 1000 - 3000 Å sur la couche 53 d'oxyde de grille et sur la couche 53<sup>+</sup> d'oxyde de paroi latérale, et un procédé de photolithographie est appliqué pour former une électrode de grille 54.

15 Alors, en utilisant l'électrode de grille 54 comme masque, une impureté de dopage est implantée par méthode ionique de manière à former une région 55 de source/drain.

20 Comme impureté de dopage, des ions As ou P sont implantés par méthode ionique avec une concentration de plus de  $5 \times 10^{14}$  ions/cm<sup>2</sup> dans le cas d'un TFT à canal n, alors que des ions B ou BF<sub>2</sub> sont implantés par méthode ionique avec une concentration de plus de  $5 \times 10^{14}$  ions/cm<sup>2</sup> dans le cas d'un TFT à canal p.

25 La cinquième étape, dans laquelle la grille et la source/drain sont formées, peut être effectuée de diverses manières.

30 On va d'abord décrire le cas dans lequel un TFT de type à décalage (se reporter à la figure 2) est formé, dans lequel l'électrode de grille 54 et la région de source/drain 55 ne se chevauchent pas. Dans ce cas, l'électrode de grille 54 n'est pas utilisée comme masque. A la place, un masque qui est plus grand que la largeur du motif de l'électrode de grille et qui est préparé en tenant 35 particulièrement compte de la région de diffusion latérale

pendant l'implantation ionique est utilisé pour effectuer l'implantation ionique.

Dans le cas du TFT à structure LDD de la figure 3, un masque correspondant à la région LDD est utilisé pour 5 effectuer l'implantation ionique.

Si une électrode à grilles multiples doit être formée, un masque correspondant au motif à grilles multiples est utilisé.

Enfin, comme le montre la figure 5f, une étape de 10 métallisation est effectuée pour former des électrodes métalliques 57, afin de terminer la formation du TFT.

Un procédé de dépôt chimique en phase vapeur est d'abord utilisé pour déposer une couche protectrice 56 d'une épaisseur de 3000 - 7000 Å, puis un procédé de 15 photolithographie est appliqué pour former un orifice de contact.

Un métal tel que l'aluminium est alors déposé dans l'orifice de contact pour former une électrode métallique 57, ce qui termine la formation du TFT.

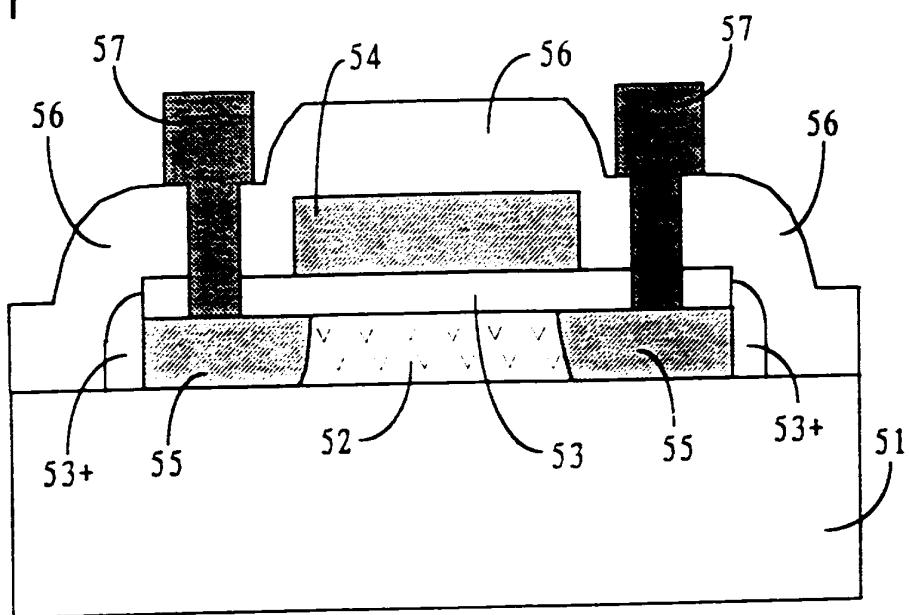

Le deuxième mode de réalisation de la présente 20 invention va maintenant être décrit en se référant aux figures 6a à 6f.

Le deuxième mode de réalisation de la présente 25 invention diffère du premier mode de réalisation en ce qu'une oxydation thermique est utilisée pour former la couche d'oxyde de grille, de sorte que les propriétés d'isolation seront supérieures et l'épaisseur peut être contrôlée à un grand niveau de minceur.

Dans le deuxième mode de réalisation, un procédé de 30 dépôt est appliqué pour former une couche d'oxyde de grille, de sorte qu'elle peut être utilisée pour un TFT à haute tension.

De plus, l'étape de formation de la couche 53<sup>t</sup> d'oxyde de paroi latérale (figure 5d) est supprimée.

Les première et deuxième étapes du deuxième mode de 35

réalisation (figures 6a et 6b) sont les mêmes que les première et deuxième étapes du premier mode de réalisation.

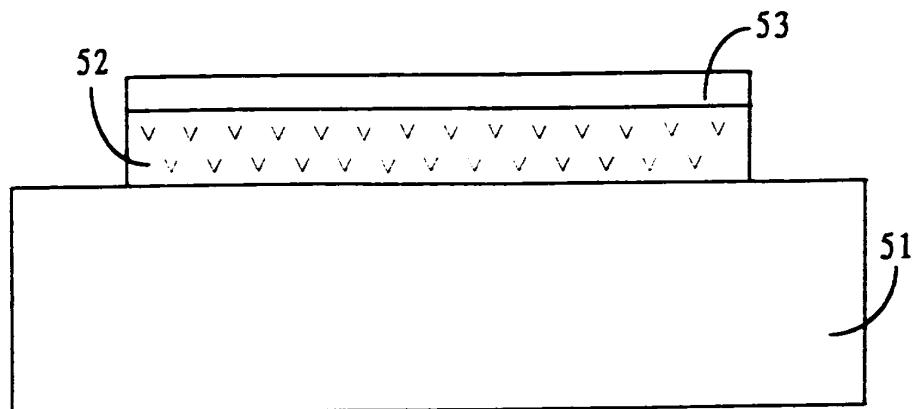

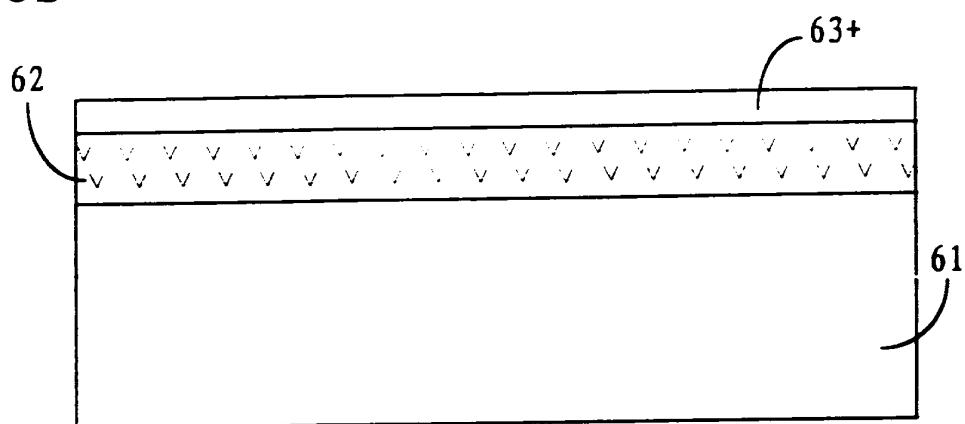

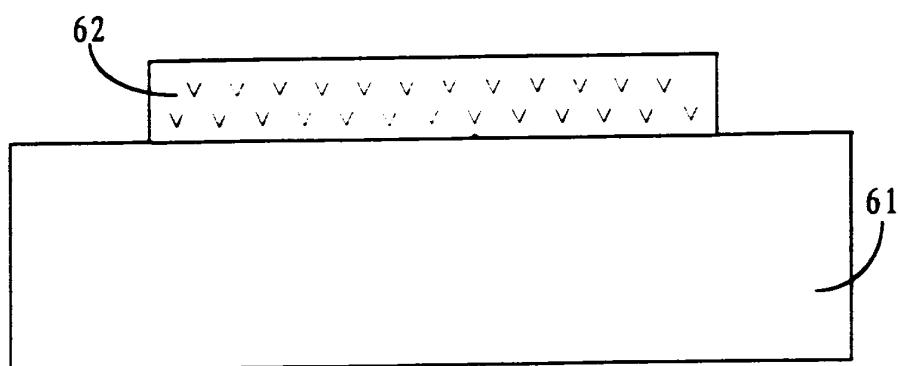

Une troisième étape, montrée sur la figure 6c, est effectuée de la manière suivante. Un procédé de 5 photolithographie est appliqué pour former un motif sur une couche de polysilicium 62 et une couche d'oxyde 63<sup>+</sup>. Une région active est ainsi définie, puis la couche d'oxyde mince 63<sup>+</sup> est éliminée par un procédé de gravure humide.

10 L'agent de gravure qui est souhaitable pour éliminer la couche d'oxyde 63<sup>+</sup> est l'acide fluorhydrique.

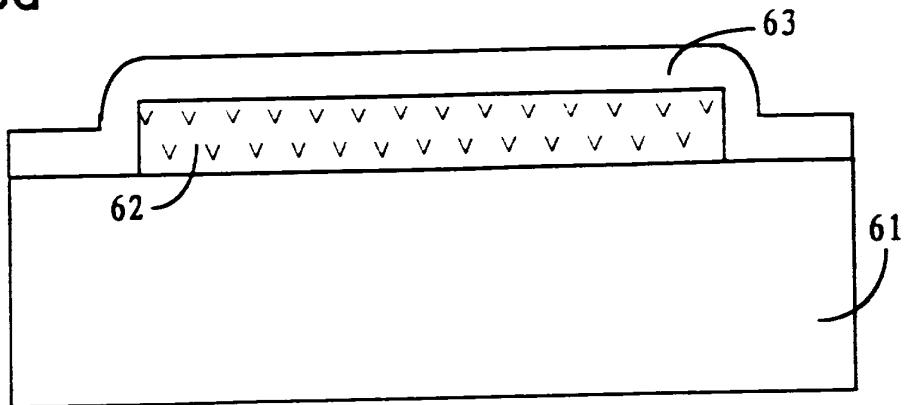

Comme le montre la figure 6d, une quatrième étape consiste à déposer une couche 63 d'oxyde de grille sur toute la surface d'un substrat 61 dans lequel une région active a été définie.

15 L'épaisseur de la couche 63 d'oxyde de grille déposée doit de préférence être comprise entre 100 et 1000 Å, mais il n'y a aucune limite, puisque le procédé de dépôt est utilisé.

20 Les étapes consistant à former une électrode de grille 64 et une région de source/drain 65 sont les mêmes que celles du premier mode de réalisation, l'étape de métallisation pour former des électrodes métalliques 67 étant également la même que celle du premier mode de réalisation.

25 Comme dans le premier mode de réalisation, l'électrode de grille 64 peut être formée selon une structure à grilles multiples, et les structures à décalage et LDD sont également possibles.

30 Selon la présente invention, comme décrit précédemment, afin de former le film de polysilicium qui est la région de canal du transistor à film mince, une cristallisation en phase solide de silicium non cristallin est effectuée sous une atmosphère d'oxygène à haute pression. Ainsi, la germination et le processus de 35 formation des grains sont effectués en une brève période de

5 temps, de sorte que la durée globale de cristallisation en phase solide et la durée de traitement thermique sont raccourcies. En conséquence, une région de canal peut être obtenue, qui est composée d'un polysilicium ayant une distribution uniforme des tailles de grain.

Les effets de la présente invention apparaissent clairement en se référant aux figures 7a et 7b.

10 Les figures 7a et 7b sont des histogrammes montrant les irrégularités de surface des polysilicium qui sont soumis à la cristallisation en phase solide sur la base du procédé conventionnel et sur la base du procédé selon la présente invention, respectivement, la surface étant observée avec un microscope de puissance atomique.

15 Dans le cas du traitement thermique du procédé conventionnel (30 heures dans N<sub>2</sub> à 1 atm), les irrégularités de surface atteignent jusqu'à 20 Å, comme le montre la figure 7a, ce qui représente une valeur élevée.

20 D'autre part, selon la présente invention, la couche d'oxyde est éliminée en utilisant de l'acide fluorhydrique (HF), puis, lorsque la surface du polysilicium était observée, la valeur moyenne des irrégularités de surface ne dépassait pas 10 Å, comme le montre la figure 7b.

25 Ainsi, selon la présente invention, on peut obtenir une couche de polysilicium dans laquelle la planéité est supérieure, et un TFT à hautes performances peut être fabriqué en utilisant le film mince comme région active.

REVENDICATIONS

1. Procédé de formation d'un transistor à film mince en polysilicium, comprenant les étapes consistant à:

- 5 a) déposer une couche de silicium non cristallin intrinsèque sur un substrat isolant transparent;

- b) traiter thermiquement la couche de silicium non cristallin sous une atmosphère d'oxygène ( $O_2$ ) sous pression élevée dans un four électrique, afin de procéder à une 10 cristallisation en phase solide et à une oxydation pour former une bonne couche de polysilicium et une couche d'oxyde;

- c) former un motif sur la couche de polysilicium et la 15 couche d'oxyde pour définir une couche d'oxyde de grille et une région active du transistor;

- d) former des couches d'oxyde de paroi latérale sur les parois latérales de la couche d'oxyde de grille et sur les parois latérales de la couche de polysilicium de la région active définie ci-dessus;

- 20 e) former une électrode de grille en un emplacement approprié de la couche d'oxyde de grille, et procéder à une implantation ionique en utilisant l'électrode de grille comme masque pour former une région de source/drain sur la région active; et

- 25 f) effectuer une métallisation pour former des électrodes métalliques.

2. Procédé selon la revendication 1, dans lequel ledit substrat isolant transparent de l'étape (a) est composé de verre ou de quartz.

- 30 3. Procédé selon la revendication 1, dans lequel la pression de l'atmosphère d'oxygène pour le traitement thermique lors de la cristallisation en phase solide est contrôlée à 1 - 100 atm.

- 35 4. Procédé selon la revendication 1, dans lequel la température de traitement thermique pour la cristallisation

en phase solide de l'étape (b) est de 600°C.

5. Procédé selon la revendication 1, dans lequel ladite couche d'oxyde de paroi latérale de l'étape (d) est formée en appliquant une oxydation sous haute pression à une température de moins de 600°C.

10. Procédé selon la revendication 1, dans lequel ladite région de source/drain de l'étape (e) est formée selon une structure à décalage en utilisant un masque plus grand que la largeur du motif de l'électrode de grille (en tenant compte de la diffusion latérale du dopant).

15. Procédé selon la revendication 1, dans lequel l'étape (e) comprend de plus une sous-étape consistant à former une région LDD (drain légèrement dopé) dans ladite région active en effectuant une implantation ionique en utilisant un masque séparé.

8. Procédé selon la revendication 1, dans lequel ladite électrode de grille de l'étape (e) est formée sous la forme d'une électrode à grilles multiples.

20. Procédé de formation d'un transistor à film mince en polysilicium, comprenant les étapes consistant à:

a) déposer une couche de silicium non cristallin intrinsèque sur un substrat isolant transparent;

25 b) traiter thermiquement la couche de silicium non cristallin sous une atmosphère d'oxygène ( $O_2$ ) sous pression élevée dans un four électrique, afin de procéder à une cristallisation en phase solide et à une oxydation pour former une bonne couche de polysilicium et une couche d'oxyde;

30 c) former un motif sur la couche de polysilicium et la couche d'oxyde pour définir une région active du transistor, puis éliminer la couche d'oxyde;

d) déposer une couche d'oxyde de grille sur toute la surface du substrat sur laquelle la région active est définie;

35 e) former une électrode de grille en un emplacement

approprié de la couche d'oxyde de grille, et procéder à une implantation ionique en utilisant l'électrode de grille comme masque pour former une région de source/drain sur la région active; et

5 f) effectuer une métallisation pour former des électrodes métalliques.

10 10. Procédé selon la revendication 9, dans lequel ladite couche d'oxyde de l'étape (c) est éliminée par un procédé de gravure humide utilisant de l'acide fluorhydrique.

15 11. Procédé selon la revendication 9, dans lequel ladite région de source/drain de l'étape (e) est formée selon une structure à décalage en utilisant un masque plus grand que la largeur du motif de l'électrode de grille (en tenant compte de la diffusion latérale du dopant).

20 12. Procédé selon la revendication 9, dans lequel l'étape (e) comprend de plus une sous-étape consistant à former une région LDD (drain légèrement dopé) dans ladite région active en effectuant une implantation ionique en utilisant un masque séparé.

13. Procédé selon la revendication 9, dans lequel ladite électrode de grille de l'étape (e) est formée sous la forme d'une électrode à grilles multiples.

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5a

FIG.5b

FIG.5c

FIG.5d

FIG.5e

FIG.5f

**FIG.6a****FIG.6b****FIG.6c**

FIG.6d

FIG.6e

FIG.6f

FIG.7a

FIG.7b

INSTITUT NATIONAL

de la

PROPRIÉTÉ INDUSTRIELLE

RAPPORT DE RECHERCHE

PRÉLIMINAIRE

établi sur la base des dernières revendications

déposées avant le commencement de la recherche

N° d'enregistrement

national

FA 510282

FR 9415630

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                         | Revendications concernées de la demande examinée                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie                                                                                                                                                                                                                                                                                          | Citation du document avec indication, en cas de besoin, des parties pertinentes                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                     |

| Y                                                                                                                                                                                                                                                                                                  | US-A-4 597 160 (IPRI ALFRED C) 1 Juillet 1986<br>* colonne 1, ligne 60 - colonne 3, ligne 4; figures 1-4 *<br>---                                                                                                                                                                       | 1,2,9,10                                                                                                                                                                                                                                                                                                                            |

| Y                                                                                                                                                                                                                                                                                                  | EP-A-0 457 596 (SHARP KK) 21 Novembre 1991<br>* colonne 3, ligne 36 - colonne 5, ligne 5; figures 6-8 *<br>---                                                                                                                                                                          | 1,2                                                                                                                                                                                                                                                                                                                                 |

| Y                                                                                                                                                                                                                                                                                                  | US-A-4 868 140 (YONEHARA TAKAO) 19 Septembre 1989<br>* colonne 4, ligne 35 - ligne 68; figure 3 *<br>---                                                                                                                                                                                | 9,10                                                                                                                                                                                                                                                                                                                                |

| A                                                                                                                                                                                                                                                                                                  | IEEE ELECTRON DEVICE LETTERS,<br>vol. 12, no. 7, 1 Juillet 1991<br>pages 390-392, XP 000207954<br>MITRA U 'LOW-TEMPERATURE POLYSILICON TFT<br>WITH GATE OXIDE GROWN BY HIGH-PRESSURE<br>OXIDATION'<br>* page 390, colonne de droite - page 391,<br>colonne de gauche; figure 1 *<br>--- | 1-4,9                                                                                                                                                                                                                                                                                                                               |

| A                                                                                                                                                                                                                                                                                                  | PATENT ABSTRACTS OF JAPAN<br>vol. 014 no. 166 (E-0911) ,30 Mars 1990<br>& JP-A-02 021663 (SHARP CORP) 24 Janvier 1990,<br>* abrégé; figures 1-4 *<br>---                                                                                                                                | 1-4,9                                                                                                                                                                                                                                                                                                                               |

| A                                                                                                                                                                                                                                                                                                  | EP-A-0 588 487 (AMERICAN TELEPHONE & TELEGRAPH) 23 Mars 1994<br>* colonne 3, ligne 41 - colonne 5, ligne 11; figure 1 *<br>---                                                                                                                                                          | 1-4,9                                                                                                                                                                                                                                                                                                                               |

| A                                                                                                                                                                                                                                                                                                  | EP-A-0 307 021 (PHILIPS NV) 15 Mars 1989<br>* colonne 4, ligne 50 - ligne 56 *<br>---                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                         | -/-                                                                                                                                                                                                                                                                                                                                 |

| 1                                                                                                                                                                                                                                                                                                  | Date d'achèvement de la recherche<br><br>19 Septembre 1995                                                                                                                                                                                                                              | Examinateur<br><br>Gélébart, J                                                                                                                                                                                                                                                                                                      |

| CATÉGORIE DES DOCUMENTS CITÉS                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                         | T : théorie ou principe à la base de l'invention<br>E : document de brevet bénéficiant d'une date antérieure à la date de dépôt et qui n'a été publié qu'à cette date de dépôt ou qu'à une date postérieure.<br>D : cité dans la demande<br>L : cité pour d'autres raisons<br>& : membre de la même famille, document correspondant |

| X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : pertinent à l'encontre d'au moins une revendication ou arrière-plan technologique général<br>O : divulgation non écrite<br>P : document intercalaire |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                     |

RAPPORT DE RECHERCHE

PRELIMINAIRE

N° d'enregistrement

nationalétabli sur la base des dernières revendications

déposées avant le commencement de la rechercheFA 510282

FR 9415630

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                                                                                                                                                                                                                                                                      |                                                                                    | Revendications concernées de la demande examinée                                                                                                                                                                                                                                                                                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Catégorie                                                                                                                                                                                                                                                                                                                                  | Citation du document avec indication, en cas de besoin, des parties pertinentes    |                                                                                                                                                                                                                                                                                                                                     |  |

| A                                                                                                                                                                                                                                                                                                                                          | EP-A-0 513 590 (SEIKO EPSON CORP) 19 Novembre 1992<br>* abrégé; figure 1 *<br>---- | 6,11                                                                                                                                                                                                                                                                                                                                |  |

| A                                                                                                                                                                                                                                                                                                                                          | EP-A-0 589 478 (SONY CORP) 30 Mars 1994<br>* figures 1,12,13 *<br>-----            | 7,8,12,<br>13                                                                                                                                                                                                                                                                                                                       |  |

| DOMAINES TECHNIQUES<br>RECHERCHES (Int.Cl.6)                                                                                                                                                                                                                                                                                               |                                                                                    |                                                                                                                                                                                                                                                                                                                                     |  |

| 1                                                                                                                                                                                                                                                                                                                                          | Date d'achèvement de la recherche                                                  | Examinateur                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                            | 19 Septembre 1995                                                                  | Gélébart, J                                                                                                                                                                                                                                                                                                                         |  |

| <b>CATEGORIE DES DOCUMENTS CITES</b><br>X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : pertinent à l'encontre d'au moins une revendication ou arrière-plan technologique général<br>O : divulgarion non-écrite<br>P : document intercalaire |                                                                                    | T : théorie ou principe à la base de l'invention<br>E : document de brevet bénéficiant d'une date antérieure à la date de dépôt et qui n'a été publié qu'à cette date de dépôt ou qu'à une date postérieure.<br>D : cité dans la demande<br>L : cité pour d'autres raisons<br>& : membre de la même famille, document correspondant |  |