등록특허 10-2514839

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2023년03월27일

(11) 등록번호 10-2514839

(24) 등록일자 2023년03월23일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/768* (2006.01) *H01L 21/02* (2006.01)

*H01L 21/027* (2006.01) *H01L 21/56* (2006.01)

- (52) CPC특허분류

*H01L 21/76816* (2013.01)

*H01L 21/0228* (2013.01)

- (21) 출원번호 10-2017-0147904

(22) 출원일자 2017년11월08일

심사청구일자 2020년11월05일

- (65) 공개번호 10-2018-0053238

(43) 공개일자 2018년05월21일

(30) 우선권주장

15/349,746 2016년11월11일 미국(US)

## (56) 선행기술조사문헌

KR1020140069326 A\*

KR1020150053253 A\*

KR1020160045527 A\*

US20110033786 A1

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

램 리씨치 코포레이션

미국 94538 캘리포니아주 프레몬트 쿠싱 파크웨이 4650

- (72) 발명자

라보이 애드리언

미국, 오리건 97132, 뉴버그, 코요테 루프 12705

- (74) 대리인

특허법인인벤싱크

전체 청구항 수 : 총 14 항

심사관 : 최상원

(54) 발명의 명칭 ALD 캡충진 스페이서 마스크를 사용하는 자기-정렬된 다중 패터닝 프로세스 풀로우

**(57) 요약**

자기-정렬된 다중 패터닝 프로세스들을 위해 대칭적 스페이서들을 형성하는 방법들 및 장치들이 본 명세서에 기술된다. 방법들은 코어 재료 및 타깃 층을 포함하는 패터닝된 기판 위에 ALD (atomic layer deposition) 에 의해 캡충진 재료를 증착하는 단계, 기판을 평탄화하는 단계, 및 대칭적 스페이서들을 형성하도록 코어 재료를 에칭하는 단계를 포함한다. 캡충진 재료는 피처들이 언더필드도록 (underfilled) 피처들을 완전히 충진하기 불충분한 지속기간 동안 증착될 수도 있다.

대 표 도 - 도31

(52) CPC특허분류

*H01L 21/0274* (2013.01)

*H01L 21/563* (2013.01)

*H01L 21/76877* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

타깃 층, 상기 타깃 층 위에 패터닝된 코어 재료, 및 상기 패터닝된 코어 재료 사이의 갭들을 가진 기판을 제공하는 단계;

상기 기판 상에서 상기 갭들을 캡충진 재료로 채우기에 충분한 시간 동안, 원자층 증착에 의해 상기 패터닝된 코어 재료 상에 실리콘 산화물(silicon oxide), 실리콘 질화물(silicon nitride), 실리콘 카바이드(silicon carbide) 및 산화 티타늄(titanium oxide)로 이루어진 그룹으로부터 선택된 물질을 포함하는 상기 캡충진 재료를 컨포멀하게 (conformally) 증착하는 단계;

상기 캡충진 재료를 증착한 후, 상기 캡충진 재료 및 상기 패터닝된 코어 재료를 포함하는 평면형 표면을 형성하도록 상기 기판을 화학 기계 평탄화(chemical mechanical planarization)에 의해 평탄화하는 단계로서, 상기 기판을 평탄화하는 단계는 상기 캡충진 재료로 하여금 대칭적으로 형상화되게 하여, 상기 캡충진 재료를 포함하는 대칭 형상 스페이서들을 형성하는, 상기 기판을 평탄화하는 단계;

상기 캡충진 재료에 대해 상기 패터닝된 코어 재료를 선택적으로 제거하도록 예칭 프로세스를 수행하는 단계; 및

상기 대칭 형상 스페이서들을 마스크로 사용하여 상기 타깃 층을 예칭하는 단계를 포함하며,

상기 대칭 형상 스페이서들은, 상기 평탄화하는 단계 후에, 상기 대칭 형상 스페이서들의 상단 수평 표면으로부터  $90^{\circ}$  배향된 상기 대칭 형상 스페이서들의 수직 표면들을 갖는 평면형 상단 프로파일을 가지고,

상기 패터닝된 코어 재료는, 스핀 온 카본 (spin on carbon), 다이아몬드-유사 카본, 및 캡충진 애쉬가능 하드 마스크로 구성된 그룹으로부터 선택되며,

상기 타깃 층을 예칭하기 위해 사용된 상기 마스크는, 상기 대칭 형상 스페이서들로 본질적으로 구성되는, 방법.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

제 1 항에 있어서,

상기 갭들은  $x \text{ nm}$  미만의 개구부들을 갖고, 상기 캡충진 재료는  $0.4 \times x \text{ nm}$  내지  $0.5 \times x \text{ nm}$ 의 두께로 상기 캡충진 재료를 증착하기 충분한 지속기간 동안 증착되는, 방법.

#### 청구항 6

제 5 항에 있어서,

$x$ 는 50인, 방법.

#### 청구항 7

제 5 항에 있어서,

$x$ 는 50 미만인, 방법.

#### 청구항 8

삭제

#### 청구항 9

삭제

#### 청구항 10

삭제

#### 청구항 11

제 1 항에 있어서,

상기 캡충진 재료를 증착하는 단계는 실리콘 함유 전구체 및 산화 플라즈마의 교번하는 펄스들에 상기 기판을 노출하는 것을 포함하는, 방법.

#### 청구항 12

삭제

#### 청구항 13

삭제

#### 청구항 14

타깃 층, 상기 타깃 층 위에 패터닝된 코어 재료, 및 상기 패터닝된 코어 재료 사이의 캡들을 가진 기판을 제공하는 단계;

상기 기판 상에서 상기 캡들을 캡충진 재료로 채우기에 충분한 시간 동안, 원자층 증착에 의해 상기 패터닝된 코어 재료의 측벽들 상에 실리콘 산화물(silicon oxide), 실리콘 질화물(silicon nitride), 실리콘 카바이드(silicon carbide) 및 산화 티타늄(titanium oxide)로 이루어진 그룹으로부터 선택된 물질을 포함하는 상기 캡 충진 재료를 직접 친포밀하게 증착하는 단계;

상기 캡충진 재료를 증착하는 단계 직후에, 상기 캡충진 재료 및 상기 패터닝된 코어 재료를 포함하는 평면형 표면을 형성하도록 상기 기판을 화학 기계 평탄화(chemical mechanical planarization)에 의해 평탄화하는 단계로서, 상기 기판을 평탄화하는 단계는 상기 캡충진 재료로 하여금 대칭적으로 형상화되게 하여, 상기 캡충진 재료를 포함하는 대칭 형상 스페이서들을 형성하는, 상기 기판을 평탄화하는 단계;

상기 기판을 평탄화하는 단계 후, 상기 대칭 형상 스페이서들을 남기기 위해 상기 캡충진 재료에 대해 상기 패터닝된 코어 재료를 선택적으로 제거하도록 예칭 프로세스를 수행하는 단계; 및

상기 대칭 형상 스페이서들로 본질적으로 구성된 예칭 마스크를 사용하여 상기 타깃 층을 예칭하는 단계;를 포함하고,

상기 대칭 형상 스페이서들은, 상기 평탄화하는 단계 후에, 상기 대칭 형상 스페이서들의 상단 수평 표면으로부터  $90^{\circ}$  배향된 상기 대칭 형상 스페이서들의 수직 표면들을 갖는 평면형 상단 프로파일을 가지고,

상기 패터닝된 코어 재료는, 스핀 온 카본 (spin on carbon), 다이아몬드-유사 카본, 및 캡충진 애쉬가능 하드 마스크로 구성된 그룹으로부터 선택되는, 방법.

#### 청구항 15

타깃 층, 상기 타깃 층 위에 패터닝된 코어 재료, 및 상기 패터닝된 코어 재료 사이의 캡들을 가진 기판을 제공하는 단계;

상기 기판 상에서 상기 캡들을 캡충진 재료로 채우기에 충분한 시간 동안, 원자층 증착에 의해 상기 패터닝된 코어 재료의 측벽들 위에 실리콘 산화물(silicon oxide), 실리콘 질화물(silicon nitride), 실리콘 카바이드(silicon carbide) 및 산화 티타늄(titanium oxide)로 이루어진 그룹으로부터 선택된 물질을 포함하는 상기 캡 충진 재료를 컨포멀하게 증착하는 단계;

상기 캡충진 재료를 증착하는 단계 후에, 상기 캡충진 재료 및 상기 패터닝된 코어 재료를 포함하는 평면형 표면을 형성하도록 상기 기판을 화학 기계 평탄화(chemical mechanical planarization)에 의해 평탄화하는 단계로서, 상기 기판을 평탄화하는 단계는 상기 캡충진 재료로 하여금 대칭적으로 형상화되고, 수평 평면 상부 프로파일을 가지게 되어, 상기 캡충진 재료를 포함하는 대칭 형상 스페이서들을 형성하는, 상기 기판을 평탄화하는 단계;

상기 대칭 형상 스페이서들을 형성하도록 상기 캡충진 재료에 대해 상기 패터닝된 코어 재료를 선택적으로 에칭하는 단계; 및

상기 대칭 형상 스페이서들로 본질적으로 구성된 에칭 마스크를 사용하여 상기 타깃 층을 에칭하는 단계; 를 포함하고,

상기 패터닝된 코어 재료는, 스픬 온 카본 (spin on carbon), 다이아몬드-유사 카본, 및 캡충진 애쉬가능 하드 마스크로 구성된 그룹으로부터 선택되며,

상기 캡충진 재료를 증착하는 단계 전에, 상기 패터닝된 코어 재료 내의 캡들은 20 : 1 보다 큰 종횡비를 가지는, 방법.

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

제 1 항, 제 5 항, 제 6 항, 제 7 항, 제 11 항, 제 14항 및 제 15 항 중 어느 한 항에 있어서,

상기 캡충진 재료를 증착하기 전에, 상기 기판 위에 또 다른 컨포멀한 막을 증착하는 단계 및 상기 코어 재료의 측벽들 상에 측벽 스페이서들을 형성하도록 상기 또 다른 컨포멀한 막을 지향성으로 에칭하는 단계를 더 포함하는, 방법.

#### 청구항 20

삭제

#### 청구항 21

삭제

#### 청구항 22

삭제

#### 청구항 23

삭제

#### 청구항 24

삭제

**청구항 25**

삭제

**청구항 26**

제 1 항에 있어서,

상기 캡충진 재료를 증착하는 단계 전에, 상기 패터닝된 코어 재료 내의 캡들은 20 : 1 보다 큰 종횡비를 가지는, 방법.

**청구항 27**

제 1 항에 있어서,

상기 마스크 내 상기 대칭 형상 스페이서들 간의 CD (critical dimension) 는 50nm 미만인, 방법.

**청구항 28**

제 1 항에 있어서,

상기 대칭 형상 스페이서들이 이중 또는 사중 패터닝 기법에 사용되는, 방법.

**청구항 29**

제 1 항에 있어서,

상기 캡충진 재료는, 상기 기판 상의 상기 캡충진 재료 내에 심(seam)이 형성되도록 증착되는, 방법.

**청구항 30**

제 1 항에 있어서,

상기 캡충진 재료는 상기 기판 상에 오버부든(overburden)을 형성하기에 충분한 지속시간 동안 증착되는, 방법.

**청구항 31**

제 1 항에 있어서,

상기 캡충진 재료가, 상기 패터닝된 코어 재료 상에 직접 증착되는, 방법.

**발명의 설명****배경기술**

[0001] 발전된 IC의 제조는 종종 반도체들의 대량 생산시 소형 피처들의 패터닝을 수반한다. 다중 패터닝 기법들은 193 nm 담금 리소그래피와 같은 리소그래픽 기법들에 기초한 피처 사이즈 스케일링을 인에이블할 수도 있다. 자기-정렬 더블 패터닝이 다중 패터닝 기법의 일 예이다.

**발명의 내용**

[0002] 반도체 기판들과 같은, 기판들을 프로세싱하는 방법들이 본 명세서에 제공된다. 일 양태는 기판을 프로세싱하는 방법으로서, 캡들 및 타깃 층을 형성하도록 패터닝된 코어 재료를 갖는 기판을 제공하는 단계; 캡 충진 재료가 기판 상의 캡들 내에 증착되도록 코어 재료 위에 캡충진 재료를 컨포멀하게 (conformally) 증착하는 단계; 캡충진 재료 및 코어 재료를 포함하는 평면형 표면을 형성하도록 기판을 평탄화하는 단계; 및 타깃 층을 에칭하기 위한 마스크로서 사용된 대칭적으로 성형된 스페이서들을 형성하도록 코어 재료를 선택적으로 에칭하는 단계를 포함하는, 기판을 프로세싱하는 방법을 수반한다.

[0003] 다양한 실시예들에서, 캡충진 재료는 ALD (atomic layer deposition) 에 의해 증착된다. 일부 실시예들에서, 캡충진 재료는 캡들을 완전히 충진하기 불충분한 지속기간 동안 ALD에 의해 된다.

[0004] 일부 실시예들에서, 캡들은 약  $x$  nm 미만의 개구부들을 갖고, 캡충진 재료는 약  $0.4 \times x$  nm 내지 약  $0.5 \times x$  nm의 두께로 캡충진 재료를 증착하기 충분한 지속기간 동안 증착된다. 일부 실시예들에서,  $x$ 는 50이다. 일부

실시예들에서,  $x$ 는 50 미만이다.

[0005] 일부 실시예들에서, 캡충진 재료는 실리콘 옥사이드, 실리콘 나이트라이드, 실리콘 카바이드, 및 티타늄 옥사이드 중 어느 하나이다.

[0006] 일부 실시예들에서, 마스크 내 대칭적으로 성형된 스페이서들 간 CD (critical dimension) 는 약 50 nm 미만이다. 대칭적으로 성형된 스페이서들은 다중 패터닝 기법들에 사용될 수도 있다. 일부 실시예들에서, 캡충진 재료를 증착하는 단계 및 기판을 평탄화하는 단계는 피치 워킹 (pitch walking) 을 감소시킨다. 다양한 실시예들에서, 대칭적으로 성형된 스페이서들은 캡충진 재료를 포함한다.

[0007] 방법은 또한 캡충진 재료를 증착하는 단계 전에, 기판 위에 또 다른 컨포멀한 막을 증착하는 단계 및 코어 재료의 측벽들 상에 측벽 스페이서들을 형성하도록 또 다른 컨포멀한 막을 지향성으로 에칭하는 단계를 포함할 수도 있다. 다양한 실시예들에서, 대칭적으로 성형된 스페이서들을 형성하도록 기판을 선택적으로 에칭하는 단계는 측벽 스페이서들에 선택적으로 코어 재료 및 캡충진 재료를 제거하는 것을 포함한다. 대칭적으로 성형된 스페이서들을 형성하도록 기판을 선택적으로 에칭하는 단계는 캡충진 재료에 선택적으로 코어 재료를 제거하는 것을 포함한다.

[0008] 다양한 실시예들에서, 코어 재료는 탄소를 포함한다. 코어 재료는 스판 온 카본, 다이아몬드-유사 카본, 및/또는 캡충진 애쉬가능 하드 마스크 중 임의의 하나일 수도 있다.

[0009] 다양한 실시예들에서, 캡충진 재료를 증착하는 단계는 실리콘 함유 전구체 및 산화 플라즈마의 교변하는 펄스들에 기판을 노출하는 것을 포함한다.

[0010] 또 다른 양태는 마스크를 형성하는 스페이서들을 포함하는 기판을 제공하는 단계로서, 스페이서 각각은 스페이서의 상단 표면에 수직인 측벽들을 포함하고, 스페이서들은 코어 재료의 캡들 내에 캡충진 재료를 컨포멀하게 증착함으로써 형성되는, 기판을 제공하는 단계; 평면형 표면을 형성하도록 캡충진 재료 및 코어 재료를 평탄화하는 단계; 코어 재료를 선택적으로 제거하는 단계; 및 스페이서들을 마스크로서 사용하여 타깃 층을 에칭하는 단계를 포함하는, 방법을 수반한다. 다양한 실시예들에서, 마스크는 약 50 nm 미만의 피치를 갖는다.

[0011] 다양한 실시예들에서, 캡충진 재료는 ALD에 의해 증착된다. 일부 실시예들에서, 캡충진 재료는 캡들을 완전히 충진하기 불충분한 지속기간 동안 ALD에 의해 된다.

[0012] 일부 실시예들에서, 캡충진 재료는 실리콘 옥사이드, 실리콘 나이트라이드, 실리콘 카바이드, 및 티타늄 옥사이드로 구성된 그룹으로부터 선택된다.

[0013] 대칭적으로 성형된 스페이서들이 다중 패터닝 기법들에 사용될 수도 있다. 일부 실시예들에서, 캡충진 재료를 증착하는 단계 및 기판을 평탄화하는 단계는 피치 워킹을 감소시킨다. 다양한 실시예들에서, 대칭적으로 성형된 스페이서들은 캡충진 재료를 포함한다.

[0014] 다양한 실시예들에서, 코어 재료는 탄소를 포함한다. 코어 재료는 스판 온 카본, 다이아몬드-유사 카본, 및/또는 캡충진 애쉬가능 하드 마스크 중 임의의 하나일 수도 있다.

[0015] 다양한 실시예들에서, 캡충진 재료를 증착하는 단계는 실리콘 함유 전구체 및 산화 플라즈마의 교변하는 펄스들에 기판을 노출하는 것을 포함한다.

[0016] 또 다른 양태는 마스크를 형성하는 스페이서들을 포함하는 기판을 제공하는 단계로서, 스페이서 각각은 스페이서의 상단 표면을  $90^{\circ} \pm 5^{\circ}$  의 각도로 만나는 측벽들을 포함하고, 스페이서들은 코어 재료의 캡들 내에 캡충진 재료를 컨포멀하게 증착함으로써 형성되는, 기판을 제공하는 단계; 평면형 표면을 형성하도록 캡충진 재료 및 코어 재료를 평탄화하는 단계; 코어 재료를 선택적으로 제거하는 단계; 및 스페이서들을 마스크로서 사용하여 타깃 층을 에칭하는 단계를 포함하는, 방법을 수반한다.

[0017] 다양한 실시예들에서, 캡충진 재료는 ALD에 의해 증착된다. 일부 실시예들에서, 캡충진 재료는 캡들을 완전히 충진하기 불충분한 지속기간 동안 ALD에 의해 된다.

[0018] 일부 실시예들에서, 캡충진 재료는 실리콘 옥사이드, 실리콘 나이트라이드, 실리콘 카바이드, 및 티타늄 옥사이드 중 어느 하나이다.

[0019] 대칭적으로 성형된 스페이서들이 다중 패터닝 기법들에 사용될 수도 있다. 일부 실시예들에서, 캡충진 재료를 증착하는 단계 및 기판을 평탄화하는 단계는 피치 워킹을 감소시킨다. 다양한 실시예들에서, 대칭적으로 성형

된 스페이서들은 캡충진 재료를 포함한다.

[0020] 다양한 실시예들에서, 코어 재료는 탄소를 포함한다. 코어 재료는 스펀 온 카본, 다이아몬드-유사 카본, 및/또는 캡충진 애쉬가능 하드 마스크 중 임의의 하나일 수도 있다.

[0021] 다양한 실시예들에서, 캡충진 재료를 증착하는 단계는 실리콘 함유 전구체 및 산화 플라즈마의 교변하는 펄스들에 기판을 노출하는 것을 포함한다.

[0022] 또 다른 양태는 하나 이상의 프로세스 챔버들; 하나 이상의 프로세스 챔버들 및 연관된 플로우 제어 하드웨어 내로의 하나 이상의 가스 유입부들; LFRF (low frequency radio frequency) 생성기; HFRF (high frequency radio frequency) 생성기; 및 적어도 하나의 프로세서 및 메모리를 갖는 제어기를 포함하고, 적어도 하나의 프로세서 및 메모리는 서로 통신가능하게 연결되고, 적어도 하나의 프로세서는 적어도 플로우 제어 하드웨어, LFRF 생성기, 및 HFRF 생성기와 동작하게 연결되고, 그리고 메모리는, 캡충진 재료가 기판 상의 캡들 내에 증착되도록, 캡들을 형성하게 패터닝된 코어 재료 및 타깃 층을 포함하는 기판의 코어 재료 위에 캡충진 재료를 컨포멀하게 증착하도록 캡충진 재료 전구체들의 도입하고; 캡충진 재료 및 코어 재료를 포함하는 평면형 표면을 형성하도록 기판을 평탄화하고; 그리고 타깃 층을 에칭하도록 마스크로서 사용된 대칭적으로 성형된 스페이서들을 형성하도록 코어 재료를 선택적으로 에칭하도록, 적어도 플로우 제어 하드웨어, HFRF 생성기, 및 LFRF 생성기를 제어하도록 적어도 하나의 프로세서를 제어하는 컴퓨터 실행가능 인스트럭션들을 저장하는, 기판들을 패터닝하기 위한 장치를 수반한다.

[0023] 또 다른 양태는 하나 이상의 프로세스 챔버들; 하나 이상의 프로세스 챔버들 및 연관된 플로우 제어 하드웨어 내로의 하나 이상의 가스 유입부들; LFRF (low frequency radio frequency) 생성기; HFRF (high frequency radio frequency) 생성기; 및 적어도 하나의 프로세서 및 메모리를 갖는 제어기를 포함하고, 적어도 하나의 프로세서 및 메모리는 서로 통신가능하게 연결되고, 적어도 하나의 프로세서는 적어도 플로우 제어 하드웨어, LFRF 생성기, 및 HFRF 생성기와 동작하게 연결되고, 그리고 메모리는, 스페이서 각각이 스페이서의 상단 표면에 수직인 측벽들을 포함하고, 스페이서들이 코어 재료 캡들 내에 캡충진 재료를 컨포멀하게 증착함으로써 형성되고, 마스크를 형성하는 스페이서들을 포함하는 기판의 하나 이상의 프로세스 챔버들 내로 이송하고, 평면형 표면을 형성하도록 캡충진 재료 및 코어 재료를 평탄화하고, 코어 재료를 선택적으로 제거하고, 그리고 스페이서들을 마스크로서 사용하여 타깃 층의 에칭하도록, 적어도 플로우 제어 하드웨어, HFRF 생성기, 및 LFRF 생성기를 제어하도록 적어도 하나의 프로세서를 제어하는 컴퓨터 실행가능 인스트럭션들을 저장하는, 기판들을 패터닝하기 위한 장치를 수반한다. 다양한 실시예들에서, 마스크는 약 50 nm 미만의 퍼치를 갖는다.

[0024] 또 다른 양태는 하나 이상의 프로세스 챔버들; 하나 이상의 프로세스 챔버들 및 연관된 플로우 제어 하드웨어 내로의 하나 이상의 가스 유입부들; LFRF (low frequency radio frequency) 생성기; HFRF (high frequency radio frequency) 생성기; 및 적어도 하나의 프로세서 및 메모리를 갖는 제어기를 포함하고, 적어도 하나의 프로세서 및 메모리는 서로 통신가능하게 연결되고, 적어도 하나의 프로세서는 적어도 플로우 제어 하드웨어, LFRF 생성기, 및 HFRF 생성기와 동작하게 연결되고, 그리고 메모리는, 스페이서 각각이 스페이서의 상단 표면을  $90^\circ \pm 5^\circ$  의 각도로 만나는 측벽들을 포함하고, 스페이서들이 코어 재료 캡들 내에 캡충진 재료를 컨포멀하게 증착함으로써 형성되고, 마스크를 형성하는 스페이서들을 포함하는 기판의 하나 이상의 프로세스 챔버들 내로 이송하고, 평면형 표면을 형성하도록 캡충진 재료 및 코어 재료를 평탄화하고, 코어 재료를 선택적으로 제거하고, 그리고 스페이서들을 마스크로서 사용하여 타깃 층을 에칭하도록, 적어도 플로우 제어 하드웨어, HFRF 생성기, 및 LFRF 생성기를 제어하도록 적어도 하나의 프로세서를 제어하는 컴퓨터 실행가능 인스트럭션들을 저장하는, 기판들을 패터닝하기 위한 장치를 수반한다.

[0025] 이를 및 다른 양태들은 도면들을 참조하여 이하에 더 기술된다.

### 도면의 간단한 설명

[0026] 도 1a 내지 도 1j는 쿼트 패터닝 스Kim (quad patterning scheme) 의 예에서 기판들의 개략적인 예시들이다.

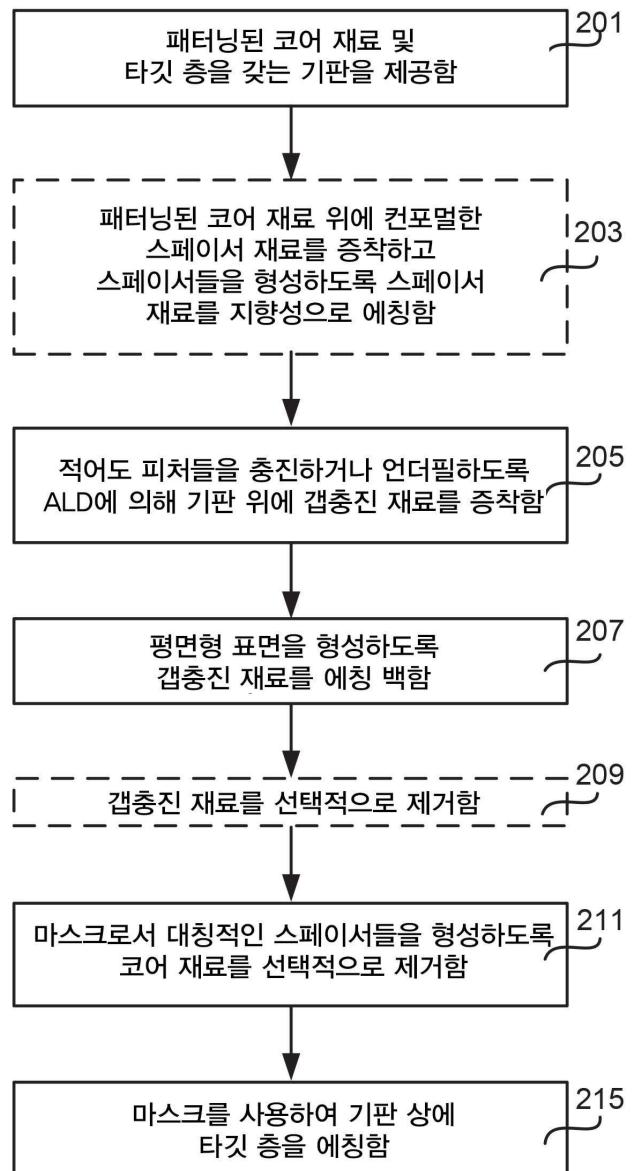

도 2는 특정한 개시된 실시예들에 따라 수행된 방법의 동작들을 도시하는 프로세스 흐름도이다.

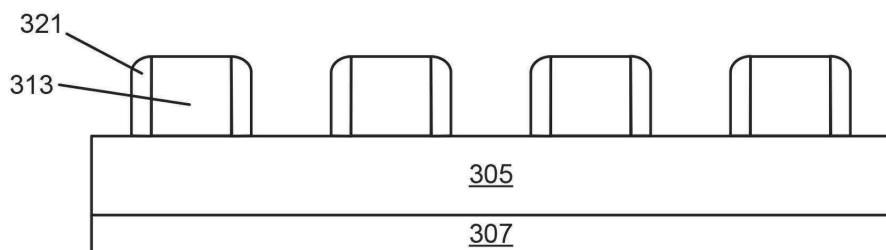

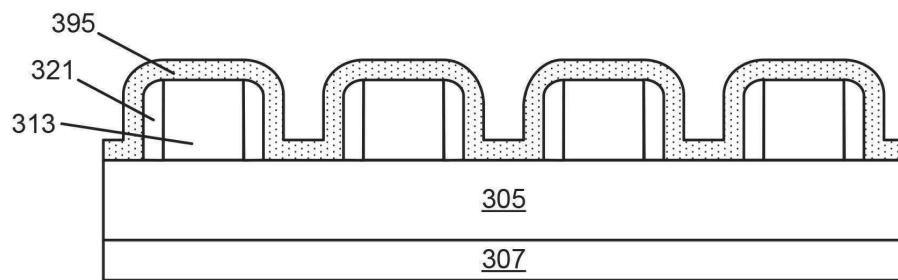

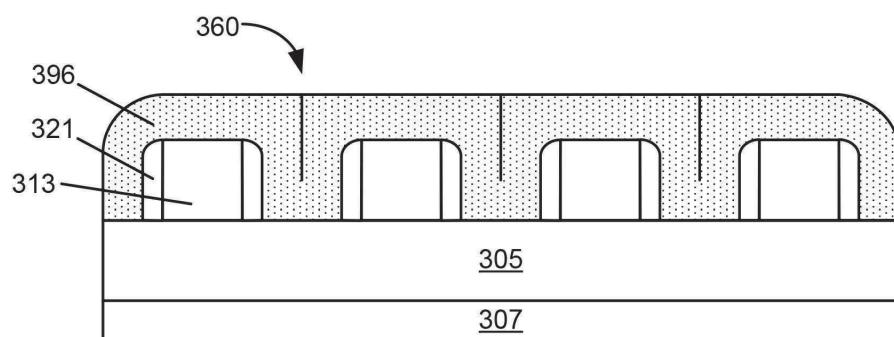

도 3a 내지 도 3g는 특정한 개시된 실시예들에 따라 수행된 패터닝 스Kim의 예에서 기판들의 개략적인 예시들이다.

도 3h 및 도 3i는 특정한 개시된 실시예들에 따라 퍼처들을 언더필 (underfill) 하는 예시적인 스Kim에서 기판들의 개략적인 예시들이다.

도 3j 내지 도 3o는 특정한 개시된 실시예들에 따라 수행된 패터닝 스킴의 예에서 기판들의 개략적인 예시들이다.

도 3p 내지 도 3r은 특정한 개시된 실시예들에 따라 피처들을 언더필하는 예시적인 스킴에서 기판들의 개략적인 예시들이다.

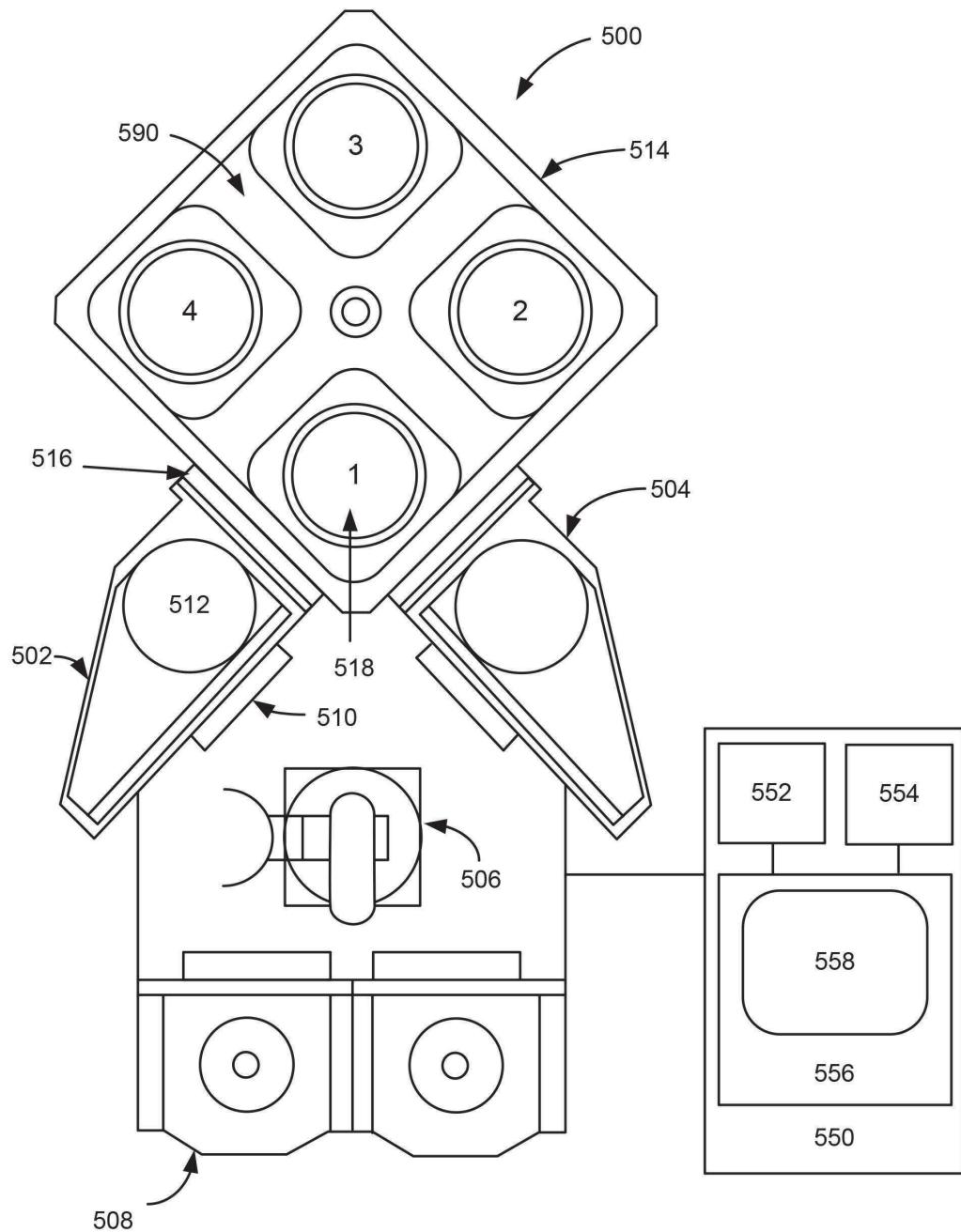

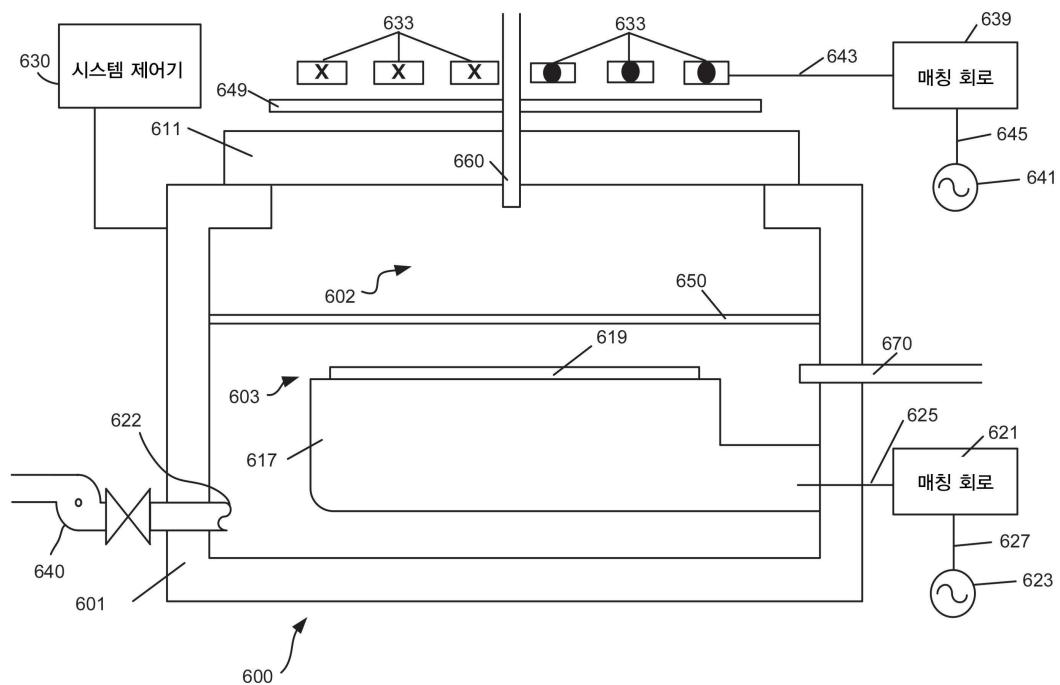

도 4 및 도 6은 특정한 개시된 실시예들을 수행하기 위한 예시적인 챔버들의 개략적인 도면들이다.

도 5 및 도 7은 특정한 개시된 실시예들을 수행하기 위한 예시적인 프로세스 툴들의 개략적인 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0027]

이하의 기술에서, 다수의 구체적인 상세들이 제시된 실시예들의 전체적인 이해를 제공하도록 언급된다. 개시된 실시예들은 이들 구체적인 상세들 중 일부 또는 전부 없이도 실시될 수도 있다. 다른 예들에서, 공지의 프로세스 동작들은 개시된 실시예들을 불필요하게 모호하게 하지 않도록 상세히 기술되지 않았다. 개시된 실시예들이 구체적인 실시예들에 관하여 기술되지만, 이는 개시된 실시예들을 제한하는 것으로 의도되지 않는다는 것이 이해될 것이다.

[0028]

많은 반도체 제조 프로세스들에 패터닝 방법들이 사용된다. 특히, 다중 패터닝은 광학적 한계들을 넘어 리소그래피 기법을 확장하도록 사용되었다. 더블 패터닝 및 퀘드 패터닝은 광학적 한계들을 넘어 리소그래피 기법을 확장하도록 사용된 예시적인 기법들이고 더블 패터닝은 이제 약 80 nm 미만의 피치들에 대해 산업계에서 광범위하게 사용된다. 현재 더블 패터닝 기술들은 종종 트렌치들을 패터닝하기 위해 2 개의 마스킹 단계들과 함께 측벽 스페이서들을 사용한다. 포지티브 더블 패터닝 프로세스 및 네거티브 더블 패터닝 프로세스 모두에서, 더블 패터닝, 특히 라인 패터닝 방법은 스페이서들 및 마스크들의 사용을 수반하였다. 스페이서들은 패터닝된 코어 상의 PEALD (plasma enhanced ALD) 에 의해 증착될 수 있고 보다 작은 피치 패턴을 생성하도록 사용될 수도 있다. 디바이스들이 축소되고 피치가 감소됨에 따라, 스페이서 리닝 (spacer leaning), 라인 벤딩 (line bending), 및 패터닝된 스페이서 붕괴와 같은 문제가 일어나고, 디바이스 고장을 유발할 수 있다. 특히, 스페이서 리닝으로 인한 피치 워킹은 코어 층이 소성되고 (bake) 제거될 때 관찰된다.

[0029]

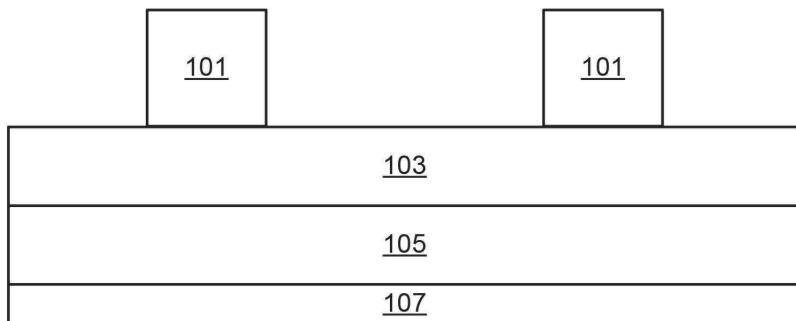

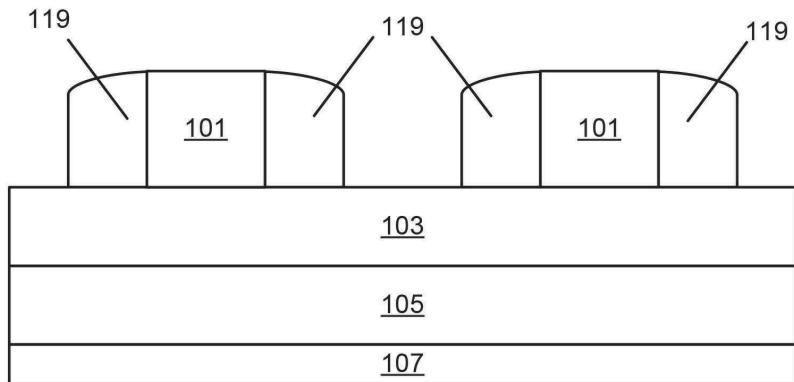

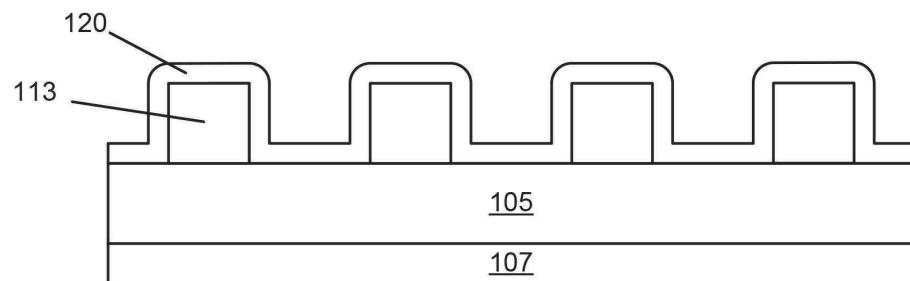

도 1a 내지 도 1j는 피치 워킹을 발생시키는 퀘트 패터닝 스킴에서 기판들의 예시적인 개략적인 예시들이다. 도 1a는 제 2 코어 (103), 타깃 층 (105), 및 하부층 (107) 상의 리소그래피로 형성 (define) 또는 패터닝된 제 1 코어 (101)를 갖는 기판이 도시된다. 당업자는 본 명세서에 기술된 바와 같은 반도체 프로세싱에 적합한 복수 층 스택이 다른 층들, 예컨대 에칭 정지층들, 캡층들, 및 다른 하부층들을 포함할 수도 있다는 것을 이해 할 것이다.

[0030]

패터닝된 제 1 코어 (101)는 포토레지스트일 수도 있고 또는 비정질 탄소 또는 비정질 실리콘 재료를 포함할 수도 있다. 패터닝된 제 1 코어 (101)는 임의의 적합한 증착 기법, 예컨대 PECVD (plasma enhanced chemical vapor deposition) 에 의해 제 2 코어 (103) 위에 증착될 수도 있고 증착 기법은 하이드로카본 전구체를 포함하는 증착 가스들로부터 증착 챔버 내에서 플라즈마를 생성하는 단계를 수반할 수도 있다. 하이드로카본 전구체는 화학식  $C_xH_y$ 으로 규정될 수도 있고,  $x$ 는 2와 10 사이의 정수이고, 그리고  $y$ 는 2와 24 사이의 정수이다. 예들은 메탄 ( $CH_4$ ), 아세틸렌 ( $C_2H_2$ ), 에틸렌 ( $C_2H_4$ ), 프로필렌 ( $C_3H_6$ ), 부탄 ( $C_4H_{10}$ ), 사이클로헥산 ( $C_6H_{12}$ ), 벤젠 ( $C_6H_6$ ), 및 톨루엔 ( $C_7H_8$ ) 을 포함한다. HF (high frequency) 전력 및 LF (low frequency) 전력을 포함하는 듀얼 RF (radio frequency) 플라즈마 소스가 사용될 수도 있다.

[0031]

제 2 코어 (103) 아래에 타깃 층 (105)이 있다. 타깃 층 (105)은 궁극적으로 패터닝될 층일 수도 있다. 타깃 층 (105)은 반도체, 유전체 또는 다른 층일 수도 있고, 예를 들어, 실리콘 (Si), 실리콘 옥사이드 ( $SiO_2$ ), 실리콘 나이트라이드 ( $SiN$ ), 또는 티타늄 나이트라이드 ( $TiN$ )로 이루어질 수도 있다. 타깃 층 (105)은 ALD (atomic layer deposition), PEALD, CVD (chemical vapor deposition), 또는 다른 적합한 증착 기법에 의해 증착될 수도 있다.

[0032]

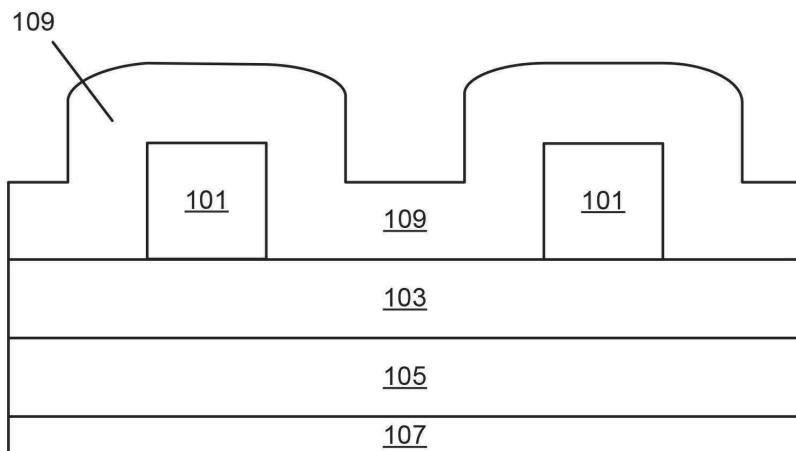

도 1b에서, 제 1 컨포멀한 막 (109)이 패터닝된 제 1 코어 (101) 위에 증착된다. 일부 실시예들에서 제 1 컨포멀한 막 (109)은 ALD 또는 PEALD에 의해 증착될 수도 있다. 제 1 컨포멀한 막 (109)은 도 1c에 도시된 바와 같이 제 1 스페이서 (119)를 형성하도록 지향성으로 에칭된다. 제 1 스페이서 (119)는 실리콘 옥사이드 ( $SiO_2$ ) 또는 티타늄 옥사이드 ( $TiO_2$ )와 같은 옥사이드일 수도 있고, 또는 실리콘 나이트라이드 ( $SiN$ )와 같은 나이트라이드일 수도 있다. 제 1 스페이서 (119)의 패턴은 후속하는 층들을 패터닝하도록 사용된다. 본 명세

서에 사용된 바와 같은 용어 "스페이서"는 코어 재료에 인접한 마스크 재료를 의미한다는 것이 이해될 것이다.

[0033] 도 1d에서, 패터닝된 제 1 코어 (101) 는 기판 상에 단독으로 서 있는 (free-standing) 제 1 스페이서들 (119) 을 남기면서 선택적으로 에칭된다. 본 명세서에 사용된 바와 같은 선택적인 제거 또는 선택적인 에칭은 서로 선택적인 일 재료를 에칭하는 것으로 규정된다. 예를 들어, 도 1d에서, 패터닝된 제 1 코어는 제 1 스페이서들 (119) 에 선택적으로 에칭된다. 일부 실시예들에서, 제 1 재료가 제 2 재료에 선택적으로 에칭된다면, 미리 결정된 지속기간 동안, 제 2 재료보다 많은 제 1 재료가 에칭되도록, 제 1 재료의 에칭 레이트는 제 2 재료의 에칭 레이트보다 빠르다는 것이 이해될 것이다.

[0034] 제 1 스페이서들 (119) 의 패턴은 약 50 nm의 피치를 가질 수도 있다. CD가 꽤 크기 때문에, 이를 보다 큰 CD에서 피치 워킹 리스크가 거의 없다.

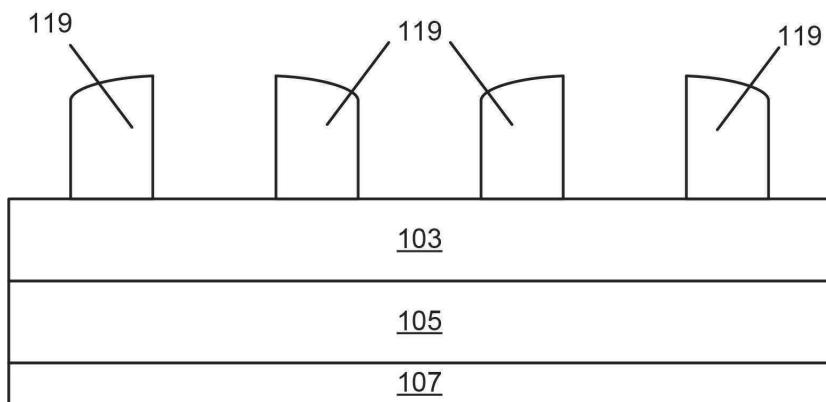

[0035] 도 1e에서, 제 2 코어 층 (103) 은 마스크로서 패터닝된 스페이서들 (119) 을 사용하여 에칭되어, 패터닝된 제 2 코어 (113) 를 형성하도록 제 2 코어 층 (103) 으로 패턴을 전사한다. 패터닝된 제 2 코어 (113) 는 패터닝된 스페이서들 (119) 이 아니라 제 2 코어 층 (103) 을 에칭하는데 적합한 화학물질을 사용하여 에칭될 수도 있다. 패터닝된 제 2 코어 (113) 는 비정질 탄소 층, 비정질 실리콘 층 또는 포토레지스트, 예전대 폴리(메틸 메타크릴레이트) 또는 폴리(메틸글루타이미드) (PMGI) 또는 폐놀 포름알데하이드 수지일 수도 있다.

[0036] 도 1f에서, 제 1 스페이서 (119) 는 패터닝된 제 2 코어 (113) 를 남기도록 선택적으로 제거된다. 일부 예에서, 스페이서는 CHF<sub>3</sub> 및/또는 CF<sub>4</sub>를 홀리프로세스로써 제거될 수도 있다.

[0037] 도 1g에서, 제 2 컨포멀한 막 (120) 이 패터닝된 제 2 코어 (113) 위에 증착된다. 제 2 컨포멀한 막 (120) 은 ALD 또는 PEALD에 의해 증착된 유전체 재료일 수도 있다. 예를 들어, 일부 실시예들에서, 제 2 컨포멀한 막 (120) 은 실리콘 옥사이드일 수도 있다. 일부 실시예들에서, 제 2 컨포멀한 막 (120) 은 제 1 컨포멀한 막 (109) 의 조성과 같거나 유사한 조성을 가질 수도 있다.

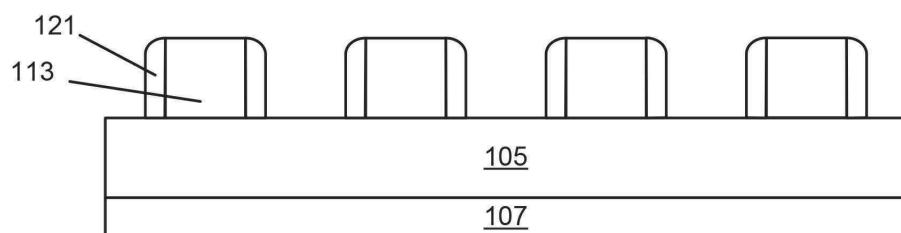

[0038] 도 1h에서, 제 2 컨포멀한 막 (120) 은 패터닝된 제 2 코어 (113) 를 플레이크하는 (flanking) 제 2 스페이서들 (121) 을 형성하도록 지향성으로 에칭된다. 도 1i에서, 패터닝된 제 2 코어 (113) 는 단독으로 서 있는 제 2 스페이서들 (121) 을 남기도록 선택적으로 제거된다. 여기서, 패터닝된 제 2 코어 (113) 는 도 1d에서 패터닝된 제 1 코어 (101) 를 에칭하는 것과 동일하거나 유사한 화학물질을 사용하여 에칭될 수도 있다.

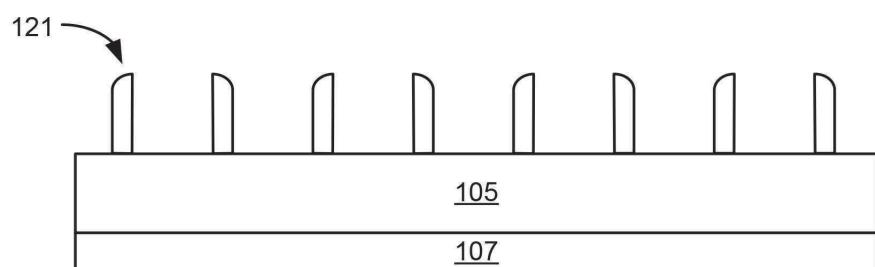

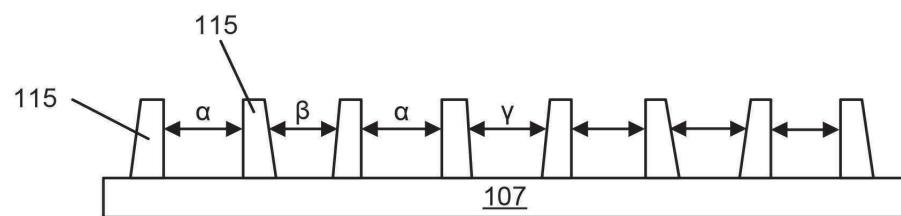

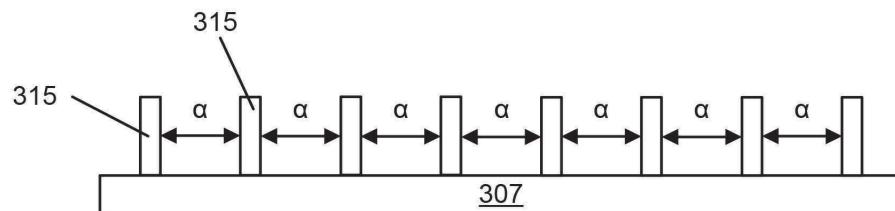

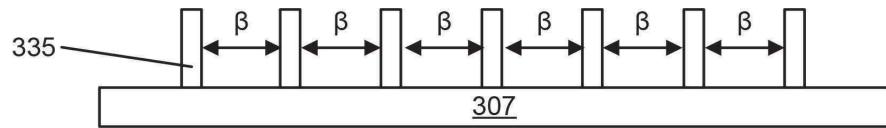

[0039] 도 1j에서, 제 2 스페이서들 (121) 의 패턴이 타깃 층 (105) 으로 전사될 때, 패터닝된 타깃 층 (115) 은, 모두 상이한 값들일 수도 있는 가변된 CD  $\alpha$ ,  $\beta$ , 및  $\gamma$ 를 포함한다. 스페이서들 (121) 의 비대칭성이 타깃 층을 형성하도록 고르지 않은 에칭을 발생시켜 피치 워킹을 발생시킨다. 비대칭적인 스페이서들 (121) 을 사용하여 타깃 층 (105) 을 에칭하는 것은 타깃 층의 기울어진 에칭을 유발하는 에칭 종의 각도 분포를 발생시킨다. 프로세스는 패터닝된 코어 재료의 제거 동안 건식 에칭 조건들이 색도우 이펙트를 발생시키기 때문에 부분적인 피치 워킹을 발생시킨다.

[0040] 현재 패터닝 스킵들 및 기법들은 피치 워킹 없이 타깃 층들을 에칭하도록 사용될 수 있는 스페이서들을 형성하기 불충분하다. ALD 캡층진 기법들을 사용하여 대칭적인 스페이서들을 형성하는 방법들이 장치들이 본 명세서에 제공된다. 대칭적인 스페이서들은 타깃 층을 에칭하기 위한 마스크로서 스페이서의 사용은 피치 워킹을 발생시키지 않고 그리고/또는 피치 워킹을 감소시키도록 개선된 상단 프로파일을 제공한다. 대칭적 스페이서들은 약 90° ± 5° 인 지점에서 만나는 날카로운 모서리들을 포함한다. 개시된 실시예들은 스페이서의 상단 표면에 수직이거나 실질적으로 수직인 측벽들을 갖는 스페이서들을 형성한다. 실질적으로 수직은 90° ± 5° 의 각도를 갖는 것으로 본 명세서에 규정된다. 방법들은 기판 상에 오버버든 (overburden) 을 형성하기 위해 ALD 를 사용하여 패터닝된 기판 위에 피쳐들을 충진하거나 부분적으로 충진하는 단계, 및 기판을 평탄화하는 단계 및 대칭적 스페이서들을 형성하기 위해 캡층진 재료 및 코어 재료를 제거하는 단계를 수반한다. 대칭적은 본 명세서에서 코어 재료가 단독으로 서 있는 스페이서들을 남기도록 제거된 후 스페이서의 측면에 실질적으로 동일한 형상을 갖는 것으로 규정된다. 예를 들어, 대칭적 스페이서들은 스페이서의 상단 수평 표면으로부터 90° 또는 약 90° 로 배향된 스페이서들의 수직 표면들을 갖는 평면형 상단 프로파일을 가질 수도 있다.

[0041] 도 2는 특정한 개시된 실시예들에 따라 수행된 방법의 동작들을 도시하는 프로세스 흐름도이다. 도 2의 하나 이상의 옵션들은 다양한 실시예들에서 수행될 수도 있다. 일부 실시예들에서, 도 2에 기술된 동작들 중 하나만이 수행된다. 예를 들어, 일부 실시예들에서, 마스크로서 형성된 대칭적 스페이서들을 포함하는 기판이 제공되고, 마스크를 사용하여 타깃 층을 에칭하도록 동작 215만이 수행된다. 또 다른 예에서, 기판이 제공되고 동작 211만이 코어 재료를 제거하고 마스크로서 대칭적 스페이서들을 형성하도록 사용된다. 이들 및 다른 실시예들

은 도 2에 대해 기술된 임의의 하나 이상의 동작들을 사용하여 수행될 수도 있다는 것이 이해될 것이다.

[0042] 동작 201에서, 패터닝된 코어 재료 및 타깃 층을 갖는 기판이 제공된다. 패터닝된 코어 재료는 포토레지스트일 수도 있고 또는 비정질 탄소 재료 또는 비정질 실리콘 재료로 이루어질 수도 있다. 일부 실시예들에서, 코어 재료는 투과성일 수도 있다. 코어 재료는 증착 기법, 예컨대 PECVD에 의해 증착되고, 증착 기법은 기판을 하우징하는 증착 챔버 내에서 하이드로카본 전구체를 포함하는 증착 가스들로부터 플라즈마를 생성하는 단계를 수반할 수도 있다. 하이드로카본 전구체는 화학식  $C_aH_b$ 으로 규정될 수도 있고,  $a$ 는 2와 10 사이의 정수이고, 그리고  $b$ 는 2와 24 사이의 정수이다. 예들은 메탄 ( $CH_4$ ), 아세틸렌 ( $C_2H_2$ ), 에틸렌 ( $C_2H_4$ ), 프로필렌 ( $C_3H_6$ ), 부탄 ( $C_4H_{10}$ ), 사이클로헥산 ( $C_6H_{12}$ ), 벤젠 ( $C_6H_6$ ), 및 톨루엔 ( $C_7H_8$ ) 을 포함한다. HF (high frequency) 전력 및 LF (low frequency) 전력을 포함하는 듀얼 RF (radio frequency) 플라즈마 소스가 사용될 수도 있다. 코어 재료는 패터닝되기 전에 타깃 층 위에 증착된다. 타깃 층은 궁극적으로 패터닝되는 층일 수도 있다. 타깃 층은 반도체, 유전체, 또는 다른 층일 수도 있고 예를 들어 실리콘 (Si), 실리콘 옥사이드 ( $SiO_2$ ), 실리콘 나이트라이드 ( $SiN$ ), 또는 티타늄 나이트라이드 ( $TiN$ ) 로 이루어질 수도 있다. 타깃 층은 ALD, PEALD (plasma-enhanced ALD), CVD (chemical vapor deposition), 또는 또 다른 적합한 증착 기법에 의해 증착될 수도 있다.

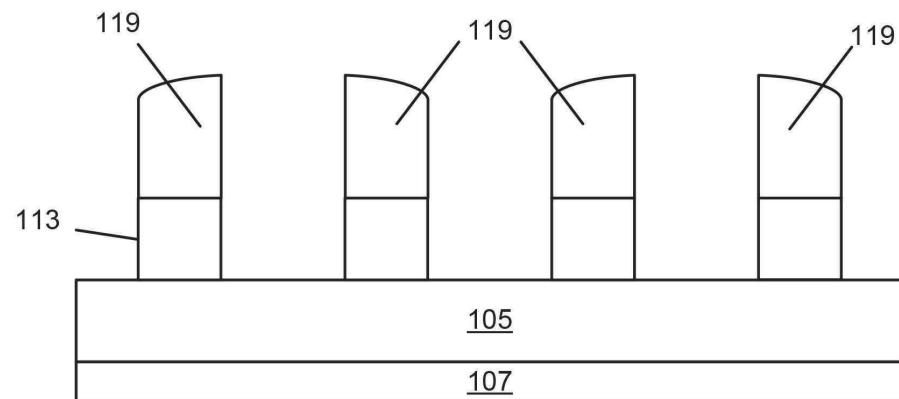

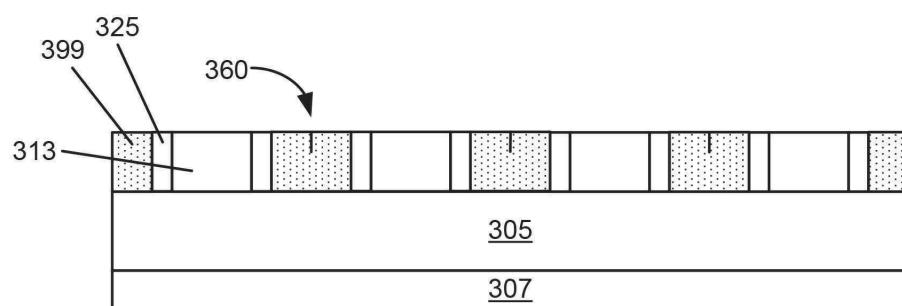

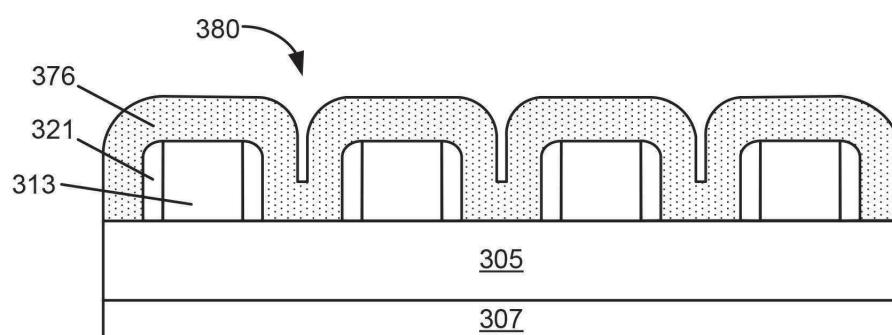

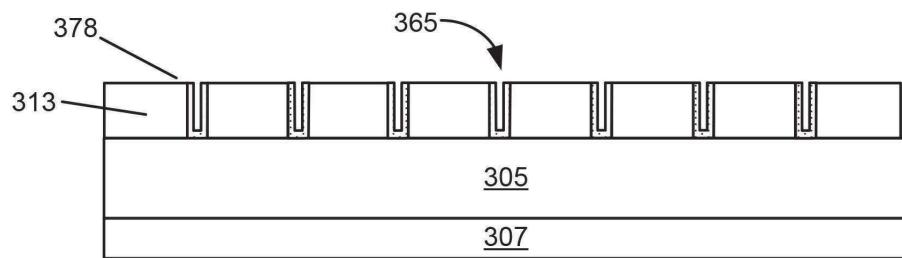

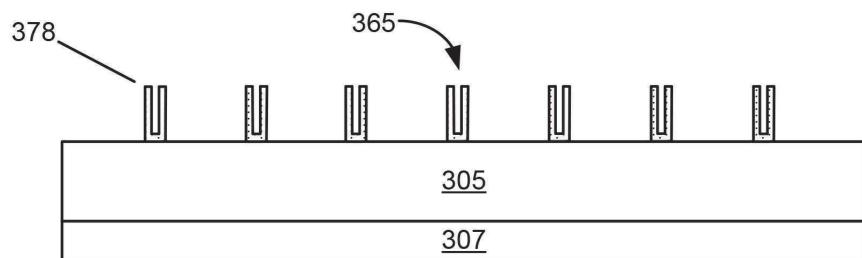

[0043] 동작 203에서, 스페이서 재료를 포함하는 컨포멀한 막은 패터닝된 코어 재료 위에 증착되고 컨포멀한 막은 패터닝된 코어 재료의 측벽들 상에 수직 스페이서들을 형성하도록 지향성으로 예칭된다. 도 3a는 하부층 (307), 타깃 층 (305), 패터닝된 코어 재료 (313), 및 스페이서들 (321) 을 포함하는 예시적인 기판의 개략적인 예시를 제공한다. 이는 도 2의 동작 203을 수행한 후 기판 상의 패턴의 예이다. 동작 203은 도 3j 내지 도 3o에 대해 이하에 기술된 바와 같이 일부 실시예들에서 선택 가능할 수도 있다는 것을 주의한다.

[0044] 다시 도 2를 참조하면, 동작 205에서, 캡충진 재료는 ALD에 의해 기판 위에 증착된다. 캡충진 재료는 실리콘 함유 재료 또는, 일부 실시예들에서, 티타늄 함유 재료일 수도 있다. 예들은 실리콘 옥사이드, 실리콘 나이트라이드, 실리콘 카바이드, 및 티타늄 옥사이드를 포함한다. 캡충진 재료는 임의의 적합한 온도, 예컨대 약 50 °C 내지 약 400 °C, 또는 약 100 °C 미만, 예컨대 약 50 °C에서 증착될 수도 있다. 캡충진 재료는 임의의 적합한 전구체, 예컨대 비스디에틸아미노실란, 비스터트부틸아미노실란, 및 디이소프로필아미노실란을 사용하여 증착될 수도 있다. 다른 전구체들이 이하에 기술된다.

[0045] 캡충진 재료는 ALD를 사용하여 컨포멀하게 증착된다. ALD는 순차적인 자기-제한 반응들을 사용하여 재료의 박층들을 증착하는 기법이다. ALD 프로세스들은 층 단위 (layer-by-layer basis) 로 막들을 사이클들로 증착하기 위한 표면 매개 반응들을 사용한다. 예로서, ALD 사이클은 이하의 동작들: (i) 전구체의 전달/흡착, (ii) 챔버로부터 전구체의 퍼지, (iii) 제 2 반응물질의 전달 및 선택 가능하게 플라즈마 점화 (ignite) 및 (iv) 챔버로부터 부산물들의 퍼지를 포함할 수도 있다. 기판의 표면 상에 막을 형성하기 위한 제 2 반응물질과 흡착된 전구체 간의 반응은 막 조성 및 특성들, 예컨대 불균일성, 응력, 습식 예칭 레이트, 건식 예칭 레이트, 전기적 특성들 (예를 들어, 브레이크다운 전압 및 누설 전류) 등에 영향을 준다.

[0046] ALD 프로세스의 일 예에서, 표면 활성 사이트들의 집단 (population of surface active sites) 을 포함하는 기판 표면은 기판을 하우징하는 챔버에 제공된 도즈의, 실리콘 함유 전구체와 같은 제 1 전구체의 가스 상 분포에 노출된다. 이 제 1 전구체 분자들은 제 1 전구체의 화학흡착된 종 및/또는 물리흡착된 분자들을 포함하여, 기판 표면 상에 흡착된다. 본 명세서에 기술된 바와 같이 화합물이 기판 표면 상에 흡착될 때, 흡착된 종은 화합물 뿐만 아니라 화합물의 유도체들을 포함할 수도 있다는 것이 이해되어야 한다. 예를 들어, 흡착된 실리콘 함유 전구체의 종은 실리콘 함유 전구체 뿐만 아니라 실리콘 함유 전구체의 유도체들을 포함할 수도 있다. 제 1 전구체 도즈 후에, 이어서 흡착된 종 대부분 또는 흡착된 종만이 남아 있도록 가스 상으로 남아 있는 제 1 전구체 대부분 또는 전부를 제거하도록 챔버가 배기된다. 일부 구현예들에서, 챔버는 완전히 배기되지 않을 수도 있다. 예를 들어, 반응기는 가스 상의 제 1 전구체의 분압이 반응을 완화시키기에 충분히 낮도록 배기될 수도 있다. 제 2 반응물질, 예컨대 산소 함유 가스는 이를 분자들 중 일부가 표면 상에 흡착된 제 1 전구체와 반응하도록 챔버로 도입된다. 일부 프로세스들에서, 제 2 반응물질은 흡착된 제 1 전구체와 즉시 반응한다. 다른 실시예들에서, 제 2 반응물질은 플라즈마와 같은 활성화 소스가 일시적으로 인가된 후에만 반응한다. 이어서 챔버는 결합되지 않은 제 2 반응물질 분자들을 제거하도록 다시 배기될 수도 있다. 상기 기술된 바와 같이, 일부 실시예들에서, 챔버는 완전히 배기되지 않을 수도 있다. 부가적인 ALD 사이클들이 막 두께를 구축하도록 사용될 수도 있다.

[0047] 일부 구현예들에서, ALD 방법들은 플라즈마 활성화를 포함한다. 본 명세서에 기술된 바와 같이, 본 명세서에

기술된 ALD 방법들 및 장치들은 2011년 4월 11일 출원되고, 명칭이 "PLASMA ACTIVATED CONFORMAL FILM DEPOSITION"인 미국 특허 출원번호 제 13/084,399 호 (현재 미국 특허 제 8,728,956 호), 및 2011년 4월 11일 출원되고, 명칭이 "SILICON NITRIDE FILMS AND METHODS"인 미국 특허 출원번호 제 13/084,305 호에 대체로 기술되고, 이들은 전체가 본 명세서에 참조로서 인용된, CFD (conformal film deposition) 방법들 및 장치들일 수도 있다.

[0048] 실리콘 옥사이드 캡충진 재료의 증착을 위해, 기판은 다음과 같은 사이클들에 노출될 수도 있다. 실리콘 함유 전구체는 기판 표면 상에 실리콘 함유 전구체를 흡착시키도록 도입된다. 개시된 실시예들에 따라 사용하기 적합한 실리콘 함유 전구체들은 폴리실란들 ( $H_3Si-(SiH_2)_n-SiH_3$ ) (여기서  $n \geq 0$ ) 을 포함한다. 실란들의 예들은 실란 ( $SiH_4$ ), 디실란 ( $Si_2H_6$ ), 및 유기 실란들, 예컨대 예를 들어 메틸실란, 에틸실란, 이소프로필실란 (isopropylsilane), t-부틸실란 (t-butyldsilane), 디메틸실란 (dimethylsilane), 디에틸실란 (diethylsilane), 디-t-부틸실란 (di-t-butyldsilane), 알릴실란 (allylsilane), sec-부틸실란 (sec-butyldsilane), 티헥실실란 (thexylsilane), 이소아밀실란 (isoamylsilane), t-부틸디실란 (t-butyldisilane), 디-t-부틸디실란 (di-t-butyldisilane), 등이다.

[0049] 할로실란은 적어도 하나의 할로겐기를 포함하고 수소기 및/또는 탄소기를 포함할 수도 있고 또는 포함하지 않을 수도 있다. 할로실란들의 예들은 요오드실란들, 브로모실란들, 클로로실란들 및 플루오로실란들이다. 할로실란들, 특히 플루오로실란들은 플라즈마가 스트라이킹될 때 실리콘 재료들을 에칭할 수 있는 반응성 할라이드 종을 형성할 수도 있지만, 할로실란이 일부 실시예들에서, 플라즈마가 스트라이킹될 때 챔버로 도입되지 않을 수도 있어서, 할로실란으로부터 반응성 할라이드 종의 형성이 완화될 수도 있다. 구체적인 클로로실란들은 테트라클로로실란, 트리클로로실란, 디클로로실란, 모노클로로실란, 클로로아릴실란, 클로로메틸실란, 디클로로메틸실란, 클로로디메틸실란, 클로로에틸실란, t-부틸클로로실란, 디-t-부틸클로로실란, 클로로이소프로필실란, 클로로-sec-부틸실란, t-부틸디메틸클로로실란, 텍실디메틸클로로실란, 등이다.

[0050] 아미노실란은 실리콘 원자에 결합된 적어도 하나의 질소 원자를 포함하지만, 또한 수소들, 산소들, 할로겐들, 및 탄소들을 함유할 수도 있다. 아미노실란들의 예들은 모노-아미노실란, 디-아미노실란, 트리-아미노실란 및 테트라-아미노실란 (각각  $H_3Si(NH_2)$ ,  $H_2Si(NH_2)_2$ ,  $HSi(NH_2)_3$  및  $Si(NH_2)_4$  뿐만 아니라, 치환된 모노-아미노실란, 디-아미노실란, 트리-아미노실란 및 테트라-아미노실란, 예를 들어, t-부틸아미노실란, 메틸아미노실란, tert-부틸실릴아민, BTBAS (bis(tertiarybutylamino)silane) ( $SiH_2(NHC(CH_3)_3)_2$ ), tert-부틸 실릴카바메이트,  $SiH(CH_3)-(N(CH_3)_2)_2$ ,  $SiHCl-(N(CH_3)_2)_2$ ,  $(Si(CH_3)_2NH)_3$  등이다. 아미노실란의 다른 예는 트리실릴아민 ( $N(SiH_3)_3$ )이다.

[0051] 프로세싱될 기판을 하우징하는 챔버는 기판 표면 상에 흡착되지 않은 전구체들을 제거하도록 퍼지될 수도 있다. 챔버를 퍼지하는 것은 다른 동작들에서 사용된 캐리어 가스일 수도 있고 또는 상이한 가스들일 수도 있는, 퍼지 가스 또는 스윕 가스를 흘리는 것을 수반할 수도 있다. 예시적인 퍼지 가스들은 아르곤, 질소, 수소 및 헬륨을 포함한다. 다양한 실시예들에서, 퍼지 가스는 불활성 가스이다. 예시적인 불활성 가스들은 아르곤, 질소 및 헬륨을 포함한다. 일부 실시예들에서, 퍼지는 챔버를 배기하는 것을 수반할 수도 있다. 일부 실시예들에서, 퍼지는 프로세스 챔버를 배기하기 위한 하나 이상의 배기 서브페이즈들을 포함할 수도 있다. 대안적으로, 일부 실시예들에서, 퍼지가 생략될 수도 있다는 것이 이해될 것이다.

[0052] 흡착된 실리콘 함유 전구체의 층을 포함하는 기판은 산화제에 노출되고 플라즈마는 산화 플라즈마를 사용하여 흡착된 전구체들을 실리콘 옥사이드로 변환하는 조건들 하에서 점화된다. 예시적인 산화제들은 산소 가스, 물, 이산화탄소, 아산화질소 및 이들의 조합들을 포함한다. 다양한 실시예들에서, 플라즈마가 점화되는 동안 기판은 산화제 및 불활성 가스에 동시에 노출된다. 예를 들어, 일 실시예에서, 플라즈마가 점화되는 동안 산소 및 아르곤 혼합물이 기판에 도입된다. 이어서 챔버는 실리콘 옥사이드를 형성하는 반응으로부터 반응되지 않은 산화제 및/또는 부산물들을 제거하도록 다시 퍼지될 수도 있다. 이들 도즈, 퍼지, 변환, 퍼지 동작들은 기판 위에 층단위로 캡충진 재료를 컨포멀하게 증착하도록 복수의 사이클들로 반복될 수도 있다.

[0053] 도 3b는 기판 위에 컨포멀하게 증착되는 캡충진 재료 (395) 의 예시적인 개략적인 예시를 도시한다. 보다 많은 사이클들이 수행되기 때문에, 스페이서들 (321) 간의 피처들이 충진되고, 도 3c에 도시된 바와 같이 측벽들 상에 증착된 재료가 만나는 심 (360) 이 형성될 수도 있다. 도 3c는 패터닝된 코어 재료 (313) 의 상단 표면 위에 오버버든을 포함하도록 증착된 캡충진 재료 (396) 를 포함한다. 일부 실시예들에서, 캡들을 완전히 충진하기 불충분한 지속기간 동안 증착하거나 피처를 언더필하도록 도 2의 동작 205의 캡충진 재료 증착이 다수의 사

이클들로 수행될 수도 있다는 것을 주의한다. 언더필은 도 3h 및 도 3i에 대해 이하에 더 기술된다. 일부 실시예들에서, 동작 205에서 증착된 캡충진 재료는 완전한 충진 및 언더필 실시예들 모두에 대해 도 3j 내지 도 3o에 대해 이하에 기술된 바와 같이, 대칭적 스페이서들을 형성하기 위한 재료로서 사용된다.

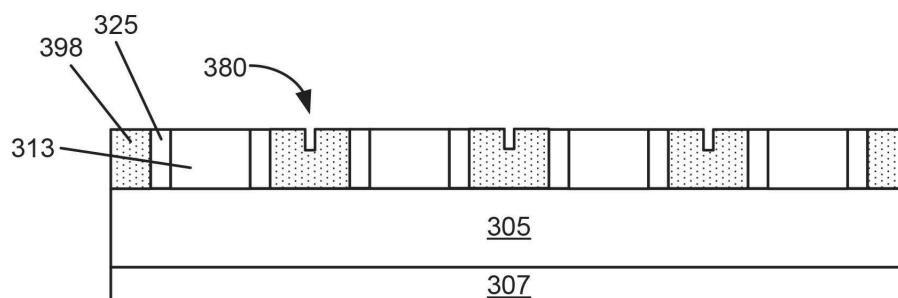

[0054] 다시 도 2를 참조하면, 동작 207에서, 캡충진 재료는 평면형 표면을 형성하도록 예칭 백된다. 예칭 백 또는 평탄화는 습식 예칭 프로세스, 건식 예칭 프로세스 또는 CMP (chemical mechanical planarization) 를 사용하여 수행될 수도 있다. 다양한 실시예들에서, 동작 207은 캡충진 재료, 스페이서 재료, 및 패터닝된 코어에 걸쳐 평면형 표면을 형성하기 위한 평탄화를 더 포함한다. 일 예가 예칭된 캡충진 재료 (399), 스페이서 재료 (325), 및 코어 재료 (313) 가 평탄화된 도 3d에 제공된다. 예칭된 캡충진 재료 (399) 에 작은 심 (360) 이 남아 있을 수도 있다는 것을 주의한다.

[0055] 대안적인 실시예에서, 기판 상의 피처들이 언더필되도록 캡충진 재료를 증착하기 위해 도 2의 동작 205가 수행된다. 예를 들어, ALD의 증착 사이클들은 측벽들 상에 증착된 막 사이의 공간의 거리가 약 5 nm 내지 약 50 nm 이도록 다수의 사이클들로 반복될 수도 있다. 예는 언더필 실시예들을 위해 도 3b에 이어지는 도 3h에 도시된다. 캡충진 재료는 도 3h에 도시된 바와 같이 기판이 언더필되어 피처들의 중심에 작은 캡 (380) 이 남아 있을 때까지 도 3b에서 ALD에 의해 기판 위에 커포멀하게 증착된다. 증착될 캡충진 재료의 양은 적어도 측벽들 상에 충분한 두께를 제공하도록 증착된 양에 따른다. 일부 실시예들에서, 피처는 약 x nm 미만의 피처 개구부들을 갖고 캡충진 재료는 약  $0.4 \times x$  nm 내지 약  $0.5 \times x$  nm의 두께로 캡충진 재료를 증착하기 충분한 지속기간 동안 증착된다. 일부 실시예들에서, 피처는 약 5 nm 미만의 피처 개구부들을 갖고 캡충진 재료는 약 2 nm 내지 약 2.5 nm의 두께로 캡충진 재료를 증착하기 충분한 지속기간 동안 증착된다. 예를 들어, 캡충진 재료는 약 50 nm의 피처 개구부를 갖는 피처들에 대해 약 20 nm 내지 약 30 nm의 두께로 증착될 수도 있다. 도 3c에 도시된 바와 같은 심을 형성하기 위해 피처를 완전히 충진하는 대신, 기판은 여전히 작은 캡 (380) 을 갖는, 예칭된 캡충진 재료 (398) 를 형성하도록 동작 207에서 예칭 백될 수도 있다. 그러나, 캡충진 재료가 대칭적 스페이서들 (325) 을 형성하는데 사용된 희생적 층이기 때문에, 동작 205의 캡충진 재료는 일부 실시예들에서, 완전히 충진되는 대신 언더필될 수도 있다.

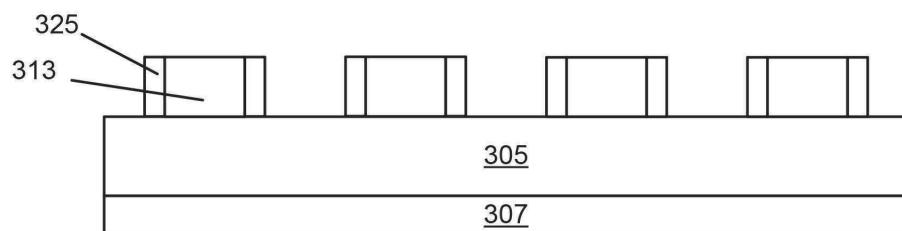

[0056] 도 2를 다시 참조하면, 동작 209에서, 캡충진 재료는 기판 상에 패터닝된 코어 재료 및 스페이서 재료를 남기도록 선택적으로 제거된다. 일 예는 도 3e에 제공된다. 도시된 바와 같이, 캡충진 재료는 타깃 층 (305) 위에 코어 재료 (313) 및 측벽 스페이서들 (325) 을 산출하도록 제거된다. 대칭적 스페이서들을 형성하기 위해 캡충진 재료가 사용되는 실시예들에서, 이 동작은 수행되지 않는다는 것을 주의한다.

[0057] 도 2를 다시 참조하면, 동작 211에서, 코어 재료는 마스크로서 대칭적 스페이서들을 형성하도록 선택적으로 예칭된다. 일 예는 도 3f에 제공된다. 도시된 바와 같이, 스페이서들 (325) 은 대칭적이고 도 1i에 도시된 스페이서들 (121) 과 비교하여 리닝을 겪지 않는다.

[0058] 도 2를 다시 참조하면, 동작 215에서, 대칭적 스페이서들을 마스크로서 사용하여 타깃 층이 예칭된다. 도 1j에 발생된 가변된 CD와 비교하여, 예칭된 타깃 층 (315) 이 일관된 CD a를 갖도록 일 예가 도 3g에 제공된다.

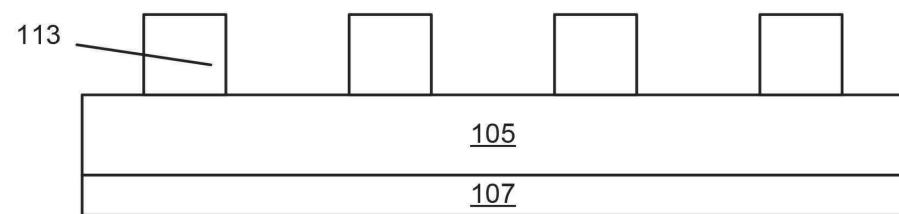

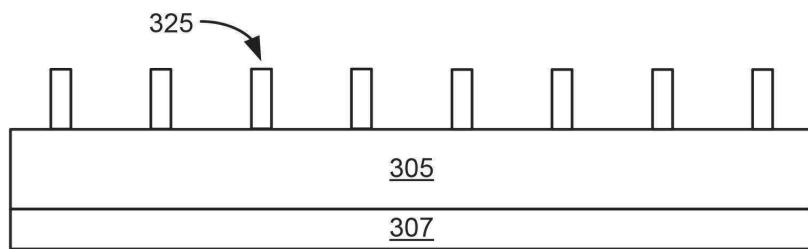

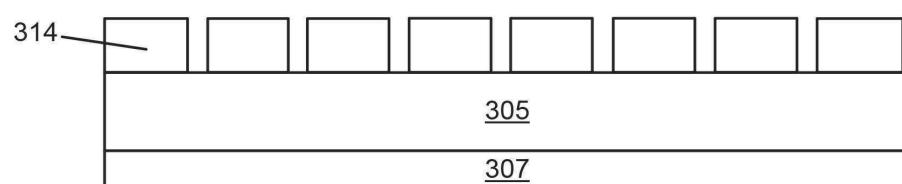

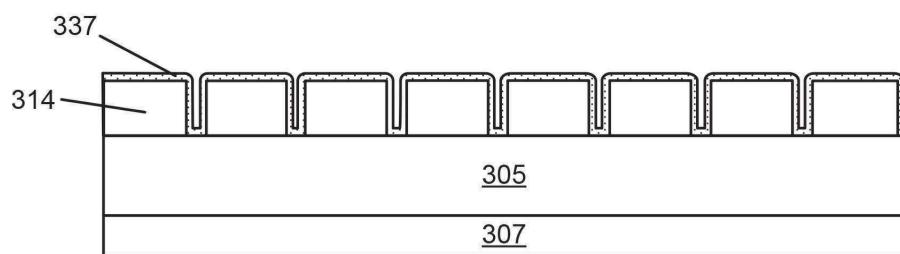

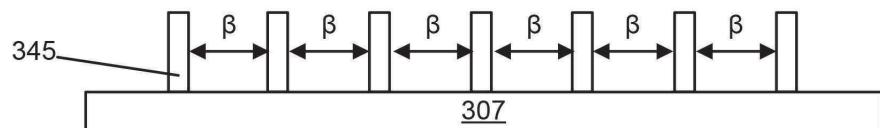

[0059] 도 3j 내지 도 3r은 특정한 개시된 실시예들을 수행하기 위한 대안적인 실시예들을 제공한다. 예를 들어, 도 3j 내지 도 3o는 도 2의 동작 205가 수행되지 않도록 기판 위에 캡충진 재료를 바로 증착함으로써 캡충진 재료를 사용하여 단독으로 서 있는 대칭적 스페이서들을 형성하는 것을 수반한다. 도 3p 내지 도 3r은 언더필을 수반하여 도 2의 동작 203이 수행되지 않고 언더필된 캡충진 재료가 타깃 층을 패터닝하기 위한 스페이서들로서 사용되는 또 다른 실시예의 예를 제공한다. 이를 실시예들은 이하에 더 상세히 기술된다.

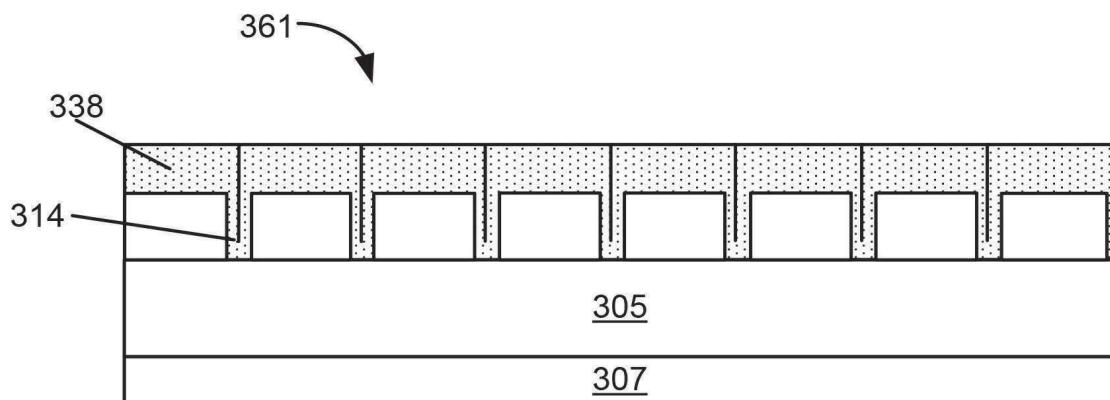

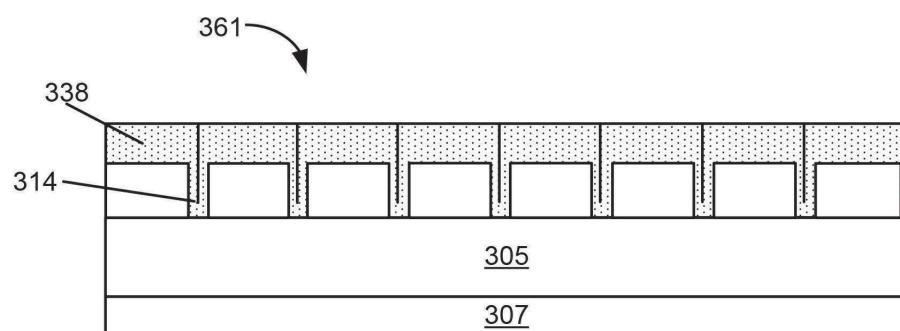

[0060] 도 3j에서, 하부층 (307), 타깃 층 (305), 및 패터닝된 코어 (314) 를 포함하는 기판이 제공된다. 도 3k에서, 캡충진 재료 (337) 는 ALD를 사용하여 기판 위에 커포멀하게 증착된다. 사용될 수도 있는 예시적인 캡충진 재료 및 사용될 수도 있는 증착 기법들은 도 2의 동작 205에 대해 상기 기술되었다. 도 3l에서, 캡충진 재료 (338) 는 패터닝된 코어 (314) 사이의 피처들 또는 캡들이 완전히 충진될 때까지 증착되어, 측벽들 상의 증착된 재료가 만나는 심 (361) 의 형성을 유발한다. 일부 실시예들에서, 도 3p 내지 도 3r에 대해 이하에 기술된 바와 같이, 피처의 중간에 작은 캡을 남기도록 언더필이 수행될 수도 있다.

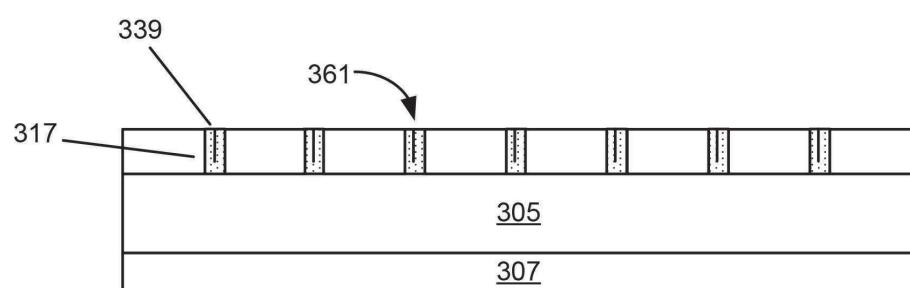

[0061] 도 3m에서, 기판은 이제 평탄화된 코어 (317) 및 평탄화된 캡충진 재료 (339) 를 포함하는 평면형 표면을 산출하도록 평탄화된다. 심 (361) 은 여전히 캡충진 재료 (339) 내에 존재할 수도 있다는 것을 주의한다. 평탄화는 도 2에 대해 상기 기술된 바와 같은 동작 207에 따라 수행될 수도 있다. 도 3n에서, 평탄화된 코어 재료 (317) 는 각각이 심 (361) 을 포함할 수도 있는, 단독으로 서 있는 대칭적 스페이서들 (339) 을 남기도록 선택

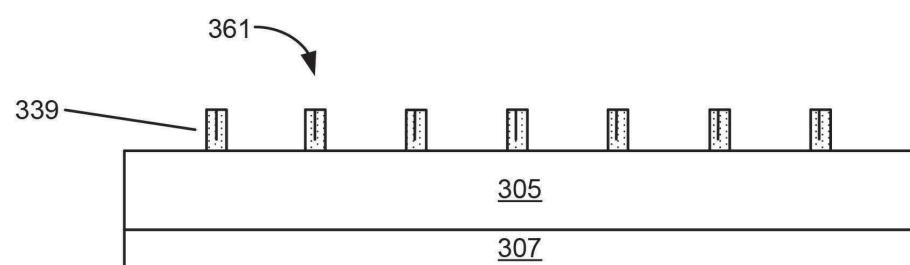

적으로 예칭된다. 코어 재료는 도 2의 동작 211에 대해 상기 기술된 바와 같이 제거될 수도 있다. 도 30에서, 대칭적 스페이서들이 타깃 층 (305) 을 예칭하기 위한 마스크로서 사용되고 이어서 마스크는 패터닝된 타깃 층 (335) 을 산출하도록 제거된다. 타깃 재료를 예칭하도록 사용된 예칭 종의 이온 각도 분포가 일관된 CD  $\beta$  를 갖는 패턴을 산출하기 위해 타깃 층을 효과적으로 예칭할 수 있다는 것을 주의한다.

[0062] 도 3p 내지 도 3r은 대칭적 스페이서 마스크로서 캡충진 재료를 사용하는 동안 피처들을 언더필하기 위한 대안적인 실시예를 제공한다. 예를 들어, 도 3p의 기판은 피처들을 부분적으로 충진하기 위해 복수의 ALD 사이클들을 겪을 수도 있어, 피처들 내에 캡 (365) 을 남긴다. 기판은 캡충진 재료 (378) 의 필드 영역들이 코어 재료 (313) 의 필드 영역들과 같은 높이인 (flush with) 평坦화된 표면을 갖는 도 3p에 도시된 기판을 산출하도록 도 2의 동작 205마다 평탄화될 수도 있다. 도 3q에서, 각각이 피처들을 언더필함으로써 여전히 캡 (365) 을 포함할 수도 있는, 단독으로 서 있는 대칭적 스페이서들 (378) 을 산출하도록 코어 재료는 도 2의 동작 211마다 선택적으로 제거된다. 스페이서들 (378) 은 타깃 층 (305) 을 패터닝하도록 사용될 수도 있고 그리고 스페이서들 (378) 이 대칭적이기 때문에 타깃 층 (305) 을 예칭하도록 사용된 예칭 종의 이온 각도 분포는 각도 예칭을 발생시키지 않아, 일관된 CD  $\beta$  를 갖는 패터닝된 타깃 층 (345) 을 형성한다.

[0063] 특정한 개시된 실시예들은 캡충진 재료이 약 2 nm 내지 약 200 nm의 CD를 갖는 기준의 피처들 내로 중착되는 애플리케이션들에 적합하다. 개시된 실시예들은 20 nm 미만 노드의 애플리케이션들에 적합하다. 개시된 실시예들은 또한 캡충진 재료가 약 20:1보다 큰 종횡비들을 갖는 기준 피처들 내로 중착되는, 패터닝된 기판들을 형성하기 적합하다.

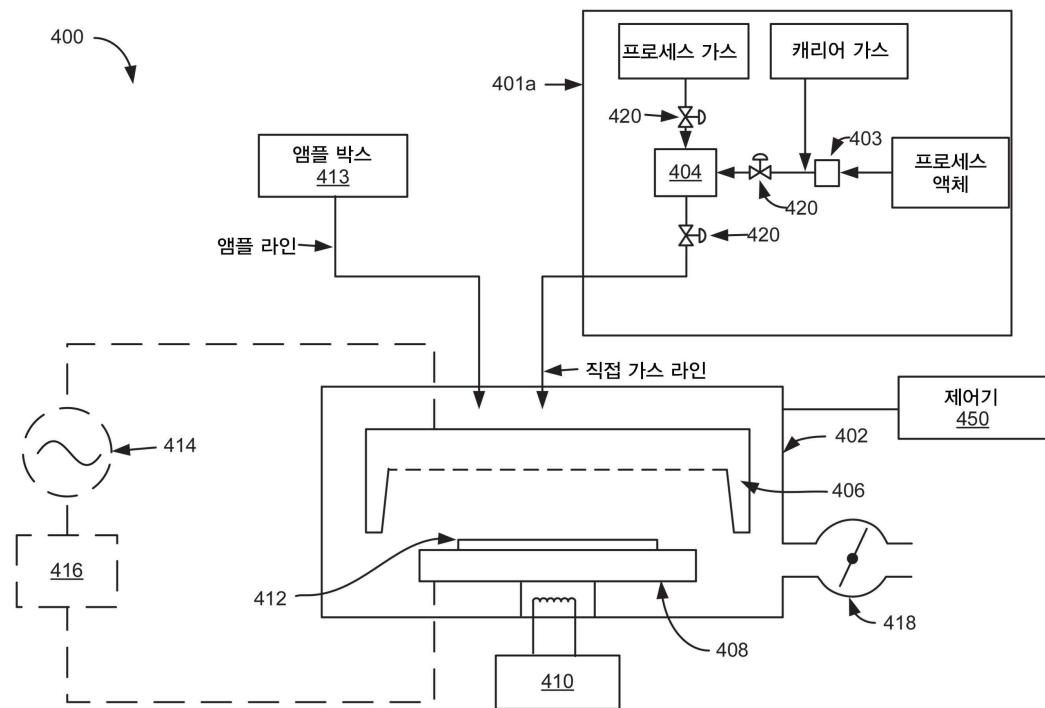

[0064] 장치

[0065] 도 4는 프로세스 챔버 (402) 를 갖는 ALD 프로세스 스테이션 (400) 의 실시예의 개략적인 예시를 도시한다. 프로세스 챔버 (402) 는 저압 분위기를 유지하는데 사용될 수도 있다. 복수의 ALD 프로세스 스테이션들이 공통 저압 프로세스 툴 분위기에 포함될 수도 있다. 예를 들어, 도 5는 멀티-스테이션 프로세싱 툴 (500) 의 실시예를 도시한다. 일부 실시예들에서, 이하에 상세히 논의된 것들을 포함하는, ALD 프로세스 스테이션 (400) 의 하나 이상의 하드웨어 파라미터들은 하나 이상의 컴퓨터 제어기들 (450) 에 의해 프로그램적으로 조정될 수도 있다.

[0066] ALD 프로세스 스테이션 (400) 은 분배 샤워헤드 (406) 로 프로세스 가스들을 전달하기 위한 반응 물질 전달 시스템 (401a) 과 유체적으로 통신한다. 반응 물질 전달 시스템 (401) 은 샤워헤드 (406) 로의 전달을 위해 프로세스 가스들, 예컨대 실리콘 함유 가스, 또는 산소 함유 가스를 블렌딩 (blending) 및/또는 컨디셔닝 (conditioning) 하기 위한 혼합 용기 (404) 를 포함한다. 하나 이상의 혼합 용기 유입부 밸브들 (420) 이 혼합 용기 (404) 로의 프로세스 가스들의 도입을 제어할 수도 있다.

[0067] 예로서, 도 4의 실시예는 혼합 용기 (404) 로 공급될 액체 반응 물질을 기화하기 위한 기화 지점 (403) 을 포함한다. 일부 실시예들에서, 기화 지점 (403) 은 가열된 기화기일 수도 있다. 이러한 증발기들로부터 생산된 포화된 반응 물질 증기는 다운스트림 전달 파이프에서 응결될 수도 있다. 양립 가능하지 않은 가스들의 응결된 반응 물질로의 노출은 작은 입자들을 생성할 수도 있다. 이들 작은 입자들은 파이프를 막고, 밸브 동작을 지연시키고, 기판을 오염시키는 등을 할 수도 있다. 이러한 문제들을 해결하기 위한 일부 방법들은 잔류 반응 물질을 제거하기 위해 전달 파이프를 퍼지 및/또는 배기하는 것을 포함할 수도 있다. 그러나, 전달 파이프를 퍼지하는 것은 프로세스 스테이션 쓰루풋을 저하시키는, 프로세스 스테이션 사이클 시간을 상승시킬 수도 있다. 따라서, 일부 실시예들에서, 기화 지점 (403) 의 전달 파이프 다운스트림은 열 추적될 수도 있다. 일부 예들에서, 혼합 용기 (404) 가 또한 열 추적될 수도 있다. 일 비제한적 예에서, 기화 지점 (403) 의 파이프 다운스트림은 혼합 용기 (404) 에서 대략 100 °C에서 대략 150 °C로 연장하는 상승하는 온도 프로파일을 갖는다.

[0068] 일부 실시예들에서, 액체 전구체 또는 액체 반응물질이 액체 주입기 (미도시) 에서 기화될 수도 있다. 예를 들어, 액체 주입기는 액체 반응물질의 월스들을 혼합 용기 (404) 의 캐리어 가스 스트림 업스트림 내로 주입할 수도 있다. 일 실시예에서, 액체 주입기는 보다 높은 압력으로부터 보다 낮은 압력으로 액체를 플래싱함으로써 반응물질을 기화할 수도 있다. 또 다른 예에서, 액체 주입기는 가열된 전달 파이프에서 후속하여 기화되는 확산된 마이크로드롭릿들로 액체를 원자화 (atomize) 할 수도 있다. 보다 작은 드롭릿들이 보다 큰 드롭릿들보다 빠르게 기화될 수도 있고, 액체 주입과 완전한 기화 사이의 지연을 감소시킨다. 보다 빠른 기화는 기화 지점 (403) 으로부터 다운스트림 파이프의 길이를 감소시킬 수도 있다. 일 시나리오에서, 액체 주입기는 혼합 용기 (404) 에 바로 장착될 수도 있다. 또 다른 시나리오에서, 액체 주입기는 샤워헤드 (406) 에 바로 장착될 수도 있다.

- [0069] 일부 실시예들에서, 기화 지점 (403)의 업스트림에 LFC (liquid flow controller) 가 기화 및 프로세싱 챔버 (402)로의 전달을 위해 액체의 대량 플로우를 제어하기 위해 제공될 수도 있다. 예를 들어, LFC는 LFC의 다운 스트림에 위치된 MFM (thermal mass flow meter) 를 포함할 수도 있다. 이어서 LFC의 플런저 밸브가 MFM과 전기적으로 통신하는 PID (proportional-integral-derivative) 제어기에 의해 제공된 피드백 제어 신호들에 응답하여 조정될 수도 있다. 그러나, 이는 피드백 제어를 사용하여 액체 플로우를 안정화시키기 위해 1 초 이상 걸릴 수도 있다. 이는 액체 반응물질을 도장하기 위한 시간을 연장할 수도 있다. 따라서, 일부 실시예들에서, LFC는 피드백 제어 모드와 직접 제어 모드 사이에서 동적으로 스위칭될 수도 있다. 일부 실시예들에서, LFC는 LFC 및 PID 제어기의 센스 튜브를 디스에이블함으로써 수행될 수도 있다.

- [0070] 샤크헤드 (406)는 기관 (412)을 향해 프로세스 가스들을 분배한다. 도 4에 도시된 실시예에서, 기관 (412)은 샤크헤드 (406) 밑에 위치되고 페데스탈 (408) 상에 놓인 것으로 도시된다. 샤크헤드 (406)는 임의의 적합한 형상을 가질 수도 있고, 기관 (412)으로 프로세스 가스들을 분배하기 위한 임의의 적합한 수 및 배열의 포트들을 가질 수도 있다.

- [0071] 일부 실시예들에서, 페데스탈 (408)은 기관 (412)과 샤크헤드 (406) 사이의 볼륨에 기관 (412)을 노출하도록 상승되거나 하강될 수도 있다. 일부 실시예들에서, 페데스탈 (408)은 히터 (410)를 통해 제어된 온도일 수도 있다. 페데스탈 (408)은 다양한 개시된 실시예들을 수행하기 위한 동작들 동안 약 25 °C 내지 약 650 °C와 같은 임의의 적합한 온도로 설정될 수도 있다. 일부 실시예들에서, 페데스탈 높이가 적합한 컴퓨터 제어기 (450)에 의해 프로그램적으로 조정될 수도 있다는 것이 이해될 것이다.

- [0072] 또 다른 시나리오에서, 페데스탈 (408)의 높이를 조정하는 것은 플라즈마 밀도로 하여금 특정한 개시된 실시예들에서 수행된 플라즈마 활성화 사이클들 동안 가변되게 할 수도 있다. 프로세스 페이즈의 종료시, 페데스탈 (408)은 페데스탈 (408)로부터 기관 (412)의 제거를 허용하도록 또 다른 기관 이송 페이스 동안 하강될 수도 있다.

- [0073] 일부 실시예들에서, 샤크헤드 (406)의 위치는 기관 (412)과 샤크헤드 (406) 사이의 볼륨을 가변시키도록 페데스탈 (408)에 대해 조정될 수도 있다. 또한, 페데스탈 (408) 및/또는 샤크헤드 (406)의 수직 위치는 본 개시의 범위 내의 임의의 적합한 메커니즘에 의해 가변될 수도 있다는 것이 이해될 것이다. 일부 실시예들에서, 페데스탈 (408)은 기관 (412)의 배향을 회전시키기 위한 회전 축을 포함할 수도 있다. 일부 실시예들에서, 하나 이상의 이를 예시적인 조정들은 하나 이상의 적합한 컴퓨터 제어기들 (450)에 의해 프로그램적으로 수행될 수도 있다는 것이 이해될 것이다. 컴퓨터 제어기 (450)는 도 5의 제어기 (550)에 대해 이하에 기술된 임의의 피처들을 포함할 수도 있다.

- [0074] 일부 실시예들에서, 상기 논의된 바와 같이 플라즈마가 사용될 수도 있으면, 샤크헤드 (406) 및 페데스탈 (408)은 플라즈마에 전력을 공급하기 위해, RF (radio frequency) 전력 공급부 (414) 및 매칭 네트워크 (416)와 전기적으로 통신한다. 일부 실시예들에서, 플라즈마 에너지는 하나 이상의 프로세스 스테이션 압력, 가스 농도, RF 소스 전력, RF 소스 주파수 및 플라즈마 전력 펄스 타이밍을 제어함으로써 제어될 수도 있다. 예를 들어, RF 전력 공급부 (414) 및 매칭 네트워크 (416)는 목표된 조성의 라디칼 종을 갖는 플라즈마를 형성하도록 임의의 적합한 전력에서 동작될 수도 있다. 유사하게, RF 전력 공급부 (414)는 임의의 적합한 주파수의 RF 전력을 제공할 수도 있다. 일부 실시예들에서, RF 전력 공급부 (414)는 HF (high-frequency) RF 전력 소스 및 LF (low-frequency) RF 전력 소스를 서로 독립적으로 제어하도록 구성될 수도 있다. 예시적인 LF RF 주파수들은 이들로 제한되는 것은 아니지만, 0 kHz 내지 500 kHz의 주파수들을 포함할 수도 있다. 예시적인 HF RF 주파수들은 이로 제한되는 것은 아니지만, 1.8 MHz 내지 2.45 GHz, 또는 약 13.56 MHz 초파, 또는 27 MHz 초파, 또는 40 MHz 초파, 또는 60 MHz 초파의 주파수들을 포함할 수도 있다. 표면 반응들을 위한 플라즈마 에너지를 제공하기 위해 임의의 적합한 파라미터들이 이산적으로 또는 연속적으로 조절될 수도 있다는 것이 이해될 것이다.

- [0075] 일부 실시예들에서, 플라즈마는 하나 이상의 플라즈마 모니터들에 의해 인시츄 모니터링될 수도 있다. 일 시나리오에서, 플라즈마 전력은 하나 이상의 전압, 전류 센서들 (예를 들어, VI 프로브들)에 의해 모니터링될 수도 있다. 또 다른 시나리오에서, 플라즈마 밀도 및/또는 프로세스 가스 농도는 하나 이상의 OES (optical emission spectroscopy) 센서들에 의해 측정될 수도 있다. 일부 실시예들에서, 하나 이상의 플라즈마 파라미터들은 이러한 인 시츄 플라즈마 모니터들로부터의 측정치들에 기초하여 프로그램적으로 조정될 수도 있다. 예를 들어, OES 센서는 플라즈마 전력의 프로그램적인 제어를 제공하기 위해 피드백 루프에서 사용될 수도 있다. 일부 실시예들에서, 플라즈마 및 다른 프로세스 특성들을 모니터링하기 위해 다른 모니터들이 사용될 수도 있다는 것이 이해될 것이다. 이러한 모니터들은 이로 제한되는 것은 아니지만, 적외선 (IR) 모니터들, 음향 모니터들,

및 압력 트랜스듀서들을 포함할 수도 있다.

[0076] 일부 실시예들에서, 제어기 (450)에 대한 인스트럭션들은 IOC (input/output control) 시퀀싱 인스트럭션들을 통해 제공될 수도 있다. 일부 예에서, 프로세스 페이즈에 대한 조건들을 설정하기 위한 인스트럭션들은 프로세스 레시피의 대응하는 레시피 페이즈에 포함될 수도 있다. 일부 경우들에서, 프로세스 레시피 페이즈들은 프로세스 페이즈에 대한 모든 인스트럭션들이 이 프로세스 페이즈와 동시에 실행되도록 순차적으로 배열될 수도 있다. 일부 실시예들에서, 하나 이상의 반응기 파라미터들을 설정하기 위한 인스트럭션들은 레시피 페이즈에 포함될 수도 있다. 예를 들어, 제 1 레시피 페이즈는 불활성 및/또는 반응물질 가스 (예를 들어, 실리콘 함유 전구체와 같은 제 1 전구체)의 플로우 레이트를 설정하기 위한 인스트럭션들, 캐리어 가스 (예컨대 아르곤)의 플로우 레이트를 설정하기 위한 인스트럭션들, 및 제 1 레시피 페이즈에 대한 시간 지연 인스트럭션들을 포함할 수도 있다. 제 2, 후속하는 레시피 페이즈는 불활성 및/또는 반응물질 가스의 플로우 레이트를 조절하거나 중지시키기 위한 인스트럭션들, 및 캐리어 또는 퍼지 가스의 플로우 레이트를 조절하기 위한 인스트럭션들 및 제 2 레시피 페이즈에 대한 시간 지연 인스트럭션들을 포함할 수도 있다. 제 3 레시피 페이즈는 산소와 같은 제 2 반응물질 가스의 플로우 레이트를 조절하기 위한 인스트럭션들, 및 캐리어 가스 또는 퍼지 가스의 플로우 레이트를 조절하기 위한 인스트럭션들, 고 플라즈마 에너지를 갖는 플라즈마를 점화시키기 위한 인스트럭션들 및 제 3 레시피 페이즈에 대한 시간 지연 인스트럭션들을 포함할 수도 있다. 제 4, 후속하는 레시피 페이즈는 불활성 가스 및/또는 반응물질 가스의 플로우 레이트를 조절하거나 중지시키기 위한 인스트럭션들 및 캐리어 가스 또는 퍼지 가스의 플로우 레이트를 조절하기 위한 인스트럭션들, 및 제 4 레시피 페이즈에 대한 시간 지연 인스트럭션들을 포함할 수도 있다. 이러한 레시피들은 대칭적인 스페이서들을 후속하여 형성하도록 패터닝된 기판 위에 캡충진 재료를 증착하도록 사용될 수도 있다. 일부 레시피들은 캡충진 재료로 패터닝된 기판을 언더필하도록 사용될 수도 있다. 이를 레시피 페이즈들은 더 세분화될 수도 있고 그리고/또는 본 개시의 범위 내의 임의의 적합한 방식으로 반복될 수도 있다는 것이 이해될 것이다.

[0077] 또한, 일부 실시예들에서, 프로세스 스테이션 (400)을 위한 압력 제어가 버터플라이 밸브 (418)에 의해 제공될 수도 있다. 도 4의 실시예에 도시된 바와 같이, 버터플라이 밸브 (418)는 다운스트림 진공 펌프 (미도시)에 의해 제공된 진공을 쓰로틀한다. 그러나, 일부 실시예들에서, 프로세스 스테이션 (400)의 압력 제어는 또한 프로세스 스테이션 (400)에 도입된 하나 이상의 가스들의 플로우 레이트를 가변시킴으로써 조정될 수도 있다.

[0078] 상기 기술된 바와 같이, 하나 이상의 프로세스 스테이션들은 멀티스테이션 프로세싱 툴에 포함될 수도 있다. 도 5는 인바운드 로드록 (502) 및 아웃바운드 로드록 (504) 중 하나 또는 모두가 리모트 플라즈마 소스 (미도시)를 포함할 수도 있는, 인바운드 로드록 (502) 및 아웃바운드 로드록 (504)을 갖는, 멀티스테이션 프로세싱 툴 (500)의 실시예의 개략도를 도시한다. 대기압에서 로봇 (506)은, 카세트로부터 포드 (508)를 통해 인바운드 로드록 (502)으로 로딩된 웨이퍼들을 대기 포트 (510)를 통해 이동시키도록 구성된다. 웨이퍼 (미도시)는 인바운드 로드록 (502) 내의 폐데스탈 (512) 상에 로봇 (506)에 의해 배치되고, 대기 포트 (510)는 폐쇄되고, 인바운드 로드록 (502)은 펌프 다운된다 (pump down). 인바운드 로드록 (502)이 리모트 플라즈마 소스를 포함하면, 웨이퍼는 프로세싱 챔버 (514) 내로 도입되기 전에 인바운드 로드록 (502) 내에서 리모트 플라즈마 처리에 노출될 수도 있다. 또한, 웨이퍼는 또한 예를 들어, 수분 및 흡착된 가스들을 제거하기 위해 인바운드 로드록 (502) 내에서 가열될 수도 있다. 다음에, 프로세싱 챔버 (514)로의 챔버 이송 포트 (516)가 개방되고, 또 다른 로봇 (미도시)이 프로세싱을 위해 반응기 내에 도시된 제 1 스테이션의 폐데스탈 상의 반응기 내로 웨이퍼를 배치한다. 도 5에 도시된 실시예는 로드록들을 포함하지만, 일부 실시예들에서, 웨이퍼의 프로세스 스테이션으로의 직접적인 진입이 제공될 수도 있다는 것이 인식될 것이다.

[0079] 도시된 프로세싱 챔버 (514)는 도 5에 도시된 실시예들에서 1 내지 4로 번호가 붙여진, 4 개의 프로세스 스테이션들을 포함한다. 스테이션 각각은 가열된 폐데스탈 (스테이션 1에 대해 518로 도시됨), 및 가스 라인 유입부들을 갖는다. 일부 실시예들에서, 프로세스 스테이션 각각이 상이한 목적 또는 다수의 목적들을 가질 수도 있다는 것이 이해될 것이다. 예를 들어, 일부 실시예들에서, 프로세스 스테이션은 ALD와 PEALD 프로세스 모드 사이에서 전환가능할 수도 있다. 일부 실시예들에서, 증착 전구체로의 노출 및 제 2 반응물질 및 플라즈마로의 노출은 동일한 스테이션에서 수행된다. 부가적으로 또는 대안적으로, 일부 실시예들에서, 프로세싱 챔버 (514)는 ALD 및 PEALD 프로세스 스테이션들의 하나 이상의 매칭된 쌍들을 포함할 수도 있다. 도시된 프로세싱 챔버 (514)는 4 개의 스테이션들을 포함하지만, 본 개시에 따른 프로세싱 챔버는 임의의 적합한 수의 스테이션들을 가질 수도 있다는 것이 이해될 것이다. 예를 들어, 일부 실시예들에서, 프로세싱 챔버는 5 개 이상의 스테이션들을 갖는 반면, 다른 실시예들에서 프로세싱 챔버는 3 개 이하의 스테이션들을 가질 수도 있다.

- [0080] 도 5는 또한 프로세싱 챔버 (514) 내에서 웨이퍼들을 이송하기 위한 웨이퍼 처리 시스템 (590)의 실시예를 도시한다. 일부 실시예들에서, 웨이퍼 처리 시스템 (590)은 다양한 프로세스 스테이션들 사이 및/또는 프로세스 스테이션과 로드 록 사이에서 웨이퍼들을 이송할 수도 있다. 임의의 적합한 웨이퍼 처리 시스템이 채택될 수도 있다는 것이 이해될 것이다. 비제한적인 예들은 웨이퍼 캐로줄들 (carousels) 및 웨이퍼 처리 로봇들을 포함한다. 도 5는 또한 프로세스 툴 (500)의 프로세스 조건들 및 하드웨어 상태들을 제어하도록 채용된 시스템 제어기 (550)의 실시예를 도시한다. 시스템 제어기 (550)는 하나 이상의 메모리 디바이스들 (556), 하나 이상의 대용량 저장 디바이스들 (554), 및 하나 이상의 프로세서들 (552)을 포함할 수도 있다. 프로세서 (552)는 CPU 또는 컴퓨터, 아날로그 입력/출력 연결부 및/또는 디지털 입력/출력 연결부, 스텝퍼 모터 제어 보드들, 등을 포함할 수도 있다.

- [0081] 일부 실시예들에서, 시스템 제어기 (550)는 프로세스 툴 (500)의 모든 액티비티들을 제어한다. 시스템 제어기 (550)는 대용량 저장 디바이스 (554)에 저장되고, 메모리 디바이스 (556)로 로딩되고, 프로세서 (552) 상에서 실행되는 시스템 제어 소프트웨어 (558)를 실행한다. 대안적으로, 제어 로직은 제어기 (550) 내에서 하드코딩될 수도 있다. ASIC, PLD (예를 들어, FPGA (field-programmable gate array)), 등이 이 목적들을 위해 사용될 수도 있다. 이하의 논의에서, "소프트웨어" 또는 "코드"가 사용될 때마다, 기능적으로 유사한 하드코딩된 로직이 그 자리에 사용될 수도 있다. 시스템 제어 소프트웨어 (558)는 타이밍, 가스들의 혼합, 가스 플로우 레이트들, 챔버 및/또는 스테이션 압력, 챔버 및/또는 스테이션 온도, 웨이퍼 온도, 타깃 전력 레벨들, RF 전력 레벨들, 기관 폐데스탈, 척 및/또는 서셉터 위치, 및 프로세스 툴 (500)에서 수행된 특정한 프로세스의 다른 파라미터들을 포함할 수도 있다. 시스템 제어 소프트웨어 (558)는 임의의 적합한 방식으로 구성될 수도 있다. 예를 들어, 다양한 프로세스 툴 구성요소 서브루틴들 또는 제어 객체들이 다양한 프로세스 툴 프로세스들을 수행하기 위해 사용된 프로세스 툴 구성요소들의 동작을 제어하도록 작성될 수도 있다. 시스템 제어 소프트웨어 (558)는 임의의 적합한 컴퓨터 판독가능 프로그래밍 언어로 코딩될 수도 있다.

- [0082] 일부 실시예들에서, 시스템 제어 소프트웨어 (558)는 상기 기술된 다양한 파라미터들을 제어하기 위한 IOC (input/output control) 시퀀싱 (sequencing) 인스트럭션들을 포함할 수도 있다. 시스템 제어기 (550)와 연관된 대용량 저장 디바이스 (554) 및/또는 메모리 디바이스 (556)에 저장된 다른 컴퓨터 소프트웨어 및/또는 프로그램들이 일부 실시예들에서 채용될 수도 있다. 이러한 목적을 위한 프로그램들 또는 프로그램들의 섹션들의 예들은 기관 포지셔닝 (positioning) 프로그램, 프로세스 가스 제어 프로그램, 압력 제어 프로그램, 히터 제어 프로그램, 및 플라즈마 제어 프로그램을 포함한다.

- [0083] 기관 포지셔닝 프로그램은 폐데스탈 (518) 상에 기관을 로딩하고 기관과 프로세스 툴 (500)의 다른 부분들 사이의 간격을 제어하도록 사용된 프로세스 툴 컴포넌트들에 대한 프로그램 코드를 포함할 수도 있다.

- [0084] 프로세스 가스 제어 프로그램은 프로세스 스테이션 내의 압력을 안정화시키기 위해 증착 전에 가스 조성 (예를 들어, 실리콘 함유 가스들, 산소 함유 가스들, 및 본 명세서에 기술된 바와 같은 퍼지 가스들) 및 플로우 레이트들을 제어하기 위한 코드 및 선택가능하게 하나 이상의 프로세스 스테이션들로 가스를 유동시키기 위한 코드를 포함할 수도 있다. 압력 제어 프로그램은 예를 들어, 프로세스 스테이션의 배기 시스템의 쓰로틀 밸브, 프로세스 스테이션으로의 가스 플로우, 등을 조절함으로써 프로세스 스테이션 내의 압력을 제어하기 위한 코드를 포함할 수도 있다.

- [0085] 히터 제어 프로그램은 기관을 가열하기 위해 사용된 히팅 유닛으로의 전류를 제어하기 위한 코드를 포함할 수도 있다. 대안적으로, 히터 제어 프로그램은 기관으로의 (헬륨과 같은) 열 전달 가스 (heat transfer gas)의 전달을 제어할 수도 있다.

- [0086] 플라즈마 제어 프로그램은 본 명세서의 실시예들에 따른, 하나 이상의 프로세스 스테이션들 내의 프로세스 전극들에 인가된 RF 전력 레벨들을 설정하기 위한 코드를 포함할 수도 있다.

- [0087] 압력 제어 프로그램은 본 명세서의 실시예들에 따른 반응 챔버 내에서 압력을 유지하기 위한 코드를 포함할 수도 있다.

- [0088] 일부 실시예들에서, 시스템 제어기 (550)와 연관된 사용자 인터페이스가 있을 수도 있다. 사용자 인터페이스는 디스플레이 스크린, 장치의 그래픽적인 소프트웨어 디스플레이 및/또는 프로세스 조건들의 그래픽적인 소프트웨어 디스플레이, 및 포인팅 디바이스들, 키보드들, 터치 스크린들, 마이크로폰들 등의 사용자 입력 디바이스들을 포함할 수도 있다.

- [0089] 일부 실시예들에서, 시스템 제어기 (550)에 의해 조정된 파라미터들은 프로세스 조건들과 관련될 수도 있다.

비제한적인 예들은 프로세스 가스 조성 및 플로우 레이트들, 온도, 압력, (RF 바이어스 전력 레벨들과 같은) 플라즈마 조건들, 등을 포함한다. 이들 파라미터들은 사용자 인터페이스를 활용하여 입력될 수도 있는, 레시피의 형태로 사용자에게 제공될 수도 있다.

[0090] 프로세스를 모니터링하기 위한 신호들은 다양한 프로세스 툴 센서들로부터 시스템 제어기 (550) 의 아날로그 입력 연결부 및/또는 디지털 입력 연결부에 의해 제공될 수도 있다. 프로세스를 제어하기 위한 신호들은 프로세스 툴 (500) 의 아날로그 출력 연결부 및/또는 디지털 출력 연결부 상에 출력될 수도 있다. 모니터링될 수도 있는 프로세스 툴 센서들의 비제한적인 예들은 질량 유량 제어기들, (압력계들 (manometers) 과 같은) 압력 센서들, 열전대들 (thermocouple), 등을 포함한다. 적절하게 프로그램된 피드백 및 제어 알고리즘들이 프로세스 조건들을 유지하기 위해 이들 센서들로부터의 데이터를 사용할 수도 있다.

[0091] 시스템 제어기 (550) 는 상기 기술된 증착 프로세스들을 구현하기 위한 프로그램 인스트럭션들을 제공할 수도 있다. 프로그램 인스트럭션들은 DC 전력 레벨, RF 바이어스 전력 레벨, 압력, 온도, 등과 같은 다양한 프로세스 파라미터들을 제어할 수도 있다. 인스트럭션들은 본 명세서에 기술된 다양한 실시예들에 따른 막 스택들의 인-시츄 증착을 동작시키기 위한 파라미터들을 제어할 수도 있다.

[0092] 시스템 제어기 (550) 는, 통상적으로 장치가 개시된 실시예들에 따른 방법을 수행하도록 인스트럭션들을 실행하도록 구성된 하나 이상의 프로세서들 및 하나 이상의 메모리 디바이스들을 포함할 것이다. 개시된 실시예들에 따른 프로세스 동작들을 제어하기 위한 인스트럭션들을 포함하는 멀티 판독가능 매체는 시스템 제어기 (550) 에 커플링될 수도 있다.

[0093] 일부 구현예들에서, 시스템 제어기 (550) 는 상술한 예들의 일부일 수도 있는 시스템의 일부이다. 이러한 시스템들은, 프로세싱 툴 또는 툴들, 챔버 또는 챔버들, 프로세싱용 플랫폼 또는 플랫폼들, 및/또는 특정 프로세싱 컴포넌트들 (웨이퍼 페데스탈, 가스 플로우 시스템, 등) 을 포함하는, 반도체 프로세싱 장비를 포함할 수 있다. 이를 시스템들은 반도체 웨이퍼 또는 기판의 프로세싱 이전에, 프로세싱 동안에 그리고 프로세싱 이후에 그들의 동작을 제어하기 위한 전자장치에 통합될 수도 있다. 전자장치들은 시스템 또는 시스템들의 다양한 컴포넌트들 또는 하위부품들을 제어할 수도 있는 "제어기"로서 지정될 수도 있다. 시스템 제어기 (550) 는, 시스템의 프로세싱 조건들 및/또는 타입에 따라서, 프로세싱 가스들의 전달, 온도 설정사항들 (예를 들어, 가열 및/또는 냉각), 압력 설정사항들, 진공 설정사항들, 전력 설정사항들, 무선 주파수 (RF) 생성기 설정사항들, RF 매칭 회로 설정사항들, 주파수 설정사항들, 플로우 레이트 설정사항들, 유체 전달 설정사항들, 위치 및 동작 설정사항들, 툴들 및 다른 이송 툴들 및/또는 특정 시스템과 연결되거나 인터페이싱된 로드록들 내외로의 웨이퍼 이송들을 포함하는, 본 명세서에 개시된 프로세스들 중 임의의 프로세스들을 제어하도록 프로그램될 수도 있다.

[0094] 일반적으로 말하면, 시스템 제어기 (550) 는 인스트럭션들을 수신하고, 인스트럭션들을 발행하고, 동작을 제어하고, 세정 동작들을 인에이블하고, 엔드포인트 측정들을 인에이블하는 등을 하는 다양한 접적 회로들, 로직, 메모리, 및/또는 소프트웨어를 갖는 전자장치로서 규정될 수도 있다. 접적 회로들은 프로그램 인스트럭션들을 저장하는 펌웨어의 형태의 칩들, 디지털 신호 프로세서들 (DSP), ASIC (application specific integrated circuit) 으로서 규정되는 칩들 및/또는 프로그램 인스트럭션들 (예를 들어, 소프트웨어) 을 실행하는 하나 이상의 마이크로프로세서들, 또는 마이크로제어기들을 포함할 수도 있다. 프로그램 인스트럭션들은 반도체 웨이퍼 상에서 또는 반도체 웨이퍼에 대한 특정 프로세스를 실행하기 위한 동작 파라미터들을 규정하는, 다양한 개별 설정사항들 (또는 프로그램 파일들) 의 형태로 시스템 제어기 (550) 로 또는 시스템으로 전달되는 인스트럭션들일 수도 있다. 일부 실시예들에서, 동작 파라미터들은 하나 이상의 층들, 재료들, 금속들, 산화물들, 실리콘, 이산화 실리콘, 표면들, 회로들, 및/또는 웨이퍼의 다이들의 제조 동안에 하나 이상의 프로세싱 단계들을 달성하도록 프로세스 엔지니어에 의해서 규정된 레시피의 일부일 수도 있다.

[0095] 시스템 제어기 (550) 는, 일부 구현예들에서, 시스템에 통합되거나, 시스템에 커플링되거나, 이와 달리 시스템에 네트워킹되거나, 또는 이들의 조합으로 될 수 있는 컴퓨터에 커플링되거나 이의 일부일 수도 있다. 예를 들어, 시스템 제어기 (550) 는 웨이퍼 프로세싱의 원격 액세스를 가능하게 할 수 있는 공장 (fab) 호스트 컴퓨터 시스템의 전부 또는 일부이거나 "클라우드" 내에 있을 수도 있다. 컴퓨터는 제조 동작들의 현 진행을 모니터링하고, 과거 제조 동작들의 이력을 조사하고, 복수의 제조 동작들로부터 경향들 또는 성능 계측치들을 조사하고, 현 프로세싱의 파라미터들을 변경하고, 현 프로세싱을 따르는 프로세싱 단계들을 설정하고, 또는 새로운 프로세스를 시작하기 위해서 시스템으로의 원격 액세스를 인에이블할 수도 있다. 일부 예들에서, 원격 컴퓨터 (예를 들어, 서버) 는 로컬 네트워크 또는 인터넷을 포함할 수도 있는 네트워크를 통해서 프로세스 레시피들을 시스템에 제공할 수 있다. 원격 컴퓨터는 차후에 원격 컴퓨터로부터 시스템으로 전달될 파라미터들 및/또는 설정사항

들의 입력 또는 프로그래밍을 인에이블하는 사용자 인터페이스를 포함할 수도 있다. 일부 예들에서, 시스템 제어기 (550)는 하나 이상의 동작들 동안에 수행될 프로세스 단계들 각각에 대한 파라미터들을 특정한, 데이터의 형태의 인스트럭션들을 수신한다. 이 파라미터들은 시스템 제어기 (550)가 제어하거나 인터페이싱하도록 구성된 툴의 타입 및 수행될 프로세스의 타입에 특정적일 수도 있다는 것이 이해되어야 한다. 따라서, 상술한 바와 같이, 시스템 제어기 (550)는 예를 들어 서로 네트워킹되어서 함께 공통 목적을 위해서, 예를 들어 본 명세서에 기술된 프로세스들 및 제어들을 위해서 협력하는 하나 이상의 개별 제어기들을 포함함으로써 분산될 수도 있다. 이러한 목적을 위한 분산형 제어기의 예는 챔버 상의 프로세스를 제어하도록 조합되는, (예를 들어, 플랫폼 레벨에서 또는 원격 컴퓨터의 일부로서) 원격으로 위치한 하나 이상의 집적 회로들과 통신하는 챔버 상의 하나 이상의 집적 회로들일 수 있다.

[0096] 비한정적으로, 예시적인 시스템들은 플라즈마 에칭 챔버 또는 모듈, 증착 챔버 또는 모듈, 스피너-런스 챔버 또는 모듈, 금속 도금 챔버 또는 모듈, 세정 챔버 또는 모듈, 베벨 에지 에칭 챔버 또는 모듈, PVD (physical vapor deposition) 챔버 또는 모듈, CVD (chemical vapor deposition) 챔버 또는 모듈, ALD (atomic layer deposition) 챔버 또는 모듈, ALE (atomic layer etch) 챔버 또는 모듈, 이온 주입 챔버 또는 모듈, 트랙 (track) 챔버 또는 모듈, 및 반도체 웨이퍼들의 제조 및/또는 제작 시에 사용되거나 연관될 수도 있는 임의의 다른 반도체 프로세싱 시스템들을 포함할 수도 있다.

[0097] 상술한 바와 같이, 툴에 의해서 수행될 프로세스 단계 또는 단계들에 따라서, 시스템 제어기 (550)는, 반도체 제작 공장 내의 툴 위치들 및/또는 로드 포트들로부터/로 웨이퍼들의 컨테이너들을 이동시키는 재료 이송 시에 사용되는, 다른 툴 회로들 또는 모듈들, 다른 툴 컴포넌트들, 클러스터 툴들, 다른 툴 인터페이스들, 인접 툴들, 이웃하는 툴들, 공장 도처에 위치한 툴들, 메인 컴퓨터, 또 다른 제어기 또는 툴들 중 하나 이상과 통신 할 수도 있다.

[0098] 본 명세서에 개시된 방법들을 수행하기 위한 적절한 장치는 이는 각각 전체가 본 명세서에 참조로서 인용된, 명칭이 2011년 4월 11일 출원된 명칭이 "PLASMA ACTIVATED CONFORMAL FILM DEPOSITION"인 미국 특허 출원 제 13/084,399 호 (현재 미국 특허 제 8,728,956 호), 및 2011년 4월 11일 출원된 명칭이 "SILICON NITRIDE FILMS AND METHODS"인 미국 특허 출원 제 13/084,305 호에서 더 논의되고 기술된다.

[0099] 본 명세서에 기술된 장치/프로세스는 예를 들어, 반도체 디바이스들, 디스플레이들, LED들, 광전 패널들 등의 제조 또는 제작을 위한 리소그래피 패터닝 툴들 또는 프로세스들과 함께 사용될 수도 있다. 통상적으로, 반드시 그러한 것은 아니지만, 이러한 툴들/프로세스들은 공동 제조 설비 내에서 함께 사용되거나 수행될 것이다. 막의 리소그래피 패터닝은 통상적으로, 단계들 각각이 다수의 가능한 툴들을 사용하여 인에이블되는, 이하의 단계들: (1) 스피너-온 (spin-on) 툴 또는 스프레이-온 (spray-on) 툴을 사용하여 워크피스, 즉, 기판 상에 포토레지스트를 도포하는 단계; (2) 핫 플레이트 또는 노 또는 UV 경화 툴을 사용하여 포토레지스트를 경화하는 단계; (3) 웨이퍼 스텝퍼와 같은 툴을 사용하여 가시광선 또는 UV 또는 x-선 광에 포토레지스트를 노출시키는 단계; (4) 습식 벤치와 같은 툴을 사용하여 레지스트를 선택적으로 제거하여 레지스트를 패터닝하도록 레지스트를 현상하는 단계; (5) 건식 또는 플라즈마 보조 에칭 툴을 사용함으로써 그 아래에 놓인 막 또는 워크피스 내로 레지스트 패턴을 전사하는 단계; 및 (6) RF 또는 마이크로파 플라즈마 레지스트 스트립퍼와 같은 툴을 사용하여 레지스트를 제거하는 단계의 일부 또는 전부를 포함한다.

[0100] 스페이서 재료에 선택적으로 코어 재료를 에칭하는 것과 같은 본 명세서에 기술된 에칭 동작들은 임의의 적합한 프로세스 챔버에서 수행될 수도 있다. 일부 실시예들에서, 기판들은 도 6에 대해 이하에 기술된 바와 같은 ICP (inductively coupled plasma) 반응기에서 에칭될 수도 있다.

[0101] 특정한 실시예들에서, 에칭 동작들에 대해 적합할 수도 있는 ICP 반응기들이 이제 기술된다. 이러한 ICP 반응기들은 또한, 전체가 참조로서 모든 목적들을 위해 본 명세서에 인용된, 2013년 12월 10일 출원되고 명칭이 "IMAGE REVERSAL WITH AHM GAP FILL FOR MULTIPLE PATTERNING"인 미국 특허 출원 공개번호 제 2014/0170853 호에 기술된다. ICP 반응기들이 본 명세서에 기술되지만, 일부 실시예들에서, CCP (capacitively coupled plasma) 반응기들이 또한 사용될 수도 있다는 것이 이해되어야 한다.

[0102] 도 6은 본 명세서의 특정한 실시예들을 구현하기에 적절한 CCP 통합된 에칭 및 증착 장치 (600)의 단면도를 개략적으로 도시하고, 이의 예는 CA, Fremont 소재의 Lam Research Corp.에 의해 생산된 Kiyo™ 반응기이다. CCP 장치 (600)는 챔버 벽들 (601) 및 윈도우 (611)에 의해서 구조적으로 구획된 전체 프로세스 챔버를 포함한다. 챔버 벽들 (601)은 스테인레스 스틸 또는 알루미늄으로 제조될 수도 있다. 윈도우 (611)는 석영 또는 다른 유전체 재료로 제조될 수도 있다. 선택가능한 내부 플라즈마 그리드 (650)는 상부 서브-챔버 (602) 및

하부 서브-챔버 (603)로 전체 프로세싱 챔버를 분할한다. 대부분의 실시예들에서, 플라즈마 그리드 (650)는 제거될 수도 있고, 따라서, 서브-챔버들 (602 및 703)로 이루어진 챔버 공간을 활용한다. 척 (617)은 하단 내측 표면 근방에서 하부 프로세싱 챔버 (603) 내에 위치된다. 척 (617)은 예칭 프로세스 및 증착 프로세스가 수행되는 반도체 웨이퍼 (619)를 수용 및 홀딩하도록 구성된다. 척 (617)은 웨이퍼 (619)가 존재하는 경우에 웨이퍼 (619)를 지지하는 정전 척일 수 있다. 일부 실시예들에서, 에지 랭 (미도시)이 척 (617)을 둘러싸며 척 (617) 위에 존재할 경우에 웨이퍼 (619)의 상단 표면과 대략 동일 평면에 있는 상부 표면을 갖는다. 척 (617)은 또한 웨이퍼 (619)를 척킹 및 디척킹하기 위한 정전 전극들을 포함한다. 필터 및 DC 클램프 전력 공급부가 이 목적을 위해서 제공될 수도 있다. 척 (617)으로부터 웨이퍼 (619)를 리프팅 (lifting) 하기 위한 다른 제어 시스템들이 또한 제공될 수 있다. 척 (617)은 RF 전력 공급부 (623)를 사용하여 전기적으로 대전될 수 있다. RF 전력 공급부 (623)는 연결부 (627)를 통해 매칭 회로 (621)에 연결된다. 매칭 회로 (621)는 연결부 (625)를 통해 척 (617)에 연결된다. 이러한 방식으로, RF 전력 공급부 (623)는 척 (617)에 연결된다.

[0103] 플라즈마 생성을 위한 엘리먼트들은 윈도우 (611) 위에 위치된 코일 (633)을 포함한다. 일부 실시예들에서, 코일은 개시된 실시예들에 사용되지 않는다. 코일 (633)은 전기적으로 도전성 재료로 제조되고, 적어도 1회의 완전한 턴 (turn)을 포함한다. 도 6에 도시된 코일 (633)의 예는 3회의 턴들을 포함한다. 코일 (633)의 단면도들은 심볼들로 도시되고, "X"를 갖는 코일들은 페이지 내로 회전하여 연장하는 한편, "●"을 갖는 코일들은 페이지로부터 회전하여 연장한다. 플라즈마 생성을 위한 엘리먼트들은 또한 코일 (633)에 RF 전력을 공급하도록 구성된 RF 전력 공급부 (641)를 포함한다. 일반적으로, RF 전력 공급부 (641)는 연결부 (645)를 통해 매칭 회로 (639)에 연결된다. 매칭 회로 (639)는 연결부 (643)를 통해 코일 (633)에 연결된다. 이러한 방식으로, RF 전력 공급부 (641)는 코일 (633)에 연결된다. 선택가능한 Faraday 차폐부 (649)는 코일 (633)과 윈도우 (611) 사이에 위치된다. Faraday 차폐부 (649)는 코일 (633)에 대해 이격된 관계로 유지될 수도 있다. Faraday 차폐부 (649)는 윈도우 (611) 바로 위에 배치된다. 코일 (633), Faraday 차폐부 (649), 및 윈도우 (611)는 각각 서로 실질적으로 평행하도록 구성된다. Faraday 차폐부는 금속 또는 다른 종이 플라즈마 챔버의 유전체 윈도우 상에 중착되는 것을 방지할 수도 있다.

[0104] 프로세스 가스들이 상부 챔버 내에 위치된 하나 이상의 주 가스 플로우 유입부들 (660)을 통해 그리고/또는 하나 이상의 측면 가스 플로우 유입부들 (670)을 통해 프로세스 챔버 내로 흐를 수도 있다. 유사하게, 명시적으로 도시되지 않지만, 프로세스 가스들을 CCP 프로세싱 챔버로 공급하도록 유사한 가스 플로우 유입부들이 사용될 수도 있다. 진공 펌프, 예를 들어, 1 또는 2 단계 기계적 드라이 펌프 및/또는 터보분자 펌프 (640)가 프로세스 챔버 (601)로부터 프로세스 가스들을 유출하도록 그리고 프로세스 챔버 (601) 내에서 압력을 유지하도록 사용될 수도 있다. 예를 들어, 펌프가 챔버 (601)를 배기하도록 사용될 수도 있다. 진공 펌프에 의해 제공된 진공 환경의 적용을 선택적으로 제어하도록 프로세스 챔버로 진공 펌프를 유체적으로 연결하도록 밸브-제어된 도관이 사용될 수도 있다. 이는 동작 중인 플라즈마 프로세싱 동안, 쓰로틀 밸브 (미도시) 또는 웬둘럼 밸브 (미도시)와 같은 폐루프 제어된 플로우 제한 디바이스를 채용함으로써 이루어질 수도 있다. 유사하게, CCP 챔버로의 진공 펌프 및 밸브 제어된 유체 연결이 채용될 수도 있다.

[0105] 장치의 동작 동안, 하나 이상의 프로세스 가스들은 가스 플로우 유입부들 (660 및/또는 670)를 통해 공급될 수도 있다. 특정한 실시예들에서, 프로세스 가스들은 주 가스 플로우 유입부 (660)를 통해서만, 또는 측면 가스 플로우 유입부 (670)를 통해서만 공급될 수도 있다. 일부 경우들에서, 도면에 도시된 가스 플로우 유입부들은 보다 복잡한 가스 플로우 유입부들, 예를 들어 하나 이상의 샤크헤드들로 대체될 수도 있다. Faraday 차폐부 (649) 및/또는 선택가능한 그리드 (650)는 챔버로의 프로세스 가스들의 전달을 허용하는 내부 채널들 및 홀들을 포함할 수도 있다. Faraday 차폐부 (649) 및 선택가능한 그리드 (650) 중 하나 또는 모두는 프로세스 가스들의 전달을 위한 샤크헤드로서 역할을 할 수도 있다. 일부 실시예들에서, 일단 액체 반응물질이 기화되면, 기화된 반응물질이 가스 플로우 유입부 (660 및/또는 670)를 통해 챔버 내로 도입되도록, 액체 기화 및 전달 시스템이 챔버 (601)의 업스트림에 위치될 수도 있다.

[0106] RF 전류로 하여금 코일 (633)을 통해 흐르게 하도록 RF 전력 공급부 (641)로부터 코일 (633)로 RF 전력이 공급된다. 코일 (633)을 통한 RF 전류는 코일 (633)을 중심으로 전자기장을 생성한다. 전자기장은 상부 서브-챔버 (602) 내에 유도 전류를 생성한다. 웨이퍼 (619)와 다양한 생성된 이온들 및 라디칼들의 물리적 및 화학적 상호작용들은 웨이퍼의 피처들을 선택적으로 에칭하고 웨이퍼 상에 충들을 중착한다.

[0107] 상부 서브-챔버 (602) 및 하부 서브-챔버 (603) 모두가 있도록 플라즈마 그리드가 사용되면, 상부 서브-챔버 (602) 내에서 전자-이온 플라즈마를 생성하도록 유도 전류는 상부 서브-챔버 (602) 내에 존재하는 가스에 작용

한다. 선택가능한 내부 플라즈마 그리드 (650) 는 하부 서브-챔버 (603) 내 핫 (hot) 전자들의 양을 제한한다. 일부 실시예들에서, 장치는 하부 서브-챔버 (603) 내에 존재하는 플라즈마가 이온-이온 플라즈마이도록 설계되고 동작된다.

[0108] 상부 전자-이온 플라즈마 및 하부 이온-이온 플라즈마 모두가 양이온 및 음이온을 포함할 수도 있지만, 이온-이온 플라즈마가 양이온들에 대한 음이온들의 보다 큰 비를 가질 것이다. 휘발성 에칭 및/또는 증착 부산물들은 포트 (622) 를 통해 하부 서브-챔버 (603) 로부터 제거될 수도 있다. 본 명세서에 개시된 척 (617) 은 약 10 °C 내지 약 850 °C의 범위의 상승된 온도들에서 동작할 수도 있다. 온도는 에칭 프로세싱 동작 및 구체적인 레시피에 따를 것이다.

[0109] 챔버 (601) 는 클린 룸 또는 제조 설비 내에 설치될 때 설비들 (미도시) 에 커플링될 수도 있다. 설비들은 프로세싱 가스들, 진공, 온도 제어, 및 환경 입자 제어를 제공하는 플럼빙을 포함한다. 이를 설비들은 타깃 제조 설비 내에 설치될 때 챔버 (601) 에 커플링된다. 부가적으로, 챔버 (601) 는 로보틱스들로 하여금 통상적인 자동화를 사용하여 반도체 웨이퍼들을 장치 챔버 (601) 내외로 이송하게 하는 이송 챔버에 커플링될 수도 있다.

[0110] 일부 실시예들에서, (하나 이상의 물리적 제어기 또는 논리적 제어기를 포함할 수도 있는) 시스템 제어기 (630) 는 프로세싱 챔버의 동작들 전부 또는 일부를 제어한다. 시스템 제어기 (630) 는 시스템 제어기 (550) 에 대해 상기 기술된 임의의 하나 이상의 특징을 포함할 수도 있다.

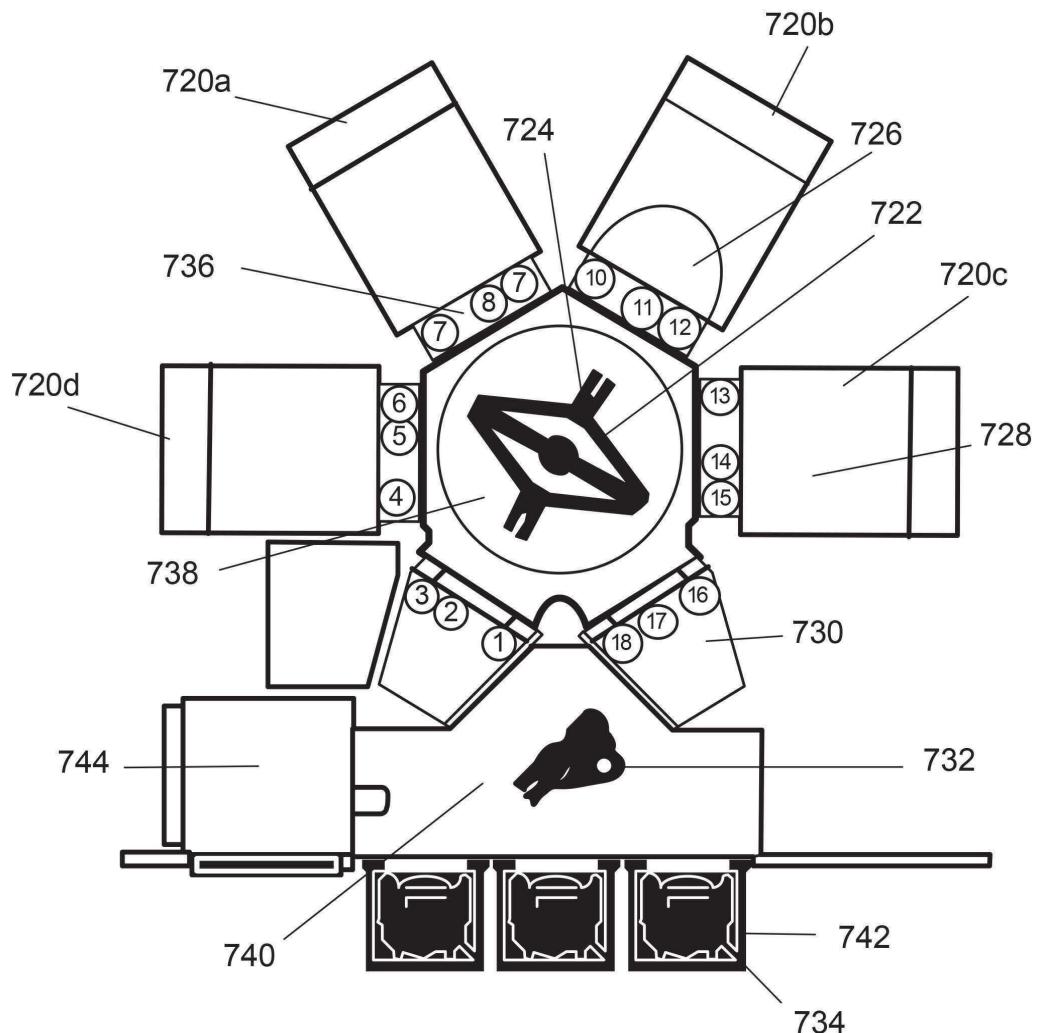

[0111] 도 7은 VTM (vacuum transfer module) (738) 과 인터페이싱하는 다양한 모듈들을 갖는 반도체 프로세스 클러스터 아키텍처를 도시한다. 복수의 저장 설비들 사이에서 웨이퍼들을 "이송"하기 위한 이송 모듈들 및 프로세스 모듈들의 장치는 "클러스터 틀 아키텍처" 시스템으로 지칭될 수도 있다. 또한 로드록 또는 이송 모듈로 공지된 에어록 (730) 이 4 개의 프로세싱 모듈들 (720a 내지 720d) 을 갖는 VTM (738) 내에 도시되고, 프로세싱 모듈들은 다양한 제조 프로세스들을 수행하도록 개별적으로 최적화될 수도 있다. 예로서, 프로세싱 모듈들 (720a 내지 720d) 은 기판 에칭, 증착, 이온 주입, 웨이퍼 세정, 스퍼터링, 및/또는 다른 반도체 프로세스들을 수행하도록 구현될 수도 있다. 일부 실시예들에서, ALD 및 선택적인 에칭이 동일한 모듈에서 수행된다. 일부 실시예들에서, ALD 및 선택적인 에칭은 동일한 틀의 상이한 모듈들에서 수행된다. 하나 이상의 기판 에칭 프로세싱 모듈들 (720a 내지 720d 중 어느 하나) 이 본 명세서에 개시된 바와 같이, 즉, 컨포멀한 막들을 증착하기 위해, ALD에 의해 막들을 선택적으로 증착하기 위해, 패턴들을 에칭하기 위해, 그리고 개시된 실시예들에 따른 다른 적합한 기능들을 위해 구현될 수도 있다. 에어록 (730) 및 프로세스 모듈 (720) 은 "스테이션들"로 지칭될 수도 있다. 스테이션 각각은 스테이션을 VTM (738) 에 인터페이싱하는 패싯 (736) 을 갖는다. 패싯 각각 내부에서, 센서들 (1 내지 18) 은 웨이퍼가 각각의 스테이션들 사이에서 이동할 때 웨이퍼 (726) 의 통과를 검출하도록 사용된다.

[0112] 로봇 (722) 이 스테이션들 사이에서 웨이퍼 (726) 를 이송한다. 일 실시예에서, 로봇 (722) 은 하나의 암을 갖고, 또 다른 실시예에서, 로봇 (722) 은 2 개의 암들을 갖고, 암 각각은 이송을 위해 웨이퍼 (726) 와 같은 웨이퍼들을 피킹하기 위해 엔드 이펙터 (724) 를 갖는다. ATM (atmospheric transfer module) (740) 의 프론트 엔드 로봇 (732) 이 LPM (Load Port Module) (742) 의 FOUP (Front Opening Unified Pod) (734) 또는 카세트로부터 에어록 (730) 으로 웨이퍼들 (726) 을 이송하도록 사용된다. 프로세스 모듈 (720) 내부의 모듈 중심 (728) 은 웨이퍼 (726) 를 배치하기 위한 일 위치이다. ATM (740) 내 열라이너 (744) 가 웨이퍼들을 정렬하기 위해 사용된다.

[0113] 예시적인 프로세싱 방법에서, 웨이퍼는 LPM (742) 내 FOUP들 (734) 중 하나에 배치된다. 프론트엔드 로봇 (732) 은 FOUP (734) 로부터 웨이퍼 (726) 로 하여금 에칭되거나 프로세싱되기 전에 적절히 중심에 위치되게 하는, 열라이너 (744) 로 웨이퍼를 이송한다. 정렬된 후, 웨이퍼 (726) 는 프론트엔드 로봇 (732) 에 의해 에어록 (730) 내로 이동된다. 에어록 모듈들이 ATM과 VTM 사이의 분위기를 매칭하는 능력을 갖기 때문에, 웨이퍼 (726) 는 손상되지 않고 두 압력 분위기들 사이에서 이동할 수 있다. 에어록 모듈 (730) 로부터, 웨이퍼 (726) 는 로봇 (722) 에 의해 VTM (738) 을 통해 프로세싱 모듈들 (720a 내지 720d) 중 하나 내로 이동된다. 이 웨이퍼 이동을 달성하기 위해, 로봇 (722) 은 암들 각각의 엔드 이펙터들 (724) 을 사용한다. 일단 웨이퍼 (726) 가 프로세싱되면, 웨이퍼는 로봇 (722) 에 의해 프로세싱 모듈들 (720a 내지 720d) 로부터 에어록 모듈 (730) 로 이동된다. 여기서부터, 웨이퍼 (726) 는 프론트엔드 로봇 (732) 에 의해 FOUP들 (734) 중 하나 또는 열라이너 (744) 로 이동될 수도 있다.

[0114] 웨이퍼 이동을 제어하는 컴퓨터는 클러스터 아키텍처에 국부적일 수 있고, 또는 제작 플로어의 클러스터 아키텍처 외부에 위치될 수 있고, 또는 리모트 위치에 있고 네트워크를 통해 클러스터 아키텍처에 연결될 수 있다.

도 5에 대해 상기 기술된 바와 같은 제어기가 도 7의 틀을 사용하여 구현될 수도 있다.

[0115] 실험

[0116] 실험은 캡충진 실리콘 옥사이드 재료를 기판의 패터닝된 코어 재료 위의 4:1의 종횡비 및 30 nm 이상의 개구부들을 갖는, 캡들 내로 증착하도록 수행되었다. 이하의 동작들: 실리콘 함유 전구체 도즈, 퍼지, 플라즈마와 함께 산소/아르곤, 퍼지의 복수의 증착 사이클들이 3 개의 기판들 각각에 수행되었다. 제 1 기판은 50 °C에서 증착되었고, 제 2 기판은 200 °C에서 증착되었고, 제 3 기판은 400 °C에서 증착되었다. 모든 3 개의 기판들이 대응하는 온도들에서 우수한 충진 능력을 나타내고, 이는 캡충진 재료를 사용하는 것에 대한 광범위한 적용가능성을 암시한다. 보다 높은 증착 온도들에서 보다 높은 막 밀도와 함께 상이한 온도들에서 막 밀도가 가변한다.

[0117] 결론

[0118] 전술한 실시예들이 이해의 명확성을 목적으로 다소 상세히 기술되었지만, 특정한 변화들 및 수정들이 첨부된 청구항들의 범위 내에서 실시될 수 있다는 것이 자명할 것이다. 본 실시예들의 프로세스들, 시스템들, 및 장치를 구현하는 많은 대안적인 방식들이 있다는 것을 주의해야 한다. 따라서, 본 실시예들은 예시적이고 제한하지 않는 것으로 간주되고, 실시예들은 본 명세서에 제공된 상세들로 제한되지 않는다.

**도면**

**도면1a**

**도면1b**

도면 1c

도면 1d

도면 1e

도면 1f

도면 1g

도면 1h

도면 1i

도면 1j

## 도면2

## 도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면3g

도면3h

도면3i

도면3j

도면3k

도면3l

도면3m

도면3n

도면3o

도면3p

도면3q

도면3r

## 도면4

## 도면5

## 도면6

도면7