### (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2006/0194437 A1 Hedberg et al.

### Aug. 31, 2006 (43) Pub. Date:

### (54) USE OF PULSED GROUNDING SOURCE IN A PLASMA REACTOR

(76) Inventors: Chuck E. Hedberg, Boise, ID (US); Kevin G. Donohoe, Boise, ID (US)

> Correspondence Address: TRASK BRITT P.O. BOX 2550 SALT LAKE CITY, UT 84110 (US)

11/405,979 (21) Appl. No.:

(22) Filed: Apr. 18, 2006

### Related U.S. Application Data

(63) Continuation of application No. 10/219,436, filed on Aug. 14, 2002, which is a continuation of application No. 09/649,748, filed on Aug. 28, 2000, now Pat. No. 6,485,572.

#### **Publication Classification**

(51) Int. Cl. C23F 1/00 (2006.01)H01L 21/306 (2006.01)H01L 21/302 (2006.01)

156/345.43; 156/345.44

#### (57) ABSTRACT

A method for grounding a semiconductor substrate pedestal during a portion of a high voltage power bias oscillation cycle to reduce or eliminate the detrimental effects of feature charging during the operation of a plasma reactor.

Fig. 1

Fig. 2C

Fig. 3

Fig. 4 (PRIOR ART)

Fig. 5A (PRIOR ART)

Fig. 6 (PRIOR ART)

Fig. 7 (PRIOR ART)

Fig. 9

# USE OF PULSED GROUNDING SOURCE IN A PLASMA REACTOR

### CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a continuation of application Ser. No. 10/219,436, filed Aug. 14, 2002, pending, which is a continuation of application Ser. No. 09/649,748, filed Aug. 28, 2000, now U.S. Pat. No. 6,485,572, issued Nov. 26, 2002.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to plasma reactor apparatus and processes. More specifically, the present invention relates to grounding a semiconductor substrate pedestal of a plasma reactor apparatus during a portion of a positive voltage power bias oscillation cycle to increase the energy of ion particles of the plasma to increase the feature charging effects regarding a substrate being etched using the plasma reactor.

[0004] 2. State of the Art

[0005] High performance, lower cost, increased miniaturization of electronic components, and greater density of integrated circuits are ongoing goals of the computer industry. One commonly used technique to increase the density of integrated circuits involves stacking multiple layers of active and passive components one atop another to allow for multilevel electrical interconnection between devices formed on each of these layers. This multilevel electrical interconnection is generally achieved with a plurality of metal-filled vias ("contacts") extending through dielectric layers that separate the component layers from one another. These vias are generally formed by etching through each dielectric layer using etching methods known in the industry, such as plasma etching. Plasma etching is also used in the forming of a variety of features for the electronic components of integrated circuits. In addition, vertical capacitors may be formed by etching the features of the wall of the capacitor in the capacitor dielectric and forming the remaining capacitor structure around the etched dielectric. Typically, the capacitance of the capacitor is proportional to the surface area of the wall of the capacitor etched in the dielectric material.

[0006] In plasma etching, a glow discharge is used to produce reactive species, such as atoms, radicals, and/or ions, from relatively inert gas molecules in a bulk gas, such as a fluorinated gas, such as CF<sub>4</sub>, CHF<sub>3</sub>, C<sub>2</sub>F<sub>6</sub>, CH<sub>2</sub>F<sub>2</sub>, SF<sub>6</sub>, or other freons, and mixtures thereof, in combination with a carrier gas, such as Ar, He, Ne, Kr, O<sub>2</sub>, or mixtures thereof. Essentially, a plasma etching process comprises: 1) reactive species are generated in a plasma from the bulk gas, 2) the reactive species diffuse to a surface of a material being etched, 3) the reactive species are absorbed on the surface of the material being etched, 4) a chemical reaction occurs that results in the formation of a volatile byproduct, 5) the byproduct is desorbed from the surface of the material being etched, and 6) the desorbed byproduct diffuses into the bulk gas.

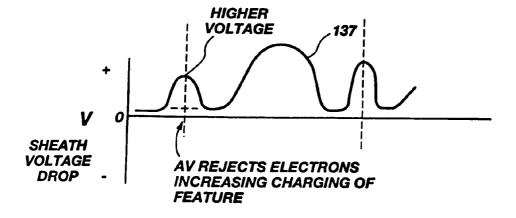

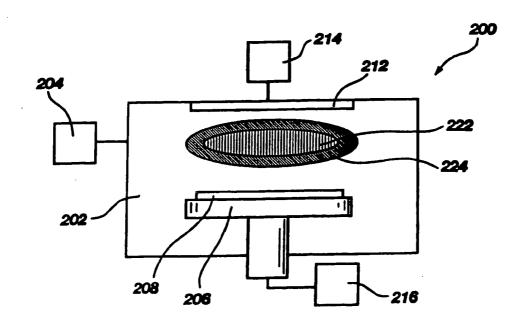

[0007] As illustrated in drawing FIG. 4, an apparatus 200 used in the plasma etching process consists of an etching

chamber 202 in electrical communication with a first AC (Alternating Current) power source 204. The etching chamber 202 further includes a pedestal 206 to support a semiconductor substrate 208 and an electrode 212 opposing the pedestal 206. The electrode 212 is in electrical communication with a second AC power source 214. The pedestal 206 has an AC power source 216. The electrode 212 and power source 214 may be an inductively coupled plasma source, a microwave plasma source, or any suitable type plasma source.

[0008] In the etching chamber 202, a plasma 222 is initiated and maintained by inductively coupling AC energy from the first AC power source 204 into an atmosphere of gases in the etching chamber 202 and the plasma 222 that comprises mobile, positively and negatively charged particles and reactive species. An electric field develops in a sheath layer 224 around the plasma 222, accelerating charged species (not shown) toward the semiconductor substrate 208 by electrostatic coupling.

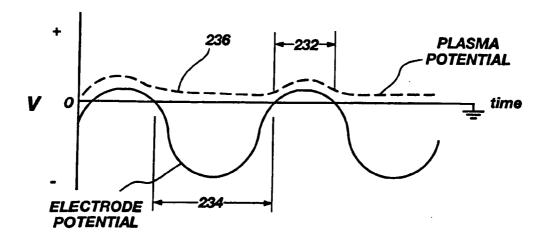

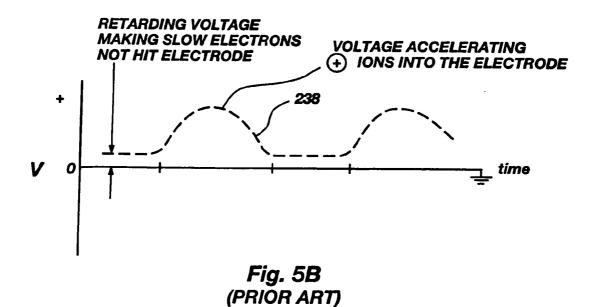

[0009] To assist with the etching, the potential difference between the plasma 222 and the semiconductor substrate 208 can be modulated by applying an oscillating bias power from the pedestal power bias source 216 to the pedestal 206, as illustrated in drawing FIG. 5A (showing the voltage profiles during such oscillation). During the positive voltage phase 232, the substrate collects electron current from electrons that have enough energy to cross the plasma sheath layer 224 (see drawing FIG. 4) having a plasma potential 236 (see drawing FIG. 5A). The difference between the instantaneous plasma potential and the surface potential defines the sheath potential voltage drop 238 (FIG. 5B). Since the plasma potential is more positive than the surface potential, this drop has a polarity that retards electron flow. Hence, only electrons with energy larger than this retarding potential are collected by the substrate. During the negative voltage phase 234, positive ions are collected by the substrate. These ions are accelerated by the sheath voltage drop 238 and strike the substrate.

[0010] However, it is known that the plasma etch results, including profile modification, can occur if the features are charged enough to modify the trajectories of the ions and electrons that are injected into these features.

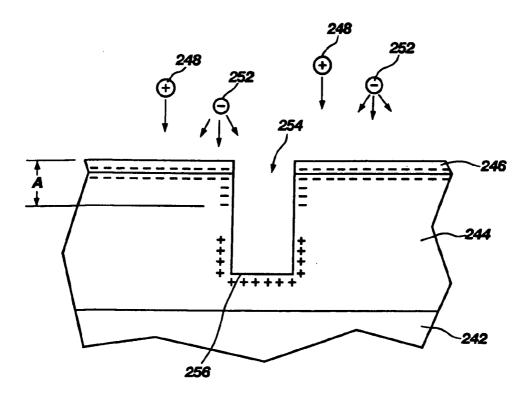

[0011] Illustrated in drawing FIG. 6 is the phenomena of electrical charging on a semiconductor device in the process of a plasma etch. A material layer 244 to be etched is shown layered over a semiconductor substrate 242. A patterned photoresist layer 246 is provided on the material layer 244 for the etching of a via. During the plasma etching process, the patterned photoresist layer 246 and material layer 244 are bombarded with positively charged ions 248 and negatively charged electrons 252. This bombardment results in a charge distribution being developed on the patterned photoresist layer 246 and/or the semiconductor substrate 242. This charge distribution is commonly called "feature charging."

[0012] In order for feature charging to occur, the positively charged ions 248 and the negatively charged electrons 252 must become separated from one another. The positively charged ions 248 and negatively charged electrons 252 become separated by virtue of the structures being etched and by the differences in directionality and energy between the positive ions and electrons as they approach the feature

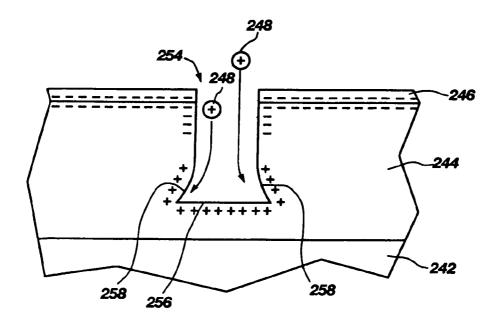

being etched. As the structure (in this example, a via 254) is formed by etching, the aspect ratio (height to width ratio) becomes greater and greater. During plasma etching, the positively charged ions 248 are accelerated toward the patterned photoresist layer 246 and the material layer 244 in a relatively perpendicular manner, as illustrated in drawing FIG. 7 by the arrows adjacent positively charged ions 248. The negatively charged electrons 252, however, are less affected by the AC power bias source at the semiconductor substrate 242 and, thus, move in a more random isotropic manner, as depicted in drawing FIG. 8 by the arrows adjacent negatively charged electrons 252. This results in an accumulation of a positive charge at a bottom 256 of via 254 because, on average, positively charged ions 248 are more likely to travel vertically towards the substrate 242 than are negatively charged electrons 252. Thus, any structure with a high enough aspect ratio tends to charge more negatively at photoresist layer 246 and an upper portion of the material layer 244 to a distance A (i.e., illustrated with "-" indicia) and more positively at the via bottom 256 and the sidewalls of the via 254 proximate the via bottom 256 (i.e., illustrated with "+" indicia).

[0013] As shown in drawing FIG. 7, the negatively charged sidewalls of the top of the opening deflects the positively charged ions 248 in trajectories towards the sidewalls. In addition, the positively charged via bottom 256 also decreases the vertical component of the ion velocity and therefore increases the relative effect of initial deflection. The deflection results in ion bombardment of the sidewalls 258 proximate the via bottom 256. This can generate a portion of the etched feature with a re-entrant profile, as shown in drawing FIG. 7. Such a profile can be useful in etching a number of films. For example, a re-entrant profile in a metal film can increase alignment tolerance to shorts to adjacent contacts by shrinking the size of the metal line as it meets the layer below it. In addition, a "bulge" can be etched into dielectric films such as borophosphosilicate glass (BPSG) with these ions. In this case, the feature charging causes a pileup of deflected ions at a location in the feature and some widening of the feature occurs.

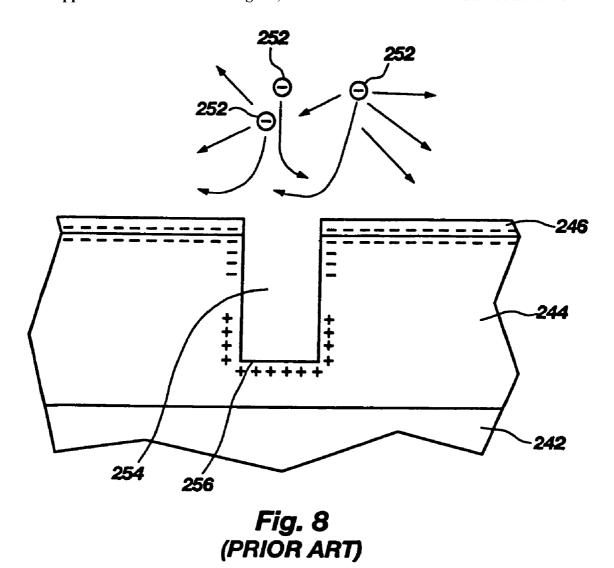

[0014] As shown in drawing FIG. 8, the negatively charged photoresist layer 246 and the upper portion of the material layer 244 deflect the negatively charged electrons 252 away from entering the via 254 or slow the negatively charged electrons 252 as they enter the via 254, both caused by charge repulsion and both of which can change the etch profile. This type of phenomenon is commonly known as "electron shading."

[0015] Thus, it can be appreciated that it would be advantageous to develop an apparatus and a process of utilizing a plasma reactor that maximizes or adds a controllable effect of feature charging while using inexpensive, commercially available semiconductor device fabrication components and without requiring complex processing steps.

### SUMMARY OF THE INVENTION

[0016] The present invention relates to an apparatus and method of reorienting electrons generated in a plasma reactor to minimize the electrons' ability to penetrate a feature and therefore reduce charging inside the feature.

[0017] One embodiment of the present invention comprises an etching chamber in electrical communication with

a first power source. The etching chamber further includes a pedestal to support a semiconductor substrate and an electrode opposing the pedestal. The electrode is in electrical communication with a second power source. The pedestal is in electrical communication with an AC power source. The etching chamber includes a second electrode in electrical communication with a second AC power source. The pedestal is further in electric communication with a triggerable, high-speed switch. When triggered, the switch closes to short the pedestal to ground. The AC power source is preferably in electrical communication with the switch through a signal line.

[0018] As previously discussed, the potential difference between the plasma and the semiconductor substrate can be modulated by applying an oscillating power from the pedestal power source to the semiconductor substrate. During the positive voltage phase, the substrate collects electron current from electrons that have enough energy to cross the plasma sheath. The difference between the instantaneous plasma potential and the surface potential defines the sheath potential drop. Since the plasma potential is more positive than the surface potential, this drop has a polarity that retards electron flow. Hence, only electrons with energy larger than this retarding potential are collected by the substrate. During the negative voltage phase, positive ions are collected by the substrate. These ions are accelerated by the sheath voltage drop and strike the substrate. However, the present invention comprises the shorting of the pedestal, either in a symmetrical manner or nonsymmetrical manner, during the positive voltage phase (i.e., during the time the negatively charged electrons flow to the wafer). This results in an increase in the electric field that retards electron flow to the wafer.

[0019] Negatively charged electrons are less affected by the DC bias at the semiconductor substrate than are positively charged ions and, thus, move in a more random manner. However, the shorting of the pedestal, according to the present invention, alters the difference between the potential of the plasma and potential of the semiconductor substrate for a part of the positive voltage phase. In addition, because the surface potential is made more negative relative to the plasma potential, only higher energy electrons can overcome this increased potential barrier and reach the surface. This results in more charging and a bigger difference between the positive voltage at the bottom of the feature and the negative voltage at the top of the feature. This increases the feature charging effects. In other words, the shorting of the pedestal increases the role of feature charging on the etch results.

[0020] The triggerable, high-speed switch is preferably controlled by the power output of the AC power source. Thus, when the power output of the AC power source reaches a first predetermined level, a first signal is sent from the AC power source or from a sensor (not shown coupled with the AC power source) to the triggerable, high-speed switch via the signal line. When the first signal is received by the switch, the switch closes to short the pedestal to ground. A second signal is sent from the AC power source or from a sensor (not shown coupled with the AC power source) to open the switch, which discontinues the grounding of the pedestal. The second signal can be sent when power output of the AC power source reaches a second predetermined level, or after a predetermined duration of time passes.

[0021] Thus, the present invention is capable of providing a simple and controllable method of effecting the quality and efficiency of plasma etching and is easily implemented on most existing plasma reactors.

[0022] Although the examples presented are directed to the formation of an opening with a plasma etching apparatus, it is understood that the present invention may be utilized in a variety of feature-formation and plasma processes.

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

[0023] While the specification concludes with claims particularly pointing out and distinctly claiming that which is regarded as the present invention, the advantages of this invention can be more readily ascertained from the following description of the invention when read in conjunction with the accompanying drawings in which:

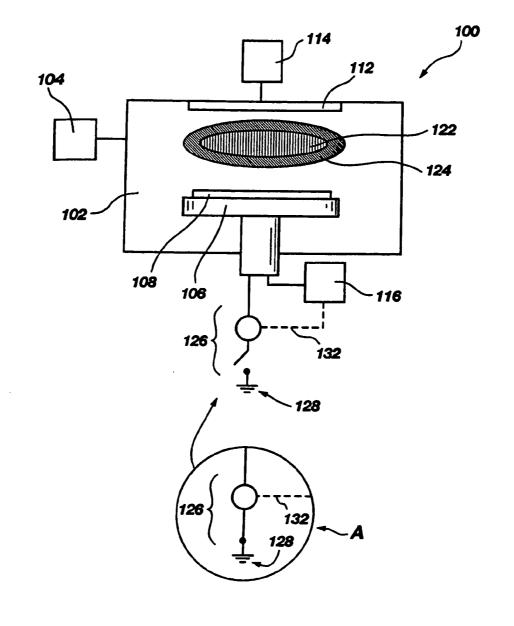

[0024] FIG. 1 is a schematic of a plasma etching apparatus according to the present invention;

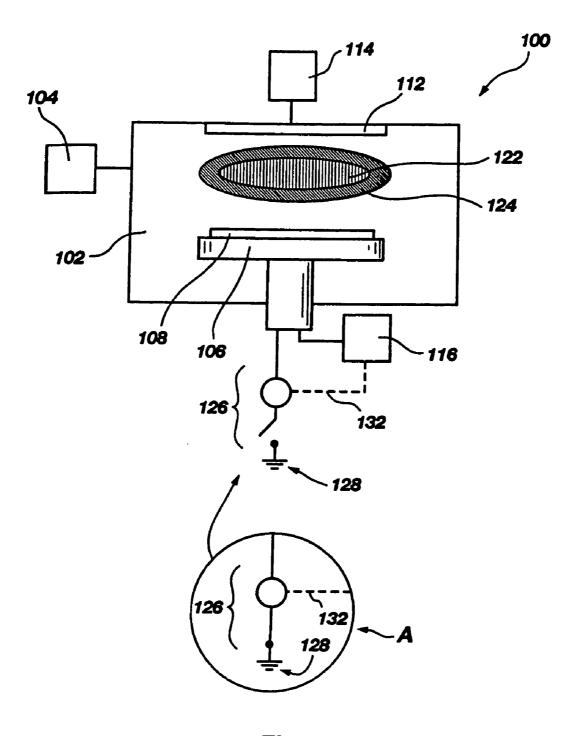

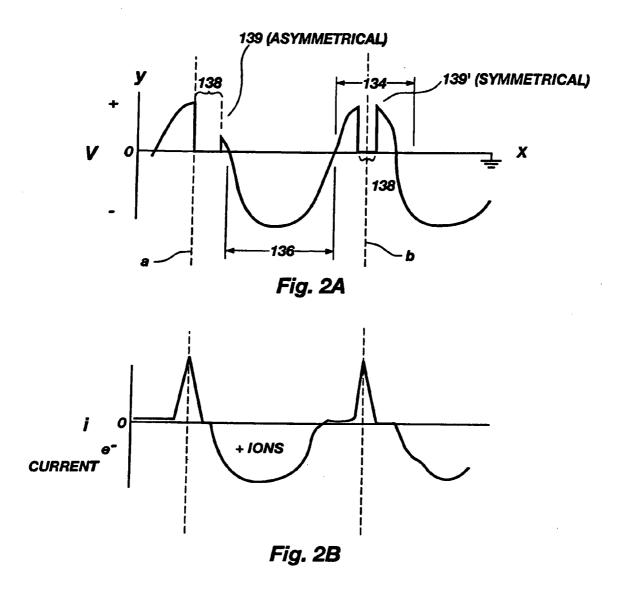

[0025] FIGS. 2A, 2B, and 2C are idealized graphs of an oscillating voltage profile, current profile, and plasma sheath voltage profile of a plasma etching apparatus pedestal according to the present invention;

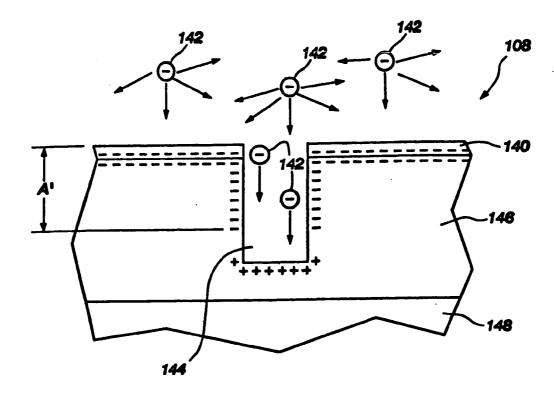

[0026] FIG. 3 is a cross-sectional view of a via during an etching process according to the present invention;

[0027] FIG. 4 is a schematic of a prior art plasma etching apparatus;

[0028] FIGS. 5A, 5B are idealized graphs of an oscillating voltage profile and plasma sheath voltage profile of prior art plasma etching apparatus pedestal of FIG. 4;

[0029] FIG. 6 is a cross-sectional view of a via during a prior art etching process that results in the phenomena on feature charging;

[0030] FIG. 7 is a cross-sectional view of a via during a prior art etching process wherein feature charging results in the deflection of positively charged ions away from the bottom of the via and toward the sidewalls of the via;

[0031] FIG. 8 is a cross-sectional view of a via during a prior art etching process wherein feature charging results in the deflection of negatively charged electrons away from entering the via or slows the negatively charged electrons as they enter the via; and

[0032] FIG. 9 is a cross-sectional view of a type of via formed by the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0033] Referring to drawings FIGS. 1 through 3, illustrated are various schematics, views, and graphs of the present invention. It should be understood that the illustrations are not meant to be actual views of any particular semiconductor device, but are merely idealized representations that are employed to more clearly and fully depict the formation of contact interfaces in the present invention than would otherwise be possible. Additionally, elements common between drawing FIGS. 1 through 3 retain the same numerical designation.

[0034] As illustrated in drawing FIG. 1, one embodiment of an etching apparatus 100 of the present invention comprises an etching chamber 102 in electrical communication with a first power source 104, such as an AC power source, a microwave power source, or any suitable power source, etc. The etching chamber 102 further includes a pedestal 106 to support a semiconductor substrate 108 and an electrode 112 opposing the pedestal 106. The electrode 112, typically a coil or set of coils, is in electrical communication with a second power source 114. The pedestal 106 is in electrical communication with an AC pulsed power bias source 116. In general, the electrode 112 can also be a plasma source driven by microwave power, electron cyclotron resonance power, or capacitively coupled rf power. Multiple frequency capacitively coupled power plasma processing tools (such as a Lam Corporation, Fremont, Calif., etcher called "EXELAN®") are also described in drawing FIG. 1 wherein the dual-frequency supplies would simply use the switching circuit 126 (also referred to as "switch 126") on one of the two power supplies.

[0035] In the etching chamber 102, a plasma 122 is maintained by inductively coupling energy from the first power source 104 into the plasma 122, which comprises mobile, positively and negatively charged particles. An electric field, or bias voltage, develops in a sheath layer 124 around the plasma 122, accelerating the electrons and ions (not shown) toward the semiconductor substrate 108 by electrostatic coupling.

[0036] The pedestal 106 is further in electric communication with a triggerable, high-speed switch 126 interposed along an electrical path to ground 128. When triggered, the switch 126 closes to short the pedestal 106 to ground 128. The AC power source 116 is preferably in electrical communication with the switch 126 with a signal line 132.

[0037] As previously discussed, the potential difference between the plasma 122 and the semiconductor substrate 108 can be modulated by applying an oscillating bias power from the pedestal AC pulsed power source 116 to the semiconductor substrate 108, as illustrated in drawing FIGS. 2A, 2B, 2C (showing the voltage profile for the pedestal and plasma sheath as well as the current profile during such oscillation). During the positive voltage phase 134, the substrate collects electron current from electrons that have enough energy to cross the sheath. The difference between the instantaneous plasma potential and the surface potential defines the sheath potential voltage drop 137. Since the plasma potential is more positive than the surface potential, this drop has a polarity that retards electron flow. Hence, only electrons with energy larger than this retarding potential are collected by the substrate. During the negative voltage phase 136, positive ions are collected by the substrate. These ions are accelerated by the sheath voltage drop and strike the substrate. However, as also illustrated in drawing FIGS. 2A, 2B, 2C, the present invention comprises the shorting of the pedestal 106 during the positive voltage phase 134 (i.e., during the time the electrons flow to the wafer) for a duration of time 138. The shorting of the pedestal 106 during the positive voltage phase 134 may occur either asymmetrically 139 or symmetrically 139'. As illustrated in drawing FIGS. 2A, 2B, 2C, with particular reference to drawing FIG. 2A, the voltage profile has been illustrated as a displaced sine wave about the x-axis and y-axis. Although a displaced sine wave has been illustrated,

the voltage could be supplied in any wave manner, displaced or not about the x-axis and y-axis. Further, as illustrated specifically with reference to drawing FIG. 2A, the asymmetrical shorting or grounding 139 of the pedestal 106 during the positive voltage phase 134 is shown as occurring for a duration of time 138 being displaced along the x-axis from the a-axis of drawing FIG. 2A, such a-axis extending through the peak of the positive voltage phase 134. However, the asymmetrical shorting or grounding 139' of the pedestal 106 during the positive voltage phase 134 could occur asymmetrically in any manner during the positive voltage phase 134 so long as the desired etching occurs. Additionally, the symmetrical shorting or grounding 139' of the pedestal 106 during the positive voltage phase 134 is illustrated as occurring for a duration of time 138 being displaced equally along the x-axis on either side (left or right) from the b-axis of drawing FIG. 2A, such a-axis extending through the peak of the positive voltage phase 134. However, the symmetrical shorting or grounding 139' of the pedestal 106 during the positive voltage phase 134 could occur symmetrically about the b-axis in any manner for any duration of time 138 so long as the desired etching occurs. Therefore, the voltage during the positive phase 134 of the electrical signal to the pedestal 106 during the closing of the switch 126 to short or ground the pedestal 106 may occur when the closing voltage is substantially higher, substantially lower or substantially equal to the voltage during the positive voltage phase 134 when the switch 126 is opened. Conversely, the opening voltage during the positive voltage phase of the electrical signal of the switch 126 to the pedestal 106 may occur when the opening voltage is substantially higher, substantially lower, or substantially equal to the voltage during the positive voltage phase 134 when the switch 126 is closed. In this manner, any desired asymmetrical or symmetrical shorting or grounding of the pedestal 106 may occur during the positive voltage phase 134 of the electrical signal.

[0038] As previously discussed and illustrated in prior art drawing FIG. 6, negatively charged electrons 252 are less affected by the AC bias at the semiconductor substrate than are positively charged ions and, thus, move in a more random manner, as depicted by the arrows adjacent negatively charged electrons 252. However, the shorting or grounding of the pedestal 106, according to the present invention, alters the difference between the potential of the plasma 122 and potential of the semiconductor substrate 108 for a part of the positive voltage phase 134, as shown in drawing FIGS. 2A, 2B, 2C.

[0039] Referring again to drawing FIG. 1, the triggerable, high-speed switch 126 is preferably controlled by the power output of the AC pulsed power source 116. Thus, when the power output of AC pulsed power source 116 reaches a first predetermined level, a first signal is sent from the AC pulsed power source 116 (or from a sensor (not shown) coupled with the AC pulsed power source 116) to the triggerable, high speed-switch 126 via the signal line 132. When the first signal is received by the switch 126, the switch 126 closes to a grounded position (see inset A of drawing FIG. 1) to short or ground the pedestal 106 to ground 128. A second signal is sent from the AC pulsed power source 116 (or from a sensor (not shown) coupled with the AC pulsed power source 116) to open the switch 126 to an open circuit position, as illustrated in FIG. 1, which discontinues the shorting or grounding of the pedestal 106. The second signal can be sent when power output of the AC pulsed power source 116 reaches a second predetermined level, or when a predetermined duration of time passes. Thus, the grounding can be controlled to occur at any point during the positive voltage cycle and for any duration to achieve the desired etching results for a particular semiconductor material. Referring to drawing FIG. 3, illustrated in a cross-sectional view of hole 144 being formed in a substrate 148 having a material layer 146 thereon having a layer of photoresist 140 thereon. Negatively charged electrons 142 are illustrated.

[0040] In using the present invention to etch typical dielectric material used in a semiconductor device, for a common IPS plasma etcher, sold by Applied Materials, the etcher would operate at a power level of approximately 800 watts having a power level bias of approximately 700 watts using a CHF<sub>3</sub> gas at a flow rate of approximately 22 sccm, the roof temperature of the etcher being independently controlled, and at a pressure level of approximately 20 mtorr. The roof temperature is set to approximately 140° C. and the ring temperature to approximately 200° C. with the bias frequency in the range of 1.7+/-0.2 MHZ. Under these conditions, the rf voltage at the wafer surface is estimated to be approximately in the range of 300 to 400 volts AC with the plasma having a potential below 50 volts at its peak.

[0041] In other instances, the present invention may be used to etch metal used in semiconductor devices, such as etching conductors in semiconductor devices. During the time that the conductor is etching, there is no feature charging. However, most metal etches finish on an insulator, including overetching. During this period, the bottom of the feature can charge up since it is an insulator, and the effects of feature charging can begin. For example, the conductor profile could be made re-entrant during the overetch if the feature charging is increased.

[0042] The present invention is particularly useful in the formation of high aspect ratio contact holes or apertures in dielectric material used in semiconductor devices. For instance, high aspect ratio contact holes or apertures in dielectric material may have a ratio of height to diameter of greater than 5:1 using the present invention.

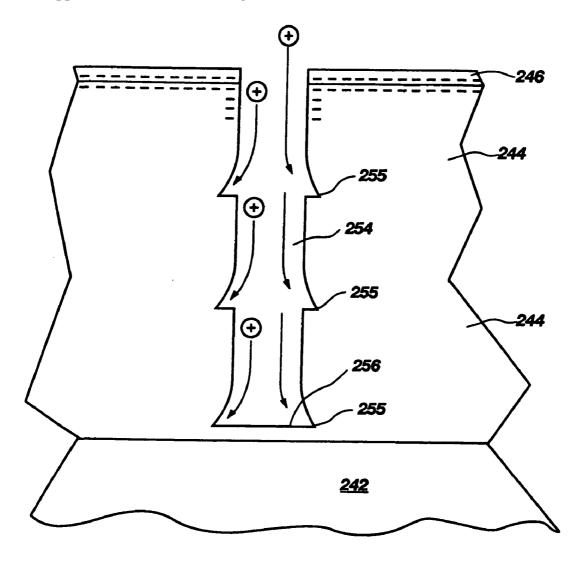

[0043] Additionally, if desired, an aperture 254, opening 254, via 254, or hole 254 may be formed having a plurality of bulges 255 therein using the present invention as illustrated in drawing FIG. 9. As illustrated, a high aspect ratio hole 254 is formed in a substrate 242 having a plurality of bulges 255 formed therein by the continual switching of the voltage during the operation of the etcher as described herein.

[0044] For instance, during the deposition of a dielectric into a high aspect ratio feature, the controlled increase in feature charging can be used to reduce ion energy to the bottom of the feature and vary the film deposition rate and film properties in the feature. For example, a fill could be made to form a bread-loaf shape of dielectric material at the top of the feature while having a low deposition rate inside the feature. This allows voids to be formed by increasing the feature charging during the deposition of the dielectric material.

[0045] Thus, the present invention is capable of providing a simple and controllable method of affecting the quality and efficiency of plasma etching and is easily implemented on

most existing plasma reactors. Furthermore, although the examples presented are directed to the formation of a via, it is understood that the present invention may be utilized in a variety of feature formation and plasma processes.

[0046] Having thus described in detail preferred embodiments of the present invention, it is to be understood that the invention defined by the appended claims is not to be limited by particular details set forth in the above description as many apparent variations thereof are possible without departing from the spirit or scope thereof.

#### What is claimed is:

- A plasma reactor comprising a reactor chamber including:

- a pedestal for supporting a semiconductor substrate;

- an AC power source in electrical communication with said pedestal; and

- an electrical path from ground to said pedestal including a switch, said switch being operable between an open position and a closed position.

- 2. A plasma reactor comprising:

- a reactor chamber;

- a first AC power source in electrical communication with said reactor chamber;

- a pedestal disposed within said reactor chamber for supporting a semiconductor substrate thereon;

- an electrode disposed within said reaction chamber and opposing said pedestal;

- a second AC power source in electrical communication with said electrode; and

- an electrical path from ground to said pedestal including a switch, said switch being operable between an open position and a closed position.

- 3. A method of operating a plasma reactor comprising:

- providing a plasma reactor including a pedestal for supporting a semiconductor substrate and an AC power bias source in electrical communication with said pedestal;

- providing an electrical path from ground to said pedestal including a switch, said switch being operable between an open position and a closed position;

- delivering an electrical signal to said pedestal from said AC power source, a voltage of said electrical signal oscillating between a high voltage phase and a low voltage phase;

- closing said switch to ground said pedestal during said high voltage phase of said electrical signal; and

- opening said switch during said high voltage phase of said electrical signal after closing said switch.

- **4**. The method of claim 3, wherein said closing said switch to ground said pedestal and said opening said switch further comprise:

- monitoring said voltage of said high voltage phase of said electrical signal until said voltage of said high voltage phase reaches a selected voltage;

- closing said switch to ground said pedestal for a selected duration of time during said high voltage phase of said electrical signal when said selected voltage is reached; and

- opening said switch during said high voltage phase of said electrical signal after said selected duration of time expires.

- **5**. The method of claim 3, wherein said closing said switch to ground said pedestal and said opening said switch further comprise:

- monitoring said voltage of said high voltage phase of said electrical signal for a first selected voltage and a second selected voltage;

- closing said switch to ground said pedestal during said high voltage phase of said electrical signal when said first selected voltage is reached; and

- opening said switch during said high voltage phase of said electrical signal when said second selected voltage is reached.

- 6. The method of claim 5, further comprising:

- closing said switch to ground said pedestal during said high voltage phase of said electrical signal when said first selected voltage comprising a substantially higher voltage than said second selected voltage is reached; and

- opening said switch during said high voltage phase of said electrical signal when a second selected voltage comprises a substantially lower voltage than said first selected voltage is reached.

- 7. The method of claim 5, further comprising:

- closing said switch to ground said pedestal during said high voltage phase of said electrical signal when a first selected voltage comprising a substantially lower voltage than said second selected voltage is reached; and

- opening said switch during said high voltage phase of said electrical signal when a second selected voltage comprising a substantially higher voltage than said first selected voltage is reached.

- 8. The method of claim 5, wherein:

- said first selected voltage and said second selected voltage include voltages during said positive voltage phase of said electrical signal that are substantially equal in magnitude.

- 9. The method of claim 5, wherein:

- said first selected voltage and said second selected voltage include voltages during said positive voltage phase of said electrical signal that are substantially unequal in magnitude.

- 10. A method of using a plasma reactor having a pedestal for supporting a semiconductor substrate and an AC power bias source in electrical communication with said pedestal and having an electrical path from ground to said pedestal including a switch, said switch having an open position and a closed position, said method comprising:

- delivering an electrical signal to said pedestal from said AC power bias source having a voltage of said electrical signal oscillating between a high voltage phase and a low voltage phase;

- determining a first selected voltage and a second selected voltage of said voltage of said electrical signal;

- closing said switch to ground said pedestal during said high voltage phase of said electrical signal when said first selected voltage is reached, said first selected voltage comprising a substantially lower voltage than a second selected voltage; and

- opening said switch during said high voltage phase of said electrical signal after closing said switch when said second selected voltage is reached, said second selected voltage comprising a substantially higher voltage than said first selected voltage.

- 11. The method of claim 10, wherein:

- said first selected voltage and said second selected voltage include voltages during a positive voltage phase of said electrical signal that are substantially equal in magnitude.

- 12. The method of claim 10, wherein:

- said first selected voltage and said second selected voltage include voltages during a positive voltage phase of said electrical signal that are substantially unequal in magnitude.

- 13. A method for creating an opening in a semiconductor device on a substrate having a material layer thereover and a photoresist layer patterned on said material layer in a plasma reactor chamber having a pedestal for supporting a semiconductor substrate and having an AC power source connected to said pedestal, said pedestal having a switched electrical path to ground for the opening and the closing thereof, said method comprising:

- generating a plasma above said semiconductor substrate;

- delivering an electrical signal to said pedestal from said AC power source, a voltage of said electrical signal oscillating between a high voltage phase and a low voltage phase;

- monitoring said voltage of said high voltage phase of said electrical signal for a first selected voltage and a second selected voltage;

- closing a switch to ground said pedestal during said high voltage phase of said electrical signal when said first selected voltage is reached, said first selected voltage comprising a substantially lower voltage than said second selected voltage; and

- opening said switch during said high voltage phase of said electrical signal after closing said switch when said second selected voltage is reached, said second selected voltage comprising a substantially higher voltage than said first selected voltage.

- 14. The method of claim 13, wherein:

- said first selected voltage and said second selected voltage include voltages during a positive voltage phase of said electrical signal that are substantially equal in magnitude

- 15. The method of claim 13, wherein:

- said first selected voltage and said second selected voltage include voltages during a positive voltage phase of said electrical signal that are substantially unequal in magnitude.

- 16. A method for creating a high aspect ratio opening in a semiconductor device in a plasma reactor chamber including a pedestal for supporting a semiconductor substrate having a material layer thereover and a photoresist layer patterned on said material layer, said photoresist layer patterned on said material layer having at least one aperture therein and having an AC power source connected to said pedestal, said pedestal including a switch connected therewith for opening and closing an electrical path to ground, said method comprising:

- generating a plasma above said semiconductor substrate;

- delivering an electrical signal to said pedestal from said AC power source, a voltage of said electrical signal oscillating between a high voltage phase and a low voltage phase;

- monitoring said voltage of said high voltage phase of said electrical signal for a first selected voltage and a second selected voltage;

- closing said switch to ground said pedestal during said high voltage phase of said electrical signal when said first selected voltage is reached, said first selected voltage comprising a substantially lower voltage than said second selected voltage;

- forming at least a portion of an opening in said semiconductor substrate;

- opening said switch during said high voltage phase of said electrical signal after closing said switch when said second selected voltage is reached, said second selected voltage comprising a substantially higher voltage than said first selected voltage; and

- forming at least another portion of said opening in said semiconductor substrate.

- 17. The method of claim 16, wherein:

- said first selected voltage and said second selected voltage include voltages during a positive voltage phase of said electrical signal that are substantially equal in magnitude.

- 18. The method of claim 16, wherein:

- said first selected voltage and said second selected voltage include voltages during a positive voltage phase of said electrical signal that are substantially unequal in magnitude.

- **19**. The method of claim 16, wherein said at least a portion of said opening includes one of a re-entrant profile and bulge therein.

- **20**. The method of claim 16, wherein said at least a portion of said opening includes at least one bulge therein.

- 21. The method of claim 16, wherein said at least another portion of said opening includes one of a re-entrant profile and bulge therein.

- 22. The method of claim 16, wherein said at least another portion of said opening includes at least one bulge therein.

- 23. The method of claim 16, wherein said at least a portion of said opening includes at least two bulges therein.

- 24. The method of claim 16, wherein said at least a portion of said opening includes a plurality of bulges therein.

- 25. The method of claim 16, wherein said at least a portion of said opening has an aspect ratio of at least 5:1.

\* \* \* \* \*