# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-74840 (P2007-74840A)

(43) 公開日 平成19年3月22日(2007.3.22)

| (51) Int.C1. |        |           | FΙ   |       |   | テーマコード (参考) |

|--------------|--------|-----------|------|-------|---|-------------|

| H02M         | 3/07   | (2006.01) | HO2M | 3/07  |   | 5BO35       |

| HO1L         | 21/822 | (2006.01) | HO1L | 27/04 | G | 5F038       |

| HO1L         | 27/04  | (2006.01) | GO6K | 19/00 | J | 5H73O       |

| G06K         | 19/07  | (2006.01) | G06K | 19/00 | Н |             |

|              |        |           |      |       |   |             |

|                       |                                                      | 審査請求     | 未請求 請求項の数 11 OL (全 20 頁)                                  |

|-----------------------|------------------------------------------------------|----------|-----------------------------------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2005-260344 (P2005-260344)<br>平成17年9月8日 (2005.9.8) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号           |

|                       |                                                      | (74) 代理人 | 100081938<br>弁理士 徳若 光政                                    |

|                       |                                                      | (72) 発明者 | 田中 均<br>東京都小平市上水本町5丁目22番1号<br>株式会社日立超エル・エス・アイ・システ<br>ムズ内  |

|                       |                                                      | (72) 発明者 | 石橋 正和<br>東京都小平市上水本町5丁目22番1号<br>株式会社日立超エル・エス・アイ・システ<br>ムズ内 |

|                       |                                                      |          | 最終頁に続く                                                    |

# (54) 【発明の名称】半導体集積回路装置

# (57)【要約】

【課題】 簡単な構成で動作電圧マージンの改善を図っ た半導体集積回路装置を提供する。簡単な構成で通信距 離を長くできる無線ICタグに向けた半導体集積回路装 置を提供する。

【解決手段】 伝播されたエネルギーを電気信号の形態 で入力端子に入力する。上記入力された電気信号を電源 回路で直流電圧を生成し、かかる直流電圧とは異なる内 部電圧を起動時の電流が制限されたチャージポンプ回路 で形成し、上記内部電圧で内部回路を動作させる。

【選択図】 図1

#### 【特許請求の範囲】

## 【請求項1】

伝播されたエネルギーが電気信号の形態で入力される入力端子と、

上記入力端子から入力された電気信号から直流電圧を生成する電源回路と、

上記電源回路で形成された直流電圧を受け、かかる直流電圧とは異なる内部電圧を形成するチャージポンプ回路と、

上記内部電圧で動作する内部回路とを備えてなり、

上記チャージポンプ回路は、起動時の電流が制限されることを特徴とする半導体集積回路装置。

#### 【請求項2】

請求項1において、

上記伝播されたエネルギーは、信号成分を含む電磁波であることを特徴とする半導体集積回路装置。

# 【請求項3】

請求項2において、

上記チャージポンプ回路は、

上記直流電圧で動作する発振回路、駆動回路、複数の要素ポンプ回路及び出力容量を含み、

上記発振回路は、発振パルスを形成し、

上記要素ポンプ回路は、ポンプ容量とそれに対応した発振パルスの信号レベルに対応してスイッチングを行うスイッチ素子とを有し、

上記駆動回路は、上記発振パルスに対応して上記要素ポンプ回路のポンプ容量を駆動する電流の制限を行うものであることを特徴とする半導体集積回路装置。

#### 【請求項4】

請求項3において、

上記駆動回路は、複数の要素ポンプ回路のそれぞれに対応して設けられるものであることを特徴とする半導体集積回路装置。

#### 【請求項5】

請求項2において、

上記チャージポンプ回路は、

上記直流電圧で動作する発振回路、駆動回路、複数の要素ポンプ回路及び出力容量を含み、

上記発振回路は、発振パルスを形成し、

上記要素ポンプ回路は、ポンプ容量とそれに対応した発振パルスの信号レベルに対応してスイッチングを行うスイッチ素子とを有し、

上記駆動回路は、上記発振パルスに対応して上記要素ポンプ回路のポンプ容量を駆動するものであり、

上記要素ポンプ回路がポンピング動作に対応して複数ブロックに分割され、

上記分割された複数ブロックは、起動時に低電圧側から順に時間差を持って動作を行うことを特徴とする半導体集積回路装置。

# 【請求項6】

請求項2において、

上記チャージポンプ回路は、

上記直流電圧で動作する発振回路、駆動回路、複数の要素ポンプ回路及び出力容量を含み、

上記発振回路は、発振パルスを形成し、

上記要素ポンプ回路は、ポンプ容量とそれに対応した発振パルスの信号レベルに対応してスイッチングを行うスイッチ素子とを有し、

上記駆動回路は、上記発振パルスに対応して上記要素ポンプ回路のポンプ容量を駆動するものであり、

10

20

30

40

上記発振パルスの周波数を制御することにより、上記起動時の電流が制限されてなることを特徴とする半導体集積回路装置。

#### 【請求項7】

請求項2において、

上記チャージポンプ回路は、

上記直流電圧で動作する発振回路、駆動回路、複数の要素ポンプ回路、チャージアップスイッチ及び出力容量を含み、

上記発振回路は、発振パルスを形成し、

上記要素ポンプ回路は、ポンプ容量とそれに対応した発振パルスの信号レベルに対応してスイッチングを行うスイッチ素子とからなり、

上記チャージアップスイッチは、起動時に一時的にオン状態となって上記各要素ポンプ回路のポンプ容量のチャージアップを行い、

上記駆動回路は、上記起動時の上記チャージアップスイッチのオン状態に合わせて上記ポンプ容量のチャージアップ動作に必要な出力信号を形成し、上記ポンプ容量がチャージアップされた後に上記発振パルスに対応して上記要素ポンプ回路のポンプ容量を駆動することを特徴とする半導体集積回路装置。

# 【請求項8】

請求項5,6又は7のいずれかにおいて、

上記駆動回路は、上記発振パルスに対応して上記要素ポンプ回路のポンプ容量を駆動する電流の制限を行うものであることを特徴とする半導体集積回路装置。

#### 【請求項9】

請求項3又は8において、

上記駆動回路は、パルス信号を受けるPチャネルMOSFETとNチャネルMOSFETを有するCMOS回路と、上記PチャネルMOSFET及びNチャネルMOSFETに直列形態に接続されて電流制限動作を行うMOSFETを有することを特徴とする半導体集積回路装置。

# 【請求項10】

請求項1ないし9のいずれかにおいて、

上記半導体集積回路装置は、無線によるデータの送受信をするものであることを特徴とする半導体集積回路装置。

## 【請求項11】

請求項10において、

上記内部回路は、上記内部電圧を用いて電気的に書き換えが可能な不揮発性メモリであることを特徴とする半導体集積回路装置。

【発明の詳細な説明】

# 【技術分野】

#### [00001]

本発明は、半導体集積回路装置に関し、例えばICチップを搭載した無線ICタグ、ICカード等の好適なチャージポンプ回路を備えた半導体集積回路装置に利用して有効な技術に関するものである。

# 【背景技術】

# [0002]

無線ICタグに電源電圧を生成する倍圧整流回路を設けた例として、特開2002-176141公報がある。チャージポンプ回路におけるノイズの発生を防止するために定電流を用いてコンデンサの充放電を制限する例として、特開2005-151777公報がある。

【特許文献1】特開2002-176141公報

【特許文献2】特開2005-15177分級報

## 【発明の開示】

【発明が解決しようとする課題】

20

10

30

50

#### [00003]

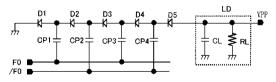

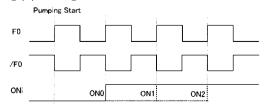

本願発明者においては、不揮発性メモリを用いてデータの書き換えを行うようにした無線ICタグの開発において、送受信距離をもっと長くすることができないかという課題に直面した。フラッシュEEPROMのような不揮発性メモリにおいては、書き込み動作及び消去動作においては、読み出し動作時の動作電圧に比べて大きな電圧を必要とする。のような大きな電圧を半導体集積回路内で形成するために、図30に示したような多段のチャージポンプ回路を用いることを検討した。このチャージポンプ回路は、ディクソン型と言われる回路であり、位相が180°ずれたパルスF0,/F0を1段ごとにダイオードDとキャパシタCPからなる要素ポンプ回路に印加することにより、上記パルスの振幅の段数分の電圧を出力することができる。同図の回路では、4段で構成されるので、ダイオードによる電圧降下をVD、パルスの振幅をVDD、負荷電流をゼロとしてVPP=・4(VDD・VD)の電圧が得られる。この他、VDによる電圧降下を防ぐためダイオードをMOSに置き換えてそのゲートを高電圧で駆動する方式もある。

#### [0004]

このチャージポンプ回路では、図31のタイミング図に示したように、キャパシタCP1のパルスF0の入力端が電源電圧VDDになったとき、キャパシタはパルスの接地で、ダイオードD1側が負に充電される。次のサイクルで入力パルスF0が回路の電位を・VDD・VD)にする。このとき次段のキャパシタCP2のパルス/F0の力力端が電で(VDD・VD)にする。このとき次段のキャパシタCP2のパルス/F0の力力ははが反対すると2段目のキャパシタのダイオード側の電位は・(2VDD・VD)になり、次にまたパルス、次にまたパルス、次にまたパルス、次にまたパルス、次にまたパルス、次にまたパルスを手をがした。とこの電位を・2(VDD・VD)になる。以下この動作を繰り返したの電位は深くなっていき、ダイオードD5を通過したときるではは、・4(VDD・VD)になる。このポンピング動作開始時においてきなくなり、無線ICタグ等の送受信距離がポンプ動作開始時における消費電流により制限されることを見出した。

# [0005]

本願発明者においては、ポンピング動作を開始したときのチャージポンプ回路に流れる電流と、出力電圧VPPが所望の電圧に到達した後のチャージポンプ回路に流れる電流とに大きな差があることに着目し、かかるチャージポンプ回路での電流を制限することで、無線ICタグにおける送受信距離を長くすることを考えた。

# [0006]

この発明の目的は、簡単な構成で動作電圧マージンの改善を図った半導体集積回路装置を提供することにある。この発明の他の目的は、簡単な構成で通信距離を長くできる無線ICタグに向けた半導体集積回路装置を提供することにある。この発明の上記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう

# 【課題を解決するための手段】

# [0007]

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。すなわち、伝播されたエネルギーを電気信号の形態で入力端子に入力する。上記入力された電気信号を電源回路で直流電圧を生成し、かかる直流電圧とは異なる内部電圧を起動時の電流が制限されたチャージポンプ回路で形成し、上記内部電圧で内部回路を動作させる。

## 【発明の効果】

# [0008]

簡単な構成で動作マージンの改善が可能となる。簡単な構成で通信距離を長くできる無線ICタグを得ることができる。

10

20

30

40

30

40

50

# 【発明を実施するための最良の形態】

# [0009]

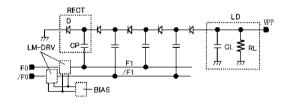

図1には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の一実施例の回路図が示されている。この実施例のチャージポンプ回路は、ダイオードDと昇圧ポンプ容量 C P からなる要素ポンプ回路 R E C T を多段接続したポンプ回路が用いられる。上記チャージポンプ回路を構成する要素ポンプ回路 R E C T にパルス F 1 , / F 1 を供給する駆動回路 L M - D R V の制限電流を行うための定電流バイアス回路 B I A S が設けられる。

## [0010]

このチャージポンプ回路は、前記説明したようなディクソン型と言われる回路であり、位相が180°ずれたパルスF1,/F1を1段ごとにダイオードDとキャパシタCPからなる要素ポンプ回路に印加することにより、上記パルスの振幅の段数分の電圧VPPを形成する。この昇圧電圧VPPは、負荷回路LDの動作電圧とされる。負荷回路LDは、キャパシタCLと抵抗RLの等価回路として示されている。

#### [0011]

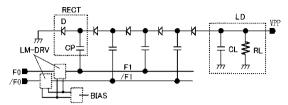

図2には、図1の駆動回路LM-DRVの一実施例の回路図が示されている。駆動回路LM-DRVは、NチャネルMOSトランジスタM1とPチャネルMOSトランジスタM2からなるCMOSインバータ回路を入力段として入力パルスF0が供給される。この入力段の出力信号は、PチャネルMOSトランジスタM5とNチャネルMOSトランジスタM4のゲートに供給される。この出力段のPMOS側とNMOS側の両方に定電流源MOSトランジスタM6およびMOSトランジスタM3が挿入されている。これにより、MOSトランジスタM5がオンした場合、吐き出し電流を制限し、MOSトランジスタM4がオンした場合、吸い込み電流を制限することができる。入力パルス/F0に対応した駆動回路LV-DRVも同様な回路とされる。

## [0012]

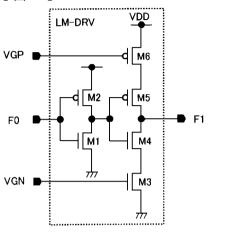

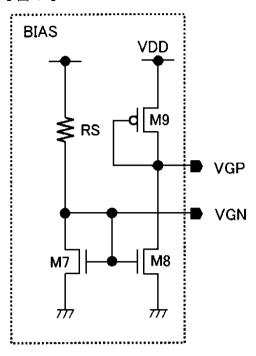

図3には、図1のバイアス回路BIASの一実施例の回路図が示されている。このバイアス回路BIASは、上記定電流源MOSトランジスタM3及びM6のゲートに供給される定電圧VGN及びVGPを形成する。(VDD-Vth)/RSの電流がMOSトランジスタM7に流れる。上記Vthは、MOSトランジスタM7のゲート,ソース間のしきい値電圧である。上記MOSトランジスタM7とMOSトランジスタM8のサイズを同じにした場合、MOSトランジスタM8、M9にも同じ電流が流れる。ここで、MOSトランジスタM7と上記MOSトランジスタM9と上記MOSトランジスタM7と上記MOSトランジスタM9と上記MOSトランジスタM7とM3およびMOSトランジスタM9とM6のサイズ比である。

# [0013]

前記図2において、MOSトランジスタM6のゲートに接地電位VSSを供給し、MOSトランジスタM3のゲートに電源電圧VDDを供給して、これらMOSトランジスタM6及びM3を抵抗素子として動作させるものであってもよい。このようにすれば、バイアス回路BIASを省略することができる。上記MOSFETM6,M3は、拡散層を利用した抵抗、あるいは配線層を利用した抵抗に置き換えることもできる。

#### [0014]

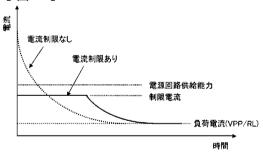

図4には、図1のチャージポンプ回路の動作電流の説明図が示されている。同図においては、本願発明の理解のためにチャージポンプ回路に前記のような駆動回路LM-DRV及びバイアス回路BIASを用いた電流制限がある場合とともに、このような電流制限を行わない場合のチャージポンプ回路の動作電流が比較のために示されている。電流制限がない場合は、同図に点線で示したように起動初期に電源回路の供給能力を越える電流が流れるのに対して、電流制限がある場合は、起動初期でも電流制限回路によってそれ以下にすることができる。また、電流制限回路付きのチャージポンプ回路では、後半では電流制限無しのチャージポンプ回路よりも大きな電流が流れるので、所望のレベルに達するまで

30

40

50

の時間はほとんど変わらない。

# [0015]

上記電源電圧VDDを形成する電源回路は、後述するように無線ICタグのようにアンテナで受信された受信信号を整流することにより形成される。それ故、例えば同図に点線で示したような一定の電源回路供給能力を持つ。前記バイアス回路BIAS及び駆動回路LM-DRVによるチャージポンプ回路の制限電流は、上記電源回路供給能力以下に設定されるものである。このような制限電流の設定により、上記電源回路供給能力以下で上記電流制限が無い場合と同様に昇圧電圧VPPを形成することができる。

#### [0016]

前記電流制限を行わない場合には、同図に点線で示したように起動時に電源回路供給能力を超える電流がチャージポンプ回路に流れることを意味する。前記のようなアンテナで受信された受信信号を整流することにより形成された電源回路では、その供給能力を超える電流が流れると、必然的に電源電圧VDDが大幅に低下してしまい、チャージポンプ回路の動作自体も行われなくなる。つまり、前記パルスF0や/F0を形成する発振回路やCMOSインバータ回路のような駆動回路も動作しなくなり、チャージポンプ回路の昇圧動作が不能となる。結局、前記電流制限を行わない無線ICタグでは、電源回路の供給能力が上記チャージポンプ回路のピーク電流以上であるという条件でしか動作しない。

## [0017]

本願発明者による試算によれば、前記 - 1 0 V のような昇圧電圧 V P P を形成するチャージポンプ回路での起動時の電流は約 1 2 0  $\mu$  A のように大きい。このような大きな電流消費を行うチャージポンプ回路を備えた無線タグICでは、前記のようなアンテナで受信された受信信号を整流することにより形成された電源回路の電流供給能力は、上記チャージポンプ回路での消費電流の上記 1 2 0  $\mu$  A 以上にする必要がある。つまり、無線ICタグの受信電波の電界強度が上記電源回路での電流供給能力に対応するから、信号発信源と無線ICタグとの通信可能な距離が上記電界強度を得るべく極短い距離になることを意味する。

# [ 0 0 1 8 ]

前記実施例のようにチャージポンプ回路に電流制限機能を設けて、起動時の電流を制限した場合、チャージポンプ回路を動作させるのに必要な電源回路供給能力を小さくすることができる。例えば、図4においてチャージポンプ回路に流れる最大電流を制限電流により40μAのように小さくすることができる。この結果、無線ICタグに搭載されたチャージポンプ回路は同じでも、上記のような電流制限機能を設けることにより電源回路での電流供給能力を約1/3に低減することができる。つまり、この実施例のチャージポンプ回路を搭載した無線ICタグでは、アンテナで受信された電界強度も上記約1/3のように小さくてもよいことを意味し、送受信距離を長くすることができる。この電流制限機能は、上記バイアス回路BIASでの電流設定により任意にできるから、上記電源回路の性能も考慮して通信可能な距離を上記電流制限により設定することも可能となる。

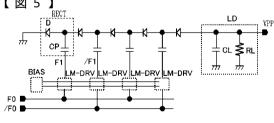

## [0019]

図 5 には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例の回路図が示されている。この実施例では、各段の昇圧容量 C P ごとに電流制限回路付きの駆動回路 L M - D R V が設けられる。パルス F 0 と / F 0 は、1段ごとにダイオード D とキャパシタ C P からなる要素ポンプ回路に対応した駆動回路 L M - D R V にそれぞれ供給される。

# [0020]

例えば、1.3Vのような電源電圧VDDのときに、前記のように-10Vの昇圧電圧 VPPを得る場合、上記要素ポンプ回路RECTは15~16段のような多段構成となる。前記図1のようにパルスF0と/F0にそれぞれ対応して駆動回路LM-DRVを設けて、8個ずつの要素ポンプ回路RECTにパルスF1,/F1を供給する場合には、パルスF1,/F1を伝える配線が長く、しかも寄生抵抗を小さくするために配線幅も大きく形成される。この結果、パルスF1,/F1を伝える配線での寄生容量が大きくなり、か

20

30

40

50

かる寄生容量でのチャージ/ディチャージ電流が大きくなってチャージポンプ回路での電力効率が低下する。

#### [ 0 0 2 1 ]

これに対して、図5の実施例回路のように各昇圧容量 C P ごとに電流制限回路付の駆動回路 L M - D R V を設けた場合には、パルス F 0 , / F 0 を駆動回路 L M - D R V に伝える配線での電流供給能力は小さくてよいので配線幅を小さくできる。これにより、パルス F 1 , / F 1 が伝えられる駆動回路 L M - D R V から昇圧容量 C P までの配線の寄生抵抗と寄生容量を低減できるので、昇圧回路全体の電力効率が向上し、さらに電流供給能力増加の効果も期待できる。

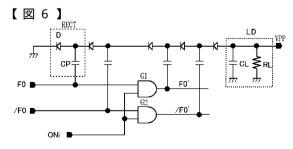

# [0022]

図6には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例の回路図が示されている。この実施例では、多段の要素ポンプ回路RECTが前段と後段とに分割されて動作させられる。同図では、4段の要素ポンプ回路RECTが2段ずつ前段と後段に分割される。前段側の2つの要素ポンプ回路RECには、パルスF0と/F0が直接供給され、後段側にはゲート回路G1とG2を通してパルスF0′と/F0′が供給される。ゲート回路G1とG2は、制御信号ONiで制御される。ゲート回路G1とG2は、例えばアンド(AND)ゲート回路で構成される。

#### [0023]

チャージポンプ回路の起動時には、制御信号ONiがロウレベル(論理0)にされて、ゲート回路G1とG2のゲートが閉じられて、パルスF0'と/F0'は共にロウレベルのままにされる。したがって、起動時には前段側の要素ポンプ回路RECTのみが動作するので、チャージポンプ回路での消費電流を半減させることができる。そして、一定時間経過後に制御信号ONiがハイレベル(論理1)にされて、ゲート回路G1とG2のゲートが開かれてパルスF0,/F0に対応したパルスF0'と/F0'が後段側の要素ポンプ回路に供給される。これにより、後段側の要素ポンプ回路も動作を開始して上記昇圧電圧VPPが形成される。この例では、2分割したが、さらに要素ポンプ回路が前記16段のように多段に接続されている場合は、3分割,4分割のように分割数を増やすようにしても良い。

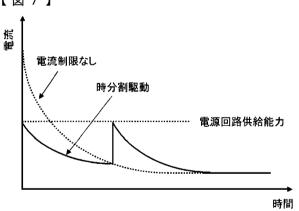

# [0024]

図7には、図6のチャージポンプ回路の動作電流の説明図が示されている。図7に示すように昇圧容量の初期充電が時間的に分散されるので、昇圧ポンプ回路の起動初期の電流を半分に低減することができる。つまり、後段の起動開始時間をONi(i=0,1,……)適当に調整することにより、昇圧ポンプ回路の消費電流のピーク値を制御することができる。このようにして分散されたチャージポンプ回路の消費電流が電源回路供給能力以下であればよい。言い換えるならば、電源回路での電源供給能力が上記チャージポンプ回路のピーク電流を超えたときに、かかる無線ICタグは信号発信源との間で通信可能な状態となるものである。

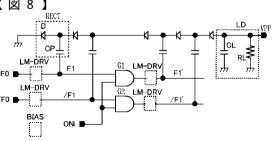

# [ 0 0 2 5 ]

図8には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例の回路図が示されている。この実施例では、前記図1の実施例と図6の実施例が組み合わされる。つまり、図6の実施例のように昇圧ポンプ回路の時分割駆動のためのゲート回路G1,G2に加えて、それぞれの分割プロックに対応して前記図1の実施例のような電流制限回路付きの駆動回路LM-DRVを設けたことである。

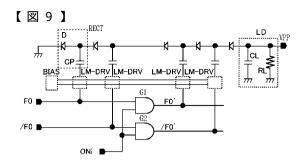

# [0026]

図9には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例の回路図が示されている。この実施例では、前記図5の実施例と図6の実施例が組み合わされる。つまり、前記図5のように各段の昇圧容量CPごとに電流制限回路付きの駆動回路LM-DRVが設けられる。そして、図6の実施例のように昇圧ポンプ回路の時分割駆動のためのゲート回路G1,G2に加えて、それぞれの分割ブロックに対応してパルスF0,/F0及びF0',/F0'を供給するというものである。

30

40

50

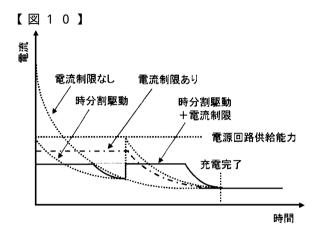

#### [0027]

図10には、図8及び図9のチャージポンプ回路の動作電流の説明図が示されている。電流制限回路付き駆動回路と時分割駆動の効果が合わさって、それぞれ単独で用いた場合よりも、動作電流を低減できる。つまり、同図においては、点線により電流制限なしと時分割駆動との電流波形が示され、一点鎖線により電流制限ありの電流波形が示され、実線により時分割駆動+電流制限の電流波形が示されている。

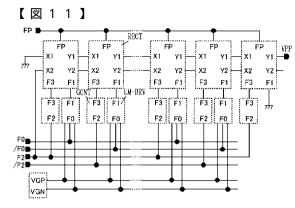

#### [0028]

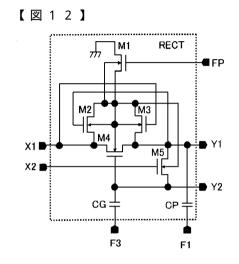

図11には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例のプロック図が示されている。この実施例では、昇圧ポンプ回路の整流素子にMOSトランジスタを用い、しきい値電圧Vthによる電圧降下が発生しないようにゲートレベルを制御するようにしたことである。つまり、要素ポンプ回路RECTは、端子X1,X2,F1,F3及びY1,Y2とFPを備え、端子F3に供給するパルスゲート制御回路GCNT、及び前記駆動回路LM-DRVが設けられる。

## [0029]

各要素ポンプ回路RECTの端子FPは共通に接続されてパルスFPが供給される。端子F3は、前記ゲート制御回路の出力F3がそれぞれ接続される。最終段の要素ポンプ回路RECTを除いて端子F1には、前記駆動回路LM-DRVの出力端子F1がそれぞれ接続される。最終段の要素ポンプ回路RECTの端子F1は、回路の接地電位が与えられる。そして、初段要素ポンプ回路RECTの端子X1に接地電位が供給され、端子X2にはパルスF2が供給される。要素ポンプ回路RECTの出力端子Y1とY2は、次段要素ポンプ回路RECTの入力端子X1とX2にそれぞれ接続される。最終段要素ポンプ回路の出力端子Y1から昇圧電圧VPPが出力され、端子Y2はオープン状態とされる。

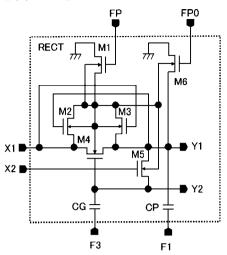

## [0030]

図12には、図11の要素ポンプ回路の一実施例の回路図が示されている。キャパシタ C P は昇圧容量、MOSトランジスタM1~M5が整流回路である。ここで、 i 番目の要素ポンプ回路RECTに着目する。駆動回路LM-DRVにより端子F1がVDDになるとき、ゲート制御回路GCNTは端子F3に2VDDに昇圧する。MOSトランジスタM4のゲート電位は、前のサイクルで-iVDDになっているので、このとき-(i-2)VDDになる。一方、キャパシタCPの他端側が接続された端子Y1は前のサイクルで-iVDDになる。上記MOSトランジスタM4のソースが接続される端子X1は-(i-1)VDDになる。上記MOSトランジスタM5にがって、MOSトランジスタM4のゲート-ソース電圧は、VDDとなりしきい値電圧Vthの損失無アリカンジスタM4のゲート・ソース電圧は、VDDとなりしきい値電圧Vthの損失無アップ直前に、パルスFPによりオン状態になってMOSトランジスタM1は、スタートアリカンで、パルスFPによりオン状態になってMOSトランジスタM2、M3、M4の基板電位をVSSにし、ゲート・基板容量による結合で基板電位が上昇し、ラッチアップが生じるのを防ぐ働きをする。

# [0031]

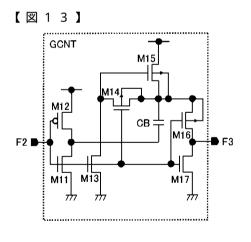

図13は、図11のゲート制御回路の一実施例の回路図が示されている。VDD振幅のパルスF2を電源電圧VDDにすることで、MOSトランジスタM15を通してキャパシタCBに充電が行われる。ここで、MOSトランジスタM15はPチャネル型なのでしきい値電圧Vthの損失無くキャパシタCBに電荷を充電することができる。一方、MOSトランジスタM16はオフ状態、MOSトランジスタM17はオン状態であるので、出力F3はVSSになっている。次に、パルスF2が接地電位VSSになるとキャパシタCBのMOSトランジスタM12側はM12のオン状態により電源電圧VDDになりMOSトランジスタM16側は2VDDに昇圧される。このとき、MOSトランジスタM16のゲートはVSSなのでMOSトランジスタM16を通して電荷が外部へ流出する。この結果、出力パルスF3はロウレベルがVSS、ハイレベルが2VDDのパルスとなる。

#### [0032]

以上図11~図13の実施例回路を用いることにより、前記図1等のようなダイオードの順方向電圧又はMOSFETをダイオード接続した場合のしきい値電圧Vthによる電圧

30

40

50

損失がなくすることができる。このため昇圧ポンプ回路の出力電圧をより高くすることができる。逆にいうなら、必要な出力電圧VPPが同じなら上記縦列する要素ポンプ回路RECTの段数を減らすことができる。

#### [0033]

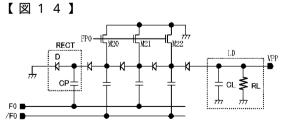

図14には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例の回路図が示されている。この実施例は、前記図30図に示したようなディクソン型と言われるチャージポンプ回路の第2段目以降の昇圧容量CPごとにプリチャージ用のスイッチ素子M20~M22を設ける。このように昇圧容量CPごとにプリチャージ用のスイッチ素子M20~M22を設け、パルスF0と/F0を共にハイレベル(VDD)にすることにより、昇圧回路を起動する前に昇圧容量を充電しておくことができる。これにより、ポンプ動作の起動時にはプリチャージの分の電流を低減することができる。上記一斉のプリチャージ時に大きなピーク電流が流れるなら、MOSトランジスタM20~M22に電流制限機能、言い換えるならば、小さな素子サイズとしてオン抵抗値を利用して電流制限を行いつつ、上記プリチャージ動作を行うようにすればよい。

#### [0034]

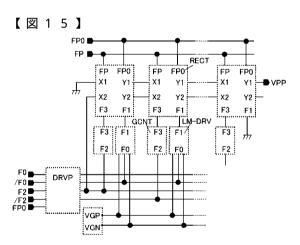

図15には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例のブロック図が示されている。この実施例は、前記図11の変形例であり、要素ポンプ回路RECTに端子FP0が追加されて、それらが共通に接続されてパルスFP0が供給される。また、これに対応してプリチャージ制御付駆動回路DRVPが設けられる。他の構成は、前記図11と同様である。

## [0035]

図16には、図15の要素ポンプ回路の一実施例の回路図が示されている。この実施例では、図12の要素ポンプ回路にMOSトランジスタM6が追加される。このMOSトランジスタM6は、回路の接地電位と端子Y1との間にソース・ドレイン経路が接続され、ゲートが上記追加された端子FP0に接続される。他の構成は、前記図12の実施例と同様である。

#### [0036]

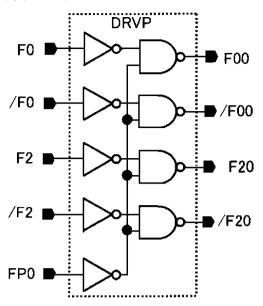

図17には、図15のプリチャージ制御付駆動回路DRVPの一実施例の回路図が示されている。プリチャージ制御付駆動回路DRVPは、パルスF0,/F0,F2,/F2をそれぞれ受けるインバータ回路に入力し、その出力信号をナンド(NAND)ゲート回路を通してパルスF00,/F00,F20,/F20として出力する。上記ナンドゲート回路は、追加されたパルスFP0を受けるインバータ回路の出力信号によりゲートが制御される。

# [0037]

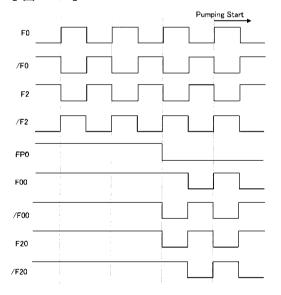

図18には、図15のチャージポンプ回路の動作を説明するためのタイミング図が示されている。パルスFP0は昇圧容量プリチャージ信号とされ、チャージポンプ回路起動前にハイレベル(『H")にしてプリチャージを行う。このパルスFP0のハイレベルによって、図17のゲート回路がゲートを閉じられてF00,/F00及びF20,/F20は全てがハイレベルにされる。これによって、前記図14の実施例と同様に昇圧容量CPごとにプリチャージ動作が行われる。つまり、各要素ポンプ回路RECTのMOSトランジスタM6が前記スイッチ素子M20等の役割を果たす。

# [0038]

昇圧ポンプ回路起動時にはパルスFP0をロウレベル( "L" )にする。これにより、パルスF0,/F0及びF2,/F2に対応してパルスF00,/F00及びF20,/F20が出力されて昇圧動作が開始される。この実施例では、各要素ポンプ回路RECTに駆動回路LM-DRVによる電流制限機能に、前記図11のようなプリチャージ動作を組み合わせるものである。

# [0039]

図19には、図15のチャージポンプ回路の動作を説明するためのタイミング図が示さ

30

40

50

れている。同図は、タイミングを大きなスケールで示したものである。ライトやイレーズ動作の前に昇圧容量のポンプ容量プリチャージを行う。つまり、前記パルスFP0をハイレベルにする。このプリチャージは、パワーオン直後から開始しても良い。この場合は、他の回路の電流にと重なっても良いようにプリチャージ用のスイッチMOSトランジスタM6のオン抵抗を大きしておくと、より大きな電流低減効果が得られる。

#### [0040]

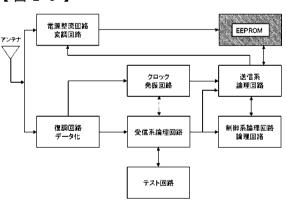

図20には、この発明が適用される無線ICタグの一実施例のブロック図が示されている。アンテナに対して電源整流回路及び変調回路と復調回路データ化が設けられる。電源整流回路は、アンテナにより電気信号に形態にされた受信信号を整流して電源電圧VDDを形成する。上記復調回路は、上記受信信号を復調してデジタルのデータにする。上記復調信号に含まれるクロック成分がクロック発振回路に伝えられ、同期化されたクロックが再生される。受信系論理回路は、上記再生されたクロックを用いて受信されたデータを受を受け取る。制御系論理回路及び論理回路は、全体の制御動作を行う。送信系論理回路は、送信信号を変調してアンテナを通して出力させる。

#### [0041]

メモリとして不揮発性メモリEEPROMが設けられる。この不揮発性メモリEEPROMは、電源整流回路からの電源電圧を受けて、ライト動作やイレーズ動作に必要なチャージポンプ回路を備えている。特に制限されないが、上記不揮発性メモリEEPROMは、送信系論理回路を介してライト/リード及びイレーズの制御が行われる。上記不揮発性メモリEEPROMへのライトデータは、受信系論理回路で受信されたデータ又は制御系論理回路で加工される。上記不揮発性メモリEEPROMからのリードデータ又は制御系論理回路で加工されたデータは、送信系論理回路を通して上記変調回路に伝えられて出力される。また、テスト回路が設けられて各種テストが実施される。

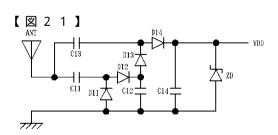

## [0042]

図21には、図20の電源整流回路の一実施例の回路図が示されている。アンテナで受信された受信電圧が負電圧のときにダイオードD11を介してキャパシタC11に充電動作が行われる。上記アンテナで受信された受信電圧が正電圧のときに、ダイオードD123を通して昇圧された電圧でキャパシタC12を充電させる。このようにして、キャパシタ12には正電圧が蓄積される。したがって、アンテナで受信された受信電圧が負電圧のときにダイオードD13を介してキャパシタC13にはより高い電圧で充電動作が行われる。そして、上記アンテナで受信された受信電圧が正電圧のときに、上記昇圧された電圧が加わってダイオードD14を通して出力キャパシタC14を充電させる。特に制限されないが、ツェナーダイオードZDは、出力電圧VDDが高くなり過ぎて、内部回路の耐圧以上の電圧になるのを防止する。

# [0043]

無線ICタグに電源整流回路は、上記のような受信信号を整流して形成するものであるので、電流供給能力を超える負荷電流が流れると上記出力キャパシタC14の電位が低下して、内部回路の下限電圧以下になってしまうものである。このため、無線ICタグは、内部回路の動作電流が上記電源整流回路の電流供給能力よりも小さいことが条件とされ、この条件が成立しないときに動作しなくなる。

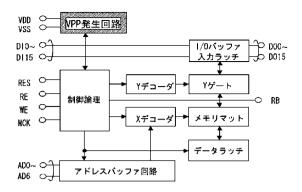

#### [0044]

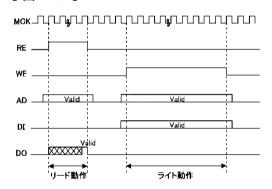

図22は、図20のEEPROMの一実施例のブロック図が示されている。制御論理は、信号RES、RE及びWEとクロックMCKを受けてメモリ動作モードの判定と、それに必要なYアドレス信号と各種制御信号を生成する。メモリマットはメモリセルがマトリックス状態に配置されて構成される。アドレスバッファはアドレス信号AD0~AD6を受けて、XデコーダにXアドレス信号を供給する。Xデコーダは、上記Xアドレス信号を解読してメモリマットのワード線の選択動作を行う。データラッチは、1ワード線分のデータを一時的に保持する。ワード線が選択されると、データラッチに記憶データが保持される。I/Oバッファを通して入力されたライトデータは、Yデコーダで形成された選択

信号に従ってYゲートを介してデータラッチに対して記憶させ、ワード線単位でのライト動作が行われる。リード動作のとき、Yゲートは上記データラッチからYデコーダで指示されたデータ単位(D00~D15)を選択し、I/Oバッファを通して出力させる。

# [0045]

特に制限されないが、ワード線単位でのイレーズが行われる構成では、読み出し動作によりデータラッチに記憶データを取り込んでおいて、かかるワード線のメモリセルを一斉にイレーズし、データラッチに対して任意のデータ単位でのライトデータを入力し、その後に1ワード線単位でのライト動作を行うことにより、1ワード線分のうちの一部のデータの書き換えが行われる。VPP発生回路は、前記実施例のチャージポンプ回路が用いられる。つまり、電源電圧VDDとVSSを受け、発振回路で形成されたパルス又は入力されたクロックMCKを用いてライト又はイレーズに必要な昇圧電圧VPPを形成する。

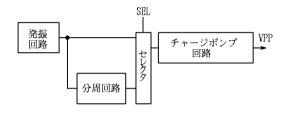

#### [0046]

図23には、この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例のブロック図が示されている。この実施例は、チャージポンプ回路の駆動周波数を最初は低く、途中から高くなるように制御することでも同様な電流低減効果が得られる。つまり、発振回路の発振パルスと、それを分周回路で分周した低い周波数のパルスとを形成しておいて、セレクタにより切り替えるというものである。つまり、選択信号SELにより、最初は分周された低い周波数のパルスでチャージポンプ回路を動作し、一定時間経過後に上記選択信号SELにより発振パルスに切り替える。この方式によれば、バイアス回路を設ける必要がないのでその分消費電流を低減できるという利点がある。この方式と前記各実施例を適当に組み合わせてもよい。

# [0047]

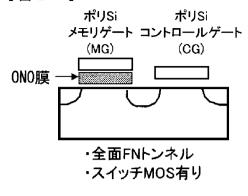

図24には、この発明に用いられるEEPROMのメモリセルの一実施例の素子構造断面図が示されている。この実施例のメモリセルは、メモリトランジスタ(MG)とスイッチMOSトランジスタ(CG)の2トランジスタ構成からなる。2トランジスタともにゲートはポリシリコンで構成され、スイッチMOSのゲート(CG)は、コントロールゲートやワード線とも呼ばれる。メモリトランジスタはゲート絶縁膜がONO膜からなり、ナイトライド膜内のトラップに電子を捕獲することで電荷を保持し不揮発性メモリとなる。トラップに一定量以上の電子が捕獲された状態が "0"、電子捕獲が少なくホールが一定量以上捕獲された状態が "1"である。EEPROMでは消去後のメモリセル状態を "1"と定義する。 "1"状態のメモリでは、読み出し時に、メモリゲート電位を 0 Vとしても、ドレインに読み出し電圧Vrを印加すると、ソース 0 Vで電流が流れるため、非選択メモリはワード線電位を 0 Vにして電流を遮断する。

# [0048]

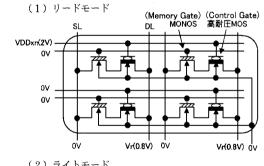

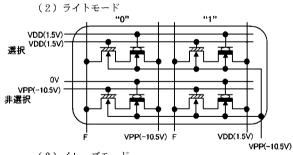

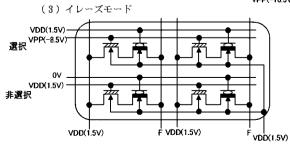

図 2 5 には、この発明に用いられるEEPROMの動作を説明するためのメモリマット 部の回路図が示されている。同図(1)はリードモードであり、(2)はライトモードで あり、(3)はイレーズモードである。

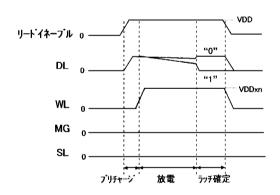

## [0049]

図25(1)のリードモードは、同図のバイアス条件及び図26のタイミング図に示すをように、EEPROMの読出し時メモリ電流の大きさは、メモリに保持している電荷量を反映している。 "1"状態のメモリではナイトライド膜内のトラップにホールが捕獲されていて、チャネル電流が流れやすく、例えば数10 μ A のような大きさの電流が流れる。 "0" 状態のメモリではナイトライド膜内のトラップに電子が捕獲されていて、チャネル電流が流れない。この特性を用いて、読み出し時には、まずデータ線 D L にプリチャージを流が流れない。この特性を用いて、読み出し時には、まずデータ線 D L にプリチャージを流が流れない。この特性を用いて、選択ワード線の電位を上げる。ワード線の S トランジスタの V thに依存するが、スイッチ M O S トランジスタの V thに依存するが、スイッチ M O S トランジスタの V thに応じて電源電圧 V D D から昇圧をしてのカン抵抗を十分に小さくするために、必要に応じて電源電圧 V D D から昇圧を見が反転してデータ線は 0 V となる。 "0" 状態のメモリを読む場合は、データ線は D F に応じてデータ線は D F に応じるとチャージシェアで電位が少し低下するが、センスラッチの反転電圧

20

30

40

20

30

40

50

りも高く維持されてラッチの電源電圧に等しい電位となる。このデータ線電位の差で "1" と "0" を判定する。

#### [0050]

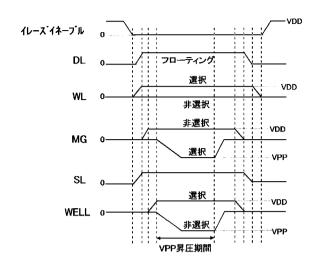

図25(3)のイレーズモードは、同図のバイアス条件及び図27のタイミング図に示すように、選択メモリゲートには負の高電圧VPP、選択WELL(ウェル)には電源電圧VDDを引加する。 データ線はフローティングとする。 選択されたメモリゲートと基板WELLの電位差による電界でトンネリング電流が流れて、ホールがナイトライド膜内のトラップに捕獲されると消去されて "1"状態となる。消去では、まず非選択メモリゲートと選択WELLの電位をVDDに上げる。その後、消去用のチャージポンプ回路によって選択メモリゲートと非選択WELLとに同時に負の高電圧VPPを印加する。

#### [0051]

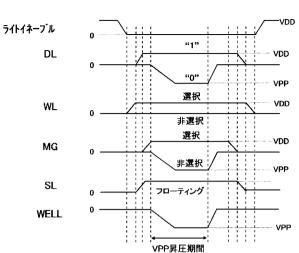

図25(2)のライトモードは、同図のバイアス条件及び図28のタイミング図に示すように、選択メモリゲートには電源電圧VDD、ウェルWELLには負の高電圧VPPを引加する。 データ線には、書き込むデータが "0" の場合は負の高電圧VPP、 "1" の場合はVDDを引加する。メモリゲートとチャネルの電位差による電界でトンネリング電流が流れて、電子がナイトライド膜内のトラップに捕獲されると "0" 状態となる。書き込みでは、データ線の電位を選択メモリゲートに伝達するために選択ワード線WLの電位を上げる。次にデータ線DLにデータ "1" に対応した書き込み阻止電圧を印加する。次に選択メモリゲートMGの電位を上げる。その後書き込み用のチャージポンプ回路によってウェルWELLと非選択メモリゲートに同時に負の高電圧VPPを印加する。

#### [0052]

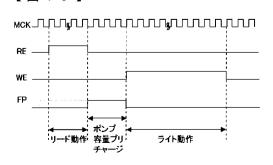

図29には、図22のEEPROMの動作の一例を説明するためのタイミング図が示されている。信号REのハイレベルによりリード動作が指示される。アドレス信号ADによりメモリマットの選択動作が行われて出力端子DOからリードデータが出力される。次に、信号WEがハイレベルにされてライト動作が指示される。アドレス信号ADによりメモリセルの選択動作が行われ、ライトデータDIの入力が行われる。このとき、1つのワード線分のライトデータがデータラッチに入力され、あるいはワード線の選択動作によってデータラッチに記憶データが保持され、特定のYアドレスについてライトデータが入力され、データラッチのデータがメモリセルに書き込まれるとき、チャージポンプ回路が動作を開始して上記昇圧電圧VPPを形成する。

# [0053]

このようなライトのためにチャージポンプ回路の動作を開始すると、前記電流制限機能を設けない場合には電源電圧VDDが急激に低下して、無線ICタグの内部回路全体が動作不能となってしまう。つまり、上記データラッチに記憶されたライトデータが失われてしまい、実質的に無線ICタグは動作不能となる。これに対して、本願のチャージポンプ回路を用いた場合には、ポンピング動作開始時に電流制限が行われて無線ICタグの動作電圧VDDが確保され、上記ライトデータが失われることなく正しくメモリセルに書き込まれる。このことは、イレーズモードを実行するときも同様である。つまり、特定のワード線を選択し、データの書き換えを行うときにはデータラッチに書き換えデータが入力された状態でイレーズが行われるので、上記書き換えデータを確保するためには、チャージポンプ回路に電流制限機能を設けることが必要である。

# [0054]

無線ICタグでは、上記EEPROMの他の受信系論理回路や制御系論理回路に含まれるレジスタ等に記憶された記憶回路の記憶情報が上記チャージポンプ回路の起動によって失われてしまうことがないようにするためにも上記電源電圧VDDが維持されることは重要である。

# [0055]

以上説明したように本願のチャージポンプ回路においては、(1)要素ポンプ回路の昇 圧ポンプ容量を駆動するインバータ回路に電流制限用の素子を追加することで、昇圧ポン

20

30

40

50

プ容量の充電電流が制限され、昇圧開始の最初のサイクルでの大きな電流が流れることを防止できる。(2)要素ポンプ回路を複数ブロックに分割し、1ブロックずつ順番に活性化することにより昇圧ポンプ容量の充電電流が分散されるので最初のサイクルでの大きな電流が流れることを防止できる。(3)電流制限機能を持った駆動回路を昇圧容量の間配置することで、起動時の電流を減らすことができると同時に駆動回路と昇圧容量の間の寄生容量と寄生抵抗が減少するので、回路の電力効率も向上できる。(4)昇圧回路の駆動周波数を最初は小さく、途中から大きく制御することで、定常動作時の電流供給能力を維持したまま、最初のサイクルでの昇圧ポンプ容量充電による大きな貫通電流を抑制することが可能である。(5)パワーオン時または昇圧ポンプ回路の起動前にポンプ内の容量をゆっくり充電することにより昇圧ポンプ容量の充電電流が分散されるので最初のサイクルでの大きな電流が流れることを防止できる。

[0056]

(6)上記(1)と(2)~(5)のいずれかまたは複数を組み合わせることにより両者の効果が合わさってさらに最初のサイクルでの昇圧ポンプ容量充電による大きな貫通電流を抑制することが可能である。(7)上記(2)と(3)~(5)のいずれかまたは両方を組み合わせることにより両者の効果が合わさってさらに最初のサイクルでの昇圧ポンプ容量充電による大きな貫通電流を抑制することが可能である。(8)上記(4)と(5)を組み合わせることにより両者の効果が合わさってさらに最初のサイクルでの昇圧ポンプ容量充電による大きな貫通電流を抑制することが可能である。以上のように、最初のサイクルでの電流が抑えられるが、昇圧動作の残り期間での電流供給能力は十分にあるため、高電圧へ昇圧に必要な時間を短く保ちつつ、消費電流のピークを抑え電流仕様を満足することが可能となる。

[0057]

以上本発明者によってなされた発明を、上記実施形態に基づき具体的に説明したが、本発明は、上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能である。無線タグICに限定されることはなく、非接触型のICカードでもよい。更に、例えば伝播されたエネルギーは光又は音であってもよい。つまり、光を電気信号に変換し、それにより電源電圧を形成したり、音声を電気信号に変換してそれを整流して電源電圧を形成したりするものにも適用できる。つまり、光応答型ICタグや音声応答型ICタグ等にも同様に適用できる。この発明は、伝播されたエネルギーを受けて電源電圧を形成し、それにより動作するチャージポンプ回路を備えた各種半導体集積回路装置に広く利用できる。

【図面の簡単な説明】

[0058]

【 図 1 】 この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の一実施例を示す回路図である。

【図2】図1の駆動回路LM-DRVの一実施例を示す回路図である。

【図3】図1のバイアス回路BIASの一実施例を示す回路図である。

【図4】図1のチャージポンプ回路の動作電流の説明図である。

【図 5 】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例を示す回路図である。

【図 6 】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例を示す回路図である。

【図7】図6のチャージポンプ回路の動作電流の説明図である。

【図8】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例を示す回路図である。

【図9】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一実施例を示す回路図である。

【図10】図8及び図9のチャージポンプ回路の動作電流の説明図である。

【図11】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一

実施例を示すブロック図である。

- 【図12】図11の要素ポンプ回路の一実施例を示す回路図である。

- 【図13】図11のゲート制御回路の一実施例を示す回路図である。

- 【 図 1 4 】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一 実施例を示す回路図である。

- 【図15】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一 実施例を示すブロック図である。

- 【図16】図15の要素ポンプ回路の一実施例を示す回路図である。

- 【図17】図15のプリチャージ制御付駆動回路DRVPの一実施例を示す回路図である

- 【図18】図15のチャージポンプ回路の動作を説明するためのタイミング図である。

- 【図19】図15のチャージポンプ回路の動作を説明するためのタイミング図である。

- 【図20】この発明が適用される無線ICタグの一実施例を示すブロック図である。

- 【図21】図20の電源整流回路の一実施例を示す回路図である。

- 【 図 2 2 】 図 2 0 の E E P R O M の 一 実施 例 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【図23】この発明に係る半導体集積回路装置に搭載されるチャージポンプ回路の他の一 実施例を示すブロック図である。

- 【図24】この発明に用いられるEEPROMのメモリセルの一実施例を示す素子構造断面図である。

- 【図 2 5 】この発明に用いられる E E P R O M の動作を説明するためのメモリマット部の 回路図である。

- 【図26】図25のリードモードを説明するためのタイミング図である。

- 【図27】図25のイレーズモードを説明するためのタイミング図である。

- 【図28】図25のライトモードを説明するためのタイミング図である。

- 【図29】図22のEEPROMの動作の一例を説明するためのタイミング図である。

- 【図30】従来のチャージポンプ回路の一例を説明するための回路図である。

- 【図31】図30のチャージポンプ回路の動作を説明するためのタイミング図である。

【符号の説明】

[0059]

R E C T ... 要素ポンプ回路、 L M - D R V ... 駆動回路、 B I A S ... バイアス回路、 G C N T ... ゲート制御回路、 D R V P ... プリチャージ制御付駆動回路、 C P 1 ~ C P 4 ... 昇圧容量、 D 1 ~ D 1 4 ... ダイオード、 L D ... 負荷回路、 G 1 , G 2 ... ゲート回路、 M 1 ~ M 2 2 ... M O S トランジスタ、 C G ... 容量、 C 1 1 ~ C 1 4 ... キャパシタ、 Z D ... ツェナーダイオード。

10

20

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図16】

【図17】

【図18】

【図19】

【図20】

# 【図22】

# 【図23】

# 【図25】

# 【図24】

# 【図26】

# 【図27】

# 【図28】

# 【図29】

# 【図30】

# 【図31】

# フロントページの続き

(72)発明者 古野 毅

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 宇都宮 裕人

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5B035 AA11 BB09 CA12 CA23 CA31

5F038 AV06 BG02 BG04 BG05 BG06 CD06 CD16 DF01 DF05 EZ20

5H730 AA20 AS04 BB02 BB57 BB86 DD04 FG01 XC09