(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6306844号

(P6306844)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

HO 1 L 27/11582 (2017.01)

HO 1 L 21/336 (2006.01)

HO 1 L 29/788 (2006.01)

HO 1 L 29/792 (2006.01)

HO 1 L 27/11582

HO 1 L 29/788 371

請求項の数 14 (全 51 頁)

(21) 出願番号 特願2013-188119 (P2013-188119)

(22) 出願日 平成25年9月11日 (2013.9.11)

(65) 公開番号 特開2014-57067 (P2014-57067A)

(43) 公開日 平成26年3月27日 (2014.3.27)

審査請求日 平成28年8月24日 (2016.8.24)

(31) 優先権主張番号 10-2012-0100516

(32) 優先日 平成24年9月11日 (2012.9.11)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 10-2013-0013509

(32) 優先日 平成25年2月6日 (2013.2.6)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 10-2013-0013510

(32) 優先日 平成25年2月6日 (2013.2.6)

(33) 優先権主張国 韓国(KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 劉 東 哲

大韓民国 京畿道 城南市 盆唐区 蔚内

3洞 プルンマウルビヨクサンシンソンア

パート 307棟 705号

最終頁に続く

(54) 【発明の名称】3次元半導体メモリ装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に積層された複数の絶縁膜と、

隣接する前記絶縁膜の間に介在するゲート電極を含む複数の水平構造体と、

前記絶縁膜及び前記水平構造体を貫通する半導体柱を含む複数の垂直構造体と、

前記基板と前記垂直構造体との各々の間に介在する複数のエピタキシャルパターンと、

を有し、

前記エピタキシャルパターンの最小幅は、前記垂直構造体の幅より小さく、

前記エピタキシャルパターンは最下部のゲート電極に隣接するリセスされて内側に膨らむ形態に配置される丸い形の側壁を有することを特徴とする3次元半導体メモリ装置。

## 【請求項2】

前記水平構造体の中の最下部の水平構造体は、前記エピタキシャルパターンに接し、前記最下部の水平構造体は、リセスされた前記エピタキシャルパターンに沿って膨らむように配置されることを特徴とする請求項1に記載の3次元半導体メモリ装置。

## 【請求項3】

前記水平構造体の中の最下部の水平構造体は、残りの他の水平構造体より厚く、

前記エピタキシャルパターンの上部面は、前記最下部の水平構造体の上部面より高いことを特徴とする請求項1に記載の3次元半導体メモリ装置。

## 【請求項4】

前記水平構造体は、同一の厚さを有し、

10

20

前記エピタキシャルパターンは、前記基板に近く配置され、垂直的に隣接する少なくとも2つの前記水平構造体に接することを特徴とする請求項1に記載の3次元半導体メモリ装置。

**【請求項5】**

前記水平構造体の各々は、前記ゲート電極と前記半導体柱との間の第1及び第2プロッキング絶縁膜を含み、

前記第1及び第2プロッキング絶縁膜の各々は、シリコン酸化膜及びアルミニウム酸化膜の中の少なくともいずれか1つを含むことを特徴とする請求項1に記載の3次元半導体メモリ装置。

**【請求項6】**

前記垂直構造体の各々は、保護膜、電荷格納膜、及びトンネル絶縁膜を含み、

前記垂直構造体に隣接する前記水平構造体は、前記垂直構造体の電荷格納膜に接することを特徴とする請求項1に記載の3次元半導体メモリ装置。

**【請求項7】**

下部ゲートパターン及び該下部ゲートパターンを貫通して基板に連結される下部半導体パターンを含む下部構造体と、

前記下部構造体上に積層された上部ゲートパターン、該上部ゲートパターンを貫通して前記下部半導体パターンに連結される上部半導体パターン、及び該上部半導体パターンと前記上部ゲートパターンとの間に介在する垂直絶縁体を含む上部構造体と、を有し、

前記下部半導体パターンは、前記下部ゲートパターンに隣接し、前記基板の上部面に対して傾いた傾斜面によって定義されるリセス領域を有するエピタキシャルパターンを含み、

前記エピタキシャルパターンのリセス領域は第1の曲率を有する内側に膨らむ丸い形の側壁を有し、

前記上部半導体パターンの前記上部ゲートパターンに隣接する側壁は第2の曲率を有し、

前記第1の曲率の度合いは前記第2の曲率の度合いよりも大きいことを特徴とする3次元半導体メモリ装置。

**【請求項8】**

前記下部ゲートパターンの垂直的な厚さは、前記下部半導体パターンの最大幅より小さいことを特徴とする請求項7に記載の3次元半導体メモリ装置。

**【請求項9】**

前記下部構造体は、前記下部ゲートパターンを複数個含み、垂直的な位置で該下部ゲートパターンの間に配置された絶縁膜を含み、

前記絶縁膜に隣接する領域で前記下部半導体パターンの横断面は、実質的に円形状を有し、

前記リセス領域で前記下部半導体パターンの横断面は、実質的に方形状を有することを特徴とする請求項7に記載の3次元半導体メモリ装置。

**【請求項10】**

前記下部半導体パターンの最小幅は、該下部半導体パターンの最大幅と前記下部ゲートパターンの垂直的な厚さとの差異に該当することを特徴とする請求項7に記載の3次元半導体メモリ装置。

**【請求項11】**

前記下部ゲートパターンと前記下部半導体パターンとの間で前記下部ゲートパターンの上部面及び下部面に延長され、前記上部ゲートパターンと前記垂直絶縁体との間で前記上部ゲートパターンの上部面及び下部面に延長される水平絶縁膜を更に含むことを特徴とする請求項7に記載の3次元半導体メモリ装置。

**【請求項12】**

基板上に、複数の犠牲膜及び複数の絶縁膜が交互に反復的に積層された複数の薄膜構造体を形成する段階と、

10

20

30

40

50

前記薄膜構造体を貫通して前記基板を露出させる開口部を形成する段階と、

前記開口部の下部領域を満たす下部半導体膜を形成する段階と、

前記下部半導体膜が形成された前記開口部内に垂直絶縁体及び上部半導体パターンを形成する段階と、

前記薄膜構造体をパターニングして、前記開口部と離隔して前記基板を露出させるトレチを形成する段階と、

前記トレチに露出した前記犠牲膜を除去してゲート領域を形成する段階と、

前記ゲート領域の中の少なくとも最下位の1つによって露出した前記下部半導体膜を選択的にエッチングして前記基板に対して傾いた傾斜面によって定義されるリセス領域を有する下部半導体パターンを形成する段階と、

10

前記ゲート領域内にゲートパターンを形成する段階と、を有し、

前記下部半導体パターンは、エピタキシャルパターンを含み、

前記エピタキシャルパターンは、前記リセス領域によって露出された丸い形の側壁を有することを特徴とする3次元半導体メモリ装置の製造方法。

#### 【請求項13】

前記下部半導体膜を形成する段階は、前記開口部によって露出した前記基板をシード( seed )として利用する選択的なエピタキシャル工程を遂行する段階を含むことを特徴とする請求項12に記載の3次元半導体メモリ装置の製造方法。

#### 【請求項14】

前記下部半導体膜を選択的にエッチングする段階は、ハロゲン元素を含有する反応ガスを利用して気相エッチング( Gas Phase Etching )工程又は化学的乾式エッチング( chemical dry etch )工程を遂行する段階を含むことを特徴とする請求項12に記載の3次元半導体メモリ装置の製造方法。

20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体メモリ装置及びその製造方法に関し、より詳細には、メモリセルが垂直的に積層された構造の3次元半導体メモリ装置及びその製造方法に関する。

#### 【背景技術】

#### 【0002】

30

消費者が要求する優れた性能及び低廉な価額を充足させるために半導体メモリ装置の集積度を増加させることが要求されている。半導体メモリ装置の場合、その集積度は製品の価額を決定する重要な要因であるため、特に増加した集積度が要求される。従来の2次元又は平面積半導体メモリ装置の場合、その集積度は単位メモリセルが占有する面積によって主に決定されるため、微細パターン形成技術の水準に大きく影響を受ける。しかし、パターンの微細化のためには超高価な装備を必要とするため、2次元半導体メモリ装置の集積度は増加しているが、相変わらず制限的である。

#### 【0003】

このような限界を克服するために、3次元的に配列されるメモリセルを具備する3次元半導体メモリ装置が提案されている。しかし、3次元半導体メモリ装置の大量生産のためには、ビット当たりの製造費用を2次元半導体メモリ装置のそれより減少させることができながら、信頼性ある製品特性を具現できる工程技術が要求されている。

40

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】韓国特許公開第10-2010-0028827号明細書

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、集積度及び

50

信頼性を向上させた3次元半導体メモリ装置を提供することにある。

また、本発明の目的は、集積度及び信頼性を向上させることができる3次元半導体メモリ装置の製造方法を提供することにある。

**【課題を解決するための手段】**

**【0006】**

上記目的を達成するためになされた本発明の一態様による3次元半導体メモリ装置は、基板上に積層された複数の絶縁膜と、隣接する前記絶縁膜の間に介在するゲート電極を含む複数の水平構造体と、前記絶縁膜及び前記水平構造体を貫通する半導体柱を含む複数の垂直構造体と、前記基板と前記垂直構造体との間に介在する複数のエピタキシャルパターンと、を有し、前記エピタキシャルパターンの最小幅は、前記垂直構造体の幅より小さく

10

、前記エピタキシャルパターンは最下部のゲート電極に隣接するリセスされて内側に膨らむ形態に配置される丸い形の側壁を有することを特徴とする。

**【0007】**

前記水平構造体の中の最下部の水平構造体は、前記エピタキシャルパターンに接し、前記最下部の水平構造体は、リセスされた前記エピタキシャルパターンに沿って膨らむよう配列され得る。

前記水平構造体の中の最下部の水平構造体は、残りの他の水平構造体より厚く、前記エピタキシャルパターンの上部面は、前記最下部の水平構造体の上部面より高くあり得る。

前記水平構造体は、同一の厚さを有し、前記エピタキシャルパターンは、前記基板に近く配置され、垂直的に隣接する少なくとも2つの前記水平構造体に接し得る。

20

前記水平構造体の各々は、前記ゲート電極と前記半導体柱との間の第1及び第2プロッキング絶縁膜を含み、前記第1及び第2プロッキング絶縁膜の各々は、シリコン酸化膜及びアルミニウム酸化膜の中の少なくともいずれか1つを含み得る。

前記垂直構造体の各々は、保護膜、電荷格納膜、及びトンネル絶縁膜を含み、前記垂直構造体に隣接する前記水平構造体は、前記垂直構造体の電荷格納膜に接し得る。

**【0008】**

上記目的を達成するためになされた本発明の一態様による3次元半導体メモリ装置の製造方法は、基板上に、複数の絶縁膜及び複数の犠牲膜が交互に反復的に積層されたモールド構造体を形成する段階と、前記モールド構造体を貫通して前記基板を露出する貫通ホールを形成する段階と、前記貫通ホール内にエピタキシャル層を形成する段階と、前記貫通ホール内に半導体柱を含む垂直構造体を形成する段階と、前記モールド構造体をパターニングしてトレンチを形成する段階と、前記トレンチによって露出した前記犠牲膜を除去してリセス領域を形成する段階と、前記リセス領域の中の少なくとも最下位の1つによって露出した前記エピタキシャル層をエッチングしてリセスされた側壁を有するエピタキシャルパターンを形成する段階と、前記リセス領域内にゲート電極を含む水平構造体を形成する段階と、を有し、少なくとも1つの層の前記水平構造体は、前記エピタキシャルパターンに接する。

30

**【0009】**

前記エピタキシャル層を形成する段階は、前記貫通ホールによって露出した前記基板をシード(seed)として選択的なエピタキシャル工程を遂行する段階を含み、前記エピタキシャル層の上部面は、最下部の前記水平構造体の上部面より高く形成され得る。

40

前記垂直構造体を形成する段階は、前記貫通ホール内に保護膜、電荷格納膜、及びトンネル絶縁膜を順に形成する段階と、前記各貫通ホール内の前記トンネル絶縁膜上に前記半導体柱を形成する段階と、を含み得る。

前記3次元半導体メモリ装置の製造方法は、前記リセス領域を形成する段階の後に、前記リセス領域によって露出した前記保護膜を選択的に除去して前記電荷格納膜を露出させる段階を更に含むことができる。

前記保護膜を選択的に除去する段階及び前記エピタキシャル層をエッチングする段階は、同一のエッチング工程を通じて同時に遂行され得る。

50

前記犠牲膜の中の前記エピタキシャル層に接する犠牲膜は、残りの他の犠牲膜に対してエッティング選択比を有する物質を含み、前記犠牲膜を除去する段階、前記保護膜を選択的に除去する段階、及び前記エピタキシャル層をエッティングする段階は、同一のエッティング工程を通じて遂行され得る。

前記エピタキシャルパターンのリセスされた両側壁に隣接する前記ゲート電極の部分の間の間隔は、前記垂直構造体の幅より小さくあり得る。

前記垂直構造体の各々は、電荷格納膜及びトンネル絶縁膜を含み、前記水平構造体の各々は、ブロッキング絶縁膜を含み得る。

#### 【0010】

上記目的を達成するためになされた本発明の他の態様による3次元半導体メモリ装置は、下部ゲートパターン及び該下部ゲートパターンを貫通して基板に連結される下部半導体パターンを含む下部構造体と、前記下部構造体上に積層された上部ゲートパターン、該上部ゲートパターンを貫通して前記下部半導体パターンに連結される上部半導体パターン、及び該上部半導体パターンと前記上部ゲートパターンとの間に介在する垂直絶縁体を含む上部構造体と、を有し、前記下部半導体パターンは、前記下部ゲートパターンに隣接し、前記基板の上部面に対して傾いた傾斜面によって定義されるリセス領域を有するエピタキシャルパターンを含み、前記エピタキシャルパターンのリセス領域は第1の曲率を有する内側に膨らむ丸い形の側壁を有し、前記上部半導体パターンの前記上部ゲートパターンに隣接する側壁は第2の曲率を有し、前記第1の曲率の度合いは前記第2の曲率の度合いよりも大きいことを特徴とする。

10

#### 【0011】

前記下部半導体パターンの最小幅は、前記上部半導体パターンの下部幅より小さくあり得る。

前記下部半導体パターンの最大幅は、前記上部半導体パターンの最大幅より大きくあり得る。

前記下部ゲートパターンの垂直的な厚さは、前記下部半導体パターンの最大幅より小さくあり得る。

前記下部構造体は、前記下部ゲートパターンを複数個含み、垂直的な位置で該下部ゲートパターンの間に配置された絶縁膜を含み、前記絶縁膜に隣接する領域で前記下部半導体パターンの横断面は、実質的に円形状を有し、前記リセス領域で前記下部半導体パターンの横断面は、実質的に方形形状を有し得る。

30

前記下部半導体パターンの最小幅は、該下部半導体パターンの最大幅と前記下部ゲートパターンの垂直的な厚さとの差異に該当し得る。

前記下部半導体パターンは、シリコンからなり、前記傾斜面は、前記シリコンの { 1 1 1 } 結晶面 ( p l a n e ) であり得る。

前記下部ゲートパターンの水平幅は、前記上部ゲートパターンの水平幅より大きくあり得る。

前記3次元半導体メモリ装置は、前記下部ゲートパターンと前記下部半導体パターンの間で前記下部ゲートパターンの上部面及び下部面に延長され、前記上部ゲートパターンと前記垂直絶縁体との間で前記上部ゲートパターンの上部面及び下部面に延長される水平絶縁膜を更に含むことができる。

40

#### 【0012】

上記目的を達成するためになされた本発明の他の態様による3次元半導体メモリ装置の製造方法は、基板上に、複数の犠牲膜及び複数の絶縁膜が交互に反復的に積層された複数の薄膜構造体を形成する段階と、前記薄膜構造体を貫通して前記基板を露出させる開口部を形成する段階と、前記開口部の下部領域を満たす下部半導体膜を形成する段階と、前記下部半導体膜が形成された前記開口部内に垂直絶縁体及び上部半導体パターンを形成する段階と、前記薄膜構造体をパターニングして、前記開口部と離隔して前記基板を露出させるトレンチを形成する段階と、前記トレンチに露出した前記犠牲膜を除去してゲート領域を形成する段階と、前記ゲート領域の中の少なくとも最下位の1つによって露出した前記

50

下部半導体膜を選択的にエッティングして前記基板に対して傾いた傾斜面によって定義されるリセス領域を有する下部半導体パターンを形成する段階と、前記ゲート領域内にゲートパターンを形成する段階と、を有し、前記下部半導体パターンは、エピタキシャルパターンを含み、前記エピタキシャルパターンは、前記リセス領域によって露出された丸い形の側壁を有することを特徴とする。

#### 【0013】

前記下部半導体膜を形成する段階は、前記開口部によって露出した前記基板をシード( seed )として利用する選択的なエピタキシャル工程を遂行する段階を含み得る。

前記下部半導体膜を選択的にエッティングする段階は、ハロゲン元素を含有する反応ガスを利用して気相エッティング( Gas Phase Etching )工程又は化学的乾式エッティング( chemical dry etch )工程を遂行する段階を含み得る。 10

前記下部半導体パターンの最大幅は、前記上部半導体パターンの最大幅より大きくあり得る。

前記下部半導体パターンの最小幅は、前記上部半導体パターンの下部幅より小さくあり得る。

#### 【0014】

上記目的を達成するためになされた本発明の更に他の態様による3次元半導体メモリ装置は、基板上に垂直的に積層された絶縁膜及び該絶縁膜の間に介在する下部ゲートパターンを含む積層構造体と、前記下部ゲートパターンを貫通して前記基板に連結され、前記下部ゲートパターンに隣接し、前記基板に対して傾いた傾斜面によって定義されるリセス領域を有する下部半導体パターンと、を有し、前記基板の上部面に対して垂直的な方向で前記リセス領域の最大幅は、隣接する前記絶縁膜の間の垂直的な距離より小さい。 20

#### 【0015】

隣接する前記絶縁膜の間の垂直的な距離は、前記下部半導体パターンの最大幅より小さくあり得る。

前記絶縁膜に隣接する領域で前記下部半導体パターンの横断面は、実質的に円形状を有し、前記リセス領域で前記下部半導体パターンの横断面は、実質的に方形状を有し得る。

前記下部半導体パターンは、シリコンからなり、前記傾斜面は、前記シリコンの { 111 } 結晶面( plane )であり得る。 30

前記3次元半導体メモリ装置は、前記下部ゲートパターンと前記下部半導体パターンとの間で前記下部ゲートパターンの上部面及び下部面に延長される水平絶縁膜を更に含むことができる。

前記3次元半導体メモリ装置は、前記下部ゲートパターン上に積層された上部ゲートパターン、該上部ゲートパターンを貫通して前記下部半導体パターンに連結される上部半導体パターン、及び該上部半導体パターンと前記上部ゲートパターンとの間に介在する垂直絶縁体を更に含むことができる。

前記下部半導体パターンの最小幅は、前記上部半導体パターンの下部幅より小さくあり得る。

前記下部半導体パターンの最大幅は、前記上部半導体パターンの最大幅より大きくあり得る。 40

前記下部ゲートパターンの水平幅は、前記上部ゲートパターンの水平幅より大きくあり得る。

#### 【0016】

上記目的を達成するためになされた本発明の更に他の態様による3次元半導体メモリ装置の製造方法は、基板に連結される下部半導体膜及び前記基板上に垂直的に積層されて前記下部半導体膜の側壁の一部分を露出させる下部ゲート領域を定義する絶縁膜を含む下部構造体を形成する段階と、前記下部ゲート領域に露出した前記下部半導体膜を選択的にエッティングして前記基板に対して傾いた傾斜面によって定義されるリセス領域を有する下部半導体パターンを形成する段階と、前記下部ゲート領域に露出した前記絶縁膜の一部分を等方性エッティングして、前記基板の上部面に対して垂直になる前記下部半導体パターンの 50

側壁の一部分を露出させる拡張された下部ゲート領域を形成する段階と、前記拡張された下部ゲート領域内にゲートパターンを形成する段階と、を有する。

【0017】

前記拡張された下部ゲート領域の垂直的な高さは、前記下部半導体パターンの最大幅より小さくあり得る。

前記下部半導体パターンを形成する段階は、ハロゲン元素を含有する反応ガスを利用して気相エッチング (Gas Phase Etching) 工程又は化学的乾式エッチング (chemical dry etch) 工程を遂行する段階を含み得る。

前記3次元半導体メモリ装置の製造方法は、前記下部半導体パターンを形成する前に、前記下部構造体上に上部構造体を形成する段階を更に含むことができ、前記上部構造体は、垂直的に前記下部半導体パターンに連結される上部半導体パターン、該上部半導体パターンの外側壁を囲む垂直絶縁体、及び前記下部構造体上に垂直的に積層されて前記垂直絶縁体の側壁の一部分を露出させる上部ゲート領域を定義する上部絶縁膜を含み得る。

10

前記下部半導体パターンの最大幅は、前記上部半導体パターンの最大幅より大きくあり得る。

前記下部半導体パターンの最小幅は、前記上部半導体パターンの下部幅より小さくあり得る。

【発明の効果】

【0018】

本発明によれば、基板と垂直構造体とを連結するエピタキシャルパターンがリセスされた側壁を有することによって、エピタキシャルパターンに接する最下部の水平構造体はリセスされた側壁のプロフィールに沿って内側に膨らんだ形態に配置される。エピタキシャルパターンの最小幅が垂直構造体の幅より小さく形成されることによって、それらと接する水平構造体を形成する過程でマージンを確保することができるため、高信頼性の3次元半導体メモリ装置を具現することができる。

20

【図面の簡単な説明】

【0019】

【図1】本発明の一実施形態による3次元半導体メモリ装置のセルアレイを示す簡略回路図である。

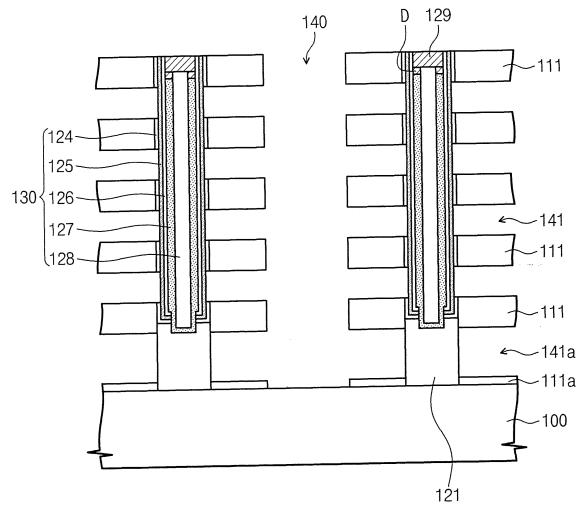

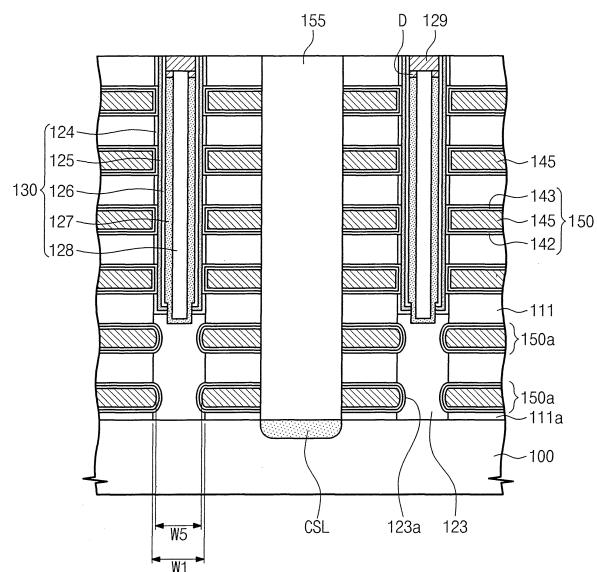

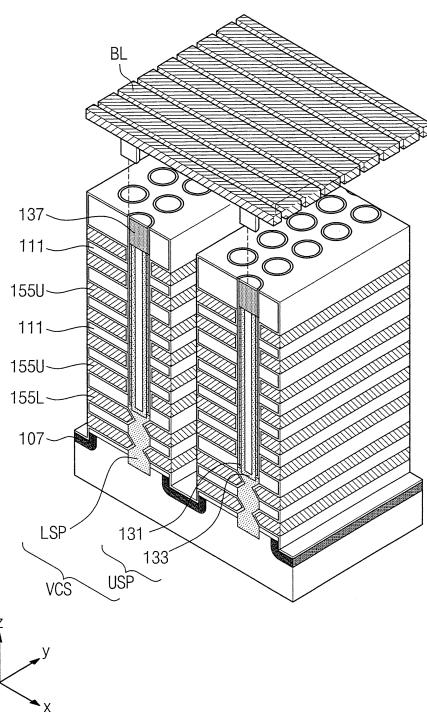

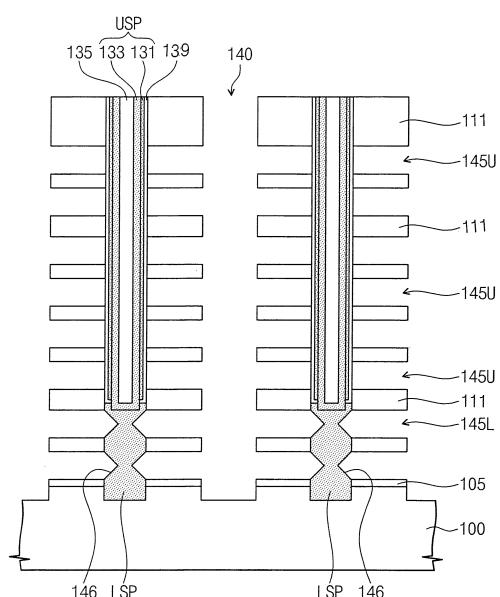

【図2】本発明の一実施形態による3次元半導体メモリ装置の構造を示す斜視図である。

30

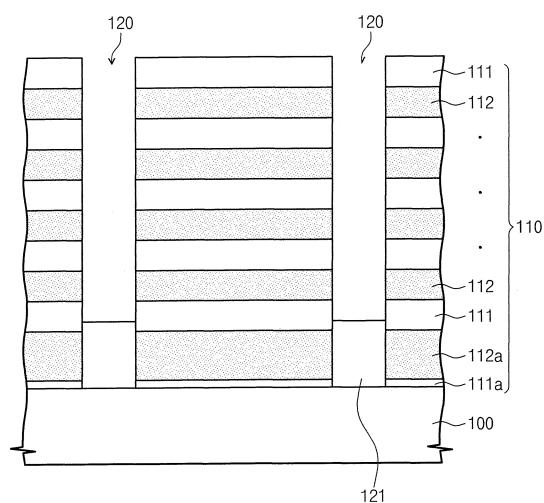

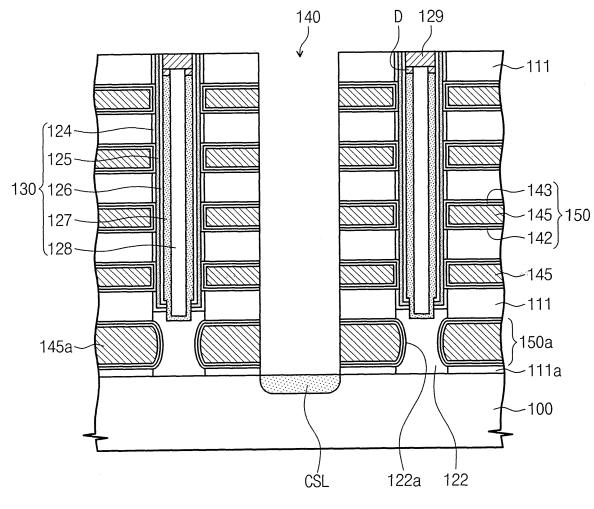

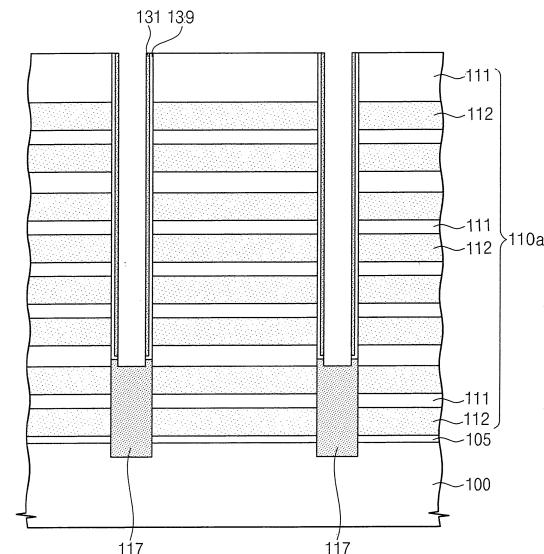

【図3】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図4】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図5】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図6】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図7】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

40

【図8】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図9】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図10】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図11】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図12】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

50

【図13】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図14】本発明の一実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図15】一般的な技術による3次元半導体メモリ装置を示す断面図である。

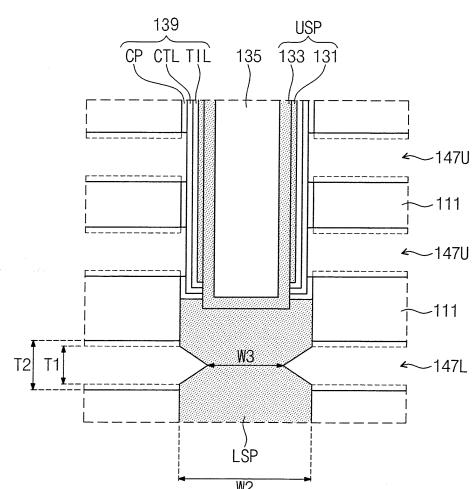

【図16】本発明の一実施形態による3次元半導体メモリ装置の他の例を示す断面図である。

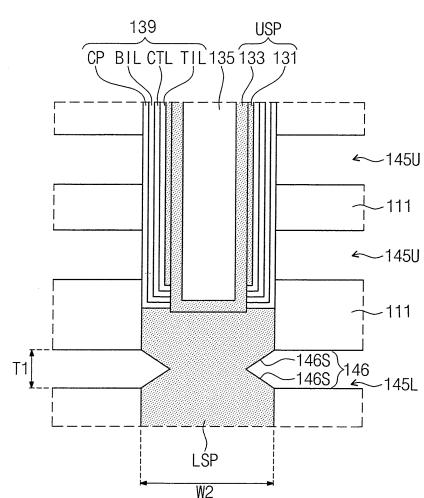

【図17】本発明の一実施形態による3次元半導体メモリ装置の更に他の例を示す断面図である。

【図18】本発明の一実施形態による3次元半導体メモリ装置を示す断面図である。 10

【図19】図18のA部分を示す図面である。

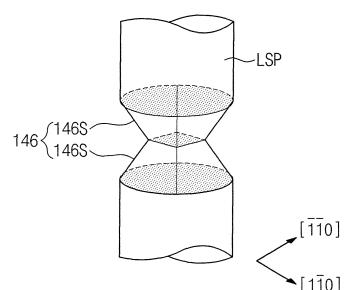

【図20】本発明の一実施形態による3次元半導体メモリ装置の下部半導体パターンを示す斜視図である。

【図21】本発明の一実施形態による3次元半導体メモリ装置の一変形形態を示す斜視図である。

【図22】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図23】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。 20

【図24】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図25】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図26】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図27】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図28】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。 30

【図29】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図30】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を示す断面図である。

【図31】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を説明するための部分断面図である。

【図32】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を説明するための部分断面図である。

【図33】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を説明するための部分断面図である。 40

【図34】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を説明するための部分断面図である。

【図35】本発明の他の実施形態による3次元半導体メモリ装置の製造方法を説明するための部分断面図である。

【図36】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

【図37】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

【図38】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

【図39】本発明の他の実施形態による3次元半導体メモリ装置の変形形態を示す部分断 50

面図である。

【図40】本発明の他の実施形態による3次元半導体メモリ装置の変形形態を示す部分断面図である。

【図41】本発明の他の実施形態による3次元半導体メモリ装置の変形形態を示す部分断面図である。

【図42】本発明の他の実施形態による3次元半導体メモリ装置の変形形態を示す部分断面図である。

【図43】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

【図44】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。 10

【図45】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

【図46】本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

【図47】本発明の他の実施形態による3次元半導体メモリ装置の更に他の例の製造方法を説明するための部分断面図である。

【図48】本発明の他の実施形態による3次元半導体メモリ装置の更に他の例の製造方法を説明するための部分断面図である。 20

【図49】本発明の他の実施形態による3次元半導体メモリ装置の更に他の例の製造方法を説明するための部分断面図である。

【図50】本発明の一実施形態による半導体記憶素子を含む電子システムの一例を示すブロック図である。

【図51】本発明の一実施形態による半導体記憶素子を含むメモリカードの一例を示すブロック図である。

【図52】本発明の一実施形態による3次元半導体メモリ装置を装着する情報処理システムの一例を示す概略ブロック図である。

#### 【発明を実施するための形態】

##### 【0020】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。 30

##### 【0021】

本発明の長所及び特徴、そしてそれらを達成する方法は、図面を参照して詳細に後述する実施形態を参照することで明確になる。しかし、本発明は、以下で開示する実施形態に限定されるものではなく、異なる多様な形態に具現でき、単に本実施形態は、本発明の開示が完全になるようにし、本発明が属する技術分野で通常の知識を有する者に発明の範疇を完全に知らしめるために提供するものである。明細書の全文に亘って同一参照符号は同一構成要素を指称する。

##### 【0022】

本明細書で使用する用語は、実施形態を説明するためのものであり、本発明を制限しようととするものではない。本明細書で单数形は文言で特別に言及しない限り複数形も含む。明細書で使用する‘含む（comprises）’及び／又は‘含む（comprising）’は、言及する構成要素、段階、動作及び／又は素子が1つ以上の他の構成要素、段階、動作及び／又は素子の存在又は追加を排除しない。また、本明細書で、ある膜が他の膜又は基板上に在ると言及する場合に、それは他の膜又は基板上に直接形成されるか、又はこれらの間に第3の膜が介在することもあることを意味する。 40

##### 【0023】

また、本明細書で記述する実施形態については、本発明の理想的な例示図である断面図及び／又は平面図を参照して説明する。図面において、膜及び領域の厚さは技術的内容の効果的な説明のために誇張したものである。従って、製造技術及び／又は許容誤差等によって例示図の形態が変形され得る。従って、本発明の実施形態は図示した特定形態に制限 50

されるものではなく、製造工程によって生成される形態の変化も含むものである。例えば、直角に図示したエッティング領域はラウンドされるか或いは所定曲率を有する形態である。従って、図面で例示した領域は概略的な属性を有し、図面で例示した領域の模様は素子の領域の特定形態を例示するためのものであり、発明の範疇を制限するためのものではない。

#### 【0024】

本発明の実施形態による3次元半導体メモリ装置は、セルアレイ領域、周辺回路領域、及び連結領域を含むことができる。セルアレイ領域には、複数のメモリセル及びメモリセルへの電気的な連結のためのビットライン及びワードラインが配置される。周辺回路領域には、メモリセルを駆動し、メモリセルに格納されたデータを読み出す周辺回路が形成され得る。具体的に、周辺回路領域(C/P)には、ワードラインドライバー(drive r)、センスアンプ(sense amplifier)、ロー(row)及びコラム(column)デコーダー、及び制御回路が配置される。連結領域はセルアレイ領域と周辺回路領域との間に配置され、ここにはビット及びワードラインと周辺回路とを電気的に連結する配線構造体が配置される。10

#### 【0025】

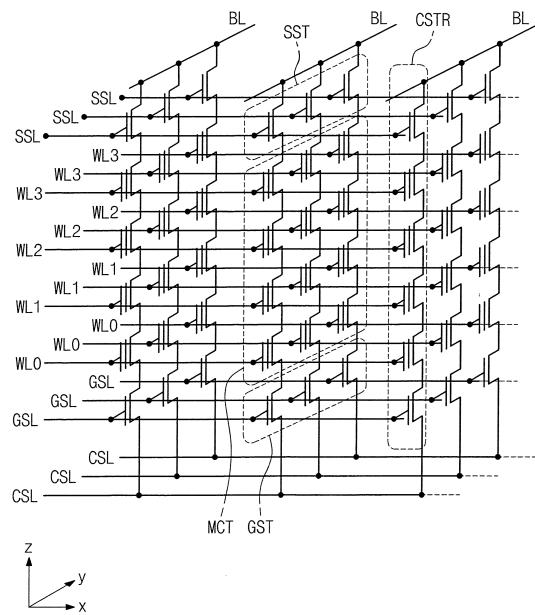

図1は、本発明の一実施形態による3次元半導体メモリ装置のセルアレイを示す簡略回路図である。

#### 【0026】

図1を参照すると、本実施形態による3次元半導体メモリ装置のセルアレイは、共通ソースラインCSL、ビットラインBL、及び共通ソースラインCSLとビットラインBLとの間に配置される複数個のセルストリングCSRを含む。20

#### 【0027】

ビットラインBLは2次元的に配列され、その各々には複数個のセルストリングCSRが並列に連結される。セルストリングCSRは共通ソースラインCSLに共通に連結される。即ち、複数のビットラインBLと1つの共通ソースラインCSLとの間に複数のセルストリングCSRが配置される。本実施形態によると、共通ソースラインCSLは複数個であり、複数個の共通ソースラインCSLが2次元的に配列される。ここで、複数個の共通ソースラインCSLには電気的に同一の電圧が印加されるか、又は複数個の共通ソースラインCSLの各々が電気的に制御される。30

#### 【0028】

セルストリングCSRの各々は、共通ソースラインCSLに接続される接地選択トランジスターGST、ビットラインBLに接続されるストリング選択トランジスターSST、及び接地及びストリング選択トランジスターGST、SSTの間に配置される複数個のメモリセルトランジスターMCTで構成される。そして、接地選択トランジスターGST、ストリング選択トランジスターSST、及びメモリセルトランジスターMCTは直列に連結される。

#### 【0029】

共通ソースラインCSLは接地選択トランジスターGSTのソースに共通に連結される。これに加えて、共通ソースラインCSLとビットラインBLとの間に配置される接地選択ラインGSL、複数個のワードラインWL0~WL3、及びストリング選択ラインSSLが、接地選択トランジスターGST、メモリセルトランジスターMCT、及びストリング選択トランジスターSSTのゲート電極として各々使用される。また、メモリセルトランジスターMCTの各々はメモリ要素(memory element)を含む。40

#### 【0030】

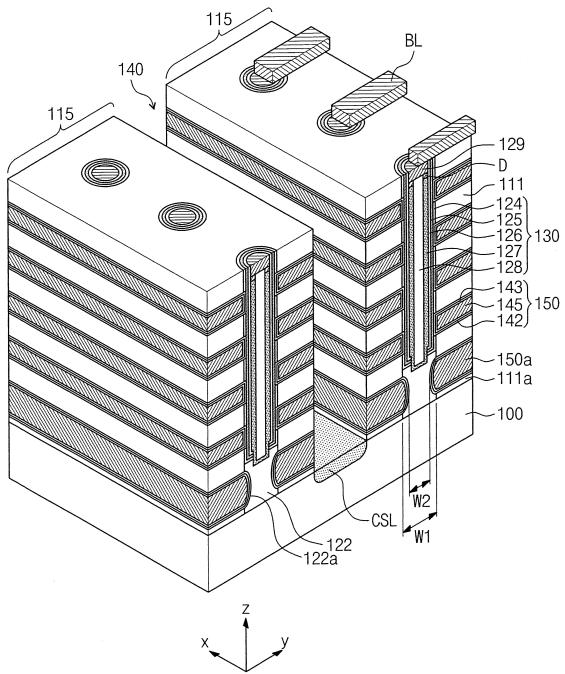

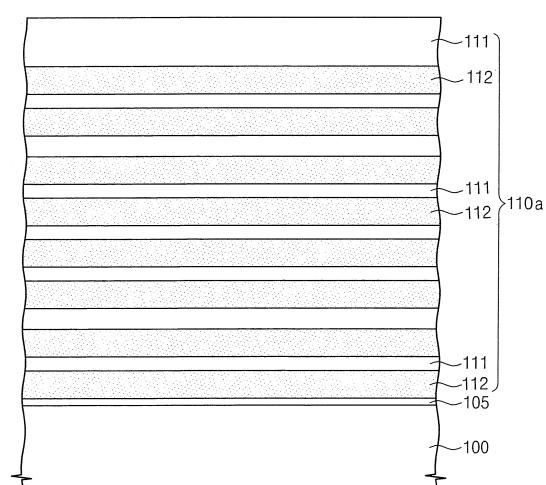

図2は、本発明の一実施形態による3次元半導体メモリ装置の構造を示す斜視図である。

#### 【0031】

図2を参照すると、基板100上に絶縁膜111a、111及び水平構造体150a、150が交互に反復的に形成された電極構造体115が配置される。絶縁膜111a、150

11及び水平構造体150a、150は第1方向に延長される。絶縁膜111a、111は一例としてシリコン酸化膜であり、絶縁膜111a、111の中の最下部の絶縁膜111aは残りの他の絶縁膜111より薄い厚さを有する。水平構造体150a、150の各々は第1及び第2ブロッキング絶縁膜142、143及びゲート電極145を含む。電極構造体115は複数個で提供され、複数個の電極構造体115は第1方向と交差する第2方向に互いに対向して配置される。第1及び第2方向は各々図2のx軸及びy軸に該当する。隣接する電極構造体115の間にはこれらを離隔させるトレンチ140が第1方向に延長される。トレンチ140によって露出した基板100内には高濃度でドーピングされた不純物領域が形成されて共通ソースラインCSLが配置される。図示しないが、トレンチ140を満たす分離絶縁膜が更に配置される。

10

#### 【0032】

電極構造体115を貫通する垂直構造体130が配置される。一例として、垂直構造体130は、平面的な視点で、第1及び第2方向に沿って整列されてマトリックス形態に配置される。他の例として、垂直構造体130は、第2方向に整列され、第1方向にジグザグ形態に配置されることもある。垂直構造体130の各々は、保護膜124、電荷格納膜125、トンネル絶縁膜126、及び半導体柱127を含む。一例として、半導体柱127はその内部の中が空いたチューブ形に配置され、この場合、半導体柱127の内部を満たす埋め込み膜128が更に配置される。半導体柱127の上部にはドレーン領域Dが配置され、ドレーン領域D上に導電パターン129が形成されて、ビットラインBLに連結される。ビットラインBLは、水平構造体150a、150と交差する方向、例えば第2方向に延長される。一例として、第2方向に整列された垂直構造体130は1つのビットラインBLに連結される。

20

#### 【0033】

水平構造体150に含まれる第1及び第2ブロッキング絶縁膜142、143及び垂直構造体130に含まれる電荷格納膜125及びトンネル絶縁膜126は3次元半導体メモリ装置の情報格納要素として定義される。即ち、情報格納要素の中の一部は垂直構造体130に含まれ、残りの一部は水平構造体150a、150に含まれる。本実施形態によると、情報格納要素の中の電荷格納膜125及びトンネル絶縁膜126は垂直構造体130に含まれ、第1及び第2ブロッキング絶縁膜142、143は水平構造体150に含まれる。

30

#### 【0034】

基板100及び垂直構造体130の間にエピタキシャルパターン122が配置される。エピタキシャルパターン122は基板100と垂直構造体130を連結する。エピタキシャルパターン122は少なくとも1つの層の水平構造体150に接する。即ち、図2に示したように、エピタキシャルパターン122は、水平構造体150、150aの中の少なくともいずれか1つ、例えば最下部の水平構造体150aに接するように配置される。他の実施形態として、エピタキシャルパターン122は、複数個の層、例えば2つの層の水平構造体150に接するように配置されることもあり、これは後述する図16で説明する。一方、図2に示したように、エピタキシャルパターン122が最下部の水平構造体150aに接するように配置された場合、最下部の水平構造体150aは、残りの他の水平構造体150より厚く配置される。エピタキシャルパターン122に接する最下部の水平構造体150aは、図1で説明した3次元半導体メモリ装置のセルアレイの接地選択ラインGSLに該当し、垂直構造体130に接する残りの水平構造体150は複数個のワードラインWL0～WL3に該当する。

40

#### 【0035】

エピタキシャルパターン122の各々はリセスされた側壁122aを有する。それによって、エピタキシャルパターン122に接する最下部の水平構造体150aはリセスされた側壁122aのプロフィールに従って配置される。即ち、最下部の水平構造体150aはエピタキシャルパターン122のリセスされた側壁122aに沿って内側に膨らむ形態に配置される。エピタキシャルパターン122の最小幅W2は垂直構造体130の幅W1

50

より小さい。本実施形態によると、エピタキシャルパターン 122 が内側にリセスされた側壁 122a を有することによって、それらと接する水平構造体 150a を形成する過程でマージンを確保することができるため、高信頼性の 3 次元半導体メモリ装置を具現することができる。

#### 【0036】

以下、図面を参照して本発明の実施形態による 3 次元半導体メモリ装置の製造方法を通じて得られる 3 次元半導体メモリ装置について、より具体的に説明する。

#### 【0037】

図 3 ~ 図 13 は、本発明の一実施形態による 3 次元半導体メモリ装置の製造方法を示す断面図である。

10

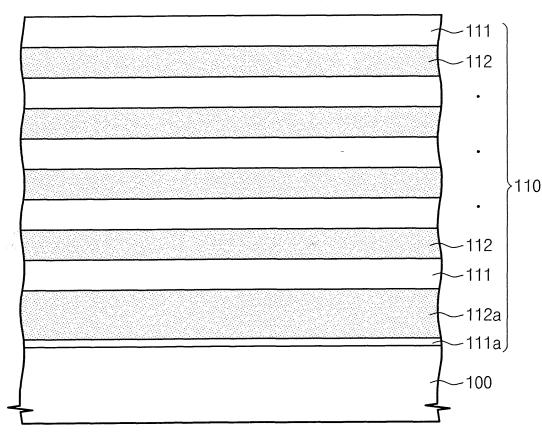

#### 【0038】

図 3 を参照すると、基板 100 上にモールド構造体 (mold stack structure) 110 が形成される。

#### 【0039】

基板 100 は、半導体特性を有する物質、絶縁性物質、絶縁性物質によって覆われた半導体又は導電体の中の 1 つである。例えば、基板 100 はシリコンウェハーである。一実施形態によると、基板 100 内に第 1 導電形の不純物をドーピングしてウェル領域（図示せず）が形成される。

#### 【0040】

モールド構造体 110 は、複数の絶縁膜 111a、111 及び複数の犠牲膜 112a、112 を含む。絶縁膜 111a、111 及び犠牲膜 112a、112 は、交互に、そして反復的に積層される。犠牲膜 112a、112 は絶縁膜 111a、111 に対してエッチング選択比を有する物質で形成される。即ち、所定のエッチングレシピを使用して犠牲膜 112a、112 をエッチングする過程で、犠牲膜 112a、112 は、絶縁膜 111 のエッチングを最少化しながら、選択的にエッチングされる物質で形成される。絶縁膜 111a、111 是シリコン酸化膜及びシリコン窒化膜の中の少なくとも 1 つであり、犠牲膜 112 是、シリコン膜、シリコン酸化膜、シリコンカーバイド、及びシリコン窒化膜の中から選択される絶縁膜 111 と異なる物質である。以下では、本発明の技術的な思想に対する容易な理解のために、絶縁膜 111 是シリコン酸化膜であり、犠牲膜 112 是シリコン窒化膜である実施形態を例に説明する。

20

#### 【0041】

本実施形態によると、犠牲膜 112 の厚さは全てが同一ではない。一例として、犠牲膜の中の最下部の犠牲膜 112a は、残りの他の犠牲膜より厚く形成される。最下部の犠牲膜 112a は、図 1 で説明した接地選択ライン GSL が形成される領域として定義される。絶縁膜 111 の厚さは全てが同一ではない。一例として、絶縁膜の中の最下部の絶縁膜 111a は、残りの他の絶縁膜及び犠牲膜 112 より薄い厚さに形成される。但し、絶縁膜 111 及び犠牲膜 112 の厚さは、図示したものから多様に変形され得、モールド構造体 110 を構成する膜の層数もやはり多様に変形され得る。絶縁膜 111 及び犠牲膜 112 は、例えば化学的気相蒸着 CVD 方法によって形成される。最下部の絶縁膜 111a は熱酸化工程によって形成される。

30

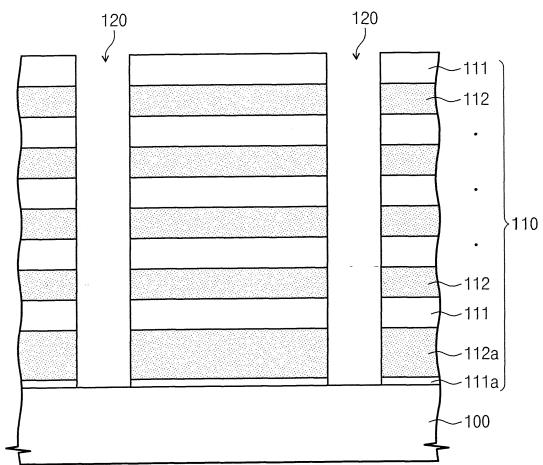

#### 【0042】

図 4 を参照すると、モールド構造体 110 を貫通して、基板 100 を露出する貫通ホール 120 が形成される。貫通ホール 120 を形成する工程は、交互に積層された絶縁膜 111 及び犠牲膜 112 を異方性エッチングして基板 100 の上部面を露出させる工程を含む。その後の工程で、貫通ホール 120 内には、図 2 で説明したエピタキシャルパターン（図 2 の 122 参照）及び垂直構造体（図 2 の 130 参照）が形成される。図 2 に示すように、貫通ホール 120 は第 1 方向及び第 2 方向に沿ってマトリックス形態に形成される。これと異なり、貫通ホール 120 は第 1 方向にジグザグに形成されることもある。第 1 及び第 2 方向は各々図 2 の x、y 軸に該当する。

40

#### 【0043】

50

図5を参照すると、貫通ホール120の一部を満たすエピタキシャル層121を形成する。エピタキシャル層121は、貫通ホール120内で、露出した基板100をシード(seed)として選択的なエピタキシャル成長(Selective Epitaxial Growth:SEG)方法で形成される。これによって、基板100が例えば単結晶シリコンである場合、エピタキシャル層121は単結晶シリコンで形成される。エピタキシャル層121は貫通ホール120によって露出した最下部の犠牲膜112aの側壁を覆うように形成される。即ち、エピタキシャル層121の上部面は、最下部の犠牲膜112aの上部面と同一であるか、或いは高く形成される。一例として、エピタキシャル層121の上部面は、最下部の犠牲膜112aの上部面より高く、最下部の犠牲膜112aの直上の絶縁膜111の上部面より低く形成される。

10

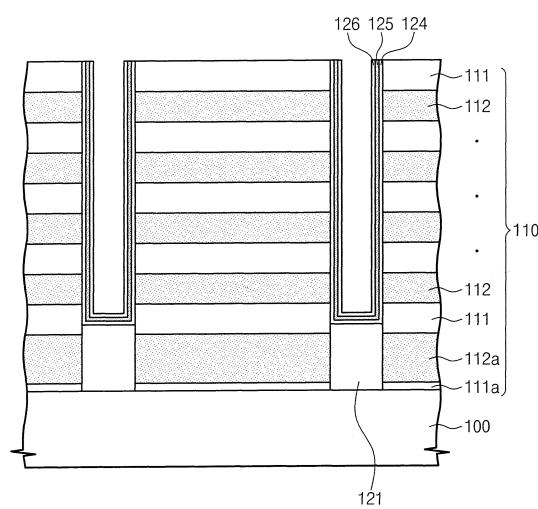

#### 【0044】

図6を参照すると、エピタキシャル層121上に保護膜124が形成される。保護膜124は、例えばシリコン酸化膜を含む。保護膜124は、エピタキシャル層121が形成された貫通ホール120内にコンフォーマルに蒸着される。保護膜124は、その後に形成される電荷格納膜125を保護する機能を遂行する。一例として、保護膜124は原子層蒸着方法で形成される。保護膜124上に電荷格納膜125が形成される。電荷格納膜125は電荷トラップ膜又は導電性ナノ粒子を含む絶縁膜である。電荷トラップ膜は、例えばシリコン窒化膜を含む。続いて、電荷格納膜125上にトンネル絶縁膜126が形成される。トンネル絶縁膜126は単層膜又は複数の薄膜で構成される多層膜である。トンネル絶縁膜126は、例えばシリコン酸化膜である。電荷格納膜125及びトンネル絶縁膜126は一例としてALD(atOMIC layer deposition)方法で形成される。

20

#### 【0045】

本実施形態によると、電荷格納膜125及びトンネル絶縁膜126が貫通ホール120内に形成されることによって、3次元半導体メモリ装置の垂直的な高さ(Vertically scale)を低くすることができる。

#### 【0046】

図7を参照すると、各貫通ホール120内のトンネル絶縁膜126上に半導体柱127が形成される。半導体柱127は単一膜又は複数の薄膜で構成される多層膜である。一例として、半導体柱127を形成する工程は、トンネル絶縁膜126上に第1半導体膜を形成し、これを異方性エッティングしてエピタキシャル層121を露出させる工程を含む。この時、第1半導体膜はトンネル絶縁膜126の側壁に残存するように形成される。続いて、貫通ホール120内の第1半導体膜上に第2半導体膜を形成することによって、半導体柱127を形成する。第2半導体膜は第1半導体膜及びエピタキシャル層121の露出した部分と接触する。エピタキシャル層121の上部面は、半導体柱127の下部面に接触する第1部分と半導体柱127に接触しない第2部分を含む。一実施形態として、エピタキシャル層121の第1部分は、エピタキシャル層121の上部面の第2部分と実質的に共面を成す。他の例として、図7に示したように、エピタキシャル層121の上部面の第1部分は第2部分より低い。即ち、半導体柱127の下部面がエピタキシャル層121の上部面の第2部分より低く形成される。半導体柱127はALD方法で形成される。半導体柱127は非晶質シリコン膜である。他の例として、熱処理工程が遂行されて半導体柱127はポリシリコン膜又は単結晶質シリコン膜に変化する。本実施形態によると、半導体柱127の第2半導体膜は貫通ホール120を完全に満たさないように形成され、半導体柱127上に貫通ホール120を完全に満たす埋め込み膜128を更に形成する。その後、半導体柱127及び埋め込み膜128は平坦化されて、最上層の絶縁膜111が露出する。他の例として、半導体柱127は貫通ホール120を完全に満たすように形成されることもある。この場合、埋め込み膜128は省略される。

30

#### 【0047】

従って、貫通ホール120内に順に形成された保護膜124、電荷格納膜125、トンネル絶縁膜126、半導体柱127、及び埋め込み膜128を含む垂直構造体130が形

40

50

成される。垂直構造体 130 はエピタキシャル層 121 によって基板 100 に連結される。

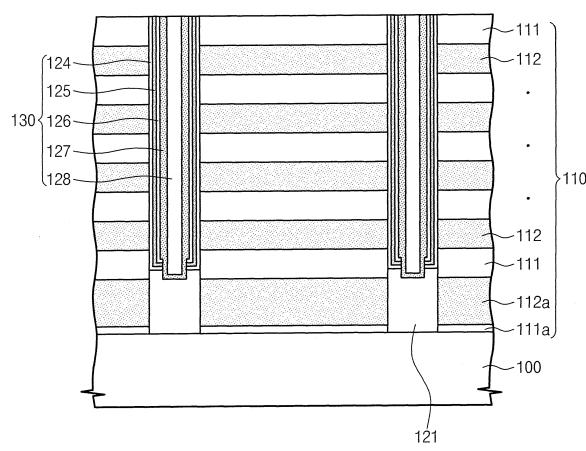

#### 【 0 0 4 8 】

図 8 を参照すると、半導体柱 127 及び埋め込み膜 128 の上部がリセスされて、最上層の絶縁膜 111 の上部面より低く形成される。半導体柱 127 及び埋め込み膜 128 がリセスされた貫通ホール 120 内に導電パターン 129 が形成される。導電パターン 129 はドーピングされたポリシリコン又は金属である。導電パターン 129 内に不純物イオンが注入されて、ドレーン領域 D が形成される。不純物イオンは、例えば N 型である。

#### 【 0 0 4 9 】

モールド構造体 110 を複数個のモールドパターンに分離させるトレンチ 140 が形成される。トレンチ 140 は隣接する垂直構造体 130 の間に形成される。トレンチ 140 を形成する工程は、絶縁膜 111 及び犠牲膜 112 を連続的にパターニングして基板 100 を露出させる工程を含む。トレンチ 140 は、第 1 方向（図 2 の x 軸方向）に延長されて形成されることによって、モールド構造体 110 を複数個のモールドパターンに分離させる。複数個のモールドパターン 110 は、第 2 方向（図 2 の y 軸方向）に互いに対向して、離隔されるように形成される。

#### 【 0 0 5 0 】

図 9 を参照すると、トレンチ 140 に露出した犠牲膜（図 8 の 112 参照）を選択的に除去してリセス領域 141a、141 を形成する。リセス領域 141a、141 は、犠牲膜 112a、112 が除去された領域に該当し、垂直構造体 130 及び絶縁膜 111a、111 によって定義される。リセス領域 141 の中の最下部のリセス領域 141a は、最下部の犠牲膜（図 8 の 112a 参照）が除去された領域として定義され、エピタキシャル層 121 を露出する。一例として、犠牲膜 112 がシリコン窒化膜又はシリコン酸窒化物を含む場合、犠牲膜 112 を除去する工程は、磷酸を含むエッティング溶液を使用して遂行される。リセス領域 141 を形成する工程は、保護膜 124 が露出する時までエッティングする工程を含む。即ち、保護膜 124 は、犠牲膜 112 の除去のためのエッティング溶液によって電荷格納膜 125 が損傷することを防止する。

#### 【 0 0 5 1 】

その後、リセス領域 141 によって露出した保護膜 124 の一部分を選択的に除去する。これによって、電荷格納膜 125 の一部が露出する。保護膜 124 を選択的に除去する工程は、電荷格納膜 125 に対してエッティング選択比を有するエッティングレシピを利用してエッティングする工程を含む。一実施形態によると、保護膜 124 を選択的に除去する過程で、最下部のリセス領域 141a によって露出したエピタキシャル層 121 はエッティングされないことがある。即ち、保護膜 124 が例えばシリコン酸化膜であり、エピタキシャル層 121 がシリコンである場合、シリコン酸化膜のみを選択的にエッティングするエッティングレシピを使用して保護膜 124 を除去することができる。一例として、保護膜 124 はフッ化水素酸を含むエッティング溶液によって除去される。

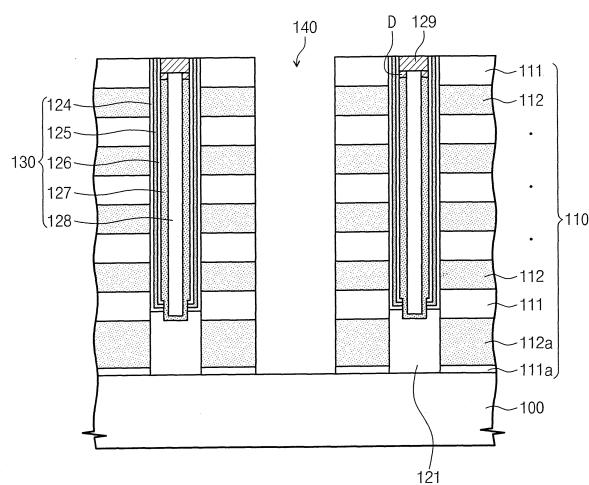

#### 【 0 0 5 2 】

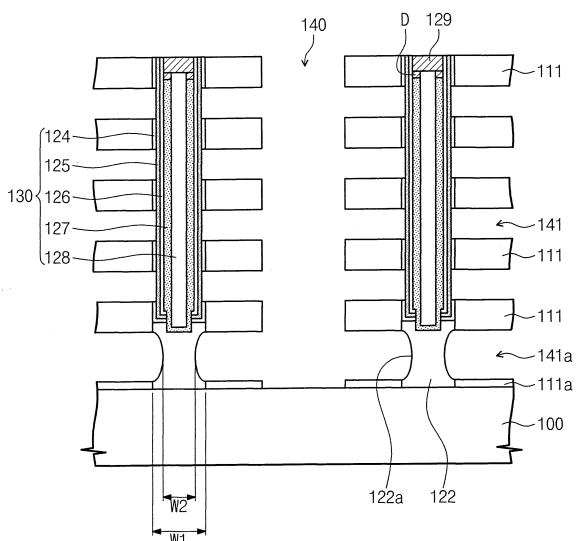

図 10 を参照すると、露出したエピタキシャル層（図 9 の 121 参照）を選択的にエッティングして、リセスされた側壁 122a を有するエピタキシャルパターン 122 を形成する。エピタキシャルパターン 122 を形成する工程は、最下部のリセス領域 141a によって露出したエピタキシャル層 121 の側壁を一部エッティングする工程を含む。エッティング工程は、電荷格納膜 125 に対するエッティング選択比を利用することによって、エピタキシャル層 121 をエッティングし、露出した電荷格納膜 125 はエッティングされないようにする。エッティング工程は湿式エッティング又は乾式エッティングを含む。一例として、湿式エッティングを利用した場合、等方性エッティングの結果、エピタキシャルパターン 122 のリセスされた側壁 122a はラウンドされた形態を有する。従って、エピタキシャルパターン 122 は、その最小幅 W2 が垂直構造体 130 及び貫通ホール 120 の幅 W1 より小さく形成される。

#### 【 0 0 5 3 】

10

20

30

40

50

他の実施形態として、図9で説明した保護膜124を選択的に除去する工程とエピタキシャルパターン122を形成する工程とは、同一のエッティング工程で同時に遂行することもできる。即ち、保護膜124が例えばシリコン酸化膜であり、エピタキシャル層121がシリコンである場合、シリコン酸化膜とシリコンを同時にエッティングできるエッティングレシピを利用して、保護膜124を除去する過程でリセスされた側壁122aを有するエピタキシャルパターン122を形成することができる。この場合にも、電荷格納膜125に対してエッティング選択比を有するエッティングレシピを利用することによって、電荷格納膜125がエッティングされないようにすることができる。一例として、エピタキシャルパターン122を形成する工程は、O<sub>3</sub>HF、SC1、又はアンモニア等を利用する湿式エッティング、又はGassを利用する乾式エッティングする工程を含む。

10

#### 【0054】

更に他の実施形態として、図9で説明したリセス領域141を形成する段階及びエピタキシャルパターン122を形成する段階は、同一のエッティング工程で同時に遂行することもできる。この場合、図3に従って絶縁膜111及び犠牲膜112を交互に反復的に形成する段階で、最下部の犠牲膜112aと残りの他の犠牲膜112とは互に異なるエッティング選択比を有する物質で形成される。即ち、犠牲膜112の中のエピタキシャル層121に接する最下部の犠牲膜112aと、垂直構造体130に接する残りの他の犠牲膜112とは、エッティング速度が互に異なる物質で形成される。一例として、最下部の犠牲膜112aを含む犠牲膜112は全てシリコン窒化物を含み、最下部の犠牲膜112aは残りの他の犠牲膜112より窒化物の比率が更に高いシリコン窒化物(N-rich SiN)を含む。それによって、犠牲膜112a、112を除去してリセス領域141を形成する段階で、最下部の犠牲膜112aが更に速い速度で除去されることに従って、露出したエピタキシャル層(図9の121参照)が共にエッティングされてリセスされた側壁122aを有するエピタキシャルパターン122が同時に形成される。エッティング工程は、一例として磷酸を含むエッティング溶液を利用することができる。この過程で、リセス領域141によって露出した保護膜124が共に除去され、結果的にリセス領域141を形成する工程、保護膜124を選択的に除去する工程、及びエピタキシャルパターン122を形成する工程は同一のエッティング工程で同時に遂行される。

20

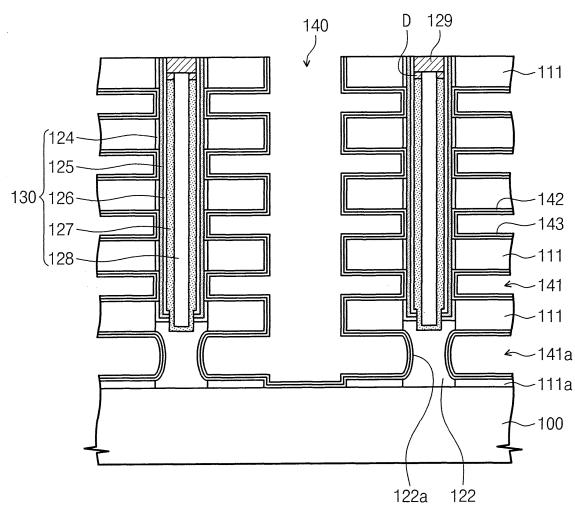

#### 【0055】

図11を参照すると、リセス領域141a、141を満たす第1及び第2ブロッキング絶縁膜142、143を順に形成する。第1及び第2ブロッキング絶縁膜142、143は、露出したリセス領域141a、141及びトレンチ140に沿ってコンフォーマルに蒸着される。一例として、第1ブロッキング絶縁膜142はシリコン酸化膜であり、第2ブロッキング絶縁膜143はアルミニウム酸化膜である。但し、これらの積層順序は多様に変更することができ、これに限定されない。第1及び第2ブロッキング絶縁膜142、143は原子層蒸着方法で形成される。一方、最下部のリセス領域141aにも、エピタキシャルパターン122のリセスされた側壁122aに沿って第1及び第2ブロッキング絶縁膜142、143がコンフォーマルに蒸着される。その結果、エピタキシャルパターン122に接する第1及び第2ブロッキング絶縁膜142、143は、内側に膨らむ形態を有する。

30

#### 【0056】

図12を参照すると、第2ブロッキング絶縁膜143上に電極膜144を形成する。電極膜144は、露出したリセス領域(図11の141参照)及びトレンチ(図11の140参照)に沿ってコンフォーマルに蒸着される。一例として、電極膜144は、リセス領域141を完全に満たすが、トレンチ140には完全に満たさない。電極膜144は、ドーピングされたポリシリコン膜、金属膜(例えば、タンゲステン)、又は金属窒化膜の中の少なくとも1つを含む。他の実施形態として、電極膜144は順に積層されたバリア金属膜及びバルク金属膜を含む。バリア金属膜は遷移金属及び/又は金属窒化物を含み、バルク金属膜はタンゲステンを含む。

40

#### 【0057】

50

図13を参照すると、リセス領域（図11の141a、141参照）の外部、即ちトレンチ（図11の140参照）に形成された電極膜（図12の144参照）が除去される。一例として、電極膜144は等方性エッチング工程で除去される。その結果、リセス領域141a、141内に局所的にゲート電極145a、145が各々形成される。一実施形態によると、電極膜144がバリア金属膜及びバルク金属膜を含む場合、トレンチ140に形成されたバリア金属膜及びバルク金属膜が除去されることによって、各ゲート電極145a、145は、各リセス領域141a、141内にバリア金属（図示せず）が形成される。従って、第1及び第2ブロッキング絶縁膜142、143及びゲート電極145を含む水平構造体150が形成される。最下部のリセス領域（図11の141a参照）内に形成された最下部の水平構造体150aは、エピタキシャルパターン122のリセスされた側壁122aに沿って形成されて、内側に膨らむ形態を有する。

10

#### 【0058】

続いて、トレンチ140によって露出した基板100に高濃度の不純物イオンが提供されて不純物領域が形成される。不純物領域は共通ソースラインCSLとして定義される。

#### 【0059】

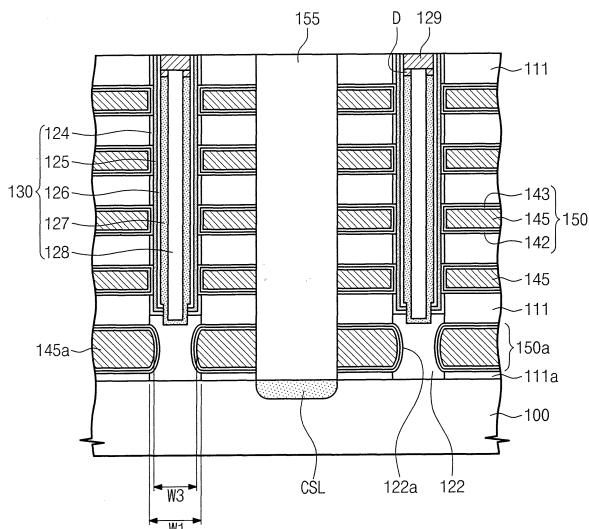

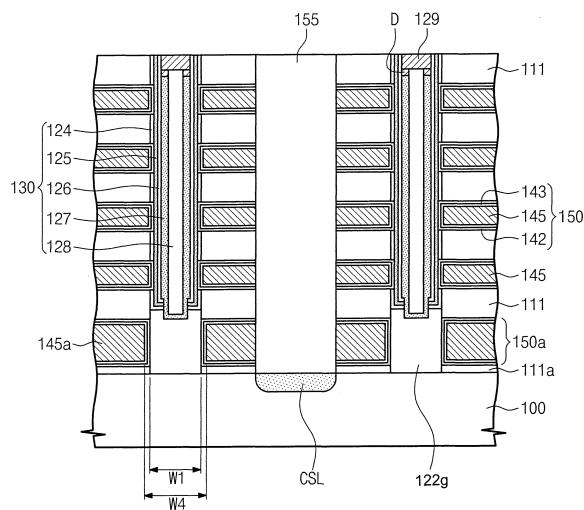

図14を参照すると、トレンチ（図13の140参照）を満たす分離絶縁膜155が更に形成される。分離絶縁膜155はトレンチ140に沿って第1方向に延長される。その後、図2に示すように、ビットラインBLが形成される。第2方向に整列された垂直構造体130は1つのビットラインBLに共通に連結される。

20

#### 【0060】

本実施形態による3次元半導体メモリ装置は、基板100及び垂直構造体130の間に介在して、これらを連結するエピタキシャルパターン122がリセスされた側壁122aを有する。エピタキシャルパターン122の最小幅W3は垂直構造体130の幅W1より小さい。それによって、エピタキシャルパターン122に接する最下部の水平構造体150aは、エピタキシャルパターン122のリセスされた側壁122aに沿って内側に膨らむ形態に形成される。その結果、最下部の水平構造体150aのゲート電極145aとエピタキシャルパターン122の中心との間の水平距離は、残りの他のゲート電極145の各々と垂直構造体130の中心との間の距離と同一であるか、或いは小さい。即ち、断面的な視点で、エピタキシャルパターン122の両側に各々配置されたゲート電極145aの部分の間の間隔W3は、垂直構造体130の幅W1と同一であるか、或いは小さく形成される。最下位のゲート電極145aはエピタキシャルパターン122が通る電極ホールを有する。最下位の水平構造体150aの第1及び第2ブロッキング絶縁膜142、143は、最下位のゲート電極145aの電極ホールの内側壁とエピタキシャルパターン122のリセスされた側壁122aとの間に配置される。最下位のゲート電極145aの距離W3は、最下位のゲート電極145内に定義された電極ホールの最小幅に該当する。これを一般的な技術による3次元半導体メモリ装置と比較すると、次の通りである。

30

#### 【0061】

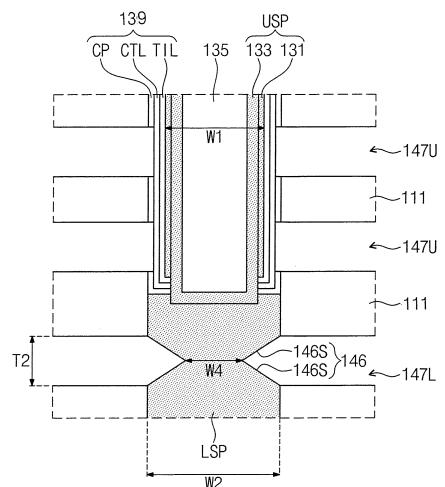

図15は、一般的な技術による3次元半導体メモリ装置を示す断面図である。

#### 【0062】

図15を参照すると、一般的な技術では、断面的な視点で、エピタキシャルパターン122gを間に置いたゲート電極145a間の間隔W4は垂直構造体130の幅W1より大きい。これはエピタキシャルパターン122gと保護膜124が互に異なる物質で形成されることによって、図9で説明した露出した保護膜124を除去して電荷格納膜125を露出させる段階で、エピタキシャルパターン122がエッチングされないことに起因する。それによって、最下部のゲート電極145aは、残りの他のゲート電極145より形成される空間が減って、最下部のゲート電極145aを蒸着する過程で不良が発生することがある。図14に示したように、本発明は、エピタキシャルパターン122がリセスされた側壁122aを有するように形成されることで、このような問題点を改善することができ、その結果、高信頼性を有する3次元半導体メモリ装置を提供することができる。

40

#### 【0063】

50

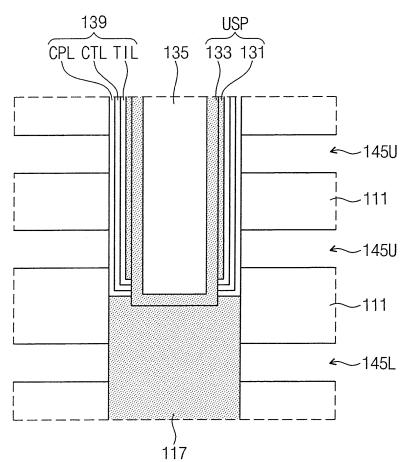

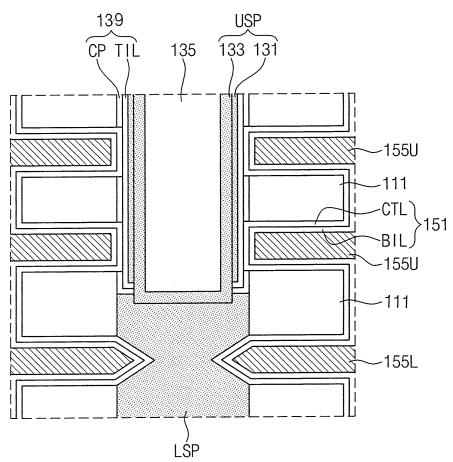

図16は、本発明の一実施形態による3次元半導体メモリ装置の他の例を示す断面図である。図1～図15に従って説明した実施形態と同一の構成要素は同一の参照符号を使用し、重複する内容を省略する。

#### 【0064】

図16を参照すると、図2で説明したように、第1及び第2プロッキング絶縁膜142、143、電荷格納膜125、及びトンネル絶縁膜126は、3次元半導体メモリ装置の情報格納要素として定義される。情報格納要素の中の一部は垂直構造体130に含まれ、残りの一部は水平構造体150に含まれる。本実施形態によると、情報格納要素の中のトンネル絶縁膜126は垂直構造体130に含まれ、電荷格納膜125及び第1及び第2プロッキング絶縁膜142、143は水平構造体150に含まれる。

10

#### 【0065】

このために、図6の段階で、貫通ホール内に保護膜124及びトンネル絶縁膜126を形成する。その後、図11の段階で、リセス領域内に電荷格納膜125及び第1及び第2プロッキング絶縁膜142、143を順に形成する。以降省略する製造方法は上述した実施形態と実質的に同一である。

#### 【0066】

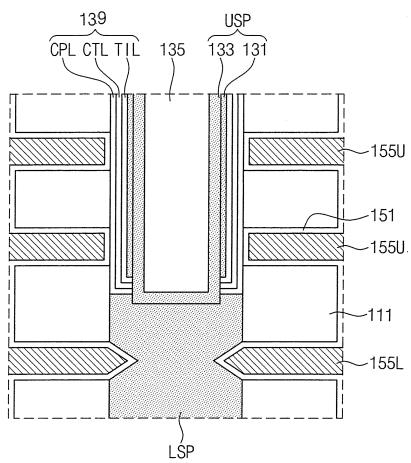

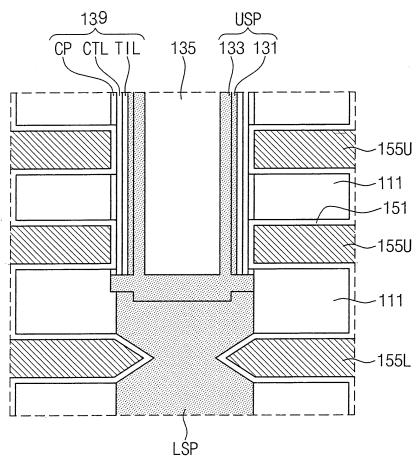

図17は、本発明の一実施形態による3次元半導体メモリ装置の更に他の例を示す断面図である。図1～図16に従って説明した実施形態と同一の構成要素は同一の参照符号を使用し、重複する内容を省略する。

20

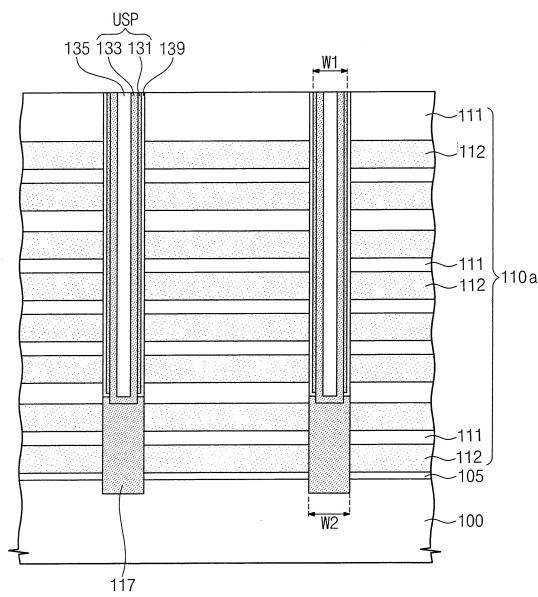

#### 【0067】

図17を参照すると、本実施形態において、エピタキシャルパターン123は、2つの層の水平構造体、即ち下から第1番目及び第2番目の層の水平構造体150aに接するように配置される。例えば、エピタキシャルパターン123は、基板100に近く配置され、隣接する2つの水平構造体に接触する。図1～図14で説明した実施形態と異なり、水平構造体150、150aは、実質的にそれぞれ同一の厚さを有して配置される。上述した実施形態のように、エピタキシャルパターン123はリセスされた側壁123aを有し、それによって、断面的な視点で、エピタキシャルパターン123と接する水平構造体150aのゲート電極145a間の間隔W5は、垂直構造体130の幅W1と同一であるか、或いは小さく配置される。この場合、下から第1番目及び第2番目の層の水平構造体150aが図1で説明した接地選択ラインGSLに該当し、以降省略する製造方法は上述した実施形態と実質的に同一である。

30

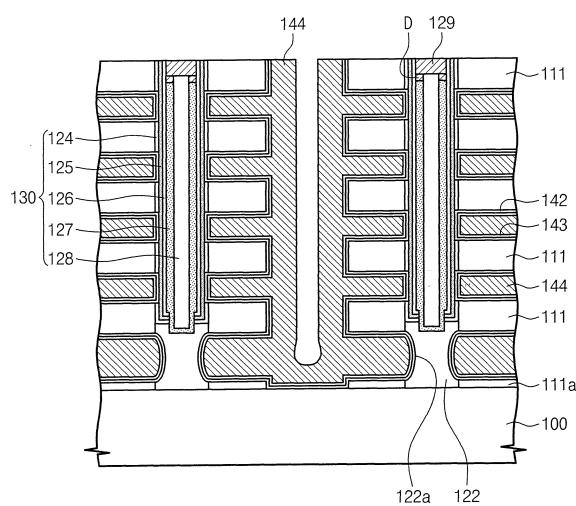

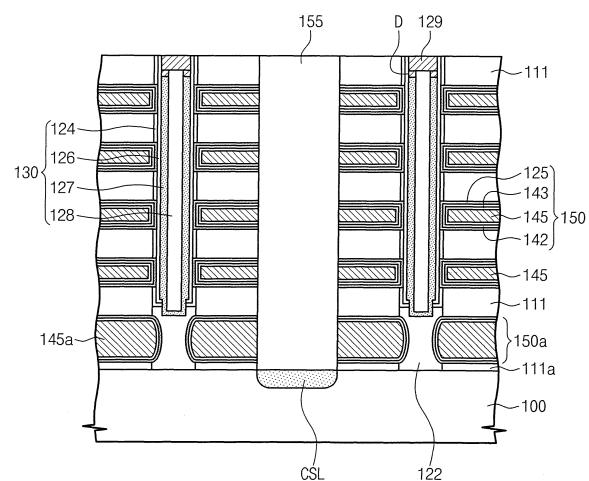

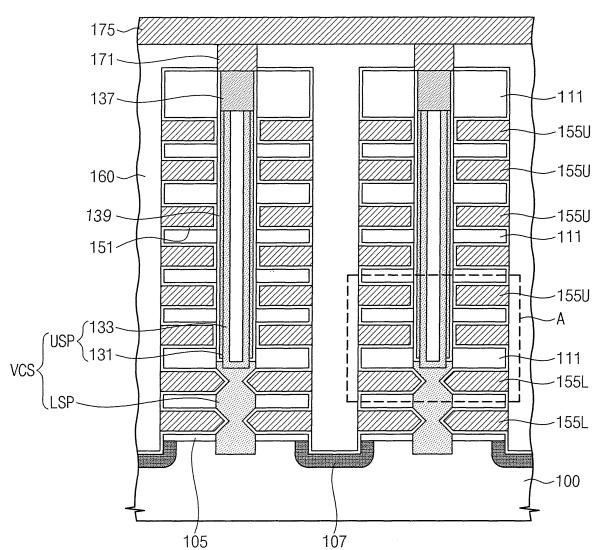

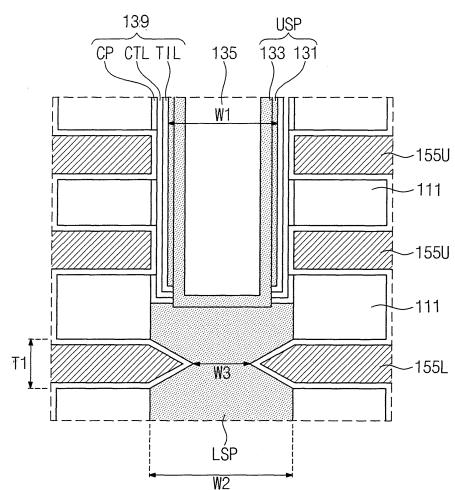

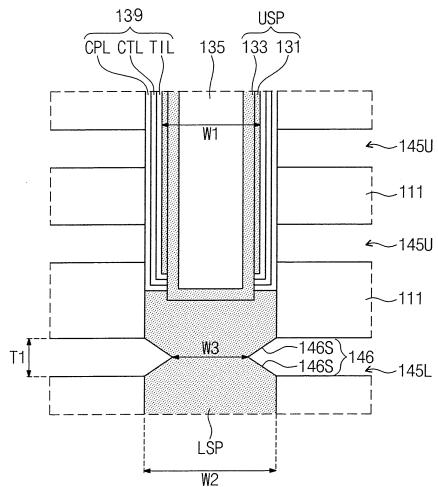

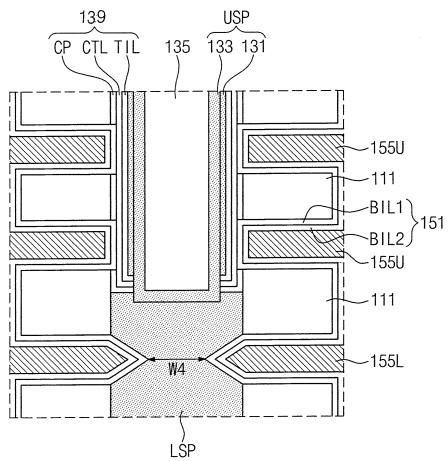

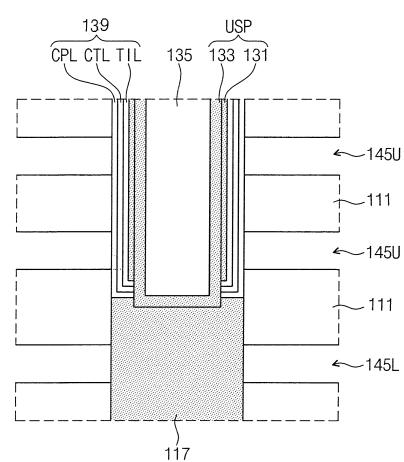

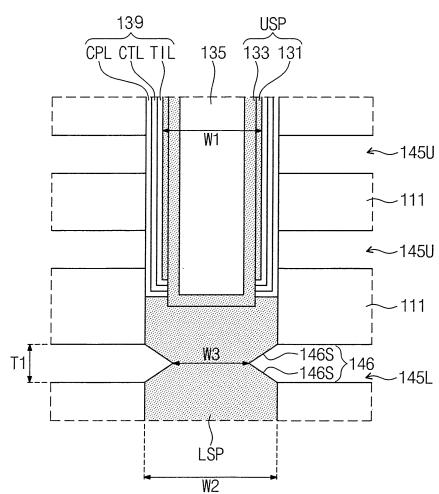

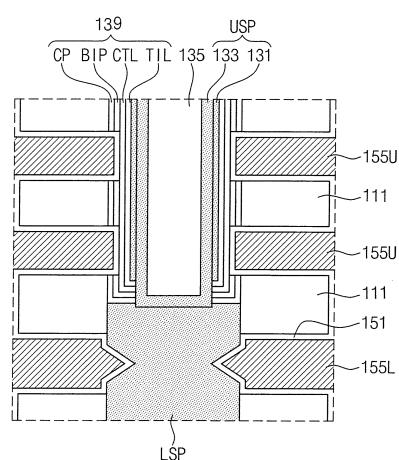

#### 【0068】

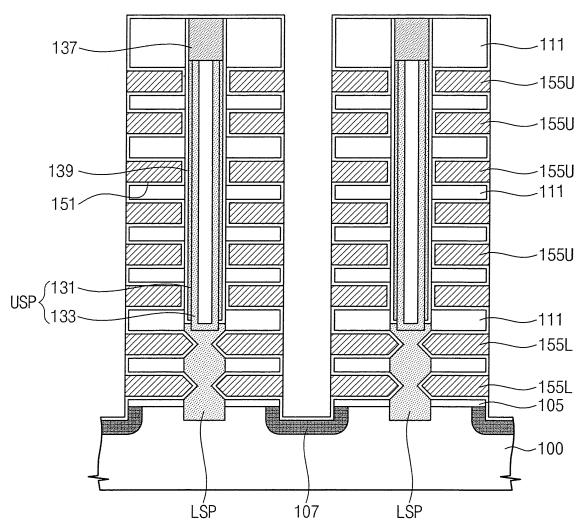

図18は、本発明の一実施形態による3次元半導体メモリ装置を示す断面図であり、図19は、図18のA部分を示す図面である。図20は、本発明の一実施形態による3次元半導体メモリ装置の下部半導体パターンを示す斜視図である。

#### 【0069】

図18を参照すると、基板100上に、絶縁膜111を介在して積層された下部及び上部ゲートパターン155L、155Uを含む積層構造体が配置される。

#### 【0070】

基板100は、半導体物質からなり、例えばシリコン基板、ゲルマニウム基板、又はシリコン-ゲルマニウム基板である。基板100は不純物がドーピングされた共通ソース領域である不純物領域107を含む。基板100と積層構造体との間に下部絶縁膜105が形成される。例えば、下部絶縁膜105は熱酸化工程を通じて形成されるシリコン酸化膜である。これと異なり、下部絶縁膜105は蒸着技術を利用して形成されたシリコン酸化膜であり得る。下部絶縁膜105はその上に形成された絶縁膜111より薄い厚さを有する。

40

#### 【0071】

積層構造体は、平面的な視点で、一方向に延長されたライン形態を有する。複数のチャンネル構造体VCSが積層構造体を貫通して基板100に電気的に連結される。積層構造体を貫通するチャンネル構造体VCSは平面的な視点で一方向に配列される。これと異な

50

り、チャンネル構造体VCSは、後述する図21に示したように、平面的な視点で一方向にジグザグ形態に配列されることもある。

#### 【0072】

一実施形態によると、積層構造体は、下部半導体パターンLSPと隣接する下部ゲートパターン155Lと、上部半導体パターンUSPと隣接する上部ゲートパターン155Uとを含む。一実施形態によると、下部ゲートパターン155Lは、図1を参照して説明した接地選択トランジスターGSTのゲート電極として利用される。即ち、3次元NANDフラッシュメモリにおいて、下部ゲートパターン155Lは、基板100に形成された不純物領域107（即ち、共通ソース領域）と下部半導体パターンLSPとの間の電気的な連結を制御する接地選択トランジスターGSTのゲート電極として使用される。そして、10 上部ゲートパターン155Uの中の一部は、図1を参照して説明したメモリセルトランジスターMCTのゲート電極として利用される。また、積層構造体の最上部に位置する上部ゲートパターン155Uは、図1を参照して説明したストリング選択トランジスターSS-Tのゲート電極として利用される。即ち、3次元NANDフラッシュメモリにおいて、積層構造体の最上部に位置する上部ゲートパターン155Uは、ビットライン175とチャンネル構造体VCSとの間の電気的な連結を制御するストリング選択トランジスターSS-Tのゲート電極として使用される。

#### 【0073】

一実施形態によると、下部ゲートパターン155Lの水平的な幅は上部ゲートパターン155Uの水平的な幅より大きい。下部ゲートパターン155Lの垂直的な厚さと上部ゲートパターン155Uの垂直的な厚さは実質的に同一である。これと異なり、下部ゲートパターン155Lの垂直的な厚さは、上部ゲートパターン155Uの垂直的な厚さより大きいこともある。20

#### 【0074】

一実施形態によると、積層構造体を貫通するチャンネル構造体VCSの各々は、積層構造体の上部部分を貫通して下部半導体パターンLSPに電気的に連結される上部半導体パターンUSPと、積層構造体の下部部分を貫通して基板100に電気的に連結される下部半導体パターンLSPとを含む。

#### 【0075】

一実施形態によると、上部半導体パターンUSPは、中が空いたパイプ形態（pipe-shaped）又はマカロニ形態（macaroni-shaped）である。この時、上部半導体パターンUSPの下端は閉じた状態（closed state）である。そして、上部半導体パターンUSPの内部は埋め込み絶縁パターン135によって満たされる。そして、上部半導体パターンUSPの底面は下部半導体パターンLSPの上部面より低いレベルに位置する。即ち、上部半導体パターンUSPは下部半導体パターンLSPに挿入された構造を有する。更に具体的に、下部半導体パターンLSPの上部面は上部半導体パターンUSPの底面と接触する第1部分及びこれと接触しない第2部分を含む。下部半導体パターンLSPの上部面の第1部分（即ち、上部半導体パターンUSPの底面は下部半導体パターンLSPの上部面の第2部分より低い。30

#### 【0076】

上部半導体パターンUSPは半導体物質からなる。例えば、上部半導体パターンUSPは、シリコンSi、ゲルマニウムGe、又はこれらの混合物を含み、不純物がドーピングされた半導体であるか、或いは不純物がドーピングされない状態の真性半導体（intrinsic semiconductor）である。また、上部半導体パターンUSPは、単結晶、非晶質（amorphous）、及び多結晶（polycrystalline）の中から選択された少なくともいずれか1つを含む結晶構造を有する。更に、上部半導体パターンUSPの上端に導電パッド137が配置される。導電パッド137は、不純物がドーピングされた不純物領域であるか、或いは導電物質からなる。

#### 【0077】

より詳細に、上部半導体パターンUSPは第1半導体パターン131及び第2半導体パ50

ターン 133 を含む。第1半導体パターン 131 は積層構造体の内側壁を覆う。第1半導体パターン 131 は、上端及び下端が開放された (open ed) パイプ形態又はマカロニ形態である。そして、第1半導体パターン 131 は、下部半導体パターン LSP と接触せずに、離隔される。第2半導体パターン 133 は下端が閉じたパイプ形態又はマカロニ形態である。このような形態の第2半導体パターン 133 の内部は埋め込み絶縁パターン 135 で満たされる。また、第2半導体パターン 133 は、第1半導体パターン 131 の内壁と下部半導体パターン LSP の上部面と接触する。即ち、第2半導体パターン 133 は、第1半導体パターン 131 と下部半導体パターン LSP とを電気的に連結する。

#### 【0078】

更に、第1及び第2半導体パターン 131、133 は、アンドープされた状態であるか、或いは基板 100 と同一の導電形を有する不純物でドーピングされる。第1半導体パターン 131 及び第2半導体パターン 133 は多結晶状態又は単結晶状態である。

#### 【0079】

下部半導体パターン LSP は、図 1 を参照して説明した接地選択トランジスター GST のチャンネル領域に利用される。下部半導体パターン LSP は基板 100 のような導電形の半導体物質からなる。一実施形態によると、下部半導体パターン LSP は、半導体物質からなる基板 100 をシードとして利用するエピタキシャル (epitaxial) 技術又はレーザー結晶化技術の中の 1 つを利用して形成されたエピタキシャルパターンである。この場合、下部半導体パターン LSP は、単結晶構造を有するか、或いは化学気相蒸着技術の結果物より増加したグレイン大きさを有する多結晶構造を有する。他の実施形態によると、下部半導体パターン LSP は、多結晶構造の半導体物質（例えば、多結晶シリコン）で形成される。

#### 【0080】

一実施形態によると、下部半導体パターン LSP の底面は、基板 100 の上部面より下に位置して基板 100 に挿入された構造を有する。下部半導体パターン LSP に隣接する絶縁膜 111 は、下部半導体パターン LSP の一側壁に直接接触する。下部半導体パターン LSP の側壁はリセス領域 146 を有する。リセス領域 146 は、下部ゲートパターン 155L に隣接し、基板 100 の上部面に対して傾いた傾斜面 146S によって定義される。

#### 【0081】

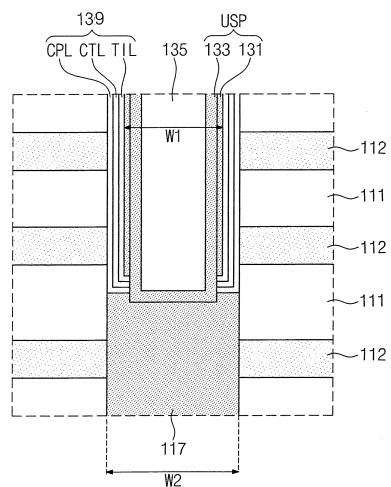

より詳細に、図 19 及び図 20 を参照すると、下部半導体パターン LSP の最大幅 W2 は、上部半導体パターン USP の最大幅 W1（即ち、上部幅）より大きい。そして、垂直的に隣接する絶縁膜 111 の間の距離 T1 は下部半導体パターン LSP の最大幅 W2 より小さい。ここで、下部半導体パターン LSP の最小幅 W3（即ち、リセス領域 146 の幅）は、上部半導体パターン USP の上部幅 W1 より小さい。下部半導体パターン LSP の最小幅 W3 は、垂直的に隣接する絶縁膜 111 の間の距離 T1 及び下部半導体パターン LSP の最大幅 W2 に従って決定される。従って、下部半導体パターン LSP の最小幅 W3 を確保するために、垂直的に隣接する絶縁膜 111 の間の距離 T1 を減少させるか、或いは下部半導体パターン LSP の最大幅 W2 を増加させる。一実施形態によると、下部半導体パターン LSP の最小幅 W3 は、下部半導体パターン LSP の最大幅と垂直的に隣接する絶縁膜 111 の間の距離との差 (W2 - T1) に該当する。

#### 【0082】

一実施形態によると、下部半導体パターン LSP のリセス領域 146 は、隣接する傾斜面 146S によって、鋭い楔形状を有する。一実施形態によると、下部半導体パターン LSP がシリコン物質で形成された場合、リセス領域 146 を定義する傾斜面 146S はシリコン物質の {111} 結晶面である。また、絶縁膜 111 に隣接する領域で下部半導体パターン LSP の横断面は円形を有し、リセス領域 146 が形成された下部半導体パターン LSP の横断面は互いに交差する <110> 方向と平行な辺の方形状を有する。

#### 【0083】

再び、図 18 を参照すると、積層構造体と上部半導体パターン USP との間に垂直絶縁

10

20

30

40

50

体 139 が介在する。垂直絶縁体 139 は上端及び下端が開放された (open ed) パイプ形態又はマカロニ形態である。一実施形態によると、垂直絶縁体 139 は下部半導体パターン LSP の上部面と接触する。

#### 【0084】

一実施形態によると、垂直絶縁体 139 はフラッシュメモリ装置のメモリ要素を含む。即ち、垂直絶縁体 139 はフラッシュメモリ装置の電荷格納膜を含む。例えば、電荷格納膜は、トラップ絶縁膜又は導電性ナノドット (conductive nano dots) を含む絶縁膜である。このような垂直絶縁体 139 に格納されるデータは、上部半導体パターン USP とゲートパターンとの間の電圧の差異によって、誘発されるファウラーノルドハイムトンネルリングを利用して変更される。これと異なり、垂直絶縁体 139 は他 10 の動作原理に基づいて情報を格納することが可能な薄膜（例えば、相変化メモリのための薄膜又は可変抵抗メモリのための薄膜）であることもある。

#### 【0085】

一実施形態によると、垂直絶縁体 139 は、順に積層された電荷格納膜 CTL 及びトンネル絶縁膜 TIL を含む。トンネル絶縁膜 TIL は、チャンネル構造体 VCS と直接接触し、上部ゲートパターン 155U とトンネル絶縁膜 TIL との間に電荷格納膜 CTL が介在する。他の実施形態として、垂直絶縁体 139 は、後述する図 39 に示すように、順に積層されたプロッキング絶縁膜 BIL、電荷格納膜 CTL、及びトンネル絶縁膜 TIL を含むことができる。トンネル絶縁膜 TIL はチャンネル構造体 VCS に直接接触し、トンネル絶縁膜 TIL とプロッキング絶縁膜 BIL との間に電荷格納膜 CTL が配置される。 20

#### 【0086】

電荷格納膜 CTL は、トラップ絶縁膜、又は導電性ナノドット (conductive nano dots) を含む絶縁膜を含む。更に具体的な例として、電荷格納膜 CTL は、シリコン窒化膜、シリコン酸化窒化膜、リッチシリコン窒化膜 (Si-rich nitride)、ナノクリスタルシリコン (nanocrystalline Si)、又は薄層化されたトラップ膜 (laminated trap layer) の中の少なくとも 1 つを含む。トンネル絶縁膜 TIL は、電荷格納膜 CTL より大きいバンドギャップを有する物質の中の 1 つである。例えば、トンネル絶縁膜 TIL はシリコン酸化膜である。プロッキング絶縁膜 BIL は、電荷格納膜 CTL より大きいエネルギー-band ギャップを有する物質の中の 1 つである。例えば、プロッキング絶縁膜 BIL はシリコン酸化膜である。 30

#### 【0087】

一方、垂直絶縁体 139 は、図 19 及び後述する図 39 に示すように、上部半導体パターン USP と絶縁膜 111 との間に介在するキャッピング膜パターン C P を含む。キャッピング膜パターン C P は、絶縁膜 111 に直接接触し、上部ゲートパターン 155U によって垂直的に分離される。他の実施形態として、後述する図 35 に示すように、キャッピング膜 CPL が上部半導体パターン USP と上部ゲートパターン 155U との間で垂直的に延長されることもある。キャッピング膜パターン C P は、電荷格納膜 CTL に対してエッチング選択性を有し、絶縁膜 111 と異なる絶縁物質で形成される。例えば、キャッピング膜パターン C P は、シリコン膜、シリコン酸化膜、ポリシリコン膜、シリコンカーバイド、及びシリコン窒化膜の中から選択される絶縁膜 111 と異なる物質である。更に他の例として、キャッピング膜パターン C P は、タンタル酸化膜 Ta<sub>2</sub>O<sub>5</sub>、チタニウム酸化膜 TiO<sub>2</sub>、ハフニウム酸化膜 HfO<sub>2</sub>、ジルコニウム酸化膜 ZrO<sub>2</sub> のような高誘電物質で形成され得る。 40

#### 【0088】

続いて、図 18 及び図 19 を参照すると、下部及び上部ゲートパターン 155L、155U の上部面及び下部面をコンフォーマルに覆う水平絶縁膜 151 が配置される。水平絶縁膜 151 の一部は上部ゲートパターン 155U と垂直絶縁体 139 との間に延長され、水平絶縁膜 151 の他の一部は下部ゲートパターン 155L と下部半導体パターン LSP との間に延長される。水平絶縁膜 151 は 1 つの薄膜又は複数の薄膜で構成される。一実 50

施形態によると、水平絶縁膜 151 は、図 19 に示したように、電荷トラップ形フラッシュメモリトランジスターのブロッキング絶縁膜を含む。他の実施形態として、水平絶縁膜 151 は、後述する図 38 に示すように、複数のブロッキング絶縁膜 BIL1、BIL2 を含むこともある。更に他の実施形態として、水平絶縁膜 151 は、後述する図 41 に示すように、電荷トラップ形フラッシュメモリトランジスターの電荷格納膜 CTL 及びブロッキング絶縁膜 BIL を含むこともある。

#### 【0089】

更に、積層構造体の間の空間に電極分離パターン 160 が満たされる。電極分離パターン 160 は、絶縁物質からなり、共通ソース領域である不純物領域 107 を覆う。また、積層構造体の上部に積層構造体を横切るビットライン 175 が配置される。ビットライン 175 は、コンタクトプラグ 171 を通じて上部半導体パターン USP の導電パッド 137 に接続される。10

#### 【0090】

以下、図 22～図 30 及び図 31～図 35 を参照して、本発明の他の実施形態による 3 次元半導体メモリ装置の製造方法を説明する。図 22～図 30 は、本発明の他の実施形態による 3 次元半導体メモリ装置の製造方法を示す断面図であり、図 31～図 35 は、本発明の他の実施形態による 3 次元半導体メモリ装置の製造方法を説明するための部分断面図である。

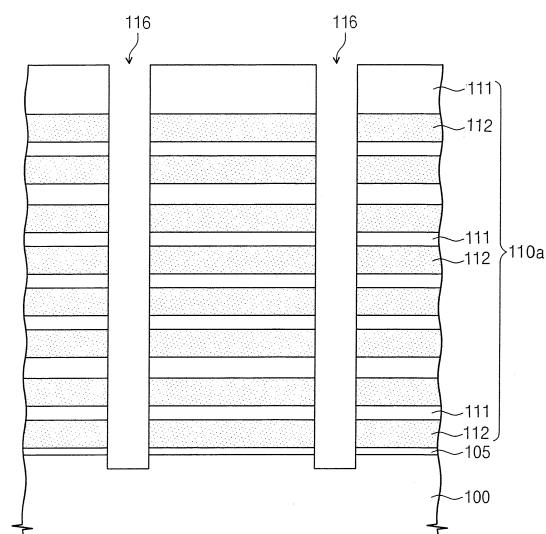

#### 【0091】

図 22 を参照すると、基板 100 上に犠牲膜 112 及び絶縁膜 111 を交互に反復的に積層して多層構造の薄膜構造体 110a を形成する。20

#### 【0092】

基板 100 は、半導体特性を有する物質、絶縁性物質、絶縁性物質によって覆われた半導体又は導電体の中の 1 つである。例えば、基板 100 は、シリコン基板、ゲルマニウム基板、又はシリコン・ゲルマニウム基板である。

#### 【0093】

犠牲膜 112 は、絶縁膜 111 に対してエッチング選択性を有してエッチングされる物質で形成される。一実施形態によると、犠牲膜 112 及び絶縁膜 111 は、ケミカル溶液を利用する湿式エッチング工程で高いエッチング選択比を有し、エッチングガスを利用する乾式エッチング工程で低いエッチング選択比を有する。30

#### 【0094】

一実施形態によると、複数の犠牲膜 112 は同一の厚さを有し、他の実施形態として、複数の犠牲膜 112 の中の最下層及び最上層の犠牲膜 112 は、それらの間に位置する犠牲膜 112 に比べて厚く形成される。また、絶縁膜 111 は同一の厚さを有するか、絶縁膜 111 の中の一部は厚さが異なることがある。

#### 【0095】

犠牲膜 112 及び絶縁膜 111 は、熱的化学気相蒸着 (Thermal CVD)、プラズマエンハンスト化学気相蒸着 (Plasma enhanced CVD)、物理的化学気相蒸着 (physical CVD)、又は原子層蒸着 (Atomic Layer Deposition: ALD) 技術を利用して蒸着される。40

#### 【0096】

一実施形態によると、犠牲膜 112 及び絶縁膜 111 は、絶縁物質で形成され、互いにエッチング選択性を有する。例えば、犠牲膜 112 は、シリコン膜、シリコン酸化膜、シリコンカーバイド、シリコン酸窒化物、及びシリコン窒化膜の中の少なくとも 1 つである。絶縁膜 111 は、シリコン膜、シリコン酸化膜、シリコンカーバイド膜、シリコン酸窒化物、及びシリコン窒化膜の中の少なくとも 1 つであり、犠牲膜と異なる物質である。例えば、犠牲膜 112 はシリコン窒化膜で形成され、絶縁膜 111 はシリコン酸化膜で形成される。一方、他の実施形態として、犠牲膜 112 は導電物質で形成され、絶縁膜 111 は絶縁物質からなることがある。

#### 【0097】

10

20

30

40

50

これに加えて、基板 100 と薄膜構造体 110a との間に下部絶縁膜 105 が形成される。例えば、下部絶縁膜 105 は熱酸化工程を通じて形成されるシリコン酸化膜である。これと異なり、下部絶縁膜 105 は蒸着技術を利用して形成されたシリコン酸化膜であり得る。下部絶縁膜 105 は、その上に形成される犠牲膜 112 及び絶縁膜 111 より薄い厚さを有する。

#### 【0098】

図 23 を参照すると、薄膜構造体 110a を貫通して基板 100 を露出させる開口部 116 を形成する。

#### 【0099】

この実施形態によると、開口部 116 はホール模様に形成される。即ち、開口部 116 の各々は、その深さがその幅より少なくとも 5 倍以上大きい模様に形成される。これに加えて、この実施形態によると、開口部 116 は、基板 100 の上部面（即ち、 $x-y$  平面）上に 2 次元的に形成される。即ち、開口部 116 の各々は、 $x$  及び  $y$  方向に沿って他の構成要素から離隔されて形成される孤立された領域である。他の実施形態として、図 21 に示したように、開口部 116 が  $y$  軸方向にジグザグ（zigzag）に配置されることもある。ここで、一方向に隣接する開口部 116 間の離隔距離は、開口部 116 の幅よりも小さいか、或いは同一である。

#### 【0100】

このような開口部 116 は、薄膜構造体 110a 上にマスクパターン（図示せず）を形成し、マスクパターン（図示せず）をエッチングマスクとして利用して異方性エッチングすることによって形成される。異方性エッチング工程で基板 100 の上部面まで過度エッチング（over-etch）され、これによって、開口部 116 に露出した基板 100 の上部面は所定の深さにリセスされる。また、異方性エッチング工程によって、開口部 116 の下部幅が開口部 116 の上部幅より小さいことがある。

#### 【0101】

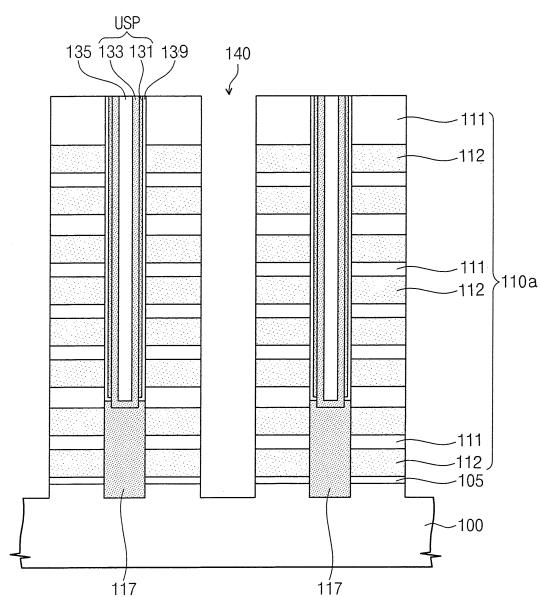

図 24 を参照すると、開口部 116 の下部領域を満たす下部半導体膜 117 を形成する。

#### 【0102】

下部半導体膜 117 は、薄膜構造体 110a の下部に位置する犠牲膜 112 及び絶縁膜 111 の一側壁と直接接触する。下部半導体膜 117 は少なくとも 1 つ以上の犠牲膜 112 の側壁を覆う。そして、下部半導体膜 117 の上部面は垂直的に隣接する犠牲膜 112 の間のレベルに位置する。

#### 【0103】

より詳細に、下部半導体膜 117 は、開口部 116 に露出した基板 100 をシード層（seed layer）として使用する選択的なエピタキシャル成長（SEG）工程を遂行して形成される。これによって、下部半導体膜 117 は、基板 100 のエッチングされた領域と開口部 116 の下部部分を満たすピラー（pillar）形態に形成される。このような場合、下部半導体膜 117 は、単結晶構造を有するか、或いは化学気相蒸着技術の結果物より増加したグレイン大きさを有する多結晶構造を有する。一方、下部半導体膜 117 の物質はシリコンであり得るが、これに限定されない。例えば、炭素ナノ構造物、有機半導体物質、及び化合物半導体が下部半導体膜 117 に使用される。他の実施形態として、下部半導体膜 117 は、多結晶構造の半導体物質（例えば、多結晶シリコン）で形成される。

#### 【0104】

一実施形態によると、下部半導体膜 117 は、 $<100>$  方向を有するシリコン単結晶基板 100 をシード（seed）として利用する選択的なエピタキシャル成長（selective Epitaxial Growth：SEG）方法を利用して形成される。この時、下部半導体膜 117 の上部面は $<100>$  方向を有する。

#### 【0105】

これに加えて、下部半導体膜 117 は基板 100 と同一の導電形を有する。下部半導体

10

20

30

40

50

膜 117 には、選択的なエピタキシャル成長工程の時にその場 (in-situ) で不純物がドーピングされる。これと異なり、下部半導体膜 117 を形成した後に、下部半導体膜 117 に不純物がイオン注入されることもある。

#### 【0106】

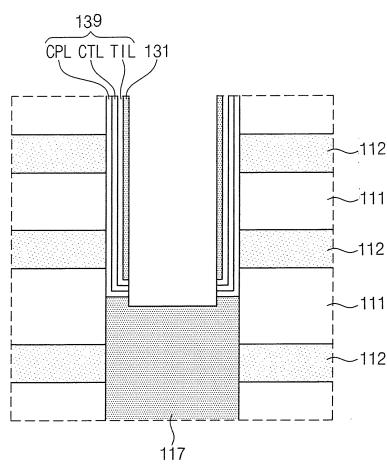

図 25 及び図 31 を参照すると、下部半導体膜 117 が形成された開口部 116 の内壁を覆い、下部半導体膜 117 の上部面を露出させる垂直絶縁体 139 及び第 1 半導体パターン 131 を形成する。

#### 【0107】

より詳細に説明すると、下部半導体膜 117 が形成された開口部 116 の内壁を覆う垂直絶縁膜及び第 1 半導体膜を順に形成する。垂直絶縁膜及び第 1 半導体膜は開口部 116 の一部分を満たす。垂直絶縁膜及び第 1 半導体膜の蒸着の厚さの合計は開口部 116 の幅の 1/2 より小さい。即ち、開口部 116 は垂直絶縁膜及び第 1 半導体膜によって完全に満たされない。更に、垂直絶縁膜は開口部 116 に露出した下部半導体膜 117 の上部面を覆う。垂直絶縁膜は、複数の薄膜で形成され、例えば、プラズマエンハンスド化学気相蒸着 (Plasma enhanced CVD)、物理的化学気相蒸着 (physical CVD)、又は原子層蒸着 (Atomic Layer Deposition: ALD) 技術を利用して蒸着される。

#### 【0108】

垂直絶縁膜は、フラッシュメモリ装置のメモリ要素として使用される電荷格納膜を含む。例えば、電荷格納膜はトラップ絶縁膜又は導電性ナノドット (conductive nano dots) を含む絶縁膜である。これと異なり、垂直絶縁膜は相変化メモリのための薄膜又は可変抵抗メモリのための薄膜を含むこともある。

#### 【0109】

一実施形態によると、図 31 に示すように、垂直絶縁膜 139 は、順に積層されたキャッピング膜 CPL、電荷格納膜 CTL、及びトンネル絶縁膜 TIL を含む。キャッピング膜 CPL は、開口部に露出した犠牲膜 112 及び絶縁膜 111 の側壁と下部半導体膜 117 の上部面とを覆う。キャッピング膜 CPL は、犠牲膜 112 及び電荷格納膜 CTL に対してエッチング選択性を有する物質で形成される。例えば、キャッピング膜 CPL は、タンタル酸化膜 Ta<sub>2</sub>O<sub>5</sub>、チタニウム酸化膜 TiO<sub>2</sub>、ハフニウム酸化膜 HfO<sub>2</sub>、及びジルコニア酸化膜 ZrO<sub>2</sub> 等のように高い誘電定数を有する高誘電膜で形成される。電荷格納膜 CTL は、トラップ絶縁膜、又は導電性ナノドット (conductive nano dots) を含む絶縁膜を含む。より具体的な例として、電荷格納膜 CTL は、シリコン窒化膜、シリコン酸化窒化膜、リッチシリコン窒化膜 (Si-rich nitride)、ナノクリスタルシリコン (nanocrystalline Si)、又は薄層化されたトラップ膜 (laminated trap layer) の中の少なくとも 1 つを含む。トンネル絶縁膜 TIL は、電荷格納膜 CTL より大きいバンドギャップを有する物質の中の 1 つである。例えば、トンネル絶縁膜 TIL はシリコン酸化膜である。

#### 【0110】

第 1 半導体膜は垂直絶縁膜上にコンフォーマルに形成される。一実施形態によると、第 1 半導体膜は、原子層蒸着 ALD 又は化学的気相蒸着 CVD 技術の中の 1 つを使用して形成される半導体物質（例えば、多結晶シリコン膜、単結晶シリコン膜、又は非晶質シリコン膜）である。

#### 【0111】

垂直絶縁膜及び第 1 半導体膜を順に形成した後、下部半導体膜 117 の上部面上の第 1 半導体膜及び垂直絶縁膜を異方性エッチングして下部半導体膜 117 の上部面を露出させる。これによって、開口部 116 の内壁に第 1 半導体パターン 131 及び垂直絶縁体 139 が形成される。即ち、垂直絶縁体 139 及び第 1 半導体パターン 131 は開放された両端を有する円筒模様に形成される。また、第 1 半導体膜及び垂直絶縁膜を異方性エッチングする間に、過度エッチング (over-etch) の結果として、第 1 半導体パターン 131 によって露出する下部半導体膜 117 の上部面がリセスされることもある。

10

20

30

40

50

**【 0 1 1 2 】**

一方、異方性エッチングする間に、第1半導体パターン131の下に位置する垂直絶縁膜の一部分はエッチングされないことがあり、この場合、垂直絶縁体139は、第1半導体パターン131の底面と下部半導体膜117の上部面との間に介在する底部を有する。

**【 0 1 1 3 】**

これに加えて、第1半導体膜及び垂直絶縁膜に対する異方性エッチングの結果として、薄膜構造体110aの上部面が露出する。これによって、垂直絶縁体139及び第1半導体パターン131は、開口部116内に局所的に形成される。即ち、垂直絶縁体139及び第1半導体パターン131は、平面上で2次元的に配列される。

**【 0 1 1 4 】**

一方、後述する図42に示す実施形態によると、垂直絶縁体139を形成した後、垂直絶縁体139の底部を除去する工程が追加的に遂行される。即ち、第1半導体パターン131と下部半導体膜117の上部面との間に介在する垂直絶縁体139の底部を等方性エッチングしてアンダーカット領域が形成される。アンダーカット領域の形成によって、図42に示すように、垂直絶縁体139の垂直的な長さが減少し、下部半導体パターンLSPの上部面と離隔される。その後、アンダーカット領域は、後続工程で形成される第2半導体パターン133で満たされる。

**【 0 1 1 5 】**

図26及び図32を参照すると、垂直絶縁体139及び第1半導体パターン131が形成された結果物上に、第2半導体パターン133及び埋め込み絶縁パターン135を順に形成する。

**【 0 1 1 6 】**

第2半導体パターン133及び埋め込み絶縁パターン135は、垂直絶縁体139及び第1半導体パターン131が形成された開口部116内に第2半導体膜及び埋め込み絶縁膜が順に形成され、薄膜構造体110aの上部面が露出するように平坦化して形成される。

**【 0 1 1 7 】**

第2半導体膜は、開口部116を完全に埋め込まない厚さに、開口部116内にコンフォーマルに形成される。第2半導体膜は下部半導体膜117と第1半導体パターン131とを連結する。第2半導体膜は、原子層蒸着ALD又は化学的気相蒸着CVD技術の中の1つを使用して形成される半導体物質（例えば、多結晶シリコン膜、単結晶シリコン膜、又は非晶質シリコン膜）である。

**【 0 1 1 8 】**

このように形成された第2半導体パターン133は、開口部116内にパイプ形態(pipe-shaped)、中空のシリンダー形態(hollow cylindrical shape)、又はカップ(cup)模様に形成される。一方、他の実施形態として、第2半導体パターン133が開口部116を満たすようにピラー(pillar)形態に形成されることもある。

**【 0 1 1 9 】**

埋め込み絶縁パターン135は、第2半導体パターン133が形成された開口部116を満たすように形成され、SOG技術を利用して形成される絶縁性物質及びシリコン酸化膜の中の1つである。

**【 0 1 2 0 】**

このように、第1及び第2半導体パターン131、133の形成によって、下部半導体膜117上に上部半導体パターンUSPが形成される。上部半導体パターンUSPは、垂直絶縁体139が形成された開口部116内に形成されることによって、上部半導体パターンUSPの最大幅W1（即ち、上部幅）は、下部半導体膜117の最大幅W2（即ち、上部幅）より小さい。

**【 0 1 2 1 】**

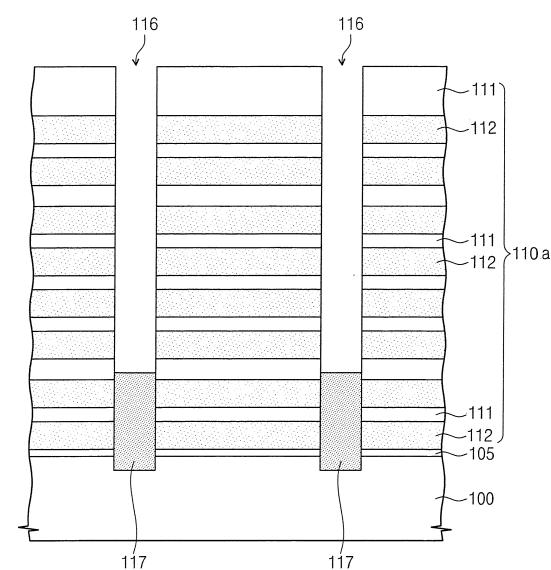

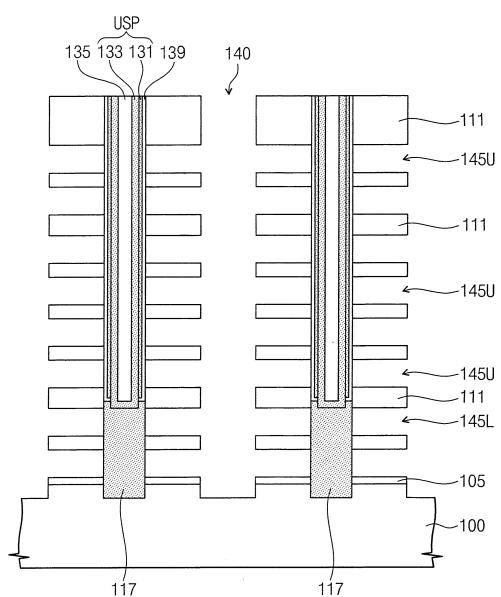

図27を参照すると、薄膜構造体110aをパターニングして隣接する開口部116の

10

20

30

40

50

間に基板 100 を露出させるトレンチ 140 を形成する。

【 0122 】

具体的に、トレンチ 140 を形成する工程は、薄膜構造体 110a 上にトレンチ 140 の平面積位置を定義するマスクパターン（図示せず）を形成する工程と、マスクパターンをエッティングマスクとして使用して薄膜構造体 110a を異方性エッティングする工程と、を含む。

【 0123 】

トレンチ 140 は、第 1 及び第 2 半導体パターン 131、133 から離隔されて、犠牲膜 112 及び絶縁膜 111 の側壁を露出させるように形成される。水平的な視点で、トレンチ 140 はライン形態又は長方形に形成され、垂直的な深さにおいて、トレンチ 140 は基板 100 の上部面を露出させるように形成される。トレンチ 140 を形成する間に、オーバーエッティング (over etch) によってトレンチ 140 に露出する基板 100 の上部面が所定の深さにリセスされる。また、トレンチ 140 は、異方性エッティング工程によって、基板 100 からの距離に従って他の幅を有し得る。

10

【 0124 】

トレンチ 140 の形成によって、薄膜構造体 110a は一方向に延長されたライン形態を有する。そして、1 つのライン形態の薄膜構造体 110a には、複数の上部半導体パターン U S P が貫通する。

【 0125 】

図 28 及び図 33 を参照すると、トレンチ 140 に露出した犠牲膜 112 を除去して、

20 隣接する絶縁膜 111 の間に下部及び上部ゲート領域 145L、145U を形成する。

【 0126 】

具体的に、下部及び上部ゲート領域 145L、145U は、絶縁膜 111、垂直絶縁体 139、下部半導体膜 117、及び基板 100 に対してエッティング選択性を有するエッティングレシピを使用して犠牲膜 112 を等方的にエッティングして形成される。ここで、犠牲膜 112 は等方性エッティング工程によって完全に除去される。例えば、犠牲膜 112 がシリコン窒化膜であり、絶縁膜 111 がシリコン酸化膜である場合、エッティング段階は、磷酸を含むエッティング液を使用して等方性エッティング工程が遂行される。

【 0127 】

このように形成された下部ゲート領域 145L は、トレンチ 140 から絶縁膜 111 の間に水平的に延長され、下部半導体膜 117 の側壁の一部分を露出させる。上部ゲート領域 145U は、トレンチ 140 から絶縁膜 111 の間に水平的に延長され、垂直絶縁体 139 の側壁の一部分を露出させる。即ち、下部ゲート領域 145L は、垂直的に隣接する絶縁膜 111 と下部半導体膜 117 の一側壁によって定義される。上部ゲート領域 145U は、垂直的に隣接する絶縁膜 111 と垂直絶縁体 139 の一側壁によって定義される。これに加えて、図 33 に示す実施形態によると、キャッピング膜 C P L は、上部ゲート領域 145U を形成するための等方性エッティング工程の時、エッティング停止膜として利用され、等方性エッティング工程に利用されるエッティング液によって電荷格納膜が損傷することを防止する。即ち、上部ゲート領域 145U は、垂直絶縁体 139 のキャッピング膜 C P L を露出させる。

30

40

【 0128 】

一実施形態によると、下部及び上部ゲート領域 145L、145U の垂直的な高さは下部半導体膜 117 の最大幅より小さい。下部及び上部ゲート領域 145L、145U の垂直的な高さは犠牲膜 112 の厚さと実質的に同一である。そして、下部及び上部ゲート領域 145L、145U の垂直的な高さは実質的に互いに同一である。これと異なり、下部ゲート領域 145L の垂直的な高さが上部ゲート領域 145U の垂直的な高さより大きいこともある。

【 0129 】

図 29 及び図 34 を参照すると、下部ゲート領域 145L に露出した下部半導体膜 117 の側壁をリセスしてリセス領域 146 を有する下部半導体パターン L S P を形成する。

50

## 【0130】

一実施形態によると、下部半導体膜117にリセス領域146を形成する工程は、下部ゲート領域145Lに露出した下部半導体膜117の側壁を選択的にエッティングする工程を含む。ここで、エッティング工程には、半導体物質の結晶方向に沿ってエッティング速度が他の特性を有するエッティングレシピを利用する。これによって、リセス領域146は、基板100の上部面に対して傾いた傾斜面146Sによって定義される。そして、リセス領域146は、隣接する傾斜面146Sによって、鋭い楔形状を有する。一実施形態によると、リセス領域146を定義する傾斜面146Sは、シリコン物質の{111}結晶面である。また、リセス領域146が形成された下部半導体パターンLSPの横断面は、図20に示したように、<110>方向が交差する方形状を有する。

10

## 【0131】

より詳細に、一実施形態によると、リセス領域146は、ハロゲン含有反応ガスを含むエッチャントを使用して気相エッティング(Gas Phase Etching)又は化学的乾式エッティング(chemical dry etch)することによって形成される。ここで、ハロゲン含有反応ガスは、HCl、Cl<sub>2</sub>、NF<sub>3</sub>、ClF<sub>3</sub>、及びF<sub>2</sub>ガスの中のいずれか1つである。他の実施形態として、有機アルカリエッチャント(水酸化テトラメチルアンモニウム: TMAH)又は水酸化アンモニウムNH<sub>4</sub>OHのようなエッティング液を利用する湿式異方性エッティング工程を遂行して、下部半導体パターンLSPにリセス領域146を形成することもある。

## 【0132】

20

具体的に、シリコンからなる下部半導体膜117を選択的にエッティングする時、シリコンの結晶面及び結晶方向に沿ってエッティング速度が異なって示される。一実施形態によると、ハロゲン含有反応ガスを使用して下部ゲート領域145Lに露出した下部半導体膜117の側壁をエッティングする時、<111>方向でエッティング速度が<110>方向でのエッティング速度より速い。このような場合、{111}結晶面でエッティング工程が停止されて、下部半導体パターンLSPの{111}結晶面が露出する。即ち、リセス領域146は、{111}結晶面によって定義され、{111}結晶面を有する2つの傾斜面146Sによって、鋭い楔形状を有する。

## 【0133】

他の実施形態として、水酸化アンモニウムNH<sub>4</sub>OHを利用してシリコンで形成された下部半導体膜117を等方性エッティングする時、下部半導体膜117は、{111}結晶面でエッティング速度が最も遅く、{100}面でエッティング速度が最も速い特性を有する。これによって、水酸化アンモニウムNH<sub>4</sub>OHを利用して等方性エッティング工程を進行する場合、エッティング速度が最も遅い{111}結晶面がリセス領域146の側面を定義する。そして、リセス領域146は、{111}結晶面を有する2つの側面によって、鋭い楔形状を有する。

30

## 【0134】

このようにエッティング工程によって形成されたリセス領域146の表面に、欠陥(defect)が存在することがある。このために、リセス領域146を形成した後、O<sub>3</sub>及びHFを利用するクリーニング工程を遂行してリセス領域146の表面欠陥を除去する。

40

## 【0135】

リセス領域146を有する下部半導体パターンLSPの形成によって、下部半導体パターンLSPの最小幅W3は、上部半導体パターンUSPの上部幅W1より減少する。一実施形態によると、リセス領域146の深さ(即ち、側面の深さ)は、隣接する絶縁膜111の間の距離T1及び下部半導体パターンLSPの最大幅W2によって決定される。より詳細に、リセス領域146の深さは、大略下部ゲート領域145Lの高さT1の半分に該当する。即ち、下部半導体パターンLSPの最小幅W3は、下部半導体パターンLSPの最大幅W2と下部ゲート領域145Lの高さT1との差異に該当する。

## 【0136】

続いて、図30及び図35を参照すると、下部及び上部ゲート領域145L、145U

50

の内壁を覆う水平絶縁膜 151 及び下部及び上部ゲート領域 145L、145U の残りの空間を満たす下部及び上部ゲートパターン 155L、155U を形成する。

#### 【0137】

水平絶縁膜 151 及び下部及び上部ゲートパターン 155L、155U を形成する工程は、下部及び上部ゲート領域 145L、145U を順に覆う水平絶縁膜 151 及び導電膜を形成した後、トレンチ 140 内で導電膜を除去して下部及び上部ゲート領域 145L、145U 内に下部及び上部ゲートパターン 155L、155U を局所的に形成する工程を含む。

#### 【0138】

一実施形態によると、上部ゲート領域 145U で、水平絶縁膜 151 は垂直絶縁体 139 に直接接触する。一実施形態によると、図 35 に示したように、水平絶縁膜 151 は垂直絶縁体 139 のキャッピング膜 CPL に直接接触する。下部ゲート領域 145L で、水平絶縁膜 151 は下部半導体パターン LSP に直接接触する。具体的に、下部ゲート領域 145L で、水平絶縁膜 151 は下部半導体パターン LSP のリセス領域 146 をコンフォーマルに覆う。水平絶縁膜 151 は、垂直絶縁膜の場合と同様に、1 つの薄膜又は複数の薄膜で構成される。一実施形態によると、水平絶縁膜 151 は電荷トラップ形フラッシュメモリトランジスターのブロッキング絶縁膜 BIL を含む。ブロッキング絶縁膜 BIL は、トンネル絶縁膜 TIL より小さく、電荷格納膜 CTL より大きいバンドギャップを有する物質の中の 1 つである。例えば、ブロッキング絶縁膜 BIL はアルミニウム酸化膜及びハフニウム酸化膜等のような高誘電膜の中の 1 つである。

#### 【0139】

一実施形態によると、導電膜は、下部及び上部ゲート領域 145L、145U を満たしながら、トレンチ 140 の内壁をコンフォーマルに覆うように形成され、この場合、下部及び上部ゲートパターン 155L、155U を形成する工程は、トレンチ 140 内の導電膜を等方性エッチング方法で除去する工程を含む。他の実施形態として、導電膜はトレンチ 140 を満たすように形成され、この場合、下部及び上部ゲートパターン 155L、155U は、トレンチ 140 内で導電膜を異方性エッチングして形成される。一実施形態によると、上部ゲート領域 145U 内に上部ゲートパターン 155U が形成され、下部ゲート領域 145L に下部ゲートパターン 155L が形成される。ここで、下部ゲートパターン 155L は下部半導体パターン LSP のリセス領域 146 内に満たされたため、下部ゲートパターン 155L は下部半導体パターン LSP 方向に鋭い側壁を有する。即ち、下部ゲートパターン 155L は傾斜面 146S と各々平行な側壁を有する。これによって、下部ゲートパターン 155L の水平幅は上部ゲートパターンの水平幅より大きくなる。一実施形態によると、導電膜を形成する工程は、バリア金属膜及び金属膜を順に蒸着する工程を含む。バリア金属膜は、例えば TiN、TaN、又は WN のような金属窒化膜からなる。そして、金属膜は、例えば W、Al、Ti、Ta、Co、又は Cu のような金属物質からなる。

#### 【0140】

続いて、図 30 に示すように、下部及び上部ゲートパターン 155L、155U を形成した後、基板 100 に不純物領域 107 が形成される。不純物領域 107 は、イオン注入工程を通じて形成され、トレンチ 140 を通じて露出した基板 100 内に形成される。不純物領域 107 は下部半導体パターン LSP と異なる導電形を有する。そして、不純物領域 107 は基板 100 と PN - 接合を構成する。これと異なり、下部半導体パターン LSP に接する基板 100 の領域は、下部半導体パターン LSP と同一の導電形を有することができる。フラッシュメモリ装置のための一実施形態によると、不純物領域 107 の各々は互いに連結されて等電位状態にある。他の実施形態として、不純物領域 107 の各々は互に異なる電位を有するように電気的に分離される。更に他の実施形態として、不純物領域 107 は、それぞれ異なる複数の不純物領域 107 を含む独立的な複数のソースグループを構成し、ソースグループの各々がそれぞれ異なる電位を有するように電気的に分離される。

10

20

30

40

50

**【0141】**

続いて、図18に示すように、不純物領域107上にトレント140を満たす電極分離パターン160を形成する。電極分離パターン160は、シリコン酸化膜、シリコン窒化膜、又はシリコン酸化窒化膜の中の少なくとも1つで形成される。

**【0142】**

これに加えて、第1及び第2半導体パターン131、133に接続される導電パッド137が形成される。導電パッド137は、第1及び第2半導体パターン131、133の上部領域をリセスした後、リセスされた領域内に導電物質を満たして形成される。また、導電パッド137は、その下に位置する第1及び第2半導体パターン131、133と異なる導電形の不純物をドーピングして形成される。これによって、導電パッド137はその下部領域とダイオードを構成する。10

**【0143】**

続いて、図18に示すように、導電パッド137に接続されるコンタクトプラグ171及びコンタクトプラグ171を連結するビットライン175を形成する。ビットライン175は、コンタクトプラグ171を通じて第1及び第2半導体パターン131、133に電気的に連絡され、下部及び上部ゲートパターン155L、155U又はトレント140を横切るように形成される。

**【0144】**

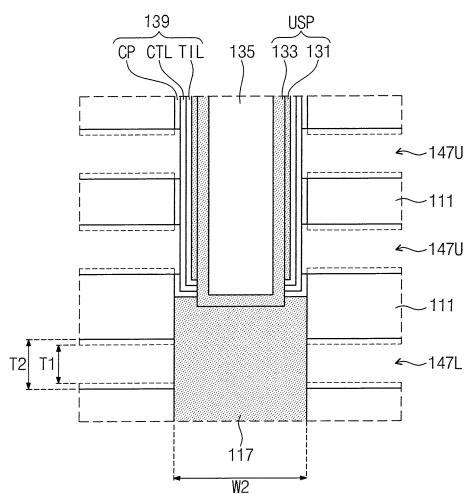

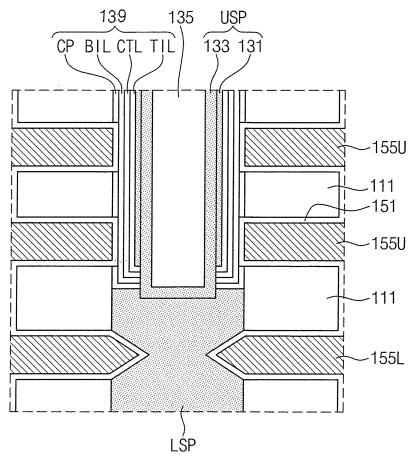

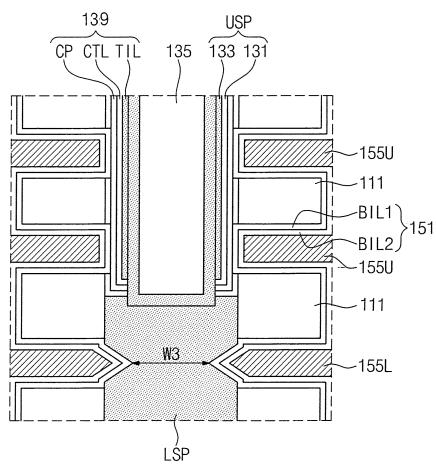

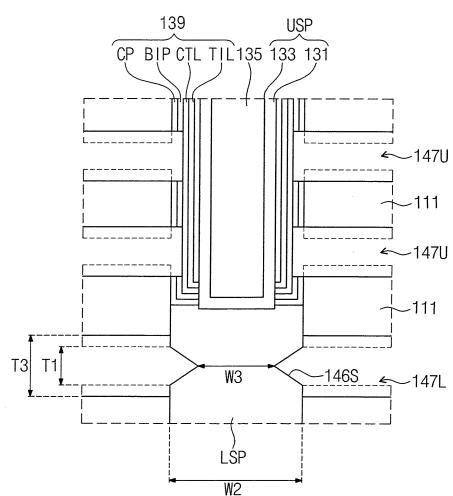

図36～図38は、本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図であり、図39～図42は、他の実施形態による3次元半導体メモリ装置の変形形態を示す部分断面図である。20

**【0145】**

この実施形態によると、図34を参照して説明したように、隣接する絶縁膜111の間に下部及び上部ゲート領域145L、145Uを形成した後、下部及び上部ゲート領域145L、145Uの水平幅及び高さを増加させる。

**【0146】**

より詳細には、図36を参照すると、下部及び上部ゲート領域145L、145Uに露出したキャッピング膜CPLと絶縁膜111の一部分を等方性エッチングして、拡張された(enlarged)下部及び上部ゲート領域147L、147U及びキャッピング膜パターンCPLを形成する。拡張された下部及び上部ゲート領域147L、147Uの垂直的な高さT2は、図34に示した下部及び上部ゲート領域145L、145Uの垂直的な高さT1より大きくなる。ここで、キャッピング膜パターンCPLを形成する前後の下部及び上部ゲート領域147L、147Uの垂直的な高さの差異(T2-T1)はキャッピング膜CPLの厚さの約2倍程度である。30

**【0147】**

一実施形態によると、垂直絶縁体139がキャッピング膜CPL、電荷格納膜CTL、及びトンネル絶縁膜TILを含む場合、拡張された下部及び上部ゲート領域147L、147Uを形成する工程は、キャッピング膜CPLの一部分をエッチングして電荷格納膜CTLの一部分を露出させる工程を含む。これによって、拡張された上部ゲート領域147Uを形成する時、電荷格納膜CTLと絶縁膜111との間にキャッピング膜パターンCPLが形成される。40

**【0148】**

他の実施形態として、垂直絶縁体139が図39に示したように、キャッピング膜CPL、プロッキング絶縁膜BIL、電荷格納膜CTL、及びトンネル絶縁膜TILを含む場合、拡張された下部及び上部ゲート領域147L、147Uを形成する工程は、キャッピング膜CPLの一部分をエッチングしてプロッキング絶縁膜BILの一部分を露出させる工程を含む。そして、拡張された上部ゲート領域147Uを形成する時、プロッキング絶縁膜BILと絶縁膜111との間にキャッピング膜パターンCPLが形成される。更に他の実施形態として、垂直絶縁体139がキャッピング膜CPL、プロッキング絶縁膜BIL、電荷格納膜CTL、及びトンネル絶縁膜TILを含む場合、拡張された下部及び上部ゲ50

ート領域 147L、147U を形成する工程は、図 40 に示したように、キャッピング膜 CPL 及びブロッキング絶縁膜 BIL の一部分をエッチングして電荷格納膜 CTL の一部分を露出させる工程を含む。これによって、電荷格納膜 CTL と絶縁膜 111との間にキャッピング膜パターン CP 及びブロッキング絶縁膜パターン BIP が形成される。

#### 【0149】

続いて、図 37 を参照すると、拡張された下部及び上部ゲート領域 147L、147U を形成した後、拡張された下部ゲート領域 147L に露出した下部半導体膜 117 を選択的にエッチングしてリセス領域 146 を形成する。リセス領域 146 の形成によって、下部半導体パターン LSP の最小幅 W4 は上部半導体パターン USP の上部幅 W1 より減少する。10 下部半導体パターン LSP のリセス領域 146 は、図 18 を参照して説明したように、半導体物質の結晶方向に沿ってエッチング速度が異なる特性を有するエッチングレシピを利用して形成される。これによって、リセス領域 146 は基板 100 の上部面に対して傾いた傾斜面 146S によって定義される。そして、リセス領域 146 は、隣接する傾斜面 146S によって、鋭い楔形状を有する。一実施形態によると、リセス領域 146 を定義する傾斜面 146S は、シリコン物質の {111} 結晶面である。また、リセス領域 146 が形成された下部半導体パターン LSP の横断面は、<110> 方向が交差する方形状を有する。

#### 【0150】

この実施形態によると、拡張された下部ゲート領域 147L の垂直的な高さ T2 が増加することによって、下部半導体パターン LSP のリセス領域 146 の深さが増加する。20 即ち、図 37 に示した下部半導体パターン LSP の最小幅 W4 は、図 18 に示した下部半導体パターン LSP の最小幅 W3 より小さい。

#### 【0151】

リセス領域 146 を有する下部半導体パターン LSP を形成した後、図 18 を参照して説明したように、水平絶縁膜 151 と下部及び上部ゲートパターン 155L、155U が形成される。水平絶縁膜 151 を形成する工程は、後述する図 46 に示すように、拡張された下部及び上部ゲート領域 147L、147U 内に、順に第 1 ブロッキング絶縁膜 BIL1 及び第 2 ブロッキング絶縁膜 BIL2 をコンフォーマルに蒸着する工程を含む。第 1 及び第 2 ブロッキング絶縁膜 BIL1、BIL2 は互に異なる物質で形成される。これに加えて、第 1 及び第 2 ブロッキング絶縁膜 BIL1、BIL2 の中の 1 つは、トンネル絶縁膜 TIL より小さく電荷格納膜 CTL より大きいバンドギャップを有する物質の中の 1 つである。30 一実施形態によると、第 1 ブロッキング絶縁膜 BIL1 はアルミニウム酸化膜及びハフニウム酸化膜等のような高誘電膜の中の 1 つであり、第 2 ブロッキング絶縁膜 BIL2 は第 1 ブロッキング絶縁膜 BIL1 より小さい誘電定数を有する物質である。他の実施形態として、第 2 ブロッキング絶縁膜 BIL2 は高誘電膜の中の 1 つであり、第 1 ブロッキング絶縁膜 BIL1 は、第 2 ブロッキング絶縁膜 BIL2 より小さい誘電定数を有する物質である。

#### 【0152】

図 18 ~ 図 42 に示した実施形態によると、選択トランジスターのチャンネルとして利用される下部半導体パターンの最小幅がセルトランジスターのチャンネルとして利用される上部半導体パターンの最大幅より小さい。これによって、下部半導体パターンに隣接する下部ゲートパターン間のマージンを確保することができる。40

#### 【0153】

更に、下部半導体パターンの幅を上部半導体パターンの幅より減少させるために、下部半導体パターンの側壁の一部分をエッチングする工程が遂行される。この時、シリコンの結晶面及び結晶方向に従うエッチング速度の差異を利用するエッチングレシピが利用される。従って、下部半導体パターンの幅を減少させる時、下部半導体パターンの幅に対するモニターリング無しでエッチング工程を自動的に制御することができる。言い換えると、シリコンからなる下部半導体パターンをエッチングする時、特定の結晶面 (crys ta

1 plane) が露出されると、自動的にエッチングが停止される。50

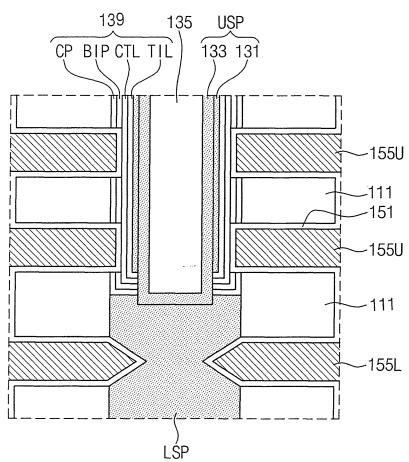

**【0154】**

以下、図22～図30及び図43～図49を参照して、本発明の他の実施形態による3次元半導体メモリ装置の製造方法を説明する。

**【0155】**

図43～図46は、本発明の他の実施形態による3次元半導体メモリ装置の他の例の製造方法を説明するための部分断面図である。

**【0156】**

この実施形態によると、図27に示したように、薄膜構造体110aをパターニングして基板100を露出させるトレンチ140を形成した後に、図28及び図43に示すように、トレンチ140に露出した犠牲膜112を除去して、隣接する絶縁膜111の間に下部及び上部ゲート領域145L、145Uを形成する。

10

**【0157】**

具体的に、下部及び上部ゲート領域145L、145Uは、絶縁膜111、垂直絶縁体139、下部半導体膜117、及び基板100に対してエッチング選択性を有するエッチングレシピを使用して犠牲膜112を等方的にエッチングして形成される。ここで、犠牲膜112は等方性エッチング工程によって完全に除去される。例えば、犠牲膜112がシリコン窒化膜であり、絶縁膜111がシリコン酸化膜である場合、エッチング段階は、磷酸を含むエッチング液を使用して等方性エッチング工程が遂行される。

**【0158】**

このように形成された下部ゲート領域145Lは、トレンチ140から絶縁膜111の間に水平的に延長され、下部半導体膜117の側壁の一部分を露出させる。上部ゲート領域145Uは、トレンチ140から絶縁膜111の間に水平的に延長され、垂直絶縁体139の側壁の一部分を露出させる。即ち、下部ゲート領域145Lは、垂直的に隣接する絶縁膜111と下部半導体膜117の一側壁によって定義される。上部ゲート領域145Uは、垂直的に隣接する絶縁膜111と垂直絶縁体139の一側壁によって定義される。これに加えて、図43に示した実施形態によると、キャッピング膜CPLは、上部ゲート領域145Uを形成するための等方性エッチング工程の時、エッチング停止膜として利用され、等方性エッチング工程に利用されるエッチング液によって電荷格納膜が損傷することを防止する。即ち、上部ゲート領域145Uは垂直絶縁体139のキャッピング膜CPLを露出させる。

20

30

**【0159】**

一実施形態によると、図43に示したように、下部及び上部ゲート領域145L、145Uの垂直的な高さは下部半導体膜117の最大幅より小さい。下部及び上部ゲート領域145L、145Uの垂直的な高さは犠牲膜112の厚さと実質的に同一である。そして、下部及び上部ゲート領域145L、145Uの垂直的な高さは実質的に互いに同一である。これと異なり、下部ゲート領域145Lの垂直的な高さが上部ゲート領域145Uの垂直的な高さより大きいこともある。

**【0160】**

図29及び図44を参照すると、下部ゲート領域145Lに露出した下部半導体膜117の側壁をリセスしてリセス領域146を有する下部半導体パターンLSPを形成する。

40

**【0161】**

一実施形態によると、下部半導体膜117にリセス領域146を形成する工程は、下部ゲート領域145Lに露出した下部半導体膜117の側壁を選択的にエッチングする工程を含む。ここで、エッチング工程には、半導体物質の結晶方向に沿ってエッチング速度が他の特性を有するエッチングレシピを利用する。これによって、リセス領域146は、基板100の上部面に対して傾いた傾斜面146Sによって定義される。そして、リセス領域146は、隣接する傾斜面146Sによって、鋭い楔形状を有する。一実施形態によると、リセス領域146を定義する傾斜面146Sは、シリコン物質の{111}結晶面である。また、リセス領域146が形成された下部半導体パターンLSPの横断面は、図20に示したように、<110>方向が交差する方形状を有する。

50

## 【0162】

より詳細に、一実施形態によると、リセス領域146は、ハロゲン含有反応ガスを含むエッチャントを使用して気相エッチング(Gas Phase Etching)又は化学的乾式エッチング(chemical dry etch)することによって形成される。ここで、ハロゲン含有反応ガスは、HCl、Cl<sub>2</sub>、NF<sub>3</sub>、ClF<sub>3</sub>、及びF<sub>2</sub>ガスの中のいずれか1つである。他の実施形態として、有機アルカリエッチャント(水酸化テトラメチルアンモニウム: TMAH)又は水酸化アンモニウムNH<sub>4</sub>OHのようなエッチング液を利用する湿式異方性エッチング工程を遂行して、下部半導体パターンLSPにリセス領域146を形成することもある。

## 【0163】

10

具体的に、シリコンからなる下部半導体パターンLSPを選択的にエッチングする時、シリコンの結晶面及び結晶方向に沿ってエッチング速度が異なって示される。一実施形態によると、ハロゲン含有反応ガスを使用して下部ゲート領域145Lに露出した下部半導体パターンLSPの側壁をエッチングする時、<111>方向でエッチング速度が<110>方向でのエッチング速度より速い。このような場合、{111}結晶面でエッチング工程が停止されて、下部半導体パターンLSPの{111}結晶面が露出する。即ち、リセス領域146は、{111}結晶面によって定義され、{111}結晶面を有する2つの傾斜面146Sによって、鋭い楔形状を有する。

## 【0164】

20

他の実施形態として、水酸化アンモニウムNH<sub>4</sub>OHを利用してシリコン基板100を等方性エッチングする時、シリコン基板100は、{111}結晶面でエッチング速度が最も遅く、{100}面でエッチング速度が最も速い特性を有する。これによって、水酸化アンモニウムNH<sub>4</sub>OHを利用して等方性エッチング工程を進行する場合、エッチング速度が最も遅い{111}結晶面がリセス領域146の側面を定義する。そして、リセス領域146は、{111}結晶面を有する2つの側面によって、鋭い楔形状を有する。

## 【0165】

このようにエッチング工程によって形成されたリセス領域146の表面に、欠陥(defect)が存在することがある。このために、リセス領域146を形成した後、O<sub>3</sub>及びHFを利用するクリーニング工程を遂行してリセス領域146の表面欠陥を除去する。

## 【0166】

30

リセス領域146を有する下部半導体パターンLSPを形成することによって、下部半導体パターンLSPの最小幅は、上部半導体パターンUSPの上部幅及び下部幅より減少する。一実施形態によると、基板100の上部面に対して水平な方向で、リセス領域146の深さは、下部ゲート領域145Lの垂直的な高さ及び下部半導体パターンLSPの最大幅によって決定される。より詳細に、リセス領域146の深さは、大略下部ゲート領域145Lの高さT1の半分に該当する。即ち、下部半導体パターンLSPの最小幅W3は、下部半導体パターンLSPの最大幅と下部ゲート領域145Lの高さの差異に該当する。

## 【0167】

40

続いて、図45を参照すると、リセス領域146を有する下部半導体パターンLSPを形成した後、下部及び上部ゲート領域145L、145Uの垂直的な高さを増加させる工程が遂行される。即ち、下部及び上部ゲート領域145L、145Uに露出した絶縁膜111の一部分を等方性エッチングして、拡張された(enlarged)下部及び上部ゲート領域147L、147Uを形成する。更に、垂直絶縁体139がキャッピング膜CPL、電荷格納膜CTL、及びトンネル絶縁膜TILを含む場合、拡張された下部及び上部ゲート領域147L、147Uを形成する工程は、キャッピング膜CPLの一部分をエッチングして電荷格納膜CTLの一部分を露出させる工程を含む。これによって、拡張された上部ゲート領域147Uを形成する時、電荷格納膜CTLと絶縁膜111との間にキャッピング膜パターンCPLが形成される。

## 【0168】

50

より詳細に、拡張された下部及び上部ゲート領域 147L、147U の垂直的な高さ T2 は、図 44 に示した下部及び上部ゲート領域 145L、145U の垂直的な高さ T1 より大きくなる。ここで、下部及び上部ゲート領域 145L、145U の垂直的な高さと拡張された下部及び上部ゲート領域 147L、147U の垂直的な高さの差異 (T2 - T1) は、キャッピング膜 CPL の厚さの約 2 倍程度である。更に、この実施形態によると、拡張された下部ゲート領域 147L は、基板 100 の上部面に対して垂直になる下部半導体パターン LSP の側壁の一部分を露出させる。

#### 【0169】

一方、他の実施形態として、拡張された下部及び上部ゲート領域 145L、145U を形成した後に、下部半導体パターン LSP にリセス領域 146 を形成する場合、下部半導体パターン LSP の最小幅 W3 は、拡張された下部ゲート領域 147L の垂直的な高さに従って決定されるため、下部半導体パターン LSP の最小幅が図 18 に示した最小幅 W3 より減少する。しかし、この実施形態によると、下部半導体パターン LSP にリセス領域 146 を形成した後に、拡張された下部及び上部ゲート領域 147L、147U を形成するため、下部半導体パターン LSP の最小幅 W3 を確保しながら、下部及び上部ゲート領域 147L、147U の垂直的な高さを増加させ得る。即ち、下部半導体パターン LSP の最小幅 W3 と、拡張された下部及び上部ゲート領域 147L、147U の垂直的な高さ T2 を独立的に制御することができる。言い換えると、下部半導体パターン LSP の最小幅 W3 を確保しながら、図 1 を参照して説明した選択トランジスター GST、SST 及びメモリセルトランジスター MCT のチャンネル長さを増加させ得る。

10

20

#### 【0170】

続いて、図 30 及び図 46 を参照すると、拡張された下部及び上部ゲート領域 147L、147U の内壁を覆う水平絶縁膜 151 及び拡張された下部及び上部ゲート領域 147L、147U の残りの空間を満たす下部及び上部ゲートパターン 155L、155U を形成する。

#### 【0171】

水平絶縁膜 151 及び下部及び上部ゲートパターン 155L、155U を形成する工程は、拡張された下部及び上部ゲート領域 147L、147U を順に覆う水平絶縁膜 151 及び導電膜を形成した後、拡張された下部及び上部ゲート領域 147L、147U の外部の導電膜を除去して、拡張された下部及び上部ゲート領域 147L、147U 内に下部及び上部ゲートパターン 155L、155U を局所的に形成する工程を含む。

30

#### 【0172】

水平絶縁膜 151 は、拡張された上部ゲート領域 147U で垂直絶縁体 139 と直接接触し、拡張された下部ゲート領域 147L で下部半導体パターン LSP と直接接触する。そして、拡張された下部ゲート領域 147L で、水平絶縁膜 151 は下部半導体パターン LSP のリセス領域 146 をコンフォーマルに覆う。

#### 【0173】

水平絶縁膜 151 は、垂直絶縁膜の場合と同様に、1 つの薄膜又は複数の薄膜で構成される。一実施形態によると、水平絶縁膜 151 は、順に積層された第 1 ブロッキング絶縁膜 BIL1 及び第 2 ブロッキング絶縁膜 BIL2 を含む。第 1 及び第 2 ブロッキング絶縁膜 BIL1、BIL2 の中の 1 つは、トンネル絶縁膜 TIL より小さく電荷格納膜 CTL より大きいバンドギャップを有する物質の中の 1 つである。例えば、一実施形態によると、第 1 ブロッキング絶縁膜 BIL1 はアルミニウム酸化膜及びハフニウム酸化膜等のような高誘電膜の中の 1 つであり、第 2 ブロッキング絶縁膜 BIL2 は第 1 ブロッキング絶縁膜 BIL1 より小さい誘電定数を有する物質である。他の実施形態として、第 2 ブロッキング絶縁膜 BIL2 は高誘電膜の中の 1 つであり、第 1 ブロッキング絶縁膜 BIL1 は第 2 ブロッキング絶縁膜 BIL2 より小さい誘電定数を有する物質である。

40

#### 【0174】

一実施形態によると、導電膜は、拡張された下部及び上部ゲート領域 147L、147U を満たしながら、トレチ 140 の内壁をコンフォーマルに覆うように形成され、この

50

場合、下部及び上部ゲートパターン 155L、155Uを形成する工程は、トレンチ 140 内で導電膜を等方性エッチング方法で除去する工程を含む。他の実施形態として、導電膜はトレンチ 140 を満たすように形成され、この場合、下部及び上部ゲートパターン 155L、155U は、トレンチ 140 内で導電膜を異方性エッチングして形成される。一実施形態によると、上部ゲート領域 145U 内に上部ゲートパターンが形成され、下部ゲート領域 145L に下部ゲートパターン 155L が形成される。ここで、下部ゲートパターン 155L は下部半導体パターン LSP のリセス領域 146 内に満たされるため、下部ゲートパターン 155L は下部半導体パターン LSP の方向に鋭い側壁を有する。即ち、下部ゲートパターン 155L は傾斜面 146S と平行な側壁を有する。これによって、下部ゲートパターン 155L の水平幅は上部ゲートパターンの水平幅より大きくなる。一実施形態によると、導電膜を形成する工程は、バリア金属膜及び金属膜を順に蒸着する工程を含む。バリア金属膜は、例えば TiN、TaN、又はWN のような金属窒化膜からなる。そして、金属膜は、例えばW、Al、Ti、Ta、Co、又はCu のような金属物質からなる。

#### 【0175】

続いて、図 30 を参照して説明したように、下部及び上部ゲートパターン 155L、155U を形成した後、基板 100 に不純物領域 107 が形成される。続いて、図 18 に示したように、不純物領域 107 上にトレンチ 140 を満たす電極分離パターン 160 が形成される。

#### 【0176】

以下、図 47～図 49 を参照して、本発明の他の実施形態による 3 次元半導体装置の更に他の例の製造方法について説明する。

#### 【0177】

この実施形態によると、図 47 に示したように、垂直絶縁体 139 は、キャッピング膜 CPL、ブロッキング絶縁膜 BIL、電荷格納膜 CTL、及びトンネル絶縁膜 TIL を含む。これによって、図 43 を参照して説明した下部及び上部ゲート領域 145L、145U を形成する時、上部ゲート領域 145U はキャッピング膜 CPL の一部分を露出させる。

#### 【0178】

続いて、図 48 を参照すると、下部及び上部ゲート領域 145L、145U に露出した絶縁膜 111 の一部分を等方性エッチングして、拡張された (enlarged) 下部及び上部ゲート領域 147L、147U を形成する。この実施形態によると、拡張された下部及び上部ゲート領域を形成する工程は、キャッピング膜 CPL 及びブロッキング絶縁膜 BIL の一部分をエッチングして電荷格納膜 CTL の一部分を露出させる工程を含む。これによって、電荷格納膜 CTL と絶縁膜 111 との間にキャッピング膜パターン CP 及びブロッキング絶縁膜パターン BIP が形成される。キャッピング膜 CPL 及びブロッキング絶縁膜 BIL を順にエッチングする時、垂直的に隣接する絶縁膜 111 の垂直的な厚さが減少する。ここで、拡張された下部及び上部ゲート領域 147L、147U の垂直的な高さ T3 は、図 44 に示した下部及び上部ゲート領域 147L、147U の垂直的な高さ T2 より大きくなる。

#### 【0179】

続いて、図 49 に示したように、拡張された下部及び上部ゲート領域 147L、147U 内に水平絶縁膜 151 及び下部及び上部ゲートパターン 155L、155U が形成される。この実施形態によると、水平絶縁膜 151 は電荷格納膜 CTL と接触し、キャッピング膜パターン CP 及びブロッキング絶縁膜パターン BIP は、上部ゲートパターン 155U によって垂直的に分離される。

#### 【0180】

図 43～図 49 に示した実施形態によると、下部半導体パターンの幅を上部半導体パターンの幅より減少させるために、下部半導体パターンの側壁の一部分をエッチングする工程が遂行される。この時、シリコンの結晶面及び結晶方向に従うエッチング速度の差異を

10

20

30

40

50

を利用するエッティングレシピが利用される。従って、下部半導体パターンの幅を減少させる時、下部半導体パターンの幅に対するモニターリング無しでエッティング工程を自動的に制御することができる。言い換えると、シリコンからなる下部半導体パターンをエッティングする時、特定の結晶面 (c r y s t a l p l a n e) が露出されると、自動的にエッティングが停止される。

#### 【0181】

これに加えて、本発明の実施形態によると、下部半導体パターンの最小幅と、下部及び上部ゲートパターンのチャンネル長さを独立的に制御することができる。

#### 【0182】

上述した実施形態で開示した半導体記憶素子は、多様な形態の半導体パッケージ (semiconductor package) で具現される。例えば、本発明の実施形態による半導体記憶素子は、P o P (P a c k a g e o n P a c k a g e)、B a l l g r i d a r r a y s (B G A s)、C h i p s c a l e p a c k a g e s (C S P s)、P l a s t i c L e a d e d C h i p C a r r i e r (P L C C)、P l a s t i c D u a l I n - L i n e P a c k a g e (P D I P)、D i e i n W a f f l e P a c k、D i e i n W a f e r F o r m、C h i p O n B o a r d (C O B)、C e r a m i c D u a l I n - L i n e P a c k a g e (C E R D I P)、P l a s t i c M e t r i c Q u a d F l a t P a c k (M Q F P)、T h i n Q u a d F l a t p a c k (T Q F P)、S m a l l O u t l i n e (S O I C)、S h r i n k S m a l l O u t l i n e P a c k a g e (S S O P)、T h i n S m a l l O u t l i n e (T S O P)、T h i n Q u a d F l a t p a c k (T Q F P)、S y s t e m I n P a c k a g e (S I P)、M u l t i C h i p P a c k a g e (M C P)、W a f e r - l e v e l F a b r i c a t e d P a c k a g e (W F P)、W a f e r - L e v e l P r o c e s s e d S t a c k P a c k a g e (W S P) 等の方式でパッケージングされる。10

#### 【0183】

本発明の実施形態による半導体記憶素子が実装されたパッケージは、半導体記憶素子を制御するコントローラ及び／又は論理素子等を更に含むこともある。

#### 【0184】

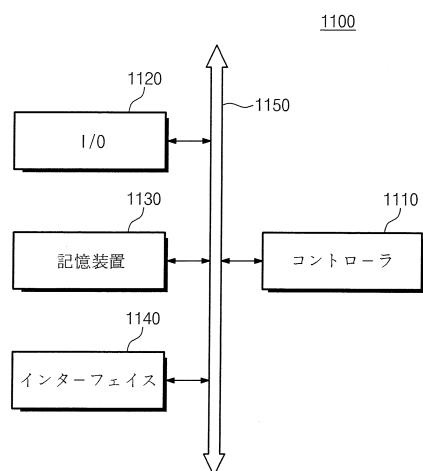

図 50 は、本発明の一実施形態による半導体記憶素子を含む電子システムの一例を示すプロック図である。30

#### 【0185】

図 50 を参照すると、本発明の一実施形態による電子システム 1100 は、コントローラ 1110、入出力装置 (I / O) 1120、記憶装置 1130、インターフェイス 1140、及びバス (bus) 1150 を含む。コントローラ 1110、入出力装置 1120、記憶装置 1130 a、及び／又はインターフェイス 1140 は、バス 1150 を通じて互いに結合される。バス 1150 はデータが移動する通路 (path) に該当する。

#### 【0186】

コントローラ 1110 は、マイクロプロセッサー、デジタル信号プロセッサー、マイクロコントローラ、及びこれらと同様な機能を遂行できる論理素子の中の少なくとも 1 つを含む。入出力装置 1120 は、キーパッド、キーボード、及びディスプレー装置等を含む。記憶装置 1130 はデータ及び／又は命令語等を格納する。記憶装置 1130 は上述した実施形態に開示した半導体記憶素子の中の少なくとも 1 つを含む。また、記憶装置 1130 は他の形態の半導体記憶素子（例えば、不揮発性記憶素子及び／又はS R A M 素子等）を更に含むことができる。インターフェイス 1140 は、通信ネットワークにデータを伝送するか、或いは通信ネットワークからデータを受信する機能を遂行する。インターフェイス 1140 は有線又は無線形態である。例えば、インターフェイス 1140 はアンテナ又は有無線トランシーバー等を含む。図示しないが、電子システム 1100 は、コントローラ 1110 の動作を向上させるための動作記憶素子として、高速のD R A M 素子及び／又はS R A M 素子等を更に含むことがある。4050

## 【0187】

電子システム1100は、個人携帯用情報端末機（PDA：personal digital assistant）、ポータブルコンピューター、ウェブタブレット、無線電話機、モバイルフォン、デジタルミュージックプレーヤー、メモリカード、又は情報を無線環境で送信及び／又は受信できる全ての電子製品に適用される。

## 【0188】

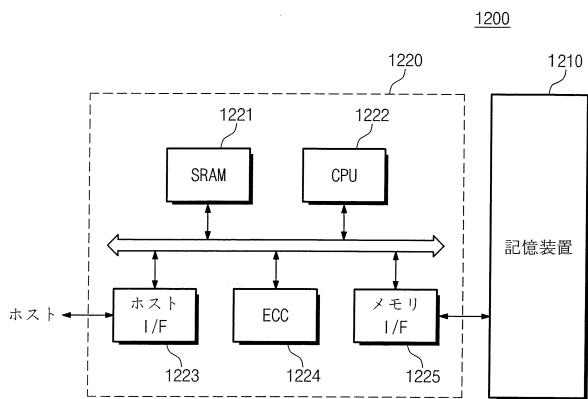

図51は、本発明の一実施形態による半導体記憶素子を含むメモリカードの一例を示すブロック図である。

## 【0189】

図51を参照すると、本実施形態によるメモリカード1200は記憶装置1210を含む。記憶装置1210は、上述した実施形態に開示した半導体記憶素子の中の少なくとも1つを含む。また、記憶装置1210は、他の形態の半導体記憶素子（例えば、不揮発性記憶素子及び／又はSRAM素子等）を更に含むことができる。メモリカード1200は、ホストと記憶装置1210との間のデータ交換を制御するメモリコントローラ1220を含む。

10

## 【0190】

メモリコントローラ1220は、メモリカードの全般的な動作を制御するプロセシングユニット（CPU）1222を含む。また、メモリコントローラ1220は、プロセシングユニット1222の動作メモリとして使用されるSRAM1221を含む。これに加えて、メモリコントローラ1220は、ホストインターフェイス1223、メモリインターフェイス1225を更に含む。ホストインターフェイス1223は、メモリカード1200とホストとの間のデータ交換プロトコルを具備する。メモリインターフェイス1225は、メモリコントローラ1220と記憶装置1210とを接続させる。更に、メモリコントローラ1220は、エラー訂正プロック（ECC）1224を更に含む。エラー訂正プロック1224は、記憶装置1210から読出されたデータのエラーを検出及び訂正する。図示しないが、メモリカード1200は、ホストとのインターフェイシングのためのコードデータを格納するROM装置を更に含むこともある。メモリカード1200は携帯用データ格納カードとして使用される。これと異なり、メモリカード1200は、コンピューターシステムのハードディスクを代替する半導体ディスク装置（SSD：Solid State Disk）としても具現される。

20

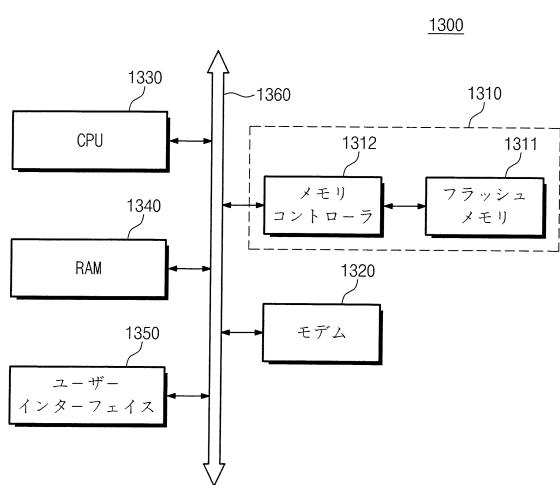

## 【0191】

図52は、本発明の一実施形態による3次元半導体メモリ装置を装着する情報処理システムの一例を示す概略ブロック図である。

## 【0192】

図52を参照すると、モバイル機器やデスクトップコンピューターのような情報処理システム1300にフラッシュメモリ装置1310が装着される。フラッシュメモリ装置1310は、上述した本発明の実施形態による3次元半導体メモリ装置を含む。本実施形態による情報処理システム1300は、フラッシュメモリ装置1310と、各々システムバス1360に電気的に連結されたモジュール1320、中央処理装置（CPU）1330、RAM1340、及びユーザーインターフェイス1350を含む。フラッシュメモリ装置1310は、上述したメモリシステム又はフラッシュメモリシステムと実質的に同様に構成される。フラッシュメモリ装置1310には、中央処理装置1330によって処理されたデータ又は外部から入力されたデータが格納される。ここで、上述したフラッシュメモリ装置1310は半導体ディスク装置SSDで構成され得、この場合、情報処理システム1300は大容量のデータをフラッシュメモリ装置1310に安定的に格納することができる。そして、信頼性の増大に伴って、フラッシュメモリ装置1310は、エラー訂正に所要される資源を節減することができるため、高速のデータ交換機能を情報処理システム1300に提供する。図示しないが、本実施形態による情報処理システム1300には、応用チップセット、カメライメージプロセッサー（CIS）、入出力装置等が更に提供され得ることはこの分野の通常的な知識を習得した者にとって明確である。

30

40

50

## 【0193】

以上、図面を参照しながら本発明の実施形態について詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

## 【符号の説明】

## 【0194】

|               |                |    |

|---------------|----------------|----|

| 100           | 基板             |    |

| 105           | 下部絶縁膜          |    |

| 107           | 不純物領域（共通ソース領域） |    |

| 110           | モールド構造体        | 10 |

| 110 a         | 薄膜構造体          |    |

| 111、111 a     | 絶縁膜            |    |

| 112、112 a     | 犠牲膜            |    |

| 115           | 電極構造体          |    |

| 116           | 開口部            |    |

| 117           | 下部半導体膜         |    |

| 120           | 貫通ホール          |    |

| 121           | エピタキシャル層       |    |

| 122、122 g、123 | エピタキシャルパターン    |    |

| 122 a、123 a   | 側壁             | 20 |

| 124           | 保護膜            |    |

| 125、CTL       | 電荷格納膜          |    |

| 126、TIL       | トンネル絶縁膜        |    |

| 127           | 半導体柱           |    |

| 128           | 埋め込み膜          |    |

| 129           | 導電パターン         |    |

| 130           | 垂直構造体          |    |

| 131           | 第1半導体パターン      |    |

| 133           | 第2半導体パターン      |    |

| 135           | 埋め込み絶縁パターン     | 30 |

| 137           | 導電パッド          |    |

| 139           | 垂直絶縁体          |    |

| 140           | レンチ            |    |

| 141、141 a、146 | リセス領域          |    |

| 142、143       | 第1、第2プロッキング絶縁膜 |    |

| 144           | 電極膜            |    |

| 145、145 a     | ゲート電極          |    |

| 145 L、147 L   | 下部ゲート領域        |    |

| 145 U、147 U   | 上部ゲート領域        |    |

| 146           | リセス領域          | 40 |

| 146 S         | 傾斜面            |    |

| 150、150 a     | 水平構造体          |    |

| 151           | 水平絶縁膜          |    |

| 155           | 分離絶縁膜          |    |

| 155 L         | 下部ゲートパターン      |    |

| 155 U         | 上部ゲートパターン      |    |

| 160           | 電極分離パターン       |    |

| 171           | コンタクトプラグ       |    |

| 175、BL        | ビットライン         |    |

| 1100          | 電子システム         | 50 |

|                   |                      |    |

|-------------------|----------------------|----|

| 1 1 1 0           | コントローラ               |    |

| 1 1 2 0           | 入出力装置 ( I / O )      |    |

| 1 1 3 0 、 1 2 1 0 | 記憶装置                 |    |

| 1 1 4 0           | インターフェイス             |    |

| 1 1 5 0           | バス ( b u s )         |    |

| 1 2 0 0           | メモリカード               |    |

| 1 2 2 0 、 1 3 1 2 | メモリコントローラ            |    |

| 1 2 2 1           | S R A M              |    |

| 1 2 2 2           | プロセシングユニット ( C P U ) |    |

| 1 2 2 3           | ホストインターフェイス          | 10 |

| 1 2 2 4           | エラー訂正ブロック ( E C C )  |    |

| 1 2 2 5           | メモリインターフェイス          |    |

| 1 3 0 0           | 情報処理システム             |    |

| 1 3 1 0           | フラッシュメモリ装置           |    |

| 1 3 1 1           | フラッシュメモリ             |    |

| 1 3 2 0           | モデム                  |    |

| 1 3 3 0           | 中央処理装置 ( C P U )     |    |

| 1 3 4 0           | R A M                |    |

| 1 3 5 0           | ユーザーインターフェイス         |    |

| 1 3 6 0           | システムバス               | 20 |

| B I L             | プロッキング絶縁膜            |    |

| B I P             | プロッキング絶縁膜パターン        |    |

| C P               | キャッピング膜パターン          |    |

| C P L             | キャッピング膜              |    |

| C S L             | 共通ソースライン             |    |

| C S T R           | セルストリング              |    |

| G S L             | 接地選択ライン              |    |

| G S T             | 接地選択トランジスター          |    |

| L S P             | 下部半導体パターン            |    |

| M C T             | メモリセルトランジスター         | 30 |

| S S L             | ストリング選択ライン           |    |

| S S T             | ストリング選択トランジスター       |    |

| U S P             | 上部半導体パターン            |    |

| V C S             | チャンネル構造体             |    |

| W L 0 ~ W L 3     | ワードライン               |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図21】

【図20】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

---

フロントページの続き

(72)発明者 南 泌 旭

大韓民国 京畿道 華城市 石隅洞 イエダンマウルウミリンジエイルブンギョンチェアパート

125棟 1701号

(72)発明者 梁 俊 圭

大韓民国 ソウル特別市 瑞草区 瑞草2洞 ヒュンダイアパート 10棟 1102号

(72)発明者 李 雄

大韓民国 ソウル特別市 鍾路区 母岳洞 インワンマウントアイ - パークアパート 113棟

202号

(72)発明者 李 宇 城

大韓民国 京畿道 龍仁市 処仁区 金良場洞 203 - 23番地 ドン - アマンション B棟

301号

(72)発明者 金 振 均

大韓民国 京畿道 水原市 靈通区 二儀洞 ウェルビーニングタウン路 ホバンベルティウムアパート

8710棟 1503号

(72)発明者 厳 大 弘

大韓民国 京畿道 華城市 盤松洞 ナルマウルシンドブラニューアパート 615棟 301号

審査官 小山 満

(56)参考文献 米国特許出願公開第2012/0068255(US, A1)

米国特許出願公開第2011/0147824(US, A1)

特開2011-211200(JP, A)

特開2009-277770(JP, A)

米国特許出願公開第2011/0233648(US, A1)

米国特許出願公開第2009/0283819(US, A1)

特開2011-066348(JP, A)

特開2009-224466(JP, A)

特開2010-093269(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/115 - 27/11597

H01L 21/336

H01L 29/788

H01L 29/792