(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-222781

(P2013-222781A)

(43) 公開日 平成25年10月28日(2013.10.28)

(51) Int.Cl.

|                    |                  |

|--------------------|------------------|

| <b>HO1L 23/48</b>  | <b>(2006.01)</b> |

| <b>HO1L 21/338</b> | <b>(2006.01)</b> |

| <b>HO1L 29/778</b> | <b>(2006.01)</b> |

| <b>HO1L 29/812</b> | <b>(2006.01)</b> |

F 1

|      |       |

|------|-------|

| HO1L | 23/48 |

| HO1L | 29/80 |

| HO1L | 23/48 |

| HO1L | 23/48 |

|   |

|---|

| R |

| H |

| T |

| G |

テーマコード(参考)

5F1O2

審査請求 未請求 請求項の数 6 O L (全 14 頁)

(21) 出願番号

特願2012-92575 (P2012-92575)

(22) 出願日

平成24年4月16日 (2012.4.16)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100114476

弁理士 政木 良文

(72) 発明者 井尻 良

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

F ターム(参考) 5F1O2 FA10 GB01 GC01 GD01 GJ03

GK04 GK08 GL04 GM04 QQ01

GR12 GV03 GV05

(54) 【発明の名称】半導体装置のデバイス実装構造

## (57) 【要約】

【課題】 GaNを用いる半導体装置の低消費電力および高速応答特性のメリットを生かすことのできるデバイス実装構造を実現する。

## 【解決手段】

表面実装型のデバイス実装構造を採用し、GaNチップ30の裏面をダイパッド14の表面と電気的に接続し、かかるダイパッド14とチップ30のソース端子11との接続をワイヤボンディングにより行う。ダイパッド14は、裏面が露出しており、プリント基板上の電極パッド(ソースパッド)と電気的に接続可能に構成されている。これにより、チップ裏面からのリーキ電流を減らし、オン抵抗を低減するとともに、ゲート-ソース間のループ電流を減らし、ソース配線側の寄生インダクタンスを低減することで、ゲート-ソース間の寄生容量を介したゲート電圧の発振を抑制する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

ソース端子、ドレン端子、ゲート端子の少なくとも三端子が基板表面側に設けられた、GaNを用いるパワーデバイスを搭載してなる半導体装置であって、

前記パワーデバイスが、表面実装タイプのリードフレームのダイパッド部の表面側に固定され、

前記パワーデバイスの前記ソース端子が前記ダイパッド部とワイヤ接続され、

前記パワーデバイスの前記ドレン端子がドレンリードと、前記パワーデバイスの前記ゲート端子がゲートリードとワイヤ接続され、前記ダイパッド部の裏面がプリント基板上のソースパッドと接続するために露出したデバイス実装構造を有することを特徴とする半導体装置。 10

## 【請求項 2】

前記ソース端子と前記ダイパッド部とのワイヤ接続における前記ダイパッド部側のワイヤとの接続位置に対応する裏面側が露出していることを特徴とする請求項 1 に記載の半導体装置。 20

## 【請求項 3】

前記ドレンリード内の樹脂封止されるインナーリード部分の面積が、前記ゲートリード内の樹脂封止されるインナーリード部分の面積よりも大きいことを特徴とする請求項 1 又は 2 に記載の半導体装置。 20

## 【請求項 4】

前記ドレン端子の長手方向に対して平行となるように前記ドレンリードが配置され、前記パワーデバイスの前記ダイパッド部上の位置が、前記ドレンリードが延伸する直線の延長線上に前記ドレン端子があるように、且つ、前記ドレンリード側に片寄って配置されていることを特徴とする請求項 1 ~ 3 の何れか一項に記載の半導体装置。 20

## 【請求項 5】

前記パワーデバイスを構成するトランジスタが、

前記ソース端子と接続するソース電極、前記ドレン端子と接続するドレン電極、及び、前記ゲート端子と接続するゲート電極を備え、

前記ゲート電極が前記ドレン電極よりも前記ソース電極側に片寄って配置される非対称構造を有することを特徴とする請求項 1 ~ 4 の何れか一項に記載の半導体装置。 30

## 【請求項 6】

前記ダイパッド部の裏面の露出部分には、前記ドレンリードよりも低電圧が供給されることを特徴とする請求項 1 ~ 5 の何れか一項に記載の半導体装置。 30

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体装置に関し、特に、GaNを用いるパワーデバイスチップをフレームに搭載する場合のデバイスの実装構造に関する。 40

## 【背景技術】

## 【0002】

GaN (窒化ガリウム) に代表される、バンドギャップが 2 eV を超えるワイドギャップ半導体を用いたデバイスは、従来の Si を用いるデバイスと比較して、低消費電力であり、高速スイッチングが可能という利点を備えている。これは、デバイスの絶縁破壊電界が大きいという理由による。

## 【0003】

一般に、デバイスの耐圧はドリフト層の長さ (WD) と絶縁破壊電界 (Ec) の積により表される。従って、耐圧を同じとした場合、絶縁破壊電界が大きい方がドリフト層の長さを短くできる。ここで、ワイドギャップ半導体において、絶縁破壊電界は Si よりも 10 倍程度高いため、ドリフト層の長さをおよそ 1 / 10 にすることができる。また、不純

物濃度は絶縁破壊電界の2乗に比例するため、Siと比べて100倍に高くすることができる。以上より、耐圧を同じとした場合、ワイドギャップ半導体を用いたデバイスのオン抵抗( $R_{on}$ )は、Siを用いるデバイスと比較して約1/1000に低抵抗化が可能となる。

【0004】

一方、デバイスの高速応答性を表す指標として、遮断周波数( $f_T$ )という指標がある。当該遮断周波数はデバイスの電流利得が1となる周波数であり、ドリフト層の長さWDに反比例する。従って、ワイドギャップ半導体を用いるデバイスでは、ドリフト層の長さをSiと比べて1/10に設定できることにより、Siよりも一桁高い周波数で使用することが可能となる。

10

【0005】

このように、ワイドギャップ半導体を用いることで、Siと比較してオン抵抗が低く、結果低消費電力で、且つ、高速性に優れたデバイスが可能である。

【0006】

上記のワイドギャップ半導体を用いるデバイスの実装方法として、下記特許文献1および2に示すように、ドレインリードとダイパッドを接続したリードフレームのダイパッド上にデバイスを固定し、デバイスとドレインリード、ソースリード、及び、ゲートリードとの接続をワイヤボンディングにより行う方法が、従来より用いられてきた。

【0007】

図8に、かかる従来構成の方法でチップ実装を行う場合の樹脂封止(モールド)される前のリードフレームとGaNチップ30とのワイヤボンディングの状態を示す平面図を示す。

20

【0008】

従来例では、図8に示すように、ドレインリード16とダイパッド14が一体成形されたリードフレームを用いて、ドレイン端子12とドレインリード16の接続が、ドレイン端子12とダイパッド14をワイヤボンディングすることによりなされている。一方、ソースリード15及びゲートリード17は、夫々、ダイパッド14と分離形成され、ソースリード15とソース端子11、ゲートリード17とゲート端子13との接続が、ワイヤボンディングによりなされている。

30

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2008-66553号公報

【特許文献2】特開2010-16103号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

従来のSiパワーデバイスでは、ゲート注入電荷量 $Q_g$ が大きいため、寄生発振が起こるような大きなインダクタンスは回路側で対応が可能であり、デバイス実装において、回路の寄生インダクタンスについて特別の注意を払う必要がなかった。

40

【0011】

ところが、GaNを用いたデバイスでは、ゲート注入電荷量 $Q_g$ が非常に小さいため、単なる配線の寄生インダクタンスであってもゲート電圧が発振する虞がある。すなわち、一般に用いられるソースリード、ドレインリード、ゲートリードの長さにより生じる寄生インダクタンスであっても、ゲート電圧の発振が問題になる。

【0012】

これに対し、ゲート抵抗として大きなものをゲート端子に接続することで発振は抑制できるが、GaNの低消費電力、高速応答性の長所を生かすことができない結果となる。

【0013】

本発明は、上記の状況に鑑み、GaNを用いたデバイスにおいて、大きなゲート抵抗を

50

付加することなく寄生発振を抑制できるように、デバイス実装構造の面から寄生インダクタンスの低減を実現するものであり、これにより、GaNの特徴である低消費電力、高速応答特性を生かしたパワーデバイスを実現することを目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するための本発明に係る半導体装置は、ソース端子、ドレイン端子、ゲート端子の少なくとも三端子が基板表面側に設けられた、GaNを用いるパワーデバイスを搭載してなる半導体装置であって、

前記パワーデバイスが、表面実装タイプのリードフレームのダイパッド部の表面側に固定され、前記パワーデバイスの前記ソース端子が前記ダイパッド部とワイヤ接続され、

前記パワーデバイスの前記ドレイン端子がドレインリードと、前記パワーデバイスの前記ゲート端子がゲートリードとワイヤ接続され、前記ダイパッド部の裏面がプリント基板上のソースパッドと接続するために露出したデバイス実装構造を有することを特徴とする。

【0015】

上記特徴の半導体装置は、更に、前記ソース端子と前記ダイパッド部とのワイヤ接続における前記ダイパッド部側のワイヤとの接続位置に対応する裏面側が露出していることが好ましい。

【0016】

上記特徴の半導体装置は、更に、前記ドレインリード内の樹脂封止されるインナーリード部分の面積が、前記ゲートリード内の樹脂封止されるインナーリード部分の面積よりも大きいことが好ましい。

【0017】

上記特徴の半導体装置は、更に、前記ドレイン端子の長手方向に対して平行となるように前記ドレインリードが配置され、前記パワーデバイスの前記ダイパッド部上の位置が、前記ドレインリードが延伸する直線の延長線上に前記ドレイン端子があるように、且つ、前記ドレインリード側に片寄って配置されていることが好ましい。

【0018】

上記特徴の半導体装置は、更に、前記パワーデバイスを構成するトランジスタが、前記ソース端子と接続するソース電極、前記ドレイン端子と接続するドレイン電極、及び、前記ゲート端子と接続するゲート電極を備え、前記ゲート電極が前記ドレイン電極よりも前記ソース電極側に片寄って配置される非対称構造を有することが好ましい。

【0019】

上記特徴の半導体装置は、更に、前記ダイパッド部の裏面の露出部分には、前記ドレンリードよりも低電圧が供給されることが好ましい。

【発明の効果】

【0020】

本発明者等は、鋭意研究により、ソース側配線の寄生インダクタンスを小さくすることで、発振が抑制され、ゲート電圧のオンオフに対して安定なスイッチングが可能になることを見出した。

【0021】

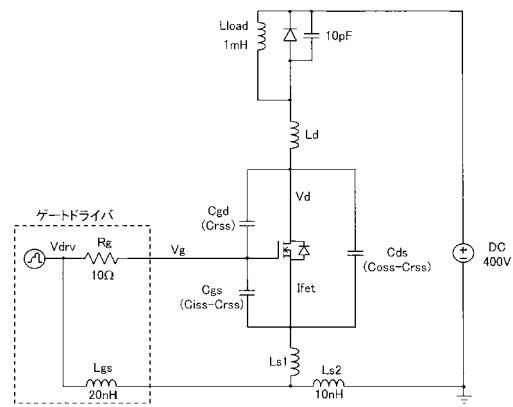

図9にシミュレーションに用いた回路の構成を示す。Ld、Ls1、Ls2、Lgsは夫々配線の寄生インダクタンスであり、Cgd、Cgs、Cdsは夫々GaN-FETの寄生容量である。図9において、FETがオンからオフに、オフからオンに切り替わると、LdからCoss、Ls1、及びLs2を介したLC直列回路が共振する。結果、Ls1の両端電圧が振動する。かかるLs1の両端電圧の振動は、ゲートドライバにとって電圧ノイズ源となる。

【0022】

更に、Ls1の両端電圧が振動することにより、CgsとLs1を介したLC直列回路が共振し、ゲート電圧Vgが振動する。この結果、FETの意図しないオンオフが繰り返

10

20

30

40

50

され、これが更に  $L_d$  から  $C_{oss}$ 、 $L_{s1}$ 、及び  $L_{s2}$  を介した LC 直列回路の共振を引き起こす。

【0023】

このように、 $L_d$  から  $C_{oss}$ 、 $L_{s1}$ 、及び  $L_{s2}$  を介した LC 直列回路の共振と、 $C_{gs}$  と  $L_{s1}$  を介した LC 直列回路の共振が相互に誘起される結果、ゲート電圧  $V_g$  の振動が増幅され、スイッチングノイズが増加し、最悪の場合 FET が発振して回路が破壊される虞がある。

【0024】

上記の LC 回路による共振を防ぐには、 $L_d$  と  $L_{s1}$ （及び、 $L_{s2}$ ）をできる限り小さくすればよいことが推察される。

10

【0025】

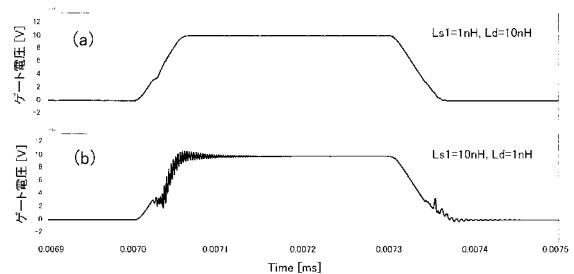

図 10 は、ソース側配線の寄生インダクタンス  $L_{s1}$ 、及び、ドレイン側配線の寄生インダクタンス  $L_d$  を変えた場合の、スイッチング時のゲート電圧の立ち上がり、立ち下がりの電圧変化をシミュレーションした結果である。図 10 より、ドレイン側配線の寄生インダクタンス  $L_d$  を小さくする（図 10（b））よりも、むしろソース側配線の寄生インダクタンス  $L_{s1}$  を小さくした（図 10（a））方が、ゲート電圧の振動防止に著しい効果があることが分かる。

【0026】

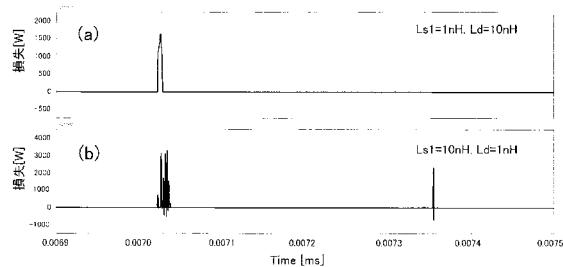

図 11 は、図 10 において FET に生じる電力損失（=  $I_{fe} * V_d$ ）を示す図であり、図 11 より、ドレイン側配線の寄生インダクタンス  $L_d$  を小さくする（図 11（b））よりも、ソース側配線の寄生インダクタンス  $L_{s1}$  を小さくした（図 11（a））方が、損失も少ないことが分かる。

20

【0027】

上記の知見に基づき、本発明では、デバイスの実装方法を変更し、表面実装型のデバイス実装構造において、GaN チップ裏面をダイパッド部の表面と電気的に接続し、かかるダイパッド部とデバイスのソース端子との接続をワイヤボンディングにより行うこととした。ダイパッド部は、裏面が露出しており、プリント基板上の電極パッド（ソースパッド）と電気的に接続可能に構成されている。

【0028】

このような構成とした場合、ダイパッド部の厚みが従来構成におけるソースリードの長さに相当するため、ソース側配線の寄生インダクタンスが大幅に低減され、ゲート電圧の発振を抑制できる。また、従来のソースリードがダイパッド厚みまで短くなるため、オン抵抗を小さくすることができる。

30

【0029】

さらに、従来のダイパッドとドレインリードを一体成形した構造と比較して、GaN チップのソース端子とチップ裏面の電位差を小さくできるため、チップ裏面からのリーク電流を減らすことができる。また、ゲート - ソース間のループ電流が小さくなることでソース配線の寄生インダクタンスに起因した電圧変動（誘導電圧）が抑制され、 $C_{gs}$  を介した LC 直列回路の発振を抑えることができる。

40

【0030】

従って、本発明に依れば、GaN を用いたデバイスにおいて、大きなゲート抵抗を付加することなく寄生発振を抑制でき、GaN の特徴である低消費電力、高速応答特性を生かしたパワーデバイスを実現することができる。

【図面の簡単な説明】

【0031】

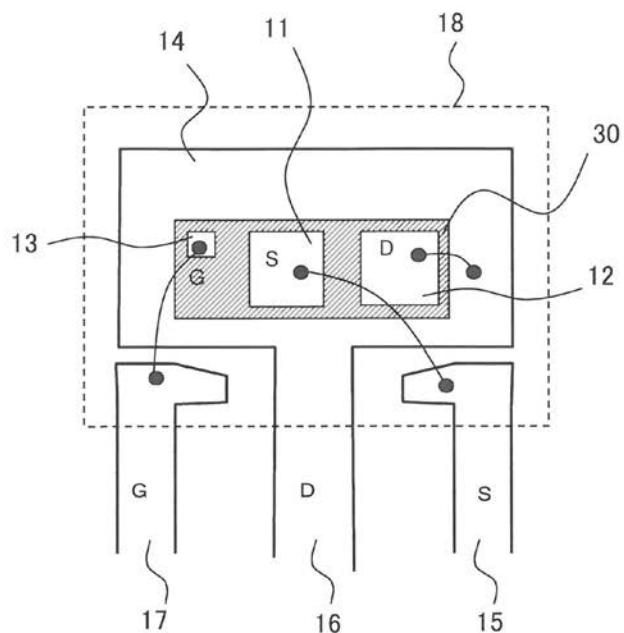

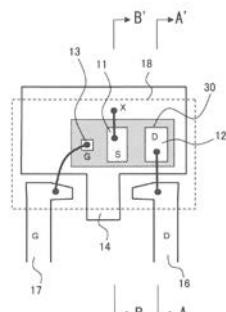

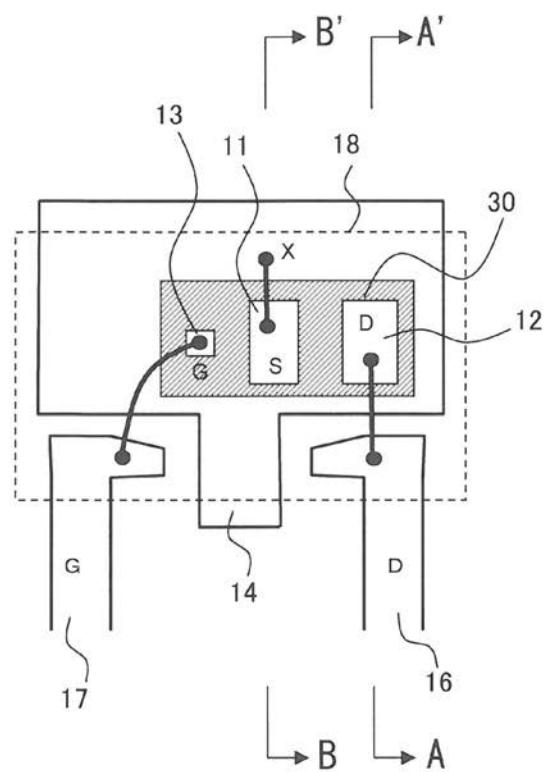

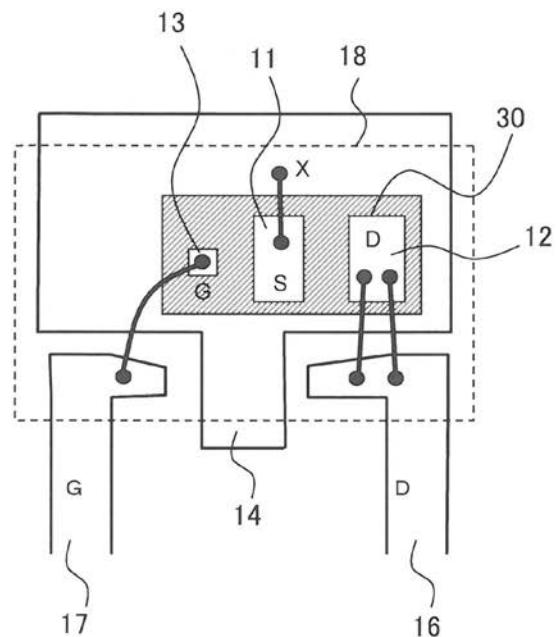

【図 1】本発明に係る半導体装置のチップ実装例を示す樹脂封止前の平面図

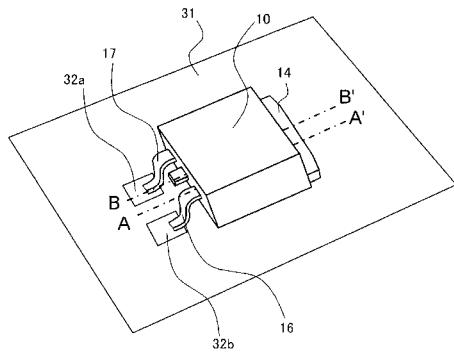

【図 2】本発明に係る半導体装置のチップ実装例を示す樹脂封止後の鳥瞰図

【図 3】本発明に係る半導体装置のチップ実装例を示す樹脂封止後の断面図

【図 4】GaN を用いるパワーデバイスのデバイス構造を示す断面図。

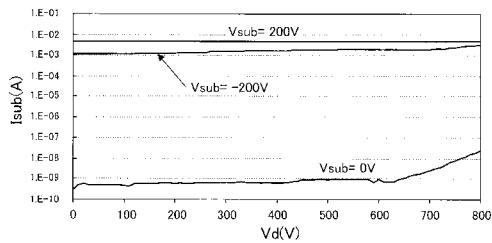

【図 5】GaN パワーデバイスにおいて、基板電位とソース電圧との電位差に対するリ

50

## ク電流の依存性を示すグラフ

【図 6】本発明に係る半導体装置の他のチップ実装例を示す樹脂封止前の平面図

【図 7】本発明に係る半導体装置の他のチップ実装例を示す樹脂封止前の平面図

【図 8】従来技術に係る半導体装置のチップ実装例を示す樹脂封止前の平面図

【図 9】本発明の課題を説明するための回路図

【図 10】本発明の効果を説明するためのグラフであり、スイッチング時のゲート電圧の立ち上がり及び立ち下がりの、ゲート電圧の変化を示すグラフ

【図 11】本発明の効果を説明するためのグラフであり、スイッチング時において F E T に生じる電力損失の時間変化を示すグラフ

【発明を実施するための形態】

【0 0 3 2】

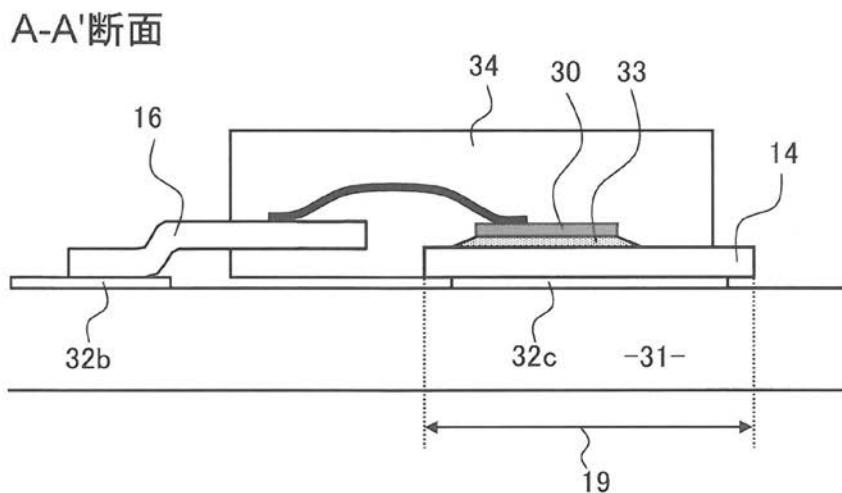

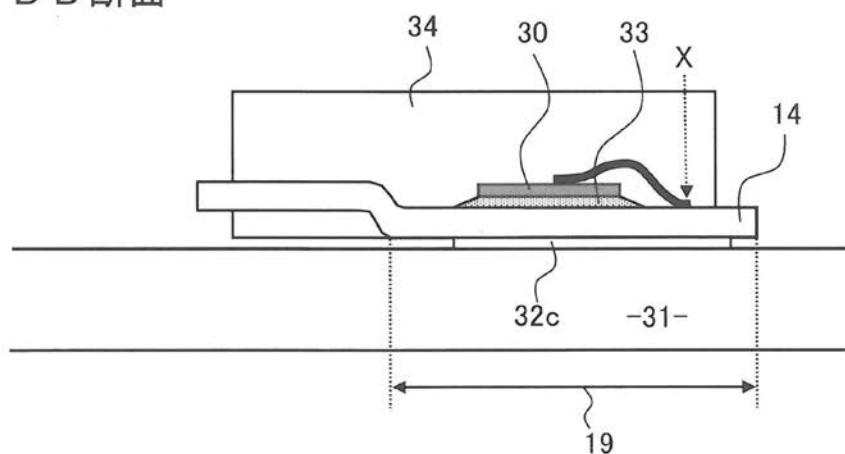

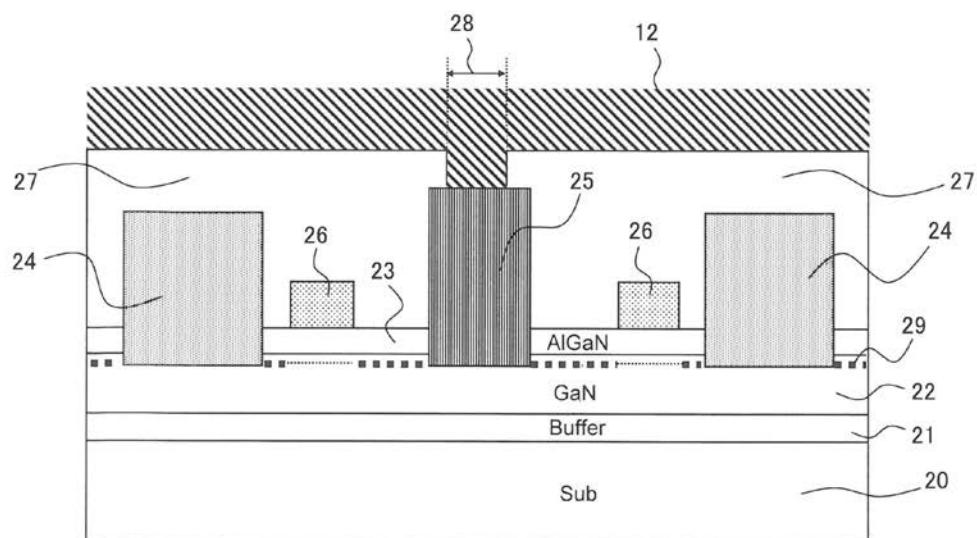

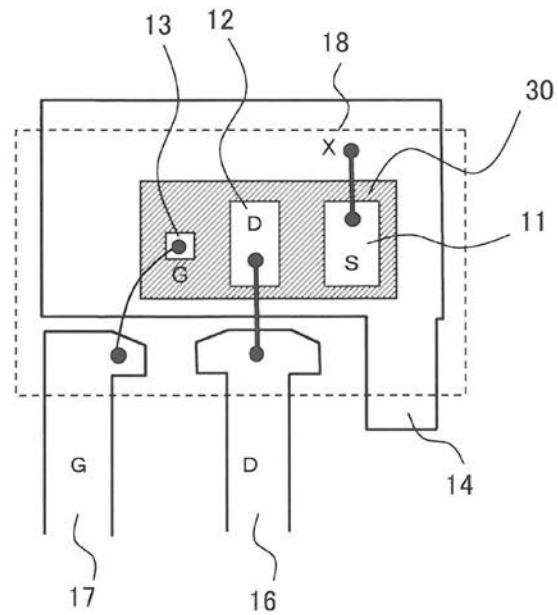

本発明のチップ実装構造を有する半導体装置 1 0 の構成例を図 1 ~ 図 3 に示す。図 1 ~ 図 3 は、半導体装置 1 0 の実装後の形態を示す模式図である。図 1 は、樹脂封止（モールド）される前のリードフレームと G a N チップとのワイヤボンディングの状態を示す平面図である。図 2 は、樹脂封止後の半導体装置 1 0 をプリント基板上に実装した状態を示す鳥瞰図である。また、図 3 は図 1 及び図 2 の A - A' 方向（ドレイン端子 1 2 及びドレインリード 1 6 上で、ドレインリード 1 6 に平行な方向）並びに B - B' 方向（ソース端子 1 1 上で、ドレインリード 1 6 に平行な方向）のプリント基板 3 1 に垂直な面における断面図である。なお、以降の実施形態の説明に用いる図面では、同一の構成要素には同一の符号を付すこととし、また、名称及び機能も同一であるので、同様の説明を繰り返すことはしない。

【0 0 3 3】

半導体装置 1 0 は、G a N を用いて構成されるパワーデバイスであり、基板表面側に、ソース端子 1 1 、ドレイン端子 1 2 、ゲート端子 1 3 が形成されたチップ 3 0 を備える。

【0 0 3 4】

一例として、G a N を用いるパワーデバイスのデバイス構造の模式的な断面図を図 4 に示す。図 4 に示すデバイスは、H E M T (High Electron Mobility Transistor) 構造の F E T であり、S i 基板 2 0 上に、A 1 と G a の組成比が異なる A 1 G a N の多層膜からなるバッファ層 2 1 を介して G a N 層 2 2 が積層され、G a N 層 2 2 の上に A 1 G a N の層 2 3 が積層されている。G a N 層 2 2 上の所定の領域には、A 1 G a N 層 2 3 を貫通するようにソース電極 2 4 とドレイン電極 2 5 が形成され、ゲート電極 2 6 が、A 1 G a N 層 2 3 上の所定の領域に、ソース電極 2 4 とドレイン電極 2 5 がゲート電極 2 6 を挟んで互いに対向するように形成されている。ドレイン電極 2 5 は、絶縁膜 2 7 上に形成されたドレイン端子 1 2 と、コンタクトホール 2 8 を介して電気的に接続される。同様に、図示しないが、ソース電極 2 4 は、別の断面において、絶縁膜 2 7 上に形成されたソース端子 1 1 と電気的に接続され、ゲート電極 2 5 は、更に別の断面において、絶縁膜 2 7 上に形成されたゲート端子 1 3 と電気的に接続される。

【0 0 3 5】

A 1 G a N 層 2 3 と G a N 層 2 2 とのヘテロ接合界面近傍において、2 次元電子ガス層 2 9 が形成され、ゲート電極 2 6 に電圧（ゲート電圧）を印加することで、かかるゲート電極 2 6 の下方の 2 次元電子ガス層 2 9 の濃度が変調され、ソース電極 2 4 とドレイン電極 2 5 間に流れる電流が制御される。通常の使用では、ドレイン電極 2 5 には、ソース電極 2 4 に対して 2 0 0 V ~ 6 0 0 V 程度の高電圧が印加される。また、図 4 に示すデバイスは、ドレイン電極 2 5 に印加される電圧とゲート電圧との差が高電圧となるため、放電しないようにゲート電極 2 6 とドレイン電極 2 5 との距離を、ゲート電極 2 6 とソース電極 2 4 との距離よりも大きくとり、ゲート電極 2 6 がドレイン電極 2 5 よりもソース電極 2 4 側に片寄って配置された非対称なデバイス構造を有している。

【0 0 3 6】

図 1 ~ 図 3 に戻って、チップ 3 0 は、図 3 に示す導電性の接着材料 3 3 によりダイパッド 1 4 の表面に固定されている。図 1 に示すように、ダイパッド 1 4 に隣接して、ドレイ

10

20

30

40

50

ンリード 16、及び、ゲートリード 17 が配置され、ドレインリード 16 はチップ 30 のドレイン端子 12 と、ゲートリード 17 はチップ 30 のゲート端子 13 と、夫々ワイヤ接続（ワイヤボンディング）されている。さらに、ダイパッド 14 の表面側で、ソース端子 11 とダイパッド 14 との接続がワイヤボンディングによりなされている。そして、図 1 の点線で示す領域 18 内において、ワイヤ接続される部分を覆うように封止樹脂 34 で封止がされ、半導体装置 10 がパッケージされる。

【0037】

このようにしてパッケージされた半導体装置 10 は、ダイパッド 14 の裏面に露出部分 19 を有している。本実施形態では、半導体装置 10 は、ダイパッド 14 の裏面がモールド材により覆わる領域を除いて、ダイパッド 14 の裏面の金属部分が露出してプリント基板 31 上の電極パッドと電気的に接続可能に構成されている。図 2 及び図 3 に示すように、ドレインリード 16、及び、ゲートリード 17 を、夫々、プリント基板 31 上に形成された配線（電極パッド）32a、32b と接続し、ダイパッド 14 の裏面のかかる露出部分を、プリント基板 31 上に形成された配線（ソースパッド）32c と接続することで、プリント基板 31 上に半導体装置 10 が実装される。

10

【0038】

半導体装置 10 では、ソース端子 11 とプリント基板 31 上のソースパッド 32c との接続が、ソース端子 11 とダイパッド 14 とをワイヤボンディングし、ダイパッド 14 の裏面の露出部分をソースパッド 32c に接触することによりなされている。つまり、ダイパッド 14 は、従来構成（図 8）におけるソースリードに相当するものである。しかしながら、ダイパッド 14 内において電流は平板内を主として膜厚方向に流れるため、ダイパッド 14 で生じる寄生インダクタンスは非常に小さくなる。

20

【0039】

このとき、ソース端子 11 とダイパッド 14 とのワイヤボンディングにおけるダイパッド 14 側のワイヤとの接続位置（図 3 の位置 X）は、その対応する裏面側が露出している位置に設定されている。これにより、ワイヤからソースパッド 32c に流れるダイパッド 14 内の電流経路が最短となり、ダイパッド 14 内における電流の殆どは膜厚方向に流れる。この結果、ダイパッド 14 内において平板に平行に流れる電流成分を最低限にでき、平板に平行に流れる電流の寄生インダクタンスへの寄与を最小限にできる。

30

【0040】

つまり、ダイパッド 14 の厚みが従来構成におけるソースリードの長さに相当するため、ソース側配線の寄生インダクタンスが大幅に低減され、ゲート電圧の発振を抑制できる。

【0041】

具体的には、従来のソースリードの長さを 15 mm、ダイパッドの厚みを 1.5 mm として、インダクタンスが電流経路の長さに比例するとした場合、寄生インダクタンスを 1/10 に低減できる。

【0042】

さらに、半導体装置 10 では、ソース端子 11 とダイパッド 14 がワイヤボンディングされて接続されているため、ダイパッド 14 を介して基板 20 の電位がソース電圧に固定され、これにより、チップ裏面とソース電極 24 との間を、基板 20、バッファ層 21、及び GaN 層 22 の端部側壁を経由して流れるリーク電流を低減できる。

40

【0043】

図 5 に、ソース端子 11 を介してソース電極 24 に印加するソース電圧を基準として、基板 20 に与える電圧  $V_{sub}$  を変化させたときの、ドレイン電圧  $V_d$  とチップ裏面に流れるリーク電流  $I_{sub}$  との依存性を示す。図 5 から、基板 20 の電位とソース電圧に電位差があるとリーク電流が大きくなり、基板 20 の電位をソース電圧と同電位とすることにより、リーク電流を大幅に抑制できることが分かる。

【0044】

なお、かかるリーク電流の防止の観点からは、ソース電極 24 を、ドレイン電極 25 の

50

全周を囲むようにチップの周辺部に配置するとよい。これにより、チップ30の端部側壁を経由してチップ裏面とドレイン電極間に流れるリーク電流のパスが存在しないため、リーク電流を効果的に抑制できる。

【0045】

さらに、図1に示す半導体装置10では、チップ30をダイパッド14の中央に配置せず、ドレイン端子12とドレインリード16の距離が最適化されるように、チップ30のダイパッド14上の位置を、ドレインリード16側に片寄らせ、且つ、ドレインリード16が延伸する直線の延長線上にドレイン端子12があるように配置している。ドレイン端子12の平面レイアウト形状が長方形である場合、ドレイン端子12の長手方向に対して略平行となるようにドレインリード15を配置し、チップをドレインリード16に近づけて配置するとよい。これにより、ドレイン端子12とドレインリード16とをワイヤボンディングするワイヤの曲げ角を小さくでき、また、長さを短くできる。この結果、ソース配線側の寄生インダクタンスと併せて、ドレイン配線側の寄生インダクタンスを低減することが可能になる。

10

【0046】

また、ゲート端子13とゲートリード17とをワイヤボンディングするワイヤの長さを短くするため、ゲート端子13をゲートリード17に近づけて配置することが好ましい。

【0047】

なお、図1では、ソース端子11がチップ中央部に配置され、ドレイン端子がチップ周辺領域（図1の右側）に配置されているため、ドレインリード16を図1の右側に、ドレイン端子12の長手方向と平行になるように配置しているが、ドレイン端子12がチップ中央部に配置されるチップ構成の場合には、例えば図6に示すように、ドレインリード16がダイパッド14に対して中央に位置するようにダイパッド14と分離形成されたリードフレームを採用し、チップ30のダイパッド14上の位置をドレインリード16側に片寄らせ、且つ、ドレインリード16が延伸する直線の延長線上にドレイン端子12があるように配置するとよい。

20

【0048】

さらに、半導体装置10の他の実装例を図7の樹脂封止前の平面図に示す。図7では、ドレインリード16の領域18との重なり部分、即ちドレインリード16内の樹脂封止される部分（インナーリード）の面積を、ゲートリード17の領域18との重なり部分、即ちゲートリード17内の樹脂封止される部分の面積よりも大きくしている。上記ドレインリード16（ゲートリード17）の樹脂封止される部分は、ワイヤボンディングが可能な部分の面積に相当する。ドレインリード16のワイヤボンディング可能な部分の面積を大きくすることで、ドレインリード16とドレイン端子12との接続を、複数のワイヤを介して行うことが可能になるため、ソース配線側の寄生インダクタンスと併せて、ドレイン配線側の寄生インダクタンスを低減することが可能になる。これにより、ゲート電圧の発振を防止できるとともに、オン抵抗を削減することができる。

30

【0049】

ところで、本発明では、ドレインリード16はドレイン端子12とワイヤボンディングされる。このため、ドレインリード16とダイパッド14が一体成形され、ドレイン端子12とダイパッド14をワイヤボンディングされる従来の構成（図8）と比較すると、ドレイン配線の寄生インダクタンスはかえって増加する場合がある。しかしながら、図10より、ソース配線側の寄生インダクタンス（図9の $L_{S1}$ ）を低減することが、ドレイン配線側の寄生インダクタンス（図9の $L_{d1}$ ）を低減することよりも、ゲート電圧の発振を抑制するという点において重要であることが示されている。別の言い方をすると、図10は、ゲート電圧の発振を抑制するという点において、ソース配線側の寄生インダクタンスを低減することで、ドレイン配線の寄生インダクタンスが増加することによるデメリットをはるかに上回るメリットが得られるることを示すものである。そして、本発明は、これを積極的に利用するものである。

40

【0050】

50

以上、本発明の半導体装置 10 では、GaN を用いたパワーデバイスの実装において、表面実装型のデバイス実装構造を採用し、GaN チップ裏面をダイパッド 14 の表面と電気的に接続し、ダイパッド 14 とチップ表面のソース端子 11 との接続をワイヤボンディングにより行うことで、ソースリード側の寄生インダクタンスを大幅に低減できる。これにより、半導体装置 10 は、大きなゲート抵抗を付加することなく寄生発振を抑制でき、GaN の特徴である低消費電力、高速応答特性を生かしたパワーデバイスが実現される。

【産業上の利用可能性】

【0051】

本発明は、GaN をスイッチング素子として用いるパワーデバイスの実装に利用可能である。

10

【符号の説明】

【0052】

|           |                                              |

|-----------|----------------------------------------------|

| 10 :      | 半導体装置 (GaN デバイス)                             |

| 11 :      | ソース端子                                        |

| 12 :      | ドレイン端子                                       |

| 13 :      | ゲート端子                                        |

| 14 :      | ダイパッド                                        |

| 15 :      | ソースリード                                       |

| 16 :      | ドレインリード                                      |

| 17 :      | ゲートリード                                       |

| 18 :      | 樹脂封止される領域                                    |

| 19 :      | ダイパッドの裏面の露出部分                                |

| 20 :      | 基板                                           |

| 21 :      | バッファ層                                        |

| 22 :      | GaN 層                                        |

| 23 :      | AlGaN 層                                      |

| 24 :      | ソース電極                                        |

| 25 :      | ドレイン電極                                       |

| 26 :      | ゲート電極                                        |

| 27 :      | 絶縁膜                                          |

| 28 :      | コンタクトホール                                     |

| 29 :      | 2 次元電子ガス                                     |

| 30 :      | チップ                                          |

| 31 :      | プリント基板                                       |

| 32a、32b : | 電極パッド                                        |

| 32c :     | ソースパッド                                       |

| 33 :      | 接着樹脂                                         |

| 34 :      | 封止樹脂                                         |

| X :       | ソース端子とダイパッドとのワイヤボンディングにおけるダイパッド 14 側のワイヤ接続位置 |

20

30

40

【図2】

【図9】

【図5】

【図10】

【図11】

【図1】

【図3】

B-B'断面

【図4】

【図6】

【図7】

【図8】