(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3984020号

(P3984020)

(45) 発行日 平成19年9月26日(2007.9.26)

(24) 登録日 平成19年7月13日(2007.7.13)

(51) Int.C1.

F 1

|                        |                |

|------------------------|----------------|

| HO1L 21/8247 (2006.01) | HO1L 27/10 434 |

| HO1L 27/115 (2006.01)  | HO1L 29/78 371 |

| HO1L 29/792 (2006.01)  |                |

| HO1L 29/788 (2006.01)  |                |

請求項の数 21 (全 30 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2001-324141 (P2001-324141)  |

| (22) 出願日     | 平成13年10月22日 (2001.10.22)      |

| (65) 公開番号    | 特開2002-203919 (P2002-203919A) |

| (43) 公開日     | 平成14年7月19日 (2002.7.19)        |

| 審査請求日        | 平成15年7月10日 (2003.7.10)        |

| (31) 優先権主張番号 | 特願2000-331407 (P2000-331407)  |

| (32) 優先日     | 平成12年10月30日 (2000.10.30)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100083806<br>弁理士 三好 秀和                |

| (74) 代理人  | 100100712<br>弁理士 岩▲崎▼ 幸邦              |

| (74) 代理人  | 100100929<br>弁理士 川又 澄雄                |

| (74) 代理人  | 100108707<br>弁理士 中村 友之                |

| (74) 代理人  | 100095500<br>弁理士 伊藤 正和                |

| (74) 代理人  | 100101247<br>弁理士 高橋 俊一                |

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表面に溝を有する半導体基板と、

前記溝に埋め込まれ側面の上部が前記基板の表面より高い第1と第2の絶縁体と、

前記基板の表面上に設けられ、一端が前記第1の絶縁体と接し、他端が前記第2の絶縁体と接する第3の絶縁膜と、

前記第3の絶縁膜の表面上に設けられ、一端面が前記第1の絶縁体と接し、他端面が前記第2の絶縁体と接する第1の浮遊ゲート電極と、

前記第1の浮遊ゲート電極の上方で、前記第1の浮遊ゲート電極の前記一端面の近傍に設けられる第2の浮遊ゲート電極と、

前記第1の浮遊ゲート電極の上方で、前記第1の浮遊ゲート電極の前記他端面の近傍に設けられる第3の浮遊ゲート電極と、

前記第2の浮遊ゲート電極の前記第3の浮遊ゲート電極と対向する側の第1の側面と、前記第3の浮遊ゲート電極の前記第2の浮遊ゲート電極と対向する側の第2の側面と、前記第1の浮遊ゲート電極の上面とを連続的に覆う第4の絶縁膜と、

前記第4の絶縁膜の上に設けられる制御ゲート電極とを有し、

前記第2の浮遊ゲート電極の前記第1の側面とは反対側の第2の側面と、前記第3の浮遊ゲート電極の前記第2の側面とは反対側の第1の側面との間隔は上ほど狭いことを特徴とする不揮発性半導体記憶装置。

## 【請求項 2】

前記第2の浮遊ゲート電極の前記第2の側面が前記第1の絶縁体と接し、前記第3の浮遊ゲート電極の前記第1の側面が前記第2の絶縁体と接することを特徴とする請求項1に記載の不揮発性半導体記憶装置。

【請求項3】

前記第1の絶縁体と前記第2の絶縁体は、縦方向に複数平行に交互に配置され、前記制御ゲート電極は横方向に複数平行に配置されることを特徴とする請求項1又は請求項2に記載の不揮発性半導体記憶装置。

【請求項4】

前記第2の浮遊ゲート電極が前記第1の浮遊ゲート電極と電気的に接続し、前記第3の浮遊ゲート電極が前記第1の浮遊ゲート電極と電気的に接続することを特徴とする請求項1乃至請求項3のいずれか1つに記載の不揮発性半導体記憶装置。 10

【請求項5】

前記第2と第3の浮遊ゲート電極の断面幅が積み上げ方向下向きに広くなることを特徴とする請求項1乃至請求項4のいずれか1つに記載の不揮発性半導体記憶装置。

【請求項6】

前記第1の絶縁体の上方に形成された前記制御ゲート電極の底面と、前記第2の絶縁体の上方に形成された前記制御ゲート電極の底面とは、ともに前記第1の浮遊ゲート電極の上面よりも高いことを特徴とする請求項1乃至請求項5のいずれか1つに記載の不揮発性半導体記憶装置。 20

【請求項7】

前記第2の浮遊ゲート電極の前記第1の側面とは反対側の前記第2の側面と前記第3の浮遊ゲート電極の前記第2の側面とは反対側の前記第1の側面の最大の間隔は前記第1の浮遊ゲート電極の前記一端面と前記他端面の距離よりも大きく、前記第2の浮遊ゲート電極の下面と前記第3の浮遊ゲート電極の下面是前記第1の浮遊ゲート電極の上面よりも低いことを特徴とする請求項2乃至請求項6のいずれか1つに記載の不揮発性半導体記憶装置。 30

【請求項8】

前記第2の浮遊ゲート電極の前記第1の側面とは反対側の前記第2の側面と前記第3の浮遊ゲート電極の前記第2の側面とは反対側の前記第1の側面の最大の間隔は前記第1の浮遊ゲート電極の前記一端面と前記他端面の距離よりも小さいことを特徴とする請求項2乃至請求項6のいずれか1つに記載の不揮発性半導体記憶装置。 30

【請求項9】

前記第2の浮遊ゲート電極の前記第1の側面とは反対側の前記第2の側面と前記制御ゲート電極の間に、前記第4の絶縁膜が配置され、前記第3の浮遊ゲート電極の前記第2の側面とは反対側の前記第1の側面と前記制御ゲート電極の間に、前記第4の絶縁膜が配置されることを特徴とする請求項2乃至請求項8のいずれか1つに記載の不揮発性半導体記憶装置。

【請求項10】

表面上に溝を有する半導体基板と、

前記溝に埋め込まれ上面が前記基板の表面より高い第1と第2の絶縁体と、 40

前記第1及び第2の絶縁体の間の前記基板の表面上に設けられる第3の絶縁膜と、

前記第3の絶縁膜の表面上に前記第1及び第2の絶縁体の間の領域に設けられる第1の浮遊ゲート電極と、

前記第1の浮遊ゲート電極の表面上に設けられ、外側面部の上面の高さが内部の上面の高さより高く、前記第2の絶縁体と接する第1の側面と前記第1の絶縁体と接する第2の側面の間隔は上ほど狭い第2の浮遊ゲート電極と、

前記第2の浮遊ゲート電極の前記内部の上面及び側面と接する第4の絶縁膜と、

前記第4の絶縁膜の上に設けられる制御ゲート電極とを有することを特徴とする不揮発性半導体記憶装置。

【請求項11】

前記第1の絶縁体と前記第2の絶縁体は、縦方向に複数平行に交互に配置され、前記制御ゲート電極は横方向に複数平行に配置されることを特徴とする請求項10に記載の不揮発性半導体記憶装置。

【請求項12】

前記第2の浮遊ゲート電極が前記第1の浮遊ゲート電極と電気的に接続することを特徴とする請求項10又は請求項11に記載の不揮発性半導体記憶装置。

【請求項13】

前記第1の絶縁体の上方に形成された前記制御ゲート電極の底面は、前記第1の浮遊ゲート電極の上面よりも高いことを特徴とする請求項10乃至請求項12のいずれか1つに記載の不揮発性半導体記憶装置。

10

【請求項14】

前記第2の浮遊ゲート電極の前記第1の側面と前記第2の側面の最大の間隔は前記第1の浮遊ゲート電極の幅よりも大きく、前記第2の浮遊ゲート電極の前記第1及び第2の側面近傍の下面は前記第1の浮遊ゲート電極の上面よりも低いことを特徴とする請求項10乃至請求項12のいずれか1つに記載の不揮発性半導体記憶装置。

【請求項15】

前記第2の浮遊ゲート電極の前記第1の側面と前記第2の側面の最大の間隔は前記第1の浮遊ゲート電極の幅よりも小さいことを特徴とする請求項10乃至請求項12のいずれか1つに記載の不揮発性半導体記憶装置。

【請求項16】

前記第2の浮遊ゲート電極の前記第2の側面と前記制御ゲート電極の間と、前記第2の浮遊ゲート電極の前記第1の側面と前記制御ゲート電極の間に、前記第4の絶縁膜がそれぞれ配置されることを特徴とする請求項10乃至請求項15のいずれか1つに記載の不揮発性半導体記憶装置。

20

【請求項17】

メモリセルアレイの端部に位置するダミーセルを有する不揮発性半導体記憶装置であつて、前記ダミーセルの構造が、

表面に溝を有する半導体基板と、

前記溝に埋め込まれ上面が前記基板の表面より高い第1の絶縁体と、

前記溝に埋め込まれ上面が前記基板の表面より高く、幅が前記第1の絶縁体より大きく、上面が前記第1の絶縁体の上面より高い第2の絶縁体と、

30

前記第1及び第2の絶縁体の間の前記基板の表面上に設けられる第3の絶縁膜と、

前記第3の絶縁膜の表面上に前記第1及び第2の絶縁体の間の領域に設けられる第1の浮遊ゲート電極と、

前記第1の浮遊ゲート電極の表面上に設けられ、外側面部の上面の高さが内部の上面の高さより高く、前記第2の絶縁体と接する第1の側面と前記第1の絶縁体と接する第2の側面の間隔は上ほど狭い第2の浮遊ゲート電極と、

前記第2の浮遊ゲート電極の前記内部の上面及び側面と接する第4の絶縁膜と、

前記第4の絶縁膜の上に設けられる制御ゲート電極とを有することを特徴とする不揮発性半導体記憶装置。

40

【請求項18】

前記第1の絶縁体と前記第2の絶縁体は、縦方向に平行に配置され、前記制御ゲート電極は横方向に複数平行に配置されることを特徴とする請求項17に記載の不揮発性半導体記憶装置。

【請求項19】

前記第2の浮遊ゲート電極が前記第1の浮遊ゲート電極と電気的に接続することを特徴とする請求項17又は18に記載の不揮発性半導体記憶装置。

【請求項20】

前記第1の絶縁体の上方に形成された前記制御ゲート電極の底面は、前記第1の浮遊ゲート電極の上面よりも高いことを特徴とする請求項17乃至請求項19に記載の不揮発性

50

半導体記憶装置。

【請求項 2 1】

前記第2の浮遊ゲート電極が前記第1の絶縁体の上面から完全に除かれ、前記第3の浮遊ゲート電極が前記第2の絶縁体の上面から完全に除かれていることを特徴とする請求項1乃至請求項9のいずれか1つに記載の不揮発性半導体記憶装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、溝型素子分離領域、浮遊ゲートと制御ゲートを有する半導体装置に関し、特に、浮遊ゲートと制御ゲート間の容量結合によってセルを動作させる不揮発性メモリの製造方法に関するものである。

10

【0002】

【従来の技術】

不揮発性半導体記憶装置は不揮発性メモリセルで構成されている。

この不揮発性メモリセルは、浮遊ゲートと制御ゲートを有する。浮遊ゲートと制御ゲート間の容量結合により浮遊ゲートの電位を制御する。制御ゲートと浮遊ゲートの容量結合が大きい程、制御ゲートの電圧を低くする事ができる。容量結合を大きくするために、制御ゲートと浮遊ゲート間の対向面積を以下のように大きくする。浮遊ゲートは、第1層目の多結晶シリコン(Si)膜と第2層目の多結晶シリコンの2層構造を有する。第1層目の多結晶シリコン膜は、溝型素子分離領域と自己整合的に形成される。第2層目の多結晶シリコンは、溝型素子分離領域上に張り出すように形成される。第2層目の多結晶シリコンの上に絶縁膜が形成される。この絶縁膜の上に制御ゲートが形成される。

20

【0003】

しかしながら、このセル構造では、メモリセルの素子分離幅Wtとして、第2層目の多結晶シリコン同士を分離する為のスペースとリソグラフィ工程の時の合わせ余裕が、必要である。

【0004】

このセル構造では、浮遊ゲートと制御ゲート間の容量結合を大きくするために、浮遊ゲートの膜厚を厚くすることが有効である。浮遊ゲートの膜厚を厚くすると、セル間の浮遊ゲートの容量結合C2が大きくなる。容量結合C2が大きくなると、隣のセルのデータの状態によって、セルのスレシホールド電圧が変調を受けやすい問題がある。

30

【0005】

【発明が解決しようとする課題】

本発明は、上記事情に鑑みてなされたものであり、その目的とするところは、浮遊ゲートと制御ゲート間の容量を大きく維持したまま素子分離幅Wtを狭めることができ可能な半導体装置を提供することにある。

【0006】

また、本発明は、浮遊ゲートと制御ゲート間の容量結合を大きくしても浮遊ゲート間容量が大きくなりにくく、セル間の電気的干渉を防ぐことができる半導体装置の製造方法を提供することにある。

40

【0007】

【課題を解決するための手段】

上記問題点を解決するための本発明の特徴は、表面に溝を有する半導体基板と、その溝に埋め込まれ側面の上部が半導体基板の表面より高い第1と第2の絶縁体と、半導体基板の表面上に設けられ、一端が第1の絶縁体と接し、他端が第2の絶縁体と接する第3の絶縁膜と、第3の絶縁膜の表面上に設けられ、一端面が第1の絶縁体と接し、他端面が第2の絶縁体と接する第1の導電体と、第1の導電体の一端面の近傍に設けられる第2の導電体と、第1の導電体の他端面の近傍に設けられる第3の導電体と、第2の導電体の第1の側面と第3の導電体の第2の側面に接し、第1の導電体の上面と接する第4の絶縁膜と、第4の絶縁膜の上に設けられる第4の導電体とを有する半導体装置にある。

50

## 【0008】

## 【発明の実施の形態】

次に、図面を参照して、本発明の実施の形態について説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。また、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。

## 【0009】

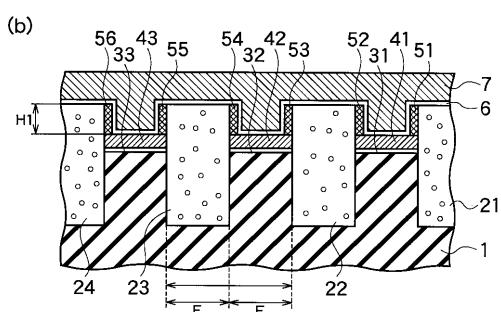

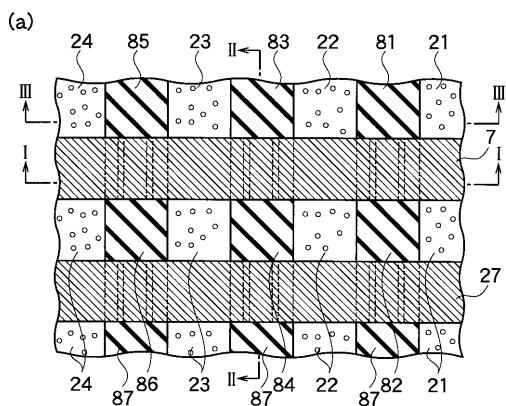

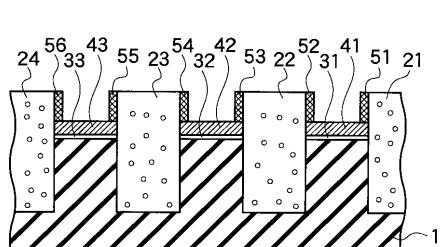

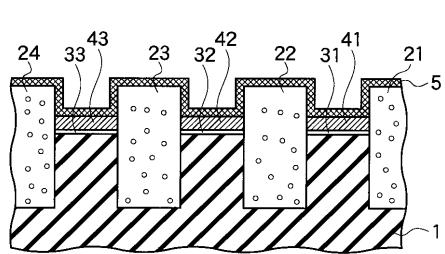

(第1の実施の形態) 図1(a)は本発明の第1の実施の形態に係る半導体装置の上面図である。図1(b)は図1(a)の半導体装置のI-I方向の断面図である。図2(a)は図1(a)の半導体装置のII-II方向の断面図である。図2(b)は図1(a)の半導体装置のIII-III方向の断面図である。 10

## 【0010】

本発明の第1の実施の形態に係る半導体装置は、以下の特徴を有する。半導体基板1は、表面に溝を有する。素子分離領域21乃至24は、その溝に埋め込まれる。素子分離領域21乃至24の側面が、基板1の表面より高い位置まで伸びている。トンネル酸化膜31乃至33が、基板1の表面上に設けられる。トンネル酸化膜31乃至33の両端が素子分離領域21乃至24と接している。

## 【0011】

トンネル酸化膜31乃至33の表面上に設けられ両端面が素子分離領域21乃至24と接している第1の導電体41乃至43と、第1の導電体41乃至43の表面上に設けられ第1の導電体の一方の端面の近傍に設けられ第1の側面が素子分離領域21乃至24と接している第2の導電体51、53、55と、第1の導電体41乃至43の表面上に設けられ第1の導電体の他方の端面の近傍に設けられ第1の側面が素子分離領域21乃至24と接している第3の導電体52、54、56とで構成される浮遊ゲート電極と、第2の導電体51、53、55と第3の導電体52、54、56の第2の側面と接し、第1の導電体41乃至43の表面と接する絶縁膜6と、絶縁膜6の上に設けられる制御ゲート7とで構成される。 20

## 【0012】

なお、以下の実施例では、電荷蓄積を担う電極(電荷蓄積領域)を、慣例に従い浮遊ゲート電極として示すが、用途に応じた保持時間、例えば、不揮発性メモリ用途では10年、揮発性メモリ用途では1秒(second)程度の時間だけ電荷保持を行える電極であればよい。 30

## 【0013】

半導体基板1の表面近傍で浮遊ゲート電極の下方以外の領域81乃至87の導電型は、他の領域の導電型と異なっている。さらに、図1(a)に示すように、溝型素子分離領域21乃至24を縦方向に複数平行に配置し、制御ゲート7と27を横方向に複数平行に配置することで、基板1上に不揮発性メモリセルを多数集積することができる。

## 【0014】

浮遊ゲート電極は、第1層目が第1の導電体41乃至43であり、第2層目が第2と第3の導電体51乃至56である2層構造になっている。第2と第3の導電体は、第1の導電体と電気的に接続しており、第1乃至第3の導電体が一体となって浮遊ゲート電極として機能する。 40

## 【0015】

溝型素子分離領域21乃至24と第1層目の浮遊ゲート電極層41乃至43のパターンは互いに反転パターンの関係にあり、溝型素子分離領域21乃至24によって第1層目の浮遊ゲート電極層41乃至43が自己整合的に分離されている。第2の浮遊ゲート電極層51乃至56は第1の浮遊ゲート電極41乃至43の端部において素子分離絶縁膜21乃至24の側面に側壁状に形成され、その側壁内面部分で制御ゲート7の下に凸の部分に対向している。

## 【0016】

浮遊ゲート 4 2、5 3、5 4 と制御ゲート 7 を有するフラッシュメモリにおいて、浮遊ゲート 4 2、5 3、5 4 と制御ゲート 7 間の容量結合を維持しながら微細化する為に、溝型素子分離領域 2 2、2 3 と、活性領域及び自己整合的に形成された第 1 の浮遊ゲート電極 4 2 を形成する第一の電極層の両端部に自己整合的に側壁 5 3、5 4 が形成され、その側壁 5 3、5 4 と制御ゲート 7 の容量結合を有効に利用する。これにより、制御ゲート 7 と浮遊ゲート 4 2、5 3、5 4 間の容量結合が増しメモリセルの性能が向上する。

【0017】

すなわち、第 2 の導電体 5 1 の側面が第 1 の素子分離領域 2 1 と接し、第 3 の導電体 5 2 の側面が第 2 の素子分離領域 2 2 と接する。このことにより、素子分離領域 2 1、2 2 に対して自己整合的に導電体 5 1、5 2 を製造することが可能になる。

10

【0018】

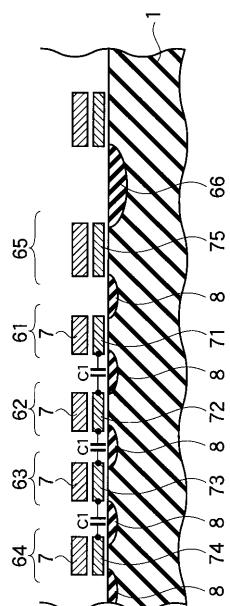

また、図 2 (a) と図 10 に示すように、浮遊ゲート 4 4 あるいは 7 1 乃至 7 4 の多結晶シリコンの膜厚を素子分離領域 2 2、2 3 に沿って側壁状に薄くできるため、隣接セル 6 1 乃至 6 4 間の浮遊ゲート電極間の寄生容量 C 1 を小さくできる。このことにより、寄生容量 C 1 を介したセル間干渉を低減することができる。

【0019】

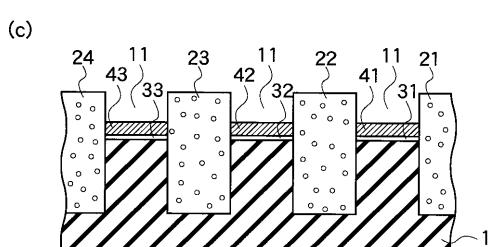

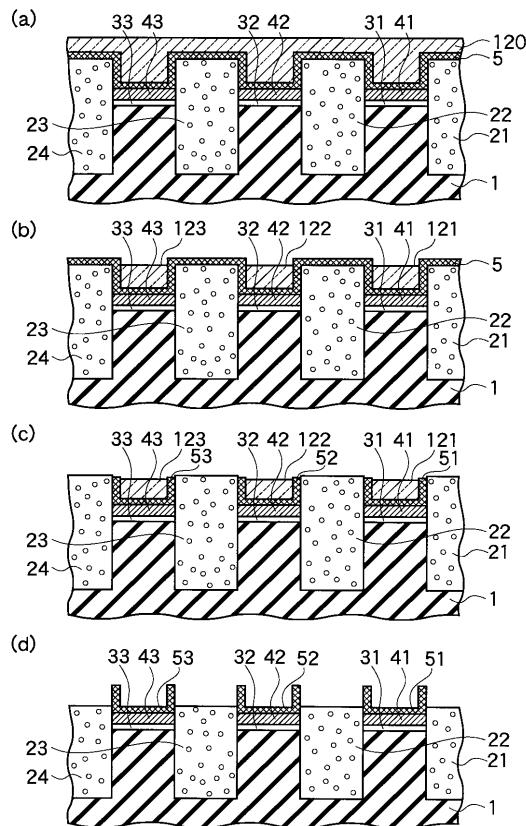

図 3 と 4 は、本発明の第 1 の実施の形態に係る半導体装置を製造する方法を示す工程断面図である。以下に製造方法を説明する。

【0020】

(1) まず、図 3 (a) に示すように、メモリセルの素子分離 2 2 と 2 3 用の溝部 1 0 と、第 1 の浮遊ゲート 4 1 乃至 4 3 及び活性領域は自己整合的に加工され、第 1 の浮遊ゲート 4 1 乃至 4 3 は活性領域を分離する素子分離領域 2 2、2 3 への落ち込みは全くないよう形成される。

20

【0021】

p 型シリコン (Si) 基板 1 上に、不揮発性メモリセルのトンネル (Tunnel) 酸化膜となる 3 nm 以上 15 nm 以下、例えば膜厚 10 nm の酸化膜または酸窒化膜 3 1 乃至 3 3、浮遊ゲートの一部の第 1 の浮遊ゲート電極となる第 1 の多結晶シリコン (Si) 膜 4 1 乃至 4 3、キャップ材として機能するシリコン窒化膜 9 1 乃至 9 3 を順次堆積する。このキャップ材 9 1 乃至 9 3 の膜厚に対応して、後で素子分離領域の側壁に形成される第 2 の浮遊ゲート電極 5 1 乃至 5 6 の高さが決まる。すなわち、キャップ材 9 1 乃至 9 3 の膜厚を厚くすることにより、第 2 の浮遊ゲート電極 5 1 乃至 5 6 の高さを高くすることができる。第 1 の多結晶シリコン膜 4 1 乃至 4 3 の膜厚は 10 nm 以上で 500 nm 以下の範囲で例えば 30 nm である。シリコン窒化膜 9 1 乃至 9 3 の膜厚は 3 nm 以上 500 nm 以下の範囲で例えば 100 nm である。

30

【0022】

次に、リソグラフィ工程とエッチングにより、素子分離領域 2 1 乃至 2 4 となる領域に溝 1 0 を掘る。具体的にはキャップ材 9 1 乃至 9 3 (シリコン窒化膜)、第 1 の浮遊ゲート材料 3 1 乃至 3 3、Si 基板 1 を順次エッチングする。素子分離用の溝 1 0 と、第一の多結晶シリコン膜 4 1 乃至 4 3、シリコン窒化膜 9 1 乃至 9 3 は自己整合的に形成される事になる。シリコン基板 1 中に掘る素子分離用の溝 1 0 の深さは、50 nm 以上 1000 nm 以下で例えば 300 nm といった深さである。素子分離用の溝 1 0 を掘った後、必要に応じて薄い酸化膜を例えば熱酸化法により形成する。この膜厚は 3 nm 以上 20 nm 以下で例えば 10 nm といった膜厚である。

40

【0023】

これにより、メモリセルの素子分離用の溝部 1 0 と、第一の浮遊ゲート 4 1 乃至 4 3 及び活性領域は、自己整合的に加工され、第一の浮遊ゲート 4 1 乃至 4 3 は活性領域を分離する素子分離領域 2 1 乃至 2 4 への落ち込みは全くないように形成される。これは、セルの微細化を実現すると共に、活性領域のコーナー部を覆うように浮遊ゲート 4 1 乃至 4 3 が形成される事がない為、電界集中の効果によるメモリセル特性のバラツキを抑制する事ができる。

50

## 【0024】

(2) 次に必要に応じて酸化膜を形成し、素子分離領域21乃至24に例えれば、高密度プラズマ(HDP: High Density Plasma)法により絶縁膜を埋め込む。次に、図3(b)に示すように、この埋め込み材を堆積後、ケミカルメカニカルポリッシュ(CMP: Chemical Mechanical Polishing)等の方法で、キャップ材91乃至93の上面まで絶縁膜21乃至24を平坦化する。素子分離領域21乃至24に埋め込まれている絶縁性埋め込み材は浮遊ゲートの端部に自己整合的に埋め込まれる。

## 【0025】

(3) 図3(c)に示すように、キャップ材91乃至93であるシリコン窒化膜を除去することにより、埋め込み材21乃至24で取り囲まれた溝部11を形成する。例えばキャップ材91乃至93がシリコン窒化膜であれば、熱(ホット)リン酸(H3PO4)といった薬液で処理すれば、キャップ材91乃至93のみを容易に除去する事ができる。

## 【0026】

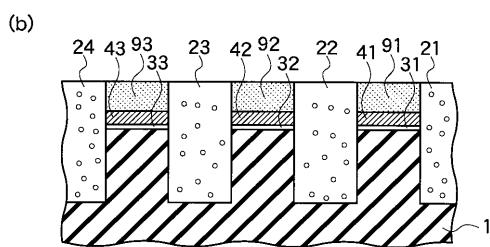

(4) 図4(a)に示すように、素子分離領域21乃至24の側壁に第2の浮遊ゲート電極51乃至56を形成する為に、薄い多結晶シリコン膜5を堆積する。

## 【0027】

(5) 図4(b)に示すように、この多結晶シリコン膜5をエッチバックすることにより、素子分離領域に埋め込まれた絶縁膜21乃至24の側面部に第2の浮遊ゲート材51乃至56を形成する。このエッチバック工程で、セル間に存在する素子分離領域21乃至24の上の第2の多結晶シリコン膜5は自己整合的に除去され、セル毎に分離することができる。例えば第2の浮遊ゲート材52と53は分離される。第1の浮遊ゲート材41乃至43と第2の浮遊ゲート材51乃至56は、第2の浮遊ゲート材51乃至56の底面で電気的に接続される。なお、第1と第2の浮遊ゲート間に薄い絶縁膜が存在していても容量結合される為、電気的に接続される場合と同様の動作が行われる。

## 【0028】

(6) 図4(c)に示すように、浮遊ゲート42、53、54と制御ゲート7間の層間絶縁膜6を形成する。層間絶縁膜6としては、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の3層構造膜いわゆるONO膜を用いる。

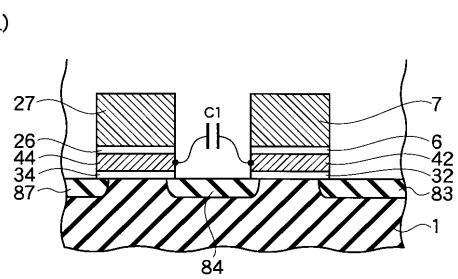

なお、この工程時の半導体装置の上方からの透視図を図5に示す。図5のI-I方向の断面図が図4(c)である。

## 【0029】

(7) 図1(b)に示すように、絶縁膜6で三方を囲まれた溝部11の内部を埋め込むように制御ゲート材7を形成する。素子分離領域の側壁に形成された第2の浮遊ゲート材料51乃至56と制御ゲート材料7の容量結合が確保できる。

## 【0030】

(8) 図1(a)に示すように、リソグラフィ工程とエッチングにより、制御ゲート材7と27を短冊状に形成する。このとき同じマスクを用い、さらに領域21乃至24もマスクに、図2の(a)(b)のように浮遊ゲート42、44等もエッチングする。なお、このエッチングにおいては、図1(b)に示すように、厚さが厚さH1でみな等しいゲート材7、導電体56等と絶縁膜6を同時に同じ速度でエッチングする必要が生じる場合がある。この場合はスパッタ性の高いエッチング条件を選択してもよいし、後述する第2の変形例を採用することで材料によってエッチング速度が異なっていても良好なエッチング形状を得ることができる。

## 【0031】

最後に、領域21乃至24や制御ゲート材料7、27をマスクに基板1にイオン注入を行い、活性化処理を行って、ソース・ドレイン領域81乃至87を形成する。

## 【0032】

この構造においては、一般に使用される浮遊ゲートを分離する為のリソグラフィとエッチング工程が不要である。浮遊ゲート41乃至43と活性領域の合わせ余裕も不要である。

10

20

30

40

50

素子分離領域 2 1 乃至 2 4 と活性領域が自己整合的に形成できる。このことにより、セルが微細化できる。図 1 ( b ) に示すようにセルの横幅を最小デザインルールを F とした時に、領域 2 3 等の幅と間隔をそれぞれ F に設定できるので、2 倍の F まで縮小できる。そして、高電圧を用いる半導体集積回路において、その素子分離スペースを F に縮小することができ、チップ面積を縮小できるので、コストを削減する事ができる。

#### 【 0 0 3 3 】

また、浮遊ゲート電極を構成するために、第 1 の浮遊ゲート（導電膜）4 1 乃至 4 3 の両端部に自己整合的に第 2 の浮遊ゲート（導電膜）5 1 乃至 5 6 による側壁が形成される。浮遊ゲート 4 1 乃至 4 3 の多結晶シリコンの膜厚を側壁状に薄くできるため、隣接セル間の浮遊ゲート電極間の寄生容量 C 1 を介したセル間干渉を低減することもできる。このように、浮遊ゲートと制御ゲートを有するフラッシュメモリにおいて、浮遊ゲート 4 1 乃至 4 3 等と制御ゲート 7 間の容量結合を維持しながら微細化できる。

#### 【 0 0 3 4 】

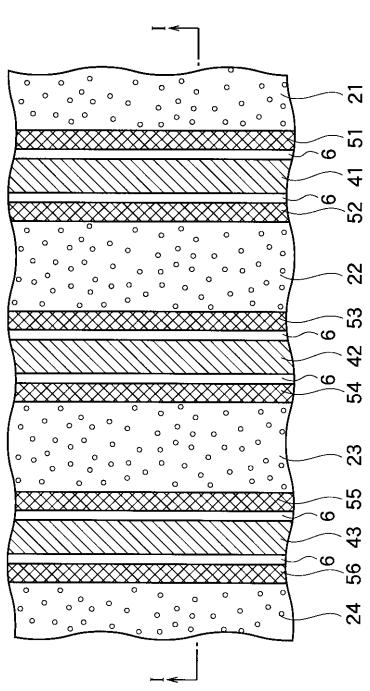

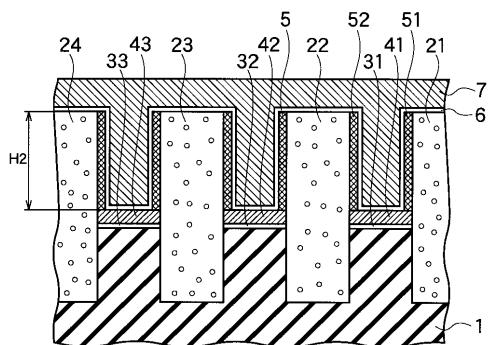

（第 1 の実施の形態の第 1 の変形例）図 6 に示すように、高さ H 2 を大きくすることによって、浮遊ゲートと制御ゲート間の容量結合を大きくすることができる。高さ H 2 を大きくするには、原理的にはキャップ材 9 1 等の膜厚を H 2 に設定すればよい。この時、導電体 4 1 の膜厚を厚くする必要が無く、幅の狭い導電体 5 1 、 5 2 等の高さが大きくなるだけなので、浮遊ゲート同士の間の容量結合 C 1 は増大するもののその増大率は、浮遊ゲート 4 1 、 5 1 、 5 2 と制御ゲート 7 間の容量結合の増大率より小さくできる。

#### 【 0 0 3 5 】

（第 1 の実施の形態の第 2 の変形例）第 1 の実施の形態では、素子分離領域 2 1 乃至 2 4 の側面に設けられる第 2 の浮遊ゲート 5 1 等の側面が、基板 1 の表面に対し垂直である。この垂直の場合、図 1 ( a ) に示すような短冊状の制御ゲート 7 、 2 7 をリアクティブイオンエッティング（ R I E : R e a c t i v e I o n E t c h i n g ）により形成するときに、自己整合的に同じマスクを用いて連続的に、制御ゲート 7 等と浮遊ゲート 5 1 、 5 2 等をエッティング加工する。このときに、浮遊ゲート 5 1 、 5 2 等の側面と制御ゲート 7 等の側面の間の垂直の絶縁膜 6 が除去されにくい。この除去されない絶縁膜 6 により、下層の第 1 層多結晶 Si 膜 4 1 等のエッティングにおいて、エッティング残りが発生する可能性がある。このエッティング残りはセル同士の浮遊ゲートをショートさせ半導体装置の歩留りを低下させる恐れがある。

#### 【 0 0 3 6 】

そこで、第 2 の変形例としては、図 7 に示すように素子分離領域 2 1 乃至 2 4 に側面に設けられる側壁の第 2 の浮遊ゲート電極層 1 5 1 乃至 1 5 6 の断面形状を順テーパー形状にする。この形状により、エッティング時の絶縁膜 1 6 の加工性を高める。これは、浮遊ゲート電極層 1 5 1 等の形状を順テーパー形状にすることで、絶縁膜 1 6 が斜めに配置されるので、 R I E のような異方性エッティングでも絶縁膜を少ないエッティング量で容易に除去することができるからである。この順テーパー形状は、例えば浮遊ゲート電極層 1 5 1 乃至 1 5 6 を形成するエッチバック時のエッティング条件を変えること（例えば基板温度を下げる等）により実現できる。

#### 【 0 0 3 7 】

（第 1 の参考例）第 1 の実施の形態では、側壁の浮遊ゲート 5 1 等の 2 面ある側面のうちの溝 1 1 の内側の側面のみで、浮遊ゲート 5 1 等は制御ゲート 7 と対向し容量結合している。第 1 の参考例では、図 8 ( b ) に示すように、溝 1 1 の外側の側面でも浮遊ゲート 5 1 等と制御ゲート 7 が対向する。

第 1 の参考例の半導体装置では、第 1 の実施の形態の半導体装置より、浮遊ゲート 5 1 等と制御ゲート 7 の容量結合をさらに増大させることができるものである。

#### 【 0 0 3 8 】

製造方法は、第 1 の実施の形態の工程 ( 5 ) の図 4 ( b ) まで同じである。次に図 8 ( a ) に示すように例えばウェット ( w e t ) エッティング法により素子分離領域 ( S T I ) 2 1 乃至 2 4 の溝部内に埋め込まれている絶縁膜をエッチバックする。以降の工程は第 1 の

10

20

30

40

50

実施の形態の工程(6)の図4(c)以降と同じである。すなわち、図8(b)に示すように、第1の浮遊ゲート41乃至43と第2の浮遊ゲート51乃至56の上に絶縁膜6を形成し、さらに、絶縁膜6上に制御ゲート7となる導電膜を形成する。このような構造を用いることにより、第2の浮遊ゲート51等の両側面で、制御ゲート7と容量結合させることができる。第2の浮遊ゲート51等の高さが同一であれば、第1の実施の形態より第2の浮遊ゲート51等と制御ゲート7の間の容量結合を大きくすることができる。また、第1の実施の形態と同じ大きさの容量結合を得るために、第2の浮遊ゲート51等の高さを第1の実施の形態より低くすることができる。

#### 【0039】

第1の参考例の半導体装置においては、メモリセル部の素子分離領域の絶縁膜21乃至24の高さは、第1の浮遊ゲート41乃至43の多結晶シリコン膜の上面の高さより高くなる。このことにより、図1(a)及び図2(a)に示す制御ゲート7と制御ゲート27のショートを防止することができる。

10

#### 【0040】

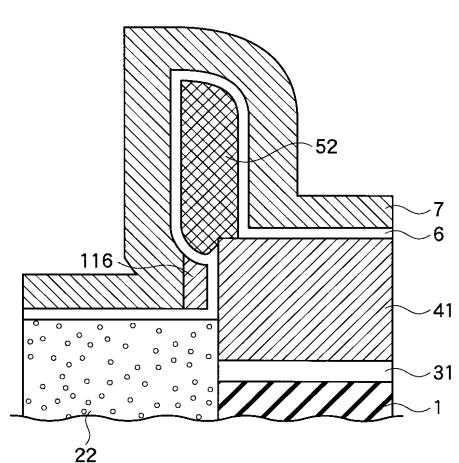

逆に、図9(a)に示すように、メモリセル部の素子分離領域の絶縁膜22の高さが、第1の浮遊ゲート41の上面の高さより低い場合について説明する。この場合に、制御ゲート電極7が、第1の浮遊ゲート41の上面の高さより低い位置に設けられる。そして、制御ゲート電極7が、領域116のように第2の浮遊ゲート52の下方に設けられる。第2の浮遊ゲート52が、第1の浮遊ゲート41よりも、素子分離領域22側に広がる。第2の浮遊ゲート52が、素子分離領域22の上方に設けられる。この広がりは、第1の浮遊ゲート41の上に第2の浮遊ゲート52を形成する処理の前処理で生じる。この前処理では、第1の浮遊ゲート41の上の自然酸化膜をエッチング除去する。このとき、露出している素子分離領域22もエッチングされ、素子分離領域21と22の間隔が広がる。

20

#### 【0041】

制御ゲート7と制御ゲート27を分離加工する。制御ゲート7、ブロック絶縁膜6と浮遊ゲート52、41を異方性エッチングによってほぼ垂直にエッチング加工しようとする、この分離加工に困難が生じる。制御ゲート7を全面形成後、MISFETのソースまたはドレイン電極を形成するために、異方性エッチングであるRIEによって、制御ゲート7、ブロック絶縁膜6、浮遊ゲート電極52、41を、ほぼ垂直に加工する。

#### 【0042】

30

まず、制御ゲート7をパターニングして垂直加工する。

ブロック絶縁膜6はエッチングされずに残る。制御ゲート電極7の第2の浮遊ゲート電極52の下方の領域116もエッチングされずに残る。これは、領域116がエッチャントから第2の浮遊ゲート52でマスクされるからである。

#### 【0043】

この後、ブロック絶縁膜6を異方性エッチングする。第2の浮遊ゲート52の下のブロック絶縁膜114は、エッチングされずに残る。これは、膜114がエッチャントから第2の浮遊ゲート52でマスクされるからである。領域116もエッチングされずに残る。

#### 【0044】

40

最後に、第1の浮遊ゲート41をエッチングによって取り除く。このエッチングのときも、膜114と領域116は除去されずに残る場合がある。

#### 【0045】

このエッチング残り領域116は、隣接するデータ制御線7と27の間の短絡不良を生じさせる。この短絡不良は、本発明者らが初めて見出した。領域116が除去されて存在せず、膜114のみがエッチャング後に残った場合も、ソース/ドレイン領域を形成するためのイオン注入を行うときや、ソース/ドレイン領域へのコンタクト電極を形成するためのエッチングを行うときに、イオン注入やエッチングのマスクとなるため、問題である。

#### 【0046】

これらのことから、第1の参考例では、メモリセル部の素子分離領域21乃至24の高さは、第1の浮遊ゲート41の上面より高くなるように制御する。このことにより、制御ゲ

50

ート電極 7 のエッティング残りの領域 116 を生じなくする。

【0047】

(第2の参考例) 第1の実施形態では、素子分離領域 21 乃至 24 の側面部に側壁状に第2の浮遊ゲート材 51 乃至 56 を形成する。第2の浮遊ゲート材 51 乃至 56 のそれぞれの分離は、エッチバック工程で行う。このエッチバック工程に関し、以下の問題が発生する場合があると考えられる。

【0048】

まず、エッチバックする第2の浮遊ゲート 51 乃至 56 の材料は多結晶シリコン膜である。第2の浮遊ゲート 51 乃至 56 の下層には、第1の浮遊ゲート 41 乃至 43 が設けられている。この第1の浮遊ゲート 41 乃至 43 の材料も多結晶シリコン膜である。エッチバック工程において、第2の浮遊ゲート 54 と 55 を確実に分離させる為に、第1の浮遊ゲート 41 乃至 43 もエッティングされる。これにより第1の浮遊ゲートの仕上がりの膜厚が、半導体記憶装置の間と内部でばらつく。このばらつきにより、セル特性がばらつく可能性を発明者は考えた。

【0049】

次に、セル間の容量結合 C1 を減少させるために、第1の浮遊ゲート 41 乃至 43 の膜厚を薄くすることができる。これは、この膜厚を減らしても、制御ゲートと浮遊ゲートの容量結合を減らすことがないからである。しかし、第1の浮遊ゲート 41 乃至 43 の膜厚を薄くすると、この薄い膜 41 乃至 43 の表面がエッチバック工程においてエッティングされる。このエッティングにより、薄い膜 41 乃至 43 にピンホールといった欠陥が発生する。この欠陥により、膜 41 乃至 43 の下層のトンネル酸化膜 31 乃至 33 の信頼性を劣化させる可能性を発明者は考えた。

【0050】

最後に、図 8 (a)において、第2の浮遊ゲート 51 乃至 56 は、下層の第一の浮遊ゲート 41 乃至 43 と密着する面積が小さい。このことにより、第2の浮遊ゲート 51 乃至 56 の高さを高くしすぎると、第2の浮遊ゲート 51 乃至 56 が、第一の浮遊ゲート 41 乃至 43 から剥がれ倒れる可能性を発明者は考えた。

【0051】

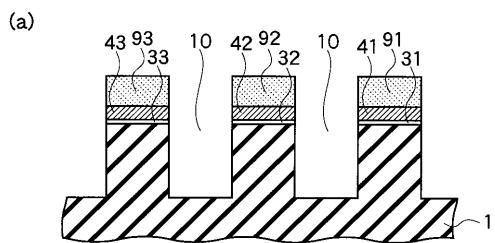

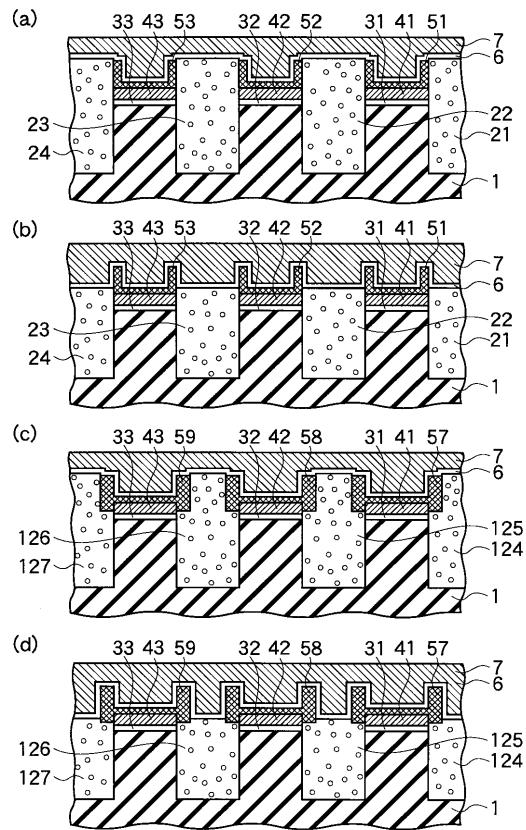

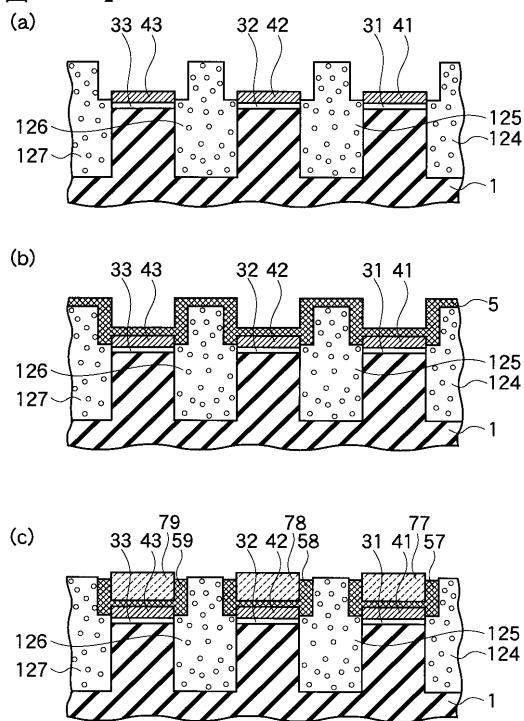

そこで第2の参考例では、半導体装置は、メモリセルの2つの第2の浮遊ゲート 51 と 52 を分離せず接続された一体のままの構造を有する。

そして、第2の浮遊ゲート 54 と 55 を分離するエッチバック工程では、第2の浮遊ゲート 55 と 56 の間に、第1の浮遊ゲート 43 を露出させない。

【0052】

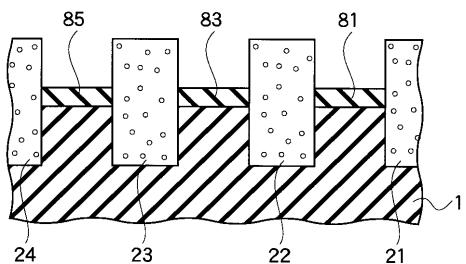

すなわち、第2の参考例に係る半導体装置は、図 11 (a) に示すように、表面に溝を有する半導体基板 1 を有する。素子分離領域 21 乃至 24 は、その溝に埋め込まれ側面が基板 1 の表面より高い位置まで伸びている。素子分離領域 21 乃至 24 の上面は、基板 1 の表面より高い。トンネル酸化膜 31 乃至 33 は、基板 1 の表面上に設けられる。トンネル酸化膜 31 乃至 33 の両端が素子分離領域 21 乃至 24 と接している。浮遊ゲートは、第1の導電体 41 乃至 43 と、第2の導電体 51 乃至 53 を有している。第1の導電体 41 乃至 43 は、トンネル酸化膜 31 乃至 33 の表面上に設けられる。第1の導電体 41 乃至 43 の両端面が、素子分離領域 21 乃至 24 と接している。第2の導電体 51 乃至 53 は、第1の導電体 41 乃至 43 の表面上に設けられる。第2の導電体 51 、 53 、 55 の底部が第1の導電体 41 乃至 43 に接する。第2の導電体 51 、 53 、 55 の両端部は、中央部より高い。その両端部の高さは、素子分離領域の上面の高さとほぼ等しい。浮遊ゲートと制御ゲートの間の絶縁膜 6 は、第2の導電体 51 乃至 53 の表面に接する。絶縁膜 6 は、素子分離領域 21 乃至 24 の上面の上に設けられる。制御ゲート 7 は、絶縁膜 6 の上に設けられる。

【0053】

浮遊ゲートは第1の導電体 41 乃至 43 と第2の導電体 51 乃至 53 の2層の積層構造になっている。導電体 41 乃至 43 と 51 乃至 53 は、いずれも厚さを薄く設定することに

10

20

30

40

50

より、浮遊ゲートと制御ゲートの間の接合容量を減らすことなく、隣接メモリセルの浮遊ゲート間の寄生容量  $C_1$  を小さくできる。

【0054】

次に、第2の参考例に係る半導体装置の製造方法を説明する。

【0055】

第1の実施形態の図3(a)から図4(a)を用いて説明した半導体装置の製造方法と基本的に同じ製造方法をまず行う。すなわち、メモリセルの素子分離用の溝部10と、第1の浮遊ゲート41乃至43及び活性領域は自己整合的に加工される。第1の浮遊ゲート41乃至43は素子分離領域21乃至24への落ち込みは全くない。

【0056】

(1) 図3(a)に示すように、p型シリコン(Si)基板1上に、シリコン酸化膜または酸窒化膜31乃至33を熱酸化により成膜する。このシリコン酸化膜または酸窒化膜31乃至33は、不揮発性メモリセルのトンネル(Tunnel)酸化膜となる。このシリコン酸化膜31乃至33の膜厚は3nm以上15nm以下、例えば10nm程度である。続けて、浮遊ゲートの一部で第1の導電体41乃至43となる多結晶シリコン(Si)膜を、シリコン酸化膜31乃至33の上に形成する。第1の導電体41乃至43の膜厚は10nm以上500nm以下で、例えば30nm程度である。さらに、キャップ材91乃至93として機能するシリコン窒化膜を、第1の導電体41乃至43の上に堆積する。このキャップ材91乃至93の膜厚によって、後で形成する第2の導電体51乃至53の高さが決まる。キャップ材91乃至93の膜厚は3nm以上500nm以下の範囲で、例えば120nm程度である。

【0057】

次に、ホトリソグラフィとエッチングにより、素子分離領域21乃至24となる領域に溝10を掘る。具体的には、素子分離領域21乃至24となる領域のキャップ材91乃至93、第1の導電体41乃至43、シリコン基板1を順次エッチングする。図3(a)に示すように、溝10と、第1の導電体41乃至43、キャップ材91乃至93は自己整合的に形成できる。これにより、セルの微細化を実現すると共に、活性領域のコーナー部を覆うように浮遊ゲートが形成される事がない為、電界集中の効果によるメモリセル特性のバラツキを抑制する事ができる。シリコン基板1中の溝10の深さは、50nm以上1000nm以下の範囲で、例えば300nm程度である。素子分離用の溝10の形成後、必要に応じて薄いシリコン酸化膜を、基板1と第1導電体の露出面の上に熱酸化法により形成する。この薄いシリコン酸化膜の膜厚は3nm以上20nm以下の範囲で、例えば5nm程度である。

【0058】

次に、溝10に例えば高密度プラズマ(HDP: High Density Plasma)法により絶縁膜を埋め込む。埋め込み材を堆積後、ケミカルメカニカルポリッシュ(CMP: Chemical Mechanical Polish)等の方法で、キャップ材91乃至93の上面まで絶縁膜を研磨して平坦化する。図3(b)に示すように、素子分離領域21乃至24として埋め込まれる絶縁性埋め込み材は、浮遊ゲート41乃至43の端部に自己整合的に埋め込まれる。次に、図3(c)に示すように、キャップ材91乃至93を除去する。このことにより、素子分離領域21乃至24で取り囲まれた溝部11を形成する。次に、浮遊ゲート電極の第2の導電体51乃至53となる薄い多結晶シリコン膜5を堆積する。この多結晶シリコン膜5の膜厚は3nm以上250nm以下の範囲で、例えば20nm程度である。ここまでで、これまでの製造方法は基本的に第1の実施形態と同じである。

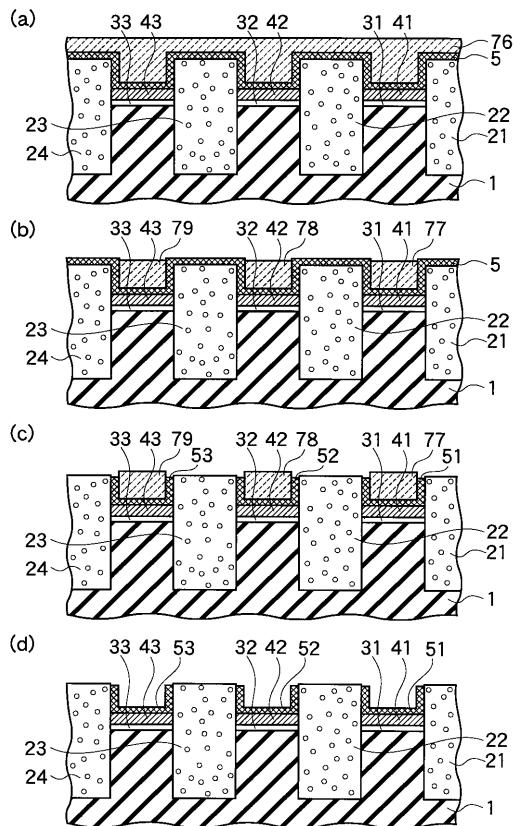

【0059】

次ぎに、図12(a)に示すように、例えばフォトレジスト76を多結晶シリコン膜5の上の全面に塗布する。図12(b)に示すように、レジスト76をエッチバックする。このことにより、素子分離領域21乃至24の上に位置する多結晶シリコン膜5を露出させる。エッチバックされたレジスト77乃至79は、溝11の中に埋め込まれる。図12(

10

20

30

40

50

c) に示すように、例えばRIE法によるエッチバックで、素子分離領域21乃至24の上の多結晶シリコン膜5を除去する。浮遊ゲート電極の第2の導電体51乃至53が形成される。図12(d)に示すように、レジスト77乃至79を剥離する。

#### 【0060】

最後に、第2の導電体51乃至53と、素子分離領域21乃至24の上に、浮遊ゲートと制御ゲート間の絶縁膜6を形成する。そして、図11(a)に示すように、制御ゲート7となる多結晶シリコン膜を堆積する。

#### 【0061】

(第2の参考例の第1の変形例) 第2の参考例の第1の変形例の半導体装置は、図11(b)に示すように素子分離領域21乃至24の上面の高さが、第2の導電体51乃至53の最上部の高さより低い。そして、素子分離領域21乃至24の上面の高さが、第2の導電体51乃至53の最下部の高さより高いか等しい。このことにより、図9のエッチング残り116を生じさせることがない。素子分離領域21乃至24の上方に配置される制御ゲート7と、第2の導電体51乃至53とが、絶縁膜6を介して対向する。すなわち、第2の導電体51乃至53の外側の側面部でも、第2の導電体51乃至53が制御ゲート7と絶縁膜6を介して対向する。このことにより、第2の参考例の第1の変形例は、第2の参考例に比較して、制御ゲート7と浮遊ゲート51乃至53の間の容量結合をより高くできる。

#### 【0062】

次に、第2の参考例の第1の変形例の半導体装置の製造方法について説明する。図4(a)に示す第2の導電体5を堆積するところまでは第1の実施の形態と第2の参考例と同じである。次に、図13(a)に示すように、シリコン酸化膜120をCVD法で堆積する。図13(b)に示すように、シリコン酸化膜120のエッチバックを行う。素子分離領域21乃至24の上方の第2の導電体5が露出する。シリコン酸化膜121乃至123は、溝11の内部に埋め込まれる。この時、溝11の内のシリコン酸化膜121乃至123の残り膜厚dは、後で素子分離領域21乃至24をエッチング除去する深さよりも薄いことが望ましい。

#### 【0063】

次に、図13(c)に示すように、CMP法あるいはエッチバック法により、素子分離領域21乃至24の上の第2の導電体5を除去する。第2の導電体5は第2の導電体51乃至53は分割される。CMP法によれば、溝11の側面に残る第2の導電体の高さを良好に制御できる。

#### 【0064】

次ぎに、図13(d)に示すように、シリコン酸化膜121乃至123と素子分離領域21乃至24のエッチングを行う。このエッチングにより、溝11の内のシリコン酸化膜121乃至123を除去する。第2の導電体の上面を露出させる。そして、素子分離領域21乃至24を所望の深さまでエッチングする。この時、所望の深さよりも、シリコン酸化膜121乃至123の残り膜厚dが薄ければ、素子分離領域21乃至24のエッチングと同時にシリコン酸化膜121乃至123の除去ができる。このエッチングにより、第2の導電体51乃至53の外側面部のフィン状の突起が露出する。第2の導電体51乃至53の底面の全面が、第1の導電体41乃至43の上面の全面に接しているので、突起は倒れにくい。

#### 【0065】

最後に、図11(b)に示すように、素子分離領域21乃至24の上と、第2の導電体51乃至53の上に、絶縁膜6を形成する。絶縁膜6の上に制御ゲート7となる多結晶シリコン膜を堆積する。

#### 【0066】

(第2の参考例の第2の変形例) 第2の参考例の第2の変形例の半導体装置は、図11(c)に示すように、第2の導電体57乃至59が、素子分離領域124乃至127の上に配置される。このことにより、浮遊ゲート57乃至59と制御ゲート7の絶縁膜6を介し

10

20

30

40

50

て対向する部分の面積を、第2の参考例の半導体装置より広くできる。第2の参考例の第2の変形例は、第2の参考例に比較して、制御ゲート7と浮遊ゲート57乃至59の間の容量結合をより高くできる。

#### 【0067】

次に第2の参考例の第2の変形例の半導体装置の製造方法について説明する。図3(c)に示すキャップ材91乃至93を除去するところまでは第1の実施の形態と第2の参考例と同じである。次に、図14(a)に示すように、素子分離領域124乃至127をウェット(wet)エッチング等の等方性エッチングによりエッチングする。このエッチングにより、素子分離領域124乃至127は後退する。第1の導電体41乃至43の側方の素子分離領域124乃至127も除去される。溝11の幅は広がる。

10

#### 【0068】

次に、図14(b)に示すように、第2の導電体5を、素子分離領域124乃至127の上と、第1の導電体41乃至43の上に成膜する。特に、第2の導電体5は、第1の導電体41乃至43の側面の上にも成膜する。この後の製造方法は、図12(a)から図12(d)に示す第2の参考例の製造方法と同じである。すなわち、図14(c)に示すように、フォトレジスト77乃至79で、溝11の内部の第2の導電体57乃至59を保護しながら、第2の導電体57乃至59を分割する。このような工程により、素子分離領域124乃至127に第2の導電体57乃至59を張り出す形状を形成することができる。

#### 【0069】

(第2の参考例の第3の変形例)第2の参考例の第3の変形例の半導体装置は、図11(d)に示すように、第2の参考例の第1の変形例と第2の参考例の第2の変形例の特徴を兼ね備えている。第2の導電体57乃至59の外側の側面が、制御ゲートと絶縁物6を介して対向している。また、第2の導電体57乃至59が、素子分離領域124乃至127の上に配置され、素子分離領域124乃至127に張り出している。

20

#### 【0070】

素子分離領域124乃至127の上面の高さが、第2の導電体57乃至59の最上部の高さより低い。そして、素子分離領域124乃至127の上面の高さが、第2の導電体57乃至59の最下部の高さより高いか等しい。このことにより、図9のエッチング残り116を生じさせることができない。素子分離領域124乃至127の上方に配置される制御ゲート7と、第2の導電体57乃至59とが、絶縁膜6を介して対向する。このことにより、第2の参考例の第3の変形例は、第2の参考例に比較して、制御ゲート7と浮遊ゲート57乃至59の間の容量結合をより高くできる。第2の参考例の第3の変形例の半導体装置の製造方法は、第2の参考例の第1の変形例と第2の参考例の第2の変形例の製造方法に基づく。

30

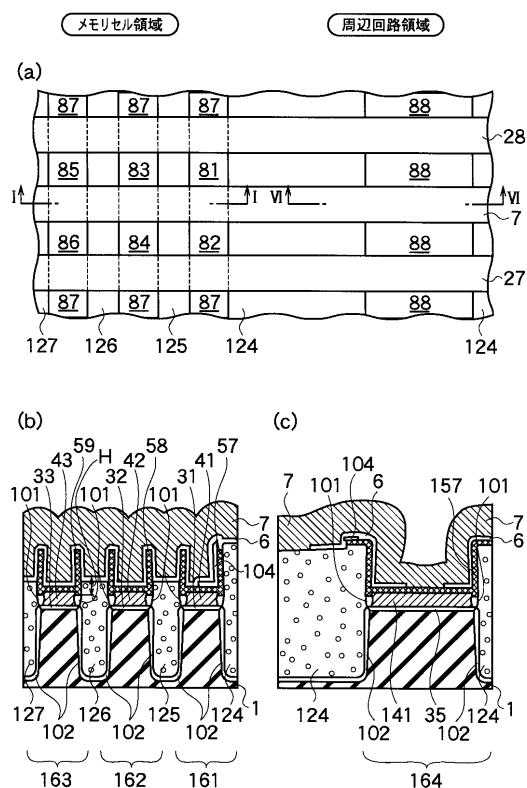

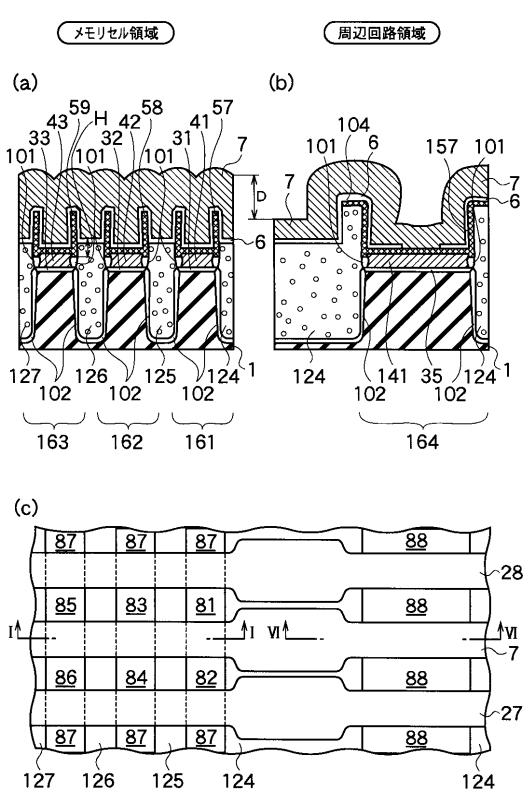

#### 【0071】

(第2の実施の形態)第2の実施の形態は、第2の参考例の、特に、第3の変形例を、さらに詳細に説明する。第2の実施の形態の半導体装置は、NAND構造の不揮発性の半導体記憶装置である。第2の実施の形態の半導体装置は、メモリセル領域と周辺回路領域の間の領域と、メモリセル領域の制御ゲート電極7の上面の段差が小さいことを特徴とする。なお、第2の実施の形態において、図15(b)の絶縁膜101、102も素子分離領域124乃至127とみなせる。このことにより、第2の実施の形態の素子分離領域101、102、124乃至127の形状は、図11(d)の第2の参考例の第3の変形例の素子分離領域124乃至127の形状と同じであると考えられる。

40

#### 【0072】

図15(a)は、第2の実施の形態の半導体装置の上方からの透視図である。図15(a)の左側がメモリセル領域である。図15(a)の右側が周辺回路領域である。図15(b)は図15(a)のI-I方向の断面図である。図15(c)は図15(a)のV1-V1方向の断面図である。互いに等しい幅の制御ゲート28、7、27が等間隔に平行に横方向に配置されている。素子分離領域124乃至127が制御ゲート28、7、27の下方において、平行に縦方向に配置されている。メモリセル領域において、素子分離領域

50

124乃至127は、例えば互いに等しい幅を有し、等間隔に配置されることが、素子分離耐圧を揃え、チャネルコンダクタンスを揃え、均一なデバイスを形成するのに望ましい。メモリセル162、163とダミーセル161のソース／ドレイン領域81乃至87は、上方に制御ゲート28、7、27と、素子分離領域124乃至127が配置されていない領域に設けられる。周辺回路164のソース／ドレイン領域88は、上方に制御ゲート28、7、27と、素子分離領域124が配置されていない領域に設けられる。

#### 【0073】

素子分離領域124乃至127の上方に形成された制御ゲート電極7の底面は、第1の導電体41乃至43の上面よりも積み上げ方向の上方に配置される。第2の導電体58、59の2つの外側の側面の最大の距離は、第1の導電体42、43の2つの端面の距離よりも大きい。第2の導電体58、59の下面すなわち外側の側面の下端は、第1の導電体42、43の上面よりも下に設けられる。第2の導電体58、59は、第1の導電体42、43の上で連結された一体の導電体である。第2の導電体58、59の2つの外側の側面の距離は、この側面の上部ほど狭い。制御ゲート電極7は、ブロック絶縁膜6を介して第2の導電体58、59の上面と側面に対向する。素子分離領域125は、第2の導電体57に接する。素子分離領域124も、第2の導電体57に接する。素子分離領域124は、素子分離領域125より幅が広い。素子分離領域124の上面の高さは、素子分離領域125の上面の高さより高い。

#### 【0074】

ダミーセル161は、複数のメモリセル162、163からなるメモリセルアレイと周辺回路164との間に形成される。ダミーセル161は、メモリセル162、163の動作やプロセス制御性を安定させる。ダミーセル161は、メモリセル162、163とほぼ同等の構造を有し、メモリセル162、163と隣接して形成される。ダミーセル161は1つに限らず、勿論複数形成しても構わない。また、記号をわかりやすく表示する便宜上、ダミーセル161と周辺回路164の間を分離して示した。ダミーセル161と周辺回路164は、素子分離領域124を同一として連続して形成される。周辺回路164とは、メモリセル162、163以外で、MISトランジスタとして機能するデバイスのことである。

#### 【0075】

p型シリコン基板1のボロン(B)の不純物濃度は、 $10^{14}$  cm<sup>-3</sup>以上で $10^{19}$  cm<sup>-3</sup>以下である。p型シリコン基板1の上に、例えば、3nm以上で15nm以下の厚さのシリコン酸化膜またはオキシナイトライド膜であるゲート絶縁膜31乃至33、35が設けられている。ゲート絶縁膜31乃至33、35の上には、ポリシリコンからなる第1の導電体41乃至43、141が設けられている。第1の導電体42と43は、メモリセル163、162の浮遊ゲートの第1の電荷蓄積層として機能する。第1の導電体41乃至43、141には、例えばリン(P)または砒素(As)が不純物濃度で $10^{18}$  cm<sup>-3</sup>以上で $10^{21}$  cm<sup>-3</sup>以下の範囲で添加されている。第1の導電体41乃至43、141の厚さは10nm以上で500nm以下の範囲である。また、ゲート絶縁膜31乃至33、35と第1の導電体41乃至43、141は、段差のない平面上に設けられている。このことにより、メモリセル162と163の電気特性のセル間のばらつきを均一にすることができる。第1の導電体41乃至43、141の側面には、浮遊ゲート側壁酸化膜101が設けられている。

#### 【0076】

第1の導電体41乃至43、141と、浮遊ゲート側壁酸化膜101の上には、第2の導電体57乃至59と157が設けられている。この第2の導電体57乃至59と157は、例えばリンまたは砒素を不純物として不純物濃度 $10^{18}$  cm<sup>-3</sup>以上で $10^{21}$  cm<sup>-3</sup>以下の範囲で添加されているポリシリコンである。第2の導電体57乃至59の厚さは、3nm以上で500nm以下の範囲である。好ましくは、第2の導電体57乃至59の厚さは、第1の導電体41乃至43の厚さの半分よりも小さく、例えば、3nm以上で100nm以下の範囲である。

10

20

30

40

50

## 【0077】

この範囲においても、制御ゲート間の容量結合を小さくすることができない。また、データの読み出し時間や書き込み時間を著しく長くするほどに、抵抗成分が大きくなることもない。一方、セル間の結合容量を小さくすることができる。

## 【0078】

第2の導電体57乃至59は、第1の導電体41乃至43の上面の全面と、対向する側面の上部に接している。すなわち、第2の導電体57乃至59は、第1の導電体41乃至43の上面および側面を覆っている。また、第2の導電体57乃至59は、図1(b)の導電体51、52と異なり、一体の導電体である。これらのことにより、第2の導電体57乃至59と第1の導電体41乃至43は、より広い面積で密着するため、第2の導電体57乃至59の内部応力や、第2の導電体57乃至59に対する外力による剥離を防止することができる。

## 【0079】

第2の導電体58、59は、メモリセル162、163の浮遊ゲートの第2の電荷蓄積層として機能する。第2の導電体58、59の外側面部の上面は、内部の上面より高い。第2の導電体58、59は大文字のHの形状を有している。第2の導電体58、59は、外側の右側に第1の側面と、外側の左側に第2の側面を有している。第2の導電体58、59は、内側の右側に第3の側面と、内側の左側に第4の側面を有している。第2の導電体58、59の外側の第1と第2の側面の下部は素子分離領域125乃至127に接している。第2の導電体58、59の外側の第1と第2の側面と内側の第3と第4の側面の上部の上にはブロック絶縁膜6が設けられている。第2の導電体58、59の内部の上面にもブロック絶縁膜6が設けられている。このブロック絶縁膜6の上には制御ゲート7が設けられている。ブロック絶縁膜6は、例えば、厚さ5nm以上で30nm以下の範囲のシリコン酸化膜またはオキシナイトライド膜、または、それぞれの厚さが2nm以上で100nm以下の範囲のシリコン酸化膜/シリコン窒化膜/シリコン酸化膜からなる積層膜(ONO膜)である。制御ゲート7は、例えばリン、砒素、またはボロンを不純物として不純物濃度 $10^{17}$ cm<sup>-3</sup>以上で $10^{21}$ cm<sup>-3</sup>以下の範囲で添加されているポリシリコンである。又、制御ゲート7は、タングステンシリサイド(WSi)とポリシリコンとのスタッカ構造であってもよい。また、ニッケルシリサイド(NiSi)、モリブデンシリサイド(MoSi)、チタニウムシリサイド(TiSi)、コバルトシリサイド(CoSi)とポリシリコンのスタッカ構造であってもよい。制御ゲート7の厚さは、10nm以上で500nm以下の範囲の厚さである。素子分離領域125乃至127の上方に位置するブロック絶縁膜6および制御ゲート7は、第1の導電体42、43の上面よりも上方に形成されている。同様に、素子分離領域125乃至127の上方に位置するブロック絶縁膜6および制御ゲート7は、第2の導電体58、59の最下面よりも上方に形成されている。すなわち、図15(b)の高さHは、正の値になる。このことにより、図9で説明した制御ゲート7のエッチング残り116が発生することができない。

## 【0080】

シリコン基板1の上には、ライナー絶縁膜102を介して素子分離領域124乃至127が設けられている。素子分離領域124乃至127は、例えば、シリコン酸化膜からなる。素子分離領域124乃至127が形成されていないシリコン基板1の表面上に、ゲート絶縁膜31乃至33、35と第1の導電体41乃至43、141と第2の導電体57乃至59が自己整合的に設けられている。

## 【0081】

第2の実施の形態では、第2の導電体58、59が一体の導電体である。このことにより、第1の導電体42、43と第2の導電体58、59との接触面積が増大する。このことによって、第1の導電体42、43と第2の導電体58、59の間の容量またはコンダクタンスを大きくできる。よって、第2の導電体58、59の電位変動に対して、第1の導電体42、43の電位変動を大きくできる。また、第1の導電体42、43と制御ゲート電極7とのカップリング比を向上させることができる。

10

20

30

40

50

## 【0082】

第2の導電体58、59の外側面部の凸部は、内部に傾いている。

凸部の対向する内側の側面の距離は、凸部の上方ほど狭い。また、第2の導電体58、59の外側面部の凸部の対向する外側の側面の距離は、凸部の上方ほど大きい。このことにより、素子分離領域125乃至127で挟まれたシリコン基板1の幅で決まるトランジスタセルのチャネル幅を変えることなく一定にしたままで、隣接するメモリセルの第2の導電体58、59間の容量結合を小さくすることができる。よって、チャネル幅によって決まるトランジスタの電流駆動能力を一定に保ったままで、隣接するメモリセル間の容量結合によるしきい値変化を小さくすることができる。また、隣接するメモリセルの第2の導電体58、59間の短絡による不具合を減少させることができる。

10

## 【0083】

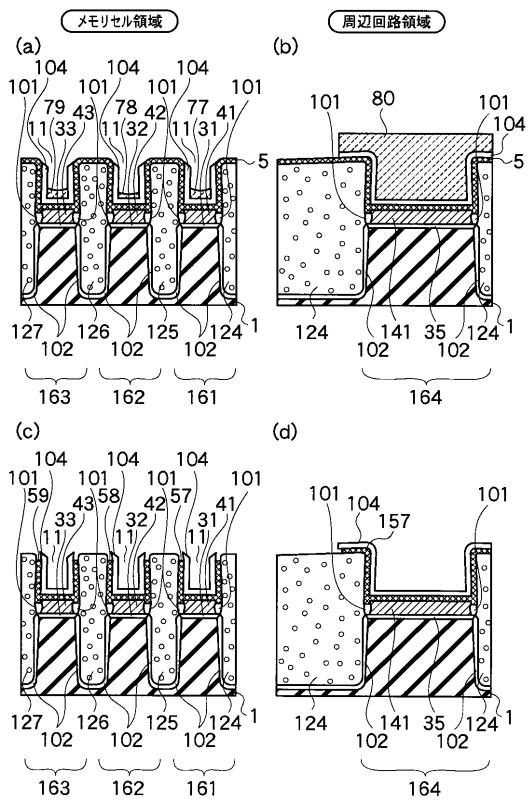

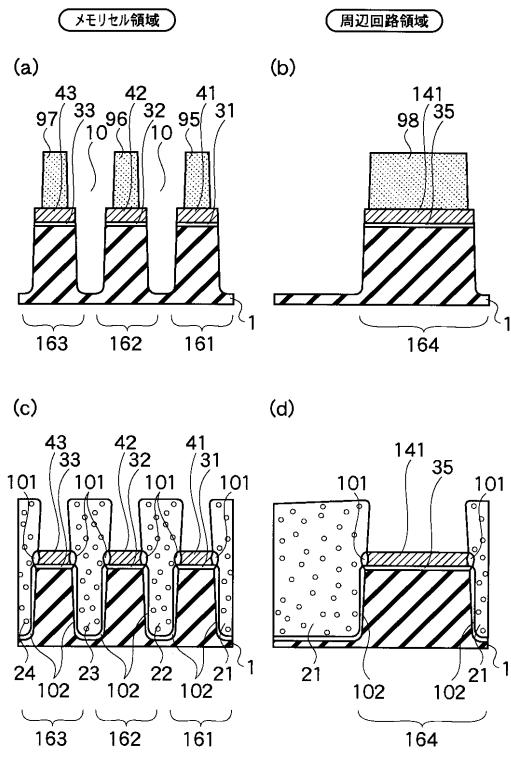

次に、第2の実施の形態の半導体装置の製造方法を説明する。第2の実施の形態の半導体装置の製造方法では、半導体装置のメモリセル領域と周辺回路領域を製造する方法を説明する。製造方法の途中までは、基本的には第1の実施形態の製造方法と同じである。図16乃至図20に第2の実施の形態の半導体装置の製造途中の断面図を示す。図16乃至図20の左側の(a)と(c)がメモリセル領域の断面図である。図16乃至図20の右側の(b)と(d)が周辺回路領域の断面図である。

## 【0084】

まず、図16(a)(b)に示すように、メモリセル162、163、ダミーセル161と周辺回路164の素子分離用の溝部10と、第1の浮遊ゲート(電荷蓄積層)41乃至43、周辺回路のゲート電極141及び活性領域1は自己整合的に加工される。第1の浮遊ゲート41乃至43、周辺回路のゲート電極141は、活性領域1の側面には形成されない。これにより、セル161乃至163の微細化を実現すると共に、活性領域1のコーナー部を覆うように浮遊ゲート42、43が形成される事が無い為、電界集中の効果によるメモリセル特性のバラツキを抑制する事ができる。

20

## 【0085】

p型シリコン基板1上に、絶縁膜31乃至33、35をシリコン基板1の酸化または窒化により形成する。絶縁膜31乃至33、35の厚さは、3nm以上で15nm以下の範囲の厚さである。この絶縁膜31乃至33、35は、不揮発性メモリセル162、163のトンネル(Tunnel)酸化膜32、33と、ダミーセル161の絶縁膜31と、周辺回路のゲート絶縁膜35として機能する。

30

## 【0086】

次に、絶縁膜31乃至33、35の上に、第1の導電体41乃至43、141を成膜する。第1の導電体41乃至43、141の材料は、多結晶シリコンであり、膜厚は、10nm以上で500nm以下の範囲の膜厚である。第1の導電体41乃至43、141は、メモリセル162、163の第1の浮遊ゲート42、43と、ダミーセル161の導電体41と、周辺回路の第1のゲート電極141として機能する。

## 【0087】

第1の導電体41乃至43、141の上に、キャップ材91乃至94として機能するシリコン窒化膜を堆積する。このキャップ材91乃至94の膜厚によって、後で形成する第2の浮遊ゲート57乃至59、すなわち、第2の電荷蓄積層の高さが決まる。このキャップ材91乃至94の膜厚は100nm以上で500nm以下の範囲の膜厚である。

40

## 【0088】

次に、図16(a)(b)に示すように、リソグラフィ工程とエッティングにより、素子分離領域124乃至127となる領域に溝10を掘る。具体的には、素子分離領域124乃至127となる領域以外をマスクするレジストパターンを形成する。このレジストパターン及びこのレジスタパターンでパターニングされたキャップ材91乃至94をマスクに、キャップ材91乃至94、第1の導電体41乃至43、141、絶縁膜31乃至33、35とシリコン基板1を順次エッティングする。素子分離用の溝10と、第1の導電体41乃至43、141、キャップ材91乃至94は自己整合的に形成される。シリコン基板1中

50

の素子分離用の溝 10 の深さは、50 nm 以上で 500 nm 以下の範囲の深さである。溝 10 の側壁の形状は順テープであることが好ましい。特に、キャップ材 91 乃至 94 の露出する側壁が順テープであることが好ましい。このことにより、制御ゲート電極のエッチング残りを発生させることなくメモリセルを分離することができる。

#### 【0089】

素子分離用の溝 10 を掘った後、必要に応じて、溝 10 の内壁の上に薄いライナー酸化膜 102 を成膜する。ライナー酸化膜 102 は、シリコン基板 1 を熱酸化して形成する。ライナー酸化膜 102 の膜厚は、3 nm 以上で 15 nm 以下の範囲の膜厚である。この熱酸化の際に、第 1 の導電体 41 乃至 43、141 の側面も酸化され、シリコン酸化膜 101 が形成される。キャップ材 91 乃至 94 はほとんど酸化されない。キャップ材 91 乃至 94 よりも、第 1 の導電体 41 乃至 43、141 の方が酸化速度が速い。図 16 (c) (d) に示すように、第 1 の導電体 41 乃至 43、141 の幅は、キャップ材 91 乃至 94 の幅よりも狭くなる。

#### 【0090】

次に、素子分離用の溝 10 に、例えば高密度プラズマ (HDP : High Density plasma) 法で形成したシリコン酸化膜 21 乃至 24 を埋め込む。シリコン酸化膜 21 乃至 24 は、減圧 (L.P.) CVD 法で形成しても良い。図 16 (c) (d) に示すように、シリコン酸化膜 21 乃至 24 を堆積後、CMP 法で、キャップ材 91 乃至 94 を CMP 法のストップ材としてシリコン酸化膜 21 乃至 24 を平坦化する。これにより、素子分離領域 21 乃至 24 は、キャップ材 91 乃至 94 とシリコン酸化膜 101 の側面に自己整合的に形成される。

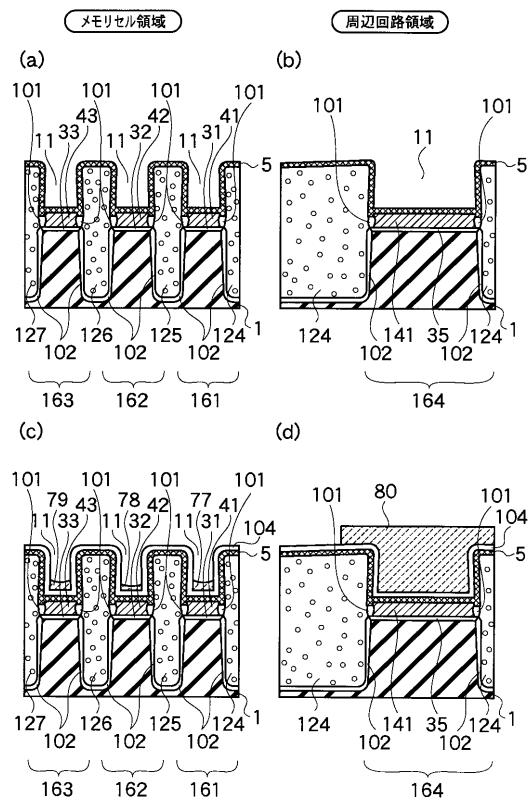

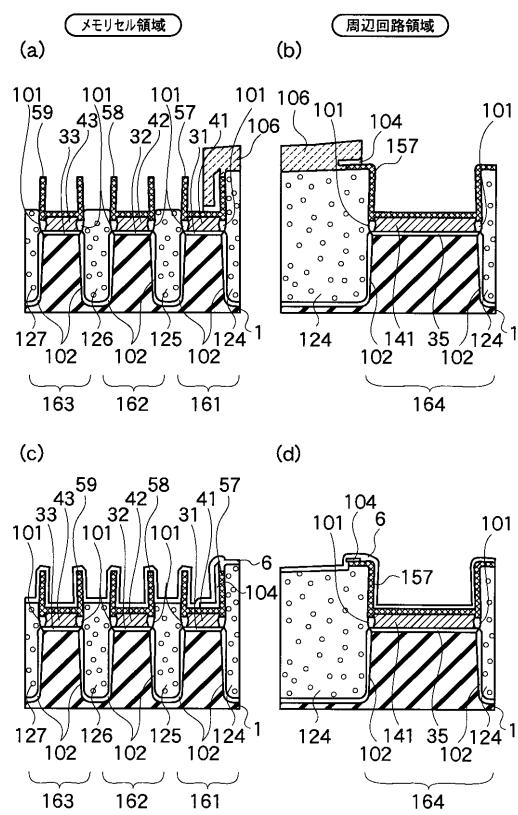

#### 【0091】

図 17 (a) (b) に示すように、キャップ材 91 乃至 94 を選択的に除去する。このことにより、素子分離領域 21 乃至 24 で取り囲まれた溝部 11 を形成する。ここまで工工程は基本的には第 1 の実施形態の半導体装置の製造方法を適用させることができる。この溝部 11 の形成によって、第 1 の導電体 41 乃至 43、141 の表面は、空気に晒される。このため、いわゆる自然酸化膜 103 が第 1 の導電体 41 乃至 43、141 の表面上に成膜される。自然酸化膜 103 の膜厚は、0.3 nm から 2 nm の範囲の膜厚である。この酸化膜 103 の膜厚は、ついで行われる第 2 の導電体 5、57 乃至 59 の堆積までの放置時間に依存する。この酸化膜 103 は、膜厚の均一性や制御性が劣るため、均一なカップリング比を得るために取り除く必要がある。フッ酸によるウェットエッチングにより酸化膜 103 を、取り除く。フッ酸によるウェットエッチングを行うと、図 17 (c) (d) に示すように、シリコン酸化膜で形成された素子分離領域 21 乃至 24 の上部がエッチングされ、その上部の幅が狭まった素子分離領域 124 乃至 127 が形成される。溝部 11 の幅が広がる。酸化膜 101 も同時にエッチングされる。ここで、酸化膜 101 もエッチングされるのは、第 1 の導電体 41 乃至 43、141 の幅はキャップ材 91 乃至 94 の幅 1 よりも狭いので、キャップ材 91 乃至 94 を除去すると、酸化膜 101 が露出するからである。

#### 【0092】

次に、図 18 (a) (b) に示すように、第 1 の導電体 41 乃至 43、141 と絶縁膜 101 と、素子分離領域 124 乃至 127 の上に第 2 の導電体 5 を成膜する。第 2 の導電膜 5 の材料は、多結晶シリコン膜であり、膜厚は、3 nm 以上で 100 nm 以下の範囲の膜厚である。特に、10 nm 以上で 30 nm 以下の範囲の膜厚が好ましい。この範囲であれば、セル間の容量結合は十分に小さく、電荷蓄積電極の内部の分布抵抗も十分に小さい。第 2 の導電体 5 は、第 2 の電荷蓄積電極 (浮遊ゲート) 58、59 として機能する。

#### 【0093】

ついで、第 2 の導電体 5 の上に、側壁マスク絶縁膜 104 を成膜する。側壁マスク絶縁膜 104 としては、例えば、テトラエトキシシラン (TEOS) を原料とするシリコン酸化膜や HTO (High Temperature Oxide) 膜を用いる。側壁マスク絶縁膜 104 の膜厚は、3 nm 以上で 100 nm 以下の範囲の膜厚で、例えば、10 nm 程度の膜厚である。フ

10

20

30

40

50

オトレジスト 77 乃至 80 を塗布する。次に、部分露光する。メモリセル 162、163 とダミーセル 161 の上のレジストを露光し、周辺回路 164 の上のレジストを露光しない。この露光の際に、露光量を調整することにより、図 18 (c) (d) に示すように、メモリセル 162、163 およびダミーセル 161 の溝部 11 の底部にレジスト 77 乃至 79 を残す。周辺回路 164 の活性領域とその周辺の素子分離領域 124 はレジスト 80 で覆う。この露光の際、メモリセル 162、163 およびダミーセル 161 のピッチよりも、波長が長い、例えば安価な i 線のレジストを用いることができる。このことにより、メモリセル 162、163 およびダミーセル 161 の溝部 11 の底部にあるレジスト 77 乃至 79 までは露光されない。この露光の条件は、メモリセル 162、163 およびダミーセル 161 の活性領域にレジストが残ることと、メモリセル 162、163 およびダミーセル 161 の素子分離領域 124 乃至 127 上部のレジストは露光され剥離されることである。10

#### 【0094】

次に、図 19 (a) (b) に示すように、レジスト 77 乃至 80 をマスクとして、異方性エッチングを行い、側壁マスク絶縁膜 104 を除去する。ここで、第 2 の導電体 5 の溝部 11 の内部で対向する側面の間隔は、溝部 11 の上部ほど狭くなっている。よって、溝部 11 の側壁に形成された絶縁膜 104 は、素子分離領域 124 乃至 127 の上面の上に設けられた第 2 の導電体 5 にマスクされ、エッチングされずに残る。レジスト 77 乃至 79 の厚さのばらつきとは無関係に、側壁マスク絶縁膜 104 の最大高さが決定される。側壁マスク絶縁膜 104 の最大高さは、異方性エッチングのエッチング量によって決定される。側壁マスク絶縁膜 104 の最大高さを、均一な高さで制御性良く形成することができる。20

#### 【0095】

次に、レジスト 77 乃至 80 を剥離する。側壁マスク絶縁膜 104 をマスクとして、素子分離領域 124 乃至 127 をエッチングストッパーとして、図 19 (c) (d) に示すように、第 2 の導電体 5 をエッチングする。素子分離領域 124 乃至 127 の上の第 2 の導電体 5 は除去される。このことにより、第 2 の導電体 57 乃至 59、157 は互いに分離する。このエッチングとしては、エッチングダメージの少ない等方性エッチングを用いる。勿論、ダメージが問題とならない場合には、側壁マスク絶縁膜 104 をマスクとして異方性エッチングを行っても良い。異方性エッチングでは、図 19 (d) に示すような、第 2 の導電膜 157 の横方向のエッチング量は小さくできる。なお、第 2 の導電体 57 乃至 59、157 に直接レジスト 77 乃至 80 が接しないため、レジスト 77 乃至 80 から第 2 の導電体へのナトリウム (Na) や鉄 (Fe)、クロム (Cr) などの金属汚染や炭素汚染を防ぐことができる。また、第 2 の導電体 57 乃至 59、157 のエッチングに CMP 法を用いていない。このことにより、CMP 法に特有のスクラッチによる残差残りや面積が広い部分のオーバーポリッシュ (over polish) 現象が生じない。30

#### 【0096】

レジスト 106 を全面塗布する。ダミーセル 161 の一部と、周辺回路の素子分離領域 124 を覆うようにレジスト 106 を露光し、パターニングする。この露光では、メモリセルの溝部 11 の底も完全に露光されるような条件を選ぶ。図 20 (a) (b) に示すように、レジスト 106 をマスクとして、例えば等方性エッチングで側壁マスク絶縁膜 104 を剥離する。引き続き、レジスト 106 をマスクとして、異方性エッチングで素子分離絶縁膜 124 乃至 127 をエッチバックする。素子分離領域 124 乃至 127 の上面の高さは、第 1 の導電体 41 乃至 43 の上面よりも高く配置する。また、素子分離領域 124 乃至 127 の上面の高さは、第 2 の導電体 57 乃至 59 の下面よりも高く配置する。すなわち、素子分離領域 124 乃至 127 の側面と第 2 の導電体 57 乃至 59 の側面は接する。さらに、レジスト 106 が第 2 の導電体 57 乃至 59、157 の端面にのみ接触する。このため、第 2 の参考例の図 12 (a) のように、第 2 の導電体 5 の全面にレジスト 76 を塗布するよりも、レジスト 106 からの第 2 の導電体 57 乃至 59、157 への汚染を抑制することができる。また、第 2 の導電体 57 乃至 59 の端部の凸部が露出するが倒れる40

ことはない。これは、第2の導電体57乃至59の底部の面積が広いからである。

【0097】

レジスト106を剥離する。第2の導電体57乃至59、157の表面は、空気に晒されるため、いわゆる自然酸化膜が0.3nm~2nm程度成長する。この自然酸化膜の膜厚は、ついで行われるブロック絶縁膜6の堆積までの時間に依存する。従って、この自然酸化膜の膜厚は、均一性や制御性が劣る。浮遊ゲートと制御ゲートの均一なカップリング比を得るためにには、この自然酸化膜を取り除くことが必要である。そこで、例えば、この自然酸化膜のフッ酸によるエッティング処理を行う。

【0098】

図20(c)(d)に示すように、第2の導電体57乃至59、157の露出する表面と、素子分離領域124乃至127の上に、ブロック絶縁膜6を堆積する。ブロック絶縁膜6としては、例えば、厚さ5nmから30nmの範囲のシリコン酸化膜またはオキシナイトライド膜、または、それぞれの厚さが2nmから100nmの範囲のシリコン酸化膜/シリコン窒化膜/シリコン酸化膜の積層構造を有するONO膜が用いられる。

【0099】

次に、レジストを塗布し、ホトリソグラフィとエッティングを行う。このことにより、周辺回路164の第2の導電体157の上と、ダミーセル161と周辺回路164の間の素子分離領域124の上のブロック絶縁膜6を取り除く。制御ゲート電極7を、ブロック絶縁膜6と第2の導電体157の上に堆積する。制御ゲート電極7としては、例えはリン、砒素、またはボロンを不純物として、不純物濃度1017cm<sup>-3</sup>以上で1021cm<sup>-3</sup>以下の範囲で添加されているポリシリコンを用いる。または、制御ゲート電極7としては、タングステンシリサイド(WSi)とポリシリコンとのスタック構造、または、NiSi, MoSi, TiSi, CoSiとポリシリコンのスタック構造であってもよい。制御ゲート電極7の膜厚は、10nm以上で500nm以下の範囲の膜厚である。この制御ゲート電極7の膜厚は、第2の導電体57乃至59の端部の凸部の最大間隔の1/2以上とする。このことにより、第2の導電体57乃至59の凹部を埋め、凸部の上方に平坦化した制御ゲート電極7の上面を設けることができる。そして、制御ゲート電極7のリソグラフィ余裕を確保することができる。

【0100】

最後に、第1の参考例の製造方法と同様に、制御ゲート電極7、ブロック絶縁膜6、電荷蓄積電極となる第1と第2の導電体42、43, 58, 59を半導体表面内のパターンで線状に異方性エッティングで加工する。図15(a)に示すような、制御ゲート電極7、27、28に分割する。ここで、第2の導電体57乃至59の周辺部の凸部の間隔は、積み上げ方向に向かって狭くなる。このことにより、制御ゲート7の加工時の異方性エッティングの際に制御ゲート電極7のエッティング残りを減少させることができる。ソースドレイン領域81乃至88を制御ゲート電極7、27、28の両側に形成する。

【0101】

一方、図21(a)(b)(c)は、第2の実施の形態の製造工程で、図20(a)(b)に示されるレジスト106のパターニングプロセスと、レジスト106によるマスクエッティングプロセスを省略した場合の半導体装置の断面図と上面図である。レジスト106によるマスクエッティングプロセスを省略すると、周辺回路164とダミーセル161の間の広い素子分離領域124がエッチバックされる。このエッチバックにより、メモリセル162、163の間の狭い素子分離領域125乃至127も共にエッチバックされるため、素子分離領域124乃至127の上面の高さはほぼ等しい。すなわち、一見すると、良好な平坦化がなされた状態である。しかし、図21(a)(b)に示すように、制御ゲート電極7を堆積すると、メモリセル領域の上面と、ダミーセル161と周辺回路164の間の広い素子分離領域124の上面とに、第2の導電体57乃至59の外側面部の凸部の高さ程度の段差Dが形成される。この段差Dにより、図21(c)に示すように、制御ゲート電極7、27、28の線幅が、広い素子分離領域124の上において、太くなる。制御ゲート電極7、27、28の線幅が太くなることにより、制御ゲート電極7、27、

10

20

30

40

50

28の間で短絡が生じやすくなる場合が考えられた。あるいは、その段差Dによって、制御ゲート電極7、27、28を加工するリソグラフィの余裕が大幅に縮小することがわかつた。このことにより、制御ゲート電極7、27、28の断線や、短絡を生じやすくなる場合が考えられた。

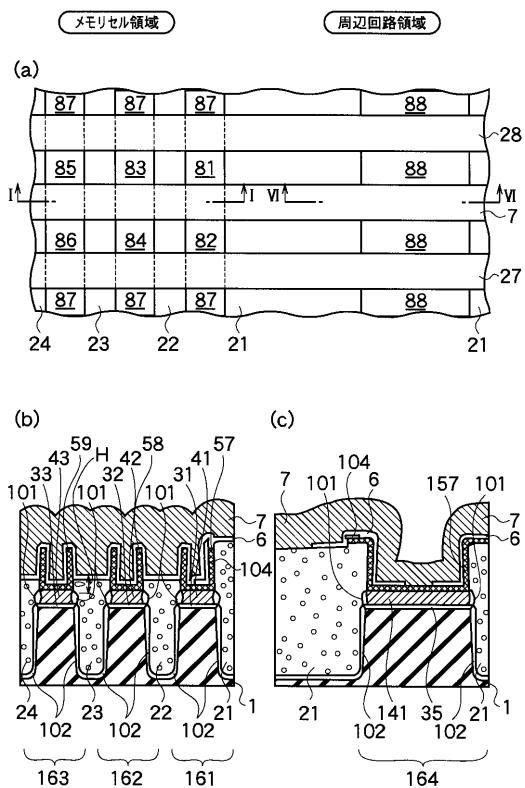

#### 【0102】

これに対し、第2の実施の形態では、制御ゲート電極7、27、28を加工するリソグラフィにおいて、段差Dを小さくする。このために、あえて、図20(a)(b)に示すように、広い素子分離領域124の上面の高さを、素子分離領域125乃至127の上面の高さより高くする。このことにより、段差Dが小さくできるので、制御ゲート電極7、27、28を加工するリソグラフィの余裕の幅が広い。そして、制御ゲート電極7、27、28の断線や、短絡が生じにくくなる。10

#### 【0103】

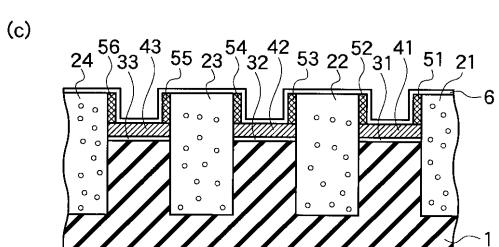

(第2の実施の形態の変形例) 第2の実施の形態の変形例は、第2の参考例の第1の変形例を、さらに詳細に説明する。第2の実施の形態の変形例の半導体装置は、メモリセル領域と周辺回路領域の間の領域と、メモリセル領域の制御ゲート電極7の上面の段差が小さいことを特徴とする。また、第2の実施の形態の変形例の半導体装置は、図9に示す制御ゲート電極7のエッチング残り116を生じさせない。このために、第2の実施の形態の変形例では、図22(b)(c)に示すように、第2の導電体57乃至59、157は、第1の導電体41乃至43、141の上面のみの上に形成される。そして、第2の導電体57乃至59、157の最大幅は、第1の導電体41乃至43、141の幅よりも小さい。20。すなわち、第2の導電体57乃至59の2つの外側の側面の最大の距離は、第1の導電体41乃至43の2つの端面の距離よりも小さい。

#### 【0104】

図22(a)は、第2の実施の形態の変形例の半導体装置の上方からの透視図である。図22(a)の左側がメモリセル領域である。図22(a)の右側が周辺回路領域である。図22(b)は図22(a)のI-I方向の断面図である。図22(c)は図22(a)のV1-V1方向の断面図である。互いに等しい幅の制御ゲート28、7、27が等間隔に平行に横方向に配置されている。素子分離領域21乃至24が制御ゲート28、7、27の下方において、平行に縦方向に配置されている。メモリセル領域において、素子分離領域21乃至24は、互いに等しい幅を有し、等間隔に配置される。30メモリセル162、163とダミーセル161のソース/ドレイン領域81乃至87は、上方に制御ゲート28、7、27と、素子分離領域21乃至24が配置されていない領域に設けられる。周辺回路164のソース/ドレイン領域88は、上方に制御ゲート28、7、27と、素子分離領域124が配置されていない領域に設けられる。

#### 【0105】

p型シリコン基板1の上に、ゲート絶縁膜31乃至33、35が設けられている。ゲート絶縁膜31乃至33、35の上には、第1の導電体41乃至43、141が設けられている。このことにより、メモリセル162と163の電気特性のセル間のばらつきを均一に40することができる。第1の導電体41乃至43、141の側面には、浮遊ゲート側壁酸化膜101が設けられている。第1の導電体41乃至43、141の上には、第2の導電体57乃至59と157が設けられている。一方、浮遊ゲート側壁酸化膜101と素子分離領域21乃至24の上には、第2の導電体57乃至59は配置されない。

#### 【0106】

第2の導電体57乃至59の底面の全面は、第1の導電体41乃至43の上面と接している。すなわち、第2の導電体57乃至59の底面の全面は、第1の導電体41乃至43の上面で覆われている。第2の導電体57乃至59も、一体の導電体である。より広い面積で第1の導電体と密着する。このため、第2の導電体57乃至59の内部応力や、第2の導電体57乃至59に対する外力による剥離を防止することができる。第2の導電体58、59は、外側面部において高く、内部において低い、いわゆる漢字の凹の形状を有している。第2の導電体58、59の外側の側面の下部は、素子分離領域21乃至24に接し50

ていることが好ましい。浮遊ゲート側壁酸化膜 101 は、素子分離絶縁膜 21 乃至 24 に接している。第 2 の導電体 58、59 の外側と内側の両側面の上にはブロック絶縁膜 6 が設けられている。第 2 の導電体 58、59 の内部の上面にもブロック絶縁膜 6 が設けられている。このブロック絶縁膜 6 の上には制御ゲート 7 が設けられている。素子分離領域 21 乃至 24 の上方に位置するブロック絶縁膜 6 および制御ゲート 7 は、第 1 の導電体 42、43 の上面（第 2 の導電体 58、59 の下面と一致する）よりも上方に形成されている。すなわち、図 22 (b) の高さ H は、正の値になる。このことにより、図 9 で説明した制御ゲート 7 のエッティング残り 116 が発生することがない。なお、素子分離領域 21 乃至 24 の上方に位置するブロック絶縁膜 6 および制御ゲート 7 は、第 1 の導電体 42、43 の下面よりも上方に形成されていてもよい。このことによっても、図 9 で説明した制御ゲート 7 のエッティング残り 116 が発生することがない。

10

#### 【0107】

シリコン基板 1 の上には、ライナー絶縁膜 102 を介して素子分離領域 21 乃至 24 が設けられている。素子分離領域 21 乃至 24 が形成されていないシリコン基板 1 の表面上に、ゲート絶縁膜 31 乃至 33、35 と第 1 の導電体 41 乃至 43、141 と第 2 の導電体 57 乃至 59、157 が自己整合的に設けられている。

#### 【0108】

第 2 の実施の形態例の変形例では、第 2 の導電体 58、59 が一体の導電体である。このことにより、第 1 の導電体 42、43 と第 2 の導電体 58、59 との接触面積が増大する。このことによって、第 1 の導電体 42、43 と第 2 の導電体 58、59 の間の容量またはコンダクタンスを大きくできる。

20

#### 【0109】

次に、第 2 の実施の形態の変形例の半導体装置の製造方法を説明する。第 2 の実施の形態の変形例の半導体装置の製造方法では、半導体装置のメモリセル領域と周辺回路領域を製造する方法を説明する。第 2 の実施の形態の製造方法の一部を変更する。図 23 に第 2 の実施の形態の変形例の半導体装置の製造途中の断面図を示す。図 23 の左側の (a) と (c) がメモリセル領域の断面図である。図 23 の右側の (b) と (d) が周辺回路領域の断面図である。

#### 【0110】

まず、第 2 の実施の形態の図 16 (a) (b) に示された構造が得られるまで、第 2 の実施の形態の製造方法を実行する。次に、キャップ材 91 乃至 94 を、熱焼酸でエッティングする。キャップ材 91 乃至 94 を厚さで 5 nm から 50 nm まで範囲で除去する。図 23 (a) (b) に示すように、このエッティングにより、キャップ材 95 乃至 98 を形成できる。この除去する厚さは、浮遊ゲート側壁酸化膜 101 を形成による第 1 の導電体 41 乃至 43、141 の減少量と、第 1 の導電体 41 乃至 43、141 の自然酸化膜を除去するときの素子分離領域 21 乃至 24 の減少量との和よりも大きい。次に、溝 10 の内壁の上に薄いライナー酸化膜 102 を成膜する。この後は、第 2 の実施の形態の製造方法で説明したのと同じ工程を行う。

30

#### 【0111】

図 23 (c) (d) に示すように、第 1 の導電体 41 乃至 43、141 の自然酸化膜を除去した直後で、第 2 の導電体 5 を堆積する直前においては、第 1 の導電体 41 乃至 43、141 の上面の上方にのみ開口が設けられている。第 1 の導電体 41 乃至 43、141 の側面は露出していない。このことにより、第 2 の導電体 57 乃至 59、157 が、第 1 の導電体 41 乃至 43、141 の側面から下に落ち込むことがない。これにより、制御ゲート電極 7 は、第 2 の導電膜 57 乃至 59、157 の上面または側面に選択的に形成される。一方、制御ゲート電極 7 は、第 2 の導電膜 57 乃至 59、157 の下方には配置されない。また、制御ゲート電極 7 の底面が、第 1 の電荷蓄積層 41 の底面よりも積み上げ方向で上方に形成されれば、第 2 の導電体 57 乃至 59、157 がマスクとなって、制御ゲート電極 7 のエッティング残り 116 が生じることがない。

40

#### 【0112】

本発明は上記実施形態に限られない。素子分離領域や絶縁膜の形成法は、シリコンをシリコン酸化膜やシリコン窒化膜に変換する酸化や窒化の方法に限られない。例えば、酸素イオンを堆積したシリコンに注入する方法や、堆積したシリコンを酸化する方法、シリコン窒化膜をシリコン酸化膜に転換する方法を用いてもよい。

#### 【0113】

また、半導体基板は、p型シリコン基板に限られない。半導体基板は、n型シリコン基板やSOI基板のシリコン層、またはシリコンゲルマニウム(SiGe)混晶、炭化シリコンゲルマニウム(SiGeC)混晶など、シリコンを含む単結晶の半導体基板であってもよい。なお、p型シリコン基板からn型シリコン基板に置き換える場合は、n型MOSFETの形成にかえて、p型MOSFETの形成に置き換える。すなわち、上述の実施形態のn型をp型に読み替え、p型をn型と読み替える。さらに、ドーピング不純物種の砒素(As)、リン(P)をインジウム(In)、ボロン(B)のいずれかと読み替えればよい。

10

#### 【0114】

また、制御ゲート電極および電荷蓄積領域はシリコン半導体、SiGe混晶、SiGeC混晶、TiSi、NiSi、CoSi、TaSi、WSi、MoSiなどのシリサイドやポリサイド、チタニウム(Ti)、アルミニウム(Al)、銅(Cu)、窒化チタニウム(TiN)、タングステン(W)などの金属を用いることができる。これらの材料は多結晶であってもよい。さらに、制御ゲート電極および電荷蓄積領域は、これら材料の積層構造であってもよい。また、制御ゲート電極および電荷蓄積領域には、アモルファスSi、アモルファスSiGe混晶、またはアモルファスSiGeC混晶を用いることができ、これらの積層構造にしてもよい。さらに、電荷蓄積領域はドット状に形成されても構わず、本発明が適用できることは言うまでもない。その他、本発明の要旨を逸脱しない範囲で、様々に変形して実施することができる。

20

#### 【0115】

#### 【発明の効果】

以上説明したように、本発明によれば、浮遊ゲートと制御ゲート間の容量を大きく維持したまま素子分離幅Wtを狭めることができ、半導体装置を提供できる。

#### 【0116】

また、本発明によれば、浮遊ゲートと制御ゲート間の容量結合を大きくしても浮遊ゲート間容量が大きくなりにくく、セル間の電気的干渉を防ぐことができる半導体装置の製造方法を提供できる。

30

#### 【図面の簡単な説明】

【図1】 第1の実施形態に係る半導体装置の上面図と断面図である。

【図2】 第1の実施形態に係る半導体装置の断面図である。

【図3】 第1の実施形態に係る半導体装置の製造工程毎の断面図(その1)である。

【図4】 第1の実施形態に係る半導体装置の製造工程毎の断面図(その2)である。

【図5】 第1の実施形態に係る製造途中の半導体装置(図4(c)に相当する工程における)の上方からの透視図である。

【図6】 第1の実施形態の第1の変形例に係る半導体装置の断面図である。

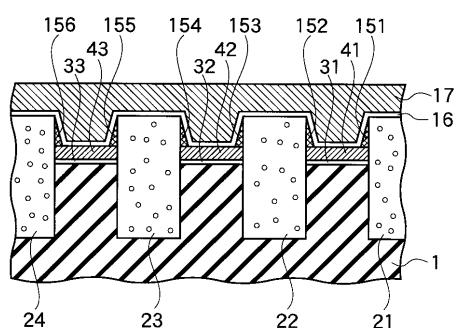

【図7】 第1の実施形態の第2の変形例に係る半導体装置の断面図である。

40

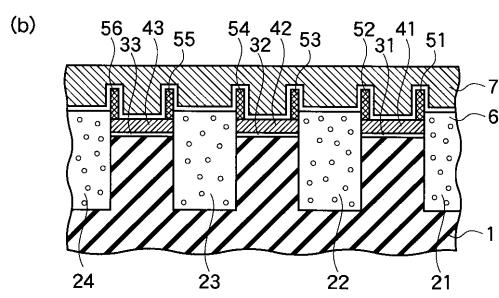

【図8】 第1の参考例に係る半導体装置の断面図である。

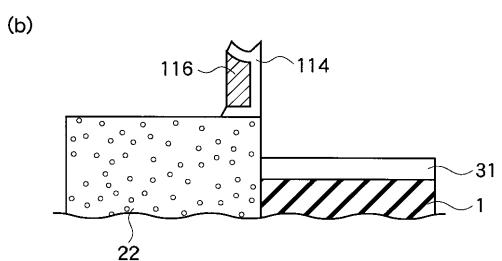

【図9】 第1の参考例に係る半導体装置の比較例の細部の断面図である。

【図10】 第1及び第1の参考例に係る半導体装置によって得られる浮遊ゲート間の結合容量低減の効果を説明するための図である。

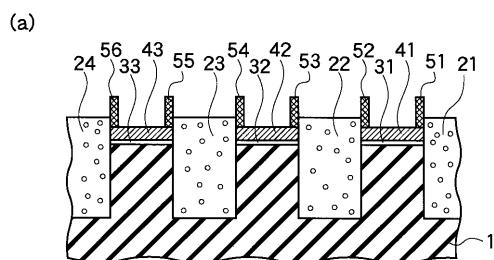

【図11】 第2の参考例とその第1乃至第3の変形例に係る半導体装置の断面図である。

【図12】 第2の参考例に係る半導体装置の製造工程毎の断面図である。

【図13】 第2の参考例の第1の変形例に係る半導体装置の製造工程毎の断面図である。

【図14】 第2の参考例の第2の変形例に係る半導体装置の製造工程毎の断面図である

50

- 【図 15】 第 2 の実施の形態に係る半導体装置の上面図と断面図である。

- 【図 16】 第 2 の実施の形態に係る半導体装置の製造工程毎の断面図（その 1）である

- 【図 17】 第 2 の実施の形態に係る半導体装置の製造工程毎の断面図（その 2）である

- 【図 18】 第 2 の実施の形態に係る半導体装置の製造工程毎の断面図（その 3）である

- 【図 19】 第 2 の実施の形態に係る半導体装置の製造工程毎の断面図（その 4）である

- 【図 20】 第 2 の実施の形態に係る半導体装置の製造工程毎の断面図（その 5）である

- 【図 21】 第 2 の実施の形態に係る半導体装置の比較例の上面図と断面図である。

- 【図 22】 第 2 の実施の形態の変形例に係る半導体装置の上面図と断面図である。

- 【図 23】 第 2 の実施の形態の変形例に係る半導体装置の製造工程毎の断面図である。

## 【符号の説明】

- 1 p 型シリコン基板

- 5 多結晶シリコン膜

- 6、16、26 浮遊ゲートと制御ゲートの間の絶縁膜、ONO 膜

- 7、17、27、28 制御ゲート

- 8、81 乃至 87 主電極領域、ソース・ドレイン領域

- 10 溝

- 11 溝

- 21 乃至 24 素子分離領域、STI

- 31 乃至 34 トンネル酸化膜

- 35 シリコン酸化膜

- 41 乃至 44、71 乃至 74 浮遊ゲートの第 1 部分

- 51 乃至 60、151 乃至 156 浮遊ゲートの第 2 部分

- 61 乃至 64 メモリセル

- 65 選択トランジスタ

- 66 ソース拡散層

- 75 選択ゲート

- 76 乃至 80 フォトレジスト

- 91 乃至 94 キャップ材

- 120 乃至 123 シリコン酸化膜

- 124 乃至 127 素子分離領域、STI

- 141、157 周辺回路のゲート電極

- 161 ダミーセル

- 162、163 メモリセル

- 164 周辺トランジスタ

10

20

30

40

【図1】

【図2】

(b)

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

---

フロントページの続き

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 森 誠一

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

(72)発明者 野口 充宏

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

審査官 瀧内 健夫

(56)参考文献 特開平11-087543(JP, A)

特開2000-232169(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792