### **CONFÉDÉRATION SUISSE**

OFFICE FÉDÉRAL DE LA PROPRIÉTÉ INTELLECTUELLE

(51) Int. Cl.<sup>3</sup>:

H 03 K

23/22

G 04 G H 01 L 3/02 27/10

### Demande de brevet déposée pour la Suisse et le Liechtenstein

Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

# <sup>(2)</sup> FASCICULE DE LA DEMANDE A3

(11)

631 597 G

(21) Numéro de la demande: 6187/79

(7) Requérant(s): Ebauches S.A., Neuchâtel

22) Date de dépôt:

03.07.1979

30 Priorité(s):

06.07.1978 FR 78 20163

(72) Inventeur(s): Jakob Lüscher, Venthône

42 Demande publiée le:

31.08.1982

Fascicule de la demande

publié le:

31.08.1982

56) Rapport de recherche au verso

#### 54) Registre à décalage intégré.

- (57) L'invention a pour objet un registre à décalage de très faible consommation. Chaque chaînon du registre est constitué de deux demi-chaînons comportant chacun:

- une structure MOS (T<sub>1</sub>.T'<sub>1</sub>) qui possède deux électrodes principales (Z<sub>00</sub>, Z<sub>1</sub>) formant respectivement l'entrée (Z<sub>00</sub>) et la sortie (Z<sub>1</sub>) du demi-chaînon, et deux électrodes de commande (k<sub>1</sub>, k'<sub>1</sub>) dont l'une (k<sub>1</sub>) peut être reliée à une source de polarisation (P) et dont l'autre (k'<sub>1</sub>) est connectée à l'électrode de sortie (Z<sub>1</sub>), et

- un condensateur  $(C_1)$  dont une armature  $(Z_1)$  est connectée à ladite électrode de sortie  $(Z_1)$  et dont l'autre armature  $(C_1)$  est destinée à recevoir l'un de deux signaux périodiques  $\emptyset_1(t)$  et  $\emptyset_2(t)$  en opposition de phase.

Bundesamt für geistiges Eigentum Office fédéral de la propriété intellectuelle Ufficio federale della proprietà intellettuale

Date d'achèvement de la recherche/Abschlussdatum der Recherche

22 octobre 1979

## RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.: Patentgesuch Nr.:

CH 6187/79

1.I.B. Nr.: HO 13726

| Documents considérés comme per inents Einschlägige Dokumente                                              |                                                                                                                                                                           |                                                            |                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie<br>Kategorie                                                                                    | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile | Revendications con-<br>cernées<br>Betrifft Anspruch<br>Nr. |                                                                                                                                                                                                                                                                                                                               |

|                                                                                                           | "3rd INTERNATIONAL CONFERENCE ON CHARGE COUPLED DEVICES, vol. 3, septembre 1976 EDINBURGH (GB) BUSS & WECKLER: "Bucket Brigade Devices -Circa 1976" pages 55-65           | 1,3,5                                                      |                                                                                                                                                                                                                                                                                                                               |

|                                                                                                           | * pages 55 et 56, paragraphe "Introduction";<br>figures 1-2 *                                                                                                             |                                                            | ,                                                                                                                                                                                                                                                                                                                             |

|                                                                                                           | <pre>US - A - 3 812 520 (BAKER) * de colonne 7, ligne 16 à colonne 9, ligne 30; figures 2, 3 *</pre>                                                                      | 1                                                          | Domaines techniques recherchés<br>Recherchierte Sachgebiete<br>(INT. CL. <sup>2</sup> )                                                                                                                                                                                                                                       |

|                                                                                                           | US - A - 3 643 106 (BERWIN & RADO)  * de colonne 2, ligne 56 à colonne 8, ligne 16:                                                                                       | 1                                                          | G 11 C 19/18 H 03 K 23/00 G 11 C 19/28 H 01 L 27/10 G 04 F 5/00 H 03 K 23/22 G 11 C 27/02                                                                                                                                                                                                                                     |

|                                                                                                           | de colonne 9, ligne 40 à colonne 10, ligne 17; figures 1-3, 6 *                                                                                                           |                                                            |                                                                                                                                                                                                                                                                                                                               |

|                                                                                                           | WEIMER)  * de colonne 9, ligne 1 à colonne 10, ligne 10; figures 3, 4 *                                                                                                   | 1                                                          | Catégorie des documents cités Kategorie der genannten Dokumente: X: particulièrement pertinent von besonderer Bedeutung                                                                                                                                                                                                       |

|                                                                                                           | DE - A - 1 616 402 (FERNSEH)                                                                                                                                              |                                                            | A. arrière-plan technologique technologischer Hintergrund O: divulgation non-écrite nichtschriftliche Offenbarung P: document intercalaire Zwischenliteratur T: théorie ou principe à la base de l'invention der Erfindung zugrunde liegende Theorien oder Grundsätze E: demande faisant interférence kollidierende Anmeldung |

|                                                                                                           | * page 2, lignes 9-26; figure, page 5 *                                                                                                                                   | 1                                                          |                                                                                                                                                                                                                                                                                                                               |

| A                                                                                                         | US - A - 3 645 088 (STE. SUISSE POUR INDUSTRIE HORLOGERE)                                                                                                                 | 1                                                          | L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument &: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie;                                                                                                                                                      |

| Etendu                                                                                                    | e de la recherche/Umfang der Recherche                                                                                                                                    |                                                            | ubereinstimmendes Dokument                                                                                                                                                                                                                                                                                                    |

| Revendications ayant fait l'objet de recherches Recherchierte Pateniansprüche: ensemble                   |                                                                                                                                                                           |                                                            |                                                                                                                                                                                                                                                                                                                               |

| Revendications n'ayant pas fait i'objet de recherches Nicht recherchierte Patentansprüche: Raison: Grund: |                                                                                                                                                                           |                                                            |                                                                                                                                                                                                                                                                                                                               |

Examinateur I.I.B./I.I.B Prüfer

#### REVENDICATIONS

- 1. Registre à décalage comprenant un ensemble de transistors et de condensateurs qui sont intégrés dans un substrat semi-conducteur et forment une pluralité de chaînons branchés les uns à la suite des autres, chaque chaînon comportant deux demi-chaînons identiques qui sont connectés en série et, en fonctionnement, alimentés respectivement par des signaux périodiques en opposition de phase, caractérisé en ce que chaque demi-chaînon comporte:

- une structure MOS à double transistor qui possède deux électrodes principales formant respectivement l'entrée et la sortie du demi-chaînon, et deux électrodes de commande dont l'une est, en fonctionnement, reliée à une source de polarisation et dont l'autre est connectée à l'électrode de sortie; et

- un condensateur dont une armature est connectée à ladite électrode de sortie et dont l'autre armature est destinée à recevoir l'un desdits signaux périodiques.

- 2. Registre à décalage selon la revendication 1, caractérisé en ce que ladite structure comprend un transistor MOS à double électrode de commande.

- 3. Registre à décalage selon la revendication 1, caractérisé en ce que ladite structure comprend deux transistors MOS connectés en série.

- 4. Registre à décalage selon la revendication 2, caractérisé en ce que la structure MOS et le condensateur d'un demichaînon sont formés par:

- une première et deuxième zones semi-conductrices d'un type opposé à celui du substrat dans lequel elles sont inté-

- une première couche conductrice isolée débutant au-dessus de la première zone et s'arrêtant sensiblement à michemin entre la première et la deuxième zone;

- une deuxième couche conductrice isolée débutant sensiet s'arrêtant au-dessus de la deuxième zone;

- une troisième couche conductrice en contact avec ladite deuxième zone et reliée à la deuxième couche conductrice;

- une quatrième couche conductrice isolée disposée en regard de la deuxième zone, les deux zones semi-conductrices formant les électrodes principales de ladite structure dont les électrodes de commande respectives sont formées par lesdites première et deuxième couches conductrices, et la quatrième couche conductrice formant une armature dudit condensateur dont l'autre armature est formée par ladite deuxième zone.

- 5. Registre à décalage selon la revendication 4, caractérisé en ce que lesdites première et deuxième zones semi-conductrices forment aussi respectivement la deuxième zone semi-conductrice du demi-chaînon précédent et la première zone semi-conductrice du demi-chaînon suivant.

La présente invention a pour objet un registre à décalage et, plus particulièrement, un registre à décalage intégré de très faible consommation. Un tel registre convient particulièrement bien, sans toutefois que cela constitue son seul domaine d'application, pour la réalisation d'un circuit diviseur de fréquence pouvant être utilisé dans tout type de dispositif portatif de petites dimensions, alimenté par une pile qui est nomie de marche pouvant atteindre plusieurs années. Comme on le sait, le problème de la consommation d'énergie se pose avec particulièrement d'acuité lorsque la fréquence à diviser est élevée, voire de quelques MHz, comme c'est le cas, par exemple, pour les montres à hautes performances chronométriques.

Pour réduire la consommation d'énergie des diviseurs de 5 fréquence, des tentatives ont été faites avec des circuits binaires intégrés C-MOS. Ce sont de tels circuits qui équipent actuellement la plupart des montres à quartz. Dans ce cas, la consommation est essentiellement donnée par la charge et décharge des capacités que présente chaque étage du registre 10 à décalage et, cela, avec la périodicité de son signal de sortie. La consommation de chaque étage est donc proportionnelle à la valeur de ses capacités et à la fréquence de son signal de sortie. Pour une montre à quartz haute fréquence, ce sont donc alors les premiers étages, c'est-à-dire ceux qui divisent 15 les fréquences les plus élevées, qui sont déterminants pour la consommation de l'électronique. Afin d'abaisser les capacités de ces étages, on a utilisé différentes techniques de fabrication, telles que celles qui sont connues sous le nom de Si-gate ou SOS. Cependant, pour maintenir la consomma-20 tion dans des limites acceptables, il est nécessaire que les dimensions des circuits intégrés soient réduites à un point tel que, dans l'état actuel de la technique, le coût de leur fabrication devient prohibitif.

Pour abaisser la consommation, on a aussi proposé des 25 diviseurs de fréquences élevées dont une grande partie des capacités font partie d'un circuit résonnant. Un système de ce type est décrit, par exemple, dans le brevet suisse no 558 111. Dans ce cas, l'énergie stockée périodiquement dans les capacités est récupérée. Le système fait usage d'un regis-30 tre à décalage réalisé sous forme intégrée, du type «IGFET bucket brigade». Un tel registre, décrit par exemple dans l'article de C.N. Bergland et al. «Fabrication and Performance Considerations of Charge - Transfer Dynamic Shift Registers» Bell Syst. Techn. Journal, Vol. 51, No 3, Mars blement à mi-chemin entre la première et la deuxième zone 35 1972, est formé de chaînons comportant chacun, d'une part, deux transistors à effet de champ à électrode isolée, qui sont montés en série, et, d'autre part, deux condensateurs respectivement branchés entre l'électrode de commande et le drain des transistors. Les électrodes de commande sont reliées de 40 façon alternée à deux lignes alimentées par des signaux alternatifs en opposition de phase. Il existe également pour ces registres une version tétrode dans laquelle chaque transistor commandé par un signal alternatif est séparé de son voisin par un transistor supplémentaire polarisé par une tension 45 continue, ce qui permet d'améliorer le rendement de transfert des charges et, de ce fait, de pouvoir augmenter le nombre de chaînons du registre. (Voir par exemple la publication de R.R. Buss et G.P. Weckler «Bucket Brigade Devices-Birca 1976», 3rd International Conference on Charge Coupled

50 Devices, vol. 3, sept. 1976, Edinburgh.) Dans le diviseur de fréquence qui fait l'objet du brevet suisse précité le registre à décalage est branché en anneau, les deux tensions alternatives sont fournies par un oscillateur symétrique à quartz et un seul paquet de charge est transféré 55 d'un chaînon à l'autre. Par ailleurs des moyens sont prévus pour polariser le substrat cristallin dans lequel les circuits sont intégrés. L'ensemble des chaînons du registre présente une faible charge pour l'oscillateur et le courant réactif dû à cette capacité provoque une faible perte dans le quartz. La 60 puissance réelle principale que doit fournir l'oscillateur est celle qui est dissipée dans le transistor par lequel se fait le transfert de la charge d'un demi-chaînon à l'autre.

Le mode de fonctionnement du registre à décalage décrit ci-dessus (et dont on trouvera une explication détaillée dans appelée à assurer l'alimentation de l'ensemble avec une auto- 65 l'article de C.N. Berglund et al. susmentionné) est tel que le courant traverse le transistor pendant 1/4 de période environ et que la tension source-drain de celui-ci passe pendant ce temps pratiquement de la valeur V<sub>P</sub> à O, V<sub>P</sub> étant la valeur

crête-crête de la tension d'alimentation de phase fournie par l'oscillateur. Il en résulte que la puissance fournie par l'oscillateur, exprimée par la relation générale:

$P^{t} = \frac{2}{T} \int_{O}^{T/2} i_{D}(t) \cdot v_{SD}(t) dt$ , où  $i_{D}(t)$  et  $v_{SD}(t)$  sont les valeurs instantanées respectivement du courant de drain et de la tension source-drain du transistor, T étant la période de l'oscillation, devient:  $P_T = (V_p + v_m)^2$ .C.f. Dans cette expression, C est la capacité associée au transistor, f est la fréquence de l'oscillateur et v<sub>m</sub> représente la tension de commande moyenne qui dépasse la tension de seuil du transistor.

La tension v<sub>m</sub> est normalement de quelques dixièmes de volt, alors que V<sub>p</sub> est de quelques volts.

En prenant un exemple typique avec les valeurs:  $V_p =$  $2 \text{ V}, v_m = 0.3 \text{ V}, C = 0.1 \text{ pF}, \text{ et } f = 4.2 \text{ MHz}, \text{ on obtient}$ pour  $P_T$  une valeur de 2,2  $\mu$ W.

C'est donc à cause de la tension élevée nécessaire pour le transfert du paquet de charges d'un chaînon du registre à l'autre que la puissance fournie par l'oscillateur est relativement élevée.

La présente invention a pour principal objet de fournir un registre à décalage nécessitant une très faible tension pour le transfert de la charge, ce qui réduit considérablement la puissance que doit fournir l'oscillateur.

Les caractéristiques et avantages de l'invention ressortiront de la description qui va suivre, faite en regard des dessins annexés et donnant, à titre explicatif mais nullement limitatif, une forme de réalisation de ce registre à décalage. Sur ces dessins:

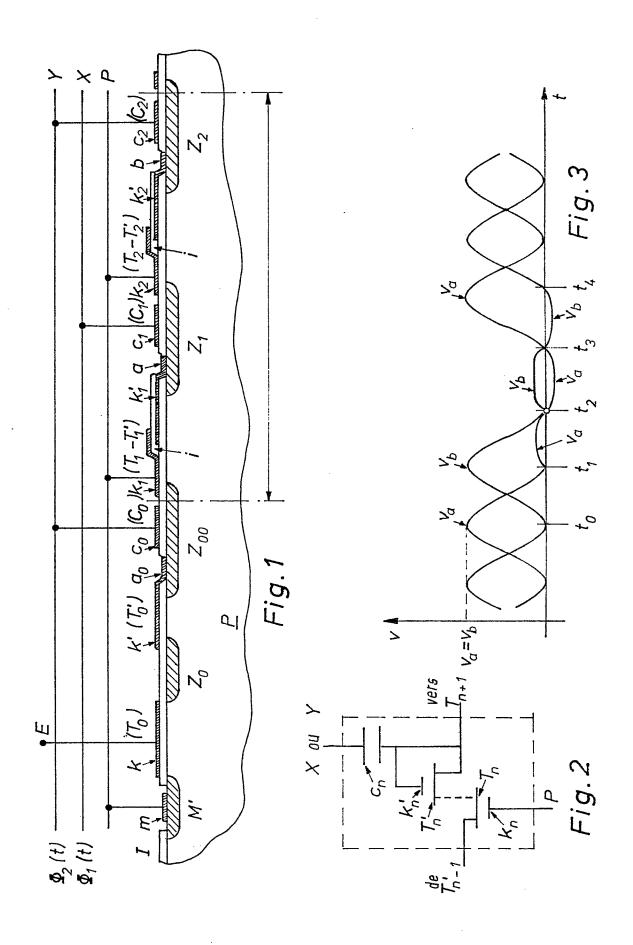

La figure 1 représente partiellement un registre à décalage selon l'invention;

la figure 2 donne le schéma équivalent d'un demi-chaînon du registre de la figure 1; et

la figure 3 est un diagramme servant à expliquer le fonctionnement du registre de la figure 1.

On se réfèrera tout d'abord à la figure 1 sur laquelle on a représenté une structure MOS comportant un substrat cristallin de type p, par exemple, dans lequel sont intégrées cinq zones de type n, respectivement désignées M', Zo, Zoo, Z1,  $Z_2$ . Le tout est recouvert par une couche isolante I interrompue localement au-dessus d'une partie des zones M',  $Z_{00}$ ,  $Z_1$  et  $Z_2$  pour permettre le dépôt, directement sur la zone n concernée, de contacts m, a<sub>o</sub>, a et b, respectivement.

La couche isolante I comporte elle-même un certain nombre de dépôts conducteurs, ou électrodes, désignés respectivement k, k', k<sub>1</sub>, k'<sub>1</sub>, k<sub>2</sub>, k'<sub>2</sub>, qui s'étendent principalement au-dessus de la zone p. Plus précisément, l'électrode k s'étend entre les extrémités des zones M' et Z<sub>0</sub>, alors que l'électrode k' s'étend de la fin de la zone Z<sub>o</sub> au début de la zone  $Z_{\infty}$  où elle est électriquement reliée au contact a déjà mentionné. L'électrode k<sub>1</sub> commence à la fin de la zone Z<sub>00</sub> pour s'arrêter sensiblement à mi-chemin entre  $Z_{00}$  et  $Z_1$  et laisser la place à l'électrode k'1 qui s'étend jusqu'au début de 55 tre à décalage selon l'invention. Ce registre comporte ainsi la zone  $Z_1$  où elle est électriquement reliée au contact a. L'électrode k<sub>1</sub>, lorsqu'elle se termine, présente une portion légèrement relevée qui recouvre, sans la toucher, la portion initiale de l'électrode k'1, une couche isolante i assurant l'absence de contact électrique entre les deux électrodes. Les électrodes k2-k'2 sont déposées entre les zones Z1 et Z2 de la même manière que les électrodes k<sub>1</sub> et k'<sub>1</sub>.

Finalement, la couche isolante I comporte des dépôts conducteurs, ou électrodes, co, c1 et c2, qui s'étendent audessus des zones  $Z_{00}$ ,  $Z_1$  et  $Z_2$  respectivement. L'électrode k est l'électrode destinée à recevoir le signal de déclenchement par lequel un nouveau paquet de charges est introduit dans le registre. Cette électrode est reliée à une borne d'entrée E.

Le registre est commandé par un oscillateur symétrique (non représenté), tel que décrit, par exemple, dans le brevet suisse no 580 837, qui fournit sur des lignes X et Y deux tensions sinusoïdales en opposition de phase  $\Phi_1(t)$  et  $\Phi_2(t)$  respectivement. Les électrodes c<sub>0</sub>, c<sub>1</sub> et c<sub>2</sub>-sont reliées alternativement aux lignes X et Y. De plus, l'oscillateur polarise, au moyen d'un multiplicateur de tension (non représenté), comme par exemple celui qui est décrit dans le brevet suisse no 553 481, le substrat cristallin de l'ensemble négativement par 10 rapport à une masse de référence M' à laquelle sont reliées, par une ligne P, les électrodes m, k<sub>1</sub> et k<sub>2</sub>.

Il apparaît ainsi que le circuit intégré de la figure 1 est formé d'un ensemble de condensateurs et de transistors MOS. Les électrodes c<sub>0</sub>, c<sub>1</sub> et c<sub>2</sub> constituent, en effet, les ar-15 matures de condensateurs Co, C1 et C2, respectivement, dont les autres armatures sont formées par les zones  $Z_{00}$ ,  $Z_1$  et  $Z_2$ , respectivement. En outre, l'électrode k constitue l'électrode de commande d'un transistor MOS T<sub>o</sub> dont la zone M' est la source et dont la zone Z<sub>0</sub> est le drain. Quant à l'électrode k', 20 elle constitue l'électrode de commande d'un transistor MOS  $T'_{o}$  dont la zone  $Z_{o}$  est la source et dont la zone  $Z_{oo}$  est le drain. Ce transistor a donc, du fait de la liaison entre k' et le contact a<sub>0</sub>, son électrode de commande reliée à son drain.

En ce qui concerne maintenant la paire d'électrodes 25  $k_1-k'_1$ , il apparaît qu'elles constituent les électrodes de commande des portions respectives T<sub>1</sub>-T'<sub>1</sub> d'une structure transistor double dont la zone  $Z_{00}$  constitue la source et dont la zone Z<sub>1</sub> constitue le drain. Le transistor T'<sub>1</sub> a, du fait de la liaison du contact a avec k'1, son électrode de commande re-30 liée à son drain. Il en est exactement de même pour la paire k<sub>2</sub>-k'<sub>2</sub> qui constituent les électrodes de commande des portions respectives T<sub>2</sub>-T'<sub>2</sub> d'une structure transistor double dont les zones  $Z_1$  et  $Z_2$  constituent respectivement la source et le drain. La zone  $Z_2$  constitue également la source de la 35 structure transistor suivante, rigoureusement identique aux structures T<sub>1</sub>-T'<sub>1</sub> et T<sub>2</sub>-T'<sub>2</sub>, et dont on a seulement représenté sur la figure 1 le début de la première électrode, reliée à la ligne P.

Le circuit représenté figure 1 regroupe l'étage d'injection, 40 ou de déclenchement, ainsi que le premier chaînon d'un registre à décalage. L'étage d'injection est formé par le condensateur Co et les transistors To et T'o, alors que le premier chaînon du registre est formé de deux demi-chaînons identiques en série formés par le condensateur C1 et la structure 45 MOS double T<sub>1</sub>-T'<sub>1</sub> pour le premier, par le condensateur C<sub>2</sub> et la structure MOS double T<sub>2</sub>-T'<sub>2</sub> pour le deuxième.

Un registre à décalage conforme à l'invention comportera donc une pluralité de chaînons semblables à celui de la figure 1 et branchés les uns à la suite des autres avec leurs 50 électrodes de commande reliées à la ligne de polarisation P et leurs deux condensateurs respectivement reliés aux lignes X pour le premier demi-chaînon et Y pour le deuxième.

On se réfèrera maintenant à la figure 2 sur laquelle on a représenté le schéma équivalent d'un demi-chaînon du regisun condensateur Cn et une structure transistor double dont les deux composants T<sub>n</sub> et T'<sub>n</sub> ont pour électrodes de commande k<sub>n</sub> et k'<sub>n</sub> respectivement. Cette structure double est représentée sur la figure par deux transistors reliés par une 60 ligne en pointillés qui symbolise le zone commune au drain de T<sub>n</sub> et à la source T'<sub>n</sub>. L'électrode de commande k<sub>n</sub> de T<sub>n</sub> est reliée à la ligne de polarisation P et sa source est connectée à la sortie du demi-chaînon précédent, formée par le drain du deuxième transistor, T'n-1 de celui-ci. L'une des ar-65 matures du condensateur C<sub>n</sub> est connectée à la ligne X ou à la ligne Y selon que le demi-chaînon est le premier ou le deuxième, respectivement, du chaînon considéré. L'autre armature de C<sub>n</sub> est reliée à la fois au drain et à l'électrode de

commande k'n de T'n. La sortie du demi-chaînon, constituée par le drain du transistor T'<sub>n</sub> est reliée à l'entrée du demichaînon suivant, formée par la source du premier transistor,  $T_{n+1}$ , de celui-ci.

En se référant maintenant aux figures 1 et 2, ainsi qu'au diagramme explicatif de la figure 3, le fonctionnement du registre à décalage selon l'invention peut être décrit comme suit. Dans un but de simplification, il sera supposé que les tensions de seuil des structures MOS seront O. Le cristal étant polarisé négativement par rapport à la masse et les deux lignes X et Y étant alimentées par les tensions sinusoïdales en opposition de phase  $\Phi_1(t)$  et  $\Phi_2(t)$  respectivement, si le transistor T<sub>o</sub> est bloqué, des tensions sinusoïdales v<sub>a</sub> et v<sub>b</sub> (ayant respectivement pour valeur crête-crête V<sub>a</sub> et V<sub>b</sub>) apparaissent sur les zones  $Z_1$  et  $Z_2$  aux points a et b respectivement. La forme de ces deux tensions est représentée sur le diagramme de la figure 3. Si le transistor T<sub>o</sub> est alors commandé, entre les instants to et t1, par application sur son électrode de commande k (borne E) d'une impulsion dérivée de de la zone de référence M' sur la zone Zo et, de là, par le transistor T'o, sur la zone Zoo. Le condensateur Co se trouve ainsi chargé sur la valeur crête de  $\Phi_2(t)$ . A l'instant  $t_1$ , le potentiel de la zone Z<sub>00</sub> par rapport à M' est donc pratiquement 0.

Le potentiel au point ao prenant ensuite une valeur négative par rapport à M', le transistor T'o est bloqué puisque son électrode de commande k' est reliée à la zone Z<sub>oo</sub>. Les électrons passent donc sur la zone  $Z_1$  par la structure MOS  $T_1-T'_1$  et chargent le condensateur  $C_1$  sur la valeur crête de  $\Phi_1(t)$ . Pendant la demi-période suivante, c'est-à-dire entre les instants t<sub>2</sub> et t<sub>3</sub>, le même mécanisme est répéte pour la transfert entre les zones  $Z_1$  et  $Z_2$ , par la structure  $MOS T_2 - T_2$ ', du paquet de charges  $Q = C_1 \cdot \Phi_1$ , et ainsi de suite. Si la valeur de la réactance  $1/\omega$   $C_1 = 1/\omega$   $C_2$  ( $\omega$  étant la pulsation de l'oscillateur) est beaucoup plus grande que la valeur de la résistance différentielle que présente la structure MOS d'un demichaînon, le courant que doit fournir l'oscillateur pour le transfert du paquet de charges est sensiblement sinusoïdal et déphasé de presque 90° par rapport aux tensions de phase  $\Phi_1(t)$  et  $\Phi_2(t)$ . La tension source-drain de la structure MOS, qui représente dans ce cas aussi sa tension de commande, devient pour ce transfert très faible. La puissance que doit fournir l'oscillateur est donc, elle aussi, très faible.

L'analyse montre, en s'exprimant dans les mêmes termes que ceux qui ont été utilisés précédemment pour un registre à décalage du type «IGFET bucket brigade», que la puissance à fournir par l'oscillateur pour le transfert du paquet de 5 charges est alors  $P_T = 1.8 V_p v_m.C.f.$

En prenant les mêmes valeurs type que précédemment, on obtient une puissance de 0,45 µW. Cette puissance était de 2,2 µW avec le registre «IGFET bucket brigade». On voit ainsi que le registre à décalage selon l'invention permet de 10 réaliser une économie de puissance considérable.

Comme le montre la figure 3, la tension v<sub>a</sub> qui s'établit sur le point a entre les instants t<sub>1</sub> et t<sub>2</sub> lors du transfert de la charge par la structure MOS T<sub>1</sub>-T'<sub>1</sub>, puis entre les instants t<sub>2</sub> et t<sub>3</sub> lors du transfert par T<sub>2</sub>-T'<sub>2</sub>, est très faible par rap-15 port à la tension qui s'établit lorsqu'il n'y a pas de transfert. Il en est de même pour la tension v<sub>b</sub> sur le point b entre les instants t2 et t3, puis entre les instants t3 et t4 lorsque la charge passe par la structure MOS suivante. Du fait de cette différence, le registre à décalage suivant l'invention se prête la tension  $\Phi_2(t)$ , des électrons passent, dans l'intervalle  $t_0-t_1$ , 20 particulièrement bien à la réalisation de circuits diviseurs de fréquence. Un tel circuit est décrit dans la demande de brevet français déposée le 6 juillet 1978 par la Demanderesse pour un «Diviseur de fréquence intégré» et publiée sous le no

Le registre à décalage selon l'invention peut être réalisé selon la technique de fabrication connue sous le nom de Sigate. On peut aussi, bien entendu, utiliser une technique plus simple appelée Al-gate. Dans ce deuxième cas, la structure d'un demi-chaînon est constituée par deux transistors MOS 30 en série. A cause, cependant, de la capacité que présente la jonction flottante formant alors le drain du premier et la source du deuxième transistor, la performance du registre risque d'être quelque peu diminuée, et cela essentiellement dans le sens que le nombre possible de chaînons est plus ré-35 duit que si la structure représentée figure 1 est utilisée. Cela est dû à une certaine perte de la charge lorsqu'elle est transférée d'un condensateur à l'autre.

Par ailleurs, l'étage d'injection du registre peut, au lieu d'être constitué par deux transistors en série, être identique à 40 un demi-chaînon du registre et comporter donc seulement deux zones n, M' et Zoo.

Naturellement, le registre à décalage qui a été décrit cidessus est susceptible de nombreuses variantes qui restent dans le cadre de l'invention.