(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5764256号

(P5764256)

(45) 発行日 平成27年8月19日(2015.8.19)

(24) 登録日 平成27年6月19日(2015.6.19)

(51) Int.Cl.

H01L 21/60 (2006.01)

F 1

H01L 21/92 604A

H01L 21/92 604R

H01L 21/92 602J

請求項の数 24 (全 16 頁)

(21) 出願番号 特願2014-502583 (P2014-502583)

(86) (22) 出願日 平成24年3月3日(2012.3.3)

(65) 公表番号 特表2014-511039 (P2014-511039A)

(43) 公表日 平成26年5月1日(2014.5.1)

(86) 國際出願番号 PCT/US2012/027631

(87) 國際公開番号 WO2012/134710

(87) 國際公開日 平成24年10月4日(2012.10.4)

審査請求日 平成26年12月18日(2014.12.18)

(31) 優先権主張番号 13/072,554

(32) 優先日 平成23年3月25日(2011.3.25)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 508301087

エーティーアイ・テクノロジーズ・ユーブ

ルシー

A T I T E C H N O L O G I E S U L

C

カナダ、オンタリオ エル3ティー 7

エックス6、マーカム、コマース バリー

ドライブ イースト 1

One Commerce Valley

Drive East, Markha

m, Ontario, L3T 7X6

Canada

最終頁に続く

(54) 【発明の名称】支持端子パッドを有する半導体チップ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導体パッドとパッシベーション構造とを有する半導体チップを設けるステップと、

第2の導体パッドを、前記パッシベーション構造上であって前記第1の導体パッドの周囲に、間隙を残すように前記第1の導体パッドと物理的に接触することなく形成するステップと、

前記第1の導体パッドと電気的に接触するアンダーバンプメタライゼーション構造を形成するステップと、を含み、

前記アンダーバンプメタライゼーション構造は、前記第2の導体パッドと上下に重なる部分を有するが前記第2の導体パッドとは電気的に接触しておらず、

前記第2の導体パッドは、前記重なる部分によって与えられる応力から、前記パッシベーション構造の一部を保護するように動作する、

製造方法。

## 【請求項 2】

前記第2の導体パッドは、前記第1の導体パッドの周囲に完全に伸びている、請求項1に記載の製造方法。

## 【請求項 3】

前記アンダーバンプメタライゼーション構造は、八角形の接地面を有する、請求項1に記載の製造方法。

10

20

**【請求項 4】**

はんだ構造を前記アンダーバンプメタライゼーション構造に結合するステップを備える、請求項 1 に記載の製造方法。

**【請求項 5】**

前記はんだ構造は、はんだバンプ及びはんだ接合のうち一方を備える、請求項 4 に記載の製造方法。

**【請求項 6】**

回路基板を前記はんだ構造に電気的に結合するステップを備える、請求項 4 に記載の製造方法。

**【請求項 7】**

前記回路基板は、半導体チップパッケージ基板を備えている、請求項 6 に記載の製造方法。

10

**【請求項 8】**

コンピュータ可読媒体内に格納された命令を用いて、前記第 1 の導体パッドと前記第 2 の導体パッドとを形成するステップを備える、請求項 1 に記載の製造方法。

**【請求項 9】**

高分子膜を前記半導体チップ上に形成するステップと、

前記間隙の近くの前記パッシベーション構造の一部を保護するために、第 3 の導体パッドを、前記間隙の近くの前記高分子膜上に形成するステップとを備える、請求項 1 に記載の製造方法。

20

**【請求項 10】**

前記第 3 の導体パッドは、前記第 2 の導体パッドと物理的に接触していない、請求項 9 に記載の製造方法。

**【請求項 11】**

パッシベーション構造と、第 1 の導体パッドと、前記第 1 の導体パッドの近くであって前記パッシベーション構造上の第 2 の導体パッドとを有する半導体チップであって、前記第 1 の導体パッド及び第 2 の導体パッドは、間隙を残すように高分子膜によって隔てられており、前記第 1 の導体パッドは、前記第 2 の導体パッドに亘って延びるとともに前記第 2 の導体パッドと上下に重なるが、前記高分子膜により前記第 2 の導体パッドと隔てられるアンダーバンプメタライゼーション構造と電気的に接触する、半導体チップを回路基板に結合する方法において、

30

はんだ構造を前記アンダーバンプメタライゼーション構造に結合するステップと、

前記はんだ構造を前記回路基板に結合するステップと、

を含む方法。

**【請求項 12】**

前記はんだ構造は、はんだバンプ及びはんだ接合のうち一方を備える、請求項 11 に記載の方法。

**【請求項 13】**

前記はんだ構造を前記回路基板に結合するステップは、前記はんだ構造を、前記回路基板に結合された予備はんだに結合するステップを備える、請求項 11 に記載の方法。

40

**【請求項 14】**

前記回路基板は、半導体チップパッケージ基板を備える、請求項 11 に記載の方法。

**【請求項 15】**

前記間隙の近くの前記パッシベーション構造の一部を保護するために、第 3 の導体パッドを、前記間隙の近くの前記高分子膜上に形成するステップを備える、請求項 11 に記載の方法。

**【請求項 16】**

前記第 3 の導体パッドは、前記第 2 の導体パッドと物理的に接触していない、請求項 15 に記載の方法。

**【請求項 17】**

50

第1の導体パッドとパッシベーション構造とを有する半導体チップと、

前記パッシベーション構造上であって前記第1の導体パッドの周囲に、間隙を残すよう

に前記第1の導体パッドと物理的に接触することなく存在する第2の導体パッドと、

前記第1の導体パッドと電気的に接触するアンダーバンプメタライゼーション構造と、

を備え、

前記アンダーバンプメタライゼーション構造は、前記第2の導体パッドと上下に重なる

部分を有するが前記第2の導体パッドとは電気的に接触しておらず、

前記第2の導体パッドは、前記重なる部分によって与えられる応力から、前記パッシベー

ーション構造の一部を保護するように動作する、

装置。

10

【請求項18】

前記第2の導体パッドは、前記第1の導体パッドの周囲に完全に伸びている、請求項1

7に記載の装置。

【請求項19】

前記アンダーバンプメタライゼーション構造は、八角形の接地面を有する、請求項17

に記載の装置。

【請求項20】

前記アンダーバンプメタライゼーション構造に結合されたはんだ構造を備える、請求項

19に記載の装置。

【請求項21】

20

前記はんだ構造は、はんだバンプ及びはんだ接合のうち一方を備える、請求項20に記

載の装置。

【請求項22】

前記半導体チップに結合された回路基板を備える、請求項17に記載の装置。

【請求項23】

前記半導体チップ上の高分子膜と、

前記間隙の近くの前記パッシベーション構造の一部を保護するために、前記間隙の近く

の前記高分子膜上に存在する第3の導体パッドとを備える、請求項17に記載の装置。

【請求項24】

前記第3の導体パッドは、前記第2の導体パッドと物理的に接触していない、請求項2

3に記載の装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して、半導体処理に関し、より具体的には、半導体チップのはんだバンプ

パッド及びその製造方法に関する。

【背景技術】

【0002】

フリップチップ実装方式は、半導体チップパッケージ基板などの回路基板に半導体チッ

プを実装するために、数十年にわたり使用されてきた。多くの従来のフリップチップの変

形例では、複数のはんだ接合は、半導体チップの入出力(I/O)部位と、回路基板の対

応するI/O部位との間で確立される。1つの従来のプロセスでは、はんだバンプは、半

導体チップの所定のI/O部位又はパッドに金属接合され、いわゆる予備はんだは、回路

基板の対応するI/O部位に金属接合される。その後、はんだバンプと予備はんだとを接

近させ、はんだバンプ及び予備はんだの一方又は両方をリフローで接合して、必要なはん

だ接合を確立する加熱処理が施される。

40

【0003】

1つの従来のプロセスでは、半導体チップの特定のI/O部位へのはんだバンプの接続

は、当該I/O部位の近くで、半導体チップの最上位の誘電体膜に開口部を形成すること

と、その後、金属を堆積させて、アンダーバンプメタライゼーション(UMB)構造を形

50

成することとを伴う。次いで、はんだバンプは、リフローにより UBM 構造に金属接合される。この従来の UBM 構造は、基部と、側壁と、誘電体膜上に配置される上部フランジとを備えている。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

フリップチップはんだ接合は、例えば、熱膨張係数の不一致、延性の違い及び回路基板の反りなどの様々な要因に起因する機械的応力にさらされることがある。このような応力は、前述の UBM 構造に曲げモーメントの影響を及ぼす。この影響は、ダイの端部及び角部に近づくほど応力が大きくなり、また、ダイの中心に近づくにつれて応力が下落する傾向にあるという点で、いくらか方向性を有する。このいわゆるエッジ効果に関連付けられた曲げモーメントは、十分に大きければ破碎を生じ得る応力を、UBM 構造の下にある誘電体膜上にかけ得る。

#### 【0005】

様々な理由により、設計者は、はんだ接合加工用の鉛フリーはんだに注目し始めている。こうしたはんだから成るバンプは、同等サイズの鉛ベースのバンプよりも高い応力を生じることがある。これらのより高い応力を相殺するために、従来の設計では、アンダーバンプメタライゼーションと、下層のチップバンプパッドとの間に、端子パッドを組み込んでいる。端子パッドは、上層のアンダーバンプメタライゼーション及び下層のチップパッドよりも大きな設置面積を有しており、パッシベーション層に応力保護をもたらす。チップが、チップパッドの近くにアクティブトレースを含む場合には、端子パッドは、そのようなトレースにオーバーラップし、寄生容量を生じ得る。

#### 【0006】

本発明は、前述した 1 つ以上の不利益の影響を克服又は低減することに向けられている。

#### 【課題を解決するための手段】

#### 【0007】

本発明の実施形態の一態様によれば、第 1 の導体パッドと、パッシベーション構造とを有する半導体チップを提供することを含む、製造方法が提供される。第 2 の導体パッドは、第 1 の導体パッドと物理的に接触することなく間隔をあいて、第 1 の導体パッドの周囲に形成されている。第 2 の導体パッドは、パッシベーション構造の一部を保護するように適用されている。

#### 【0008】

本発明の実施形態の別の態様によれば、半導体チップを回路基板に結合する方法が提供される。半導体チップは、パッシベーション構造と、互いに近接するが高分子層により間隔をあいて隔てられた第 1 及び第 2 の導体パッドとを有しており、第 1 の導体パッドは、第 2 の導体パッドに亘って延びるが高分子層により前記第 2 の導体パッドと隔てられるアンダーバンプメタライゼーション構造と電気的に接触している。本方法は、はんだ構造をアンダーバンプメタライゼーション構造に結合するステップと、はんだ構造を回路基板に結合するステップとを含む。

#### 【0009】

本発明の実施形態の別の態様によれば、第 1 の導体パッドとパッシベーション構造とを有する半導体チップを含む装置が提供される。第 2 の導体パッドは、第 1 の導体パッドと物理的に接触することなく間隔をあいて、第 1 の導体パッドの周囲に形成されている。第 2 の導体パッドは、パッシベーション構造の一部を保護するように適用されている。

#### 【0010】

本発明の上述及びその他の利点は、以下の詳細な説明を読むことによって、また図面を参照することによって明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0011】

10

20

30

40

50

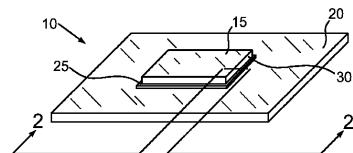

【図1】回路基板上に実装された半導体チップを含む半導体チップデバイスの例示的実施形態の図である。

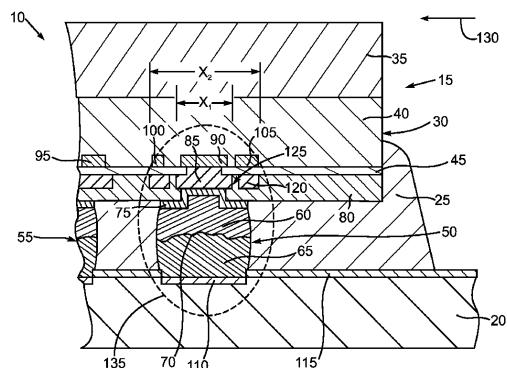

【図2】断面2-2における図1の断面図である。

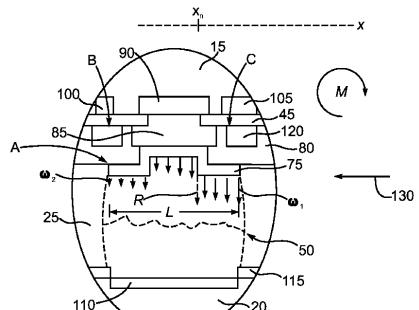

【図3】図2の一部を拡大して示す図である。

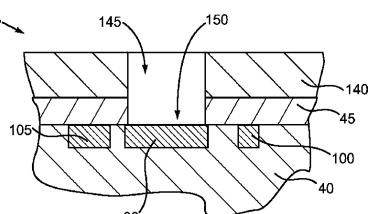

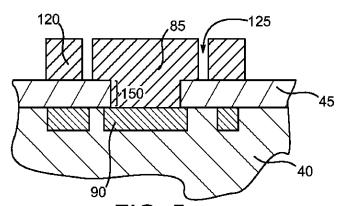

【図4】半導体チップの導体構造への開口部の例示的な形成を示す断面図である。

【図5】図4と同様の断面図である。ただし、例示的なアクティブ端子及び仮想パッドの形成を示している。

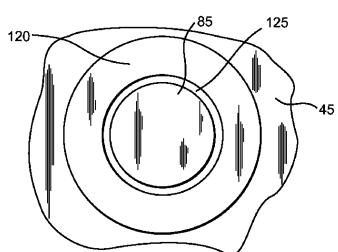

【図6】例示的なアクティブ端子及び仮想パッドの平面図である。

【図7】図5と同様の断面図である。ただし、例示的なアクティブ端子及び仮想パッド上の高分子膜の適用を示している。

10

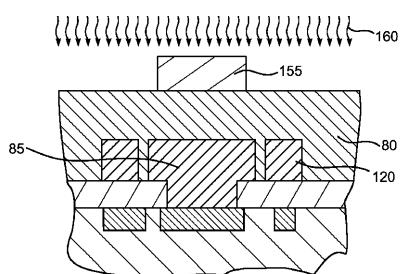

【図8】図7と同様の断面図である。ただし、例示的なリソグラフィーマスキング及び高分子膜の露光を示している。

【図9】図8と同様の断面図である。ただし、高分子膜の開口部の例示的なリソグラフィー加工を示している。

【図10】図9と同様の断面図である。ただし、例示的なアンダーバンプメタライゼーション構造の形成を示している。

【図11】図10と同様の断面図である。ただし、アンダーバンプメタライゼーション構造へのはんだ構造の形成を概略的に示している。

【図12】例示的なアンダーバンプメタライゼーション構造の平面図である。

【図13】他の例示的なアンダーバンプメタライゼーション構造の平面図である。

20

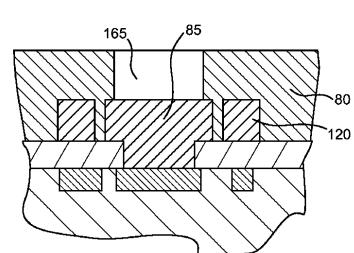

【図14】図3と同様の断面図であるが、他の例示的な半導体チップの実施形態の断面図である。

【図15】例示的なアクティブ端子、仮想パッド、高分子膜及び付加仮想パッドの形成を示す断面図である。

【図16】図15と同様の断面図である。ただし、第1の高分子膜上の例示的な付加高分子膜の形成を示している。

【図17】図3と同様の断面図であるが、さらに他の例示的な半導体チップの実施形態の断面図である。

#### 【発明を実施するための形態】

##### 【0012】

30

半導体チップの様々な実施形態が本明細書において説明される。1つの例は、例えば、それぞれのアクティブ端子パッド上に形成されるUBM構造などのはんだバンプ接続構造を含む。アクティブ端子パッドは、当該アクティブパッドと物理的に接続されずに周囲を取り囲む仮想パッドとともに、チップパッセーション構造上に形成される。仮想パッドは、下層のチップアクティブ導体トレースに伴う寄生容量を生じさせることなしに、パッセーション構造を保護する。以下、さらなる詳細を説明する。

##### 【0013】

以下に説明される図面において、同一の要素が2つ以上の図面に現れる場合には、参照番号は概して繰り返される。図面、特に図1を参照すると、回路基板20上に実装された半導体チップ15を含む半導体チップデバイス10の例示的な実施形態の図が示されている。アンダーフィル材料層25は、半導体チップ15と回路基板20との間に配置されている。本明細書に開示されたはんだ相互接続構造は、半導体チップ15又は回路基板20のどちらの特定の機能にも依存しない。これにより、半導体チップ15は、例えばマイクロプロセッサ、グラフィクスプロセッサ、マイクロプロセッサ/グラフィクスプロセッサの組み合わせ、特定用途向け集積回路、メモリデバイスなどの、エレクトロニクスにおいて用いられる多数の異なる種類の回路デバイスのいずれであってもよく、また、單一コア又は多重コアであってよく、あるいは追加的なダイスとともに積層されていてもよい。半導体チップ15は、シリコン又はゲルマニウムなどのバルク半導体、あるいはシリコンオンインシュレータ材料などの絶縁材料上の半導体から構成されてもよい。半導体チップ15は、回路基板20にフリップチップ実装され、はんだ接合又はその他の構造(図1では

40

50

見えないが、以降の図面に示す)によって回路基板 20 と電気的に接続されてもよい。

【0014】

回路基板 20 は、半導体チップパッケージ基板、回路カード、又は実際上、他のあらゆる種類のプリント回路基板であってもよい。回路基板 20 に対してモノリシック構造を用いることもできるが、より典型的な構成では、ビルドアップ設計を利用するであろう。この点において、回路基板 20 は、1 つ以上のビルドアップ層が上方に形成され、かつ、付加的な 1 つ以上のビルドアップ層が下方に形成された中央コアから構成され得る。コア自身は、1 つ以上の層の積層体から構成され得る。このような構成の 1 つの例は、いわゆる「2-2-2」構成と呼ぶことができ、この構成では、単層コアが、2 セットの 2 層のビルドアップ層の間に積層される。半導体チップパッケージ基板として実装される場合、回路基板 20 内の層の数は、4 層から 16 層、又は 17 層以上に及び得るが、4 層未満であってもよい。いわゆる「コアレス」設計が用いられてもよい。回路基板 20 の層は、金属相互接続が組み込まれた、例えば様々な周知のエポキシなどの絶縁材料から構成されてもよい。ビルドアップ以外の多重層構造が用いられてもよい。任意で、回路板 20 は、周知のセラミックス、又は、パッケージ基板もしくはその他のプリント回路板に適するその他の材料から構成されていてよい。

【0015】

半導体チップ 15 と、図示されていない別の回路デバイスとの間で電源、接地及び信号の伝達を提供するために、回路基板 20 には、多数の導体トレース及びビアならびにその他の構造が設けられている。これらの伝達を容易にするために、回路基板 20 には、ピングリッドアレイ、ボールグリッドアレイ、ランドグリッドアレイ又はその他の種類の相互接続スキームの形態の入出力が設けられてもよい。

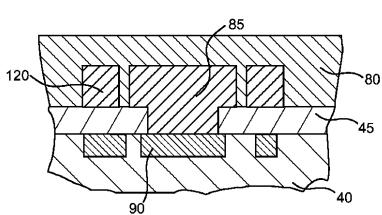

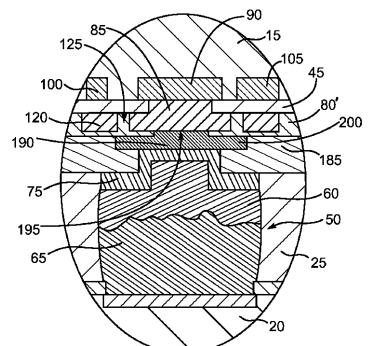

【0016】

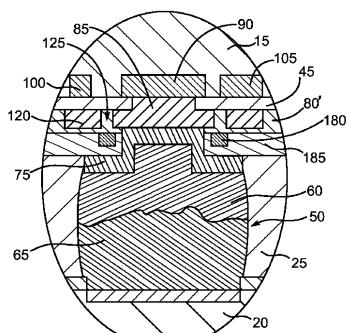

断面 2-2 における図 1 の断面図である図 2 と併せて、半導体チップ 15 のさらなる詳細を説明する。図 2 へ進む前に、パッケージ 10 の断面図で示される部分の正確な位置に注意を払うと便利である。断面 2-2 は、縁部 30 を含む、半導体チップ 15 の小さな部分を通過することに注意されたい。こうした状況を確認した上で、次いで図 2 を参照する。上述したように、半導体チップ 15 は、バルク半導体又は SOI (semiconductor-on-insulator) 構成として構成されていてもよい。この例示的な実施形態では、半導体チップ 15 は、バルク半導体層 35 と半導体デバイス層 40 とを含むバルク半導体として実装される。半導体デバイス層 40 は、半導体チップ 15 の機能を提供する様々な回路を含み、一般的には、半導体チップ 15 とやりとりする電源、接地及び信号の伝達を容易にする、複数のメタライゼーション層及び/又はその他の種類の導体層を含むであろう。パッシベーション構造 45 は、半導体デバイス層 40 上に形成されており、複数層の絶縁材料から構成されてもよい。パッシベーション構造 45 に関するさらなる詳細は、以下の図面と併せて説明する。半導体チップ 15 は、回路基板 20 にフリップチップ実装され、複数のはんだ構造又ははんだ接合により回路基板 20 と電気的に接続されてもよく、複数のはんだ構造又ははんだ接合のうち 2 つをそれぞれ 50, 55 と符号をつけて示す。断面 2-2 の位置に起因して、はんだ接合 55 の一部だけが視認できる。

【0017】

アンダーフィル材料層 25 は、半導体チップ 15 と基板 20 との間に分散しており、半導体チップ 15、はんだ接合 50, 55 など、及び回路基板 20 の熱膨張係数 (CTE) の差の影響を低減する。アンダーフィル材料層 25 は、例えば、シリカ充填剤及びフェノール樹脂と混合したエポキシ樹脂であってもよく、リフロー処理の前又は後に堆積され、はんだ接合 50, 55 を確立してもよい。適切な熱硬化が用いられてもよい。

【0018】

以下のはんだ接合 50 の説明は、その他のはんだ接合の例示になる。はんだ接合 50 は、はんだ構造又はバンプ 60 を含み、これは、予備はんだと呼ばれることがある他のはんだ構造 65 に金属接合されている。はんだバンプ 60 と予備はんだ 65 とは、はんだリフロー処理によって金属接合される。不規則な線 70 は、リフロー後における、はんだバン

ブ 6 0 と予備はんだ 6 5 との間の仮想的な境界線を表している。しかしながら、当業者は、そのような境界線 7 0 は、顕微鏡による検査の間であっても、めったにそのように容易に見ることはできないことを理解するであろう。はんだバンプ 6 0 は、様々な鉛ベース又は鉛フリーはんだから構成されてもよい。例示的な鉛ベースのはんだは、例えば約 6 3 % の S n 及び 3 7 % の P b などの共晶比、又はその近傍の組成を有していてもよい。鉛フリーの例は、錫 - 銀 ( 約 9 7 . 3 % の S n 、 2 . 7 % の A g ) 、錫 - 銅 ( 約 9 9 % の S n 、 1 % の C u ) 、錫 - 銀 - 銅 ( 約 9 6 . 5 % の S n 、 3 % の A g , 0 . 5 % の C u ) などを含む。予備はんだ 6 5 は、同じ種類の材料で構成されてもよい。任意で、予備はんだ 6 5 は、単一のはんだ構造又ははんだと導電性ポストとの構成を選択することで、除去されてもよい。

10

#### 【 0 0 1 9 】

はんだバンプ 6 0 は、アンダーバンプメタライゼーション又は U B M 構造と別称される導体構造 7 5 に金属接合されてもよい。U B M 構造 7 5 の一部は、パッシベーション構造 4 5 上に配置された高分子膜 8 0 を通って突出し、導電体又はアクティブ端子パッド 8 5 とオーミック接触している。U B M 構造 7 5 の別の部分は、高分子膜 8 0 の外面に取り付けられている。高分子膜 8 0 は、柔軟な保護膜を提供するように設計されており、したがって、ポリイミド、ベンゾシクロブテンなどの様々な材料から構成されてもよい。アクティブ端子パッド 8 5 は、半導体チップ 1 5 における複数のメタライゼーション層の一部であってもよい、チップ 1 5 内の別の導体構造又はパッド 9 0 に電気的に接続されている。実際に、いくつかのこののような導体又はトレースは、それぞれ 9 5 , 1 0 0 , 1 0 5 と符号をつけて示されている。導体パッド 8 5 は、電源、接地又は信号の入出力部位として使用されてもよいし、あるいはその他の構造に電気的に結合されていないダミーパッドとして使用されてもよい。予備はんだ 6 5 は、同様に、はんだマスク 1 1 5 と横方向に境を接する導体 1 1 0 に金属接合されている。導体構造 1 1 0 は、複数層の導体構造であって、ビアにより相互接続され、誘電体材料層 ( 図示せず ) により取り囲まれるもの一部を形成してもよい。

20

#### 【 0 0 2 0 】

アクティブ端子パッド 8 5 は、ある程度の横方向の大きさ X 1 ( プロセス技術によって異なる ) を有する。従来の設計では、アクティブ端子パッド 8 5 は、はんだバンプ 6 0 及び接合 5 0 によってパッシベーション構造 4 5 上にかかる機械的応力を打ち消すのを助けるために、はるかに大きな横方向の寸法 X 2 で形成されている。これらの応力は、鉛フリーはんだを用いた場合、特に高くなり得る。応力が充分耐え難ければ、パッシベーション構造 4 5 が破碎し得て、多くの潜在的な問題に至る。しかしながら、アクティブ端子パッド 8 5 がこのように幅広い横方向の寸法 X 2 で形成される場合には、半導体チップ 1 5 の導体トレース 1 0 0 , 1 0 5 との重なりが生じ、その結果、寄生容量ひいては付随する電気的性能の低下を生じさせ得る。大きな寄生容量を引き起こすことなしにパッシベーション構造 4 5 用の十分な応力保護を提供するには、アクティブ端子パッド 8 5 は、横方向の寸法 X 1 で構成され、ひいては導体トレース 1 0 0 , 1 0 5 との重複なしに構成される。また、アクティブ端子パッド 8 5 は、間隙 1 2 5 によってアクティブ端子パッドから離間された導体又は仮想パッド 1 2 0 によって横方向に取り囲まれている。仮想パッド 1 2 0 は、アクティブ端子パッド 8 5 から電気的に絶縁されている。この場合、電気的な絶縁は、間隙 1 2 5 内の高分子膜 8 0 の一部により提供される。仮想パッド 1 2 0 は、所望に応じて、電源又は接地に対して、浮かんでいてもよいし、結合されていてもよい。

30

#### 【 0 0 2 1 】

様々な物理プロセスによって、パッシベーション構造 4 5 にかかる応力がもたらされる。1 つの原因是、熱サイクルの間における、半導体チップ 1 5 と、回路基板 2 0 と、アンダーフィル材料層 2 5 との間の歪み速度の違いである。差応力の別の要因は、はんだバンプ 6 0 と予備はんだ 6 5 との間の延性の違いであり得る。エッジ効果として知られている現象のために、これらの差応力及び合成歪みは、半導体チップ 1 5 の縁部 3 0 の近くで最大になり得るものであり、縁部 3 0 から離れ、半導体チップ 1 5 の中心に向かって突き出

40

50

している矢印 130 により示される方向に向かって漸減し得る。

【0022】

パッシベーション構造応力につながるいくつかの例示的な物理的な力の説明に役立てるために、破線の楕円 135 に囲まれた図 2 の一部を拡大して、図 3 に示す。図 3 は断面図であるが、クロスハッチングを省いて、当該構造に対して作用する様々な力をより明瞭に示され得るようにしている。ここでは、半導体チップ 15 の小さな部分、バンプパッド 90、パッシベーション構造 45、高分子膜 80、アクティブ端子パッド 85、仮想パッド 120、UBM 構造 75、アンダーフィル材料層 25、はんだマスク 115、導体パッド 110、及び回路基板 20 の小さな部分といった特徴が表示されている。はんだ接合 50 は、破線で表示されている。半導体チップ 15 の中心に向かう方向は、矢印 130 によって示されている。10

【0023】

製造中、信頼性試験中若しくはデバイス動作中の基板 20 の反りに起因して、又は、CTE の不一致を主因として、基板 20 は、はんだ接合 50 を介して、一連の下向きの矢印によって概略的に表される分布荷重を与える。分布荷重の強度は、長さ L に沿って、最大

1 から最小 2 まで変化し、ここで、1 及び 2 の単位は、単位長さ当たりの力である。分布荷重の合力 R は、x 軸上の点 x\_n に配置されている。UBM 構造 75 に作用する分布荷重は、図 3 が断面図であることから、線分布として表されている。実際には、分布荷重は、面積分布になる。中心に向かう方向 130 における x 軸に沿った距離に応じた、

1 から 2 までの力の強度の漸減は、本明細書の「背景技術」の段落で説明したエッジ降下に起因する。コーナー点 A に対する合力 R の位置は、コーナー点 A の周りで UBM 構造 75 に作用するモーメント M を生じる。コーナー点 A は、UBM 構造 75 の延性及び距離 L に依存する、下方かつ点 A の周りにおける UBM 構造 75 の望ましくない旋回運動の枢動点として振る舞い得る。モーメント M に起因して、パッシベーション構造 45 の領域 B は圧縮状態にあり、反対側の領域 C は伸張状態にあることもあり得る。しかしながら、仮想パッド 120 の存在は、領域 B 及び C のために応力保護をもたらす。20

【0024】

例示的な UBM 構造 75 を形成するための例示的な方法は、最初に図 4 を参照し、図 5、図 6、図 7、図 8、図 9、図 10 及び図 11 を参照することによって理解されるであろう。図 4 は、半導体チップ 15 の半導体デバイス層 40 の小さな部分と、導体パッド 90 と、トレース 100, 105 と、パッシベーション構造 45 とを示す断面図である。なお、図 4 は、図 2 及び図 3 に示される方位からひっくり返された半導体デバイス層 40 及び導体パッド 90 を図示していることが理解されるべきである。本明細書に記載されるプロセスは、ウエハレベル又はダイバイダイ方式で行われてよいことが理解されるべきである。この段階で、導体パッド 90 及びパッシベーション構造 45 が形成されている。導体パッド 90 は、アルミニウム、銅、銀、金、チタン、耐火金属、耐火金属化合物、これらの合金などの様々な導体材料から構成されてもよい。単一構造の代わりに、導体パッド 90 は、チタン層に続いてニッケル-バナジウム層、さらに銅層が続くなどの複数の金属層の積層体から構成されてもよい。他の実施形態では、チタン層は、銅層で覆われ、ニッケルのトップコーティングが続いているてもよい。しかしながら、当業者は、多種多様の導電性材料が導体パッド 90 に使用され得ることを理解するであろう。例えば物理蒸着、化学蒸着、めっきなどのように、金属材料を適用するための様々な周知の技術が用いられてもよい。付加的な導体構造を使用できることが理解されるべきである。30

【0025】

パッシベーション構造 45 は、二酸化ケイ素及び窒化ケイ素などの誘電材料の交互層から構成されてもよく、周知の化学蒸着 (CVD) 及び / 若しくは酸化、又は酸化技術によって形成されてもよい。適切なリソグラフィーマスク 140 は、パッシベーション構造 45 上に形成され、周知のリソグラフィー工程によって、導体パッド 90 と位置合わせされた適切な開口部 145 がパターニング形成されてもよい。その後、1 つ以上の材料除去工程が、パッシベーション構造 45 内に開口部 150 を形成するために実行されて、これに40

より、導体パッド 90 が露出してもよい。例えば、材料除去工程は、パッシベーション構造 45 のために選択された特定の材料に適した 1 つ以上のドライエッチング工程及び／又はウェットエッチング工程を含むことができる。材料を除去して開口部 150 を得た後、マスク 140 は、灰化、溶媒剥離などによって剥離されてよい。

【0026】

開口部 150 がパッシベーション構造 45 内に形成され、且つ、導体パッド 90 が露出された状態で、アクティブ端子パッド 85、仮想パッド 120 及び高分子膜 80 の形成を進めることができる。これらの工程は、様々な順序で行うことができる。例えば、高分子膜 80 の適用は、アクティブ端子パッド 85 及び仮想パッド 120 の形成前又は形成後とすることが可能である。この例示的な実施形態において、図 5 を参照すると、アクティブ端子パッド 85 及び仮想パッド 120 は、図 2 に示すように、高分子膜 80 を適用する前に形成され得る。アクティブ端子パッド 85 及び仮想パッド 120 は、物理蒸着、めっき又はその他の材料形成技術によってパッシベーション構造 45 上に形成されてもよい。パッシベーション構造への接着、及びその他の導体との金属接合に有益性を示す様々な導体材料が用いられてもよい。実際に、導体構造 90 に関連して説明した同じタイプの材料及び技術は、アクティブ端子パッド 85 及び仮想パッド 120 にも同様に使用され得る。この例示的な実施形態では、アクティブ端子パッド 85 及び仮想パッド 120 は、銅の物理蒸着後、リン酸ウェットエッチングなどの適切なエッチングを行うことにより形成されてもよい。使用されるいかなる加工プロセスにおいても、アクティブ端子パッド 85 と仮想パッド 120 との間の間隙 125 は、ショートを避けるために、連続的であることを確実にすべきである。アクティブ端子パッド 85 の一部は、パッシベーション構造 45 の開口部 150 を充填し、下層の導体パッド 90 との金属接合を形成する。必要に応じて、予備的な自然酸化物剥離エッチングを行って、導体パッド 90 の表面が、アクティブ端子パッド 85 との金属接合を可能にするのに十分に露出していることを確実にしてもよい。

【0027】

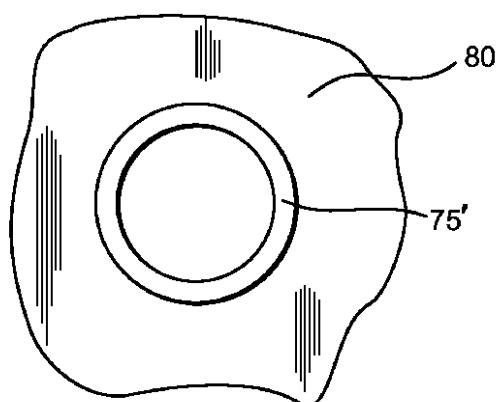

図 6 は、形成後のアクティブ端子 85 及び仮想パッド 120 の平面図である。この例示的な実施形態において、アクティブ端子パッド 85 及び仮想パッド 120 は、図示のように、概して円形かつ環状の形状を有してもよい。アクティブ端子パッド 85 と仮想パッド 120 との間の間隙 125 は、連続的である。しかしながら、円形かつ環状の接地面以外の、実質的にあらゆる他の形状を使用してもよいことが理解されるべきである。セグメント構造を、仮想パッド 120 に使用することができる。

【0028】

図 7 に示すように、高分子膜 80 は、アクティブ端子パッド 85、仮想パッド 120 及びパッシベーション構造 45 の露出部分の上に適用される。高分子膜 80 は、ポリイミド、ベンゾシクロブテン、又は窒化ケイ素などの他の絶縁材料で構成されてもよく、スピンドル法、CVD 又は他の技術によって堆積されてもよい。硬化ベーク処理は、適用後に行われてもよい。高分子膜 80 が最初に適用される他の方法が使用される場合には、高分子膜 80 内に適切な開口部（図示せず）を形成して、アクティブ端子パッド 85 及び仮想パッド 120 を形成する必要がある。これは、高分子膜 80 の組成に応じて様々な方法で達成することができる。ポリイミド高分子膜 80 は、光活性化合物を注入され、リソグラフィーでパターニングされ、そして材料堆積又はめっきプロセスを受けてもよい。高分子層 80 が、露光及び現像を経て材料除去することができない場合には、適切なリソグラフィーマスクが適用され、エッチングが行われることにより、必要な開口部を得るようにしてもよい。ここで、半導体領域 40、導体パッド 90 及びアクティブ端子パッド 85 から電気経路を確立するための構造の形成について説明する。

【0029】

図 8 を参照すると、高分子膜 80 は、リソグラフィーによりパターニングされ、後に形成されるUBM構造 75（図 2 に示されている）のための適切な開口部が形成されてもよい。これは、高分子膜 80 の組成に応じて様々な方法でなされ得る。ポリイミド高分子膜 80 は、光活性化合物が注入され、リソグラフィーでパターニングされ、そして材料堆積

10

20

30

40

50

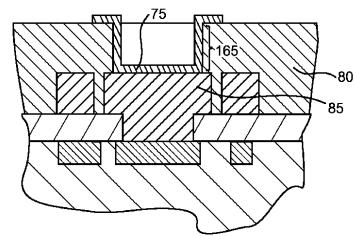

又はめっきプロセスを受けてもよい。この例示的な実施形態では、高分子膜 80 は、光活性化合物を含有している。非接触マスク 155 は、アクティブ端子パッド 85 に位置合わせされるが、仮想パッド 120 を覆うことなしに、高分子膜 80 上に配置されている。次いで、適切な放射線 160 による露光が行われる。マスク 155 によって覆われていない高分子膜 80 の部分は、現像液において不溶性が与えられている。図 9 を参照すると、図 8 に示した非接触マスク 155 が除去され、高分子膜 80 が現像されて、アクティブ端子パッド 85 の一部が露出し、アクティブ端子パッド 85 に概して位置合わせされた開口部 165 が得られる。仮想パッド 120 は、覆われたままである。高分子層 80 が、露光及び現像を経て材料除去することができない場合には、適切なリソグラフィーマスクが適用され、エッチングが行われることにより、必要な開口部を得てもよい。

10

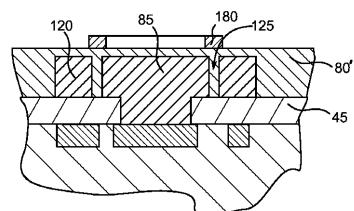

### 【0030】

図 10 と共に UBM 構造 75 の形成を説明する。当業者は、UBM 構造が、いくつかの重要な目標を満たすように設計されていることを理解するであろう。すなわち、いくつかの重要な目標とは、上層のはんだバンプ又はその他のはんだ構造に接合すること、下層の導体構造、ここではアクティブ端子パッド 85 と導電性の接合部分を確立すること、必要に応じて下層又は周囲の誘電体と接合することであり、いずれの場合も、下層の導体構造内へのはんだ成分の拡散に対するバリアを提供しながら行われるものであり、そうでなければこれらの導体構造が劣化することがある。これらの材料要件を満たすために、UBM 構造は、はんだ適用プロセスの種類に応じて、異なる組成の複数の膜を使用してもよい。この例示的な実施形態では、UBM 構造 75 は、連続して適用された一連のフィルムとして形成されてもよい。印刷されたはんだバンプでは、最初に、チタン又はチタン - タングステン膜が、高分子膜 80 上及び開口部 165 の側壁に沿って、並びにアクティブ端子パッド 85 上にスパッタリング蒸着されてもよい。チタン膜は、接着層として機能し、高分子膜 80 に容易に接着する。次に、ニッケル、ニッケル - バナジウム又はその他の材料からなるバリア層が、めっき又は他の方法でチタン膜上に堆積される。最後に、銅、金又はその他の材料からなるはんだ濡れ性層が、めっき、スパッタ堆積又は他の技術によって、ニッケル膜に適用される。材料の堆積に続いて、ウェットエッチングが行われ、図 10 に示すようなパターニングされた UBM 75 が得られる。しかしながら、後に形成するはんだバンプを確立するために、バンプめっきプロセスが使用される場合には、UBM 構造 75 は、上述のタイプの接着層から構成されていてもよく、無電解めっき又はスパッタ堆積によって堆積される銅などのめっきシード層が続き、さらには、上述のタイプのニッケル又はニッケル - バナジウムのバリア層が続く。めっきバンププロセスでは、ウェットエッチングが同様に行われる。しかし、ニッケルのバリア膜は、エッチングによるパターニングを必要としないこともある。

20

### 【0031】

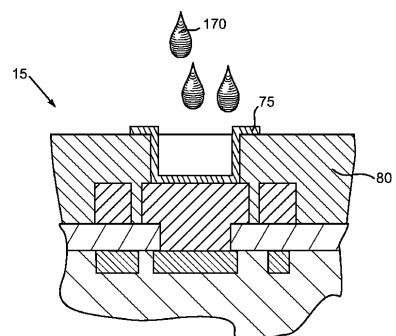

所定の場所に UBM 構造 75 がある状態で、適切なはんだ材料 170 が、図 11 に示すように、印刷、めっき又は他の方法で UBM 構造 75 上に配置されてもよい。模式的に示すように、はんだ材料 170 は、図 2 に示したはんだバンプ 60 になる。図 2 に示すようなはんだバンプ 60 を確立するために、堆積されたはんだ 170 には、様々なプロセスが使用され得る。1 つの例示的な実施形態では、印刷プロセスが使用される。ここでは、適切なリソグラフィーマスク（図示せず）が高分子層 80 に適用されることもある。次いで、はんだ 170 は、スクリーン印刷プロセスによって堆積される。別の例示的な実施形態では、めっきプロセスを用いてもよい。この点に関して、適切なリソグラフィーマスクは、前述したが図示されていないマスクと大して違わないが、UBM 構造 75 を露出させる開口部が形成されてもよい。この段階では、はんだ 170 は、UBM 構造 75 にめっきされてもよい。適用技術によらず、半導体チップ 15 の熱リフローが続いて、図 2 のバンプ 60 が確立される。

30

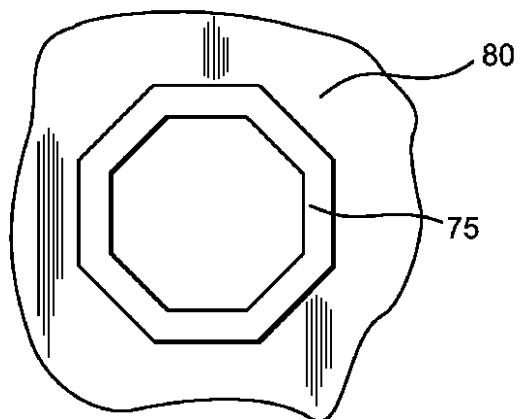

### 【0032】

図 12 及び図 13 は、UBM 構造の実施形態の連続する平面図を示している。図 12 は、概して八角形の接地面を有する UBM 構造 75 を示す。高分子膜 80 の小さな部分が表

40

50

示されていることに注意されたい。図13は、概して円形の接地面を有する別のUBM構造75'の平面図を示す。ここでもまた、高分子膜80の小さな部分だけが表示されている。言うまでもなく、UBM構造75, 75'は、様々な異なるタイプの接地面を採用することができる。

#### 【0033】

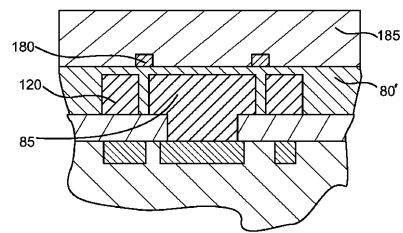

図14は、図3と同様の断面図であるが、別の例示的な実施形態の断面図であり、通常のクロスハッチングが入れられてある。この例示的な実施形態は、本明細書の他の箇所で説明し、図2に概して示されている実施形態の多くの特徴を共有している。よって、半導体チップ15は、複数の導体パッド（1つの導体パッドが符号90として示されている）と、アクティブトレース100, 105とを備える。パッシベーション構造45は、導体トレース100, 105に亘って、且つ、少なくとも部分的に導体パッド90に亘って、半導体チップ15上に配置されている。アクティブ端子パッド85及び仮想パッド120は、概して本明細書の他の箇所で説明したように構成及び形成加工されてもよい。高分子膜80'は、重要な留意点とともに本明細書の他の箇所で説明したように、同様に形成されてもよい。この例示的な実施形態では、高分子膜80'は、いくらか小さい厚さで形成されており、高分子膜80'の小さな部分だけが仮想パッド120を覆うようにしてもよい。間隙125は、概して本明細書の他の箇所で説明したようであってよく、ひいては高分子膜80'の一部分で満たされてもよい。しかしながら、この例示的な実施形態では、UBM構造75と、それ以外の比較的柔軟な材料であって、他の点ではパッシベーション構造を圧迫する、間隙125内に位置する高分子膜80'の一部分との間の応力支持を提供するように設計されている第2の仮想パッド180を含む。図14に開示された実施形態の形成は、注目すべきいくつかの違いと共に図4から図8に関連して上述したように概して進めることができる。図8によるプロセスフローでは、高分子膜80の実質的な材料厚さは、アクティブ端子パッド85及び仮想パッド120を越える。代替の実施形態では、高分子膜80'は、比較的薄くなつて、アクティブ端子パッド85及び仮想パッド120よりも薄いコーティングが存在するようにしている。この段階で、図15に示すように、第2の仮想パッド180は、アクティブ端子パッド85及び仮想パッド120を形成するのと同じタイプの技術、すなわち、本明細書の他の箇所に記載のような材料成形技術に加えた物理蒸着、めっき又はその他の材料適用技術を用いて、高分子フィルム80'上に形成される。第2の仮想パッド180は、間隙125を覆って、パッシベーション構造45を保護することに注意されたい。接地面に関しては、第2の仮想パッド180は、図示のような環状又はその他の形状であつてもよい。アクティブ端子パッド85が短絡しない限り、第2の仮想パッド180は、仮想パッド120に機械的に接続できる。

#### 【0034】

ここで図16を参照すると、第2の仮想パッド180の形成後に、追加の高分子膜185が、本明細書の他の箇所に記載された高分子膜80, 80'用の材料及び技術を用いて、高分子膜80'上に形成されてもよい。その後、プロセスフローは、図9から図11と共に本明細書に記載の技法を辿って、UBM構造75と、はんだバンプ60と、仮想パッド120を除くアクティブ端子パッド85への接続とを確立する。プロセスフローは、回路基板20の実装と、予備はんだ65に対するはんだ接合50の確立と、アンダーフィル25の堆積とを含むようにしてもよい。

#### 【0035】

図17は、図14と同様の断面図であるが、さらに別の例示的な実施形態の断面図である。この別の実施形態は、図14に示された実施形態の特徴の多くを共有している。すなわち、この特徴とは、半導体チップ15、導体パッド90、導体トレース100, 105、アクティブ端子パッド85、仮想パッド120及び比較的薄い高分子膜80'である。しかしながら、間隙125内の柔軟な材料に関連付けられた応力の望ましい保護レベルを提供するために、図14に示す第2の仮想パッド180は、本質的に非仮想である導体パッド190に変更されてもよい。この導体パッド190は、アクティブ端子パッド85とオーミック接触を確立する中央接触部195と、高分子膜80'上で間隙125の近くに

10

20

30

40

50

配置され、必要な応力保護を提供するように設計されたフランジ部 200 とを有する。図 17 に示す別の実施形態を確立するためのプロセスフローは、図 4 ~ 図 8 とともに本明細書の他の箇所で説明されたプロセスフローをここでも辿ってもよい。ただし、高分子膜 80' が、図 8 に示されているものよりも相対的に薄い厚さで形成されるという条件付きである。この段階で、適切な開口部が高分子膜 80' に形成され、その後、材料堆積又はめっきプロセスを用いて、パッド 190 が形成されるべきである。堆積プロセス及び / 又はめっきプロセスに続いて、パッド 190 は、エッティング又はその他の材料除去技術により、図示の構成にパターニング形成されてもよく、その後、追加の高分子膜 185 は、高分子膜 80' 及び導体パッド 190 に亘って形成されてもよい。この段階で、UBM 構造 75 と、はんだバンプ 60 と、仮想パッド 120 を除くアクティブ端子パッド 85 への接続 10 とが確立されてもよい。また、予備はんだ 65 に対するはんだ接合 50 の確立と、アンダーフィル 25 の堆積とが含まれてもよい。

#### 【 0036 】

本明細書に開示した例示的な実施形態は何れも、例えば半導体、磁気ディスク、光ディスク若しくはその他の記憶媒体などのコンピュータ可読媒体内に配置された命令に組み込まれてもよいし、コンピュータデータ信号として組み込まれてもよい。命令又はソフトウェアは、本明細書に開示された回路構造を合成及びシミュレートすることが可能であってもよい。例示的な実施形態では、Cadence 社の APD、Encore などの電子設計自動化プログラムを、開示された回路構造を合成するために使用することができる。得られたコードは、開示された回路構造を形成するために使用することができる。 20

#### 【 0037 】

本発明は、種々の修正及び代替的な形態を許容し得る一方で、特定の実施形態が例示を目的として図面に示され、又はここに詳細に説明されてきた。しかし、本発明は、開示されている特定の形態に限定されることを意図していないことが理解されるべきである。むしろ、本発明は、以下に添付される特許請求の範囲によって画定される本発明の精神及び範囲内に含まれる全ての修正、均等物及び代替案に及ぶものである。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図8】

FIG. 8

【図6】

FIG. 6

【図9】

FIG. 9

【図7】

FIG. 7

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

【図 13】

FIG. 13

【図 14】

FIG. 14

【図 15】

FIG. 15

【図16】

FIG. 16

【図17】

FIG. 17

---

フロントページの続き

(73)特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド

A D V A N C E D M I C R O D E V I C E S I N C O R P O R A T E D

アメリカ合衆国、94088-3453 カリフォルニア州、サニベイル、ピィ・オウ・ボック

ス・3453、ワン・エイ・エム・ディ・プレイス、メイル・トップ・68 (番地なし)

(74)代理人 100108833

弁理士 早川 裕司

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ローデン アール. トーパシオ

カナダ国 L3R 4S8、オンタリオ州、マーカム、カルマ ロード 7

(72)発明者 マイケル ゼット. スー

アメリカ合衆国 78681 テキサス州、ラウンド ロック、ロック スプリング コーブ 9

09

(72)発明者 ニール マクレラン

アメリカ合衆国 78737 テキサス州、オースティン、ヤング レーン 8800

審査官 高 須 甲斐

(56)参考文献 特開2007-335629 (JP, A)

特表2010-535411 (JP, A)

特開2007-103848 (JP, A)

米国特許第06118180 (US, A)

米国特許第07098540 (US, B1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60