(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-15400

(P2012-15400A)

(43) 公開日 平成24年1月19日(2012.1.19)

(51) Int.Cl. F 1 テーマコード (参考)

|                    |                  |      |       |     |       |

|--------------------|------------------|------|-------|-----|-------|

| <b>HO1L</b> 27/146 | <b>(2006.01)</b> | HO1L | 27/14 | F   | 4M118 |

| <b>HO4N</b> 5/369  | <b>(2011.01)</b> | HO1L | 27/14 | A   | 5C024 |

| <b>HO4N</b> 5/374  | <b>(2011.01)</b> | HO4N | 5/335 | 69O |       |

| <b>HO4N</b> 5/378  | <b>(2011.01)</b> | HO4N | 5/335 | 74O |       |

|                    |                  | HO4N | 5/335 | 78O |       |

審査請求 未請求 請求項の数 9 O.L. (全 14 頁)

(21) 出願番号 特願2010-151973 (P2010-151973)

(22) 出願日 平成22年7月2日 (2010.7.2)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 乾 文洋

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

F ターム (参考) 4M118 AA10 AB01 BA14 BA19 CA03

DD04 DD09 DD12 FA06 FA25

FA33 GA02 GD04

5C024 CX03 CY47 GX03 GX16 GX18

GY31 HX01

(54) 【発明の名称】 固体撮像装置

(57) 【要約】

【課題】 光電変換部と、周辺回路部もしくは画素回路の一部とを別基板に分けて電気的に接続する構成における好適なウエルの分離構造を提供すること。

【解決手段】 本発明は、光電変換部と、該光電変換部で生じた信号を増幅する増幅トランジスタとを含む画素を複数有し、複数の光電変換部が配された第1の基板と、複数の増幅トランジスタが配された第2の基板とを有する固体撮像装置であって、前記増幅トランジスタのソース領域及びドレイン領域が配される第1導電型のウエルは、少なくとも一方向に隣接する増幅トランジスタのソース領域及びドレイン領域が配される第1導電型のウエルと分離されていることを特徴とする。

【選択図】 図 2

## 【特許請求の範囲】

## 【請求項 1】

光電変換部と、該光電変換部で生じた信号を増幅する増幅トランジスタとを含む画素を複数有し、

複数の光電変換部が配された第1の基板と、

複数の増幅トランジスタが配された第2の基板とを有する固体撮像装置であって、

前記増幅トランジスタのソース領域及びドレイン領域が配される第1導電型のウエルは

、少なくとも一方向に隣接する増幅トランジスタのソース領域及びドレイン領域が配される第1導電型のウエルと分離されていることを特徴とする固体撮像装置。10

## 【請求項 2】

隣接する第1導電型のウエル間には、第2導電型の半導体領域が配されることにより、前記第1導電型のウエル間が分離されていることを特徴とする請求項1に記載の固体撮像装置。10

## 【請求項 3】

前記増幅トランジスタのソースと前記第1導電型のウエルとが電気的に接続されていることを特徴とする請求項1または2のいずれかに記載の固体撮像装置。

## 【請求項 4】

各画素に、前記増幅トランジスタの入力ノードの電圧をリセットする複数のリセットトランジスタを有し、20

前記複数のリセットトランジスタの各々は、同一画素の前記増幅トランジスタが配される前記分離された第1導電型のウエルに配されることを特徴とする請求項1～3のいずれか1項に記載の固体撮像装置。

## 【請求項 5】

各画素に選択トランジスタを有し、前記複数の選択トランジスタの各々は、同一画素の前記増幅トランジスタが配された前記分離された第1導電型のウエルに配されることを特徴とする請求項1～4のいずれか1項に記載の固体撮像装置。

## 【請求項 6】

前記増幅トランジスタが行列状に配されており、

前記第1導電型のウエルが複数の増幅トランジスタの列間で分離されていることを特徴とする請求項1～5のいずれか1項に記載の固体撮像装置。30

## 【請求項 7】

前記増幅トランジスタが行列状に配されており、

前記第1導電型のウエルが複数の増幅トランジスタの行間で分離されており、

分離されたウエルごとに第1の電圧と、該第1の電圧よりも高い第2の電圧を供給する電圧供給部を有することを特徴とする請求項1に記載の固体撮像装置。

## 【請求項 8】

前記第1導電型のウエルが画素毎に分離されていることを特徴とする請求項1～5のいずれか1項に記載の固体撮像装置。

## 【請求項 9】

前記増幅トランジスタが電流源と共にソースフォロワ回路を構成することを特徴とする請求項1～8のいずれか1項に記載の固体撮像装置。40

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は固体撮像装置に関する。

## 【背景技術】

## 【0002】

固体撮像装置において、光電変換部と、周辺回路部もしくは画素回路の一部とを別基板に分けて形成し、それらを電気的に接続する構成が知られている。50

**【0003】**

特許文献1には、第1の基板に受光画素および貫通配線とが配され、第2の基板に読み出し回路が配された構成が開示されている。読み出し回路は、貫通配線を介して電気信号を読み出して画像信号として出力する。この固体撮像装置は、第1の基板の反対面と、第2の基板の読み出し回路とが対向する向きに配置され、貫通配線と読み出し回路との端子間が電気的に接合された構成となっている。

**【0004】**

また特許文献2には一の基板に光電変換部及び画素回路とをモノリシックに配した構成において、光電変換部を構成するウエルを画素毎に分離する構成が開示されている。

**【0005】**

更に特許文献3には、一の基板に光電変換部及び画素回路とをモノリシックに配した構成において、アンプ用トランジスタのウエルを画素に含まれる他のトランジスタのウエルと電気的に分離した構成が開示されている。

10

**【先行技術文献】****【特許文献】****【0006】**

【特許文献1】特開2008-235478号公報

【特許文献2】特開2006-196729号公報

【特許文献3】特開2001-160619号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

特許文献1～3においては、光電変換部と、周辺回路部もしくは画素回路の一部とを別基板に分けて電気的に接続する構成において、好適なウエルの分離構造に関しては検討が不充分であった。

**【0008】**

ウエルを分離している特許文献2においては、飽和した画素から漏れ出した電荷による影響を考慮して光電変換部を構成するウエルを画素毎に分離している。そのため、基板を分けた構成において光電変換部が配されない基板のウエル分離に関して何等述べられていない。

30

**【0009】**

また特許文献3においては、画素を構成するアンプ用トランジスタの基板バイアス効果によるしきい値の変動を抑えることを目的としてアンプ用トランジスタのウエルを、画素の他のトランジスタのウエルと分離している。しかしながら他の画素に含まれるアンプ用トランジスタどうしのウエルに関しては何等述べられていない。

**【0010】**

また特許文献2、3に共通していえるのは、一の基板に光電変換部と画素回路とがモノリシックに配された構成であるため、ウエルを分離するために余分なスペースが必要となり、光電変換部の受光面積を圧迫するという課題があった。

40

**【0011】**

本発明は上記課題に鑑み、光電変換部と、周辺回路部もしくは画素回路の一部とを別基板に分けて電気的に接続する構成における好適なウエルの分離構造を提供することを目的とする。

**【課題を解決するための手段】****【0012】**

本発明は、光電変換部と、該光電変換部で生じた信号を増幅する増幅トランジスタとを含む画素を複数有し、複数の光電変換部が配された第1の基板と、複数の増幅トランジスタが配された第2の基板とを有する固体撮像装置であって、前記増幅トランジスタのソース領域及びドレイン領域が配される第1導電型のウエルは、少なくとも一方向に隣接する増幅トランジスタのソース領域及びドレイン領域が配される第1導電型のウエルと分離さ

50

れていることを特徴とする。

【発明の効果】

【0013】

本発明によれば、光電変換部と、周辺回路部もしくは画素回路の一部とを別基板に分けて電気的に接続する構成における好適なウエルの分離構造を提供することが可能となる。

【図面の簡単な説明】

【0014】

【図1】本発明の画素の等価回路図の一例である。

【図2】本発明の固体撮像装置の断面の概念図である。

【図3】実施例1の固体撮像装置の上面の概念図である。

10

【図4】実施例1の固体撮像装置の画素の等価回路の一例である。

【図5】実施例1の固体撮像装置の1画素の上面の概念図である。

【図6】ソースフォロワ回路の等価回路図である。

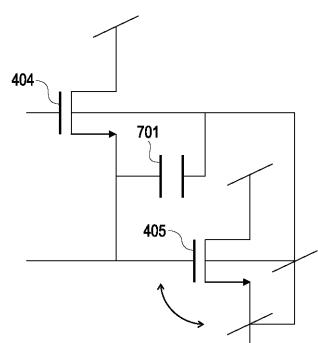

【図7】画素の一部分を抜き出した等価回路図である。

【図8】実施例2の固体撮像装置の上面の概念図である。

【図9】実施例3の固体撮像装置の上面の概念図である。

【発明を実施するための形態】

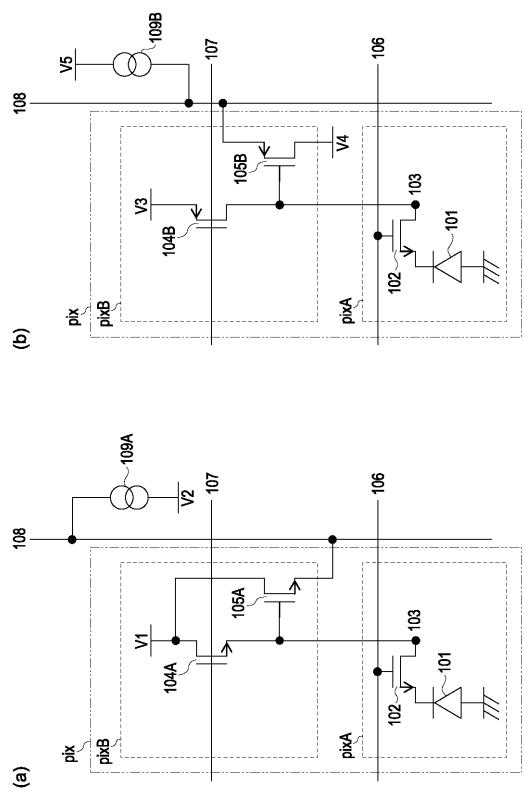

【0015】

図1に本発明に適用可能な固体撮像装置の1画素の等価回路の一例を示す。ここでは1画素のみを示すが実際には画素を複数有して画素配列が構成される。

20

【0016】

101は光電変換部である。光電変換により正孔と電子を生じる。例えばフォトダイオードが用いられる。

【0017】

102は転送部である。光電変換部の電荷を転送する。例えばMOSトランジスタ(転送トランジスタ)が用いられる。

【0018】

103はFDである。電位がフローティング状態で転送部により光電変換部の電荷が転送される。

30

【0019】

104は画素リセット部である。少なくともFDの電位を基準電位に設定する。言い換えると、増幅トランジスタの入力ノードの電圧をリセットしているともいえる。または転送部と同時にオン状態とすることにより光電変換部の電位を基準電位に設定する。画素リセット部としては、例えばMOSトランジスタ(リセットトランジスタ)が用いられる。

【0020】

105は画素増幅部である。光電変換部で生じた電荷対のうち一方の電荷に基づく信号を増幅して出力する。例えばMOSトランジスタが用いられ、この場合には画素増幅部のMOSトランジスタ(増幅トランジスタ)のゲートとFDとが電気的に接続された構成となる。

【0021】

106は転送トランジスタの動作を制御するための転送制御線である。107はリセットトランジスタの動作を制御するためのリセット制御線である。これら制御線には不図示の垂直走査回路からの駆動パルスが供給される。

40

【0022】

108は垂直出力線である。垂直出力線108には、画素列に含まれる複数の画素増幅部で増幅された信号が順次出力される。

【0023】

109は電流源である。増幅部へバイアス電流を供給するためのものである。本回路構成においては増幅MOSトランジスタをソースフォロワ動作させるためのバイアス電流を供給するものである。

50

## 【0024】

V1は図1(a)において増幅トランジスタ及びリセットトランジスタのドレインに供給される電圧である。ここでは共通電圧で記載しているが別電源とすることも可能である。V2は図1(a)において電流源109aに供給される電圧である。

## 【0025】

V3は図1(b)においてリセットトランジスタのドレインに供給される電圧である。V4は図1(b)において増幅トランジスタのドレインに供給される電圧である。V5は図1(b)において電流源109bに供給される電圧である。

## 【0026】

画素を構成する要素のうち、 $p_i \times A$ は第1の基板に配される部分を示し、 $p_i \times B$ は第2の基板に配される部分を示している。 $p_i \times A$ 、 $p_i \times B$ により画素 $p_i \times$ が構成される。

10

## 【0027】

ここで図1(a)と(b)との違いについて説明する。異なる部材にはそれぞれ添字a、bを振って区別している。具体的には、増幅トランジスタ及びリセットトランジスタの導電型が異なり、図1(a)においてはN MOSトランジスタが用いられ、図1(b)においてはP MOSトランジスタが用いられる。これに対応してそれぞれのトランジスタ、電流源に供給される電圧が異なっている。

## 【0028】

図1(a)において、V1は例えば5V、3.3Vなどの電源電圧である。V2はV1よりも低い電圧であり、例えば接地電位である。これに対して図1(b)のV3、V4は、接地電位などの相対的に低い電位であり、V5は3.3V、1.8VなどのV3に比べて高い電圧である。

20

## 【0029】

図1(b)は増幅トランジスタがP MOSトランジスタである。光電変換部は信号電荷として電子を用いる構成となっており、入射光量が大きい場合に、P MOSトランジスタのゲート電位は下がる。これに応じてP MOSトランジスタのソース電位は暗い場合に比べて上昇する方向である。つまり、リセット時に比べて信号振幅が大きい時の垂直出力線の駆動を駆動力が高い状態で行なうことが可能になる。したがって図1(a)の構成に比べて読み出し速度という観点で有利である。従来であれば、このような構成を同一基板に配していたため、画素内でウエルを分ける等、構造として複雑となってしまっていた。これに対して本発明のように、別基板に分けて構成することにより、このような弊害を抑制することが可能となる。更に動作電圧範囲も図1(b)の方を狭くすることが可能となり、低電源電圧化という観点で有利である。

30

## 【0030】

この本質は、増幅トランジスタがP MOSトランジスタである点ではなく、信号電荷と逆極性のトランジスタを用いることである。つまり、信号電荷が電子の場合には増幅トランジスタ及びリセットトランジスタにP MOSトランジスタ、信号電荷がホールの場合にはN MOSトランジスタを用いる点である。転送トランジスタの導電型で言えば、転送トランジスタが第1導電型のMOSトランジスタであり、増幅トランジスタ及びリセットトランジスタが第1導電型と逆導電型の第2導電型のトランジスタとなる。

40

## 【0031】

以上、画素の構成に関して説明したがこれら構成に限られるものではない。例えば増幅トランジスタとして接合型電界効果型トランジスタ(JFET)を用いることもできる。また光電変換部としてホールを信号電荷として用いる構成としてもよい。この場合には転送トランジスタをP MOSトランジスタとする。また複数の光電変換部で増幅トランジスタ、リセットトランジスタを共有する構成としても良い。また、別途増幅トランジスタと直列に選択トランジスタを用いる構成としてもよい。また複数の基板への画素の構成を振り分ける例としては上記の構成に限られない。上記構成以外にも、リセットトランジスタ、増幅トランジスタを第1の基板に配しても良い。更に画素に、増幅トランジスタ、リセ

50

ットトランジスタを設けずに、転送トランジスタにより光電変換部の電荷を直接垂直出力線へ出力する構成としてもよい。

【0032】

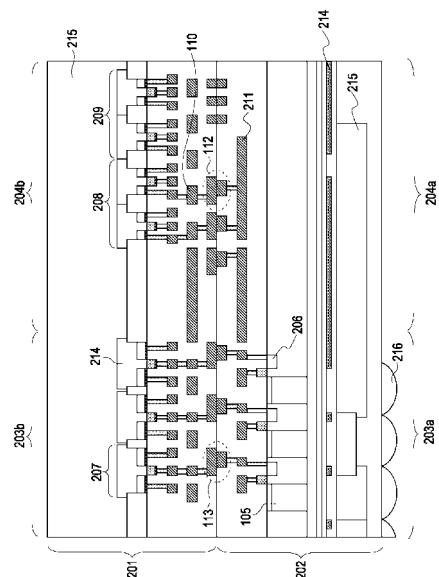

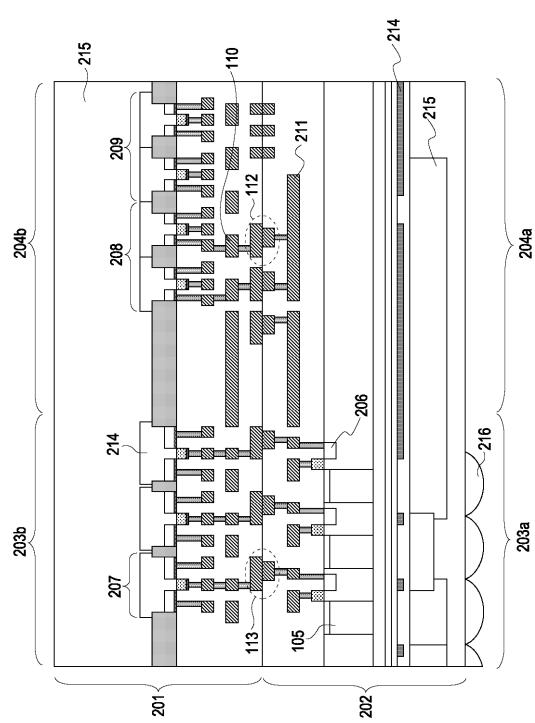

図2に、本発明の固体撮像装置に共通に適用可能な第1の基板及び第2の基板の電気的接続部を含めた断面の概念図の一例を示す。

【0033】

201は第1の基板である。202は第2の基板である。203aは第1の基板に配された画素領域である。203bは第2の基板に配された画素領域である。204aは第1の基板に配された第1の周辺領域である。第1の周辺領域204aは画素領域203a外に配される領域である。204bは第2の基板に配される第2の周辺領域である。第2の周辺領域204bは画素領域203b外に配される領域であり、画素領域から共通出力線を介して出力された信号の処理もしくは、画素領域からの信号出力を制御する回路が配される。

10

【0034】

105は光電変換部である。206はFDである。207は増幅トランジスタである。そのゲートがFDと電気的に接続されている。ここでは画素回路として増幅トランジスタのみを示しているが、他に上述したリセットトランジスタなどが設けられる。

【0035】

208は第2の周辺領域に配される読み出し回路の一部を構成するMOSトランジスタである。読み出し回路の一例として、複数の画素列ごとに読み出された信号を並列に処理する並列処理回路が挙げられる。このような並列処理回路としては列増幅器、列ADなどがある。209は第2の周辺回路に配される並列処理回路以外の回路を構成するMOSトランジスタである。

20

【0036】

110は並列処理回路を構成するMOSトランジスタ209に直流電圧を供給する直流電圧供給配線を構成する第1の導電パターンである。第1の導電パターン110は、紙面奥行き方向に延在して、各並列処理回路のMOSトランジスタに共通に直流電圧を供給する。第1の導電パターンは画素領域外に配される。

30

【0037】

211は第1の基板に配された第2の導電パターンである。第2の導電パターンは画素領域外に配される。

【0038】

112は第1の導電パターン110と第2の導電パターン211とを電気的に接続する電気的接続部である。例えば、電気的接続部112は第1の基板に配された最上配線層と第2の基板に配された最上配線層により導電パターンを形成し、これらを電気的に接続することにより構成することができる。

40

【0039】

第2の導電パターン211は第1の基板の第1の周辺領域に配される。第1の周辺領域は第2の基板に配される第2の周辺領域に比べ配置される回路素子が少ない、もしくは回路素子自体が存在しない。したがってレイアウトの自由度は比較的高いため、第2の導電パターンの面積を第1の導電パターン面積よりも大きくすることにより、第2の基板の配線レイアウトの自由度を維持しつつ、抵抗値を低下させることができると好ましい。

【0040】

113はFD206と増幅トランジスタ207のゲートとを電気的に接続する電気的接続部である。第2の電気的接続部は第1の基板の最上配線層と第2の基板の最上配線層により導電パターンを形成し、これらを電気的に接続することにより構成することができる。

【0041】

214は少なくとも1画素の増幅トランジスタ207のソース領域、ドレイン領域が配される第1導電型のウエルである。増幅トランジスタ207がNMOSトランジスタの場

50

合にはウエルの導電型はP型であり、増幅トランジスタ207がPMOSトランジスタの場合にはウエルの導電型はN型である。つまり、ウエルはソース領域、ドレイン領域と反対導電型の半導体領域で構成される。

【0042】

各ウエル114は少なくとも一方向に隣接するウエルと電気的に分離されている。つまり1つ目の実施形態としては、1つのウエルに1画素列に含まれる複数の増幅トランジスタのソース領域、ドレイン領域が配される構成である。この場合には隣接する画素列の増幅トランジスタのソース領域、ドレイン領域が配されるウエルどうしが分離されている。2つ目の実施形態としては、1つのウエルに1画素行に含まれる複数の増幅トランジスタのソース領域、ドレイン領域が配される構成である。この場合には隣接する画素行の増幅トランジスタのソース領域、ドレイン領域が配されるウエルどうしが分離されている。3つ目の実施形態としては1つのウエルに1画素の増幅トランジスタのソース領域、ドレイン領域が配される構成である。この場合には垂直方向及び水平方向に隣接する画素の増幅トランジスタのソース領域及びドレイン領域が配されるウエルと分離されている。

10

【0043】

代表的には上記3実施形態となるが、画素列ごと、画素行ごとにウエルが分離される場合には、更に、1画素行、1画素列内でウエルが分離されていてもよい。

【0044】

ここで分離されているとは、隣接するウエル214間に、該ウエルとは反対導電型の半導体領域が配されていることをいう。更に反対導電型の半導体領域に加えて絶縁体が配されていてもよい。215は第2導電型の半導体領域である。ウエル214とは反対導電型の半導体領域である。第2導電型の半導体領域215は隣接するウエル214間に配されて、各ウエルどうしを電気的に分離している。第2導電型の半導体領域215としては半導体基板そのもの、エピ層、もしくはイオン注入で形成された半導体領域を用いることができる。

20

【0045】

本発明は光電変換部が配されていない第2の基板において所定の単位で画素領域に配されるウエルを分離する。このため、従来1基板に光電変換部と画素回路とをモノリシックに配した場合に比べてウエル分離に伴なう光電変換部の受光面積低減を抑制することが可能となる。

30

【0046】

更に各実施例においては下記効果のいずれか1つを得ることが可能となる。

【0047】

第1点目は増幅トランジスタのゲインの向上である。第2点目はウエル214経由のクロストークの抑制である。第3点目はFD容量の増加の抑制である。

【0048】

以下具体的に実施例を挙げて本発明を詳細に説明する。

【0049】

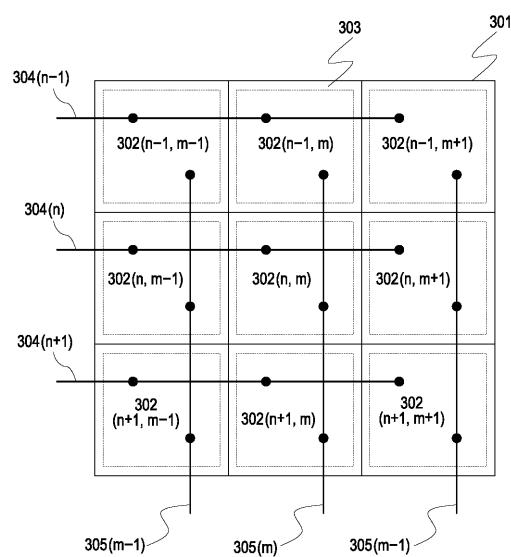

(実施例1)

本実施例はウエルを各画素毎に分離することを特徴とする。図3に第2の基板に配された画素回路部分の上面概念図を示す。本実施例においては画素回路を構成する部材のうち、第2の基板に増幅トランジスタ、リセットトランジスタ、画素を選択する選択トランジスタが配されている。

40

【0050】

301は第2の基板の画素領域を示している。画素を構成する上記部材が所定の繰り返しピッチで配されている。格子状に区画しているのは第2の基板において1画素が占有する領域を概念的に示しているものである。各画素が行列状に配されている。

【0051】

302は第1導電型のウエルである。ここではP型とする。ウエル302は画素毎に分離されている。各ウエルには1画素回路を構成する増幅トランジスタ、リセットトランジ

50

スタ、選択トランジスタのソース領域、ドレイン領域が配されている。ソース領域、ドレイン領域はウエルと反対導電型である第2導電型の半導体領域により構成される。

【0052】

303は第2導電型の半導体領域である。ここではN型とする。少なくとも各ウエル302間に配され、各ウエルを隣接するウエルと分離する。更に各ウエル302の下部に配されていてもよい。

【0053】

304は画素回路を構成するリセットトランジスタ、選択トランジスタのゲートに駆動パルスを供給する制御線である。ここでは1本で示されているが、実際には各画素行に対してリセットトランジスタ用、選択トランジスタ用の計2本が設けられている。添え字は行番号を示している。

10

【0054】

305は各画素行からの信号が並列に読み出される垂直信号線である。垂直信号線305は各画素列ごとに設けられている。添え字は列番号を示している。

【0055】

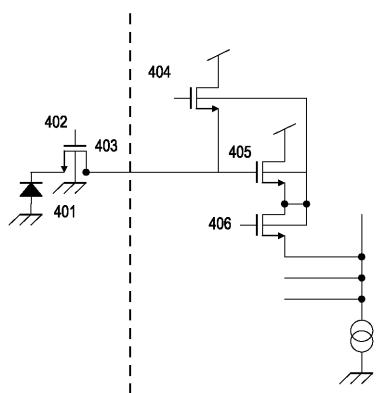

図4に本実施例の固体撮像装置の1画素の等価回路図の一例を示す。

【0056】

401は光電変換部、402は転送部を構成する転送トランジスタ、403はFD、404は画素リセット部を構成するリセットトランジスタである。405は画素増幅部を構成する増幅トランジスタである。電流源と共にソースフォロワ回路を構成する。406は画素選択部を構成する選択トランジスタである。図1の構成と比較すると選択トランジスタを有している点が異なる。

20

【0057】

光電変換部401、転送トランジスタ402、FD403が第1の基板に配され、リセットトランジスタ404、増幅トランジスタ405、選択トランジスタ406が第2の基板に配される。リセットトランジスタ404、増幅トランジスタ405、選択トランジスタ406はそれぞれN型のMOSトランジスタで構成される。

20

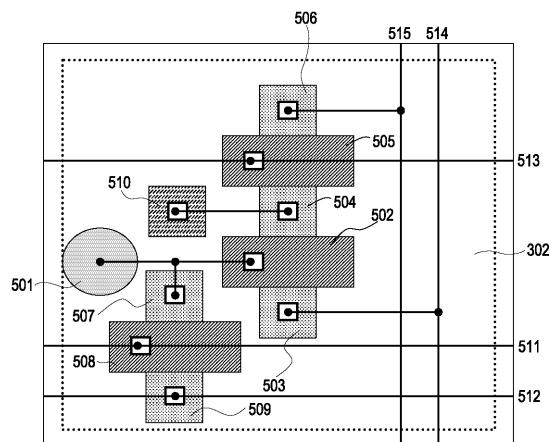

【0058】

図5に第2の基板の上面概念図を示す。図3、4と同様の機能を有する部分には同様の符号を付し詳細な説明は省略する。

30

【0059】

501は第1の基板との電気的接続部である。502は増幅トランジスタのゲート電極を構成するポリシリコンである。電気的接続部501を介して第1の基板に配されたFDと電気的に接続される。503は増幅トランジスタのソース領域である。504は増幅トランジスタのドレイン領域である。またドレイン領域504は選択トランジスタのソース領域を兼ねている。505は選択トランジスタのゲート電極を構成するポリシリコンである。506は選択トランジスタのソース領域である。507はリセットトランジスタのソース領域である。508はリセットトランジスタのゲート電極を構成するポリシリコンである。509はリセットトランジスタのドレイン領域である。

40

【0060】

510はウエル302と同導電型の半導体領域である。ウエル302よりも不純物濃度が高い。ウエルに所定の電圧を供給する機能を有するため、以下ウエルコンタクト領域と呼ぶ。

【0061】

511はリセットトランジスタに駆動パルスを供給するリセット制御線である。512はリセットトランジスタのドレインにリセット電圧を供給するリセット電源線である。513は選択トランジスタのゲートに駆動パルスを供給するための選択制御線である。514は増幅トランジスタのドレインにドレイン電圧を供給するための電源線である。515は垂直信号線である。

【0062】

50

ここで、増幅トランジスタはソースフォロワ動作をする。光電変換部 401 で発生した電荷が転送トランジスタ 402 を介して増幅トランジスタのゲートに供給される。供給された電荷量に基づいて増幅トランジスタのゲート電圧が変化する。増幅トランジスタのゲート電圧の変化に基づいて増幅トランジスタのソース電圧が変化する。本実施例においてはウエル 302 がウエルコンタクト領域 510 を介して増幅トランジスタのソース 504 と電気的に接続されている。したがってウエル 302 の電位は画素ごとに増幅トランジスタのソースの電圧変化と同様に変化する。このような構成によればソースフォロワ回路のゲインを 1 に近づけることが可能となり、ソースフォロワ回路の電圧ゲインを向上させることが可能となる。これをより詳細に説明する。

## 【0063】

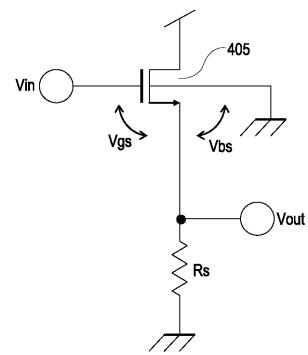

10

図 6 に比較例として増幅トランジスタのウエルが交流的に接地された場合を示す。例えば GND である。ソースフォロワ回路のゲインは、増幅トランジスタのゲート・ソース間電圧を  $V_{gs}$ 、ソースとバックゲート間の電圧を  $V_{bs}$ 、負荷抵抗の抵抗値を  $R_s$  とするとき、以下の式で表される。

$$A_v = V_{in} / V_{out}$$

$$= g_m \times R_s / (1 + (g_m + g_m b_s) \times R_s) \quad (\text{式 1})$$

ここで  $A_v$  はソースフォロワ回路の電圧ゲイン、 $g_m = I_{ds} / V_{gs}$ 、 $g_m b_s = I_{ds} / V_{bs}$  である。

## 【0064】

20

負荷抵抗の抵抗値  $R_s = \infty$  とする。そうすると式 1 は以下のように変形できる。

$$A_v = g_m / (g_m + g_m b_s) \quad (\text{式 2})$$

式 2 の値は通常 0.8 ~ 0.9 の範囲である。ここで増幅トランジスタのソースをウエルと電気的に接続する、つまり増幅トランジスタのソースをバックゲートと接続することにより  $g_m b_s = 0$  となる。このため、このときの電圧ゲインは 1.0 となる。したがって通常のようにバックゲートを交流的に接地する場合に比べて電圧ゲインを高くすることが可能となる。

## 【0065】

30

また更にリセットトランジスタを増幅トランジスタのソースと電気的に接続されたウエルに配すれば FD 容量も低減することが可能となる。これを説明するために FD に生じる寄生容量の一部を図示したものを図 7 に示す。図 7 は、図 4 のリセットトランジスタと増幅トランジスタを抜き出したものである。701 は FD とリセットトランジスタのバックゲートとの間に生じる寄生容量である。増幅トランジスタのウエルとソースとが電気的に接続された場合、増幅トランジスタのゲート・ソース間電圧が FD 電位によらずほぼ一定となる。したがって寄生容量 701 が FD 容量に寄与しない。これは増幅トランジスタのソースと同様の電圧変化をするためである。したがって、リセットトランジスタを増幅トランジスタと同じウエルに配することにより、FD 容量を低減することが可能となる。これによって感度を向上させることが可能となる。

## 【0066】

30

また本実施例においては垂直出力線と増幅トランジスタのソースとの間に選択トランジスタを配している。このような構成によれば、選択トランジスタを非導通とすることにより垂直出力線の電位変化のウエルへの影響を低減することが可能となり更に好ましい。

## 【0067】

40

以上述べたように本実施例によれば、光電変換部が配されない第 2 の基板に配された画素回路を構成するトランジスタのウエルを画素毎に分離した。このような構成によって、光電変換部の受光面積を低減させることなくウエルを分離することが可能となる。

## 【0068】

50

更に、増幅トランジスタのソースと該増幅トランジスタが配されるウエルとを電気的に接続することにより増幅トランジスタの電圧ゲインを向上させることが可能となる。また、リセットトランジスタを増幅トランジスタと同じウエルに配することにより、FD 容量を低減させることができる。更に、選択トランジスタを配して、垂直出力線と増幅ト

ランジスタのソースとを電気的に分離させることにより、垂直出力線の電位変化のウエルへの影響を低減させることが可能となる。

【0069】

(実施例2)

本実施例の実施例1との違いは画素列間でウエルが分離されている点である。第2の基板に配置されるトランジスタで言えば、増幅トランジスタの列間でウエルが分離されているとも言える。

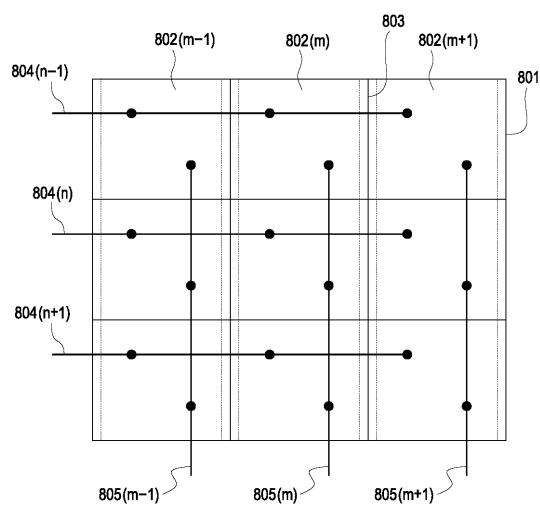

【0070】

更に実施例1と異なる点としては、選択トランジスタを設けていない点である。したがって画素等価回路としては図一の構成を適用することが可能である。図8に本実施例の固体撮像装置の上面の概念図を示す。

10

【0071】

801は第2の基板に配された画素領域を示している。等価回路図で示した画素を構成するトランジスタが所定の繰り返しピッチで配されている。格子状に区画しているのは1画素が占有する領域を概念的に示しているものである。各画素が行列状に配されている。

20

【0072】

802は第1導電型のウエルである。ここではP型である。ウエル802は画素列毎に分離されている。各ウエルには1画素列に含まれる複数の増幅トランジスタ、複数のリセットトランジスタのソース領域、ドレイン領域が配されている。ソース領域、ドレイン領域は第2導電型の半導体領域により構成される。

20

【0073】

803は第2導電型の半導体領域である。ここではN型である。少なくとも各ウエル802間にスリット状に配されて、ウエルどうしを分離する。更に第2導電型の半導体領域803は各ウエル802の下部に配されていてもよい。

30

【0074】

804は画素回路を構成するリセットトランジスタのゲートに駆動パルスを供給する制御線である。添え字は行番号を示している。

【0075】

805は各画素行からの信号を並列に読み出す垂直信号線である。各画素列ごとに設けられている。添え字は列番号を示している。

30

【0076】

本実施例によれば実施例1の効果に加えて、垂直方向に隣接する増幅トランジスタが配されるウエルどうしを電気的に分離する必要がないため、第2の基板の1画素あたりの面積を小さくすることが可能となる。更に選択トランジスタを設けていないため、この分の面積も小さくすることが可能となる。本実施例において特に選択トランジスタを設けなくてもよい構成とするためには、少なくとも同時に読み出しを行なう複数の画素間でウエルが分離されていれば良い。同一画素行に含まれる複数の画素の信号がそれぞれ対応する垂直出力線に略同時に読み出される。つまりある画素行に含まれる複数の画素信号は略同時に読み出される。したがってウエルは画素列ごとに分離されている。したがって同一画素行の隣接する画素どうしが異なるウエルに配される。

40

【0077】

(実施例3)

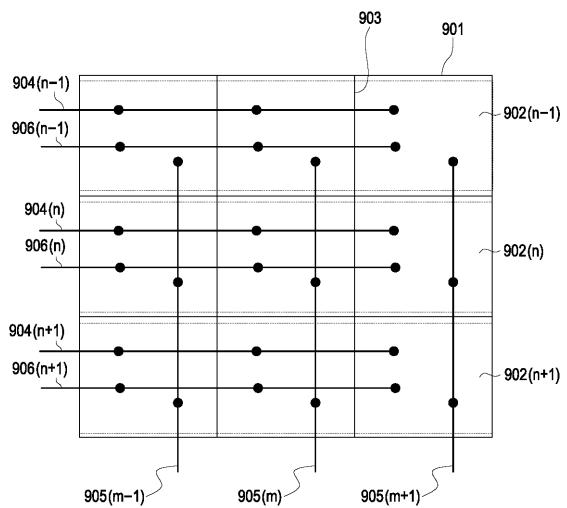

本実施例の実施例1、2との違いは、ウエルが画素行単位で分離されている点である。第2の基板に配置されるトランジスタで言えば、増幅トランジスタの行間でウエルが分離されている。図9に本実施例の固体撮像装置の第2の基板の上面の概念図を示す。

【0078】

901は第2の基板に配された画素領域を示している。等価回路図で示した画素を構成するトランジスタが所定の繰り返しピッチで配されている。格子状に区画しているのは1画素が占有する領域を概念的に示しているものである。各画素が行列状に配されている。

50

【0079】

902は第1導電型のウエルである。ここではP型である。ウエル902は画素行毎に分離されている。添え字は行番号を示している。各ウエルには1画素行に含まれる複数の増幅トランジスタ、複数のリセットトランジスタのソース領域、ドレイン領域が配されている。ソース領域、ドレイン領域は第2導電型の半導体領域により構成される。

【0080】

903は第2導電型の半導体領域である。ここではN型である。少なくとも各ウエル902間にスリット状に配されてウエルどうしを分離する。更に第2導電型の半導体領域903は各ウエル802の下部に配されていてもよい。

【0081】

904は画素回路を構成するリセットトランジスタのゲートに駆動パルスを供給する制御線である。添え字は行番号を示している。

10

【0082】

905は各画素行からの信号を並列に読み出す垂直信号線である。各画素列ごとに設けられている。添え字は列番号を示している。

【0083】

906は画素行ごとに分離されたウエルに少なくとも第1の電圧、第2の電圧を供給するための制御配線である。制御配線には不図示の電圧供給部から所定の電圧が供給される。電圧供給部は、例えば垂直走査回路、タイミングジェネレータ、電源供給部などで構成される。

20

【0084】

本実施例においては、制御配線906に読み出し画素行と非読み出し画素行とで第1の電圧、第2の電圧を選択的に供給することにより画素の選択を行なう。具体的にはウエルに供給する電圧によって増幅トランジスタの閾値を変化させて画素の選択を行なう。増幅トランジスタがN型MOSトランジスタの場合には読み出し画素行のウエルに第1の電圧を供給し、非読み出し画素行には第1の電圧よりも高い電圧である第2の電圧を供給する。これにより、垂直出力線に読み出し画素行の信号が選択に読み出される。

【0085】

以上本発明を実施例を挙げて具体的に説明したが、本発明は発明の思想を超えない範囲で適宜組み合わせ、変更が可能である。例えば、各実施例においては画素回路を構成するトランジスタの導電型をN型のトランジスタとして説明したがP型のトランジスタを用いることもできる。この場合には各半導体領域の導電型を反対導電型とすればよい。更に光電変換部で生じた電子とホールのうち信号電荷として電子を用いる場合の説明をしたが、ホールを用いることも可能である。更にウエル間を分離する半導体領域として局所的に不純物濃度の高い領域を設けてより分離特性を高めてよい。

30

【0086】

また実施例で説明した行、列は便宜上のものであり入れ替えてよい。

【符号の説明】

【0087】

101 光電変換部

40

105 増幅トランジスタ

214 第1導電型のウエル

215 第2導電型の半導体領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】