(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7128039号**

**(P7128039)**

(45)発行日 令和4年8月30日(2022.8.30)

(24)登録日 令和4年8月22日(2022.8.22)

## (51)国際特許分類

|        |                  |        |        |   |

|--------|------------------|--------|--------|---|

| H 01 L | 27/146 (2006.01) | H 01 L | 27/146 | A |

| H 01 L | 31/10 (2006.01)  | H 01 L | 31/10  | A |

| H 01 L | 29/423 (2006.01) | H 01 L | 27/146 | D |

| H 01 L | 29/49 (2006.01)  | H 01 L | 29/58  | G |

| H 01 L | 21/8234(2006.01) | H 01 L | 27/088 | E |

請求項の数 17 (全27頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2018-113807(P2018-113807) |

| (22)出願日           | 平成30年6月14日(2018.6.14)       |

| (65)公開番号          | 特開2019-4149(P2019-4149A)    |

| (43)公開日           | 平成31年1月10日(2019.1.10)       |

| 審査請求日             | 令和3年6月14日(2021.6.14)        |

| (31)優先権主張番号       | 10-2017-0075815             |

| (32)優先日           | 平成29年6月15日(2017.6.15)       |

| (33)優先権主張国・地域又は機関 | 韓国(KR)                      |

|          |                                                                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 12<br>9<br>129, Samsung-ro, Yeo<br>ngtong-gu, Suwon-si<br>, Gyeonggi-do, Repub<br>lic of Korea<br>110000051弁理士法人共生国際特許事<br>務所<br>陳 喆 究<br>大韓民国 京畿道 水原市 灵通区 東水原<br>路 316、10-1108 |

| (74)代理人  |                                                                                                                                                                                                                                                               |

| (72)発明者  |                                                                                                                                                                                                                                                               |

最終頁に続く

(54)【発明の名称】 距離測定のためのイメージセンサ

**(57)【特許請求の範囲】****【請求項1】**

互いに反対側に位置する第1面及び第2面を有し、前記第1面に隣接するウェル領域を有し、第1導電型である半導体基板と、

ここで、前記半導体基板は、前記第2面に前記第1面に陥没された複数のリセスを有し、

前記ウェル領域の少なくとも一部を貫通するように、前記第1面から前記半導体基板の厚み方向に沿って延長され、互いに離隔されている第1垂直伝達ゲート及び第2垂直伝達ゲートと、

前記ウェル領域と前記第2面との間の前記半導体基板内に配置され、前記半導体基板の厚み方向に、前記第1垂直伝達ゲート及び前記第2垂直伝達ゲートと重畠し、前記第1導電型と異なる第2導電型である光電変換領域と、

前記半導体基板の前記第1面上に配置された配線構造体と、

前記半導体基板の前記第2面上に順次に積層された、負固定電荷層、反射防止層、及びマイクロレンズと、

前記複数のリセスに配置され、絶縁物からなる複数の散乱誘導層と、を含み、

前記負固定電荷層は、前記複数の散乱誘導層と、前記半導体基板の前記第2面とが離隔されるように、前記複数の散乱誘導層を覆い包むことを特徴とするイメージセンサ。

**【請求項2】**

前記光電変換領域は、第1光電変換領域、及び前記第1光電変換領域と前記ウェル領域との間に配置され、前記第1光電変換領域より小さい値の幅を有する第2光電変換領域を

含むことを特徴とする請求項 1 に記載のイメージセンサ。

**【請求項 3】**

前記第 2 光電変換領域は、前記半導体基板の厚み方向に、前記第 1 垂直伝達ゲート及び前記第 2 垂直伝達ゲートと重畳されることを特徴とする請求項 2 に記載のイメージセンサ。

**【請求項 4】**

前記第 2 光電変換領域の不純物濃度は、前記第 1 光電変換領域の不純物濃度より濃い値を有することを特徴とする請求項 2 に記載のイメージセンサ。

**【請求項 5】**

前記第 1 光電変換領域は、前記半導体基板の厚み方向に、前記第 2 光電変換領域の全てと重畳されることを特徴とする請求項 2 に記載のイメージセンサ。

10

**【請求項 6】**

前記光電変換領域の周囲を取り囲み、前記半導体基板の前記第 2 面から前記第 1 面に向けて延長されるように配置された D T I ( d e e p t r e n c h i n s u l a t o r ) 構造物をさらに含むことを特徴とする請求項 1 に記載のイメージセンサ。

**【請求項 7】**

前記配線構造体上に配置された背面反射層をさらに含むことを特徴とする請求項 1 に記載のイメージセンサ。

**【請求項 8】**

前記第 2 導電型を有し、前記第 1 面に隣接する前記ウェル領域に互いに離隔して配置された第 1 電荷保存領域及び第 2 電荷保存領域を含むことを特徴とする請求項 1 に記載のイメージセンサ。

20

**【請求項 9】**

前記第 1 電荷保存領域は、前記第 1 垂直伝達ゲートの、前記第 2 垂直伝達ゲートに対して反対となる側に配置され、

前記第 2 電荷保存領域は、前記第 2 垂直伝達ゲートの、前記第 1 垂直伝達ゲートに対して反対となる側に配置されることを特徴とする請求項 8 に記載のイメージセンサ。

**【請求項 10】**

前記第 1 垂直伝達ゲート及び前記第 2 垂直伝達ゲートには、互いに  $180^\circ$  の位相差を有するパルス電圧が印加されることを特徴とする請求項 1 に記載のイメージセンサ。

**【請求項 11】**

30

配線構造体と、

デモデュレーション領域を有し、前記配線構造体上に前記配線構造体に接触して配置されるウェル領域と、

前記ウェル領域上に配置される光電変換領域と、

前記光電変換領域上に配置されるマイクロレンズと、

前記ウェル領域の少なくとも一部を貫通するように、前記ウェル領域の厚み方向に沿って延長される垂直伝達ゲート、及び前記垂直伝達ゲートを各々取り囲む伝達ゲート絶縁膜を各々含み、前記デモデュレーション領域を挟んで互いに離隔されるように配置された少なくとも 2 個の伝達ゲート構造体と、

前記光電変換領域に隣接する前記ウェル領域の前記デモデュレーション領域以外の一部分に、前記少なくとも 2 個の伝達ゲート構造体と離隔されて配置され、前記ウェル領域の不純物濃度より濃い値の不純物濃度を有する複数の第 1 バリア不純物領域と、を含むことを特徴とするイメージセンサ。

40

**【請求項 12】**

前記配線構造体に隣接する前記デモデュレーション領域の一部分に配置され、前記ウェル領域の不純物濃度より濃い値の不純物濃度を有する第 2 バリア不純物領域をさらに含むことを特徴とする請求項 11 に記載のイメージセンサ。

**【請求項 13】**

前記第 2 バリア不純物領域に接する、前記デモデュレーション領域の一部分は、前記ウェル領域及び前記第 2 バリア不純物領域と異なる導電型を有することを特徴とする請求項

50

1\_2に記載のイメージセンサ。

【請求項 14】

前記光電変換領域は、

前記マイクロレンズに隣接して配置される第1光電変換領域、及び前記ウェル領域に隣接して配置される第2光電変換領域からなり、

前記第1光電変換領域の不純物濃度は、前記第2光電変換領域の不純物濃度より薄い値を有し、前記第1光電変換領域の幅は、前記第2光電変換領域の幅より広い値を有することを特徴とする請求項1\_1に記載のイメージセンサ。

【請求項 15】

B S I ( b a c k s i d e i l l u m i n a t i o n 、 背面照明 ) 構造を有するイメージセンサであって、

10

第1面及び前記第1面の反対側に位置する第2面を有し、

前記第1面に隣接するウェル領域を有する第1導電型である半導体基板と、

ここで、前記半導体基板は前記第2面に前記第1面に陥没された複数のリセスを有し、

前記ウェル領域の少なくとも一部を貫通するように、前記第1面から前記第2面に向けて延長され、互いに離隔されている複数の垂直伝達ゲートと、

前記第2面に隣接する半導体基板内に配置される第1光電変換領域と、

前記第1光電変換領域と前記ウェル領域との間に配置され、前記第1光電変換領域より小さい値の幅、及び大きい値の不純物濃度を有し、前記第1導電型と異なる第2導電型である第2光電変換領域と、

20

前記半導体基板の前記第2面上に順次に積層された、負固定電荷層、反射防止層、及びマイクロレンズと、

前記複数のリセスに配置され、絶縁物からなる複数の散乱誘導層と、を含み、

前記負固定電荷層は、前記複数の散乱誘導層と、前記半導体基板の前記第2面とが離隔されるように、前記複数の散乱誘導層を覆い包むことを特徴とするイメージセンサ。

【請求項 16】

前記半導体基板の前記第2面は、光の入射面であることを特徴とする請求項1\_5に記載のイメージセンサ。

【請求項 17】

前記第2光電変換領域は、前記複数の垂直伝達ゲートの各々の全体と前記半導体基板の厚み方向に重畳され、前記第1光電変換領域は、前記第2光電変換領域の全てと重畳されることを特徴とする請求項1\_5に記載のイメージセンサ。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、イメージセンサに係り、さらに詳細には、距離測定のためのイメージセンサに関する。

【背景技術】

【0002】

一般的なイメージセンサは、被写体までの距離に係わる情報を有しない。被写体までの正確な距離情報を得るために、光飛行時間法 (T o F : time - of - flight) イメージセンサが開発された。該 T o F イメージセンサは、光を被写体に照射した後、被写体から反射される光が受光されるまでの光飛行時間を測定して被写体までの距離に係わる情報を得る。

40

【発明の概要】

【発明が解決しようとする課題】

【0003】

本発明の技術的課題は、ピクセルを小型化し、且つ、感度を改善できる距離測定のためのイメージセンサを提供することである。

【課題を解決するための手段】

50

**【 0 0 0 4 】**

前記技術的課題を解決するために、本発明は、次のような距離測定のためのイメージセンサを提供する。

本発明によるイメージセンサは、互いに反対側に位置する第1面及び第2面を有し、前記第1面に隣接するウェル領域を有し、第1導電型である半導体基板、前記ウェル領域の少なくとも一部を貫通するように、前記第1面から前記半導体基板の厚み方向に沿って延長され、互いに離隔されている第1垂直伝達(トランスファー)ゲート及び第2垂直伝達ゲート、前記ウェル領域と前記第2面との間の前記半導体基板内に配置され、前記半導体基板の厚み方向に、前記第1垂直伝達ゲート及び前記第2垂直伝達ゲートと重畠し、前記第1導電型と異なる第2導電型である光電変換領域、及び前記半導体基板の前記第1面上に配置された配線構造体を含む。

**【 0 0 0 5 】**

本発明によるイメージセンサは、配線構造体、デモデュレーション領域を有し、前記配線構造体上に配置されるウェル領域、前記ウェル領域上に配置される光電変換領域、前記光電変換領域上に配置されるマイクロレンズ、前記ウェル領域の少なくとも一部を貫通するように、前記ウェル領域の厚み方向に沿って延長される垂直伝達ゲート、及び前記垂直伝達ゲートを各々取り囲む伝達ゲート絶縁膜を各々含み、前記デモデュレーション領域を挟んで互いに離隔されるように配置された少なくとも2個の伝達ゲート構造体を含む。

**【 0 0 0 6 】**

本発明によるイメージセンサは、互いに反対側に位置する第1面及び第2面を有し、前記第1面に隣接するウェル領域を有し、第1導電型である半導体基板、前記ウェル領域の少なくとも一部を貫通するように、前記第1面から前記第2面に向けて延長され、互いに離隔されている複数の垂直伝達ゲート、前記第2面に隣接する半導体基板内に配置される第1光電変換領域、前記第1光電変換領域と前記ウェル領域との間に配置され、前記第1光電変換領域より小さい値の幅、及び大きい値の不純物濃度を有し、前記第1導電型と異なる第2導電型である第2光電変換領域を有し、B S I ( b a c k s i d e i l l u m i n a t i o n ) 構造によってなる。

**【 発明の効果 】****【 0 0 0 7 】**

本発明によるイメージセンサは、少なくとも2個の垂直伝達ゲートを含み、更に好ましくはB S I構造を有する。従って、該イメージセンサを構成するピクセルを小型化し、且つ、伝達トランジスタのゲートを相対的に長く形成できるので、イメージセンサの感度が向上する。

**【 図面の簡単な説明 】****【 0 0 0 8 】**

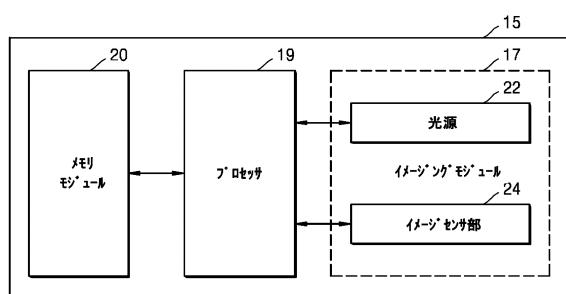

**【図1】**本発明の一実施形態によるシステムに係わる概略的な構成図である。

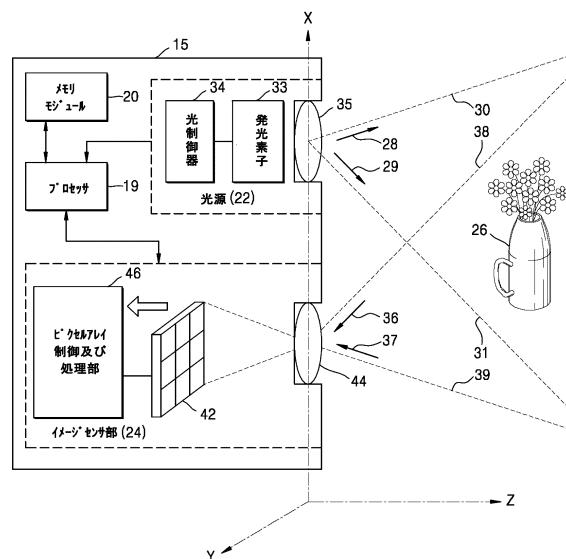

**【図2】**本発明の一実施形態によるシステムの例示的な動作について説明するための構成図である。

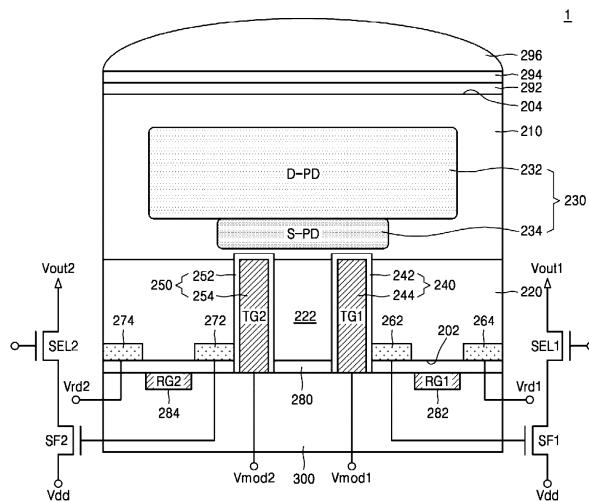

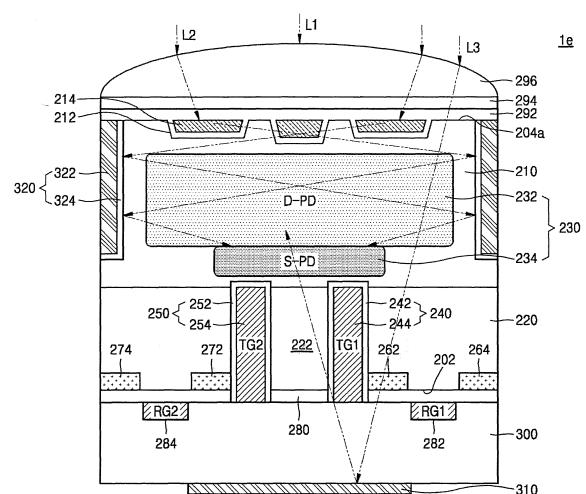

**【図3】**本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

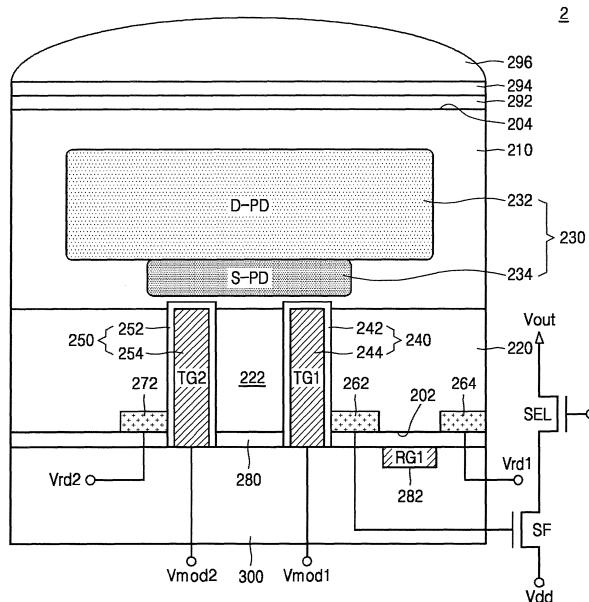

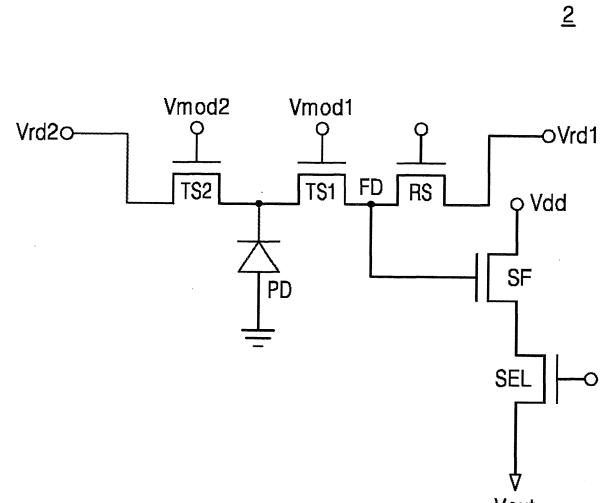

**【図4】**本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図である。

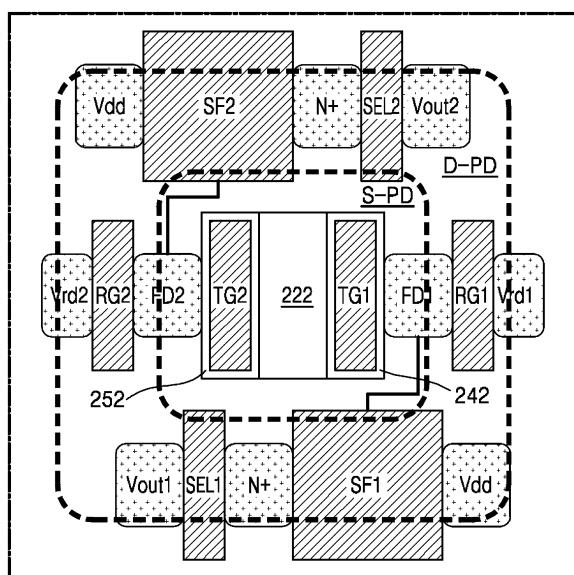

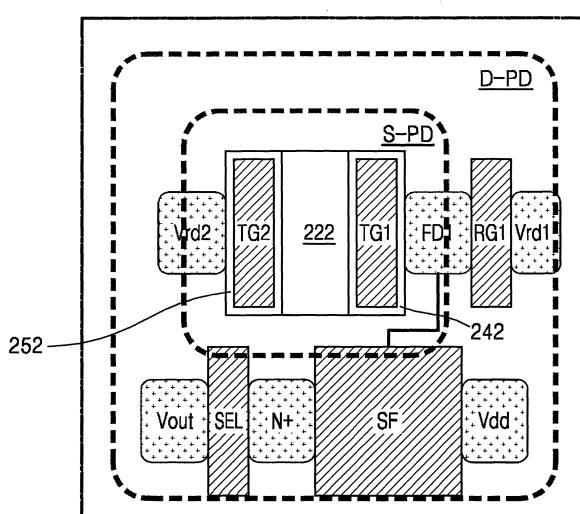

**【図5】**本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な平面図である。

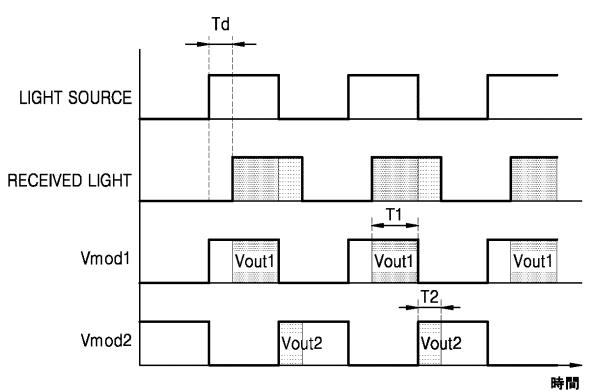

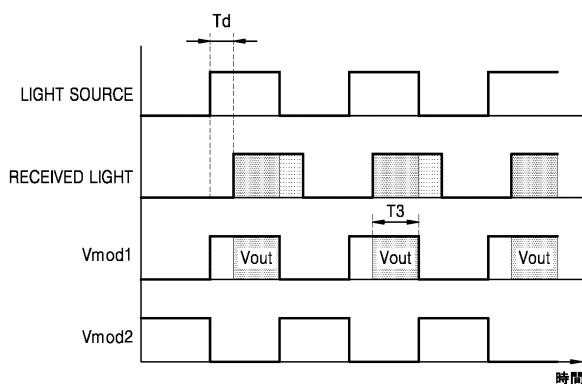

**【図6】**本発明の一実施形態による、距離測定のためのイメージセンサの作用について説明するタイミング図である。

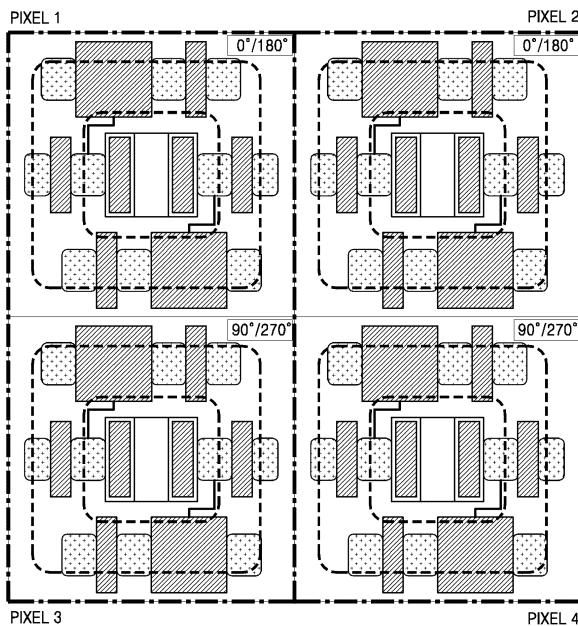

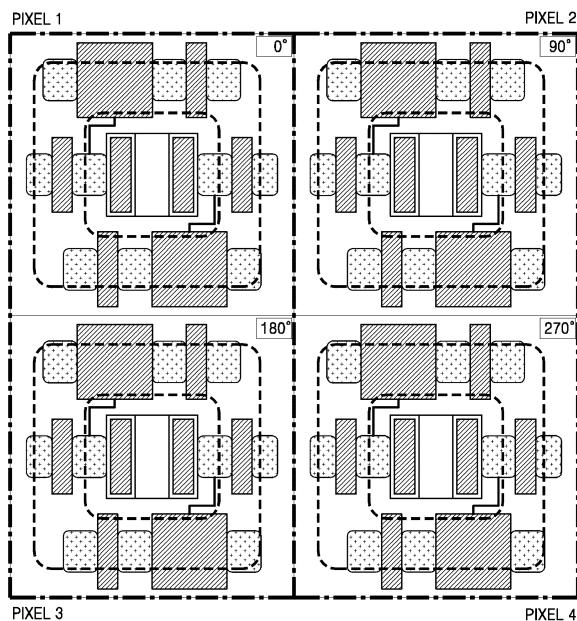

**【図7】**本発明の一実施形態によるイメージセンサのピクセルアレイの概略的な平面図である。

**【図8】**本発明の一実施形態による、距離測定のためのイメージセンサの作用について説明するためのピクセルアレイの平面図である。

10

20

30

40

50

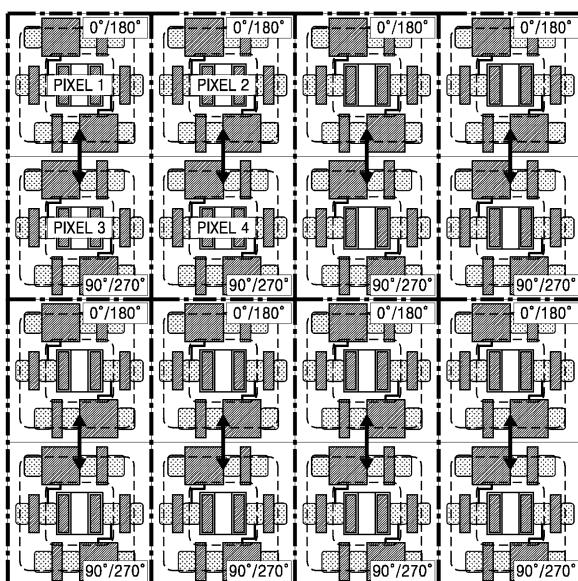

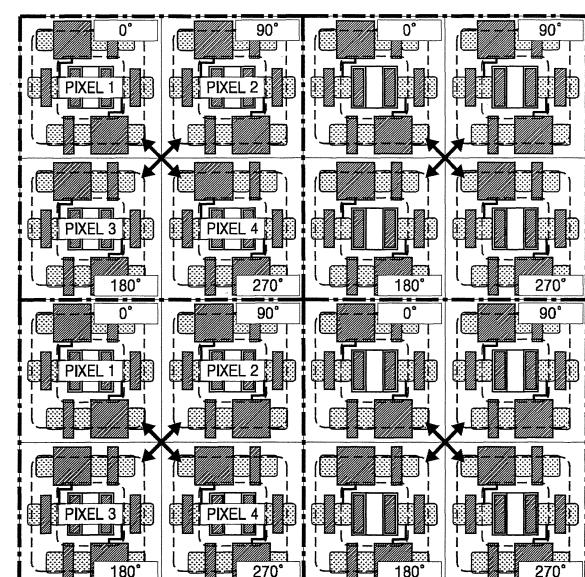

【図 9】本発明の一実施形態による、距離測定のためのイメージセンサの作用について説明するためのピクセルアレイの平面図である。

【図 10】本発明の一実施形態による、距離測定のためのイメージセンサの作用について説明するタイミング図である。

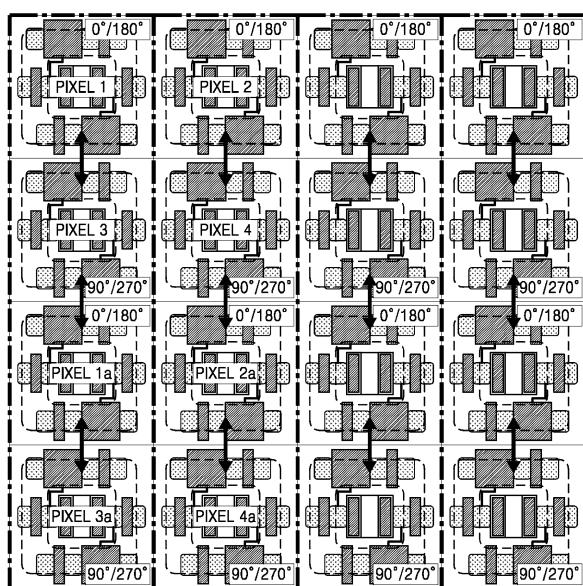

【図 11】本発明の一実施形態によるイメージセンサのピクセルアレイの概略的な平面図である。

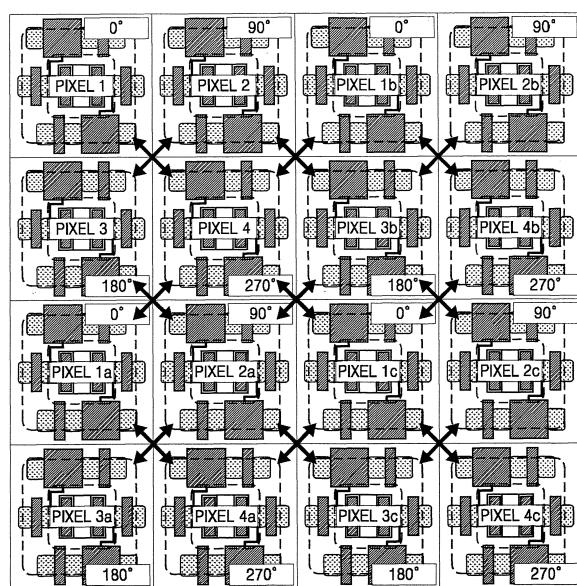

【図 12】本発明の一実施形態による、離測定のためのイメージセンサの作用について説明するピクセルアレイの平面図である。

【図 13】本発明の一実施形態による、離測定のためのイメージセンサの作用について説明するピクセルアレイの平面図である。

【図 14】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 15】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 16】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 17】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 18】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 19】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 20】本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図である。

【図 21】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な平面図である。

【図 22】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な平面図である。

【図 23】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 24】本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図である。

【図 25】本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。

【図 26】本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図である。

#### 【発明を実施するための形態】

##### 【0009】

本発明の構成要素及び効果を十分に理解するために、添付図面を参照し、本発明の実施形態について詳細に説明する。

##### 【0010】

図1は、本発明の一実施形態によるシステムに係わる概略的な構成図である。

図1を参照すれば、システム15は、プロセッサ19又はホストと通信して結合されるイメージングモジュール17を含む。一実施形態において、システム15は、プロセッサ19に連結され、イメージングモジュール17から受信されるイメージデータのような情報を保存するメモリモジュール20をさらに含む。一実施形態において、システム15は、1つの半導体チップとして集積される。他の一実施形態において、イメージングモジュール17、プロセッサ19及びメモリモジュール20の各々は、分離された別途の半導体チップとして具現される。一実施形態において、メモリモジュール20は、1又はそれより多くのメモリチップを含む。一実施形態において、プロセッサ19は、多重プロセッシ

10

20

30

40

50

ングチップを含む。

【0011】

システム15は、本発明の実施形態による距離測定向けのイメージセンサ応用のための低電力電子装置である。システム15は、ポータブル又は固定式である。システム15のポータブル形態の例としては、モバイル装置、携帯電話、スマートフォン、ユーザ装置(UE)、タブレット、デジタルカメラ、ラップトップコンピュータ又はデスクトップコンピュータ、電子スマート時計、M2M(machine-to-machine)通信装置、仮想現実(VR、virtual reality)装置又は仮想現実(VR)モジュール、ロボットなどを含む。システム15の固定式形態の例としては、ビデオゲームセンターのゲームコンソール、相互的ビデオターミナル、自動車、機械視野システム、産業用ロボット、仮想現実(VR)装置、自動車の運転手側実装カメラ(例えば、運転手が眠っているか否かということをモニタリングする)などを含む。

10

【0012】

一実施形態において、イメージングモジュール17は、光源22及びイメージセンサ部24を含む。光源22は、例えば、赤外線又は可視光を発光するレーザダイオード(LD:laser diode)又は発光ダイオード(LED:light emitting diode)、近赤外線レーザ(NIR)、ポイント光源、白色ランプ及びモノクロメータ(monochromator)が組み合わされた単色(monochromatic)照明源、又は他のレーザ光源の組み合わせからなる。一実施形態において、光源22は、800nm乃至1,000nmの波長を有する赤外線を発光する。イメージセンサ部24は、図2以下に図示されて説明されるピクセルアレイ及び補助処理回路を含んでもよい。

20

【0013】

例示的には、プロセッサ19は、汎用プロセッサである中央処理装置(CPU)である。ここで、「プロセッサ」及び「中央処理装置(CPU)」は、説明の便宜のために互換的に使用される。一実施形態において、プロセッサ19は、中央処理装置に加え、マイクロコントローラ、デジタル信号処理器(DSP:digital signal processor)、グラフィック処理部(GPU:graphic processing unit)、専用集積回路(特定用途専用集積回路、ASIC:application specific integrated circuit)プロセッサなどをさらに含む。また、プロセッサ19は、分散処理環境で動作する1より多い中央処理装置を含み得る。プロセッサ19は、x86\_ISA(32ビットバージョン又は64ビットバージョン)、PowerPC(登録商標)\_ISA、RISC(reduced instruction set computer)\_ISAに依存するMIPS(microprocessor without interlocked pipeline stages)\_ISAなどの命令集合構造(ISA、instruction set architecture)の何れかによって命令を実行し、データを処理するように構成される。例示的には、プロセッサ19は、中央処理装置の機能に追加的な機能を有するシステムオンチップ(SoC、system on chip)である。

30

【0014】

メモリモジュール20は、例えば、SDRAM(synchronous dynamic random access memory)などのDRAM(dynamic random access memory)、HBM(high bandwidth memory)モジュール、又はHMC(hybrid memory cube)メモリモジュールのようなDRAM基盤3DS(3次元スタック、3-dimensional stack)メモリモジュールである。メモリモジュール20は、例えば、SSD(solid-state drive)、DRAMモジュール、SRAM(static random access memory)、PRAM(phase-change random access memory)、RRAM(登録商標)(resistive random access memory)、CBRAM(conductive-bridging random access memory)、MRAM(magneti

40

50

c r a n d o m a c c e s s m e m o r y ) 、 S T T - M R A M ( s p i n - t r a n s f e r t o r q u e M R A M ) などの何れかの半導体基盤格納装置である。

#### 【 0 0 1 5 】

図 2 は、本発明の一実施形態によるシステムの例示的な動作について説明するための構成図である。

#### 【 0 0 1 6 】

図 2 を参照すれば、システム 15 は、個別物体、又は場面（図示せず）内の物体である 3 次元物体 26 に対する Z 軸に沿ったデプス（奥行き）情報の獲得に使用される。一実施形態において、該デプス情報は、イメージセンサ部 24 から受信されるスキャンデータに基づいて、プロセッサ 19 によって計算される。一実施形態において、該デプス情報は、イメージセンサ部 24 で自主的にも計算される。一実施形態において、該デプス情報は、プロセッサ 19 によって、3 次元ユーザインターフェースの一部として使用され、システム 15 のユーザが、ゲーム、又はシステム 15 で実行される他のアプリケーションの一部として、3 次元物体 26 の 3 次元イメージと相互動作、及び／又は、3 次元物体 26 の 3 次元イメージ使用を可能にする。

10

#### 【 0 0 1 7 】

X 軸は、システム 15 の前面に沿った水平方向であり、Y 軸は、ページを外れる垂直方向であり、Z 軸は、システム 15 からイメージされる物体 26 の方向に延伸される。一実施形態において、光源 22 及びイメージセンサ部 24 の光軸は、深さ測定のために、Z 軸に平行である。

20

#### 【 0 0 1 8 】

光源 22 は、矢印 ( 28 , 29 ) で図示されているように、3 次元物体 26 を照明する。矢印 ( 28 , 29 ) は、光ビーム又は光放射の経路を示す破線 ( 30 , 31 ) に各々対応する。光ビーム又は光放射は、光視野角内の 3 次元物体 26 をポイントスキャンする際に使用される。物体表面のライン単位スキャンは、光制御器 34 によって動作及び制御される発光素子 33 である光学放射源を利用して行われる。発光素子 33 からの光ビームは、光制御器 34 の制御によって、投射レンズ 35 を介して、3 次元物体 26 の表面にわたって、X Y 方向にポイントスキャンされる。一実施形態において、該ポイントスキャンは、スキャンラインに沿って、3 次元物体の表面に光点 ( light spots ) を投写することができる。投射レンズ 35 は、ガラス又はプラスチックの表面を有する集中レンズ、又は発光素子 33 からのレーザビームを物体 26 表面上の一点に集中させる円筒状光学元素である。例えば、投射レンズ 35 は、凸状構造を有する集中レンズであるが、それに限定されず、投射レンズ 35 として、他の形態の適切なレンズデザインが選択され得る。3 次元物体 26 は、発光素子 33 からの照明光が、投射レンズ 35 によって、光点に集中する焦点位置に位置する。従って、該ポイントスキャンにより、3 次元物体 26 表面上の狭い領域又は点が投射レンズ 35 からの集中された光ビームによって順次に照明される。

30

#### 【 0 0 1 9 】

一実施形態において、発光素子 33 は、赤外線又は可視光を発光するレーザダイオード又は発光ダイオード、近赤外線レーザ、ポイント光源、白色ランプ及びモノクロメータが組み合わされた単色照明源、或いは他のレーザ光源の組み合わせの何れかである。発光素子 33 は、システム 15 のハウジング内の一位置に固定され、X Y 方向に回転可能である。

40

発光素子 33 は、光制御器 34 によって、X Y 方向に制御可能であり、3 次元物体 26 のポイントスキャンを遂行できる。一実施形態において、該可視光は、緑色光である。発光素子 33 からの放出された光は、鏡（図示せず）を利用して、3 次元物体 26 の表面に照射される。又は、該ポイントスキャンは、鏡を使わず遂行される。例示的には、光源 22 は、図 2 に図示されたよりも少ないか、又は多い、構成要素を含む。

#### 【 0 0 2 0 】

3 次元物体 26 のポイントスキャンから反射された光は、矢印 ( 36 , 37 ) 及び破線 ( 38 , 39 ) によって表示された集光経路に沿って進む。該集光経路を介して発光素子 33 からの照明が受信され、3 次元物体 26 の表面によって散乱、又は表面から反射され

50

る光子が該集光経路に沿って移動する。図2において、矢印及び破線によって表示された多様な経路は、例示的なものである。実際の光信号が進む具体的な経路は図示された経路に限定されない。

#### 【0021】

照明された3次元物体26から受信される光は、イメージセンサ部24の収集レンズ44を介して、2次元ピクセルアレイ42の、1又はそれより多くのピクセルに集中される。投射レンズ35と類似して、収集レンズ44は、3次元物体26から受信される反射光を、2次元ピクセルアレイ42の、1又はそれより多くのピクセルに集中するガラス表面又はプラスチック表面の集中レンズ、又は他の円筒状光学素子である。一実施形態において、収集レンズ44は、凸状構造を有する集中レンズであるが、それに限定されない。また、説明の便宜のために、 $3 \times 3$ ピクセルアレイが図2に図示されている。しかし、実際のピクセルアレイは、数千又は数百万のピクセルを含むことが理解されるであろう。

ピクセルアレイ42は、異なるピクセルが異なる色の光信号を収集するRGBピクセルアレイである。ピクセルアレイ42は、例えば、赤外線(IR)遮断フィルタを有する2次元RGBセンサ、2次元赤外線(IR)センサ、2次元近赤外線(NIR)センサ、2次元RGBWセンサ、2次元RGB-IRセンサなどの2次元センサである。システム15は、3次元物体26の3次元イメージング(深さ測定を含む)のためだけではなく、物体26の2次元RGBカラー(又は、物体を含む場面)のイメージングのために、同一ピクセルアレイ42を使用できる。

#### 【0022】

2次元ピクセルアレイ42は、受信された光子を、対応する電気信号に変換し、それらは、ピクセルアレイ制御/処理部46によって処理され、物体26の3次元深さイメージが判別される。例示的には、ピクセルアレイ制御/処理部46は、深さ測定のために、位相情報を組み合わせて計算する。ピクセルアレイ制御/処理部46は、ピクセルアレイ42の動作を制御するための関連回路を含む。

#### 【0023】

プロセッサ19は、光源22及びイメージセンサ部24の動作を制御する。例えば、システム15は、ユーザによって制御され、2次元イメージングモード及び3次元イメージングモードを転換するモードスイッチ(図示せず)を具備する。ユーザが、モードスイッチを利用して、2次元イメージングモードを選択するとき、プロセッサ19は、イメージセンサ部24を活性化するが、2次元イメージングモードの場合は、周辺光を利用するので光源22を活性化しない。一方、ユーザが、モードスイッチを利用して、3次元イメージングモードを選択するとき、プロセッサ19は、光源22及びイメージセンサ部24を何れも活性化し、ピクセルアレイ制御/処理部46内のリセット信号(RST)のレベル変化をトリガし、周辺光が過度に強く、線形モードで反射しないとき、線形モードから対数モードに転換する。

ピクセルアレイ制御/処理部46から受信され、処理されたイメージデータは、プロセッサ19によって、メモリモジュール20に保存される。プロセッサ19は、ユーザによって選択された2次元イメージ又は3次元イメージを、システム15の表示スクリーン(図示せず)に表示する。プロセッサ19は、上述の多様な処理作業を行うソフトウェア又はファームウェアによってプログラムされる。一実施形態において、プロセッサ19は、上述の機能の一部又は全部を遂行するためのプログラム可能なハードウェア論理回路を含む。例えば、メモリモジュール20は、プログラムコード、ルックアップテーブル、又は中間演算結果を保存し、プロセッサ19に当該機能を遂行させる。

#### 【0024】

システム15のプロセッサ19は光源22を利用して、3次元物体26に対する1次元ポイントスキャンをスキャンラインに沿って行う。該ポイントスキャンの最中に、光源22は、ライン単位で3次元物体26の表面に順次的な光点(又は、一連の光点)を投写するように、プロセッサ19によって制御される。システム15のピクセルアレイ制御/処理部46は、2次元ピクセルアレイ42のようなイメージセンサにおいて、1行のピクセ

10

20

30

40

50

ルを選択する。2次元ピクセルアレイ42のようなイメージセンサは、イメージプレーンを形成する2次元アレイに配列された複数のピクセルを有する。ピクセルの選択された行は、イメージプレーンにおいて、スキャンラインのエピポーラ（登極）線（`e p i p o l a r_l i n e`）を形成する。

ピクセルアレイ制御／処理部46は、1行のピクセル中の対応するピクセルを利用して、各光点を検出するように、プロセッサ19によって制御される。照明光点から反射された光が、収集レンズ44によって、2又はそれより多くの隣接ピクセルに集中されるとき、照明光点から反射された光は、単一ピクセル、又は1より多くのピクセルによって検出される。言い換れば、2又はそれより多くの光点から反射された光が2次元アレイ42の単一ピクセルに収集される。ピクセルアレイ制御／処理部46は、順次的な光点で対応する光点のピクセル特定検出に応答し、ピクセル特定出力を生成するように、プロセッサ19によって制御される。従って、ピクセルアレイ制御／処理部46は、少なくとも、ピクセル特定出力、及び対応する光点を投写する光源22によって使用されたスキャン角に基づいて、3次元物体表面上の対応する光点までの3次元距離（又は、深み）を決定できる。

#### 【0025】

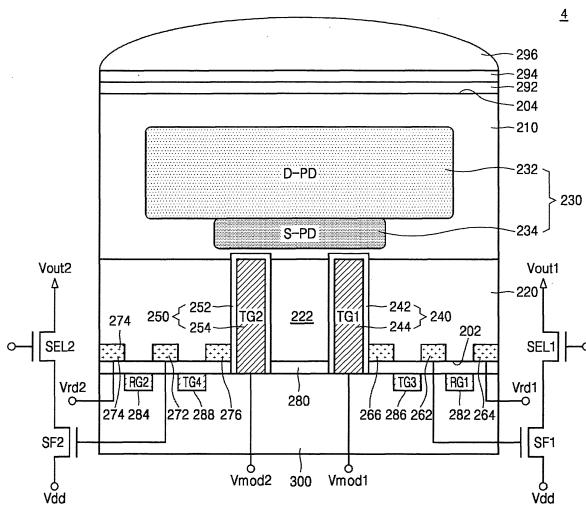

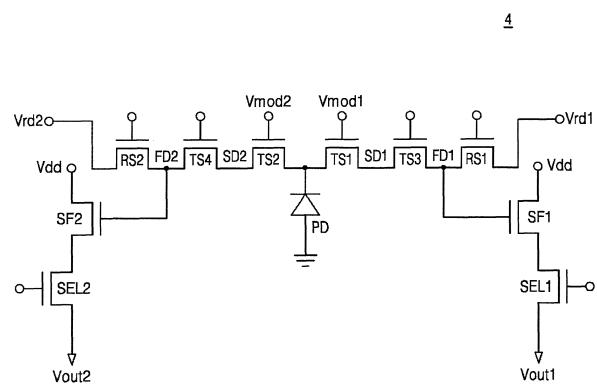

図3は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図であり、図4は、本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図であり、図5は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な平面図である。

#### 【0026】

本明細書としては、説明の便宜のために、断面図及び／又は平面図と等価回路図とを混用して図示して説明し、部材番号も、断面図及び／又は平面図と等価回路図とのための部材番号を混用して表記する。

#### 【0027】

図3乃至図5を共に参照すれば、イメージセンサ1は、互いに反対となる第1面202及び第2面204を有し、第1面202に隣接するウェル領域220を有する半導体基板210、ウェル領域220と第2面204との間の半導体基板210内に配置される光電変換領域230、ウェル領域220の少なくとも一部を貫通するように、第1面202及び第2面204の各々に垂直な方向である半導体基板210の厚み方向に沿って延長され、互いに離隔されている少なくとも2個の垂直伝達ゲート244, 254、並びに半導体基板210の第1面202上に配置される配線構造体300を含む。配線構造体300は、後述する第1リセットゲート（RG1）282、第2リセットゲート（RG2）284、並びに関連回路を構成するための配線、コンタクトプラグ、及び層間絶縁膜を含む。

#### 【0028】

半導体基板210は、例えば、Si、Ge、SiGe、SiC、GaAs、InAs及びInPのうちから選択された少なくとも一つを含む。一実施形態において、半導体基板210は、第1導電型を有する。例えば、前記第1導電型は、p型である。

#### 【0029】

ウェル領域220は、例えば、第1導電型を有する。ウェル領域220は、半導体基板210に、第1導電型を有する不純物をドーピングして形成される。ウェル領域220の不純物濃度は、ウェル領域220以外の半導体基板210の部分の不純物濃度より濃い値を有する。

#### 【0030】

光電変換領域230は、第2導電型を有する。例えば、前記第2導電型は、n型である。光電変換領域230は、フォトダイオード（PD）を構成する。光電変換領域230は、第1光電変換領域232及び第2光電領域234からなる。第2光電変換領域234の不純物濃度は、第1光電変換領域232の不純物濃度より濃い値を有する。第1光電変換領域232は、半導体基板210の第1面202から相対的に深いところに形成され、第2光電変換領域234は、相対的に浅いところに形成されるので、第1光電変換領域23

2 及び第 2 光電変換領域 234 を各々 D-PD (deep-photo diode) 及び S-PD (shallow-photo diode) と称する。

#### 【0031】

半導体基板 210 の第 1 面 202 又は第 2 面 204 と平行な方向に沿って、第 1 光電変換領域 232 の幅は、第 2 光電変換領域 234 の幅より広い。第 1 光電変換領域 232 は、例えば、半導体基板 210 の厚み方向に、第 2 光電変換領域 234 の全体と重畠する。従って、光電変換領域 230 で発生した光電荷は、広い第 1 光電変換領域 232 から狭い第 2 光電変換領域 234 に移動しながら集中される。

#### 【0032】

少なくとも 2 個の垂直伝達ゲート 244, 254 は、各々半導体基板 210 の厚み方向に沿って、50 nm 乃至 500 nm の長さを有して延長される。一実施形態において、ウェル領域 220 の厚みは、少なくとも 2 個の垂直伝達ゲート 244, 254 の延長長と類似している。一実施形態において、少なくとも 2 個の垂直伝達ゲート 244, 254 は、ウェル領域 220 を完全に貫通するように、半導体基板 210 の厚み方向に沿って延長される。

10

#### 【0033】

ウェル領域 220 は、デモデュレーション領域 (demodulation regi on) 222 を有する。ウェル領域 220 内のデモデュレーション領域 222 は、光電変換領域 230 で発生した光電荷が、少なくとも 2 個の垂直伝達ゲート 244, 254 によって移動する領域である。従って、デモデュレーション領域 222 は、少なくとも 2 個の垂直伝達ゲート 244, 254 の周囲を取り囲みながら隣接するウェル領域 220 の部分、例えば、少なくとも 2 個の垂直伝達ゲート 244, 254 の互いに対向する側面の反対側側面に隣接するウェル領域 220 の部分を含むけれども、本明細書としては、説明の便宜のために、ウェル領域 220 において、互いに離隔されている少なくとも 2 個の垂直伝達ゲート 244, 254 間の部分をデモデュレーション領域 222 と称する。

20

従って、少なくとも 2 個の垂直伝達ゲート 244, 254 は、デモデュレーション領域 222 を挟んで互いに離隔される。一実施形態において、デモデュレーション領域 222 は、第 1 導電型を有する。一実施形態において、デモデュレーション領域 222 は、第 1 導電型を有し、ウェル領域 220 の他の部分と同一不純物濃度を有することができる。他の一実施形態において、デモデュレーション領域 222 は、ウェル領域 220 の他の部分と不純物濃度が異なる。さらに他の一実施形態において、デモデュレーション領域 222 は、第 2 導電型を有する。

30

#### 【0034】

少なくとも 2 個の垂直伝達ゲート 244, 254 の周囲には、少なくとも 2 個の垂直伝達ゲート 244, 254 と、ウェル領域 220 とを絶縁させる伝達ゲート絶縁膜 242, 252 が配置される。イメージセンサ 1 が、2 個の垂直伝達ゲート 244, 254、即ち、第 1 垂直伝達ゲート (TG1) 244 及び第 2 垂直伝達ゲート (TG2) 254 を有する場合、第 1 垂直伝達ゲート 244、及びそれを取り囲む第 1 伝達ゲート絶縁膜 242 を、共に第 1 伝達ゲート構造体 240 と称し、第 2 垂直伝達ゲート 254、及びそれを取り囲む第 2 伝達ゲート絶縁膜 252 を、共に第 2 伝達ゲート構造体 250 と称する。第 1 垂直伝達ゲート 244 及び第 2 垂直伝達ゲート 254 には各々、第 1 モジュレーション電圧 Vmod1 及び第 2 モジュレーション電圧 Vmod2 が印加される。第 1 垂直伝達ゲート 244 及び第 2 垂直伝達ゲート 254 は、各々第 1 伝達トランジスタ TS1 及び第 2 伝達トランジスタ TS2 を構成する。

40

#### 【0035】

光電変換領域 230 は、半導体基板 210 の厚み方向に、デモデュレーション領域 222 と重畠される。また、光電変換領域 230 は、半導体基板 210 の厚み方向に、第 1 垂直伝達ゲート 244 を含む第 1 伝達ゲート構造体 240、及び第 2 垂直伝達ゲート 254 を含む第 2 伝達ゲート構造体 250 と各々重畠される。光電変換領域 230 は即ち、半導体基板 210 の厚み方向に、デモデュレーション領域 222、第 1 垂直伝達ゲート 244

50

を含む第1伝達ゲート構造体240、及び第2垂直伝達ゲート254を含む第2伝達ゲート構造体250の各々の全体と重畠される。

#### 【0036】

一実施形態において、第2光電変換領域(S-PD)234は、半導体基板210の厚み方向に、デモデュレーション領域222と重畠される。また、第2光電変換領域(S-PD)234は、半導体基板210の厚み方向に、第1垂直伝達ゲート244を含む第1伝達ゲート構造体240、及び第2垂直伝達ゲート254を含む第2伝達ゲート構造体250の各々と重畠される。第1光電変換領域(D-PD)232は、例えば、半導体基板210の厚み方向に、デモデュレーション領域222、第1垂直伝達ゲート244を含む第1伝達ゲート構造体240、及び第2垂直伝達ゲート254を含む第2伝達ゲート構造体250の各々の全体と重畠される。10

#### 【0037】

従って、光電変換領域230で発生した光電荷は、第1光電変換領域232から第2光電変換領域234に移動しながら集中された後、デモデュレーション領域222に伝達される。

#### 【0038】

ウェル領域220には、第1面202に隣接し、第1垂直伝達ゲート244及び第2垂直伝達ゲート254に各々隣接した位置に配置される第1電荷保存領域262及び第2電荷保存領域272が配置される。第1電荷保存領域(FD1)262及び第2電荷保存領域(FD2)272は、各々第1垂直伝達ゲート244及び第2垂直伝達ゲート254を基準に、デモデュレーション領域222の反対側の第1面202に隣接するウェル領域220に配置される。具体的には、第1電荷保存領域262は、第1垂直伝達ゲート244の、第2垂直伝達ゲート254に対して反対となる側に配置され、第2電荷保存領域272は、第2垂直伝達ゲート254の、第1垂直伝達ゲート244に対して反対となる側に配置される。20

#### 【0039】

第1電荷保存領域262及び第2電荷保存領域272は、各々第1ソースフォロワトランジスタSF1及び第2ソースフォロワトランジスタSF2のゲートと連結される。第1ソースフォロワトランジスタSF1のソース及びドレインは、各々第1選択トランジスタSEL1のソース及びVdd電圧と連結される。第1選択トランジスタSEL1のドレインには、第1出力電圧Vout1が出力される。第2ソースフォロワトランジスタSF2のソース及びドレインは、各々第2選択トランジスタSEL2のソース及びVdd電圧と連結される。第2選択トランジスタSEL2のドレインには、第2出力電圧Vout2が出力される。第1ソースフォロワトランジスタSF1及び第2ソースフォロワトランジスタSF2と、第1選択トランジスタSEL1及び第2選択トランジスタSEL2の各々のソースは、図5において、N+と表示された領域である。30

#### 【0040】

一実施形態において、第1ソースフォロワトランジスタSF1及び第2ソースフォロワトランジスタSF2と、第1選択トランジスタSEL1及び第2選択トランジスタSEL2との各々のゲートは、配線構造体300内の第1リセットゲート282及び第2リセットゲート284と同一レベルに配置される。一実施形態において、第1ソースフォロワトランジスタSF1及び第2ソースフォロワトランジスタSF2と、第1選択トランジスタSEL1及び第2選択トランジスタSEL2との各々のソース及びドレインは、ウェル領域220内の第1電荷保存領域262及び第2電荷保存領域272と同一レベルに配置される。40

#### 【0041】

第1電荷保存領域262及び第2電荷保存領域272を基準に、第1垂直伝達ゲート244及び第2垂直伝達ゲート254の各々の反対側の半導体基板210の第1面202上に、第1リセットゲート(RG1)282及び第2リセットゲート(RG2)284が配置される。第1リセットゲート(282)及び第2リセットゲート(284)は、各々第50

1リセットトランジスタR S 1及び第2リセットトランジスタR S 2を構成することができる。

#### 【0042】

第1リセットゲート282及び第2リセットゲート284と、半導体基板210の第1面202との間には、ゲート絶縁膜280が配置される。図3には、ゲート絶縁膜280が、半導体基板210の第1面202の殆どを覆っているように図示されているが、それに限定されず、一実施形態において、ゲート絶縁膜280は、第1リセットゲート282及び第2リセットゲート284と、半導体基板210の第1面202との間にのみ配置される。

#### 【0043】

第1リセットゲート282及び第2リセットゲート284を基準に、第1電荷保存領域262及び第2電荷保存領域272の各々の反対側の第1面202に隣接するウェル領域220には、第1リセット不純物領域264及び第2リセット不純物領域274が配置される。第1リセット不純物領域264及び第2リセット不純物領域274の各々には、第1リセットドレイン電圧Vrd1及び第2リセットドレイン電圧Vrd2が連結される。一実施形態において、第1リセットドレイン電圧Vrd1と第2リセットドレイン電圧Vrd2は、同一電位を有する。

10

#### 【0044】

イメージセンサ1は、半導体基板210の第2面204上に配置されるマイクロレンズ296をさらに含む。従って、半導体基板210の第2面204は、光の入射面である。半導体基板210の第2面204とマイクロレンズ296との間には、負固定電荷層(negative fixed charge layer)292及び反射防止層294のうち少なくとも1層が配置される。一実施形態において、負固定電荷層292、反射防止層294及びマイクロレンズ296は、半導体基板210の第2面204上に順次に積層されて配置される。一実施形態において、負固定電荷層292は、半導体基板210の第2面204と直接接し、半導体基板210の第2面204上を覆う。一実施形態において、マイクロレンズ296と反射防止層294との間には、バッファ層又はカラーフィルタ層(図示省略)がさらに配置される。

20

#### 【0045】

負固定電荷層292は、例えば、HfO<sub>x</sub>、AlO<sub>x</sub>又はZrO<sub>x</sub>のような高誘電率物質から形成される。反射防止層294は、例えば、SiON、SiC、SiCN又はSiCOによって形成される。前記カラーフィルタ層は、マイクロレンズ296を介して入射された光を通過させ、第2面204を介して、必要な波長の光のみを光電変換領域230に入射させる。

30

#### 【0046】

本発明によるイメージセンサ1は、少なくとも2個の垂直伝達ゲート244, 254を有し、BSI(back side illumination、背面照明)構造を有する。従って、イメージセンサ1を構成するピクセルを小型化し、且つ、伝達トランジスタTS1, TS2のゲートTG1, TG2を相対的に長く形成できるので、イメージセンサのデモデュレーション性能、及び単位面積当たり感度が向上される。

40

#### 【0047】

図6、本発明の一実施形態による、距離測定のためのイメージセンサの作用について説明するタイミング図であり、図7は、本発明の一実施形態によるイメージセンサのピクセルアレイの概略的な平面図であり、図8及び図9は、各々本発明の一実施形態による、距離測定のためのイメージセンサの作用について説明するためのピクセルアレイの平面図である。

#### 【0048】

図6を参照すれば、光源22(図2)からの出力光(light source)と、3次元物体26(図2)で反射され、イメージセンサ1(図3)で受信された反射光(received light)は、ディレイタイムTdを有する。前記出力光は、例えば

50

パルス電圧によるパルス光信号である。一実施形態において、前記パルス光信号は、10 MHz乃至100MHzの周波数を有する。

#### 【0049】

第1垂直伝達ゲートTG1(図3)に印加される第1モジュレーション電圧Vmod1は、前記パルス光信号と同期化されたパルス電圧である。第2垂直伝達ゲートTG2(図3)に印加される第2モジュレーション電圧Vmod2は、前記パルス光信号に対して所定の位相差を有するパルス電圧である。一実施形態において、前記位相差は、180°である。

#### 【0050】

反射光のパルス信号と第1垂直伝達ゲート(TG1)のパルス電圧Vmod1とが重なる時間T1と、反射光のパルス信号と第2垂直伝達ゲート(TG2)のパルス電圧Vmod2とが重なる時間T2との差(T1-T2)が大きいほど、測定された距離は短く示される。反射光のパルス信号と、第1垂直伝達ゲート(TG1)のパルス電圧と重なる時間T1の間、第1出力電圧Vout1が発生し、反射光のパルス信号と、第2垂直伝達ゲート(TG2)のパルス電圧とが重なる時間T2の間、第2出力電圧Vout2が発生する。従って、第1出力電圧Vout1と第2出力電圧Vout2との差を分析(2相(2-phase)アルゴリズム)し、イメージセンサ1から3次元物体26までの距離を決定できる。第1出力電圧Vout1と第2出力電圧Vout2は、単一反射光パルス信号だけではなく、複数の反射光パルス信号の和としても示すことができる。

#### 【0051】

一実施形態において、第1モジュレーション電圧Vmod1及び第2モジュレーション電圧Vmod2で、前記パルス光信号と同期化されたパルス電圧と、180°の位相差が出るパルス電圧と、を印加して得られた第1出力電圧Vout1及び第2出力電圧Vout2と、さらには、第1モジュレーション電圧Vmod1及び第2モジュレーション電圧Vmod2で、前記パルス光信号と90°の位相差が出るパルス電圧と、270°の位相差が出るパルス電圧とを印加して得られた第1出力電圧Vout1及び第2出力電圧Vout2を、共に4相(4-phase)アルゴリズムで分析し、イメージセンサ1から3次元物体26までの距離を決定できる。

#### 【0052】

図7及び図8を参照すれば、第1ピクセルPIXEL1では、0及び180°の相(phase)の反射光を収集し、第3ピクセルPIXEL3では、90°及び270°の相の反射光を収集する。例えば、第1ピクセルPIXEL1の第1モジュレーション電圧Vmod1(図6)は、パルス光信号と同期化されたパルス電圧であり、第2モジュレーション電圧Vmod2(図6)は、パルス光信号と180°の位相差を有するパルス電圧である。また、第3ピクセルPIXEL3の第1モジュレーション電圧Vmod1は、パルス光信号と90°の位相差を有するパルス電圧であり、第2モジュレーション電圧Vmod2は、パルス光信号と270°の位相差を有するパルス電圧である。

その場合、第1ピクセルPIXEL1と第3ピクセルPIXEL3との各々の第1出力電圧のVout1及び第2出力電圧Vout2(図3)を4相アルゴリズムで分析し、イメージセンサ1から3次元物体26までの距離を決定できる。同様に、ピクセルアレイにおいて、第2ピクセルPIXEL2及び第4ピクセルPIXEL4など他の2個のピクセルの各々の第1出力電圧Vout1及び第2出力電圧Vout2を4相アルゴリズムで分析し、イメージセンサ1から3次元物体26の表面までの距離を決定できる。即ち、2個のピクセルから、1個の距離情報を得ることができる。

#### 【0053】

図9を参照すれば、第1ピクセルPIXEL1及び第3ピクセルPIXEL3の各々の第1出力電圧Vout1及び第2出力電圧Vout2を分析し、第3ピクセルPIXEL3、及び他の第1ピクセルPIXEL1aの各々の第1出力電圧Vout1及び第2出力電圧Vout2を分析し、距離を決定できる。即ち、第3ピクセルPIXEL3の第1出力電圧Vout1及び第2出力電圧Vout2は、第1ピクセルPIXEL1の

10

20

30

40

50

第1出力電圧 $V_{out1}$ 及び第2出力電圧 $V_{out2}$ との分析に使用されると同時に、他の第1ピクセルPIXEL\_1aの第1出力電圧 $V_{out1}$ 及び第2出力電圧 $V_{out2}$ との分析にも同時に使用される。他の第1ピクセルPIXEL\_1aは、第3ピクセルPIXEL\_3との分析だけではなく、他の第3ピクセルPIXEL\_3aとの分析にも共に使用される。同様に、第4ピクセルPIXEL\_4は、第2ピクセルPIXEL\_2との分析、及び他の第2ピクセルPIXEL\_2aとの分析に共に使用され、他の第2ピクセルPIXEL\_2aは、他の第4ピクセルPIXEL\_4aとの分析に共に使用される。

#### 【0054】

従って、ピクセルアレイ全体について考慮すれば、1個のピクセルから、1個の距離情報を得ることができるので、該距離情報に係わる解像度が上昇する。

10

#### 【0055】

図10は、本発明の一実施形態による距離測定のためのイメージセンサの作用について説明するタイミング図であり、図511、本発明の一実施形態によるイメージセンサのピクセルアレイの概略的な平面図であり、図12及び図13は、本発明の一実施形態による距離測定のためのイメージセンサの作用について説明するピクセルアレイの平面図である。

#### 【0056】

図10乃至図13は、図3のイメージセンサ1において、第2リセットトランジスタR\_S2、第2ソースフォロワトランジスタS\_F2及び第2選択トランジスタS\_EL2を動作させず、第1リセットトランジスタR\_S1、第1ソースフォロワトランジスタS\_F1及び第1選択トランジスタS\_EL1のみを動作させる場合、距離測定のためのイメージセンサの作用について説明するための図面である。

20

#### 【0057】

図10を参照すれば、光源22(図2)からの出力光と、3次元物体26(図2)で反射されてイメージセンサ1(図3)で受信される反射光(light source)は、ディレイタイムT\_dを有する。前記出力光は、パルス電圧によるパルス光信号である。第1垂直伝達ゲートTG1(図3)に、前記パルス光信号と同期化されたパルス電圧、90°の位相差を有するパルス電圧、180°の位相差を有するパルス電圧、及び270°の位相差を有するパルス電圧を、第1モジュレーション電圧Vmod1で順次に印加し、反射光のパルス信号と、第1垂直伝達ゲート(TG1)のパルス電圧とが重なる時間T3間に発生した第1出力電圧 $V_{out}$ を共に4相アルゴリズムで分析し、イメージセンサ1から3次元物体26までの距離を決定できる。第1出力電圧 $V_{out}$ は、单一反射光パルス信号だけではなく、複数の反射光パルス信号の和としても示すことができる。第2垂直伝達ゲートTG2(図3)に印加される第2モジュレーション電圧Vmod2は、第1モジュレーション電圧Vmod1と180°の位相差を有するパルス電圧である。

30

#### 【0058】

一実施形態において、第1垂直伝達ゲートTG1に、前記パルス光信号と同期化されたパルス電圧、及び180°の位相差が出るパルス電圧を、第1モジュレーション電圧Vmod1で順次に印加して、反射光のパルス信号と、第1垂直伝達ゲートTG1のパルス電圧とが重なる時間T3間に発生した第1出力電圧 $V_{out}$ を、共に2相アルゴリズムで分析し、イメージセンサ1から3次元物体26までの距離を決定できる。第1出力電圧 $V_{out}$ は、单一反射光パルス信号だけではなく、複数の反射光パルス信号の和としても示すことができる。

40

#### 【0059】

図11及び図12を参照すれば、第1ピクセルPIXEL\_1では、0°の相の反射光を収集し、第2ピクセルPIXEL\_2では、90°の相の反射光を収集し、第3ピクセルPIXEL\_3では、180°の相の反射光を収集し、第4ピクセルPIXEL\_4では、270°の相の反射光を収集する。その場合、第1ピクセル乃至第4ピクセルPIXEL\_1, PIXEL\_2, PIXEL\_3, PIXEL\_4の各々の第1出力電圧 $V_{out1}$ (図3)を4相アルゴリズムで分析し、イメージセンサ1から3次元物体26までの距離を決定できる。即ち、4個のピクセルから、1個の距離情報を得ることができる。

50

**【0060】**

図13を参照すれば、PIXEL 1, PIXEL 2, PIXEL 3及びPIXEL 4、PIXEL 1b, PIXEL 2, PIXEL 3b及びPIXEL 4、又はPIXEL 1a, PIXEL 2a, PIXEL 3及びPIXEL 4などの、隣接する4個のピクセルの各々の第1出力電圧Vout1(図3)を4相アルゴリズムで分析し、イメージセンサ1から3次元物体26までの距離を決定できる。即ち、1個のピクセルから、1個の距離情報を得ることができる。

**【0061】**

別途に図示されていないが、一実施形態において、2個のピクセルの各々の第1出力電圧を2相アルゴリズムで分析して距離を決定でき、その場合、2個のピクセル、又は1個のピクセルから、1個の距離情報を得ることができる。

10

**【0062】**

図14乃至図18は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図である。図14乃至図18に係わる説明において、図3に係わる説明と重複する内容は省略する。

**【0063】**

図14を参照すれば、イメージセンサ1aは、光電変換領域230に隣接するウェル領域220の一部分、具体的には、ウェル領域220の内で第1面202の反対側の境界面に隣接する部分に配置される第1バリア不純物領域224をさらに含む。第1バリア不純物領域224は、第1伝達ゲート構造体240及び第2伝達ゲート構造体250の各々と離隔されるように配置される。

20

**【0064】**

第1バリア不純物領域224は、第1導電型を有する。一実施形態において、第1バリア不純物領域224の不純物濃度は、ウェル領域220の不純物濃度より濃い値を有する。第1バリア不純物領域224は、光電変換領域230で発生した光電荷の移動を遮断する。従って、光電変換領域230で発生した光電荷は、第1伝達ゲート構造体240及び第2伝達ゲート構造体250、並びにデモデュレーション領域222に集中して移動する。

**【0065】**

図15を参照すれば、イメージセンサ1bは、デモデュレーション領域222(図3)に対応する部分に配置されるサブウェル領域222aを含む。サブウェル領域222aは、第1導電型を有する。一実施形態において、サブウェル領域222aの不純物濃度は、ウェル領域220の不純物濃度より濃い値を有する。

30

**【0066】**

サブウェル領域222aは、光電荷が、第1垂直伝達ゲート244及び第2垂直伝達ゲート254の間ににおけるトラップ(trap)を防止するか、或いは意図していない箇所への移動を防止する。サブウェル領域222aも、デモデュレーション領域222と同一機能を遂行するので、デモデュレーション領域と称し得る。

**【0067】**

図15には、イメージセンサ1bが、第1バリア不純物領域224を有するようにも図示されているが、それに限定されず、第1バリア不純物領域224は、省略可能である。

40

**【0068】**

図16を参照すれば、イメージセンサ1cは、デモデュレーション領域222において、第1面202に隣接する部分に配置される第2バリア不純物領域226を含む。

**【0069】**

第2バリア不純物領域226は、第1導電型を有する。一実施形態において、第2バリア不純物領域226の不純物濃度は、ウェル領域220の不純物濃度より濃い値を有する。一実施形態において、第2バリア不純物領域226の不純物濃度は、デモデュレーション領域222の不純物濃度より濃い値を有する。

**【0070】**

第2バリア不純物領域226は、少なくとも2個の垂直伝達ゲート244, 254によ

50

つて移動する光電子が、第1電荷保存領域262及び第2電荷保存領域272に迅速に保存されるようとする。

#### 【0071】

図17を参照すれば、イメージセンサ1dは、デモデュレーション領域222b及び第2バリア不純物領域226を含む。デモデュレーション領域222bは、第2導電型を有する。一実施形態において、デモデュレーション領域222bの不純物濃度は、光電変換領域230の不純物濃度より薄い値を有する。

#### 【0072】

第2導電型を有するデモデュレーション領域222bは、光電荷をデモデュレーション領域222bと、第1伝達ゲート構造体240及び第2伝達ゲート構造体250との界面から、デモデュレーション領域222bの中心部に集める。従って、該光電荷が、デモデュレーション領域222bと、第1伝達ゲート構造体240及び第2伝達ゲート構造体250との界面に形成されるトラップによって損失されることを最小化する。

10

#### 【0073】

図18を参照すれば、イメージセンサ1eは、第2面204aに凹凸構造を有する半導体基板210を含む。一実施形態において、半導体基板210は、第2面204aに、第1面202に向けて陥没された複数個のリセス212を有する。複数リセス212の各々には、散乱誘導層214が配置される。負固定電荷層292は、散乱誘導層214を覆い包み、半導体基板210の第2面204aを覆う。従って、散乱誘導層214は、負固定電荷層292を挟み、半導体基板210の第2面204aと離隔される。散乱誘導層214は、例えば、酸化物などの絶縁物からなる。

20

#### 【0074】

イメージセンサ1eの複数のピクセルの各々の間には、DTI (deep trench insulator) 構造物320が配置される。DTI構造物320は、光電変換領域230、特に、第1光電変換領域232の周囲を取り囲むように、半導体基板210内に配置される。DTI構造物320は、半導体基板210の第2面204aから第1面202に向けて延長されるように配置される。一実施形態において、DTI構造物320は、ウェル領域220から離隔するように、半導体基板210の第2面204aから第1面202に向けて延長される。DTI構造物320は、例えば、酸化物、窒化物、酸窒化物、又はそれらの組み合わせからなる絶縁物である。一実施形態において、DTI構造物320は、導電物質層322、及び導電物質層322を覆い包むカバー絶縁層324からなる。導電物質層322は、例えば、ポリシリコン、金属又は金属窒化物からなる。カバー絶縁層324は、酸化物、窒化物、酸窒化物、又はそれらの組み合わせからなる絶縁物である。

30

#### 【0075】

マイクロレンズ296を介して、イメージセンサ1e内に入射される光のうち一部(L1)は、光電変換領域230に向けて進む。マイクロレンズ296を介して、イメージセンサ1e内に入射される光のうち他の一部の光(L2)は、散乱誘導層214によって散乱された後、DTI構造物320によってさらに反射する経路を有する。それを介して、他の一部の光(L2)は、光経路が増大し、光電変換領域230で吸収率が高くなる。

40

#### 【0076】

イメージセンサ1eは、配線構造体300上に配置される背面反射層310をさらに含む。光電変換領域230で吸収されていない光L3は、背面反射層310で反射され、さらに光電変換領域230に進み、光電変換領域230で吸収される。

#### 【0077】

図18で説明した散乱誘導層214、DTI構造物320及び背面反射層310のうち少なくとも一部は、図14乃至図18で説明したイメージセンサ1a, 1b, 1c, 1dにも適用される。

#### 【0078】

図19は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わ

50

る概略的な断面図であり、図20は、本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図であり、図21は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な平面図である。図19乃至図21に係わる説明において、図3乃至図18に係わる説明と重複する内容は、省略される。

#### 【0079】

図19乃至図21を共に参照すれば、イメージセンサ2は、ウェル領域220を有する半導体基板210、光電変換領域230、少なくとも2個の垂直伝達ゲート244, 254、配線構造体300、リセットゲート(RG)282、リセット不純物領域264、第1電荷保存領域(FD)262及び第2電荷保存領域272を含む。第1電荷保存領域262は、ソースフォロワトランジスタSFのゲートとも連結される。ソースフォロワトランジスタSFのソース及びドレインは、選択トランジスタSELのソース及びVdd電圧とも連結される。選択トランジスタSELのドレインには、出力電圧Voutが出力される。リセットゲート282は、リセットトランジスタRSを構成する。リセット不純物領域264及び第2電荷保存領域272の各々には、第1リセットドレイン電圧Vrd1及び第2リセットドレイン電圧Vrd2が連結される。一実施形態において、第1リセットドレイン電圧Vrd1と第2リセットドレイン電圧Vrd2は、同一電位を有する。

10

#### 【0080】

イメージセンサ2は、図10乃至図13で説明したように、図3のイメージセンサ1において、第2リセットトランジスタRS2、第2ソースフォロワトランジスタSF2及び第2選択トランジスタSEL2を動作させず、第1リセットトランジスタRS1、第1ソースフォロワトランジスタSF1及び第1選択トランジスタSEL1のみを動作させる場合と実質的に同一に作用するので、詳細な説明は省略する。

20

#### 【0081】

即ち、イメージセンサ2は、イメージセンサ1において動作させない第2リセットトランジスタRS2、第2ソースフォロワトランジスタSF2及び第2選択トランジスタSEL2を含まず、イメージセンサ1で動作させる第1リセットトランジスタRS1、第1ソースフォロワトランジスタSF1及び第1選択トランジスタSEL1の各々に対応するリセットトランジスタRS、ソースフォロワトランジスタSF及び選択トランジスタSELを含む。

#### 【0082】

30

図22は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な平面図である。

#### 【0083】

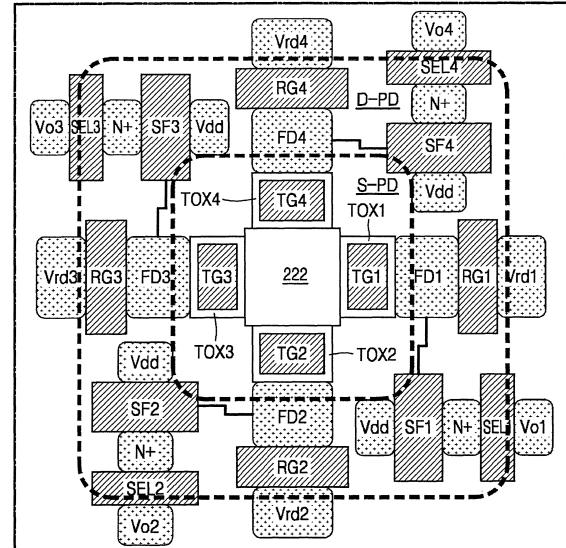

図22を参照すれば、イメージセンサ3は、半導体基板210(図3)の厚み方向に沿って延長され、互いに離隔されている4個の垂直伝達ゲートTG1, TG2, TG3, TG4を含む。第1垂直伝達ゲート乃至第4垂直伝達ゲートTG1, TG2, TG3, TG4は、デモデュレーション領域222を挟み、互いに離隔されるようにも配置される。第1垂直伝達ゲート乃至第4垂直伝達ゲートTG1, TG2, TG3, TG4の各々の周囲には、第1伝達ゲート絶縁膜乃至第4伝達ゲート絶縁膜TOX1, TOX2, TOX3, TOX4が配置される。第1垂直伝達ゲート乃至第4垂直伝達ゲートTG1, TG2, TG3, TG4の各々に対応し、第1電荷保存領域乃至第4電荷保存領域FD1, FD2, FD3, FD4、第1リセットゲート乃至第4リセットゲートRG1, RG2, RG3, RG4、第1リセットドレイン電圧乃至第4リセットドレイン電圧Vrd1, Vrd2, Vrd3, Vrd4が連結される不純物領域、第1ソースフォロワトランジスタ乃至第4ソースフォロワトランジスタSF1, SF2, SF3, SF4、及び第1選択トランジスタ乃至第4選択トランジスタSEL1, SEL2, SEL3, SEL4が配置される。第1選択トランジスタ乃至第4選択トランジスタSEL1, SEL2, SEL3, SEL4の各々のドレインには、第1出力電圧乃至第4出力電圧Vo1, Vo2, Vo3, Vo4が出力される。

40

#### 【0084】

50

イメージセンサ3は、第1垂直伝達ゲートTG1及び第3垂直伝達ゲートTG3、又は第2垂直伝達ゲートTG2及び第4垂直伝達ゲートTG4によって切斷した断面図が、図3に示したイメージセンサ1の断面図と実質的に同一であるので、詳細な説明は省略する。

#### 【0085】

イメージセンサ3は、第1垂直伝達ゲート乃至第4垂直伝達ゲートTG1,TG2,TG3,TG4の各々に、パルス光信号と同期化されたパルス電圧、90°の位相差を有するパルス電圧、180°の位相差を有するパルス電圧、及び270°の位相差を有するパルス電圧が印加される。従って、イメージセンサ3は、1つのピクセルで得られる第1出力電圧乃至第4出力電圧V01,V02,V03,V04を共に4相アルゴリズムで分析し、イメージセンサ3から3次元物体26(図2)までの距離を決定できる。

10

#### 【0086】

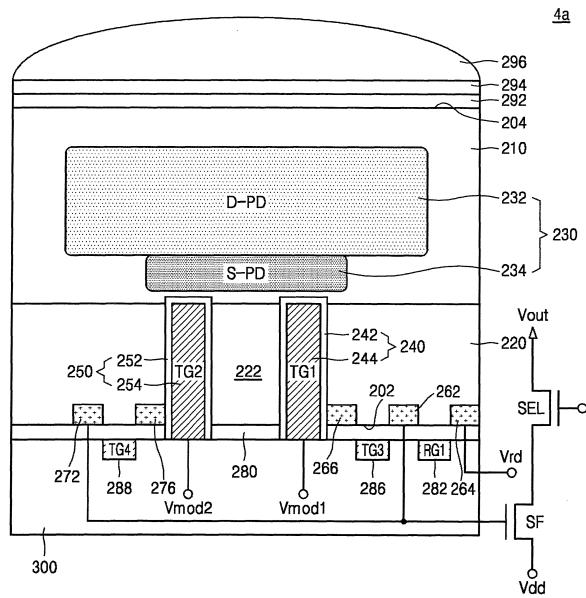

図23は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図であり、図24は、本発明の一実施形態によるイメージセンサの単位ピクセルに係わる等価回路図である。図23及び図24に係わる説明において、図3及び図4に係わる説明と重複する内容は、省略される。

#### 【0087】

図23及び図24を共に参照すれば、イメージセンサ4は、ウェル領域220には、第1面202に隣接し、第1電荷保存領域262及び第2電荷保存領域272、及び第1垂直伝達ゲート244及び第2垂直伝達ゲート254の各々の間に配置される第1ストレージ拡散領域(SD1)266及び第2ストレージ拡散領域(SD2)276、並びに、第1電荷保存領域262及び第2電荷保存領域272と、第1ストレージ拡散領域266及び第2ストレージ拡散領域276との各々の間で、半導体基板210の第1面202上に配置される第1水平伝達ゲート(TG3)286及び第2水平伝達ゲート(TG4)288をさらに含む。

20

#### 【0088】

第1電子保存領域(FD1)262及び第2電子保存領域(FD2)272は、各々第1ソースフォロートランジスタSF1及び第2ソースフォロートランジスタSF2のゲートと連結される。

#### 【0089】

イメージセンサ4は、第1ストレージ拡散領域266及び第2ストレージ拡散領域276、及び第1水平伝達ゲート286及び第2水平伝達ゲート288をさらに含み、グローバルシャッタ(global shutter)機能を遂行する。また、イメージセンサ4は、第1垂直伝達ゲート244及び第2垂直伝達ゲート254、並びに、第1水平伝達ゲート286及び第2水平伝達ゲート288からなる4個の伝達ゲートを含み、ノイズが低減される。

30

#### 【0090】

図25は、本発明の一実施形態によるイメージセンサの単位ピクセルの主要部分に係わる概略的な断面図であり、図26は、本発明の一実施形態によるイメージセンサの単位ピクセルに対応する等価回路図である。図25及び図26に係わる説明において図23及び図24に係わる説明と重複する内容は、省略される。

40

#### 【0091】

図25及び図26を共に参照すれば、イメージセンサ4aは、図23及び図24に示されたイメージセンサ4と異なり、1個の選択トランジスタSELが継続接続された1個のソースフォロートランジスタSFが、第1電子保存領域(FD1)262及び第2電子保存領域(FD2)272と連結され、さらに1個のリセットトランジスタRSが、第1電荷保存領域(FD1)262及び第2電荷保存領域(FD2)272と連結される。即ち、第1ストレージ拡散領域(SD1)266及び第1電荷保存領域(FD1)262、並びに、第2ストレージ拡散領域(SD2)276及び第2電荷保存領域(FD2)272が、1個のソースフォロートランジスタSF、1個の選択トランジスタSEL、及び1個のリセットトランジスタRSを共有する。

50

## 【0092】

本発明によるイメージセンサは、少なくとも2個の垂直伝達ゲートを含み、更に好ましくはB S I構造を有する。従って、該イメージセンサを構成するピクセルを小型化し、且つ伝達トランジスタのゲートを相対的に長く形成できるので、イメージセンサの感度が向上する。

## 【0093】

以上、本発明について、望ましい実施形態を挙げて詳細に説明したが、本発明は、実施形態に限定されることなく、本発明の技術的思想及び範囲内で、当分野で当業者によってさまざまな変形及び変更が可能である。

## 【産業上の利用可能性】

## 【0094】

本発明の距離測定のためのイメージセンサは、例えば、撮像関連の技術分野に効果的に適用可能である。

## 【符号の説明】

## 【0095】

|                                                   |         |    |

|---------------------------------------------------|---------|----|

| 1 , 1 a , 1 b , 1 c , 1 d , 1 e , 2 , 3 , 4 , 4 a | イメージセンサ |    |

| 1 5           システム                                |         | 10 |

| 1 7           イメージングモジュール                         |         |    |

| 1 9           プロセッサ                               |         |    |

| 2 0           メモリモジュール                            |         | 20 |

| 2 2           光源                                  |         |    |

| 2 4           イメージセンサ部                            |         |    |

| 2 6           3次元物体                               |         |    |

| 2 8 、 2 9     ( 照明方向を示す ) 矢印                      |         |    |

| 3 0 、 3 1     光放射経路を示す破線                          |         |    |

| 3 3           発光素子                                |         |    |

| 3 4           光制御器                                |         |    |

| 3 5           投射レンズ                               |         |    |

| 3 6 、 3 7     ( 集光方向を示す ) 矢印                      |         | 30 |

| 3 8 、 3 9     ( 集光経路を示す ) 破線                      |         |    |

| 4 2           2次元ピクセルアレイ                          |         |    |

| 4 4           収集レンズ                               |         |    |

| 4 6           ピクセルアレイ制御 / 処理部                     |         |    |

| 2 0 2          第1面                                |         |    |

| 2 0 4 , 2 0 4 a     第2面                           |         |    |

| 2 1 0          半導体基板                              |         |    |

| 2 1 2          リセス                                |         |    |

| 2 1 4          散乱誘導層                              |         |    |

| 2 2 0          ウェル領域                              |         |    |

| 2 2 2          デモデュレーション領域                        |         | 40 |

| 2 2 2 a        サブウェル領域                            |         |    |

| 2 2 2 b        デモデュレーション領域                        |         |    |

| 2 2 4          第1バリア不純物領域                         |         |    |

| 2 2 6          第2バリア不純物領域                         |         |    |

| 2 3 0          光電変換領域                             |         |    |

| 2 3 2          第1光電変換領域 ( D - P D )               |         |    |

| 2 3 4          第2光電変換領域 ( S - P D )               |         |    |

| 2 4 0          第1伝達ゲート構造体                         |         |    |

| 2 4 2          伝達ゲート絶縁膜                           |         |    |

| 2 4 4          第1垂直伝達ゲート                          |         | 50 |

|       |                         |

|-------|-------------------------|

| 2 5 0 | 第 2 伝達ゲート構造体            |

| 2 5 2 | 伝達ゲート絶縁膜                |

| 2 5 4 | 第 2 垂直伝達ゲート             |

| 2 6 2 | 第 1 電荷保存領域 ( F D 1 )    |

| 2 6 4 | 第 1 リセット不純物領域           |

| 2 6 6 | 第 1 ストレージ拡散領域 ( S D 1 ) |

| 2 7 2 | 第 2 電荷保存領域 ( F D 2 )    |

| 2 7 4 | 第 2 リセット不純物領域           |

| 2 7 6 | 第 2 ストレージ拡散領域 ( S D 2 ) |

| 2 8 0 | ゲート絶縁膜                  |

| 2 8 2 | 第 1 リセットゲート ( R G 1 )   |

| 2 8 4 | 第 2 リセットゲート ( R G 2 )   |

| 2 8 6 | 第 1 水平伝達ゲート ( T G 3 )   |

| 2 8 8 | 第 2 水平伝達ゲート ( T G 4 )   |

| 2 9 2 | 負固定電荷層                  |

| 2 9 4 | 反射防止層                   |

| 2 9 6 | マイクロレンズ                 |

| 3 0 0 | 配線構造体                   |

| 3 1 0 | 背面反射層                   |

| 3 2 0 | D T I 構造物               |

| 3 2 2 | 導電物質層                   |

| 3 2 4 | カバー絶縁層                  |

## 【図面】

## 【図 1】

## 【図 2】

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

【図 7】

【図 8】

【図 9】

【図 10】

10

20

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

【図 1 4】

20

30

40

50

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

10

20

30

40

50

【図 19】

【図 20】

10

2

【図 21】

【図 22】

30

3

40

50

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

## (51)国際特許分類

|                         | F I    |       |         |

|-------------------------|--------|-------|---------|

| H 01 L 27/088 (2006.01) | H 01 L | 27/04 | A       |

| H 01 L 21/822 (2006.01) | H 04 N | 5/369 |         |

| H 01 L 27/04 (2006.01)  | G 01 C | 3/06  | 1 2 0 Q |

| H 04 N 5/369 (2011.01)  |        |       |         |

| G 01 C 3/06 (2006.01)   |        |       |         |

審査官 加藤 俊哉

## (56)参考文献

米国特許出願公開第 2015 / 0115291 (U.S., A1)

特開 2016 - 100347 (JP, A)

特開 2015 - 029054 (JP, A)

特開 2015 - 153772 (JP, A)

米国特許出願公開第 2016 / 0056198 (U.S., A1)

特開 2005 - 353994 (JP, A)

特開平 03 - 109769 (JP, A)

米国特許出願公開第 2014 / 0374808 (U.S., A1)

特開 2010 - 114273 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 27 / 146

H 01 L 31 / 10

H 01 L 29 / 423

H 01 L 21 / 8234

H 01 L 21 / 822

H 04 N 5 / 369

G 01 C 3 / 06