(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-27762

(P2009-27762A)

(43) 公開日 平成21年2月5日(2009. 2.5)

(51) Int.Cl.

H04N 7/32 (2006.01)

F 1

H04N 7/137

Z

テーマコード(参考)

5C059

審査請求 有 請求項の数 10 O L (全 15 頁)

(21) 出願番号 特願2008-286621 (P2008-286621)

(22) 出願日 平成20年11月7日 (2008. 11. 7)

(62) 分割の表示 特願2004-352384 (P2004-352384)

の分割

原出願日 平成16年12月6日 (2004. 12. 6)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 斎藤 昇平

東京都国分寺市東恋ヶ窪1丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 長谷 昌

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 泉原 史幸

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】動き補償画像符号化装置及び符号化方法

## (57) 【要約】

## 【課題】

動き補償画像符号化装置又は符号化方法において、動きベクトル決定のための演算処理量を軽減し、実時間で動画像情報の符号化処理を行うことを可能とする。

## 【解決手段】

動き補償画像符号化において、動きベクトルの検索(120)を、マクロプロック及びマクロプロックを分割したサブプロックについて整数画素精度で検索し(122)、その検索結果によって小数画素精度で動きベクトルの検索を行うべきプロック形状を形状モードとして決定し(124)、その形状モードのプロックについて少數画素精度で動きベクトルの検索を行って(125)、予測画像を得るために動きベクトルとする。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

動画像のフレームを分割したブロック単位で動き検索を行い、検索した動きベクトルを用いて動き補償予測を行い生成した予測画像と上記動画像との間の差分信号及び動き情報を符号化する動画像情報の符号化装置であって、

上記動き検索を行う動き検索部が、第1の複数画素ブロック及び上記第1の複数画素ブロックを分割した複数種の形状のサブブロックの動きベクトルの探索を整数画素精度で行う第1の動きベクトル探索部と、上記第1の動きベクトル探索部で得られた情報を用いて、上記複数種の形状ブロックの1ないし複数の形状を選択する形状モード選択部と、上記形状モード選択部で選択された1ないし複数のサブブロックに対して小数画素精度の動きベクトル探索を行う第2の動きベクトル探索部をもつことを特徴とする動画像情報の符号化装置。

10

**【請求項 2】**

請求項1記載の動画像情報の符号化装置において、形状モード選択部が上記第1の動きベクトル探索部による動きベクトルの各種形状ブロックの符号化コストを計算し、符号化コスト値が最小の形状を決める手段をもち、上記第2の動きベクトル探索部が上記符号化コスト値が最小の形状ブロックについて小数画素精度の動きベクトル探索を行うことを特徴とする動画像情報の符号化装置。

**【請求項 3】**

請求項1記載の動画像情報の符号化装置において、形状モード選択部が上記第1の動きベクトル探索部による動きベクトルの各種形状ブロックの符号化コスト値を計算し、符号化コスト値が小さい順に複数の形状を決める手段をもち、上記第2の動きベクトル探索部が上記複数の形状ブロックについて小数画素精度の動きベクトル探索を行い、上記複数の形状ブロックについて小数画素精度の動きベクトルによる各種形状ブロックの符号化コスト値を計算し、上記形状モード選択部がその符号化コスト値が最小の形状を決める手段を持つことを特徴とする動画像情報の符号化装置。

20

**【請求項 4】**

請求項1又は2記載の動画像情報の符号化装置であって、上記動き検索を行う動き検索部が第2の動きベクトル探索部を駆動するか否かを決定する制御を行う符号化モード選択切り換え処理部を有し、上記動き検索部は、第2の動きベクトル探索部を駆動しないと決定したとき、第2の動きベクトル探索部を駆動せず、全ての形状モードに対し小数画素精度の動きベクトル検索を行い、動きベクトルを決定する手段をもつことを特徴とする動画像情報の符号化装置。

30

**【請求項 5】**

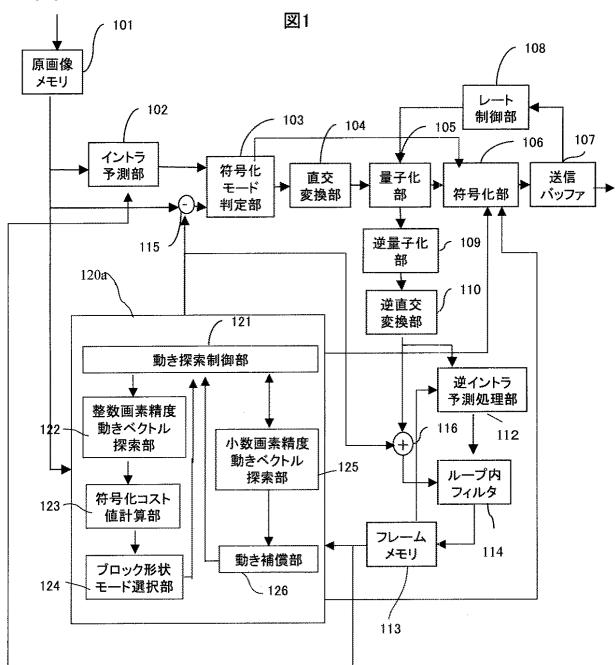

請求項1ないし4の一つに記載の動画像情報の符号化装置において、上記記載の第1の複数画素ブロック葉 $16 \times 16$ 画素のマクロブロックであり、上記サブブロックは $16 \times 8$ 画素、 $8 \times 16$ 画素、 $8 \times 8$ 画素、 $4 \times 8$ 画素、 $8 \times 4$ 画素、 $4 \times 4$ 画素のブロックであり、上記小数画素精度は $1/2$ 画素精度、 $1/4$ 画素精度であることを特徴とする動画像情報の符号化装置。

**【請求項 6】**

動画像のフレームを分割したブロック単位で動き検索を行い、検索した動きベクトルをもちいて動き補償予測を行い生成した予測画像と上記動画像との間の差分信号及び動き情報を符号化する動画像情報の符号化手順をコンピュータに実行させるためのプログラムであって、

上記動き検索を行う手順が、第1の複数画素ブロック及び上記第1の複数画素ブロックを分割した複数種の形状のサブブロックの動きベクトルの探索を整数画素精度で行う第1のステップと、

上記第1のステップで得られた情報を用いて、上記複数種の形状ブロックの1ないし複数を選択する第2のステップと、

上記第2のステップで選択された1ないし複数のサブブロックに対して小数画素精度の動きベクトル探索を行う第3のステップをもつことを特徴とするプログラム。

40

50

**【請求項 7】**

請求項 6 記載の動画像情報のプログラムにおいて、上記第 2 のステップが符号化コストを計算し、その符号化コスト値が最小の形状ブロックを識別する形状モード情報を有することを特徴とするプログラム。

**【請求項 8】**

請求項 6 記載の動画像情報のプログラムにおいて、上記第 2 のステップが符号化コスト値を計算し、その符号化コスト値が小さい順に複数の形状ブロック種別を識別する第5ステップと、上記第5ステップで得られた複数の形状ブロックに対して小数画素精度の動きベクトル探索を行う第 6 のステップと、第 6 のステップで得られた動きベクトルによる符号化コスト値を計算し、その符号化コスト値が最小の形状ブロックを識別する形状モード情報を有することを特徴とするプログラム。 10

**【請求項 9】**

請求項 6 7 記載のプログラムにおいて、

上記第 1 のステップの後に第 2 のステップを行うか否かを決定するステップを有し、第 2 のステップを行うと決定したときは上記第 2 のステップを実行し、第 2 のステップを行わないと決定したときは全ての形状のサブブロックについて小数画素精度の動きベクトルの検索を行い動きベクトルを決める第 7 ステップと、第7ステップで決められた小数画素精度の動きベクトルの中で符号化コストの最小のものを選択する第8ステップとを有することを特徴とするプログラム。

**【請求項 10】**

請求項6ないし9の一つに記載のプログラムにおいて、上記第 1 の複数画素ブロックは  $16 \times 16$  画素のマクロブロックであり、上記サブブロックは  $16 \times 8$  画素、  $8 \times 16$  画素、  $8 \times 8$  画素、  $4 \times 8$  画素、  $8 \times 4$  画素、  $4 \times 4$  画素のブロックであり、上記小数画素精度は  $1/2$  画素精度、  $1/4$  画素精度であることを特徴とするプログラム。 20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、動き補償画像符号化装置及び符号化方法、さらに詳しく言えば、動画像のフレームを分割したブロック単位で動き補償予測を行い生成した予測画像と上記動画像との間の差分信号及び動き情報すなわち動きベクトルを符号化する動画像情報の圧縮符号化技術、特に動きベクトルの探索技術に関するものである。 30

**【背景技術】****【0002】**

近年、MPEG (Moving Picture Experts Group) に代表されるように、内挿符号化、動き補償予測、直交変換、量子化、可変長符号化を用いた動画像符号化装置が広く普及している。動き補償予測では、参照フレームから動きを推定し、予測残差信号と動きベクトル情報を符号化している。ITU-T Recommendation H.263やISO / IEC International Standard 14496 - 2(MPEG - 4 Visual)などの国際標準化動画像符号化方式では、フレーム画像をマクロブロックと呼ばれる  $16 \times 16$  画素のブロックに分割し、さらにマクロブロックを  $8 \times 8$  画素ブロックに分けて、各ブロック単位で動き補償予測を行っている。 40

**【0003】**

また、より高圧縮率な符号化方式である規格H.264/AVCでは、マクロブロックを  $16 \times 8$ 、  $8 \times 16$ 、  $8 \times 8$ 、  $4 \times 8$ 、  $8 \times 4$ 、  $4 \times 4$  画素の複数のブロック(サブブロック)に分割し、各ブロック単位で動き補償予測を行っている(非特許文献 1 参照)。複数のサブブロックを用いることで、平坦で動きの少ない画像から細かい複雑な動きをする画像に至るまで、適応的に動き予測を行うことが可能となる。

上記MPEG-4やH.264/AVC符号化方式では、 $1/2$ 、 $1/4$ 画素精度の動き補償予測が行われている。 $1/2$ 、 $1/4$ 画素精度の動き補償予測とは、実際に得られる整数画素位置の画素を用いて内挿処理を行い、仮想的に $1/2$ 画素位置や $1/4$ 画素位置の画素値を作りだすことによって動き予測精度を向上させる方法である。 50

**【0004】**

従来の動画像情報符号化では、マクロブロック及びサブブロックの全てに対して小数画素精度の動き情報（動きベクトル）を検索して、その後で最適の動きベクトルを決定している。また、ブロックの形状、大きさによって動きベクトル検索の画素精度を変える技術が、例えば特許文献1で提案されている。

**【0005】**

【非特許文献1】Joint Video Team (JVT) of ISO/IEC MPEG & ITU-T VCEG : "Text of International Standard of Joint Video Specification", ITU-T Rec. H.264 | ISO/IEC 14496-10 Advanced Video Coding, (December, 2003).

**【特許文献1】特開2004-48552号公報**

10

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

上述のように、H.264/AVCのようなマクロブロック及びサブブロックのようなブロック形状の種類が多数存在する場合に、マクロブロック及び複数種のサブブロック全てに対して小数画素精度の動きベクトルを求め、最適の動きベクトルを決定し、予測画像を得て、動き補償予測画像符号化を行う方式では、予測画像を生成のための演算量が膨大になる。特に大きいサイズの画像フレームに対しては、実時間で符号化処理を行うことが困難である。

**【0007】**

20

ブロックの形状、大きさによって動きベクトル検索の画素精度を固定的に変える技術では、符号化効率が低下する場合がある。また、演算量の観点から、符号化効率の悪いブロック形状に対しても、固定的に少数画素精度が割当てられる場合がある。

従って本発明の目的は、動き補償画像符号化を行う際に、マクロブロック及び複数種のサブブロックの動きベクトルを整数精度及び小数画素精度で検索し、動きベクトルを探索する符号化方式において、画質を実質的に保持しながら、動きベクトル探索処理演算量の大削減を実現する動き補償動画像符号化装置及び動き補償動画像符号化をコンピュータで実施させるためのプログラムを提供するものである。

**【課題を解決するための手段】****【0008】**

30

上記課題を解決するために、本願において開示する代表的な発明概要は以下のとおりである。

本願の動き補償動画像符号化装置は、動きベクトル探索部が、第1の複数画素ブロック及び上記第1の複数画素ブロックを分割した複数種の形状の小ブロック（サブブロック）の動きベクトル探索を整数画素精度で行う第1の動きベクトル探索部と、上記第1の動きベクトル探索部で得られた情報を用いて、上記サブブロックの1ないし複数種を選択する形状モード選択部と、上記形状モード選択部で選択された1ないし複数種のサブブロックに対して小数画素精度の動きベクトル探索を行う第2の動きベクトル探索部をもつ。すなわち、小数画素精度の動きベクトル探索を行うブロック種別の決定を、第1の複数画素ブロック及び上記第1の複数画素ブロック分割した複数種の形状の小ブロック動きベクトルの探索を整数画素精度で行って得られた情報に基づいて実行する形状モード選択部とを持つ。

40

**【発明の効果】****【0009】**

本発明により、MPEG-4やH.264/AVC符号化方式の動画像符号化のように、マクロブロック及びマクロブロックを分割した複数種の小ブロックに対して、1/2、1/4画素精度の動き補償予測を行う場合に、1/2、1/4画素精度の動ベクトル探索の対象のブロックが大幅に軽減されるため、内挿演算処理量を大幅に削減することができ、符号化処理を高速に行うことができる。

**【発明を実施するための最良の形態】**

50

## 【0010】

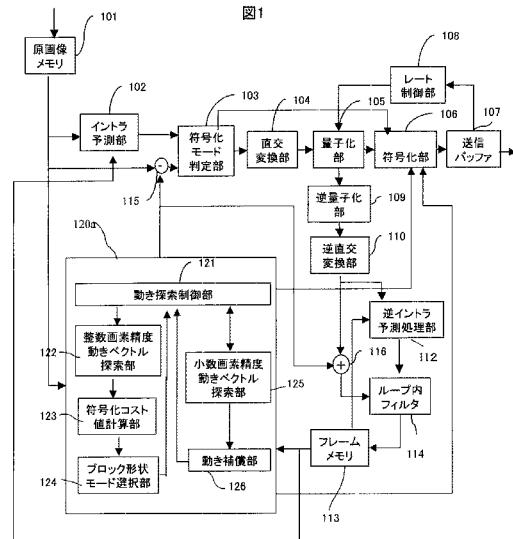

&lt;実施例1&gt;

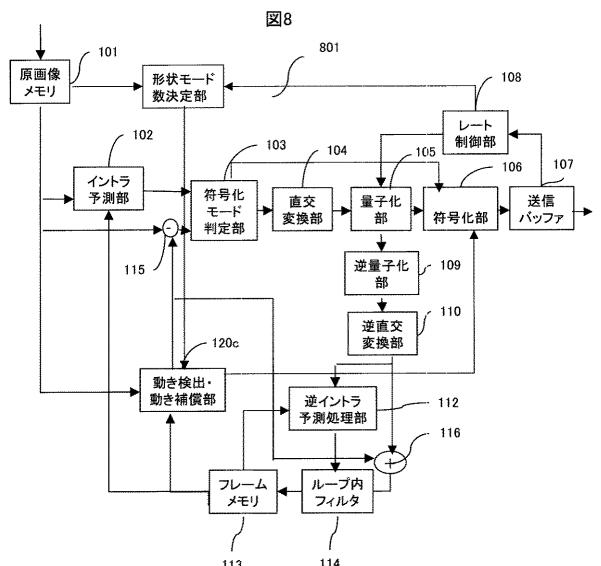

図1は本発明による動き補償画像符号化装置の一実施例の構成を示すブロック構成図を示す。同図に示すように、動き補償画像符号化装置は、画像情報のデータを記憶する原画像メモリ101、イントラ予測部102、符号化モード判定部103、直交変換部104、量子化部105、逆量子化部109、逆直交変換部110、逆イントラ処理部112、フレームメモリ113、ループ内フィルタ114、動き検出・動き補償部120、符号化部106、送信バッファ107、レート制御部108をもつ。

## 【0011】

上記構成において、動き検出・動き補償部120aを除いては、従来知られている画像情報符号化装置と実質的に同じである。すなわち原画像メモリ101は、符号化される原画像フレームのデータを一時的にバッファリングする。上記バッファリングされた画像フレームのデータを $16 \times 16$ の画素からなるマクロブロック単位で読み出し、イントラ予測部102及び動き検出・動き補償部120aに入力する。イントラ予測部102は、符号化しようとするマクロブロックがある同じ画像フレームで既に符号化された隣接ブロックの境界画素の信号レベルから予測ブロックの画素の信号レベルを予測し、それらの差分を取って残差成分を作り、その残差成分の情報に基づいてイントラモード符号化の選択が行われる。

10

## 【0012】

一方、インターモード符号化の予測処理を行う動き検出・動き補償部120aでは、フレームメモリ113に格納されている参照画像フレームから、探索ブロック、すなわち原画像メモリ101から入力し符号化しようとするマクロブロックと最も画像が似ているブロックの位置を検出し、その位置の画像を予測画像とする。上記画像が似ている位置の検出は、原画像と予測画像の残差成分や発生符号量が最も小さくなる参照画像ブロックが選択される。

20

符号化モード判定部103では、イントラ予測部102で選択されたイントラモード符号化と動き検出・動き補償部120aで選択された情報を利用したインターモード符号化との符号化効率の高い方の符号化モードが選択される。符号化モード判定部103において選択された符号化対象信号すなわち画像の予測誤差信号は、直交変換部104、量子化部105、符号化部106、送信バッファ107へ伝送される。ここで、直交変換部104では、DCT等の直交変換が行われ、直交変換係数は、量子部105で量子化処理が行われる。量子部105で量子化された変換係数は、符号化部106により、可変長符号化、算術符号化等の可逆符号化が行われた後、送信バッファ107に蓄積され、画像圧縮情報として出力される。

30

## 【0013】

また、量子化部105より出力された変換係数は、逆量子化部109により入力され、逆量子化が施され、逆直交変換部110において逆直交変換が施された後、符号化モード判定部103でイントラモードが選択された画像の符号は逆イントラ処理部112により、逆イントラ予測が行われる。逆イントラ予測が行われた復号化画像情報は、ループ内フィルタ112によりデブロック処理が行われ、ブロック歪みが除去された後、フレームメモリ113に格納される。なおループ内フィルタ112は適用してもしなくても良い。

40

## 【0014】

一方、符号化モード判定部103でインターモードが選択された画像は、逆直交変換部110において逆直交変換が施された後、動き検出・動き補償部120aにおいて作られた予測画像ブロックの動き補償がなされた画像信号と加算器116で加算される。加算器116の出力は、ループ内フィルタ112によりデブロック処理が行われ、ブロック歪みが除去された後、フレームメモリ113に格納される。

## 【0015】

動き検出・動き補償部120aでは、フレームメモリ113に格納されている画像データを参照画像として用いてマクロブロック単位に動きベクトルが検出され、検出された動きベクトルに対応する参照画像ブロックの画像の動き補償が行なわれ、予測画像（動き補償され

50

た画像ブロック)として生成される。その際、動き検出・動き補償部120aで利用されるフレームメモリに格納されているフレーム数は複数であってもよい。

動き検出・動き補償部120aで検出された動きベクトル情報も符号化部106に送られ、可変長符号化、算術符号化等の可逆符号に変換される。動き検出・動き補償部120aで得られた予測画像は減算器115及び加算器116加えられる。減算器115では原画像と予測画像の差分が取られ、その残差成分情報は形状モード符号化選択時に利用される。

次に、本発明の主要部である動き検出・動き補償部120aの構成動作を図2, 3及び4を参照して説明する。

#### 【0016】

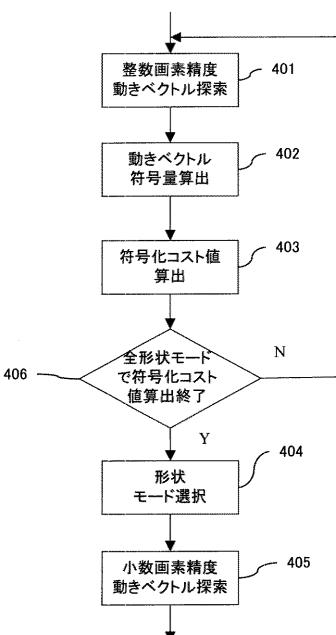

図4は、動き検出・動き補償部120aの機能構成、処理の流れを示すフローチャート図である。

動き検出・動き補償部120aでは、動き探索制御部121の制御に従って、符号化対象画像ブロックと参照フレームメモリ113からの参照画素データが整数画素精度動きベクトル探索制御部122に取り込まれる。整数画素精度動きベクトル探索制御部122では、図2に示すような複数種類のブロック201, 202, 203, 204, 0205, 206、及び207(16×16のマクロブロック及び16×8(202)、8×16(203)、8×8(204)、4×8(205)、8×4(206)、4×4(207)画素の複数ブロック)のそれについて整数画素精度の動きベクトルをブロックマッチング法に基づいた演算処理によって求める(図4、ステップ401)。この段階では、全部ロックに対してブロックマッチングの演算処理が行われるが、次に述べる仮想画素を作る内挿演算を必要としないので、演算は高速に行われる。図2の各ブロックの辺に示す数字は画素の行数及び列数を示す。

#### 【0017】

動きベクトル探索は探索ブロックとフレームメモリ113の予測画像フレームの上記探索ブロックに対応する位置の近傍のブロックをブロックマッチング法に基づいて行い、誤差量が最小となる位置を整数画素動きベクトルとする。誤差量は原画像と予測画像の二乗誤差の和(SSD)や、差分絶対値の和(SAD)などを用いる。

#### 【0018】

符号化コスト値計算部123は、動きベクトル探索制御部122で検索した複数種類のブロックそれぞれの整数画素精度の動きベクトルに対する動きベクトルを用いた形状モード符号化による符号量を算出する(図4、ステップ402)と共に、各動きベクトルの符号量予測誤差を算出する。動きベクトルの符号量Rは、周囲のブロックの動きベクトルから算出された動きベクトルの予測値と動きベクトル探索で求められた動きベクトルとの差分値(MVD)を可逆符号化することによって算出される。但し、ステップ401で得られる動きベクトルは整数画素精度である。動きベクトルとの差分値MVDを整数画素精度MVDと呼ぶことにする。さらに、符号化コスト計算部123は、検出された上記各ブロックの動きベクトルのときの差分絶対値の和(SAD)情報と上記整数画素精度MVDを用いて符号化コスト値の算出を行う(図4、ステップ403)。

#### 【0019】

ブロック形状モード選択部124は、符号化コスト計算部123で得られた各ブロックの上記符号化コスト値が最小となるブロック形状を選択し、選択したブロック形状を指定する情報を形状モード信号として動き探索制御部121に送る(図4、ステップ404)。

動き探索制御部121は小数画素精度動きベクトル探索部125に対し上記形状モード信号に対応する形状のブロックの小数画素精度動きベクトル探索命令を送る(図4、ステップ405)。小数画素精度動きベクトル探索部125は上記形状モード信号に対応する形状のブロックを選択し、選択されたブロックの仮想画素を内挿処理演算によって作り、内挿処理演算によって求められる仮想画素を含む参照画素ブロックを生成する。そして原画像ブロックと仮想画素を含む参照画素ブロックとのブロックマッチング法によって小数画素精度の動きベクトル探索を行う(図4、ステップ405)。上記内挿処理演算によって求められる仮想画素の生成はフィルタ演算処理によって実現される。

フィルタ演算処理による輝度成分の1/2画素精度と1/4画素精度の仮想画素の生成について説

10

20

50

30

40

50

明する。

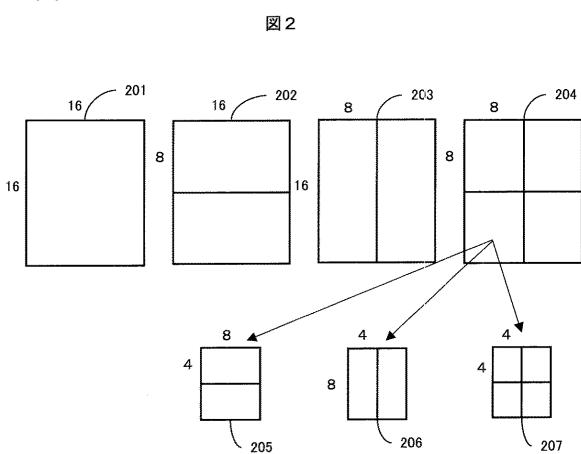

### 【0020】

図3は、内挿処理演算によって求められる仮想画素を説明するための画素配列の例を示す図である。図3は便宜上実在の $6 \times 6$ 画素(例えば、A、B、～R、S、Tなど)、1/2画素精度検出のための仮想画素(a,b,c,～l、mなど)，及び1/4画素精度の仮想画素を例示する。1/2画素精度の仮想画素c(301)は、整数画素E(303)、F(304)、G(305)、H(306)、I(307)、J(308)を用いて次式(数式1)の演算によって生成される。

### 【0021】

$$c=\text{round}((E-5*F+20*G+20*H-5*I+J)/32) \quad (\text{数式1})$$

ここで、roundは丸めを示す。数字5, 20, などはフィルタ係数を示す。

さらに1/4画素精度のフィルタ演算においては、1/2画素精度で得られた仮想画素値の平均値をとって求められる。例えば、図2に示す1/4画素精度の仮想画素cc(302)は1/2画素c(301)とg(309)を用いて次式(数式2)の演算によって求められる。

### 【0022】

$$cc=\text{round}((c+g)/2) \quad (\text{数式2})$$

一般的に、内挿処理演算はフィルタ処理のため、フィルタ係数が多いほど演算量が多くなる。

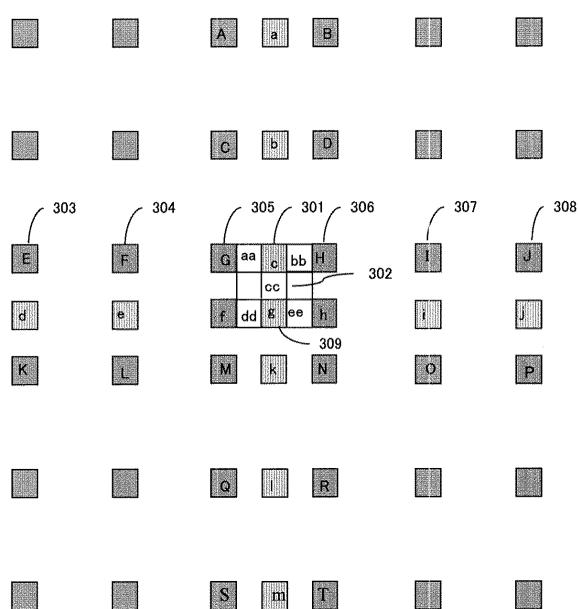

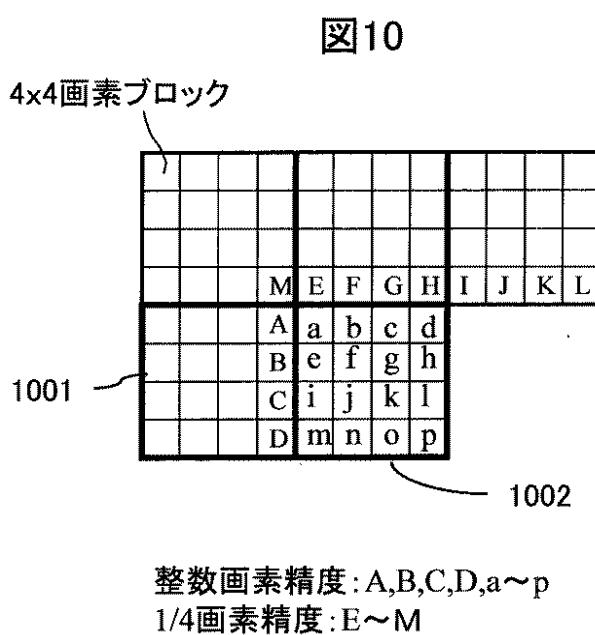

ここで、符号化コスト値はSADではなく、原画像と予測画像の二乗誤差の和(SSD)でも良い。ただし、SADやSSDだけではブロック形状の小さいモードが選択されやすくなり符号化効率が低下するため、動きベクトルの差分符号量を考慮した評価関数が一般的に用いられる。動きベクトルの差分符号量を考慮した評価関数を用いて符号化コスト値を求める際に利用する予測動きベクトルは、隣接ブロックの小数画素精度の動きベクトルが得られないときは、整数画素精度の動きベクトル情報を用いることとする。例えば、マクロブロック単位でパイプライン処理に基づいて整数画素精度の動きベクトル探索と小数画素精度の動きベクトル探索が異なるステージで符号化処理が行われる場合、図10に示すように、符号化対象マクロブロック(1002)の符号化コスト値計算に利用する周辺の動きベクトル情報A～M(A～Bの升目は $4 \times 4$ 画素のブロック)のうち符号化対象マクロブロックの1つ前のマクロブロック(1001)のA～Dのブロックは整数画素精度の動きベクトルしか用いることができない。そこで、本方法を用いることにより、ブロック形状モードの選択処理を小数画素精度の動きベクトル探索処理が終了するまで待つ必要がなく、整数画素精度の動きベクトル探索直後に実行できるため高速に符号化処理を行うことが可能となる。なお、整数画素精度の動きベクトル差分符号量と、小数画素精度の動きベクトル差分符号量はほぼ同等であるため、符号化コスト値の差はほとんど変わらず符号化性能低下への影響も小さい。本方法は、以下の実施例についても適用できる。

動き補償部126は、上記小数画素精度動きベクトル探索部125で選択された形状モードの小数画素精度の動きベクトル情報及び予測誤差情報を用いて予測画像を作成する。動きベクトル情報の一部は符号化部106に加えられ符号化される。また、予測画像は減算器115に加えられる。

### <実施例2>

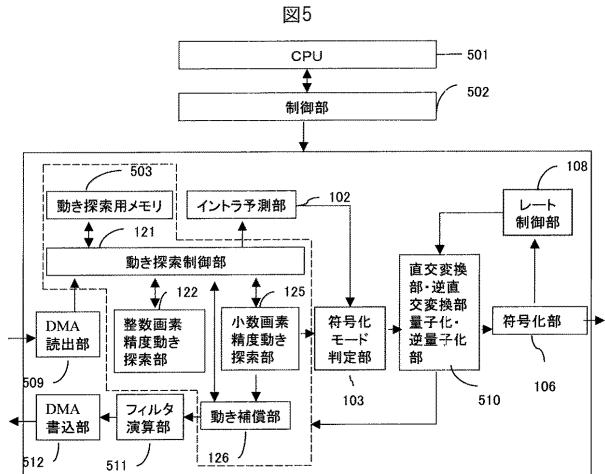

図5は本発明による動き補償画像符号化装置をCPUなどの信号処理装置を用いて構成した実施例の構成を示すブロック図である。図1の実施例1と同一機能ブロックについては図1と同一番号を付して説明を省く。図1に示したデータ伝送及び制御は図5に示す制御部502で行われる。また、原画像メモリ101、フレームメモリ113からのデータはDMA読出部509により読み込まれ、動き検出・動き補償部120へ传送される。

### 【0023】

動き検出・動き補償部120aは、動き探索制御部121、整数画素精度動き探索部122、小数精度動き探索部125、動き補償部126、動き探索用メモリ503から構成されている。また、イントラモードを選択するイントラ予測部102、イントラモードとインターモードを選択する符号化モード判定部103、可逆符号化を行う係数符号化部106、レート制御を行うレート制御部108、デブロックフィルタ処理を行うループ内フィルタ114は、それぞれ図5

10

20

30

40

50

のイントラ予測部102、符号化モード判定部103、符号化部106、レート制御部108、フィルタ演算部511に対応している。また、図1の直交変換部104、量子化部105、逆量子化部109、逆直交変換部110は、直交変換部・逆直交変換部/量子化・逆量子化部510に対応している。フィルタ演算部511で処理されたデータは、DMA書き込部512で、フレームメモリ113(図示せず)に書き込まれる。図4に示した動きベクトル探索の各ステップを実行するプログラムを記憶した記録媒体が備えられ、そのプログラムを実行することによって、図5の動きベクトル探索部(点線で囲む部分)が実現される。

## &lt;実施例3&gt;

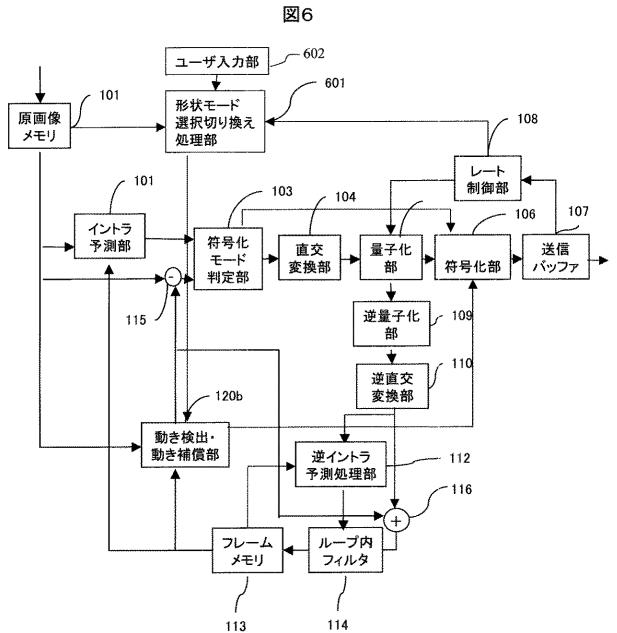

図6は本発明による動き補償画像符号化装置の他の実施例の構成を示すブロック図を示す。本実施例は、小数画素精度の動きベクトル探索を行う前に形状モードの選択を行うか行わないかの選択を行うようにしたものである。一般的に、画素精度を上げれば、動き補償予測による残差成分が小さくなり、その結果発生符号量が削減されるため、予測効率が高くなる。一方、画素精度を上げれば、それに伴うフィルタ処理が多くなり演算負荷も高くなる。

10

## 【0024】

図1に示した実施例1で説明した動き補償画像符号化装置と実質的に同じ機能ブロックについては、図1に示した番号と同じ番号を付して、その詳細な説明を省く。図1に示した実施例1と本実施例の動き補償画像符号化装置との違いは、図1に示した実施例1の構成に形状モード選択切り換え処理部601が追加された点である。形状モード選択切り換え処理部601は、入力画像やフレームレート、発生符号量などに基づいて、適応的に小数画素精度の動きベクトル探索前に形状モード選択処理を行うか行わないかを決定する。例えば、図6に示すレート制御部108では、対象マクロブロックの符号量を取得し、その発生符号量が多ければ、次に処理するマクロブロックの符号量を減らすために量子化パラメータ値を大きくするように制御が行われている。そのため、量子化誤差が大きくなり、画質が低下するので、整数画素精度、小数画素精度の動きベクトル探索が終了後に形状モードを選択して予測精度を上げる。

20

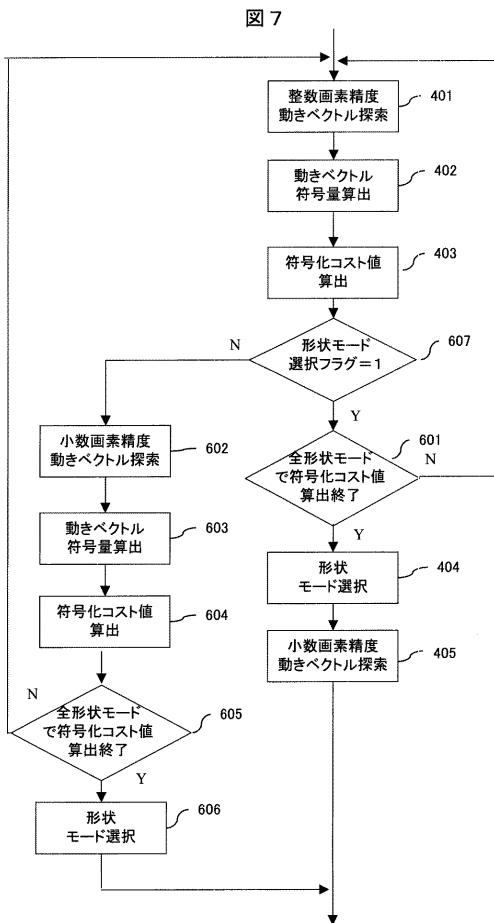

## 【0025】

次に動き検出・動き補償部120bの機能構成及び処理の流れについて説明する。図7は、図6の実施例における動き検出・動き補償部120bの機能構成、処理の流れを示すフローチャート図である。同図において、整数画素精度の動きベクトル探索401、動きベクトル符号量算出402、符号化コスト値の算出403処理は、実施例1と同じであるが、形状モード選択処理は以下のように行う。

30

## 【0026】

形状モード選択切り換え処理部601では、小数画素精度の動きベクトル探索前に形状モード選択を行うか行わないかを決定するフラグ(以下形状モード選択フラグと呼ぶ)が用意されており、形状モード選択フラグの値が“0”的時は、動き検出・動き補償部120bは形状モード選択の処理404、処理404の結果に基づく小数画素精度の動きベクトル探索405を行わずに、全てのブロック(マクロブロック及びサブブロック)に対して小数画素精度の動きベクトル探索行う(ステップ602)。そして、動きベクトルの符号量を算出する(ステップ603)。小数画素精度の動きベクトル探索(ステップ602)で得られた誤差量やステップ603で得られた動きベクトル情報の符号量を用いて符号化コスト値の算出を行う(ステップ604)。符号化コスト値はSADを用いても良いし、SSDやその他の評価関数を用いても良い。そして、全ての形状モードで符号化コスト値の算出が終了したら符号化コスト値が最も小さくなるモードを選択する(ステップ606)。

40

## 【0027】

一方、形状モードフラグの値が“1”的時は、動き検出・動き補償部120bは、小数画素精度の動きベクトル探索(ステップ405)前に形状モード選択処理を行う(ステップ404)。そして、選択された形状モードに対してのみ、小数画素精度の動きベクトル探索を行い(ステップ405)、動き検出・動き補償予測処理を終了する。なお、形状モード選択フラグの“1”、“0”的関係は、これに固定化されるものではなく、ON、OFFなど2値判別でき

50

るものであれば何でも良い。また、逆の関連付けを行ってもよい。

#### 【0028】

形状モード選択フラグの切り換え単位は、例えばマクロブロック、スライス、フレーム、シーケンス単位がある。また、小数画素精度の動きベクトル探索前に形状モード選択処理を行うか行わないかの判定をユーザが任意に行っても良い。その際、装置の構成としては図6に示す入力のようにユーザ入力部602を追加する。ユーザ入力部では、ユーザから入力された小数画素精度の動きベクトル探索前に形状モード選択処理を行うか行わないかの命令を受け取り、形状モード選択フラグを立てるか、立てないかの信号を形状モード選択切り換え部601へ送る。

#### 【0029】

本実施例の構成により、例えばHD(High Definition)等の大きな画像を符号化処理する場合、整数画素精度の動きベクトル探索後に形状モードを選択し、選択された形状モードに対してのみ小数画素精度の動きベクトル探索を行うことで、処理時間を短縮することができる。逆に、QCIF(Quarter Common Intermediate Format)等の小さい画像を符号化する場合、処理演算量が少ないため、すべての形状モードに対して整数画素精度、小数画素精度の動きベクトル探索を行ってから形状モードを選択することで、予測効率の高さを優先して処理することができる。同様に符号化処理装置の性能が高い、すなわち短時間で多くのブロックを処理できる符号化装置においては、すべての形状モードに対して整数画素精度、小数画素精度の動きベクトル探索を行ってから形状モードを選択することで予測効率の高さを優先して処理を行うことができる。

以上のように、本実施例では、入力画像サイズや符号化装置の性能によって、予測効率と演算負荷とのトレードオフを制御することで自由度の高い映像符号化を行うことができる。

#### <実施例4>

図8は本発明による動画像情報符号化装置の更に他の実施例の構成を示すブロック図である。本実施例は、小数画素精度の動きベクトル探索前に選択される選択される形状モードの数を決定する構成とした。すなわち、整数画素精度の動きベクトル探索終了後に複数の形状モードを選択するようにした動き補償動画像情報符号化装置である。前記実施例で説明した動画像情報符号化装置との違いは、形状モード数決定部801が追加された点である。図1に示した実施例1で説明した動画像符号化装置と実質的の同じ機能ブロックについては、図1に示した番号と同じ番号を付して、その詳細な説明を省く。具体的には、入力画像サイズに応じてn段階にわけ(ここでnはブロック形状モード数)、HDのような大きい画像においては、1モード、SDTV画像においては、2モードというように、画像サイズが大きいものから小さいものに対して選択する形状モード数を増やしていく。

#### 【0030】

また、符号化時のフレームレートに応じて、閾値をn個用意( $Th_1 > Th_2 > Th_3 > \dots > Th_n$ とする)し、フレームレートがある閾値以内(例えば $Th_1 < 閾値 < Th_2$ )ならば、モード数は2というように決定する。ここで、閾値 $Th$ は値が大きいほど選択するブロック形状モード数は少なくなるように設定する。以上、入力画像とフレームレートにおいて例を示したが、この他、符号化装置の性能に応じても同様に決定することができる。つまり、演算処理量に余裕のあるときには、ブロック形状モード数を増やし、逆に、演算処理量に余裕のないときには、ブロック形状モード数を少なくするように決定すればよい。

#### 【0031】

形状モード数決定部801は、小数画素精度の動きベクトル探索前に選択される形状モードの数を決定する。選択する形状モードの数は、ユーザが任意に決定しても良いし、入力画像やフレームレート、発生符号量に応じて適応的に決定されるようにしても良い。形状モード数決定部801では、選択する形状モードの数を決定するフラグ(以下形状モード数決定フラグと呼ぶ)が用意されており、複数の形状モードの中から、形状モード数決定フラグの値だけ小数画素精度の動きベクトル探索が行われる。

形状モード数決定部801及び動き検出・動き補償部120cの構成及び処理の流れについて説

10

20

30

40

50

明する。

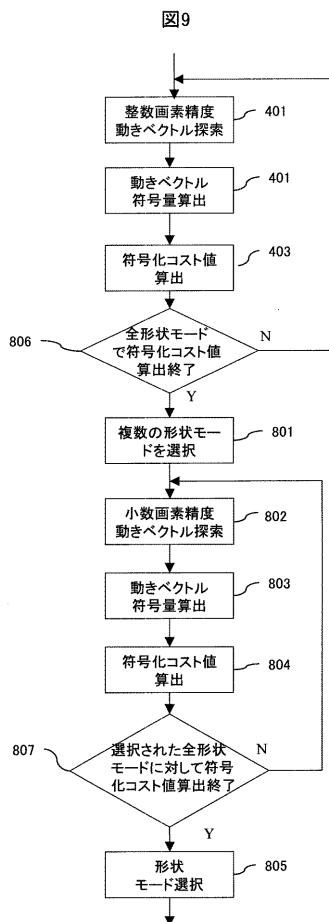

### 【0032】

図9は、動き検出・動き補償部120cの機能構造及び処理の流れを示す。前記実施例と同様に、整数画素精度の動きベクトル探索(ステップ401)、動きベクトルの符号量算出(ステップ402)、符号化コスト値の算出(ステップ403)を行う。符号化コスト値の算出(ステップ403)後、ステップ403で得られた符号化コスト値の算出の情報に基づいて、複数の形状モードを選択する(ステップ803)。例えば、形状モード数決定フラグが3であれば、符号化コスト値の小さい上位3つのブロック形状に対して、小数画素精度の動きベクトル探索を行う。なお、符号化コスト値はSADを用いても良いし、SSDやその他の評価関数を用いても良い。なお、形状モード数決定フラグの値3は、これに固定化されるものではなく、ブロック種別の識別が判別できるものであれば何でも良い。

10

### 【0033】

動き検出・動き補償部120は、選択された複数の形状モードそれぞれについて、小数画素精度の動きベクトル探索(ステップ802)で得られた動きベクトルの符号量を算出する(ステップ803)。そして、小数画素精度の動きベクトル探索で得られた誤差量や動きベクトルに基づいて算出された符号量を用いて符号化コスト値の算出を行う(ステップ804)。符号化コスト値はSADでも良いしSSDやその他の評価関数でも良い。選択された全ての複数の形状モードにたいして符号化コスト値の算出が終了すると(ステップ807)、選択された複数の形状モードの中で符号化コスト値が最も小さいモードを最終的に選択する(ステップ805)。

20

上記形状モード数決定フラグの値は、例えばマクロブロック、スライス、フレーム、シーケンス単位で変更することができる。

入力画像サイズがHDのような非常に大きい場合でも、符号化処理装置の性能が非常に高い場合には、すべての形状モードに対して小数画素精度の動きベクトル探索はできなくても複数の形状モードに対してはできる場合がある。しかし、実施例3では、整数画素精度の動きベクトル探索終了後に選択する形状モード数は1モードのみであったため、予測効率と演算負荷とのトレードオフを細かく制御することはできなかった。

一方、本実施例によれば、上記のような条件で符号化処理を行う場合においても、複数の形状モードに対して小数画素精度の動きベクトル探索を行うことが可能なため、予測効率と演算負荷とのトレードオフを細かく制御することができる。つまり、実施例3よりもさらに自由度の高い映像符号化を行うことが可能といえる。

30

### 【0034】

上記実施例では、常に画像入力の単位をフレームとして説明してきたが、インタース画像入力を想定する画像入力をフィールドとする場合においても、適用される。また、動き検出・動き補償部120において、フレームメモリから参照される予測画像が時間的に前後のフレームから作られる場合においても適用できる。

尚、本願は、MPEG符号化方法以外であっても、複数種類の形状モードが想定されている動き補償を用いた符号化方法に適応することができ、処理量低減の効果を奏する。

40

### 【図面の簡単な説明】

#### 【0035】

【図1】本発明による動き補償画像符号化装置の一実施例の構成を示すブロック図である。

【図2】マクロブロック及びサブブロックを示す図である。

【図3】整数画素位置及び、小数画素位置を示した図である。

【図4】実施例1の符号化処理における動き補償予測処理ステップを示したフロー図である。

【図5】本発明による動き補償画像符号化装置をCPUなどの信号処理装置を用いて構成した実施例の構成を示すブロック図である。

【図6】本発明による動き補償画像符号化装置の他の実施例の構成を示すブロック図である。

50

【図7】図6の実施例における動き検出・動き補償部120の機能、処理の流れを示すフロー図である。

【図8】本発明による動き補償画像符号化装置の更に他の実施例の構成を示すブロック図である。

【図9】図8の動き検出・動き補償部120の処理の流れを示すフロー図である。

【図10】マクロブロックと動きベクトル検索の画素精度説明のための画素分布図である。

【符号の説明】

【0036】

101...原画像メモリ； 102...イントラ予測部； 103...符号化モード判定部； 10

104...直交変換部； 105...量子化部； 106...符号化部； 107...送信バッファ；

108...レート部制御； 109...逆量子化部； 110...逆直交変換部；

120...動き検出・動き補償部； 112...逆イントラ予測処理部； 113...フレームメモリ；

114...ループ内フィルタ； 115...減算器； 116...加算器；

601...形状モード選択切り換え処理部； 801...形状モード数決定部；

201...16×16モード； 202...16×8モード； 203...8×16モード；

204...8×8モード； 205...8×4モード； 206...4×8モード； 207... 20

4×4モード；

301, 309...1/2画素； 302...1/4画素； 303, 304, 305, 30

6, 307, 308...整数画素；

501...CPU； 502...制御部； 503...動き探索メモリ； 509...DMA読出部；

511...フィルタ演算部； 512...DMA書込部。

【図1】

【図2】

【図3】

図3

【図4】

図4

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 望月 誠二

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5C059 MA01 NN02 NN14 RC16 RC40 TA12 TB08 TC03 TD11 UA02