(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3934538号

(P3934538)

(45) 発行日 平成19年6月20日(2007.6.20)

(24) 登録日 平成19年3月30日(2007.3.30)

(51) Int.C1.

F 1

|                    |                  |             |      |

|--------------------|------------------|-------------|------|

| <b>HO1L 29/786</b> | <b>(2006.01)</b> | HO1L 29/78  | 612B |

| <b>HO1L 21/336</b> | <b>(2006.01)</b> | HO1L 29/78  | 627G |

| <b>HO1L 21/20</b>  | <b>(2006.01)</b> | HO1L 21/20  |      |

| <b>HO1L 21/268</b> | <b>(2006.01)</b> | HO1L 21/268 | J    |

| <b>GO2F 1/1368</b> | <b>(2006.01)</b> | GO2F 1/1368 |      |

請求項の数 11 (全 42 頁) 最終頁に続く

(21) 出願番号 特願2002-350939 (P2002-350939)

(22) 出願日 平成14年12月3日 (2002.12.3)

(62) 分割の表示 特願2002-349963 (P2002-349963)

の分割

原出願日 平成14年12月2日 (2002.12.2)

(65) 公開番号 特開2003-229434 (P2003-229434A)

(43) 公開日 平成15年8月15日 (2003.8.15)

審査請求日 平成17年11月24日 (2005.11.24)

(31) 優先権主張番号 特願2001-367994 (P2001-367994)

(32) 優先日 平成13年11月30日 (2001.11.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 加藤 清

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 尾崎 匠史

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 牟田口 浩平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 河本 充雄

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に絶縁膜を形成し、

前記絶縁膜上に第1の領域と第2の領域と第3の領域を有する半導体膜を形成し、

前記第1の領域に連続発振レーザーを照射して熔融帯を形成し、前記熔融帯を連続的に走査することによって、前記第1の領域を結晶化し、

前記第2の領域及び前記第3の領域にパルス発振レーザーを照射して前記第2の領域及び前記第3の領域を結晶化し、

前記結晶化された前記第1の領域を用いて、チャネル方向が前記熔融帯の走査方向と平行となるように第1のトランジスタの活性層を形成することによって、前記第1のトランジスタを有する信号線駆動回路を形成し、 10

前記結晶化された前記第2の領域を用いて、第2のトランジスタの活性層を形成することによって、前記第2のトランジスタを有する走査線駆動回路を形成し、

前記結晶化された前記第3の領域を用いて、第3のトランジスタの活性層を形成することによって、前記第3のトランジスタを有する画素回路を形成することを特徴とする半導体装置の作製方法。

## 【請求項2】

請求項1において、前記第1の領域は前記基板の面積の50%以下であることを特徴とする半導体装置の作製方法。

## 【請求項3】

請求項 1 又は請求項 2 において、前記パルス発振レーザーは、エキシマレーザー、YAG レーザー、YVO<sub>4</sub> レーザー、YLF レーザー、YAlO<sub>3</sub> レーザー、ガラスレーザー、ルビーレーザー、又は、Ti : サファイアレーザーであることを特徴とする半導体装置の作製方法。

**【請求項 4】**

請求項 1 乃至請求項 3 のいずれか一において、前記連続発振レーザーは、YVO<sub>4</sub> レーザー、YLF レーザー、又は YAG レーザーであることを特徴とする半導体装置の作製方法。

**【請求項 5】**

請求項 1 乃至請求項 4 のいずれか一において、前記結晶化された前記第 1 の領域を用いて、回路ブロックを形成することを特徴とする半導体装置の作製方法。 10

**【請求項 6】**

請求項 5 において、前記回路ブロックは、トランジスタ、容量素子、抵抗素子によって構成されることを特徴とする半導体装置の作製方法。

**【請求項 7】**

請求項 5 において、前記回路ブロックは、レジスタ、デコーダ、カウンタ、分周回路、メモリ、CPU、又は DSP であることを特徴とする半導体装置の作製方法。

**【請求項 8】**

請求項 7 において、前記メモリは SRAM、DRAM、マスク ROM、又は EEPROM であることを特徴とする半導体装置の作製方法。 20

**【請求項 9】**

請求項 1 乃至請求項 8 のいずれか一において、前記結晶化された前記第 1 の領域を用いて、制御回路を形成することを特徴とする半導体装置の作製方法。

**【請求項 10】**

請求項 9 において、前記制御回路はインターフェース回路、タイミング生成回路、フォーマット変換部、又は、画像処理回路であることを特徴とする半導体装置の作製方法。

**【請求項 11】**

請求項 1 乃至請求項 10 のいずれか一において、前記基板は、石英基板、シリコン基板、金属基板、ステンレス基板、プラスチック基板、又はガラス基板であることを特徴とする半導体装置の作製方法。 30

**【発明の詳細な説明】**

**【0001】**

**【発明が属する技術分野】**

本発明は、表示部を有する半導体装置に関する。特に、薄膜トランジスタを絶縁表面を有する基板上に形成してなる半導体装置に関する。

**【0002】**

**【従来の技術】**

近年の半導体装置、特に半導体表示部を有する電子機器の発展はめざましく、その応用例は、ゲーム機、ノートパソコン、携帯電話を始めとする携帯機器、液晶テレビ、液晶ディスプレイ、ELディスプレイ等、様々である。半導体表示部は、従来の CRT と比較して軽量薄型化が可能であり、消費電力が小さいことを特徴とする。 40

**【0003】**

従来の半導体表示部としては、液晶層または発光層を挟んで上下に、ストライプ状の電極を互いに交差するように形成した画素領域を有するパッシブマトリクス型の半導体表示部と、薄膜トランジスタ ( TFT ) をマトリクス状に配置した画素領域を有するアクティブマトリクス型の半導体表示部と、が知られている。

**【0004】**

近年、基板上に TFT を形成する技術が進歩し、アクティブマトリクス型半導体表示部の応用開発が進められている。特に、ポリシリコン膜を用いた TFT は、従来のアモルファスシリコン膜を用いた TFT よりも電界効果移動度 ( モビリティともいう ) が高く、従来

、基板外の駆動回路で行っていた画素の制御を、画素と同一の基板上に形成した駆動回路で行うことが可能となっている。

#### 【0005】

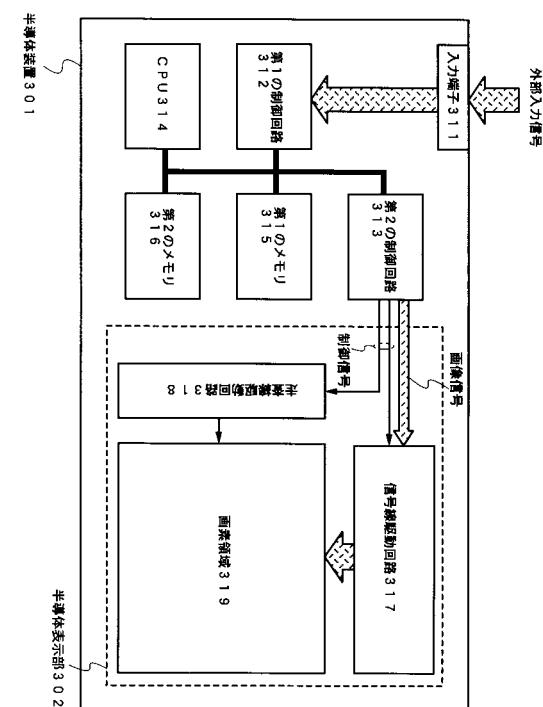

次に、従来の半導体表示部を有する電子機器の構成について説明する。図21は、画像の表示に関する部分のブロック図を簡略に表したものである。

#### 【0006】

図21において、半導体装置301は、画像データを取り込み、または作成して、画像データの加工とフォーマット変換を行い、画像を表示する装置である。半導体装置301としては、例えば、ゲーム機、ビデオカメラ、カーナビゲーション、パーソナルコンピュータ等を考えることができる。

10

#### 【0007】

半導体装置301において、画素領域319、走査線駆動回路318および信号線駆動回路317によって構成される半導体表示部302は、絶縁表面を有する基板上に一体形成されているが、他の回路ブロックはそれぞれ異なるシリコン基板上に形成され、ICチップとして実装されている。回路ブロックの幾つかは同一のシリコン基板上に形成される場合もある。

#### 【0008】

半導体装置301は、入力端子311、第1の制御回路312、第2の制御回路313、CPU314、第1のメモリ315、第2のメモリ316、及び半導体表示部302によって構成される。入力端子311からは、それぞれの電子機器に応じて、画像データの基となるデータが入力される。例えば、放送受信機ではアンテナからの入力データであり、ビデオカメラではCCDからの入力データである。DVテープやメモリーカードからの入力データであってもよい。入力端子311から入力されたデータは、第1の制御回路312によって画像信号に変換される。第1の制御回路312では、MPEG規格やテープフォーマット等に従って圧縮符号化された画像データの復号処理、画像の補間やりサイズといった画像信号処理が行われる。第1の制御回路312から出力された画像信号や、CPU314が作成または加工した画像信号は、第2の制御回路313に入力され、半導体表示部302に適したフォーマット（例えば走査フォーマット等）に変換される。第2の制御回路313からは、フォーマット変換された画像信号と制御信号が出力される。

20

#### 【0009】

CPU314は、第1の制御回路312、第2の制御回路313および他のインターフェース回路における信号処理を効率良く制御する。また、画像データを作成したり、加工したりする。第1のメモリ315は、第1の制御回路312から出力される画像データや第2の制御回路313から出力される画像データを格納するメモリ領域、CPUによる制御を行う際のワークメモリ領域、CPUによって画像データを作成する際のワークメモリ領域、等として用いられる。第1のメモリ315としては、DRAMやSRAMが用いられる。第2のメモリ316は、CPU314によって画像データを作成または加工する場合に必要となる、色データや文字データを格納するメモリ領域であり、マスクROMやEPROMによって構成される。

30

#### 【0010】

半導体表示部302は、信号線駆動回路317、走査線駆動回路318、画素領域319によって構成される。信号線駆動回路317は第2の制御回路313から画像信号と制御信号（クロック信号、スタートパルス等）を、走査線駆動回路318は第2の制御回路313から制御信号（クロック信号、スタートパルス等）をそれぞれ受け取り、画素領域319において画像を表示する。

40

#### 【0011】

なお、半導体表示部を有する電子機器としては、図21に示した構成以外にも様々な構成をとり得る。最も簡単な構成としては、半導体表示部と入出力端子と簡単な制御回路による構成が考えられ、例えば液晶ディスプレイ、ELディスプレイを考えることができる。また、高性能ゲーム機のように、図21に示したアーキテクチャではCPUの負担が大き

50

すぎる場合には、新たに画像処理用のプロセッサを設けて C P U の負荷を軽減した構成をとる場合もある。

#### 【0012】

##### 【発明が解決しようとする課題】

上述した従来の半導体表示部を有する電子機器では、駆動回路以外の回路ブロックは画素を形成する基板とは別の基板に形成され、実装されている。

#### 【0013】

携帯型の電子機器の普及を背景に、電子機器の小型化が重要な課題となっているが、このような構成の半導体装置は、画素を形成する基板とは別に I C チップを多数実装することが必要となるため、小型化を実現することが難しい。特に、I C チップ内の回路ブロックを小さくできたとしても、実装するためのマージンが大きいため、装置全体の小型化が困難となっている。一方、装置の小型化を実現するために実装のマージンを減らそうとすると、高度な実装技術が必要となり、コスト面や実装部分での信頼性において問題が生じてくる。

10

また、配線容量の問題もある。つまり、I C チップによる実装を行う場合は、配線の負荷が大きくなるため、高速動作を行うことが難しいという問題がある。

#### 【0014】

このような問題点を解決する方法の一つとして、回路ブロックを半導体表示部と一体形成することが期待されている。

#### 【0015】

しかしながら、絶縁表面を有する基板上に回路ブロックを形成する場合には、しばしば動作速度が問題となる。これは、ガラス基板等の絶縁表面を有する基板上に形成される T F T は、単結晶シリコン基板上に形成されるトランジスタと比較して、移動度やしきい値の特性が劣るためである。

20

#### 【0016】

その結果、従来の半導体装置をある周波数で動作させる場合に、回路ブロックを I C チップによって実装した半導体装置では動作するが、回路ブロックを絶縁表面を有する基板上に作製した半導体装置では動作しないといったことが起こり得る。

#### 【0017】

本発明はこのような問題点を鑑みてなされたものである。本発明は、小型化が可能であり、I C チップ等の基板の実装に伴う不良を低減し、かつ高速動作を実現する半導体表示部を有する電子機器を提供することを課題とする。

30

#### 【0018】

##### 【課題を解決するための手段】

本発明では上記課題を解決するために、絶縁表面を有する基板上に半導体表示部および他の回路ブロックを一体形成する。

#### 【0019】

さらに、絶縁表面を有する基板上に回路ブロックを形成した場合の、動作速度の問題を低減するために、高移動度を実現する T F T 作製プロセスを用いる。

#### 【0020】

高移動度を実現する T F T 作製プロセスとしては、半導体膜にエネルギービームを照射して熔融帯を形成し、その熔融帯をチャネル方向に連続的に走査して結晶化を行う、活性層の形成プロセスを用いる。詳細は実施例に説明するが、具体的には連続発振レーザを用いてこれを行う。

40

#### 【0021】

そのように作製した T F T で構成した回路ブロックは、従来のポリシリコンを T F T の活性層として用いた回路ブロックと比較して、個々の T F T の移動度が高いため、動作周波数が大幅に向かう。

#### 【0022】

その結果、絶縁表面を有する基板上に表示部と他の回路ブロックを一体形成して、かつ高

50

速動作を実現することが可能となる。つまり、従来は動作速度の問題によって絶縁表面を有する基板上に形成しても実用化できなかった回路ブロックも、本発明によって実用化することが可能となる。

【0023】

さらに本発明では、そのような高い動作周波数を保ったまま、以下のようにしてスループットの向上を実現する。

【0024】

連続発振レーザには、YVO<sub>4</sub>レーザ、YLFレーザ、YAGレーザなどが知られているが、現状での出力は高いものでも10W程度と弱い。従って、活性層に連続発振レーザ光を照射することで結晶化を行うには、レーザ光の大幅な絞り込みが必要であり、そのビーム幅は50～500μm（典型的には200μm）程度である。10

【0025】

例えば、600mm×720mmのガラス基板全面に幅200μmのレーザ光を、スキャン速度50cm/secで走査した場合、一枚辺り72分の時間を要する。実際には、レーザ光の走査方向の転換や加速のため、さらに時間を要する。つまり、低スループットという問題に直面する。

【0026】

本発明では、連続発振レーザによる結晶化プロセスを、高速動作が必要な回路ブロックのみに選択的に行うことを行つて特徴とする。これによつて、連続発振レーザによる結晶化プロセスのスループットが大幅に向上する。20

【0027】

例えば、連続発振レーザ光を照射する領域を基板面積の50%以下（好ましくは30%以下）に抑える事によつて、連続発振レーザによる結晶化プロセスに要する時間をおよそ50%（好ましくは30%以下）に低減することができる。

【0028】

また、連続発振レーザ光または基板の移動距離を抑えるために、高速動作が必要な回路ブロックをなるべく近い領域に配置することが好ましい。そうすることによつて、連続発振レーザによる結晶化プロセスのスループットはさらに向上する。

【0029】

さらに、回路ブロックの動作周波数を向上するために、TFTのチャネル長方向をレーザ光の走査方向と一致させることが好ましい。これは、連続発振レーザによる半導体膜の結晶化プロセスでは、TFTのチャネル方向とレーザ光の基板に対する走査方向とが概ね並行（好ましくは-30°～30°）であるときに、最も高い移動度が得られるためである。このように作製したTFTは、結晶粒がチャネル方向に延在する多結晶半導体によって構成される活性層を有する。また、このことは結晶粒界が概ねチャネル方向に沿つて形成されていることを意味するため、活性層の電気特性はチャネル方向とこれに垂直な方向とで異なる。つまり、活性層はチャネル方向に電気異方性を有する。30

【0030】

なお、連続発振レーザによる結晶化プロセスを行わない回路ブロックまたは画素領域に含まれる半導体活性層は、公知の作製方法によつて作製すればよい。40

【0031】

特に、連続発振レーザによる結晶化プロセスよりもスループットの高い結晶化プロセスを適用することが好ましい。

【0032】

また特に、特開平7-183540号においてに開示されている半導体膜結晶化（金属触媒を用いた熱結晶化）の方法は好ましい。この場合、連続発振レーザによる半導体膜の結晶化を行う領域では、金属触媒を用いた熱結晶化と連続発振レーザによる結晶化との組み合わせプロセスが行なわれるが、実施例に示すように、そのようなプロセスは、連続発振レーザによる結晶化だけを行う場合と比較して、同等あるいはそれ以上の移動度を有するTFTが作製されている。50

## 【0033】

また、連続発振レーザによる結晶化プロセスを行わない領域の半導体活性層には、パルス発振レーザを用いたレーザ結晶化の方法を用いても良い。パルス発振レーザは高い出力を実現できるため、100mm以上の幅を有するビームを照射することが可能であり、スループットは高い。実施者は、動作周波数やコストの面から、これらを含む公知の活性層の作製方法を自由に組み合わせて実施すればよい。なお、このような公知の作製方法によって作製したTFTでは、連続発振レーザによる結晶化プロセスとは異なり、チャネル方向に電気的異方性を持たない、あるいは持ったとしても連続発振レーザによる結晶化プロセスよりも電気的異方性が弱い活性層を有する。

## 【0034】

10

このように本発明では、画素領域と回路ブロックを同一基板上に形成し、かつ、連続発振レーザによる結晶化プロセスを、高速動作が必要な回路ブロックのみに選択的に行うことによって、小型化、ICチップ等の基板の実装に伴う不良の低減、高い動作周波数、高スループットを実現した半導体装置を提供することが可能となる。また、配線容量の観点からも高動作速度を実現することが可能となる。

## 【0035】

20

なお、本発明でいう半導体装置とは、半導体特性を利用することで機能する装置全般を指し、例えば、液晶表示装置や発光装置に代表される半導体表示装置や、半導体表示部を有する電子機器をその範疇に含む。なお、半導体表示部とは、絶縁表面を有する基板上に電極あるいは薄膜トランジスタを形成してなる表示部を言い、例えば、液晶表示部や発光表示部、あるいは、パッシブマトリクス型表示部やアクティブマトリクス型表示部をその範疇に含む。なお、自明な場合には、半導体表示部を単に表示部とも表す。

## 【0036】

また、本発明でいう回路ブロックとは、トランジスタ、容量素子、抵抗素子等の回路素子によって構成された特性の機能を有する電気回路のブロックを指し、例えば、信号線駆動回路、走査線駆動回路、レジスタ、デコーダ、カウンタ、分周回路、メモリ、CPU、DSPをその範疇に含む。特に、本明細書では回路ブロックを絶縁表面を有する基板上に形成するため、薄膜トランジスタ（以下、TFTという）が回路ブロックの主な構成素子となる。なお、薄膜トランジスタ（TFT）とは、SOI技術を用いて形成されるトランジスタの全体を指す。

30

## 【0037】

以下に本願発明の構成を示す。

## 【0038】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は半導体膜にエネルギー ビームを照射して熔融帯を形成し、該熔融帯をチャネル長方向に連続的に走査して結晶化して形成されたものであって、前記第2活性層は半導体膜を加熱処理により結晶化して形成されたものであって、

前記画素領域は前記第2TFTで構成され、

40

前記走査線駆動回路は前記第2TFTで構成され、

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

## 【0039】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は半導体膜にエネルギー ビームを照射して熔融帯を形成し、該熔融帯をチャネル長方向に連続的に走査して結晶化して形成されたものであって、前記第2活性層は半導体膜に金属元素を添加して加熱処理により結晶化して形成されたものであって、

50

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第2 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

【0040】

前記エネルギー ビームは、連続発振レーザ光であってもよい。

【0041】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は半導体膜にエネルギー ビームを照射して熔融帯を形成し、該熔融帯をチャネル長方向に連続的に走査して結晶化して形成されたものであって、前記第2活性層は半導体膜にパルス状のエネルギー ビームを照射して結晶化して形成されたものであって、

10

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第2 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

【0042】

前記エネルギー ビームは、パルス発振レーザ光であってもよい。

【0043】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は、結晶粒はチャネル方向に延在する多結晶半導体によって形成され、

前記第2活性層は、結晶粒の形状がチャネル方向に異方性を持たない多結晶半導体によって形成され、

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第2 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

20

【0044】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は、結晶粒はチャネル方向に延在する多結晶半導体によって形成され、

前記第2活性層は、結晶粒のチャネル方向の形状異方性が前記第1活性層よりも弱い多結晶半導体によって形成され、

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第2 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

30

【0045】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は、チャネル方向に電気的異方性を有する多結晶半導体によって形成され、

前記第2活性層は、チャネル方向に電気的異方性を有さない多結晶半導体によって形成され、

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第2 TFTで構成され、

40

50

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

【0046】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は、チャネル方向に電気的異方性を有する多結晶半導体によって形成され、

前記第2活性層は、チャネル方向の電気的異方性が前記第1活性層よりも弱い多結晶半導体によって形成され、

前記画素領域は前記第2 TFTで構成され、

10

前記走査線駆動回路は前記第2 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

【0047】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は、結晶粒がチャネル方向に延在し、短径方向の粒径が $0.5 \sim 100 \mu\text{m}$ であり長径方向の粒径が $3 \sim 10000 \mu\text{m}$ である、多結晶半導体によって形成され、

前記第2活性層は、結晶粒の粒径が $0.01 \mu\text{m} \sim 10 \mu\text{m}$ である多結晶半導体によって形成され、

20

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第2 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

【0048】

前記走査線駆動回路の駆動周波数は、 $1 \text{ kHz} \sim 1 \text{ MHz}$ であり、

前記信号線駆動回路の駆動周波数は、 $100 \text{ kHz} \sim 100 \text{ MHz}$ であることが好ましい

。

【0049】

30

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は半導体膜にエネルギービームを照射して熔融帯を形成し、該熔融帯をチャネル長方向に連続的に走査して結晶化して形成されたものであって、前記第2活性層は半導体膜を加熱処理により結晶化して形成されたものであって、

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第1 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提供される。

40

【0050】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1 TFTと、第2活性層を有する第2 TFTと、を有し、前記第1活性層は半導体膜にエネルギービームを照射して熔融帯を形成し、該熔融帯をチャネル長方向に連続的に走査して結晶化して形成されたものであって、前記第2活性層は半導体膜に金属元素を添加して加熱処理により結晶化して形成されたものであって、

前記画素領域は前記第2 TFTで構成され、

前記走査線駆動回路は前記第1 TFTで構成され、

前記信号線駆動回路は前記第1 TFTで構成されていることを特徴とする半導体装置が提

50

供される。

【0051】

前記エネルギー ビームは、連続発振レーザ光であってもよい。

【0052】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は半導体膜にエネルギー ビームを照射して熔融帯を形成し、該熔融帯をチャネル長方向に連続的に走査して結晶化して形成されたものであって、前記第2活性層は半導体膜にパルス状のエネルギー ビームを照射して結晶化して形成されたものであって、

10

前記画素領域は前記第2TFTで構成され、

前記走査線駆動回路は前記第1TFTで構成され、

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

【0053】

前記エネルギー ビームは、パルス発振レーザ光であってもよい。

【0054】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は、結晶粒はチャネル方向に延在する多結晶半導体によって形成され、

20

前記第2活性層は、結晶粒の形状がチャネル方向に異方性を持たない多結晶半導体によって形成され、

前記画素領域は前記第2TFTで構成され、

前記走査線駆動回路は前記第1TFTで構成され、

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

【0055】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は、結晶粒はチャネル方向に延在する多結晶半導体によって形成され、

30

前記第2活性層は、結晶粒のチャネル方向の形状異方性が前記第1活性層よりも弱い多結晶半導体によって形成され、

前記画素領域は前記第2TFTで構成され、

前記走査線駆動回路は前記第1TFTで構成され、

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

【0056】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は、チャネル方向に電気的異方性を有する多結晶半導体によって形成され、

40

前記第2活性層は、チャネル方向に電気的異方性を有さない多結晶半導体によって形成され、

前記画素領域は前記第2TFTで構成され、

前記走査線駆動回路は前記第1TFTで構成され、

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

【0057】

50

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は、チャネル方向に電気的異方性を有する多結晶半導体によって形成され、

前記第2活性層は、チャネル方向の電気的異方性が前記第1活性層よりも弱い多結晶半導体によって形成され、

前記画素領域は前記第2TFTで構成され、

前記走査線駆動回路は前記第1TFTで構成され、

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

10

#### 【0058】

本発明によって、

画素領域と、走査線駆動回路と、信号線駆動回路とが同一の基板上に設けられ、第1活性層を有する第1TFTと、第2活性層を有する第2TFTと、を有し、前記第1活性層は、結晶粒がチャネル方向に延在し、短径方向の粒径が $0.5 \sim 100\text{ }\mu\text{m}$ であり長径方向の粒径が $3 \sim 10000\text{ }\mu\text{m}$ である多結晶半導体によって形成され、

前記第2活性層は、結晶粒の粒径が $0.01\text{ }\mu\text{m} \sim 10\text{ }\mu\text{m}$ である多結晶半導体によって形成され、

前記画素領域は前記第2TFTで構成され、

前記走査線駆動回路は前記第1TFTで構成され、

20

前記信号線駆動回路は前記第1TFTで構成されていることを特徴とする半導体装置が提供される。

#### 【0059】

前記走査線駆動回路の駆動周波数は、 $10\text{ kHz} \sim 1\text{ MHz}$ であり、

前記信号線駆動回路の駆動周波数は、 $100\text{ kHz} \sim 100\text{ MHz}$ であることが好ましい。

。

#### 【0060】

前記半導体装置には、メモリが、前記画素領域と同一の基板上に設けられ、

前記メモリは前記第1TFTで構成されていてもよい。

#### 【0061】

前記メモリはSRAMであり、該SRAMの読み出しサイクル時間は $200\text{ nsec}$ 以下であってもよい。

30

#### 【0062】

前記メモリはDRAMであり、該DRAMの読み出しサイクル時間は $1\text{ usec}$ 以下であってもよい。

#### 【0063】

前記半導体装置には、CPUが、前記画素領域と同一の基板上に設けられ、

前記CPUは前記第1TFTで構成されていてもよい。

#### 【0064】

前記CPUの動作周波数は $5\text{ MHz}$ 以上であることが好ましい。

40

#### 【0065】

前記半導体装置には、画像処理回路が、前記画素領域と同一の基板上に設けられ、

前記画像処理回路は前記第1TFTで構成されていてもよい。

#### 【0066】

前記画像処理回路の動作周波数は $5\text{ MHz}$ 以上であることが好ましい。

#### 【0067】

前記半導体装置には、DSPが、前記画素領域と同一の基板上に設けられ、

前記DSPは前記第1TFTで構成されていてもよい。

#### 【0068】

前記画像処理回路の動作周波数は $5\text{ MHz}$ 以上であることが好ましい。

50

**【0069】**

前記半導体装置には、タイミング発生回路が、前記画素領域と同一の基板上に設けられ、前記タイミング発生回路は前記第1 TFTで構成されていてもよい。

**【0070】**

前記絶縁表面を有する基板とは、プラスチック基板、ガラス基板あるいは石英基板のうちのいずれか一つであってもよい。

**【0071】**

前記第1 TFTによって構成される回路の面積は、前記基板の面積の50%以下であることが好ましい。

**【0072】**

前記第1 TFTによって構成される回路は、1~10個の長方形領域内に構成され、前記長方形領域全体の面積は、前記基板の面積の50%以下であることが好ましい。

10

**【0073】**

前記半導体装置は液晶表示装置であってもよい。

**【0074】**

前記半導体装置は発光装置であってもよい。

**【0075】**

前記半導体装置は、ゲーム機、ビデオカメラ、頭部取り付け型のディスプレイ、DVDプレーヤー、パソコン用コンピュータ、携帯電話、カーオーディオから選ばれた一つであってもよい。

20

**【0076】****【発明の実施の形態】****(実施の形態1)**

本発明の表示部を有する半導体装置の代表的な形態として、アクティブマトリクス型の半導体表示装置を例にとって説明する。

**【0077】**

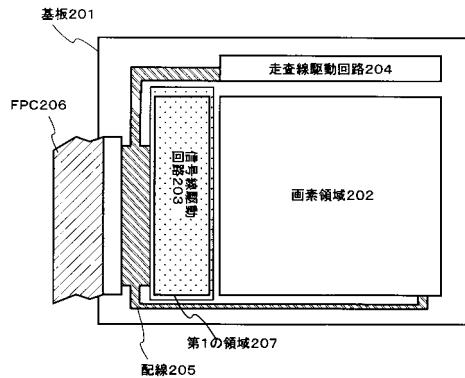

図2に示すのは、本発明のアクティブマトリクス型半導体表示装置を上から見たときの構成図である。図2において、アクティブマトリクス型半導体表示装置は、基板201上に形成された画素領域202、走査線駆動回路204、信号線駆動回路203、配線205、およびFPC206によって構成されている。

30

**【0078】**

アクティブマトリクス型半導体表示装置の動作を簡単に説明する。

**【0079】**

信号線駆動回路203は画像信号、クロック信号、スタートパルスを、走査線駆動回路204はクロック信号とスタートパルスを、外部よりFPC206を介してそれぞれ受け取り、画素領域202において画像を表示する。

**【0080】**

画素領域は、複数の信号線と複数の走査線が交差するように配置されており、信号線と走査線との各交点に、それぞれ画素TFTが配置されている。画素TFTのゲート電極には走査線が、ソース電極またはドレイン電極の一方には信号線が接続されており、ソース電極またはドレイン電極の残る一方に液晶素子が接続されている。

40

**【0081】**

各画素における表示動作について述べる。走査線が選択されると、選択された走査線に接続される画素TFTがオン状態となる。その間に画素TFTに接続された信号線にデータが入力されると、その信号線の電位が液晶素子に印加され、液晶素子は印加された電圧に応じて光の透過率を変化させる。こうして、各画素における輝度が決定し表示が行なわれる。

**【0082】**

一つの画像は、全ての走査線が順に選択されることによって形成される。また、各走査線が選択されている期間には、全ての信号線に順次、または一斉にデータが入力され、選択

50

された行に画像データが入力される。一つの画像が表示される期間を1フレームといい、毎秒60フレーム以上であることが好ましい。

#### 【0083】

上述した動作方法によると、画素数が決まれば、駆動回路に必要なおよその駆動周波数が決ることになる。例えば、カラーVGA規格では、画素数は $640 \times 480 \times RGB$ であるから、 $60\text{フレーム}/\text{秒} / 480\text{sec} = 35\mu\text{sec}$ となる。また、画像データの取り込みを1クロックあたりRGB×1画素分とすると、1クロックは $T_d = T_g / 640\text{sec} = 54\text{nsec}$ 程度としなければならない。なお、画素にデータを入力する時間は、線順次駆動では、一本の走査線を選択する期間( $T_g = 35\mu\text{sec}$ )程度となる。

10

#### 【0084】

実際の動作周波数は、画像データの分割数、フレーム周波数、帰線期間等に依存するが、画素および走査線駆動回路は、1~100kHzの周波数で動作し、信号線駆動回路は、0.1~100MHzの周波数で動作することが要求される。

#### 【0085】

なお、ここでは液晶表示装置の場合の説明を行った。EL層に代表される発光層を有する表示装置では、駆動方法は多少異なるが、一つの画像は、全ての走査線が順に選択されることによって形成されること、各走査線が選択されている期間には全ての信号線に順次、または一斉にデータが入力され、選択された行に画像データが入力されるという方式は共通である。従って、駆動周波数に関しても同様な考え方を適用することができる。

20

#### 【0086】

実施の形態1では、このような動作周波数の考察に基づいて、高速動作が必要となる信号線駆動回路203を含む領域に、高移動度TFT作製プロセスを適用した場合を示す。つまり、図2において、第1の領域207にのみ連続発振レーザを用いた半導体膜の結晶化の方法を適用する。なお、第1の領域を除く領域については、公知の活性層形成技術を用いれば良い。

#### 【0087】

図2において、第1の領域207は、基板201の30%以下(好ましくは10%以下)にすることが可能であり、連続発振レーザプロセスに要する時間は、基板全体に対して連続発振レーザプロセスを行なう場合と比較して、およそ30%以下(好ましくは10%以下)にすることが可能となる。

30

#### 【0088】

実施の形態1では、律速となる信号線駆動回路を含む第1の領域207に、高移動度TFT作製プロセスを用いることによって、装置全体の高速動作を達成したアクティブマトリクス型の半導体表示装置を実現している。また、連続発振レーザを用いた結晶化プロセスを用いているにもかかわらず、高スループットを実現している。

#### 【0089】

なお、実施の形態1では、信号線駆動回路を含む領域に高移動度のTFTを作製するプロセスを適用したが、もちろん、走査線駆動回路を含む領域に適用しても構わないし、画素を含む領域に適用しても構わない。特に、全てのTFTを含む領域に対して高移動度のTFTを作製するプロセスを適用する場合であっても、基板全体に対して適用する場合と比較してスループットは向上するため好ましい。

40

#### 【0090】

##### (実施の形態2)

本発明の表示部を有する半導体装置の代表的な形態として、表示部を有する半導体装置を例にとって説明する。

#### 【0091】

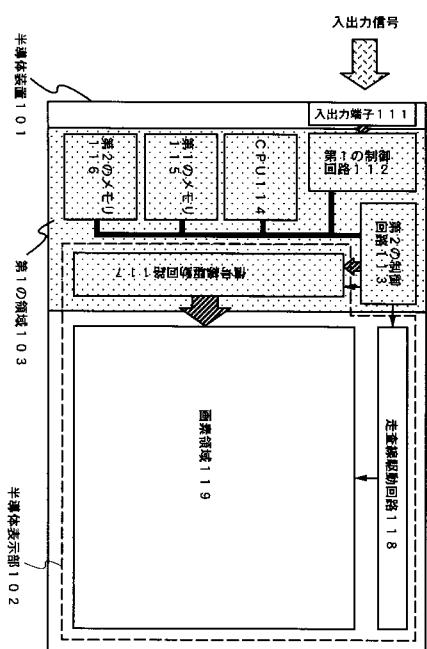

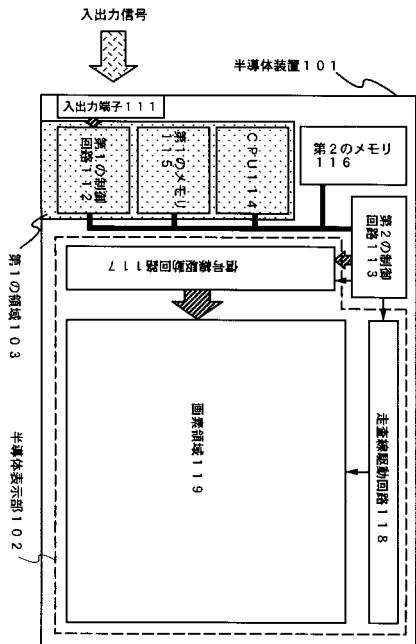

図1に示すのは、本発明の表示部を有する半導体装置を上から見たときの構成図である。図1において、表示部を有する半導体装置は、基板101上に形成された半導体表示部102、第1の制御回路112、第2の制御回路113、CPU114、第1のメモリ11

50

5、第2のメモリ116、入出力端子111によって構成されている。また、半導体表示部102は、画素領域119、信号線駆動回路117、走査線駆動回路118によって構成されている。

#### 【0092】

図1に示した半導体装置は、画像データを取り込み、または作成して、画像データの加工とフォーマット変換を行い、画像を表示する装置である。ロック構成は図21に示したロック図と同等であり、動作および機能に関しては図21で説明した通りであるので、ここでは説明を省略する。

#### 【0093】

各回路ロックの動作周波数については、個々の半導体装置に依存するため一概には言えないが、CPUの動作周波数に同期して他の回路ロックも動作するのが通常である。従って、CPU114およびバスにつながる各回路ロックの動作周波数を改善することが好ましい。

#### 【0094】

そのため、実施の形態2では、CPU114およびバスにつながる第1の制御回路112、第2の制御回路113、第1のメモリ115、第2のメモリ116と、信号線駆動回路117とに高移動度TFTの作製プロセスを適用する。つまり、図1において、第1の領域103にのみ連続発振レーザを用いた半導体活性層の結晶化の方法を適用する。なお、第1の領域を除く領域については、公知の活性層形成技術を用いれば良い。

#### 【0095】

図1において、第1の領域103は、基板の50%以下（好ましくは30%以下）にすることが可能であり、連続発振レーザプロセスに要する時間は、基板全体に対して連続発振レーザプロセスを行う場合と比較して、およそ50%以下（好ましくは30%以下）とすることが可能となる。

#### 【0096】

また、連続発振レーザを用いた半導体活性層の結晶化を適用する領域は、スループットの観点からは、なるべく局在していることが好ましい。図1に示した構成では、信号線駆動回路と走査線駆動回路の位置を入れ換えることが可能であるが、高速動作を必要とする信号線駆動回路を、CPU114およびバスにつながる第1の制御回路112、第2の制御回路113、第1のメモリ115、第2のメモリ116の近くに配置することによって、第1の領域を基板上に局在させている。

#### 【0097】

このように配置することによって、連続発振レーザ光の照射位置を基板の全面に移動させる必要がなく、同じ面積で基板上に散在する複数の領域に連続発振レーザを照射する場合と比較して、結晶化に要する時間を短縮することが可能となる。

#### 【0098】

このように、連続発振レーザ光の照射位置は、基板上に局在していることが好ましい。また、連続発振レーザ光あるいは基板の移動は単純であることが好ましく、連続発振レーザ光の照射領域は、長方形であることが好ましい。つまり、連続発振レーザ光の照射領域は、長方形で表される数個（好ましくは1～10個）の領域であることが好ましい。

#### 【0099】

実施の形態2では、高速動作が要求されるCPU114を含むシステムを含む第1の領域103に、高移動度TFT作製プロセスを用いることによって、装置全体の高速動作を達成した半導体装置を実現した。また、第1の領域の基板に占める割合を減らすことによって、連続発振レーザを用いた結晶化プロセスを用いているにもかかわらず、高スループットを実現した。

#### 【0100】

なお、実施の形態2では、CPU114、第1の制御回路112、第2の制御回路113、第1のメモリ115、第2のメモリ116および信号線駆動回路117を含む領域に高移動度のTFTを作製するプロセスを適用したが、回路ロックの構成によっては、同じ

10

20

30

40

50

周波数で動作する場合であっても、TFTに要求される特性が異なってくる。

【0101】

例えば、特にCPU114、第1の制御回路112、第1のメモリ115を構成するTFTに特に高特性が要求される場合には、それらを含む領域のみに高移動度のTFTを作製するプロセスを適用することも有効である。

【0102】

そのような場合においても、連続発振レーザによる活性層の結晶化時間が短縮されるよう、CPU114、第1の制御回路112、第1のメモリ115の配置方法を工夫することが好ましい。そのような例を、図22に示す。

【0103】

もちろん、第1の領域だけでなく、走査線駆動回路を含む領域、あるいは画素を含む領域に高移動度のTFTを作製するプロセスを適用しても構わない。特に、全てのTFTを含む領域に対して高移動度のTFTを作製するプロセスを適用する場合であっても、基板全体に対して適用する場合と比較してスループットは上昇するため好ましい。

【0104】

なお、本実施の形態では、CPUやメモリといった大まかな回路ブロックに分割をしているが、本発明はこれに限らない。回路ブロックとして、レジスタや分周回路といったより小さな回路構成を扱っても良い。そして、そのような小さなブロックに対して連続発振レーザを用いた結晶化プロセスの適用を選択しても良い。

【0105】

また、CPUやメモリといった大きな回路ブロックに対して、連続発振レーザを用いた結晶化プロセスを適用する場合には、必ずしもその全面に適用する必要はない。回路ブロック内で相対的に動作周波数の高い領域のみに選択的に適用することも可能である。

【0106】

以下に本発明の実施例を示す。

【0107】

【実施例】

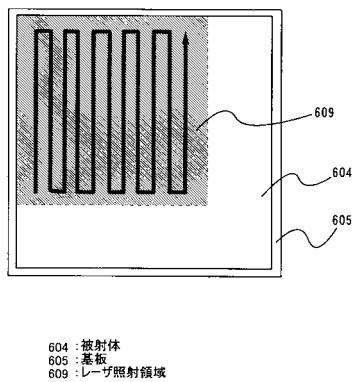

[実施例1]

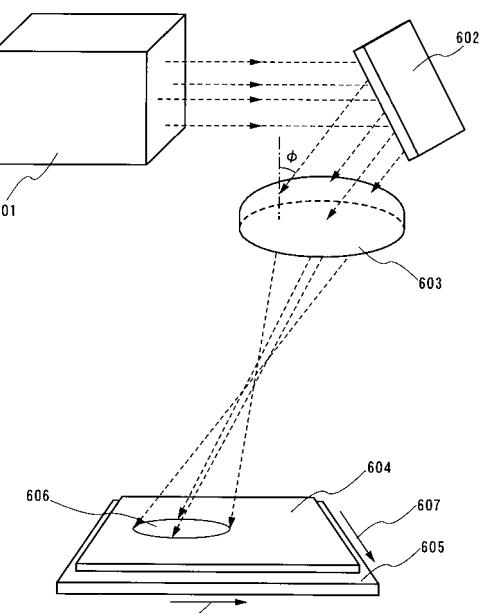

本実施例では、基板上の任意の領域にレーザ光の照射を行う方法について図6および図20を用いて説明する。

【0108】

図6には、線状ビームを形成し、基板に照射する装置の概略が示されている。

【0109】

レーザ601から射出されたレーザ光は、ミラー602を経由して、凸レンズ603に入射する。ここで、レーザ601は連続発振またはパルス発振の固体レーザまたは気体レーザまたは金属レーザのいずれでもよい。本実施例では、連続発振YAGレーザを用いる。レーザ601から発振されるレーザ光は非線形光学素子により高調波に変換してもよい。また、レーザ601とミラー602との間、またはミラー602と凸レンズ603との間にビームエキスパンダーを設置して長尺方向および短尺方向ともにそれぞれ所望の大きさに拡大してもよい。ビームエキスパンダーはレーザから射出されたレーザ光の形状が小さい場合に特に有効である。また、ミラーは設置しなくても良いし、複数設置してもよい。

【0110】

レーザ光は凸レンズ603に対して斜めに入射させる。このようにすることで、非点収差などの収差により焦点位置がずれ、照射面またはその近傍において線状ビーム606を形成することができる。なお、凸レンズ603は合成石英ガラス製とすれば、高い透過率が得られるので望ましい。また、凸レンズは球面収差を補正した非球面レンズとするのが望ましい。非球面レンズを用いれば、集光性がよくなり、アスペクト比の向上やエネルギー密度の分布が向上する。

【0111】

なお、ここでいう「線状」は、厳密な意味で「線」を意味しているのではなく、アスペク

10

20

30

40

50

ト比の大きい長方形もしくは長橢円形を意味する。例えば、アスペクト比が2以上（好ましくは10～10000）のもの指す。なお、線状とするのは被照射体に対して十分なアニールを行うためのエネルギー密度を確保するためである。なお、線状ビームとは厳密に線状である必要はない。

#### 【0112】

そして、このようにして形成される線状ビーム606を照射しながら、例えば607で示す方向または608で示す方向に被照射体604に対して相対的に移動することで、被照射体604において所望の領域または全面を照射することができる。

#### 【0113】

そして、このようにして形成される線状ビームを照射しながら、例えば607で示す方向または608で示す方向に被照射体604に対して相対的に移動することで、被照射体604において所望の領域に照射することができる。レーザを基盤に照射ときの様子を図20に示す。レーザ照射領域609上に描かれた矢印は、照射レーザの軌跡を表す。

#### 【0114】

なお、レーザを生成する光学系は他の公知のものでもよい。

#### [実施例2]

本実施例では、本発明の半導体装置において、高移動度TFTの作製プロセスに用いられる、連続発振レーザを用いた半導体膜の結晶化の方法について述べる。

#### 【0115】

ガラス基板上に下地膜として、プラズマCVD法により酸化窒化珪素膜（組成比Si = 32%、O = 59%、N = 7%、H = 2%）400nmを形成した。続いて、前記下地膜上に半導体膜として、プラズマCVD法により非晶質珪素膜150nmを形成した。そして、500で3時間の熱処理を行って、半導体膜が含有する水素を放出させた後、レーザアニール法により半導体膜の結晶化を行った。

#### 【0116】

レーザアニール法に用いるレーザとしては、連続発振のYVO<sub>4</sub>レーザを用いた。レーザアニール法の条件は、レーザ光としてYVO<sub>4</sub>レーザの第2高調波（波長532nm）を用いた。レーザ光を光学系により所定の形状のビームとして、基板表面上に形成した半導体膜を照射した。

#### 【0117】

また、レーザ光を基板表面上に形成した半導体膜に照射する際に用いる光学系としては、実施例1で説明した光学系（図6参照）を用いた。

#### 【0118】

本実施例では、凸レンズに対するレーザ光の入射角を約20°として200μm×50μmの橢円状ビームを形成し、ガラス基板105を50cm/sの速度で移動させながら照射して、半導体膜の結晶化を行った。

#### 【0119】

また、橢円状ビームの相対的な走査方向は、橢円状ビームの長軸に垂直な方向とした。

#### 【0120】

このようにして得られた結晶性半導体膜にセコエッチングを行って、SEMにより1万倍にて表面を観察した結果を図7に示す。なお、セコエッチングにおけるセコ液はHF:H<sub>2</sub>O = 2:1に添加剤としてK<sub>2</sub>Cr<sub>2</sub>O<sub>7</sub>を用いて作製されるものである。図7は、図中の矢印で示す方向にレーザ光を相対的に走査させて得られたものである。レーザ光の走査方向に平行に大粒径の結晶粒が形成されている様子がわかる。つまり、レーザ光の走査方向に対して延在するように結晶成長がなされる。

#### 【0121】

このように、本実施例の手法を用いて結晶化を行った半導体膜には大粒径の結晶粒が形成されている。そのため、前記半導体膜を半導体活性層として用いてTFTを作製すると、前記TFTのチャネル形成領域に含まれる結晶粒界の本数を少なくすることができる。また、個々の結晶粒の内部は実質的に単結晶と見なせる結晶性を有することから、単結晶半

10

20

30

40

50

導体を用いたトランジスタと同等の高いモビリティ（電界効果移動度）を得ることも可能である。

#### 【0122】

さらに、TFTを、そのキャリアの移動方向が、形成された結晶粒の延在する方向と揃うように配置すれば、キャリアが結晶粒界を横切る回数を極端に減らすことができる。そのため、オン電流値（TFTがオン状態にある時に流れるドレイン電流値）、オフ電流値（TFTがオフ状態にある時に流れるドレイン電流値）、しきい値電圧、S値及び電界効果移動度のバラツキを低減することも可能となり、電気的特性は著しく向上する。

#### 【0123】

なお、半導体膜の広い範囲に橢円状ビーム606を照射するため、橢円状ビーム606をその長軸に垂直な方向に走査して半導体膜に照射する動作（以下、スキャンと表記する）を、複数回行っている。ここで、1回のスキャン毎に、橢円状ビーム606の位置は、その長軸に平行な方向にずらされる。また、連続するスキャン間では、その走査方向を逆にする。ここで、連続する2回のスキャンにおいて、一方を往路のスキャン、もう一方を復路のスキャンと呼ぶこととする。

#### 【0124】

橢円状ビーム606の位置を、1回のスキャン毎にその長軸に平行な方向にずらす大きさを、ピッチdと表現する。また、往路のスキャンにおいて、図7に示したような大粒径の結晶粒が形成された領域の、橢円状ビーム606の走査方向に垂直な方向の長さを、D1と表記する。復路のスキャンにおいて、図7に示したような大粒径の結晶粒が形成された領域の、橢円状ビーム606の走査方向に垂直な方向の長さを、D2と表記する。また、D1とD2の平均値を、Dとする。

#### 【0125】

このとき、オーバーラップ率R<sub>0,L</sub>[%]を式(1)で定義する。

#### 【0126】

$$R_{0,L} = (1 - d / D) \times 100 \cdots \text{式(1)}$$

#### 【0127】

本実施例では、オーバーラップ率R<sub>0,L</sub>を0[%]とした。

#### 【0128】

#### [実施例3]

本実施例では、本発明の半導体装置において、高移動度TFTの作製プロセスに用いられる、連続発振レーザを用いた半導体膜の結晶化の方法について、実施例2とは異なる例を示す。

#### 【0129】

半導体膜として非晶質珪素膜を形成するまでの工程は、実施例2と同様である。その後、特開平7-183540号公報に記載された方法を利用し、前記半導体膜上にスピントロート法にて酢酸ニッケル水溶液（重量換算濃度5ppm、体積10ml）を塗布し、500の窒素雰囲気で1時間、550の窒素雰囲気で12時間の熱処理を行った。続いて、レーザアニール法により、半導体膜の結晶性の向上を行った。

#### 【0130】

レーザアニール法に用いるレーザとしては、連続発振のYVO<sub>4</sub>レーザを用いた。レーザアニール法の条件は、レーザ光としてYVO<sub>4</sub>レーザの第2高調波（波長532nm）を用い、図6で示した光学系における凸レンズ103に対するレーザ光の入射角θを約20°として、200μm×50μmの橢円状ビームを形成した。ガラス基板105を50cm/sの速度で移動させながら、前記橢円状ビームを照射して、半導体膜の結晶性の向上を行った。

#### 【0131】

なお、橢円状ビーム606の相対的な走査方向は、橢円状ビーム606の長軸に垂直な方向とした。

#### 【0132】

10

20

20

30

40

50

このようにして得られた結晶性半導体膜にセコエッチングを行って、SEMにより1万倍にて表面を観察した。その結果を図8に示す。図8は、図中の矢印で示す方向にレーザ光を相対的に走査させて得られたものであり、走査方向に対して延在して大粒径の結晶粒が形成されている様子がわかる。

#### 【0133】

このように、本発明を用いて結晶化を行った半導体膜には大粒径の結晶粒が形成されているため、前記半導体膜を用いてTFTを作製すると、そのチャネル形成領域に含まれる結晶粒界の本数を少なくすることができる。また、個々の結晶粒は実質的に単結晶と見なせる結晶性を有することから、単結晶半導体を用いたトランジスタと同等の高いモビリティ(電界効果移動度)を得ることも可能である。

10

#### 【0134】

さらに、形成された結晶粒が一方向に揃っている。そのため、TFTを、そのキャリアの移動方向が、形成された結晶粒の延在する方向と揃うように配置すれば、キャリアが結晶粒界を横切る回数を極端に減らすことができる。そのため、オン電流値、オフ電流値、しきい値電圧、S値及び電界効果移動度のバラツキを低減することも可能となり、電気的特性は著しく向上する。

#### 【0135】

なお、半導体膜の広い範囲に橢円状ビーム606を照射するため、橢円状ビーム606をその長軸に垂直な方向に走査して半導体膜に照射する動作(スキャン)を、複数回行っている。ここで、1回のスキャン毎に、橢円状ビーム606の位置は、その長軸に平行な方向にずらされる。また、連続するスキャン間では、その走査方向を逆にする。ここで、連続する2回のスキャンにおいて、一方を往路のスキャン、もう一方を復路のスキャンと呼ぶことにする。

20

#### 【0136】

橢円状ビーム606の位置を、1回のスキャン毎にその長軸に平行な方向にずらす大きさを、ピッチdと表現する。また、往路のスキャンにおいて、図8に示したような大粒径の結晶粒が形成された領域の、橢円状ビーム606の走査方向に垂直な方向の長さを、D1と表記する。復路のスキャンにおいて、図8に示したような大粒径の結晶粒が形成された領域の、橢円状ビーム606の走査方向に垂直な方向の長さを、D2と表記する。また、D1とD2の平均値を、Dとする。

30

#### 【0137】

このとき、式(1)と同様に、オーバーラップ率R<sub>0..L</sub>[%]を定義する。本実施例では、オーバーラップ率R<sub>0..L</sub>を0[%]とした。

#### 【0138】

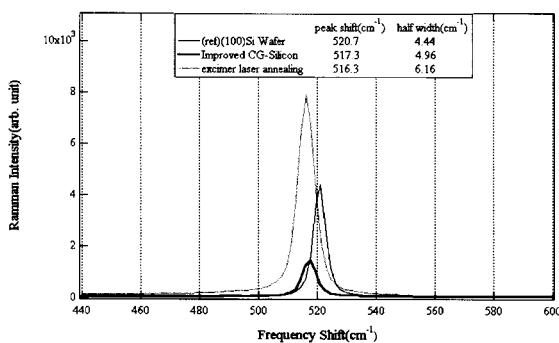

また、上記結晶化の手法によって得られた半導体膜(図中、Improved CG-Siliconと表記)のラマン散乱分光の結果を図9に太線で示す。ここで、比較のため、単結晶シリコン(図中、ref.(100)Si Waferと表記)のラマン散乱分光の結果を細線で示した。また、非晶質珪素膜を形成後、熱処理を行って半導体膜が含有する水素を放出させた後、パルス発振のエキシマレーザを用い結晶化を行った半導体膜(図中、excimer laser annealingと表記)のラマン散乱分光の結果を図9に点線で示した。

40

#### 【0139】

本実施例の手法によって得られた半導体膜のラマンシフトは、517.3cm<sup>-1</sup>のピークを有する。また、半値幅は、4.96cm<sup>-1</sup>である。一方、単結晶シリコンのラマンシフトは、520.7cm<sup>-1</sup>のピークを有する。また、半値幅は、4.44cm<sup>-1</sup>である。パルス発振のエキシマレーザを用い結晶化を行った半導体膜のラマンシフトは、516.3cm<sup>-1</sup>である。また、半値幅は、6.16cm<sup>-1</sup>である。

#### 【0140】

図9の結果により、本実施例に示した結晶化の手法によって得られた半導体膜の結晶性が、パルス発振のエキシマレーザを用い結晶化を行った半導体膜の結晶性と比べて、単結晶シリコンに近いことがわかる。

50

## 【0141】

## [実施例4]

本実施例では、実施例2に示した手法によって結晶化した半導体膜を用いてTFTを作製した例について、図6、図10および図11を用いて説明する。

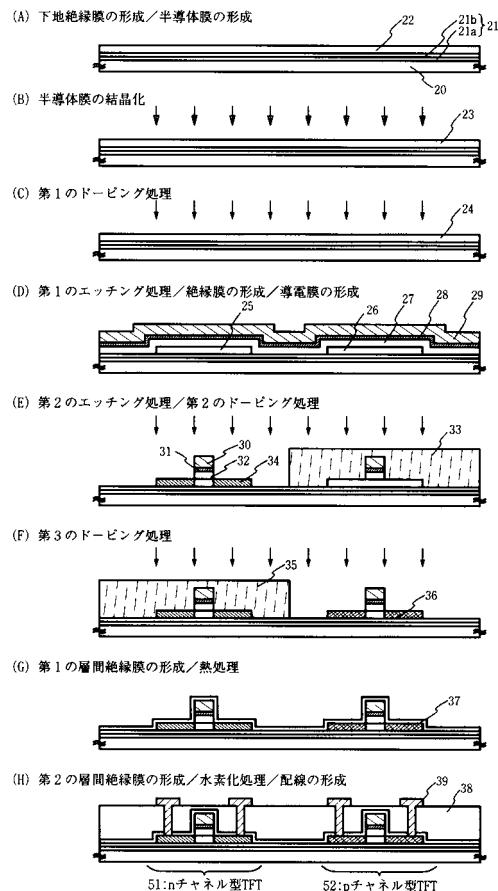

## 【0142】

本実施例では基板20として、ガラス基板を用い、ガラス基板上に下地膜21として、プラズマCVD法により酸化窒化珪素膜（組成比Si=32%、O=27%、N=24%、H=17%）50nm、酸化窒化珪素膜（組成比Si=32%、O=59%、N=7%、H=2%）100nmを積層した。次いで、下地膜21上に半導体膜22として、プラズマCVD法により非晶質珪素膜150nmを形成した。そして、500で3時間の熱処理を行って、半導体膜が含有する水素を放出させた。（図10（A））

## 【0143】

その後、レーザ光として連続発振のYVO<sub>4</sub>レーザの第2高調波（波長532nm、5.5W）を用い、図6で示した光学系における凸レンズ603に対するレーザ光の入射角を約20°として200μm×50μmの楕円状ビームを形成した。前記楕円状ビームを、50cm/sの速度で相対的に走査して、半導体膜22に照射した。（図10（B））

## 【0144】

そして、第1のドーピング処理を行う。これはしきい値を制御するためのチャネルドープである。材料ガスとしてB<sub>2</sub>H<sub>6</sub>を用い、ガス流量30sccm、電流密度0.05μA、加速電圧60keV、ドーズ量1×10<sup>14</sup>/cm<sup>2</sup>として行った。（図10（C））

## 【0145】

続いて、パターニングを行って、半導体膜24を所望の形状にエッチングした後、エッチングされた半導体膜を覆うゲート絶縁膜27としてプラズマCVD法により膜厚115nmの酸化窒化珪素膜を形成する。次いで、ゲート絶縁膜27上に導電膜として膜厚30nmのTaN膜28と、膜厚370nmのW膜29を積層形成する。（図10（D））

## 【0146】

フォトリソグラフィ法を用いてレジストからなるマスク（図示せず）を形成して、W膜、TaN膜、ゲート絶縁膜をエッチングする。

## 【0147】

そして、レジストからなるマスクを除去し、新たにマスク33を形成して第2のドーピング処理を行い、半導体膜にn型を付与する不純物元素を導入する。この場合、導電層30、31がn型を付与する不純物元素に対するマスクとなり、自己整合的に不純物領域34が形成される。本実施例では第2のドーピング処理は、半導体膜の膜厚が150nmと厚いため2条件に分けて行った。本実施例では、材料ガスとしてフォスфин（PH<sub>3</sub>）を用い、ドーズ量を2×10<sup>13</sup>/cm<sup>2</sup>とし、加速電圧を90keVとして行った後、ドーズ量を5×10<sup>14</sup>/cm<sup>2</sup>とし、加速電圧を10keVとして行った。（図10（E））

## 【0148】

次いで、レジストからなるマスク33を除去した後、新たにレジストからなるマスク35を形成して第3のドーピング処理を行う。第3のドーピング処理により、pチャネル型TFTの活性層となる半導体膜に前記一導電型とは逆の導電型を付与する不純物元素が添加された不純物領域36を形成する。導電層30、31を不純物元素に対するマスクとして用い、p型を付与する不純物元素を添加して自己整合的に不純物領域36を形成する。本実施例では第3のドーピング処理においても、半導体膜の膜厚が150nmと厚いため2条件に分けて行った。本実施例では、材料ガスとしてジボラン（B<sub>2</sub>H<sub>6</sub>）を用い、ドーズ量を2×10<sup>13</sup>/cm<sup>2</sup>とし、加速電圧を90keVとして行った後、ドーズ量を1×10<sup>15</sup>/cm<sup>2</sup>とし、加速電圧を10keVとして行った。（図10（F））

## 【0149】

以上までの工程で、それぞれの半導体層に不純物領域34、36が形成される。

## 【0150】

次いで、レジストからなるマスク35を除去して、プラズマCVD法により第1の層間絶

10

20

30

40

50

縁膜 3 7 として膜厚 5 0 nm の酸化窒化珪素膜（組成比 Si = 32.8%、O = 63.7%、N = 3.5%）を形成した。

#### 【0151】

次いで、熱処理により、半導体層の結晶性の回復、それぞれの半導体層に添加された不純物元素の活性化を行う。本実施例ではファーネスアニール炉を用いた熱アニール法により、窒素雰囲気中にて 550 度 4 時間の熱処理を行った。（図 10 (G)）

#### 【0152】

次いで、第 1 の層間絶縁膜 3 7 上に無機絶縁膜材料または有機絶縁物材料から成る第 2 の層間絶縁膜 3 8 を形成する。本実施例では、CVD 法により膜厚 50 nm の窒化珪素膜を形成した後、膜厚 400 nm の酸化珪素膜を形成した。

10

#### 【0153】

そして、熱処理を行うと水素化処理を行うことができる。本実施例では、ファーネスアニール炉を用い、410 度で 1 時間、窒素雰囲気中にて熱処理を行った。

#### 【0154】

続いて、各不純物領域とそれぞれ電気的に接続する配線 3 9 を形成する。本実施例では、膜厚 50 nm の Ti 膜と、膜厚 500 nm の Al-Si 膜と、膜厚 50 nm の Ti 膜との積層膜をパターニングして形成した。もちろん、二層構造に限らず、単層構造でもよいし、三層以上の積層構造にしてもよい。また、配線の材料としては、Al と Ti に限らない。例えば、TaN 膜上に Al や Cu を形成し、さらに Ti 膜を形成した積層膜をパターニングして配線を形成してもよい。（図 10 (H)）

20

#### 【0155】

以上の様にして、チャネル長 6 μm、チャネル幅 4 μm の n チャネル型 TFT 5 1 と p チャネル型 TFT 5 2 が形成された。

#### 【0156】

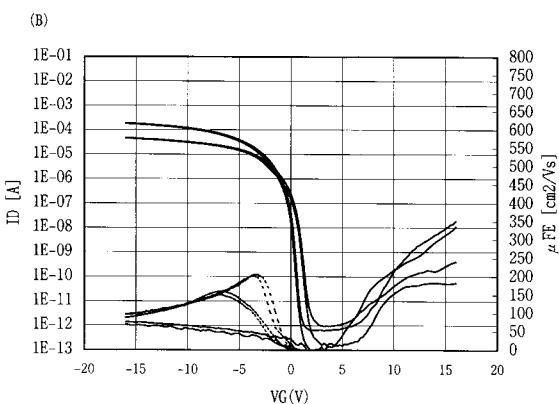

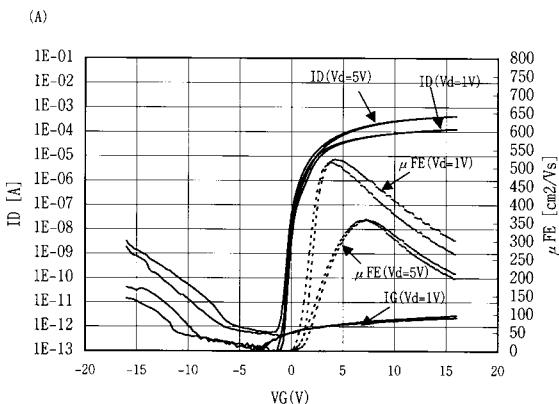

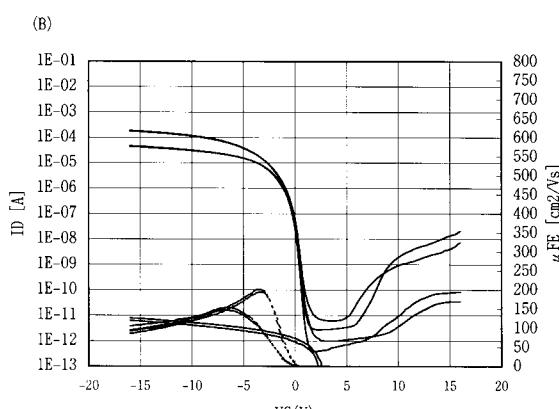

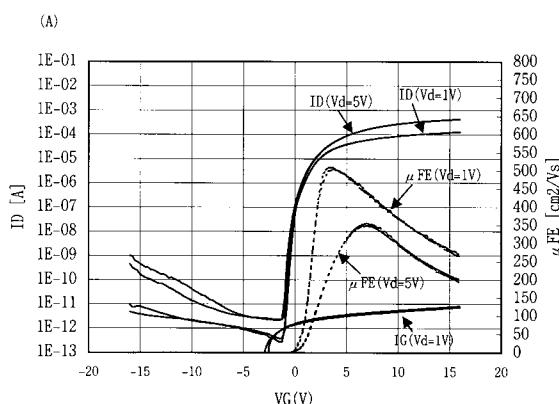

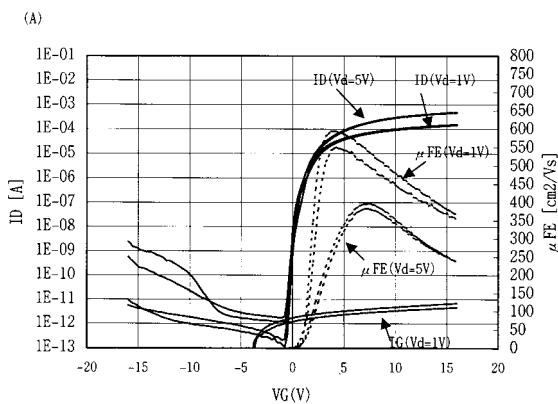

これらの電気的特性を測定した結果を図 11 に示す。n チャネル型 TFT 5 1 の電気的特性を図 11 (A) に、p チャネル型 TFT 5 2 の電気的特性を図 11 (B) に示す。電気的特性の測定条件は、測定点をそれぞれ 2 点とし、ゲート電圧 Vg = -16 ~ 16 V の範囲で、ドレイン電圧 Vd = 1 V 及び 5 V とした。また、図 11 において、ドレイン電流 (ID)、ゲート電流 (IG) は実線で、移動度 (μFE) は点線で示している。

30

#### 【0157】

上述した方法で結晶化を行った半導体膜には大粒径の結晶粒が形成されているため、前記半導体膜を用いて TFT を作製すると、そのチャネル形成領域に含まれる結晶粒界の本数を少なくすることができる。さらに、形成された結晶粒は一方向に揃っているため、TFT のチャネル方向とレーザ光の走査方向とをおおむね平行とすることで、キャリアが結晶粒界を横切る回数を極端に減らすことができる。そのため、図 11 に示したように電気的特性の良い TFT が得られる。特に移動度が、n チャネル型 TFT において  $524 \text{ cm}^2/\text{Vs}$ 、p チャネル型 TFT において  $205 \text{ cm}^2/\text{Vs}$  となることがわかる。

#### 【0158】

本実施例に示した連続発振レーザを用いた半導体膜の活性化方法は、本発明における、高速動作が必要な回路ブロックを構成する TFT に対して適用することができる。

40

特に、TFT のチャネル方向とレーザ光の走査方向とをおおむね平行（30°以内）とすることで、単結晶シリコン基板に形成した場合とほぼ同等な動作特性を有する回路ブロックを実現することができる。

#### 【0159】

#### [実施例 5]

本実施例では、実施例 3 に示した手法によって結晶化した半導体膜を用いて TFT を作製した例について、図 6、図 12 ~ 図 14、図 15 を用いて説明する。

#### 【0160】

半導体膜として非晶質珪素膜を形成するまでの工程は、実施例 4 と同様である。なお、非晶質珪素膜は、150 nm の厚さで形成した。（図 12 (A)）

50

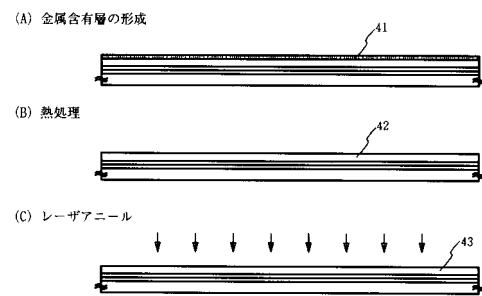

**【0161】**

その後、特開平7-183540号公報に記載された方法を利用し、前記半導体膜上にスピニコート法にて酢酸ニッケル水溶液（重量換算濃度5 ppm、体積10ml）を塗布して金属含有層41を形成する。そして、500の窒素雰囲気で1時間、550の窒素雰囲気で12時間の熱処理を行った。こうして半導体膜42を得た。（図12（B））

**【0162】**

続いて、レーザアニール法により、半導体膜42の結晶性の向上を行う。

**【0163】**

レーザアニール法の条件は、レーザ光として連続発振の $\text{YVO}_4$ レーザの第2高調波（波長532nm、5.5W）を用い、図6で示した光学系における凸レンズ603に対するレーザ光の入射角を約20°として $200\mu\text{m} \times 50\mu\text{m}$ の楕円状ビームを形成した。前記楕円状ビームを、基板を $20\text{cm/s}$ または $50\text{cm/s}$ の速度で移動させながら照射して、半導体膜42の結晶性の向上を行った。こうして半導体膜43を得た。（図12（C））

**【0164】**

図12（C）の半導体膜の結晶化の後の工程は、実施例5において示した図10（C）～図10（H）の工程と同様である。こうして、チャネル長 $6\mu\text{m}$ 、チャネル幅 $4\mu\text{m}$ のnチャネル型TFT51とpチャネル型TFT52が形成された。これらの電気的特性を測定した。

**【0165】**

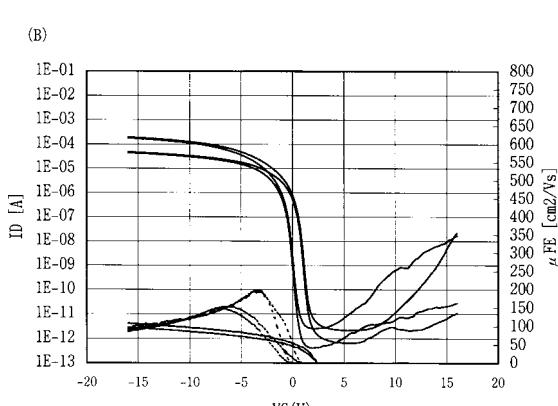

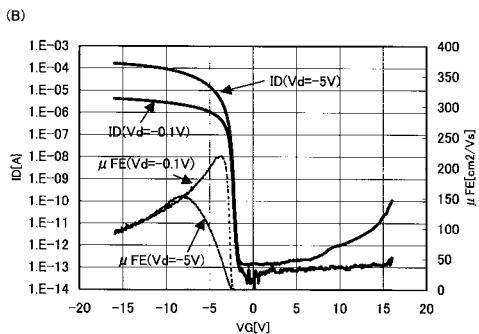

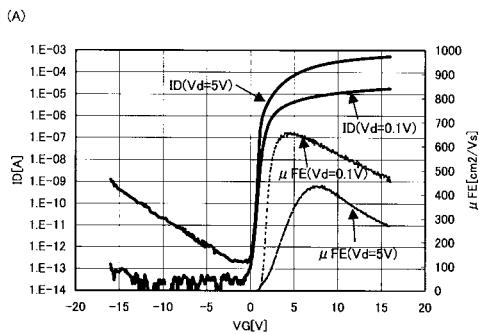

上記工程によって作製したTFTの電気的特性を、図13、図14、図15に示す。

**【0166】**

図13（A）及び図13（B）に、図12（C）のレーザアニール工程において、基板の速度を $20\text{cm/s}$ で移動させて作製したTFTの電気的特性を示す。図13（A）に、nチャネル型TFT51の電気的特性を示す。また図13（B）に、pチャネル型TFT52の電気的特性を示す。また、図14（A）及び図14（B）に、図12（C）のレーザアニール工程において、基板の速度を $50\text{cm/s}$ で移動させて作製したTFTの電気的特性を示す。図14（A）に、nチャネル型TFT51の電気的特性を示す。また図14（B）に、pチャネル型TFT52の電気的特性を示す。

**【0167】**

なお、電気的特性の測定条件は、ゲート電圧 $V_g = 16 \sim 16\text{V}$ の範囲で、ドレイン電圧 $V_d = 1\text{V}$ 及び $5\text{V}$ とした。また、図13、図14において、ドレイン電流（ID）、ゲート電流（IG）は実線で、移動度（μFE）は点線で示している。

**【0168】**

本実施例に示した結晶化を行った半導体膜には大粒径の結晶粒が形成されているため、前記半導体膜を用いてTFTを作製すると、そのチャネル形成領域に含まれる結晶粒界の本数を少なくすることができる。さらに、形成された結晶粒は一方向に揃っており、レーザ光の相対的な走査方向に対して交差する方向に形成される粒界が少ないため、キャリアが結晶粒界を横切る回数を極端に減らすことができる。

**【0169】**

そのため、図13及び図14に示したように電気的特性の良いTFTが得られる。特に移動度が、図13ではnチャネル型TFTにおいて $510\text{cm}^2/\text{Vs}$ 、pチャネル型TFTにおいて $200\text{cm}^2/\text{Vs}$ 、また、図14ではnチャネル型TFTにおいて $595\text{cm}^2/\text{Vs}$ 、pチャネル型TFTにおいて $199\text{cm}^2/\text{Vs}$ と非常に優れていることがわかる。そして、このようなTFTを用いて半導体装置を作製すれば、その動作特性および信頼性をも向上することが可能となる。

**【0170】**

また、図15に、図12（C）のレーザアニール工程において、基板の速度を $50\text{cm/s}$ で移動させて作製したTFTの電気的特性を示す。図15（A）に、nチャネル型TFT51の電気的特性を示す。また図15（B）に、pチャネル型TFT52の電気的特性

10

20

30

40

50

を示す。

**【0171】**

なお、電気的特性の測定条件は、ゲート電圧  $V_g = 16 \sim 16$  V の範囲で、ドレイン電圧  $V_d = 0.1$  V 及び 5 V とした。

**【0172】**

図 15 に示したように電気的特性の良い TFT が得られる。特に移動度が、図 15 (A) に示した n チャネル型 TFT において  $657 \text{ cm}^2 / \text{Vs}$  、図 15 (B) に示した p チャネル型 TFT において  $219 \text{ cm}^2 / \text{Vs}$  と非常に優れていることがわかる。そして、このような TFT を用いて半導体装置を作製すれば、その動作特性および信頼性をも向上することが可能となる。

10

**【0173】**

本実施例に示した連続発振レーザを用いた半導体膜の活性化方法は、本発明における、高速動作が必要な回路ブロックを構成する TFT に対して適用することができる。

特に、TFT のチャネル方向とレーザ光の走査方向とをおおむね平行 ( $30^\circ$  以内) とすることで、単結晶シリコン基板に形成した場合とほぼ同等な動作特性を有する回路ブロックを実現することができる。

**【0174】**

**[実施例 6]**

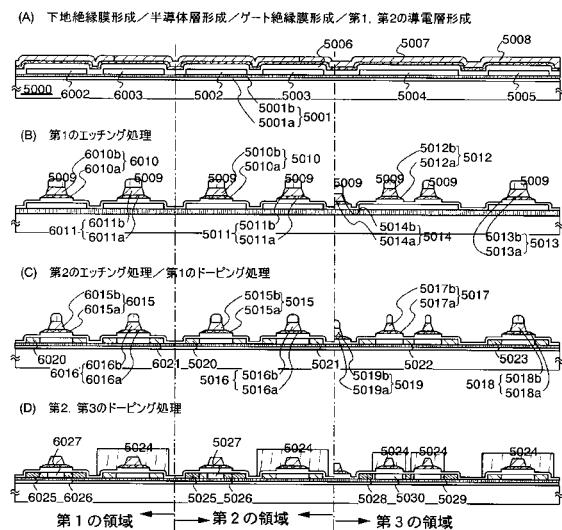

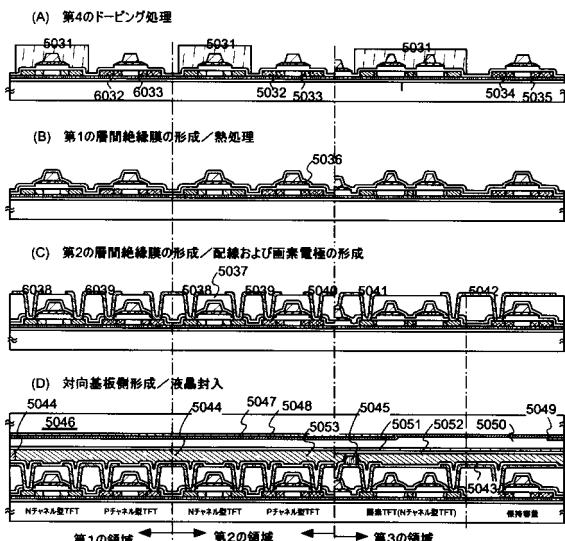

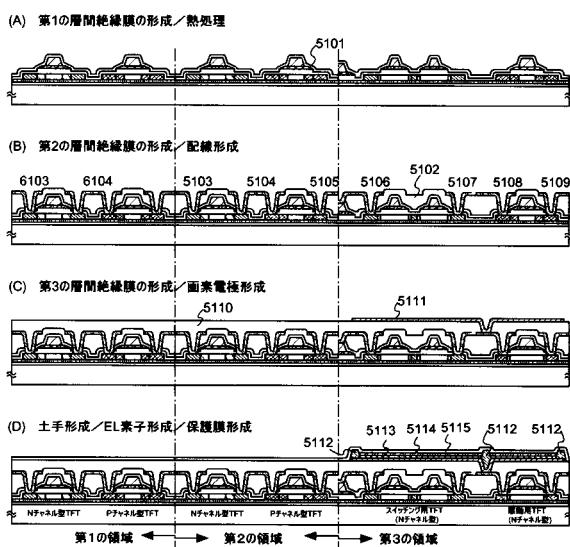

本実施例では複数の回路とアクティピマトリクス型液晶表示部が同一基板上に形成される半導体装置の作製工程について図 3、図 4 を用いて説明する。

20

**【0175】**

図 3 及び図 4 に示した断面図は、第 1 の領域、第 2 の領域、第 3 の領域によって構成されている。

第 1 の領域は特に高速動作を要求する回路ブロック（例えば、CPU、信号線駆動回路等）であり、本発明において連続発振レーザを用いた半導体膜の結晶化の方法を行う領域である。また、第 2 の領域はそれ以外の回路ブロック（例えば、走査線駆動回路）、第 3 の領域は画素領域を示す。

**【0176】**

なお、図 3 及び図 4 では、回路ブロックを代表して N チャネル型 TFT と P チャネル型 TFT を、画素領域を代表して、N チャネル型 TFT（画素 TFT）と、保持容量を示す。

30

**【0177】**

基板 5000 は、石英基板、シリコン基板、金属、基板又はステンレス基板の表面に絶縁膜を形成したものを用いる。また本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いても良い。本実施例ではバリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス等のガラスからなる基板 5000 を用いた。

**【0178】**

次いで、基板 5000 上に酸化珪素膜、窒化珪素膜又は酸化窒化珪素膜などの絶縁膜から成る下地膜 5001 を形成する。本実施例の下地膜 5001 は 2 層構造で形成したが、前記絶縁膜の単層構造又は前記絶縁膜を 2 層以上積層させた構造であっても良い。

**【0179】**

本実施例では、下地膜 5001 の 1 層目として、プラズマ CVD 法を用いて、SiH<sub>4</sub>、NH<sub>3</sub>、及び N<sub>2</sub>O を反応ガスとして成膜される窒化酸化珪素膜 5001a を  $10 \sim 200$  [nm]（好ましくは  $50 \sim 100$  [nm]）の厚さに形成する。本実施例では、窒化酸化珪素膜 5001a を 50 [nm] の厚さに形成した。次いで下地膜 5001 の 2 層目として、プラズマ CVD 法を用いて、SiH<sub>4</sub> 及び N<sub>2</sub>O を反応ガスとして成膜される酸化窒化珪素膜 5001b を  $50 \sim 200$  [nm]（好ましくは  $100 \sim 150$  [nm]）の厚さに形成する。本実施例では、酸化窒化珪素膜 5001b を 100 [nm] の厚さに形成した。

40

**【0180】**

続いて、下地膜 5001 上に半導体層 5002 ~ 5006、6002、6003 を形成する。半導体層 5002 ~ 5005、6002、6003 は公知の手段（スパッタ法、LPCVD 法等）で形成する。

50

CVD法、プラズマCVD法等)により25~80[nm](好ましくは30~60[nm])の厚さで半導体膜を成膜する。なお前記半導体膜としては、非晶質半導体膜、微結晶半導体膜、結晶質半導体膜、又は非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜などを用いても良い。

#### 【0181】

次いで、第2の領域と第3の領域、あるいは基板全域の前記半導体膜に対して第1の結晶化を行う。第1の結晶化法としては、公知の結晶化法(レーザ結晶化法、RTA又はファーネスアーナー炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等)を用いることができる。

#### 【0182】

本実施例では、プラズマCVD法を用いて、膜厚55[nm]の非晶質珪素膜を成膜した。そして、第1の結晶化法として、ニッケルを含む溶液を非晶質珪素膜上に保持させ、この非晶質珪素膜に脱水素化(500[ ], 1時間)を行った後、熱結晶化(550[ ], 4時間)を行って第1の結晶質珪素膜を形成した。

#### 【0183】

なおレーザ結晶化法で第1の結晶質半導体膜を作製する場合には、第2の領域と第3の領域のみを選択的に行っても良いし、基板全域の前記半導体膜に対して結晶化に行ってもよい。レーザは、パルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、Ti:サファイアレーザ等を用いることができる。また後者の固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を使ったレーザを用いることができる。当該レーザの基本波はドーピングする材料によって異なり、1[μm]前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ることができる。

#### 【0184】

結晶化の条件は適宜設定されるが、エキシマレーザを用いる場合はパルス発振周波数300[Hz]とし、レーザーエネルギー密度を100~700[mJ/cm<sup>2</sup>](代表的には200~300[mJ/cm<sup>2</sup>])とすると良い。またYAGレーザを用いる場合には、その第2高調波を用いてパルス発振周波数1~300[Hz]とし、レーザーエネルギー密度を300~1000[mJ/cm<sup>2</sup>](代表的には350~500[mJ/cm<sup>2</sup>])とすると良い。そして幅100~1000[μm](好ましくは幅400[μm])で線状に集光したレーザ光を基板全面に渡って照射し、このときの線状ビームの重ね合わせ率(オーバーラップ率)を50~98[%]として行っても良い。

#### 【0185】

次いで、第1の領域の半導体膜に対して第2の結晶化を行う。第2の結晶化法には、連続発振レーザを用いた結晶化を行う。連続発振レーザを用いた結晶化の方法としては、実施例2、3に示した方法を用いることができる。こうして第2の結晶質珪素を得る。

#### 【0186】

このような半導体膜の結晶化工程によって、高速動作が要求される回路ロジックを含む第1の領域には、第1の結晶性珪素膜が、他の領域には第2の結晶性珪素膜が、それぞれ形成される。

#### 【0187】

第1の結晶性珪素膜は、レーザ光の相対的な走査方向に延在して、大粒径の結晶粒が形成されているため、第1の結晶性珪素膜を活性層として有するTFTは、高い電気的特性を有する。

特に、チャネル方向がレーザ光の相対的な走査方向とおおむね平行に形成されている場合には、キャリアが結晶粒界を横切る回数を極端に減らすことができるため、単結晶シリコン上に形成されたトランジスタと同程度の電気特性を実現することも可能である。

#### 【0188】

10

20

30

40

50

一方、連続発振レーザはビーム幅が狭い(50~500μm)ため、広い領域にこの結晶化プロセスを適用するのはスループットの観点から不利である。本発明では、連続発振レーザを用いた結晶化を基板上の限られた領域に限定することでスループットの向上を図っている。

#### 【0189】

次に、フォトリソグラフィ法を用いたパターニング処理によって半導体層5002~5005、6002、6003を形成した。

#### 【0190】

本実施例では、結晶化を助長する金属元素を用いて非晶質珪素膜の結晶化を行ったため、前記金属元素が結晶質珪素膜中に残留している。そのため、前記結晶質珪素膜上に50~100[nm]の非晶質珪素膜を形成し、加熱処理(RTA法やファーネスアニール炉を用いた熱アニール等)を行って、該非晶質珪素膜中に前記金属元素を拡散させ、前記非晶質珪素膜は加熱処理後にエッティングを行って除去する。その結果、前記第1の結晶質珪素膜中の金属元素の含有量を低減または除去することができる。10

#### 【0191】

なお半導体層5002~5005、6002、6003を形成した後、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

#### 【0192】

次いで、半導体層5002~5005、6002、6003を覆うゲート絶縁膜5006を形成する。ゲート絶縁膜5006はプラズマCVD法やスパッタ法を用いて、膜厚を40~150[nm]として珪素を含む絶縁膜で形成する。本実施例では、ゲート絶縁膜5006としてプラズマCVD法により酸化窒化珪素膜を110[nm]の厚さに形成した。勿論、ゲート絶縁膜5006は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。20

#### 【0193】

なおゲート絶縁膜5006として酸化珪素膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40[Pa]、基板温度300~400[ ]とし、高周波(13.56[MHz])電力密度0.5~0.8[W/cm<sup>2</sup>]で放電させて形成しても良い。上記の工程により作製される酸化珪素膜は、その後400~500[ ]の熱アニールによって、ゲート絶縁膜5006として良好な特性を得ることができる30。

#### 【0194】

次いで、ゲート絶縁膜5006上に膜厚20~100[nm]の第1の導電膜5007と、膜厚100~400[nm]の第2の導電膜5008とを積層形成する。本実施例では、膜厚30[nm]のTaN膜からなる第1の導電膜5007と、膜厚370[nm]のW膜からなる第2の導電膜5008を積層形成した。

#### 【0195】

本実施例では、第1の導電膜5007であるTaN膜はスパッタ法で形成し、Taのターゲットを用いて、窒素を含む雰囲気内でスパッタ法で形成した。また第2の導電膜5008であるW膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することもできる。40

#### 【0196】

なお本実施例では、第1の導電膜5007をTaN膜、第2の導電膜5008をW膜としたが、第1の導電膜5007及び第2の導電膜5008を構成する材料は特に限定されない。第1の導電膜5007及び第2の導電膜5008は、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選択された元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体膜やAgPdCu合金で形成してもよい。

#### 【0197】

次いで、フォトリソグラフィ法を用いてレジストからなるマスク5009を形成し、電極50

及び配線を形成するための第1のエッティング処理を行う。第1のエッティング処理では第1及び第2のエッティング条件で行う。(図3(B))

#### 【0198】

本実施例では第1のエッティング条件として、ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッティング法を用い、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25:25:10[sccm]とし、1.0[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成してエッティングを行った。基板側(試料ステージ)にも150[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加した。そしてこの第1のエッティング条件によりW膜をエッティングして第1の導電層5007の端部をテーパー形状とした。

10

#### 【0199】

続いて、レジストからなるマスク5009を除去せずに第2のエッティング条件に変更し、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30:30[sccm]とし、1.0[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成して15秒程度のエッティングを行った。基板側(試料ステージ)にも20[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加した。第2のエッティング条件では第1の導電層5007及び第2の導電層5008とも同程度にエッティングを行った。なお、ゲート絶縁膜5006上に残渣を残すことなくエッティングするためには、10~20[%]程度の割合でエッティング時間を増加させると良い。

#### 【0200】

上記の第1のエッティング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層5007及び第2の導電層5008の端部がテーパー形状となる。こうして、第1のエッティング処理により第1の導電層5007と第2の導電層5008から成る第1の形状の導電層5010~5014、6010、6011を形成した。ゲート絶縁膜5006においては、第1の形状の導電層5010~5014、6010、6011で覆われない領域が20~50nm程度エッティングされたため、膜厚が薄くなった領域が形成された。

20

#### 【0201】

次いで、レジストからなるマスク5009を除去せずに第2のエッティング処理を行う。(図3(C))第2のエッティング処理では、エッティングガスにSF<sub>6</sub>とCl<sub>2</sub>とO<sub>2</sub>を用い、それぞれのガス流量比を24:12:24(sccm)とし、1.3Paの圧力でコイル側の電力に700WのRF(13.56MHz)電力を投入してプラズマを生成して25秒程度のエッティングを行った。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加した。こうして、W膜を選択的にエッティングして、第2の形状の導電層5015~5019、6015、6016を形成した。このとき、第1の導電層5015a~5018a、6015a、6016aは、ほとんどエッティングされない。

30

#### 【0202】

そして、レジストからなるマスク5009を除去せずに第1のドーピング処理を行い、半導体層5002~5005、6002、6003にN型を付与する不純物元素を低濃度に添加する。第1のドーピング処理はイオンドープ法又はイオン注入法で行えば良い。イオンドープ法の条件はドーザ量を $1 \times 10^{13} \sim 5 \times 10^{14}$ [atoms/cm<sup>2</sup>]とし、加速電圧を40~80[keV]として行う。本実施例ではドーザ量を $5.0 \times 10^{13}$ [atoms/cm<sup>2</sup>]とし、加速電圧を50[keV]として行った。N型を付与する不純物元素としては、15族に属する元素を用いれば良く、代表的にはリン(P)又は砒素(A s)が用いられるが、本実施例ではリン(P)を用いた。この場合、第2の形状の導電層5015~5019、6015、6016がN型を付与する不純物元素に対するマスクとなって、自己整合的に第1の不純物領域(N--領域)5020~5023、6020、6021を形成した。そして第1の不純物領域5020~5023、6020、6021には $1 \times 10^{18} \sim 1 \times 10^{20}$ [atoms/cm<sup>3</sup>]の濃度範囲でN型を付与する不純物元素が添加された。

40

50

**【0203】**

続いてレジストからなるマスク5009を除去した後、新たにレジストからなるマスク5024を形成して、第1のドーピング処理よりも高い加速電圧で第2のドーピング処理を行う。イオンドープ法の条件はドーザ量を $1 \times 10^{13} \sim 3 \times 10^{15}$ [atoms/cm<sup>2</sup>]とし、加速電圧を60～120[keV]として行う。本実施例では、ドーザ量を $3 \times 10^{15}$ [atoms/cm<sup>2</sup>]とし、加速電圧を65[keV]として行った。第2のドーピング処理は第2の導電層5015b～5018b、6015b、6016bを不純物元素に対するマスクとして用い、第1の導電層5015a～5018a、6015a、6016aのテーパー部の下方の半導体層に不純物元素が添加されるようにドーピングを行う。続いて、第2のドーピング処理より加速電圧を下げて第3のドーピング処理を行って図3(D)の状態を得る。イオンドープ法の条件はドーザ量を $1 \times 10^{15} \sim 1 \times 10^{17}$ [atoms/cm<sup>2</sup>]とし、加速電圧を50～100keVとして行う。

10

**【0204】**

上記の第2のドーピング処理及び第3のドーピング処理を行った結果、第1の導電層と重なる第2の不純物領域(N-領域、Lov領域)5026、6026には $1 \times 10^{18} \sim 5 \times 10^{19}$ [atoms/cm<sup>3</sup>]の濃度範囲でN型を付与する不純物元素を添加された。また第3の不純物領域(N+領域)5025、5028、6025には $1 \times 10^{19} \sim 5 \times 10^{21}$ [atoms/cm<sup>3</sup>]の濃度範囲でN型を付与する不純物元素を添加された。また、第1、第2のドーピング処理を行った後、半導体層5002～5005、6002、6003において、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域が形成された。本実施例では、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域をチャネル領域5027、5030、6027とよぶ。また前記第1のドーピング処理により形成された第1の不純物領域(N--領域)5020～5023、6020、6021のうち、第2のドーピング処理においてレジスト5024で覆われていた領域が存在するが、本実施例では、引き続き第1の不純物領域(N--領域、LDD領域)5029とよぶ。

20

**【0205】**

なお本実施例では、第2のドーピング処理のみにより、第2の不純物領域(N-領域)5026、6026及び第3の不純物領域(N+領域)5025、5028、6025を形成したが、これに限定されない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で形成しても良い。

30

**【0206】**

次いで図4(A)に示すように、レジストからなるマスク5024を除去した後、新たにレジストからなるマスク5031を形成する。その後、第4のドーピング処理を行う。第4のドーピング処理により、Pチャネル型TFTの活性層となる半導体層に、前記第1の導電型とは逆の導電型を付与する不純物元素が添加された第4の不純物領域(P+領域)5032、5034、6032及び第5の不純物領域(P-領域)5033、5035、6033を形成する。

**【0207】**

第4のドーピング処理では、第2の導電層5016b、5018bを不純物元素に対するマスクとして用いる。こうして、P型を付与する不純物元素を添加し、自己整合的に第4の不純物領域(P+領域)5032、5034、6032及び第5の不純物領域(P-領域)5033、5035、6033を形成する。

40

**【0208】**

本実施例では、第4の不純物領域5032、5034、6032及び第5の不純物領域5033、5035、6033はジボラン(B<sub>2</sub>H<sub>6</sub>)を用いたイオンドープ法で形成する。イオンドープ法の条件としては、ドーザ量を $1 \times 10^{16}$ [atoms/cm<sup>2</sup>]とし、加速電圧を80[keV]とした。

**【0209】**

なお、第4のドーピング処理の際には、Nチャネル型TFTを形成する半導体層はレジストからなるマスク5031によって覆われている。

50

## 【0210】

ここで、第1及び2のドーピング処理によって、第4の不純物領域(P+領域)5032、5034、6032及び第5の不純物領域(P-領域)5033、5035、6033にはそれぞれ異なる濃度でリンが添加されている。しかし、第4の不純物領域(P+領域)5032、5034、6032及び第5の不純物領域(P-領域)5033、5035、6033のいずれの領域においても、第4のドーピング処理によって、P型を付与する不純物元素の濃度が $1 \times 10^{19} \sim 5 \times 10^{21}$ [atoms/cm<sup>3</sup>]となるようにドーピング処理される。こうして、第4の不純物領域(P+領域)5032、5034、6032及び第5の不純物領域(P-領域)5033、5035、6033は、Pチャネル型TFTのソース領域およびドレイン領域として問題なく機能する。

10

## 【0211】

なお本実施例では、第4のドーピング処理のみにより、第4の不純物領域(P+領域)5032、5034、6032及び第5の不純物領域(P-領域)5033、5035、6033を形成したが、これに限定されない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で形成しても良い。

## 【0212】

次いで図4(B)に示すように、レジストからなるマスク5031を除去して第1の層間絶縁膜5036を形成する。この第1の層間絶縁膜5036としては、プラズマCVD法またはスパッタ法を用い、厚さを100~200[nm]として珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚100[nm]の酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜5036は酸化窒化珪素膜に限定されるものではなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

20

## 【0213】

次いで、図4(C)に示すように、加熱処理(熱処理)を行って、半導体層の結晶性の回復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1[ppm]以下、好ましくは0.1[ppm]以下の窒素雰囲気中で400~700[°C]で行えばよく、本実施例では410[°C]、1時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

## 【0214】

30

また、第1の層間絶縁膜5036を形成する前に加熱処理を行っても良い。ただし、第1の導電層5015a~5019a、6015a、6016a及び、第2の導電層5015b~5019b、6015b、6016bを構成する材料が熱に弱い場合には、本実施例のように配線等を保護するため第1の層間絶縁膜5036(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うことが好ましい。

## 【0215】

上記の様に、第1の層間絶縁膜5036(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行うことができる。水素化の工程では、第1の層間絶縁膜5036に含まれる水素により半導体層のダングリングボンドが終端される。

40

## 【0216】

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い。

## 【0217】

ここで、第1の層間絶縁膜5036の存在に関係なく、半導体層を水素化することもできる。水素化の他の手段として、プラズマにより励起された水素を用いる手段(プラズマ水素化)や、3~100[%]の水素を含む雰囲気中において、300~450[°C]で1~12時間の加熱処理を行う手段でも良い。

## 【0218】

次いで、第1の層間絶縁膜5036上に、第2の層間絶縁膜5037を形成する。第2の層間絶縁膜5037としては、無機絶縁膜を用いることができる。例えば、CVD法によ

50

って形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素膜等を用いることができる。また、第2の層間絶縁膜5037として、有機絶縁膜を用いることができる。例えば、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリル等の膜を用いることができる。また、アクリル膜と酸化窒化珪素膜の積層構造を用いても良い。

#### 【0219】

本実施例では、膜厚1.6[μm]のアクリル膜を形成した。第2の層間絶縁膜5037によって、基板上5000に形成されたTFTによる凹凸を緩和し、平坦化することができる。特に、第2の層間絶縁膜5037は平坦化の意味合いが強いので、平坦性に優れた膜が好ましい。

10

#### 【0220】

次いで、ドライエッティングまたはウェットエッティングを用い、第2の層間絶縁膜5037、第1の層間絶縁膜5036、およびゲート絶縁膜5006をエッティングし、第3の不純物領域5025、5028、6025第4の不純物領域5032、5034、6032に達するコンタクトホールを形成する。

#### 【0221】

続いて、各不純物領域とそれぞれ電気的に接続する配線5038～5041、6038、6039および画素電極5042を形成する。なお、これらの配線は、膜厚50[nm]のTi膜と、膜厚500[nm]の合金膜(A1とTiの合金膜)との積層膜をパターニングして形成する。もちろん、二層構造に限らず、単層構造でも良いし、三層以上の積層構造にしても良い。また、配線材料としては、A1とTiに限らない。例えば、TaN膜上にA1膜やCu膜を形成し、さらにTi膜を形成した積層膜をパターニングして配線を形成しても良いが、反射性に優れた材料を用いることが望ましい。

20

#### 【0222】

続いて、画素電極5042を少なくとも含む部分上に配向膜5043を形成しラビング処理を行う。なお、本実施例では配向膜5043を形成する前に、アクリル樹脂膜等の有機樹脂膜をパターニングすることによって基板間隔を保持するための柱状のスペーサ5045を所望の位置に形成した。また、柱状のスペーサに代えて、球状のスペーサを基板全面に散布してもよい。

#### 【0223】

30

次いで、対向基板5046を用意する。対向基板5046上に着色層(カラーフィルタ)5047～5049、平坦化膜5050を形成する。このとき、第1の着色層5047と第2の着色層5048とを重ねて、遮光部を形成する。また、第1の着色層5047と第3の着色層5049とを一部重ねて、遮光部を形成してもよいし、第2の着色層5048と第3の着色層5049とを一部重ねて、遮光部を形成しても良い。

#### 【0224】

このように、新たに遮光層を形成することなく、各画素間の隙間を着色層の積層からなる遮光部で遮光することによって工程数の低減を可能とした。

#### 【0225】

次いで、平坦化膜5050上に透明導電膜からなる対向電極5051を少なくとも画素領域に形成し、対向基板の全面に配向膜5052を形成し、ラビング処理を施した。

40

#### 【0226】

そして、画素領域と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール材5044で貼り合わせる。シール材5044にはフィラーが混入されていて、このフィラーと柱状スペーサによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料5053を注入し、封止剤(図示せず)によって完全に封止する。液晶材料5053には公知の液晶材料を用いれば良い。このようにして図4(D)に示す液晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基板を所望の形状に分断する。さらに、偏光板およびFPC(図示せず)を貼りつけた。

50

**【0227】**

このように、高速動作を必要とする領域とそうでない領域とで、半導体膜の活性化プロセスを異ならせることにより、装置全体として高速動作を有する半導体装置を、スループットの高い作製工程で作製することが可能となる。

**【0228】**

また特に、第1の領域（高速動作を必要とする回路ブロックを有する領域）においては、連続発振レーザを用いた結晶化を行うことにより、大粒径の結晶粒が形成された半導体膜を有するTFTが作製され、高速動作が可能な回路ブロックを実現している。

**【0229】**

なお、本実施例で作製するTFTは、ボトムゲート構造もしくはデュアルゲート構造としてもよい。 10

**[実施例7]**

本実施例では、薄膜トランジスタで構成される回路ブロックと、EL表示部とが同一基板上に形成された基板の作製工程について説明する。

**【0230】**

なお、図5(A)までの工程は、実施例6において、図3(A)～(D)、図4(A)に示した工程と同様である。 20

**【0231】**

図3及び図4と同じ部分は同じ符号を用いて示し、説明は省略する。

**【0232】**

図5(A)に示すように、第1の層間絶縁膜5101を形成する。この第1の層間絶縁膜5101としては、プラズマCVD法またはスパッタ法を用い、厚さを100～200nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚100nmの酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜5101は酸化窒化珪素膜に限定されるものではなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。 20

**【0233】**

次いで、図5(B)に示すように、加熱処理（熱処理）を行って、半導体層の結晶性の回復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニール炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700で行えばよく、本実施例では410、1時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法（RTA法）を適用することができる。 30

**【0234】**

また、第1の層間絶縁膜5101を形成する前に加熱処理を行っても良い。ただし、第1の導電層5015a～5019a及び、第2の導電層5015b～5019bが熱に弱い場合には、本実施例のように配線等を保護するため第1の層間絶縁膜5101（珪素を主成分とする絶縁膜、例えば窒化珪素膜）を形成した後で熱処理を行うことが好ましい。 40

**【0235】**

上記の様に、第1の層間絶縁膜5101（珪素を主成分とする絶縁膜、例えば窒化珪素膜）を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行なうことができる。水素化の工程では、第1の層間絶縁膜5001に含まれる水素により半導体層のダンギングボンドが終端される。 40

**【0236】**

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い。

**【0237】**

ここで、第1の層間絶縁膜5101の存在に関係なく、半導体層を水素化することもできる。水素化の他の手段として、プラズマにより励起された水素を用いる手段（プラズマ水素化）や、3～100%の水素を含む雰囲気中において、300～450で1～12時間の加熱処理を行う手段でも良い。

**【0238】**

以上の工程により、画素の下部領域にNチャネル型TFTとPチャネル型TFTからなるCMOS回路を形成することができる。

#### 【0239】

次いで、第1の層間絶縁膜5101上に、第2の層間絶縁膜5102を形成する。第2の層間絶縁膜5102としては、無機絶縁膜を用いることができる。例えば、CVD法によって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素膜等を用いることができる。また、第2の層間絶縁膜5102として、有機絶縁膜を用いることができる。例えば、ポリイミド、ポリアミド、BCB(ベンジシクロブテン)、アクリル等の膜を用いることができる。また、アクリル膜と酸化珪素膜の積層構造を用いても良い。また、アクリル膜と、スパッタ法で形成した窒化珪素膜または窒化酸化珪素膜との積層構造を用いても良い。10

#### 【0240】

次いで、ドライエッティングまたはウェットエッティングを用い、第1の層間絶縁膜5101、第2の層間絶縁膜5102及びゲート絶縁膜5006をエッティングし、回路ブロックを構成する各TFTの不純物領域(第3の不純物領域(N+)及び第4の不純物領域(P+))に達するコンタクトホールを形成する。

#### 【0241】

次いで、各不純物領域とそれぞれ電気的に接続される配線5103～5109、6103、6104を形成する。なお本実施例では、配線5103～5109、6103、6104は、膜厚100nmのTi膜と、膜厚350nmのAl膜と、膜厚100nmのTi膜との積層膜をスパッタ法で連続形成し、所望の形状にパターニングして形成する。20

#### 【0242】

もちろん、三層構造に限らず、単層構造でもよいし、二層構造でもよいし、四層以上の積層構造にしてもよい。また配線の材料としては、AlとTiに限らず、他の導電膜を用いても良い。例えば、TaN膜上にAlやCuを形成し、さらにTi膜を形成した積層膜をパターニングして配線を形成してもよい。

#### 【0243】

次いで図5(C)に示すように、第3の層間絶縁膜5110を形成する。第3の層間絶縁膜5110としては、無機絶縁膜や有機絶縁膜を用いることができる。無機絶縁膜としては、CVD法によって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。また、アクリル膜と、スパッタ法で形成した窒化珪素膜または窒化酸化珪素膜との積層構造を用いても良い。30

#### 【0244】

第3の層間絶縁膜5110によって、基板上5000に形成されたTFTによる凹凸を緩和し、平坦化することができる。特に、第3の層間絶縁膜5110は平坦化の意味合いが強いので、平坦性に優れた膜が好ましい。

#### 【0245】

次いで、ドライエッティングまたはウェットエッティングを用い、第3の層間絶縁膜5110に、配線5108に達するコンタクトホールを形成する。40

#### 【0246】

次いで、導電膜をパターニングして画素電極5111を形成する。本実施例の場合、導電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。画素電極5111がEL素子の陰極に相当する。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を自由に用いることができる。

#### 【0247】

画素電極5111は、第3の層間絶縁膜5110に形成されたコンタクトホールによって、配線5108と電気的な接続がとられる。こうして、画素電極5111は、駆動回路を構成するTFTのソース領域またはドレイン領域の一方と、電気的に接続される。50

## 【0248】

次いで図5(D)に示すように、各画素間のEL層を塗り分けるために、土手5112を形成する。土手5112としては、無機絶縁膜や有機絶縁膜を用いて形成する。無機絶縁膜としては、スパッタ法によって形成された窒化珪素膜または窒化酸化珪素膜、CVD法によって形成された酸化珪素膜や、SOG法によって塗布された酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。

## 【0249】

ここで、土手5112を形成する際、ウエットエッチング法を用いることで容易にテーパー形状の側壁とすることが出来る。土手5112の側壁が十分になだらかでないと段差に起因するEL層の劣化が顕著な問題となってしまうため、注意が必要である。

10

## 【0250】

第3の層間絶縁膜5110と土手5112の組み合わせの例を以下に挙げる。

## 【0251】

第3の層間絶縁膜5110として、アクリルと、スパッタ法によって形成された窒化珪素膜または窒化酸化珪素膜の積層膜を用い、土手5112として、スパッタ法によって形成された窒化珪素膜または窒化酸化珪素膜を用いる組み合わせがある。第3の層間絶縁膜5110として、プラズマCVD法によって形成した酸化珪素膜を用い、土手5112としてもプラズマCVD法によって形成した酸化珪素膜を用いる組み合わせがある。また、第3の層間絶縁膜5110として、SOG法によって形成した酸化珪素膜を用い、土手5112としてもSOG法によって形成した酸化珪素膜を用いる組み合わせがある。また第3の層間絶縁膜5110として、SOG法によって形成した酸化珪素膜とプラズマCVD法によって形成した酸化珪素膜の積層膜を用い、土手5112としてプラズマCVD法によって形成した酸化珪素膜を用いる組み合わせがある。また、第3の層間絶縁膜5110として、アクリルを用い、土手5112としてもアクリルを用いる組み合わせがある。また、第3の層間絶縁膜5110として、アクリルとプラズマCVD法によって形成した酸化珪素膜の積層膜を用い、土手5112としてプラズマCVD法によって形成した酸化珪素膜を用いる組み合わせがある。また、第3の層間絶縁膜5110として、プラズマCVD法によって形成した酸化珪素膜を用い、土手5112としてアクリルを用いる組み合わせがある。

20

## 【0252】

土手5112中に、カーボン粒子や金属粒子を添加し、抵抗率を下げ、静電気の発生を抑制してもよい。この際、抵抗率は、 $1 \times 10^6 \sim 1 \times 10^{12} \text{ m}$ (好ましくは、 $1 \times 10^8 \sim 1 \times 10^{10} \text{ m}$ )となるように、カーボン粒子や金属粒子の添加量を調節すればよい。

30

## 【0253】

次いで、土手5112に囲まれた、露出している画素電極5038上に、EL層5113を形成する。

## 【0254】

EL層5113としては、公知の有機発光材料や無機発光材料を用いることができる。

## 【0255】

有機発光材料としては、低分子系有機発光材料、高分子系有機発光材料、中分子系有機材料を自由に用いることができる。なお、本明細書中においては、中分子系有機発光材料とは、昇華性を有さず、かつ、分子数が20以下または連鎖する分子の長さが $10 \mu\text{m}$ 以下の有機発光材料を示すものとする。

40

## 【0256】

EL層5113は通常、積層構造である。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層/発光層/電子輸送層」という積層構造が挙げられる。また他にも、陰極上に電子輸送層/発光層/正孔輸送層/正孔注入層、または電子注入層/電子輸送層/発光層/正孔輸送層/正孔注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。但し発光する前の電荷励起状態はトリプレットであってもシングレットであっても良い。

50

## 【0257】

また、本明細書中において、発光素子とは、一重項励起子から基底状態に遷移する際の発光（蛍光）を利用するものと、三重項励起子から基底状態に遷移する際の発光（燐光）を利用するものの両方を示す。

## 【0258】

本実施例では蒸着法により低分子系有機発光材料を用いてEL層5113を形成している。具体的には、発光層として70nm厚のトリス-8-キノリノラトアルミニウム錯体（Alq<sub>3</sub>）膜を設け、その上に、正孔注入層として20nm厚の銅フタロシアニン（CuPc）膜を設けた積層構造としている。Alq<sub>3</sub>にキナクリドン、ペリレンもしくはDCM1といった蛍光色素を添加することで発光色を制御することができる。

10

## 【0259】

なお、図5（D）では一画素しか図示していないが、複数の色、例えば、R（赤）、G（緑）、B（青）の各色に対応したEL層5113を作り分ける構成とすることができる。

## 【0260】

また、高分子系有機発光材料を用いる例として、正孔注入層として20nmのポリチオフェン（PEDOT）膜をスピンドル塗布法により設け、その上に、発光層として100nm程度のポリフェニレンビニレン（PPV）やPPVの誘導体膜を設けた積層構造によってEL層5113を構成しても良い。なお、共役系高分子であるPPVやPPVの誘導体を用いると、赤色から青色まで発光波長を選択できる。また、電子輸送層や電子注入層として炭化珪素等の無機材料を用いることも可能である。

20

## 【0261】

なお、EL層5113は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層5113は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混合した層を有する構造であってもよい。

## 【0262】

例えば、電子輸送層を構成する材料（以下、電子輸送材料と表記する）と、発光層を構成する材料（以下、発光材料と表記する）とによって構成される混合層を、電子輸送層と発光層との間に有する構造のEL層5113であってもよい。

## 【0263】

次に、EL層5113の上には、透明導電膜からなる画素電極5114を形成する。透明導電膜としては、酸化インジウムと酸化スズの化合物（ITO）、酸化インジウムと酸化亜鉛の化合物、酸化亜鉛、酸化スズ、酸化インジウム等を用いることができる。また、前記透明導電膜にガリウムを添加したもの用いてもよい。画素電極5114がEL素子の陽極に相当する。

30

## 【0264】

画素電極5114まで形成された時点でEL素子が完成する。なお、EL素子とは、画素電極（陰極）5111、EL層5113及び画素電極（陽極）5114で形成されたダイオードを指す。

## 【0265】

EL素子を完全に覆うようにして保護膜（パッシベーション膜）5115を設けることは有効である。保護膜5115としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いることができる。

40

## 【0266】

なお本実施例のように、EL素子が発した光が画素電極5114側から放射される場合、保護膜5115としては、光を透過する膜を用いる必要がある。

## 【0267】

なお、土手5112を形成した後、保護膜5115を形成するまでの工程をマルチチャンバー方式（またはオンライン方式）の成膜装置を用いて、大気開放せずに連続的に処理することは有効である。

50

## 【0268】

なお、実際には図5(D)の状態まで完成したら、さらに外気に曝されないように、気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)等のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとEL素子の信頼性が向上する。

## 【0269】

また、パッケージング等の処理により気密性を高めたら、基板500上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクタ(フレキシブルプリントサーキット:FPC)を取り付けて製品として完成する。

10

## 【0270】

なお、本実施例で作製するTFTは、ボトムゲート構造もしくは、チャネル領域の上下に絶縁膜を介して配置された2つのゲート電極を有するデュアルゲート構造としてもよい。

## 【0271】

## [実施例8]

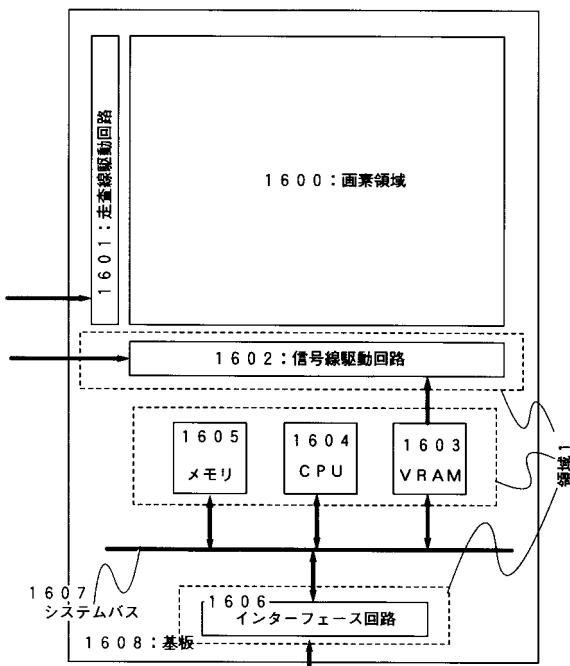

本実施例では、本発明の半導体装置の一例を、図16を用いて説明する。

## 【0272】

図16において、半導体装置は、画素領域1600、走査線駆動回路1601、信号線駆動回路1602、VRAM1603、CPU1604、メモリ1605及びインターフェース回路1606が、絶縁表面を有する基板上に一体形成されてなる。

20

## 【0273】

図16に示した半導体装置の動作について説明する。画像データや外部装置の制御信号は、インターフェース回路1606及びシステムバス1607を介して、CPU1604と外部装置との間で通信される。外部装置として、キーボードやROMなどが挙げられる。CPU1604は処理中の画像データやロジック回路の制御信号をメモリ1605に一時的に格納し、処理された画像データはVRAM1603に格納される。VRAM1603に格納された画像データは、信号線駆動回路1602および走査線駆動回路1601により、画素領域1600に表示される。

## 【0274】

なお、VRAMとは、画像データを保存するためのメモリであり、SRAMやDRAMといった揮発性メモリによって構成される。また、メモリ1605にも、SRAMやDRAMといった揮発性メモリが用いられる。インターフェース回路は、外部装置から入力された信号を一時的に保存したり、内部で用いられるフォーマットに変換したり、他の制御を行ったりする回路である。

30

## 【0275】

本実施例では、領域1に含まれる回路ブロックは特に高速動作が要求されるため、例えば実施例3乃至6に示すような、連続発振レーザを用いた半導体膜の結晶化工程を用いた高移動度のTFT作製プロセスを適用する。

## 【0276】

領域1に高移動度のTFT作製プロセスを適用することによって、領域1に含まれる回路ブロックは高速動作を実現する。

40

## 【0277】

メモリとしてSRAMを用いる場合には、読み出しサイクルとして200nsec、DRAMを用いる場合には、読み出しサイクルとして1μsec以下が実現される。

## 【0278】

また、CPUの動作周波数は5MHz以上が実現される。

## 【0279】

なお、本実施例では、領域1に高移動度TFT作製プロセスを適用したが、本発明はこれに限らない。実施者は、半導体装置の用途に応じて、任意の領域に高移動度のTFT作製プロセスを適用すればよい。

50

**【0280】**

なお、その場合には、高移動度のTFT作製プロセスを適用する面積の基板1608全体の面積に占める割合は50%以下（好ましくは30%以下）であることが好ましい。かつ、領域1はなるべく少数（好ましくは10個以下）の長方形領域で形成されることが好ましい。

**【0281】**

本実施例は、実施例1乃至7と組み合わせて用いることが可能である。

**【0282】****[実施例9]**

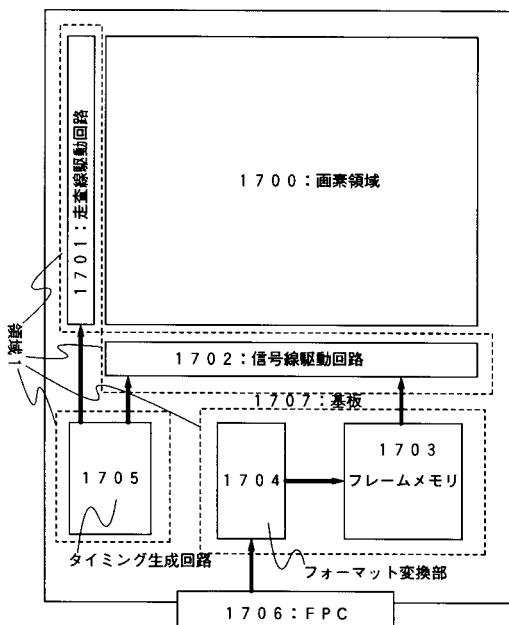

本実施例では、本発明の半導体装置の一例を、図17を用いて説明する。

10

**【0283】**

図17において、半導体装置は、画素領域1700、走査線駆動回路1701、信号線駆動回路1702、フレームメモリ1703、タイミング生成回路1705、フォーマット変換部1704が絶縁表面を有する基板上に一体形成されてなる。

**【0284】**

本実施例の構成を以下に説明する。

**【0285】**

タイミング生成回路1705で、走査線駆動回路1701及び信号線駆動回路1702の動作タイミングを決めるクロック信号を生成する。フォーマット変換部1704で、外部装置からFPC1706を介して入力される圧縮符号化された信号の伸長復号、画像の補間やリサイズなどの画像処理が行われる。フォーマット変換された画像データは、フレームメモリ1703に格納される。そして、フレームメモリ1703に格納された画像データは、走査線駆動回路1701および信号線駆動回路1702により画素1700に表示される。

20

**【0286】**

本実施例では、領域1に含まれる回路ブロックは特に高速動作が要求されるため、例えば実施例3乃至6に示すような、連続発振レーザを用いた半導体膜の結晶化工程を用いた高移動度のTFT作製プロセスを適用する。

**【0287】**

フレームメモリとしてSRAMを用いる場合には、読み出しサイクルとして200nsec、DRAMを用いる場合には、読み出しサイクルとして1μsec以下が実現される。

30

**【0288】**

本実施例において、領域1に含まれるロジック回路の駆動周波数は5MHz以上である。

**【0289】**

なお、本実施例では、領域1に高移動度TFT作製プロセスを適用したが、本発明はこれに限らない。実施者は、半導体装置の用途に応じて、任意の領域に高移動度のTFT作製プロセスを適用すればよい。

**【0290】**

なお、その場合には、高移動度のTFT作製プロセスを適用する面積の基板1608全体の面積に占める割合は50%以下（好ましくは30%以下）であることが好ましい。かつ、領域2はなるべく少数（好ましくは10個以下）の長方形領域で形成されることが好ましい。

40

**【0291】**

本実施例は、実施例1乃至7と組み合わせて用いることが可能である。

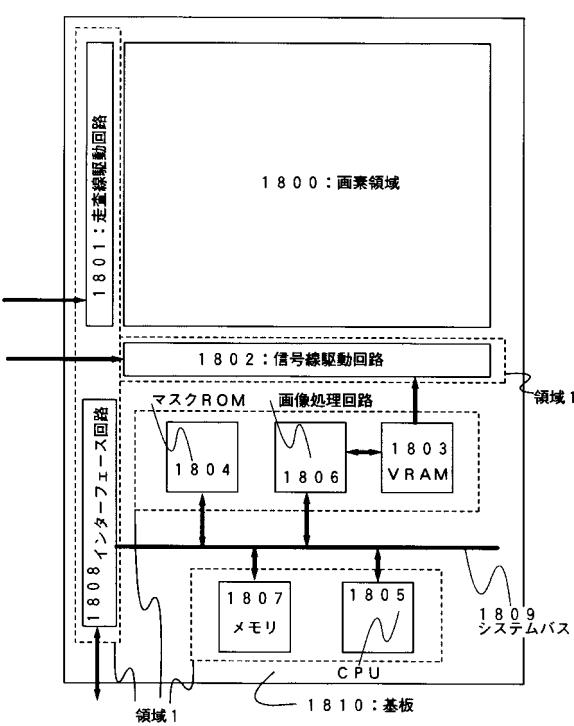

**【0292】****[実施例10]**

本実施例では、本発明の半導体装置の一例を、図18を用いて説明する。

**【0293】**

図18において、半導体装置は、画素領域1800、走査線駆動回路1801、信号線駆動回路1802、VRAM1803、マスクROM1804、演算処理回路1805、画

50

像処理回路 1806、メモリ 1807、インターフェース回路 1808 が、絶縁表面を有する基板上に一体形成されてなる。

【0294】

本実施例の構成を以下に示す。

【0295】

インターフェース回路 1808 およびシステムバス 1809 を介して、外部装置との間で制御信号が通信される。外部装置としてキーボード等が挙げられる。マスク ROM 1804 には、プログラムデータや画像データが格納されている。マスク ROM に格納されているデータは、CPU 1805 によって、メモリ 1807 との間で随時読み書きしながら処理される。画像データは画像処理回路 1806 でリサイズ等の処理が施され、VRAM 1803 に格納される。VRAM 1803 に格納されたデータは、走査線駆動回路 1801 10 及び信号線駆動回路 1802 により、画素領域 1800 に表示される。

【0296】

メモリや VRAM として、SRAM や DRAM が用いられる。

【0297】

本実施例において、画像処理回路の動作周波数は 5MHz 以上である。また、CPU の動作周波数は 5MHz 以上である。

【0298】

本実施例では、領域 1 に含まれる回路ブロックは特に高速動作が要求されるため、例えば実施例 3 乃至 6 に示すような、連続発振レーザを用いた半導体膜の結晶化工程を用いた高移動度の TFT 作製プロセスを適用する。 20

【0299】

なお、本実施例では、領域 1 に高移動度 TFT 作製プロセスを適用したが、本発明はこれに限らない。実施者は、半導体装置の用途に応じて、任意の領域に高移動度の TFT 作製プロセスを適用すればよい。

【0300】

なお、その場合には、高移動度の TFT 作製プロセスを適用する面積の基板 1608 全体の面積に占める割合は 50% 以下（好ましくは 30% 以下）であることが好ましい。かつ、領域 2 はなるべく少数（好ましくは 10 個以下）の長方形領域で形成されることが好ましい。 30

【0301】

本実施例は、実施例 1 乃至 7 と組み合わせて用いることが可能である。

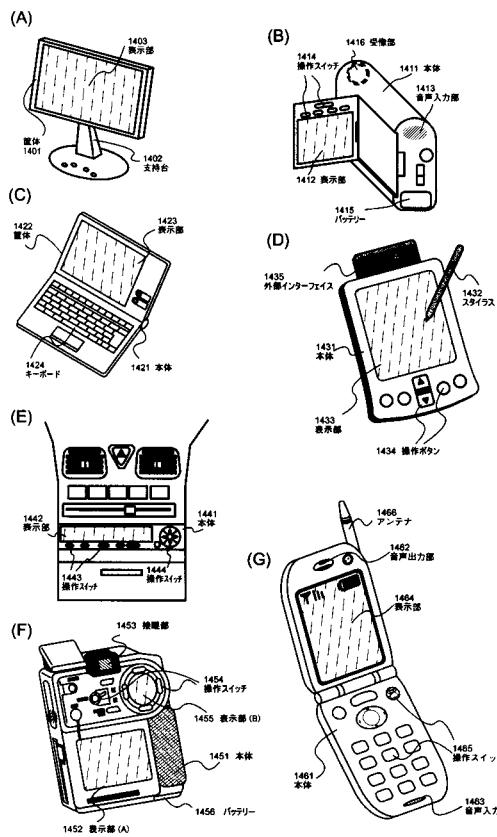

【0302】

[実施例 11]

本発明を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それらの電子機器の具体例を図 19 に示す。 40

【0303】

図 19 (A) は表示装置であり、筐体 1401、支持台 1402、表示部 1403 を含む。本発明は表示部 1403 を有する表示装置に適用が可能である。

【0304】

図 19 (B) はビデオカメラであり、本体 1411、表示部 1412、音声入力 1413、操作スイッチ 1414、バッテリー 1415、受像部 1416 などによって構成されている。本発明は表示部 1412 を有する表示装置に適用が可能である。

【0305】

図 19 (C) はノート型のパーソナルコンピュータであり、本体 1421、筐体 1422 50

、表示部 1423、キーボード 1424などによって構成されている。本発明は表示部 1423を有する表示装置に適用が可能である。

#### 【0306】

図 19 (D) は携帯情報端末であり、本体 1431、スタイルス 1432、表示部 1433、操作ボタン 1434、外部インターフェイス 1435などによって構成されている。本発明は表示部 1433を有する表示装置に適用が可能である。

#### 【0307】

図 19 (E) は音響再生装置、具体的には車載用のオーディオ装置であり、本体 1441、表示部 1442、操作スイッチ 1443、1444などによって構成されている。本発明は表示部 1442を有する表示装置に適用が可能である。また、今回は車載用オーディオ装置を例に上げたが、携帯型もしくは家庭用オーディオ装置に用いてもよい。10

#### 【0308】

図 19 (F) はデジタルカメラであり、本体 1451、表示部 (A) 1452、接眼部 1453、操作スイッチ 1454、表示部 (B) 1455、バッテリー 1456などによって構成されている。本発明は表示部 (A) 1452および表示部 (B) 1455を有する表示装置に適用が可能である。

#### 【0309】

図 19 (G) は携帯電話であり、本体 1461、音声出力部 1462、音声入力部 1463、表示部 1464、操作スイッチ 1465、アンテナ 1466などによって構成されている。本発明は表示部 1464を有する表示装置に適用が可能である。20

#### 【0310】

これらの電子機器に使われる表示装置はガラス基板だけでなく耐熱性のプラスチック基板を用いることもできる。それによってよりいっそうの軽量化を図ることができる。

#### 【0311】

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

#### 【0312】

本実施例は、実施の形態及び実施例 1 乃至実施例 7 と自由に組み合わせて実施することができる。

#### 【0313】

30

【発明の効果】

本発明では、絶縁表面を有する基板上に、高移動度を実現する TFT 作製プロセスを用いて、半導体表示部および他の回路ブロックを一体形成する。高移動度を実現する TFT 作製プロセスとして、連続発振レーザを用いた半導体活性層の結晶化工程を用いる。

#### 【0314】

その結果、小型で、ICチップ等の基板の実装に伴う信頼性を向上した、表示部を有する半導体装置が提供されると共に、

一体化による配線容量の低減と回路特性の向上により、高い動作周波数を実現する半導体装置が提供される。

#### 【0315】

40

さらに、本発明では、連続発振レーザによる結晶化プロセスを、高速動作が必要な回路ブロックのみに選択的に行うことを行つことを特徴とする。これによって、半導体装置の動作速度を落とすことなく、結晶化工程のスループットが大幅に向かう。また、ICチップ等の実装する基板の大規模な減少や高スループットの効果により、低コストの表示部を有する半導体装置が提供される。

#### 【図面の簡単な説明】

【図 1】 本発明の半導体装置を上面から見た図

【図 2】 本発明の半導体装置を上面から見た図

【図 3】 本発明の半導体装置を構成する TFT の作製工程を示した断面図

【図 4】 本発明の半導体装置を構成する TFT の作製工程を示した断面図

50

- 【図 5】 本発明の半導体装置を構成する TFT の作製工程を示した断面図

【図 6】 レーザ光を照射する際に用いる光学系の模式図

【図 7】 結晶性半導体膜の表面の SEM 像

【図 8】 結晶性半導体膜の表面の SEM 像

【図 9】 半導体膜のラマン散乱分光スペクトル

【図 10】 TFT の作製工程を示した断面図

【図 11】 TFT の電気的特性を示したグラフ

【図 12】 半導体の結晶化の工程を示した断面図

【図 13】 TFT の電気的特性を示したグラフ

【図 14】 TFT の電気的特性を示したグラフ

【図 15】 TFT の電気的特性を示したグラフ

【図 16】 本発明の半導体装置のブロック図

【図 17】 本発明の半導体装置のブロック図

【図 18】 本発明の半導体装置のブロック図

【図 19】 本発明の半導体表示部を用いた電子機器

【図 20】 レーザ光を照射する方法を示す図

【図 21】 従来の半導体装置のブロック図

【図 22】 本発明の半導体装置を上面から見た図

10

【図 1】

【図 2】

【図3】

|                       |             |                                        |

|-----------------------|-------------|----------------------------------------|

| 5000                  | : 基板        | 5015~5019, 6015, 6016: 第2の形状の導電層       |

| 5001                  | : 下地膜       | 5020~5023, 6020, 6021: 第1の不純物領域(N--領域) |

| 5002~5005, 6002, 6003 | : 半導体層      | 5025, 5028, 6025: 第2の不純物領域(N--領域)      |

| 5006                  | : ゲート絶縁膜    | 5026, 6026: 第3の不純物領域(N++領域)            |

| 5007                  | : 第1の導電層    | 5027, 5030, 6027: チャネル領域               |

| 5008                  | : 第2の導電層    | 5029: 第1の不純物領域(N--領域)                  |

| 5009, 5024            | : レジストマスク   |                                        |

| 5010~5014, 6010, 6011 | : 第1の形状の導電層 |                                        |

【図4】

|                       |                  |                         |          |

|-----------------------|------------------|-------------------------|----------|

| 5031                  | : レジストマスク        | 5044                    | : シール材   |

| 5032, 5034, 6032      | : 第4の不純物領域(P+領域) | 5045                    | : 柱状スペーサ |

| 5033, 5035, 6033      | : 第5の不純物領域(P+領域) | 5046                    | : 対向基板   |

| 5036                  | : 第1の層間絶縁膜       | 5047~5049: 着色層(カラーフィルタ) |          |

| 5037                  | : 第2の層間絶縁膜       | 5050                    | : 平坦化膜   |

| 5038~5041, 6038, 6039 | : 配線             | 5051                    | : 対向電極   |

| 5042                  | : 画素電極           | 5053                    | : 液晶     |

| 5043, 5052            | : 配向膜            |                         |          |

【図5】

|                       |            |                |

|-----------------------|------------|----------------|

| 5101                  | : 第1の層間絶縁膜 | 5112: 土手       |

| 5102                  | : 第2の層間絶縁膜 | 5113: EL層      |

| 5103~5109, 6013, 6014 | : 配線       | 5114: 画素電極(陽極) |

| 5110                  | : 第3の層間絶縁膜 | 5115: 保護膜      |

| 5111                  | : 画素電極(陰極) |                |

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(51)Int.Cl. F I

**H 01L 51/50 (2006.01)** H 05B 33/14 A

(56)参考文献 特開平07-183536 (JP, A)

特開2000-196101 (JP, A)

特開平10-065180 (JP, A)

特開2001-255560 (JP, A)

特開2000-353810 (JP, A)

特開平11-121753 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/20

H01L 21/268

H01L 21/336

H01L 51/50

G02F 1/1368