(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5806600号

(P5806600)

(45) 発行日 平成27年11月10日(2015.11.10)

(24) 登録日 平成27年9月11日(2015.9.11)

(51) Int.Cl.

F 1

H01L 29/12 (2006.01)

H01L 29/78 652T

H01L 29/78 (2006.01)

H01L 29/78 653A

H01L 21/336 (2006.01)

H01L 29/78 652K

H01L 29/78 658G

請求項の数 7 (全 14 頁)

(21) 出願番号

特願2011-253556 (P2011-253556)

(22) 出願日

平成23年11月21日(2011.11.21)

(65) 公開番号

特開2013-110238 (P2013-110238A)

(43) 公開日

平成25年6月6日(2013.6.6)

審査請求日

平成26年7月2日(2014.7.2)

(73) 特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(73) 特許権者 504143441

国立大学法人 奈良先端科学技術大学院大学

奈良県生駒市高山町8916-5

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 増田 健良

大阪市此花区島屋一丁目1番3号 住友電氣工業株式会社 大阪製作所内

(72) 発明者 畑山 智亮

奈良県生駒市高山町8916-5 国立大学法人奈良先端科学技術大学院大学内

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

厚さ方向を有し、第1の主面と前記第1の主面に対して前記厚さ方向において対向する第2の主面とを有する炭化珪素層を準備する工程を備え、

前記炭化珪素層は、前記第1の主面をなし第1の導電型を有する第1の領域と、前記第1の領域上に設けられ、前記第1の導電型と異なる第2の導電型を有する第2の領域と、前記第2の領域の上に設けられ、前記第1の導電型を有する第3の領域とを含み、さらに

前記炭化珪素層の前記第2の主面上に、開口部を有するマスクを形成する工程と、

前記マスクを用いて前記炭化珪素層をエッチングすることにより、前記炭化珪素層の前記第2の主面に、内面を有し、前記第2および第3の領域を貫通するトレンチを形成する工程とを備え、

前記トレンチを形成する工程は、前記炭化珪素層を物理的にエッチングすることにより、前記炭化珪素層の前記第2の主面に凹部を形成する工程と、前記凹部の内面に対して熱エッチングを行うことで、前記トレンチの前記内面に、前記第2の主面に対して傾斜する第1の側壁と、前記第1の側壁よりも深くに位置し前記第2の主面に対して傾斜しつつ前記第2の領域からなる部分を有する第2の側壁とを設け、かつ、前記第2の主面に対する前記第1の側壁の傾斜を、前記第2の主面に対する前記第2の側壁の傾斜に比して小さくする工程とを含み、さらに

前記トレンチの前記内面を覆うゲート絶縁膜を形成する工程と、

前記トレンチの少なくとも一部を埋めるゲート電極を形成する工程とを備える、炭化珪

素半導体装置の製造方法。

【請求項 2】

前記凹部を形成する工程は、前記凹部が前記第2の領域よりも浅くに位置するように行われる、請求項1に記載の炭化珪素半導体装置の製造方法。

【請求項 3】

前記凹部を形成する工程は、前記凹部の内面が、第1の側面と、前記第1の側面よりも深くに位置し、かつ前記第1の側面に対して傾斜した第2の側面とを含むように行われる、請求項2に記載の炭化珪素半導体装置の製造方法。

【請求項 4】

前記トレンチを形成する工程の前に、前記炭化珪素層中に前記マスクを用いてイオンを注入することにより、前記炭化珪素層中に変質層を形成する工程をさらに備え。10

前記トレンチを形成する工程は、前記炭化珪素層のうち前記変質層を含む領域を熱エッチングにより除去する工程を含む、請求項1に記載の炭化珪素半導体装置の製造方法。

【請求項 5】

前記変質層を形成する工程は、前記変質層が前記第2の領域よりも浅くに位置するように行われる、請求項4に記載の炭化珪素半導体装置の製造方法。

【請求項 6】

前記変質層を形成する工程は常温下で行われる、請求項4または請求項5に記載の炭化珪素半導体装置の製造方法。20

【請求項 7】

前記炭化珪素層を準備する工程は、前記第3の領域の結晶性が前記第2の領域の結晶性よりも低くなるように行われる、請求項1に記載の炭化珪素半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、炭化珪素半導体装置およびその製造方法に関し、より特定的には、トレンチが形成された炭化珪素層を有する炭化珪素半導体装置およびその製造方法に関する。

【背景技術】

【0002】

特開2009-188221号公報によれば、トレンチが形成された炭化珪素基板を有するMOSFET (Metal Oxide Semiconductor Field Effect Transistor) が開示されている。また高いチャネル移動度を有するMOSFETを得るために、トレンチ側壁の角度を特定の角度に制御する必要があることが開示されている。30

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009-188221号公報

【発明の概要】

【発明が解決しようとする課題】40

【0004】

しかしながら、トレンチ側壁の角度をチャネル移動度の観点で定めた場合、トレンチのアスペクト比が高くなることでトレンチ内にゲート電極を埋め込む工程が困難になることがあった。本発明は、このような課題を解決するためになされたものであり、この発明の目的は、好ましいチャネル特性と、トレンチ中へのゲート電極の埋め込みの容易性とを兼ね備えた炭化珪素半導体装置およびその製造方法を提供することである。

【課題を解決するための手段】

【0005】

本発明の炭化珪素半導体装置は、炭化珪素層と、ゲート絶縁膜と、ゲート電極とを有する。炭化珪素層は、厚さ方向を有し、第1の主面と第1の主面に対して厚さ方向において50

対向する第2の主面とを有する。また炭化珪素層は、第1の主面をなし第1の導電型を有する第1の領域と、第1の領域上に設けられ、第1の導電型と異なる第2の導電型を有する第2の領域と、第2の領域の上に設けられ、第1の導電型を有する第3の領域とを含む。炭化珪素層の第2の主面上には内面を有するトレンチが形成されている。トレンチは第2および第3の領域を貫通している。ゲート絶縁膜はトレンチの内面を覆っている。ゲート電極はトレンチの少なくとも一部を埋めている。トレンチの内面は、第1の側壁と、第1の側壁よりも深くに位置しあつ第2の領域からなる部分を有する第2の側壁とを有する。第2の主面に対する第1の側壁の傾斜は、第2の主面に対する第2の側壁の傾斜に比して小さい。

【0006】

10

上記炭化珪素半導体装置によれば、トレンチの内面は、チャネルとして機能し得る第2の領域からなる部分を有する第2の側壁を含む。この第2の側壁の、炭化珪素層の第2の主面に対する傾斜は、好ましいチャネル特性が得られるように選択され得る。第2の側壁よりも浅くに位置する第1の側壁の傾斜がより小さくされることで、トレンチの浅い部分がより大きく開口するので、トレンチ中にゲート電極をより容易に埋め込むことができる。

【0007】

好ましくは、第2の側壁は、第1および第2の領域の境界と、第2および第3の領域の境界とをつないでいる。

【0008】

20

これにより、チャネル特性上好ましい傾斜が設けられた第2の側壁からなる部分により、第1および第2の領域の間を結ぶチャネルが設けられる。このチャネルはその全体が、好ましい傾斜を有する側壁からなるので、チャネル特性をより好ましいものとすることができます。

【0009】

より好ましくは、ゲート電極は、少なくとも第1および第2の側壁の間に達するまでトレンチを埋めている。

【0010】

30

これによりゲート電極は深さ方向において第2の側壁の全体に対向するように埋められる。よって、第2の側壁からなる部分により設けられるチャネルの全体を制御することができるように、トレンチ中に十分にゲート電極が埋められる。

【0011】

本発明の炭化珪素半導体装置の製造方法は、次の工程を有する。厚さ方向を有し、第1の主面と第1の主面に対して厚さ方向において対向する第2の主面とを有する炭化珪素層が準備される。炭化珪素層は、第1の主面をなし第1の導電型を有する第1の領域と、第1の領域上に設けられ、第1の導電型と異なる第2の導電型を有する第2の領域と、第2の領域の上に設けられ、第1の導電型を有する第3の領域とを含む。炭化珪素層の第2の主面上に、開口部を有するマスクが形成される。マスクを用いて炭化珪素層をエッティングすることにより、炭化珪素層の第2の主面上に、内面を有し、第2および第3の領域を貫通するトレンチが形成される。トレンチを形成する工程は、トレンチの内面が、第1の側壁と、第1の側壁よりも深くに位置しあつ第2の領域からなる部分を有する第2の側壁とを有するように、かつ、第2の主面に対する第1の側壁の傾斜が、第2の主面に対する第2の側壁の傾斜に比して小さくなるように行われる。トレンチの内面を覆うゲート絶縁膜が形成される。トレンチの少なくとも一部を埋めるゲート電極が形成される。

40

【0012】

上記製造方法によれば、トレンチの内面は、チャネルとして機能し得る第2の領域からなる部分を有する第2の側壁を含む。この第2の側壁の、炭化珪素層の第2の主面に対する傾斜は、好ましいチャネル特性が得られるように選択され得る。第2の側壁よりも浅くに位置する第1の側壁の傾斜がより小さくされることで、トレンチの浅い部分がより大きく開口するので、トレンチ中にゲート電極をより容易に埋め込むことができる。

50

**【 0 0 1 3 】**

上記製造方法におけるトレンチを形成する工程は、次の工程を含んでもよい。炭化珪素層を物理的にエッティングすることにより、炭化珪素層の第2の主面上に凹部が形成される。凹部の内面に対して熱エッティングが行われる。

**【 0 0 1 4 】**

これにより、第2の主面に対する第1の側壁の傾斜が、第2の主面に対する第2の側壁の傾斜に比して小さくなるように、トレンチを形成することができる。

**【 0 0 1 5 】**

好ましくは、凹部を形成する工程は、凹部が第2の領域よりも浅くに位置するように行われる。

10

**【 0 0 1 6 】**

これにより、第1の側壁が過度に深く形成されることを避けることができる。よってチャネルのより多くの部分を、チャネル特性上好ましい傾斜を有する第2の側壁によってなすことができる。

**【 0 0 1 7 】**

より好ましくは、凹部を形成する工程は、凹部の内面が、第1の側面と、第1の側面よりも深くに位置し、かつ第1の側面に対して傾斜した第2の側面とを含むように行われる。

**【 0 0 1 8 】**

これにより、物理的なエッティングにより形成された第1および第2の側面のそれぞれが熱エッティングによって侵食されることで、第1および第2の側壁をより確実に形成することができる。

20

**【 0 0 1 9 】**

上記製造方法は、トレンチを形成する工程の前に、炭化珪素層中にマスクを用いてイオンを注入することにより、炭化珪素層中に変質層を形成する工程をさらに有してもよい。この場合、トレンチを形成する工程は、炭化珪素層のうち変質層を含む領域を熱エッティングにより除去する工程を含み得る。

**【 0 0 2 0 】**

これにより、炭化珪素層中に形成された変質層において熱エッティングのエッティングレートを高めることができる。よって熱エッティングの前半過程においては主に変質層のエッティングが相対的に高いレートで行われ、後半過程においては通常の炭化珪素層のエッティングが相対的に低いレートで行われる。このような2段階の過程を経ることで、互いに傾斜の程度が異なる第1および第2の側壁がより確実に形成される。

30

**【 0 0 2 1 】**

好ましくは、変質層を形成する工程は、変質層が第2の領域よりも浅くに位置するように行われる。

**【 0 0 2 2 】**

これにより、第2の側壁がより浅い位置にまで形成されるので、第2の領域のうち浅くに位置する部分にも第2の側壁を形成することができる。よって第2の領域からなるチャネルのより広い部分を、好ましい傾斜を有する側壁によってなすことができるので、チャネル特性をより好ましいものとすることができる。

40

**【 0 0 2 3 】**

好ましくは、変質層を形成する工程は常温下で行われる。

これにより、常温下でイオン注入が行われるので、高温下でイオン注入が行われる場合に比して、イオン注入の際に生じる結晶欠陥の程度がより大きくなる。この結果、変質層に対する熱エッティングのエッティングレートがより高まるので、炭化珪素層中の変質層とそれ以外の部分とのエッティングレートの差異がより大きくなる。よって、互いに傾斜の程度が異なる第1および第2の側壁がより確実に形成される。

**【 0 0 2 4 】**

上記製造方法における炭化珪素層を準備する工程は、第3の領域の結晶性が第2の領域

50

の結晶性よりも低くなるように行われてもよい。

【0025】

これにより熱エッチングにおいて、第3の領域のエッチングレートが、第2の領域のエッティングレートよりも高くなる。よって、互いに傾斜の程度が異なる第1および第2の側壁がより確実に形成される。

【発明の効果】

【0026】

上述したように本発明によれば、好ましいチャネル特性と、トレンチ中へのゲート電極の埋め込みの容易性とを両立させることができる。

【図面の簡単な説明】

10

【0027】

【図1】本発明の実施の形態1における炭化珪素半導体装置の構造を概略的に示す断面図である。

【図2】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第1工程を概略的に示す断面図である。

【図3】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第2工程を概略的に示す断面図である。

【図4】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第3工程を概略的に示す断面図である。

【図5】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第4工程を概略的に示す断面図である。

20

【図6】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第5工程を概略的に示す断面図である。

【図7】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第6工程を概略的に示す断面図である。

【図8】本発明の実施の形態1における炭化珪素半導体装置の製造方法の第7工程を概略的に示す断面図である。

【図9】図1の炭化珪素半導体装置の構造の第1の変形例を概略的に示す断面図である。

【図10】図1の炭化珪素半導体装置の構造の第2の変形例を概略的に示す断面図である。

30

【図11】本発明の実施の形態2における炭化珪素半導体装置の製造方法の第1工程を概略的に示す断面図である。

【図12】本発明の実施の形態2における炭化珪素半導体装置の製造方法の第2工程を概略的に示す断面図である。

【図13】本発明の実施の形態3における炭化珪素半導体装置の製造方法の第1工程を概略的に示す断面図である。

【図14】本発明の実施の形態3における炭化珪素半導体装置の製造方法の第2工程を概略的に示す断面図である。

【発明を実施するための形態】

【0028】

40

以下、図面に基づいて本発明の実施の形態について説明する。なお、以下の図面において同一または相当する部分には同一の参照番号を付しその説明は繰返さない。また、本明細書中における結晶学的説明においては、個別方位を[ ]、集合方位を<>、個別面を( )、集合面を{}でそれぞれ示している。また、負の指数については、結晶学上、"-"(バー)を数字の上に付けることになっているが、本明細書中では、数字の前に負の符号を付けている。

【0029】

(実施の形態1)

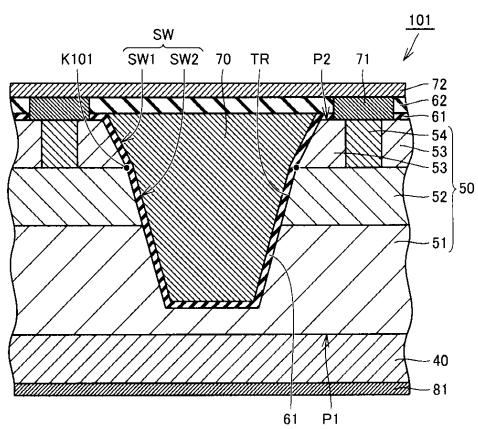

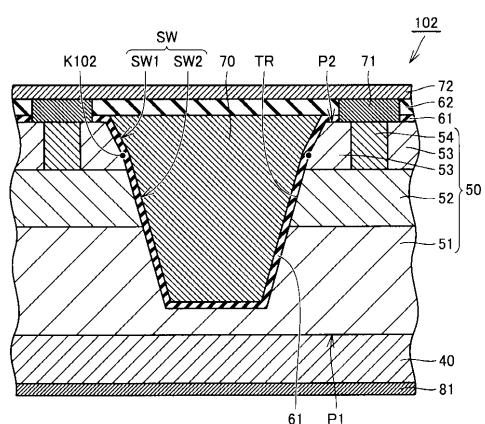

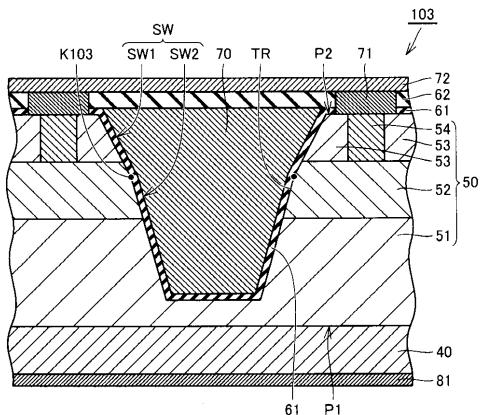

図1に示すように、本実施の形態の炭化珪素半導体装置としてのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)

50

sistor) 101は、基板40と、エピタキシャル層(炭化珪素層)50と、ゲート絶縁膜61と、層間絶縁膜62と、ゲート電極70と、ソース電極71と、ソース配線電極72と、ドレイン電極81とを有する。

#### 【0030】

基板40は、n型(第1の導電型)の半導体、または導体から作られており、好ましくは単結晶炭化珪素基板である。基板40の一方側の上にはドレイン電極81が設けられており、他方側の上にはエピタキシャル層50が設けられている。ドレイン電極81はオーミック電極である。

#### 【0031】

エピタキシャル層50は、厚さ方向(図中、縦方向)を有し、基板40に面する下面(第1の正面)P1と、下面P1に対して厚さ方向において対向する上面(第2の正面)P2とを有する。エピタキシャル層50の結晶構造が六方晶の場合、上面P2の面方位は好ましくは、実質的に{000-1}面であり、より好ましくは、実質的に(000-1)面である。またその結晶構造が立方晶の場合、上面P2の面方位は好ましくは、実質的に{111}面である。エピタキシャル層50は、第1～第3の領域51～53と、コンタクト領域54とを有する。第1の領域51は、下面P1をなしており、n型を有する。第2の領域52は、第1の領域51上に設けられており、n型とは異なる導電型すなわちp型(第2の導電型)を有する。第3の領域53は、第2の領域52の上に設けられており、n型を有する。コンタクト領域54は、p型を有し、第2の領域52とソース電極71とをつないでいる。

10

20

#### 【0032】

エピタキシャル層50の上面P2上には、内面を有するトレンチTRが形成されている。トレンチTRは、第2および第3の領域52、53を貫通している。トレンチTRの内面は、側壁SWを有する。側壁SWは、上部側壁(第1の側壁)SW1と、上部側壁SW1よりも深くに位置しあつ第2の領域52からなる部分を有する下部側壁SW2(第2の側壁)とを有する。上面P2に対する上部側壁SW1の傾斜は、上面P2に対する下部側壁SW2の傾斜に比して小さい。エピタキシャル層50の結晶構造が六方晶の場合、下部側壁SW2の結晶面は、好ましくは、実質的に{0-33-8}面または{01-1-4}面となっている。またその結晶構造が立方晶である場合、下部側壁SW2の結晶面は、好ましくは、実質的に{100}面となっている。下部側壁SW2は、第1および第2の領域51、52の境界と、第2および第3の領域52、53の境界とをつないでいる。トレンチTRの内面上における上部側壁SW1および下部側壁SW2の間の屈曲点K101は、第2および第3の領域52、53の境界に位置している。

30

#### 【0033】

ゲート絶縁膜61はトレンチTRの内面を覆っている。ゲート電極70はトレンチTRの少なくとも一部を埋めている。また本実施の形態においては、ゲート電極70は、少なくとも上部側壁SW1および下部側壁SW2の間に達するまでトレンチTRを埋めている。すなわちゲート電極70は少なくとも屈曲点K101に達するまで埋め込まれており、本実施の形態においては、ゲート電極70は屈曲点K101を越えて埋め込まれている。

40

#### 【0034】

ソース電極71は、第3の領域53およびコンタクト領域54の各々に接するように配置されたオーミック電極である。ソース配線電極72は、ソース電極71上に配置されている。ソース配線電極72は、層間絶縁膜62によってゲート電極70と電気的に絶縁されている。

#### 【0035】

次にMOSFET101(図1)の製造方法について説明する。

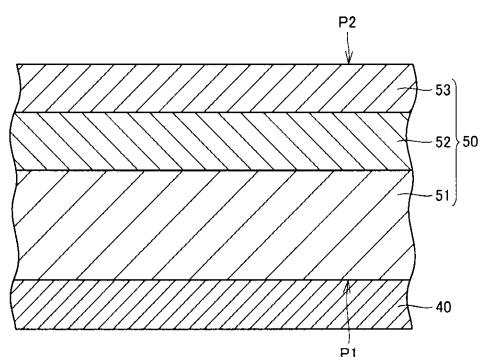

図2に示すように、基板40上にn型のエピタキシャル層50が形成される。このためのエピタキシャル成長は、たとえば原料ガスとしてシラン(SiH<sub>4</sub>)とプロパン(C<sub>3</sub>H<sub>8</sub>)との混合ガスを用い、キャリアガスとしてたとえば水素ガス(H<sub>2</sub>)を用いたCVD法により実施することができる。またエピタキシャル成長の際に、n型を付与するための導

50

電型不純物としてたとえば窒素( N )またはリン( P )を導入することが好ましい。エピタキシャル層 50 のこの n 型不純物の濃度は、たとえば  $5 \times 10^{15} \text{ cm}^{-3}$  以上  $5 \times 10^{16} \text{ cm}^{-3}$  以下である。

#### 【 0036 】

図 3 に示すように、エピタキシャル層 50 上への不純物イオンの注入によって、エピタキシャル層 50 中に第 1 ~ 第 3 の領域 51 ~ 53 が形成される。第 2 の領域 52 を形成するためのイオン注入においては、たとえばアルミニウム( A1 )が用いられる。第 3 の領域 53 を形成するためのイオン注入においては、たとえばリン( P )が用いられる。イオンの加速エネルギーを調整することにより、第 2 および第 3 の領域 52 、 53 の各々が形成される領域の深さは調整される。

10

#### 【 0037 】

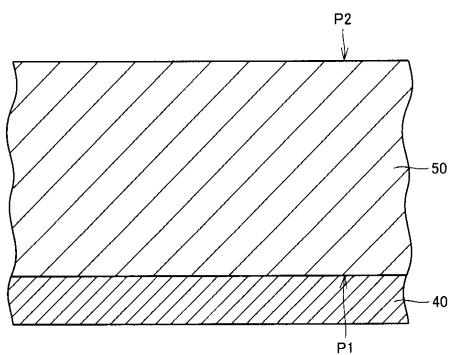

図 4 に示すように、エピタキシャル層 50 の上面 P2 上にマスク 90 が形成される。好ましくはマスク 90 の形成は堆積法によって行われる。ここで堆積法とは、形成される膜の材料のすべてが外部から供給されることを特徴とする方法である。よって堆積法は、熱酸化法、すなわち、膜が形成されることになる領域に既に存在していた元素を材料の一部として利用する方法を含まない。堆積法としては、たとえば、 CVD ( Chemical Vapor Deposition ) 法、スパッタ法、または抵抗加熱型蒸着法を用いることができる。

#### 【 0038 】

図 5 に示すように、マスク 90 に開口部が形成される。開口部の形成は、たとえば、フォトリソグラフィおよびエッチングを用いて行い得る。開口部の幅は、たとえば  $0.1 \mu\text{m}$  以上  $2 \mu\text{m}$  以下である。次にマスク 90 を用いてエピタキシャル層 50 をエッチングすることにより、エピタキシャル層 50 の上面 P2 上に、内面を有し、第 2 および第 3 の領域 53 を貫通するトレンチ TR ( 図 1 ) が形成される。トレンチ TR を形成する工程は、トレンチ TR の内面が、上部側壁 SW1 と、上部側壁 SW1 よりも深くに位置しつつ第 2 の領域 52 からなる部分を有する下部側壁 SW2 とを有するように、かつ、上面 P2 に対する上部側壁 SW1 の傾斜が、上面 P2 に対する下部側壁 SW2 の傾斜に比して小さくなるよう行われる。以下、このエッチング工程について説明する。

20

#### 【 0039 】

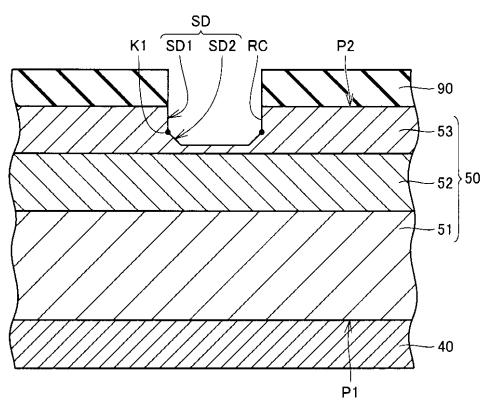

図 6 および図 7 に示すように、エピタキシャル層 50 を物理的にエッチングすることにより、エピタキシャル層 50 の上面 P2 上に凹部 RC が形成される。本実施の形態においては、凹部 RC は、図 7 に示すように、第 2 の領域 52 よりも浅くに位置するように形成される。また凹部 RC は、その側面 SD が、上部側面( 第 1 の側面 ) SD1 と、上部側面 SD1 よりも深くに位置し、かつ上部側面 SD1 に対して傾斜した下部側面( 第 2 の側面 ) SD2 とを含むように形成される。これにより、上部側面 SD1 および下部側面 SD2 の間に屈曲点 K1 が設けられる。

30

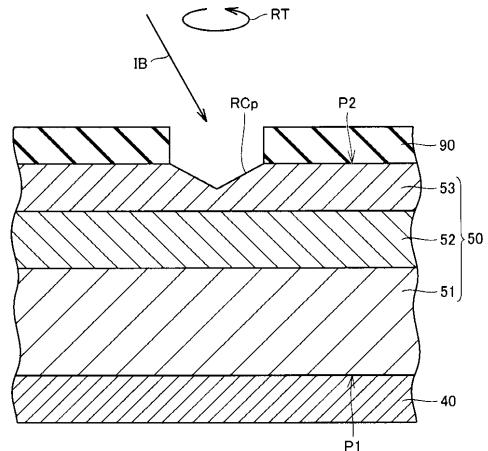

#### 【 0040 】

具体的には、まず、矢印 RT ( 図 6 ) に示すように上面 P2 を面内回転させながら、上面 P2 に対して傾いた入射角を有するイオンビーム IB を用いたイオンビームエッチングが行われる。このイオンビームエッチングにより上面 P2 上に凹部 RCp が形成される。凹部 RCp は、上面 P2 に対して傾いた内面を有する。次に、イオンビーム IB の入射角が上面 P2 に対してより垂直に近いものとされたイオンビームエッチング、または RIE ( Reactive Ion Etching ) が行われることで、図 7 に示すように、エピタキシャル層 50 の上面 P2 上に凹部( RC ) が形成される。RIE としては、たとえば、反応ガスとして SF<sub>6</sub> または SF<sub>6</sub> と O<sub>2</sub> との混合ガスを用いた ICP - RIE ( Induction Coupled Plasma - RIE ) を用いることができる。

40

#### 【 0041 】

次に凹部 RC の内面に対して熱エッチングが行われる。具体的には、炭化珪素層に、反応ガスを含有するプロセスガスに接触させながら炭化珪素層を加熱する処理が行われる。反応性ガスとしては、塩素系ガスを用いることができ、たとえば塩素ガスを用いることが

50

できる。またプロセスガス中に酸素原子を含有するガスが混ぜられてもよく、たとえば酸素ガスが混ぜられてもよい。またプロセスガスは、窒素ガス、アルゴンガス、またはヘリウムガスなどのキャリアガスを含んでもよい。熱エッティングにおける熱処理温度は、好ましくは700以上1200以下とされる。熱処理温度を700以上とすることで、SiCのエッティング速度 $70 \mu\text{m/h}$ 程度を確保し得る。下限温度は、より好ましくは800以上とされ、さらに好ましくは900以上とされる。上限温度は、より好ましくは1100以下とされ、さらに好ましくは1000以下とされる。また、この場合にマスク90の材料として酸化珪素、窒化珪素、酸化アルミニウム、窒化アルミニウム、または窒化ガリウムを用いると、マスク90の材料に対するSiCのエッティング選択比を極めて大きくすることができるので、SiCのエッティング中のマスク90の消耗を抑制することができる。

#### 【0042】

図8に示すように、上記の熱エッティングにより、トレンチTRが形成される。なおこの熱エッティングの進行にともなって、屈曲点K1(図7)が徐々に移動して屈曲点K101に至る。次にマスク90が、たとえばエッティングにより除去される。

#### 【0043】

再び図1を参照して、上面P2の一部の上への選択的なイオン注入によって、コンタクト領域54が形成される。次にエピタキシャル層50中の不純物イオンを活性化するためのアニールが行われる。次にエピタキシャル層50のトレンチTRの内面および上面P2を覆うゲート絶縁膜61が形成される。ゲート絶縁膜61は、好ましくは酸化珪素膜である。酸化珪素膜は、たとえばエピタキシャル層50を熱酸化することによって形成され得る。

#### 【0044】

次にトレンチTRの少なくとも一部を埋めるゲート電極70が形成される。この形成は、たとえば、ゲート電極70となる材料を堆積した後にCMP(Chemical Mechanical Polishing)を行うことで行い得る。次に、層間絶縁膜62、ソース電極71、およびソース配線電極72が形成される。これにより、図1に示すMOSFET101が得られる。

#### 【0045】

本実施の形態によれば、トレンチTRの内面は、MOSFET101のチャネルとして機能し得る第2の領域52からなる部分を有する下部側壁SW2を含む。この下部側壁SW2の、エピタキシャル層50の上面P2に対する傾斜は、好ましいチャネル特性が得られるように選択され得る。一方で、下部側壁SW2よりも浅くに位置する上部側壁SW1の傾斜がより小さくされることで、トレンチTRの深い部分がより大きく開口するので、トレンチTR中にゲート電極70をより容易に埋め込むことができる。

#### 【0046】

下部側壁SW2は、第1および第2の領域51、52の境界と、第2および第3の領域52、53の境界とをつないでいる。これにより、チャネル特性上好ましい傾斜が設けられた下部側壁SW2からなる部分により、第1および第2の領域51、52の間を結ぶチャネルが設けられる。このチャネルはその全体が、好ましい傾斜を有する側壁からなるので、チャネル特性をより好ましいものとすることができます。

#### 【0047】

ゲート電極70は、少なくとも上部側壁SW1および下部側壁SW2の間に達するまでトレンチTRを埋めている。これによりゲート電極70は深さ方向において下部側壁SW2の全体に対向するように埋められる。よって、下部側壁SW2からなる部分により設けられるチャネルの全体を制御することができるよう、トレンチTR中に十分にゲート電極70が埋められる。

#### 【0048】

エピタキシャル層50を物理的にエッティングすることにより、エピタキシャル層50の上面P2上に凹部RCが形成される。凹部RCの内面に対して熱エッティングが行われる。

10

20

30

40

50

これによりより確実に、上面 P 2 に対する上部側壁 S W 1 の傾斜が、上面 P 2 に対する下部側壁 S W 2 の傾斜に比して小さくなるように、トレント R を形成することができる。

#### 【 0 0 4 9 】

凹部が第 2 の領域 5 2 よりも浅くに位置するように形成される。これにより、上部側壁 S W 1 が過度に深く形成されることを避けることができる。よってチャネルのより多くの部分を、チャネル特性上好ましい傾斜を有する下部側壁 S W 2 によってなすことができる。

#### 【 0 0 5 0 】

凹部 R C を形成する工程は、凹部の内面が、上部側面 S D 1 と、上部側面 S D 1 よりも深くに位置し、かつ上部側面 S D 1 に対して傾斜した下部側面 S D 2 を含むように行われる。これにより、物理的なエッチングにより形成された上部側面 S D 1 および下部側面 S D 2 のそれぞれが熱エッチングによって侵食されることで、上部側壁 S W 1 および下部側壁 S W 2 をより確実に形成することができる。10

#### 【 0 0 5 1 】

次に M O S F E T 1 0 1 の 2 つの変形例について説明する。

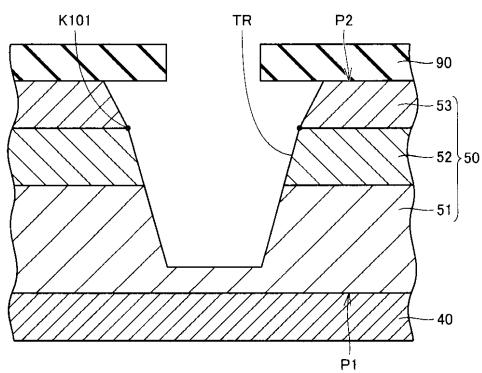

図 9 に示すように、M O S F E T 1 0 2 においては、トレント R の内面上における上部側壁 S W 1 および下部側壁 S W 2 の間の屈曲点 K 1 0 2 は、第 2 および第 3 の領域 5 2 、5 3 の境界から離れて第 3 の領域 5 3 上に位置している。この変形例によれば、工程ばらつきによって屈曲点 K 1 0 2 の位置がばらついても、下部側壁 S W 2 が、第 1 および第 2 の領域 5 1 、5 2 の境界と、第 2 および第 3 の領域 5 2 、5 3 の境界とをより確実につなぐことができる。20

#### 【 0 0 5 2 】

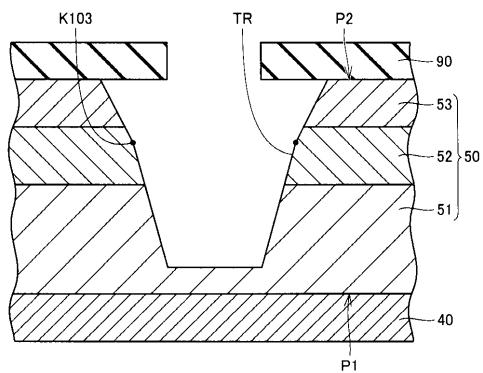

図 1 0 に示すように、M O S F E T 1 0 3 においては、トレント R の内面上における上部側壁 S W 1 および下部側壁 S W 2 の間の屈曲点 K 1 0 3 は、第 2 および第 3 の領域 5 2 、5 3 の境界から離れて第 2 の領域 5 2 上に位置している。この変形例によれば、トレント R の深い部分がより大きく開口するので、トレント R 中にゲート電極 7 0 をより容易に埋め込むことができる。

#### 【 0 0 5 3 】

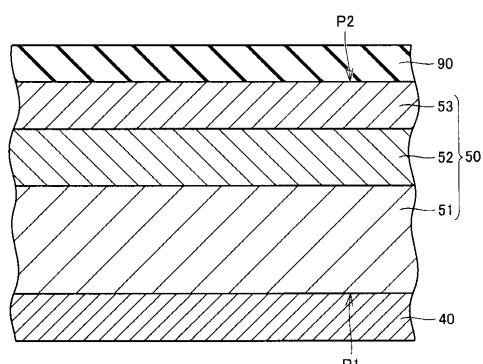

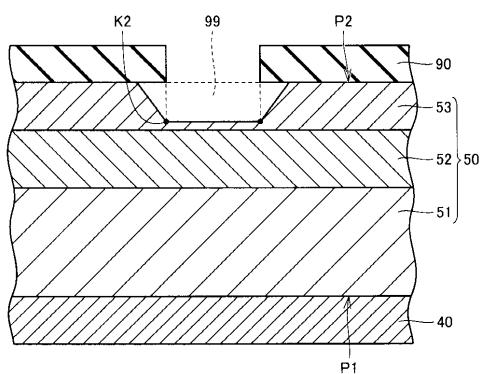

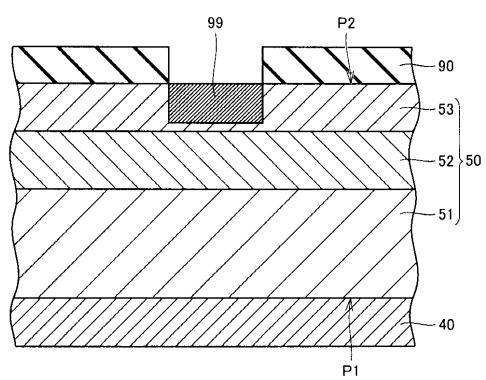

##### ( 実施の形態 2 )

本実施の形態においては、まず実施の形態 1 における図 5 までと同様の工程が行われる。次に図 1 1 に示すように、エピタキシャル層 5 0 中にマスク 9 0 を用いてイオンを注入することにより、エピタキシャル層 5 0 中に変質層 9 9 が形成される。好ましくは、変質層 9 9 を形成する工程は、変質層 9 9 が第 2 の領域 5 2 よりも浅くに位置するように行われる。好ましくは、変質層 9 9 を形成する工程は常温下で行われる。次に実施の形態 1 と同様の熱エッチングが行われる。この場合、熱エッチングの前半過程において、図 1 2 に示すように、エピタキシャル層 5 0 のうち変質層 9 9 を含む領域が除去される。これにより形成される凹部は、屈曲点 K 2 を有する。なおこれ以外の工程は実施の形態 1 とほぼ同様であるためその説明を省略する。30

#### 【 0 0 5 4 】

本実施の形態によれば、トレント R を形成する工程の前に、エピタキシャル層 5 0 中にマスク 9 0 を用いてイオンを注入することにより、エピタキシャル層 5 0 中に変質層 9 9 が形成される。この結果、トレント R を形成する工程は、エピタキシャル層 5 0 のうち変質層 9 9 を含む領域を熱エッチングにより除去する工程を含む。これにより、エピタキシャル層 5 0 中に形成された変質層 9 9 において熱エッチングのエッチングレートを高めることができる。よって熱エッチングの前半過程においては主に変質層 9 9 のエッチングが相対的に高いレートで行われ、屈曲点 K 2 ( 図 1 2 ) が形成される。後半過程においては通常のエピタキシャル層 5 0 のエッチングが相対的に低いレートで行われ、熱エッチングの進行にともなって、屈曲点 K 2 ( 図 1 2 ) が徐々に移動して屈曲点 K 1 0 1 ~ K 1 0 3 ( 図 1 、図 9 、図 1 0 ) のいずれかに至る。これにより上部側壁 S W 1 および下部側壁 S W 2 がより確実に形成される。40

**【 0 0 5 5 】**

屈曲点 K 1 0 1 ~ K 1 0 3 のいずれが得られるかは、変質層 9 9 の厚さによって調整され得る。屈曲点 K 1 0 1 または K 1 0 2 を得るには、図 1 1 に示すように、変質層 9 9 の厚さは第 3 の領域 5 3 の厚さよりも小さくされる。言い換えれば、変質層 9 9 を形成する工程が、変質層 9 9 が第 2 の領域 5 2 よりも浅くに位置するように行われる。これにより、下部側壁 S W 2 がより浅い位置にまで形成されるので、第 2 の領域 5 2 うち浅くに位置する部分にも下部側壁 S W 2 を形成することができる。よって第 2 の領域 5 2 からなるチャネルのより広い部分を、好ましい傾斜を有する側壁によってなすことができるので、チャネル特性をより好ましいものとすることができます。

**【 0 0 5 6 】**

10

変質層 9 9 を形成するためのイオン注入が常温下で行われると、高温下の場合に比して、イオン注入の際に生じる結晶欠陥の程度がより大きくなる。この結果、変質層 9 9 に対する熱エッティングのエッティングレートがより高まるので、エピタキシャル層 5 0 中の変質層 9 9 とそれ以外の部分とのエッティングレートの差異がより大きくなる。よって、互いに傾斜の程度が異なる上部側壁 S W 1 および下部側壁 S W 2 がより確実に形成される。

**【 0 0 5 7 】**

20

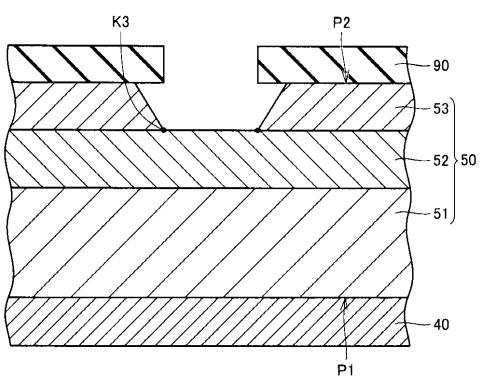

**( 実施の形態 3 )**

本実施の形態においては、実施の形態 1 における第 3 の領域 5 3 を形成するためのイオン注入（図 3）において、結晶欠陥が特に生じやすいような方法が選択される。たとえば、第 3 の領域 5 3 を形成するためのイオン注入が常温下で行われる。この結果、第 3 の領域 5 3 の結晶性は、第 2 の領域 5 2 の結晶性に比して十分に低くなる。その後、実施の形態 1 における図 5 までと同様の工程が行われる。次に実施の形態 1 と同様の熱エッティングが行われる。この場合、熱エッティングの前半過程において、図 1 3 に示すように、エピタキシャル層 5 0 のうち第 3 の領域 5 3 が除去される。これにより形成される凹部は、屈曲点 K 3 を有する。そして熱エッティングの後半工程を経て、たとえば図 1 4 に示すように、トレンチ T R が形成される。なおこれ以外の工程は実施の形態 1 とほぼ同様であるためその説明を省略する。

**【 0 0 5 8 】**

30

本実施の形態によれば、エピタキシャル層 5 0 を準備する工程は、第 3 の領域 5 3 の結晶性が第 2 の領域 5 2 の結晶性よりも十分に低くなるように行われる。これにより熱エッティングにおいて、第 3 の領域 5 3 のエッティングレートが、第 2 の領域 5 2 のエッティングレートよりも高くなる。よって熱エッティングの前半過程においては第 3 の領域 5 3 のエッティングが相対的に高いレートで行われ、屈曲点 K 3（図 1 3）が形成される。後半過程においてはエピタキシャル層 5 0 の第 2 の領域 5 2 および第 1 の領域 5 1 のエッティングが相対的に低いレートで行われ、熱エッティングの進行にともなって、屈曲点 K 3（図 1 3）が徐々に移動して屈曲点 K 1 0 1 ~ K 1 0 3 のいずれか（図 1、図 9、図 1 0）に至る。これにより、上部側壁 S W 1 および下部側壁 S W 2 が形成される。これにより上部側壁 S W 1 および下部側壁 S W 2 がより確実に形成される。

**【 0 0 5 9 】**

40

なお上記各実施の形態においては M O S F E T について特に説明したが、炭化珪素半導体装置は M O S F E T 以外の M I S F E T (Metal Insulator Semiconductor Field Effect Transistor) であってもよい。また炭化珪素半導体装置は M I S F E T 以外のものであってもよく、たとえば I G B T (Insulated Gate Bipolar Transistor) であってもよい。

**【 0 0 6 0 】**

また上記各実施の形態における n 型と p 型とが入れ替えられた形態が用いられてもよい。

**【 0 0 6 1 】**

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えら

50

れるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

**【符号の説明】**

**【0062】**

40 基板、50 エピタキシャル層、51～53 第1～第3の領域、54 コンタクト領域、61 ゲート絶縁膜、62 層間絶縁膜、70 ゲート電極、71 ソース電極、72 ソース配線電極、81 ドレイン電極、90 マスク、99 変質層、P1 下面(第1の正面)、P2 上面(第2の正面)、R C 凹部、S W 側壁、S W 1 上部側壁(第1の側壁)、S W 2 下部側壁(第2の側壁)、T R トレンチ。

10

**【図1】**

**【図3】**

**【図2】**

**【図4】**

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図12】

【図11】

【図13】

【図14】

---

フロントページの続き

審査官 棚田 一也

(56)参考文献 特開2010-182857(JP,A)

特開2002-141407(JP,A)

特開2007-165657(JP,A)

特開2007-258465(JP,A)

特開2000-068505(JP,A)

特開2006-196523(JP,A)

特開2007-227649(JP,A)

特開平10-154809(JP,A)

特開平11-031815(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/12

H01L 21/336

H01L 29/78