(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0008405

(43) 공개일자 2009년01월21일

(51) Int. Cl.<sup>9</sup>

H05K 1/02 (2006.01) H05K 9/00 (2006.01)

(21) 출원번호 10-2008-7028721

(22) 출원일자 2008년11월24일

심사청구일자 없음

번역문제출일자 2008년11월24일

(86) 국제출원번호 PCT/US2007/010009

국제출원일자 2007년04월26일

(87) 국제공개번호 WO 2007/133405

국제공개일자 2007년11월22일

(30) 우선권주장

11/739,550 2007년04월24일 미국(US)

(뒷면에 계속)

(71) 출원인

멀티-파인라인 일렉트로닉스, 인크.

미합중국 92806 캘리포니아 애너하임 이스트 코로나도 스트리트 3140-에이

(72) 발명자

웨셀만, 데일

미국 92870 캘리포니아, 플라체티아, 리베라 팔래스 169

탭 스코트, 찰스 이.

미국 92897 캘리포니아, 애너하임, 이스트 선크레스트 로드 5468

(74) 대리인

특허법인무한

전체 청구항 수 : 총 38 항

#### (54) 차폐된 가요성 회로 및 이의 제조 방법

#### (57) 요 약

서로 근접한 복수개의 차폐된 전기전도체를 갖는 차폐된 가요성 케이블로서, 상기 복수개의 차폐된 전기 회로의 하나로 전송된 신호가 상기 복수개의 차폐된 전기 전도체의 다른 것으로 전송된 신호와 실질적으로 간섭하지 않으며, 폴리아미드 지지부재로서, 상기 폴리아미드 지지부재의 제 1면의 복수개의 에칭된 구리 트레이스와, 상기 폴리아미드 지지부재의 제 2면의 구리층을 지지하고; 상기 폴리아미드 지지부재는 적어도 하나의 축을 따라서 가요성이며; 상기 복수개의 에칭된 구리 전도체와 상기 구리층은 실질적으로 상기 지지부재와 같은 정도로 가요성이 있으며; 예를 들면, 은 잉크 또는 은 필름과 같은 은 베이스 물질로서, 상기 복수개의 구리 트레이스의 각각의 전체 길이를 따라 상기 구리 트레이스의 각각의 부분을 둘러싸며; 상기 은 베이스 물질은 상기 지지부재의 불연속을 통해 (i)상기 폴리아미드 지지부재의 불연속을 통해 상기 구리층과, (ii)접지된 말단부와 전기적으로 연결되고; 전기적으로 절연성 물질로서, 상기 복수개의 구리 트레이스와 실질적으로 근접하여, (i)상기 복수개의 구리 트레이스의 다른 트레이스와, (ii)상기 은 베이스 물질로부터 상기 복수개의 구리 트레이스의 각각을 전기적으로 절연하며; 상기 전기적으로 절연성 물질은 상기 은 베이스 물질과 상기 복수개의 구리 트레이스 사이에 물리적으로 위치하며; 상기 은 베이스 물질의 노출된 전체 표면을 실질적으로 커버하는 제1 유전층; 및 상기 구리층의 노출된 전체 표면을 실질적으로 커버하는 제 2 유전층으로 구성된다.

**대 표 도** - 도1H

(30) 우선권주장

60/796,716 2006년05월02일 미국(US)

60/811,927 2006년06월08일 미국(US)

---

## 특허청구의 범위

### 청구항 1

서로 근접한 복수개의 차폐된 전기전도체를 갖는 차폐된 가요성 회로로서,

상기 복수개의 차폐된 전기 회로의 하나로 전송된 신호가 상기 복수개의 차폐된 전기 전도체의 다른 것으로 전송된 신호와 실질적으로 간섭하지 않으며,

지지부재로서, 상기 지지부재의 제 1면의 복수개의 에칭된 구리 트레이스와, 상기 지지부재의 제 2면의 구리층을 지지하고, 상기 트레이스의 적어도 몇개는 상기 전기 전도체로서 작용하는 지지부재;

상기 지지부재는 적어도 하나의 축을 따라서 가요성이며;

상기 복수개의 에칭된 구리 전도체와 상기 구리층은 실질적으로 상기 지지부재와 같은 정도로 가요성이 있으며;

상기 복수개의 구리 트레이스의 각각에 실질적으로 근접한 전기적으로 절연성인 물질로서, 상기 전기 전도체들의 각각을 전기적으로 절연하기 위한 전기 전도체로서 작용하며;

상기 전기적 절연 물질, 상기 에칭된 구리 전도체의 각각의 부분을 실질적으로 상기 복수개의 구리 트레이스의 각각의 전체 길이를 따라 둘러싸는 부분에 대한 차폐;

상기 지지부재, 상기 전도성 차폐와, 상기 구리층에서 불연속을 통해 상기 구리층과 전기적으로 연결된 상기 전도성 차폐는 전기 전도체로서 작용하는 상기 에칭된 구리 트레이스 각각에 실질적으로 360도 전기 차폐를 제공하고;

상기 전기적으로 절연성 물질은 상기 전도성 차폐와, 전기적 전도체로서 작용하는 상기 복수개의 구리 트레이스의 각각의 사이에 물질적으로 위치하며;

상기 전도성 차폐의 노출된 전체 표면을 실질적으로 커버하는 제1 유전층; 및

상기 구리층의 노출된 전체 표면을 실질적으로 커버하는 제 2 유전층으로 구성되는 것인 차폐된 가요성 회로.

### 청구항 2

제 1 항에 있어서,

상기 전도성 차폐는:

상기 전기 전도체로 작용하지 않는 교대로 에칭된 구리 트레이스; 및

상기 전도성 차폐가 (i) 상기 구리층, (ii)전기 전도체로서 작용하는 각각의 트레이스의 각각의 사이드에 위치하는 각각의 트레이스, 및 (iii)전도성 물질 상기 에칭된 구리 트레이스의 각각의 둘레에 360도 전도성 차폐를 제공하는 불연속으로 구성되는 것인 차폐된 가요성 회로.

### 청구항 3

제1항에 있어서,

상기 모든 에칭된 구리 트레이스는 전기 전도체로서 작용하고, 상기 가요성 회로는,

상기 복수개의 절연된 구리 트레이스의 각각의 사이의 틈(interstices) 및

(i)상기 구리층, (ii)상기 구리 트레이스에 대한 전도성 물질층, 및 (iii)상기 틈(interstices) 에서의 전도성 물질을 포함하는 상기 전도성 차폐층으로 구성되는 것인 차폐된 가요성 회로.

### 청구항 4

제 3항에 있어서,

상기 틈(interstices)은 채널인 것인 차폐된 가요성 회로.

### 청구항 5

제 4항에 있어서,

상기 채널은 상기 지지 부재에 위치하는 것인 차폐된 가요성 회로.

#### 청구항 6

제 1항에 있어서,

상기 지지 부재는 비-전도성 가요성 물질로 만들어지는 것인 차폐된 가요성 회로.

#### 청구항 7

제 1항에 있어서,

상기 가요성 지지부재는 폴리이미드 필름인 것인 차폐된 가요성 회로.

#### 청구항 8

제 1항에 있어서,

상기 전도성 차폐는 은 베이스 물질을 포함하는 것인 차폐된 가요성 회로.

#### 청구항 9

서로 근접한 복수개의 차폐된 전기 회로를 갖는 차폐된 가요성 케이블로서,

상기 복수개의 차폐된 전기 회로의 하나로 전송된 신호가 상기 복수개의 차폐된 전기 전도체의 다른 것으로 전송된 신호와 실질적으로 간섭하지 않으며:

폴리이미드 지지부재로서, 상기 폴리이미드 지지부재의 제 1면의 복수개의 에칭된 구리 트레이스와, 상기 폴리이미드 지지부재의 제 2면의 구리층을 지지하고;

상기 폴리이미드 지지부재는 적어도 하나의 축을 따라서 가요성이며;

상기 복수개의 에칭된 구리 트레이스와 상기 구리층은 실질적으로 상기 폴리이미드 지지부재와 같은 정도로 가요성이 있으며;

예를 들면, 은 잉크 또는 은 필름과 같은 은 베이스 물질로서, 상기 복수개의 구리 트레이스의 각각의 전체 길이를 따라 상기 구리 트레이스의 각각의 부분을 둘러싸며;

상기 은 베이스 물질은 상기 지지부재의 불연속을 통해 (i)상기 지지부재, (ii)접지된 말단부와 전기적으로 연결되고;

전기적으로 절연성 물질로서, 상기 복수개의 구리 트레이스와 실질적으로 근접하여, (i)상기 복수개의 구리 트레이스와, (ii)상기 은 베이스 물질로부터 상기 복수개의 구리 트레이스의 각각을 전기적으로 절연하며;

상기 전기적으로 절연성 물질은 상기 은 베이스 물질과 상기 복수개의 구리 트레이스 사이에 물리적으로 위치하며;

상기 은 베이스 물질의 노출된 전체 표면을 실질적으로 커버하는 제1 유전층; 및

상기 구리층의 노출된 전체 표면을 실질적으로 커버하는 제 2 유전층으로 구성되는 것인 차폐된 가요성 케이블.

#### 청구항 10

복수개의 차폐된 전기 전도체를 갖는 차폐된 가요성 케이블로서,

각각의 전도체는 각각의 전도체의 실질적으로 전체 길이를 따라 상기 전도체를 실질적으로 둘러싸는 가요성 전도성 차폐를 가지며;

금속성 전도층을 지지하는 유전 물질의 가요성 쉬트로서, 상기 쉬트와 금속층은 상기 가요성 전도체의 전체를 지지하는 길이와 폭을 가지며;

복수개의 분리된 비-전도성 가요성 필름으로서, 상기 금속성 전도층에 부착되며;

상기 가요성 전도체는 상기 가요성 필름에서 각각 지지하고;

상기 가요성 전도체의 상기 노출된 부분을 각각 커버하는 분리된 유전 부재로서, 상기 유전 부재와 상기 비-전도성 필름은 상기 가요성 전도체의 각각을 전기적으로 완전히 절연하며;

가요성 전도성 물질로서 (i)상기 절연된 전도체의 각각의 사이의 틈을 채우고, (ii)상기 금속성 전도층과 직접 전기적으로 연결되어, 상기 전도성 물질과 상기 금속성 전도층에 의해 형성된 전기적으로 전도성 차폐에 의해, 상기 복수의 전도체의 각각이 그 길이를 따라서 실질적으로 둘러싸이며;

상기 전도성 물질의 상기 노출된 전체 표면을 실질적으로 커버하는 제 1 가요성 절연층과 상기 금속층의 노출된 전체 표면을 실질적으로 커버하는 제 2 가요성 절연층으로 구성되는 것인 차폐된 가요성 케이블.

### 청구항 11

신호 수신부와 셀룰라 폰의 디스플레이부를 기계적 헌지를 가로 질러 연결하기 위한 가요성 케이블로서:

(i)상기 복수개의 전도체의 제1 말단부에서 상기 수신부와 전기적으로 연결되고, (ii)상기 복수개의 전도체의 제2 말단부에서 상기 디스플레이브와 연결되는 복수개의 전도체;

상기 기판의 제1 면에서 상기 복수개의 전도체와 상기 기판의 제2면에서 전도층을 지지하는 가요성 비-전도성 기판;

상기 복수개의 전도체의 각각의 부분을 상기 복수개의 전도체의 각각의 전체 길이를 따라서 실질적으로 둘러싸는 전도성 물질;

상기 전도성 물질은, 상기 가요성 비-전도 기판의 불연속을 통해 상기 전도층과 전기적으로 연결되며;

상기 복수개의 전도체의 부분을 상기 복수개의 전도체의 각각의 실질적으로 전체 길이를 따라서 실질적으로 둘러싸는 비-전도성 물질; 및

상기 전도층으로부터의 상기 복수개의 전도체의 각각을 전기적으로 절연하는 상기 비-전도성 물질로 구성되는 가요성 케이블.

### 청구항 12

차폐된 가요성 회로로서

가요성 지지부재;

상기 가요성 지지부재의 제1 면과 연결된 제1 전도체, 제2 전도체, 및 제3 전도체;

상기 제2 전도체는 상기 제1 전도체와 제3 전도체 사이에 위치하고, 상기 제1 전도체와 제3 전도체로부터 전기적으로 절연되며;

상기 가요성 지지부재와 연결된 제1 비-전도층으로서, 상기 제1 전도층은 상기 제1 전도체와 연결되며;

상기 제1 비-전도층, 상기 제1 전도체와 상기 제3 전도체와 연결된 상기 제1 전도층과 연결된 제1 전도층;

상기 가요성 지지부재의 제2 면과 연결되고, 상기 제1 전도체 및 제 3 전도체와 연결되고, 상기 제2 전도체로부터 전기적으로 절연되는 제2 전도층으로 구성되는 차폐된 가요성 회로.

### 청구항 13

차폐된 가요성 회로로서,

가요성 지지부재;

상기 가요성 지지부재의 제1 면과 연결되는 전도체;

상기 전도체와 연결되는 제1 비-전도층;

상기 제1 비-전도층은 상기 가요 부재와 상기 전도체와 연결되며;

상기 제1 비-전도층과 연결되는 제1 전도층;

상기 가요성 지지부재의 제2 면과 연결되고, 상기 전도층은 상기 제1 전도층과 연결되고 상기 전도층으로부터 전기적으로 절연되는 것으로 구성되는 차폐된 가요성 회로.

#### 청구항 14

제13항에 있어서,

상기 가요성 지지부재는 채널로 구성되며, 상기 채널은 상기 제1, 제2 전도층이 서로 연결되는 것을 허용하는 것인 차폐된 가요성 회로.

#### 청구항 15

차폐된 가요성 회로로서,

가요성 지지부재;

상기 가요성 지지부재의 제1 면과 연결되는 전도체;

상기 전도체와 연결되는 제1 비-전도층, 상기 제1 비-전도층은 상기 가요성 지지 부재와 상기 전도체와 연결되며;

상기 제1 비-전도층과 연결되는 제1 전도층;

상기 가요성 지지부재의 제2 면과 연결되는 제2 전도층; 및

상기 제1, 제2 전도층과 연결되고 상기 전도체로부터 전기적으로 절연되는 제3 전도층을 포함하는 차폐된 가요성 회로.

#### 청구항 16

제 12항의 차폐된 가요성 회로에 있어서,

상기 가요성 지지부재는 채널을 포함하며, 상기 채널의 전도성 물질은 상기 제1, 제2 및 제3의 전도층을 서로 전기적으로 연결시키는 것인 차폐된 가요성 회로.

#### 청구항 17

차폐된 가요성 회로로서,

가요성 지지부재;

상기 가요성 지지부재와 연결되는 제1 전도체와 제2 전도체;

상기 제1, 제2 전도체는 서로 전기적으로 절연되고;

상기 제1 전도체의 주변에 동축으로 배치되고, 상기 제1 전도체로부터 전기적으로 절연되는 제1 전도성 물질; 및

상기 제2 전도체의 주변에 동축으로 배치되고, 상기 제2 전도체로부터 전기적으로 절연되는 제2 전도성 물질로 구성되는 차폐된 가요성 회로.

#### 청구항 18

제17항에 있어서,

상기 제1, 제2 전도체는 2 GHz 이상의 속도로 데이터를 전송하는 것이 가능한 차폐된 가요성 회로.

#### 청구항 19

제17항에 있어서,

상기 제1 전도체의 중심과 상기 제2 전도체의 중심간의 거리는 2만분의 1 인치 이하인 것인 차폐된 가요성 회로.

#### 청구항 20

차폐된 회로를 제조하는 방법으로서,

가요성 지지부재의 제1 면에 부착된 전도성 물질로부터 제1 전도체, 제2 전도체, 제3 전도체를 형성하고, 상기 제2 전도체는 상기 제1, 제3 전도체 사이에 위치하며, 상기 제1, 제3 전도체로부터 전기적으로 절연되는 단계;

제1 비-전도층을 상기 가요성 지지부재의 제1면에 부착하고, 상기 제1 비-전도층은 상기 제1 전도체와 접촉하는 단계;

제1 전도층을 상기 제1 비-전도층에 부착하고, 상기 제1 전도층은 상기 제1, 제3 전도층과 연결되는 것인 단계; 및

제2 전도층을 상기 가요성 지지부재의 제2 면에 부착하고, 상기 제2 전도층은 상기 제1, 제3 전도층과 연결되며, 상기 제2 전도체로부터 전기적으로 절연되는 것인 단계로 구성되는 차폐된 회로를 제조하는 방법.

### **청구항 21**

제20항에 있어서,

상기 제1, 제2, 및 제3 전도체를 형성하는 단계는 구리 트레이스를 예칭하는 것을 포함하는 것인 차폐된 회로를 제조하는 방법.

### **청구항 22**

제20항에 있어서,

상기 가요성 지지 부재는 폴리이미드 필름인 것인 차폐된 회로를 제조하는 방법.

### **청구항 23**

제20항에 있어서,

상기 제1, 제3 전도체는 전기적으로 접지된 것인 차폐된 회로를 제조하는 방법.

### **청구항 24**

제20항에 있어서,

상기 제1 전도층은 은 베이스 물질인 것인 차폐된 회로를 제조하는 방법.

### **청구항 25**

제20항에 있어서,

상기 제1 전도층은 전도성 부분과 비-전도성 부분으로 구성되는 것인 차폐된 회로를 제조하는 방법.

### **청구항 26**

제20항에 있어서,

상기 제2 전도층은 은 베이스 물질인 것인 차폐된 회로를 제조하는 방법.

### **청구항 27**

제20항에 있어서,

상기 제2 전도층은 전도성 부분과 비-전도성 부분으로 구성되는 것인 차폐된 회로를 제조하는 방법.

### **청구항 28**

제20항에 있어서,

상기 가요성 지지부재에서 채널을 형성하고, 상기 채널은 상기 제1, 제3 전도체와 상기 제1, 제2 도전층이 서로 연결되도록 하는 것인 차폐된 회로를 제조하는 방법.

### **청구항 29**

차폐된 회로를 제조하는 방법으로서, 상기 방법은

제1 전도층에 부착된 제2 사이드로 구성되는 가요성 지지부재의 제1 면에 부착된 전도성 물질로부터 전도성 물질을 형성하는 단계;

제1 비-전도층을 상기 전도체와 상기 지지부재에 부착하는 단계; 및

상기 제1 전도층과 연결되고 상기 전도체로부터 전기적으로 절연된 제2 전도층을 상기 제1 비-전도층에 부착하는 단계로 구성되는 것인 차폐된 회로를 제조하는 방법.

### 청구항 30

차폐된 회로를 제조하는 방법으로서, 상기 방법은

제1 전도층에 부착된 제2 사이드로 구성되는 가요성 지지부재의 제1 면에 부착된 전도성 물질로부터 전도체를 형성하는 단계;

상기 전도체와 상기 가요성 지지부재에 제1 비-전도층을 부착하는 단계

상기 제1 비-전도층에 제2 도전층을 부착하는 단계; 및

상기 제1, 제2 전도층과 연결되며, 상기 전도체로부터 전기적으로 절연된 제3 전도층을 배치하는 단계로 구성되는 차폐된 회로를 제조하는 방법.

### 청구항 31

차폐된 회로를 제조하는 방법으로서, 상기 방법은

가요성 부재의 제1면에 부착된 제1 전도성 물질로부터, 서로 전기적으로 절연된 제1, 제2 전도체를 형성하는 단계;

상기 제1 전도체의 주변에 동축상으로 배치되고, 상기 제1 전도체로부터 전기적으로 절연된, 제2 도전성 물질을 형성하는 단계;

상기 제2 전도체의 주변에 동축상으로 배치되고, 상기 제2 전도체로부터 전기적으로 절연된, 제3 도전성 물질을 형성하는 단계로 구성되는 차폐된 회로를 제조하는 방법.

### 청구항 32

제31항에 있어서,

상기 제1, 제2 도전체를 형성하는 단계는 구리 트레이스를 에칭하는 것을 포함하는 차폐된 회로를 제조하는 방법.

### 청구항 33

제31항에 있어서,

상기 가요성 지지부재는 폴리이미드 필름인 것인 차폐된 회로를 제조하는 방법.

### 청구항 34

제31항에 있어서,

상기 제1 전도성 물질과 상기 제1 전도체 사이, 상기 제2 전도성 물질과 상기 제2 전도체 사이에 각각 동축적으로 배치된 제1, 제2 비-전도층을 적층하는 단계를 더 포함하는 차폐된 회로를 제조하는 방법.

### 청구항 35

제31항에 있어서,

상기 제2, 제3 전도성 물질은 서로 연결되어 있는 것인 차폐된 회로를 제조하는 방법.

### 청구항 36

제31항에 있어서,

상기 제2, 제3 전도성 물질은 은 베이스 물질인 것인 차폐된 회로를 제조하는 방법.

### 청구항 37

제31항에 있어서,

상기 제1, 제3 전도체는 2 Ghz 이상의 속도로 데이터를 전송하는 것이 가능한 것인 차폐된 회로를 제조하는 방법.

### 청구항 38

제31항에 있어서,

상기 제1 전도체의 중심과 상기 제2 전도체의 중심사이의 거리는 1인치의 2만분의 일 이하인 것인 차폐된 회로를 제조하는 방법.

## 명세서

### 기술 분야

&lt;1&gt;

본 발명은 (i)2006년 5이월 2일 출원된 미합중국 가출원 출원번호 60/796,716, (ii)2006년 6월 8일 출원된 미합중국 가출원 출원번호 60/811,927 의 이익을 가진다. 상기 가출원 출원번호 60/796,716 과 가출원 출원번호 60/811,927 의 전체 내용은 본 출원에서 참조로 사용되었다.

&lt;2&gt;

본 출원은 일반적으로 가요성 전기 회로에 관한 것이며, 더욱 상세하게는 가요성 부재에 지지되는 차폐된 전기 회로를 위한 방법과 장치에 관한 것이다.

### 배경 기술

&lt;3&gt;

이동 통신 장치의 등장은 무선 디지털 신호 전송(wireless digital signal transmission)을 통해 개인이 서로 통신하는 것을 가능하게 했다. 더욱더, 개인들은 이동 통신 장치에 의존하게 되고, 또한, WWW, 컴퓨터, 컴퓨터 네트워크 등을 통해서 서로 데이터를 전달하게 되었다. 개인들은, 고품질 디지털 오디오, 디지털 비디오, 스트리밍 디지털 비디오(streaming digital video), 사진 이미지, 컴퓨터 파일 등의, 여러 형태의 데이터를 전송하기 위해, 이동 통신 장치를 사용한다.

&lt;4&gt;

따라서, 이러한 형태의 데이터 전송을 뒷받침하는 장치들은, 이동 통신 장치의 디자인과 조화를 이루게 되며, 이러한 장치들은, 예를 들면, 메가 픽셀 카메라(megapixel cameras), 비디오 카메라, 및, 디지털 오디오 레코더들을 포함한다. 더구나, 많은 상업적으로 사용되는 셀룰러폰과 개인 휴대 정보 단말기(personal digital assistant devices)는, 대량의 데이터 파일을 생성하고, 활용하고, 통신하는 전형적인 컴퓨터 기반 활용 프로그램을 동작시키는 것이 가능하다. 결과적으로, 이 분야에서는 대량의 데이터를 빠른 속도로 전송하기 위한 이동 통신 장치가 필요하다.

&lt;5&gt;

이동 통신 장치를 포함하는, 많은 전자 장치들이, 라디오 주파수 스펙트럼(radio frequency spectrum)에서 전자 기장(electromagnetic fields)을 발생시킨다. 특히, 도전로(conductive path)를 따라 전기적 신호를 전송하는 것이 전자기장(electromagnetic fields)을 발생시킨다. 전송 주파수(transmission frequencies)가 증가함에 따라, 대응하는 전자기장(electromagnetic fields)의 크기와 유효 공간 리치(effectice spatial reach)도 따라서 증가한다. 두개의 물리적으로 연결되지 않는 도전로(conductive path)가 서로 가까이 있을 경우, 하나의 도전로(conductive path)에 의한 고주파수 전송(high frequency transmission)이, 다른 하나의 도전로(conductive path)를 따르는 전송에 대하여 전자파 장애(electromagnetic interference,EMI)를 일으킨다. 전자파 장애(electromagnetic interference,EMI)는 이동 통신 장치의 작동에 여러가지 해로운 영향을 줄 수 있다. 예를 들면, 전자파 장애(electromagnetic interference,EMI)는 전송된 데이터의 일그러짐(distortion) 및 데이터의 전체적 손실도 일으킬 수 있다.

&lt;6&gt;

고속 전송 속도 때문에, 이동 통신 장치들은, 전자파 장애(electromagnetic interference,EMI)에 영향을 받지 않는 전도체(conductor)를 필요로 하게 된다. 특히, 스크린이 회전하는 힌지(hinge)를 통해 폰의 몸체와 연결되는 플립폰, 및 스크린이 평행하게 슬라이딩하는 기계적 콘넥터(connector)에 의해 폰의 몸체와 연결된 슬라이

더 폰은, 회전하는 힌지 또는 기계적 커넥터를 통해 데이터를 전송하기 위해 가요성 전도체(flexible conductor)를 필요로 하게 된다. 따라서, 고 주파수 전송 과정에서 발생하는 전자파 장애(electromagnetic interference,EMI)를 차폐할 수 있는 가요성 전도체(flexible conductor)에 대한 필요가 있다.

<7> 전자파 장애(electromagnetic interference,EMI)를 차폐하는 것에 대한 종래 기술에서 잘 알려진 것은 동축 케이블(coaxial cables)이다. 동축 케이블은 공통축(common axis)의 주변에 배치된 전도체(conductor)의 쌍으로 구성된다. 제 1 전도체(conductor)는 케이블의 중심축을 따라서 놓여지고, 전송된 신호를 전달한다. 제 2 전도체(conductor)는, 전기적으로 접지(electrical ground)되어, 절연체 또는 유전체(dielectric) 물질에 의해, 상기 제1 전도체의 주변에 원통형으로 배치된다. 상기 제1 전도체를 상기 제 2 전도체로 차폐함으로써, 동축 케이블은 상기 전도체에 의해 만들어진 전자기장을, 케이블 내부의 면적으로 제한할 수 있다. 따라서, 동축 케이블은 텔레비전 및 브로드밴드 전송(broadband transmission)을 위해 널리 사용되고 있다.

<8> 차폐된 가요성 회로를 위해 본 출원에서 개시하고 있는 상기 장치와 방법은, 가요성 회로에서 근접하게 위치한 전도체를 따른 고속도 데이터 전송을 가능하게 한다. 상기 장치와 방법은 플립폰 및 슬라이더 폰에서 사용되기에 적절하다. 또한, 데이터 전송 속도가 1 GHz 를 넘는 경우, EMI에 대항한 전도성 트레이스(conductive traces)를 차폐하는 것이 가능하다. 결과적으로, 몇몇 실시예에서는, 실질적인 신호 손실 또는 일그러짐(distortion) 없이, 셀폰(cell phone)이, 스트리밍 비디오 및 다른 고속도 어플리케이션을 위해 필요한 속도로 데이터를 전송하는 것이 가능하다. 다른 실시예에서, 차폐된 가요성 회로들은 2 내지 4 GHz 의 속도로 데이터를 전송하는 것이 가능하다.

<9> 일 실시예에서, 장치는 가요성 지지 부재(a flexible support member); 상기 가요성 지지부재와 접하고 있는 제 1 전도체 및 제 2 전도체; 상기 제1 및 제2 전도체는 서로 전기적으로 절연되어 있으며; 제1 전도성 물질은 동축상으로 상기 제1 전도체의 주변에 배치되어 있고, 상기 제1 전도성 물질은 상기 제1 전도체와 전기적으로 절연되어 있고; 제2 전도성 물질은 상기 제2 전도체의 주변에 동축상으로 배치되어 있고, 상기 제2 전도성 물질은 상기 제2 전도체와 전기적으로 절연되어 있다.

<10> 다른 일 실시예에서, 가요성 회로를 차폐하는 방법은, 가요성 지지 부재의 상부에 부착된 제1 전도 물질로부터 제1 전도체와 제2 전도체를 형성하고, 상기 제1 전도체와 제 2 전도체는 서로 전기적으로 절연되어 있으며; 상기 제1 전도체의 주변에 동축상으로 배치된 제2 전도 물질을 형성하고, 상기 제2 전도 물질은 상기 제1 전도체와 전기적으로 절연되어 있으며; 상기 제2 전도체의 주변에 동축상으로 배치된 제3 전도성 물질을 형성하고, 상기 제3 전도 물질은 상기 제 2 전도체와 전기적으로 절연되어 있는 것으로 구성된다.

<11> 이러한 목적을 위해, 본원 발명의 몇몇 일면, 장점 및 새로운 구성요소들이 개시되어 있다. 본 발명의 어떤 실시예에서 이러한 모든 장점들이 발현될 필요가 없다는 것은 알 수 있다. 따라서, 예를 들어, 당업자는 여기서 제시되거나 암시되는 다른 장점들에 대해 반드시 실현할 필요 없이, 하나의 장점 또는 몇몇의 장점을 실현하는 방법으로 실현된다는 것을 알 수 있다.

### 발명의 상세한 설명

<12> 도 1 내지 도 9를 참조하여, 본 발명의 다양한 실시예와 하나의 실시예의 예시적 적용을 나타내는 장치와 방법이 설명될 것이다. 장치에 대한 변형과 다른 실시예를 나타내는 방법들이 또한 설명될 것이다.

<13> 설명을 위하여, 몇몇 실시예들은 이동 통신 장치 및/또는 이동 전화로 설명될 것이다. 여기 개시된 발명은 장치나 방법들이 사용된 문맥에 의해서 제한되지 않으며, 장치와 방법들은 다른 환경에서도 사용될 수 있다. 또한, 여기서 설명된 특별한 제한(implementation)은 설명하기 위한 것이며, 제한하기 위한 것은 아니다. 본 발명의 범위는 청구범위에 의해서만 정의된다.

<14> 이러한 특징들은 도면을 참조하여 설명된다. 도면과 그에 따른 설명들은 본 발명을 설명하기 위한 것이고, 본 발명의 범위를 제한하지 않는다. 도면을 통해서, 동일한 참조 부호는 같은 요소를 설명하기 위해 사용된다.

<15> I. 개요 (Overview)

<16> 본 발명의 장치와 방법은 가요성 지지 부재(a flexible support member)의 활성 신호 트레이스(active signal traces)를 차폐하는 것에 관한 것이다.

<17> 일 실시예에서, 차폐된 가요성 회로는, 상부의 가요성 비-전도성 기판(flexible non-conductive substrate)과 바닥부의 구리층으로 구성되는 베이스 가요성 물질을 사용해서 만들어진다. 이러한 실시예들에서, 교대의 트

레이스(alternate trace)는 구리층에 접하고, 이들 사이의 트레이스를 차폐하기 위해 사용된다. 참조를 쉽게 하기 위해, 이러한 타입의 실시예들은, 이하에서 "교대로 접지된 트레이스에 의한 구리 단층 차폐" ("Single-Copper Layer Shielding With Alternate Grounded Traces") 실시예라고 한다.

- <18> 다른 실시예에서, 차폐된 가요성 회로는 상부가 가요성 기판으로, 바닥부에 구리층으로 구성된 베이스 물질을 사용해서 만들어진다. 이러한 실시예들에서, 실질적으로 모든 트레이스가 활성 신호 트레이스(active signal traces)로서 사용될 수 있다. 참조를 쉽게 하기 위해, 이러한 타입의 실시예들은, 이하에서 "모든 트레이스가 차폐된 구리 단층" ("Single Copper Layer With All Traces Shielded") 실시예라고 한다.

- <19> 또 다른 실시예에서, 차폐된 가요성 회로는 상부에 구리층을 포함하고, 바닥부에 구리층을 갖는 가요성 기판(flexible substrate)으로 구성된 베이스 물질을 사용해서 만들어진다. 참조를 쉽게 하기 위해, 이러한 타입의 실시예들은, 이하에서 "두개의 구리층" ("Two Copper Layer") 실시예라고 한다.

- <20> 또 다른 실시예에서, 차폐된 가요성 회로는, 상부에 구리층을 포함하고, 바닥부에 구리층을 포함하는 가요성 기판으로 구성된 베이스 물질을 사용해서 만들어진다. 이러한 실시예들에서, 구리는 모든 면에서 구리 트레이스를 차폐하기 위해 사용될 수 있다. 참조를 쉽게 하기 위해, 이러한 타입의 실시예들은, 이하에서 "세개의 구리층" ("Three Copper Layer") 실시예라고 한다.

- <21> 추가적으로, 상기, 아래, 상부 및 바닥부라는 용어는 상세한 설명을 통해서 사용된다. 이러한 용어들이 한정하는 것으로 되어서는 안된다. 이러한 용어들은 적용할 수 있는 도면의 상대적인 방향에 따라 사용된다. 또한, "공정도"는 단지 발명의 일 실시예에 대한 것이다. 여기서 설명된 발명들은, 공정도에서 설명된 순서에 따라 제한되어서는 안될 것이다. 순서들은, 당업자들에게 적절하다고 생각되는 어떠한 순서로도 수행될 수 있다는 것을 알 수 있다.

## 실 시 예

- <49> II. 교대로 접지된 트레이스에 의한 구리 단층 차폐(Single Copper Layer Shielding With Alternate Grounded Traces) 실시

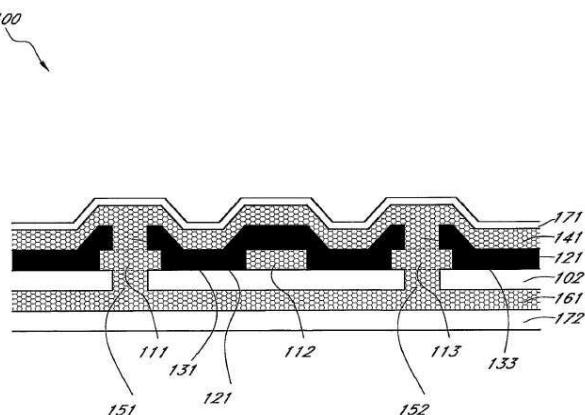

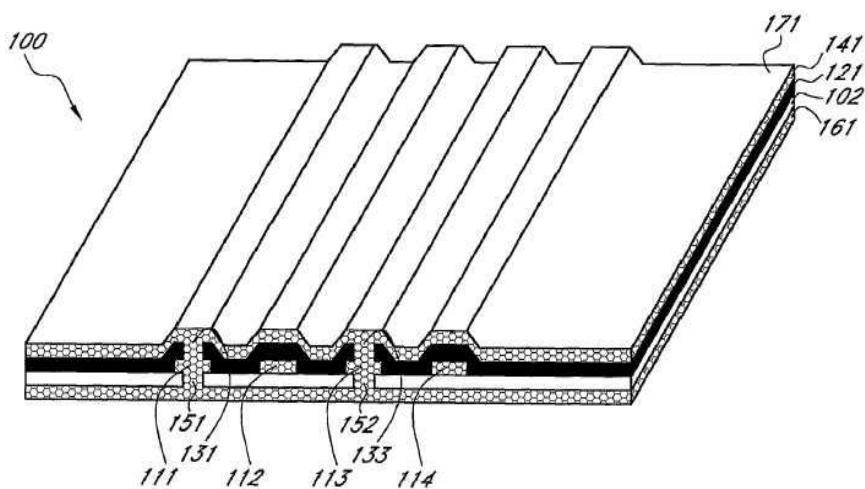

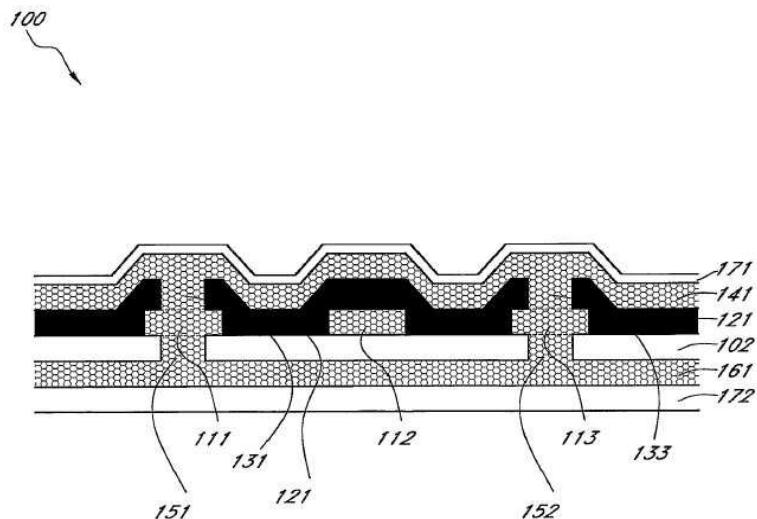

- <50> 도 1H는 교대로 접지된 트레이스에 의한 구리 단층 차폐(Single Copper Layer Shielding With Alternate Grounded Traces)의 일 실시예를 나타낸다. 도 2는, 차폐된 가요성 회로를 제조하기 위한, 스텝 501-508 을 포함하는 공정도를 나타내며, 도 1A 내지 1H 는 상기 방법의 각각의 단계가 실행됨에 따른 상기 차폐된 가요성 회로의 구조를 나타낸다. 여기서 설명하는 바와 같이, 방법의 각각의 단계에서의 회로의 구조와 연관되어 있는 도면들이 참조될 것이다. 이와는 대조적으로, 도 2의 방법의 각각의 스텝은 도 2 만의 참조 번호를 사용하여 참조될 것이다.

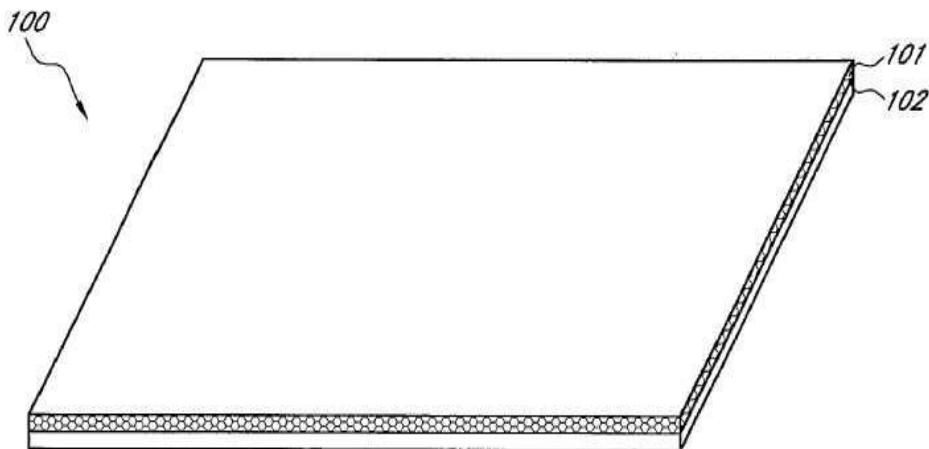

- <51> 이러한 실시예에서, 차폐된 가요성 회로를 제조하기 위한 방법은 도 1A 에도시된 가요성 지지 부재 100 으로 시작된다. 상기 가요성 지지 부재 100은, 가요성 기판 102와 베이스 전도층 101의 두개의 층으로 구성된다. 당업자들에게 가요성 지지 부재 100은 상업적으로 만들어지며 쉽게 구입이 가능하다고 알려져 있다. 다른 실시예들에서, 상기 방법은, 상기 베이스 전도층 101을 상기 가요성 기판 102에, 플레이팅, 라미네이팅, 증기 증착(vapor deposition) 또는 알려진 기술들을 사용해서, 부착시키는 것으로 시작된다.

- <52> 바람직한 실시예에서, 상기 가요성 기판 102는 폴리이미드(polyimide)로 만들어진다. 다른 실시예에서, 상기 가요성 기판 102는 일반적으로 사용되는 "FLEX" 또는 FR4, PET/PEN, Teflon/high speed materials 등등의 인쇄회로기판(printed circuit board, "PCB") 물질들 중 하나 일 수 있다.

- <53> 바람직한 실시예에서, 상기 베이스 전도층 101 은 구리층이다. 다른 실시예에서, 베이스 전도층 101 은, 금 또는 은과 같은, 전기적으로 전도성 물질일 수 있다. 다른 물질들이 사용될 수 있지만, 여기서 상기 베이스 전도층 101 은 구리 베이스 전도층 101로 불리울 것이다.

- <54> 전통적인 PCB 제조 방법은 상기 가요성 지지 부재 100에 툴링 홀(tooling holes) 또는 바이아스(vias)를 만들기 위해서 사용될 수 있다.

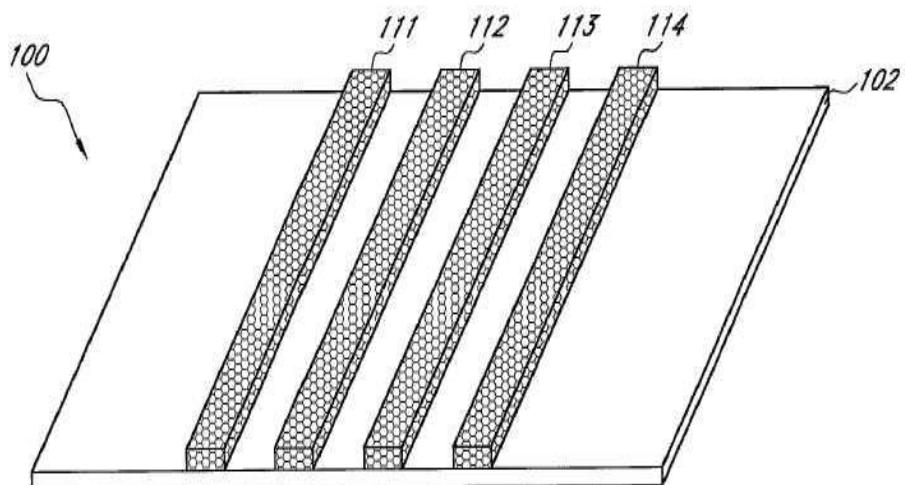

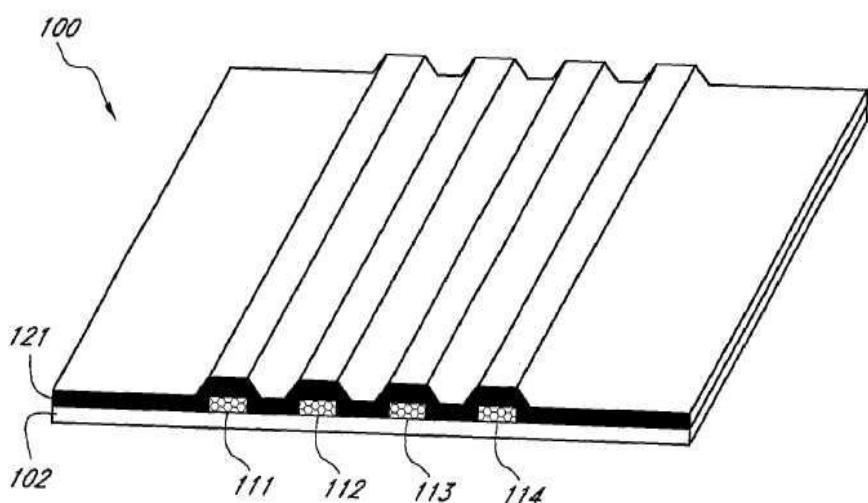

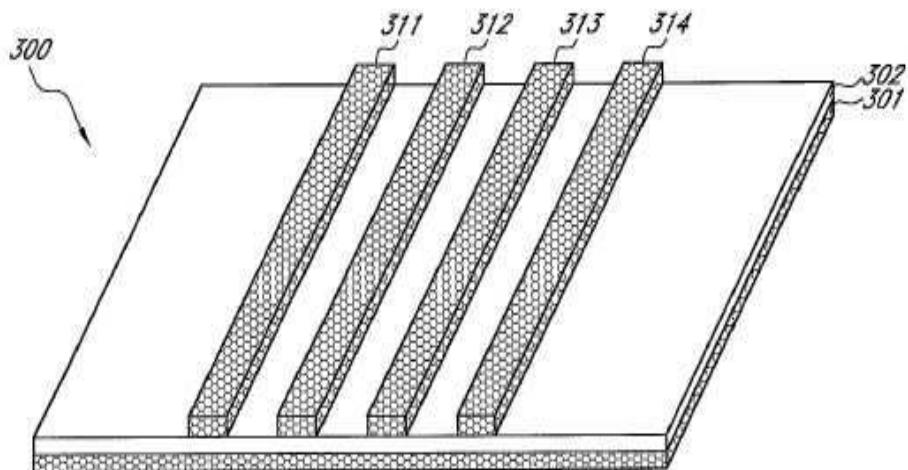

- <55> 도 1B 는 스텝 501 의 완성 후에 형성된 구리 트레이스 111, 112, 113, 114를 나타낸다. 일 실시예에서, 상기 구리 트레이스 111, 112, 113, 114 는 인쇄되고, 해당 기술 분야의 당업자에게 잘 알려진 포토리소그래피 기술을 사용해서 에칭된다. 포토리소그래피 기술은, 핫롤 라이네이터(hot roll laminator) 또는 진공 라미네이션 공정(vacuum lamination process)을 사용하여, 에칭 저항성 건조 필름(dry film etch resist)을 상기 베이스 전도

층 101에 라미네이팅하는 것을 필요로 한다. 많은 에칭 저항성 건조 필름(dry film etch resist)층들은 상업적으로 구할 수 있으며, Dupont®과 같은 회사에 의해서 만들어지고 있다. 몇몇 실시예에서, 상기 에칭 저항 층 건조 필름(dry film etch resist)층의 두께는 0.0007" 내지 0.0020" 이다. 자외선(UV) 에너지와, 포토톨, Mylar®film, 또는 Mylar®glass 와 같은 적절한 도구를 사용하여, 회로 이미지는 에칭 저항층으로 전달된다. UV 에너지에 노출되지 않은 에칭 저항 부분은 그후 패널에서 화학적으로 세정된다. 예를 들어, 탄산칼륨(Potassium Carbonate)을 포함하는 용액이, 현상되지 않은(즉, UV 에너지에 노출되지 않은) 에칭 저항 부분을 세정하기 위해서 사용될 수 있다. 다음으로, 상기 현상된 에칭 저항을 통해서 노출된 상기 구리가 화학적으로 제거된다. 예를 들어, 염화제2구리 에천트(cupric chloride etchant)의 수용액이 구리를 제거하기 위해 사용될 수 있다. 선택적으로, 알칼린-베이스 에천트와 염화제2철 베이스 에천트(ferric chloride-based etchant) 등의 다른 타입의 구리 에천트가 사용될 수 있다.

<56> 도 1C는, 트레이스 111, 112, 113, 114를 갖는 가요성 회로 100의 상부에 적층된, 절연성 또는 유전층을 나타낸다. 이 층은 스텝 502에 의해서, 전기적 쇼트를 방지하고, 트레이스 111, 112, 113, 114를 오염으로부터 보호하기 위해, 방법에 있어서 후에 만들어지는 접지된 차폐(grounded shielding)로부터, 에칭된 트레이스 111, 112, 113, 114를 절연하기 위해서 만들어진다. 어떠한 유전적(dielectric) 또는 비-전도성 절연 물질(non-conductive insulative material)이라도 사용될 수 있다. 예를 들면, 일실시예에서, 유전층 121은 필름의 일면에 부착된 써멀 세트(thermal set)를 가진 폴리이미드 필름(polyimide film)으로 만들어진다. 이 실시예에서, 상기 폴리이미드 필름(polyimide film)은 두께가 0.0005" 내지 0.0010"의 범위이고, 부착된 써멀 세트(thermal set)의 두께는 0.0005" 내지 0.0015"이다. 상기 필름 121은 상기 에칭된 트레이스 111, 112, 113, 114의 상부에 위치하고, 상기 접착층은 상기 에칭된 트레이스 111, 112, 113, 114와 접한다. 그후, 오토클레이브 또는 진공 프레스를 사용해서, 상기 필름은 상기 가요성 회로 100에 라미네이트된다. 예를 들면, 기압 210 psi, 온도 385 °F에서 60분간 등과 같은 라미네이션 파라미터가 사용될 수 있다. 다른 알려진 기술들은 상기 유전층 121을 상기 가요성 회로 100에 부착시키기 위해 사용될 수 있다.

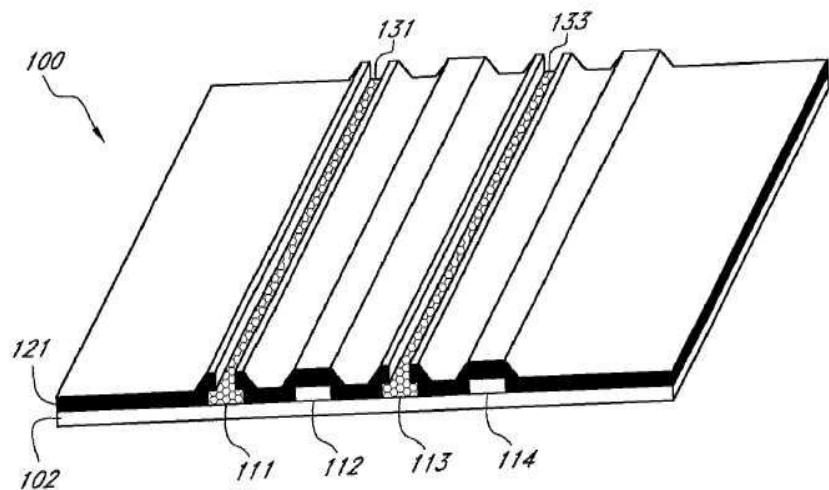

<57> 도 1D는 스텝 503에 의해서 유전층 121에 형성된 채널 131, 133을 나타낸다. 상기 채널들 131, 133은 교대 트레이스 111, 113에 대응하는 위치에서 형성되고, 불연속(discontinuities)을 형성하여, 후에 그들 사이의 트레이스 112를 위한 차폐를 형성한다. 상기 채널 131, 133은, 각각의 트레이스의 길이 방향으로 그 위의 유전층 121을 제거함으로써, 교대로 접지된 트레이스 111, 113을 노출시킨다. 일 실시예에서, 상기 채널들은 레이저 어블레이션 기술(laser ablation techniques)을 사용해서 형성된다. 다른 실시예에서, 다른 공정 기술, 예를 들면, 플라즈마 에칭과 화학적 밀링 등이 사용될 수 있다.

<58> 다른 실시예에서, 채널들이 대체로 교대의 트레이스에 대응하는 위치에서 형성될 수 있다는 것이 감지된다. 다른 실시예에서, 상기 생성된 채널들 사이에서의 상기 트레이스들은 차폐된다.

<59> 다음으로, 몇몇의 실시예에서, 상기 노출된 교대로 접지된 트레이스들 111, 113은 금속화되어(metalized) 트레이스 111, 113을 산화로부터 보호한다. 예를 들면, 니켈과 금 화합물이 트레이스 111, 113을 금속화(metalize)하기 위해 사용될 수 있다.

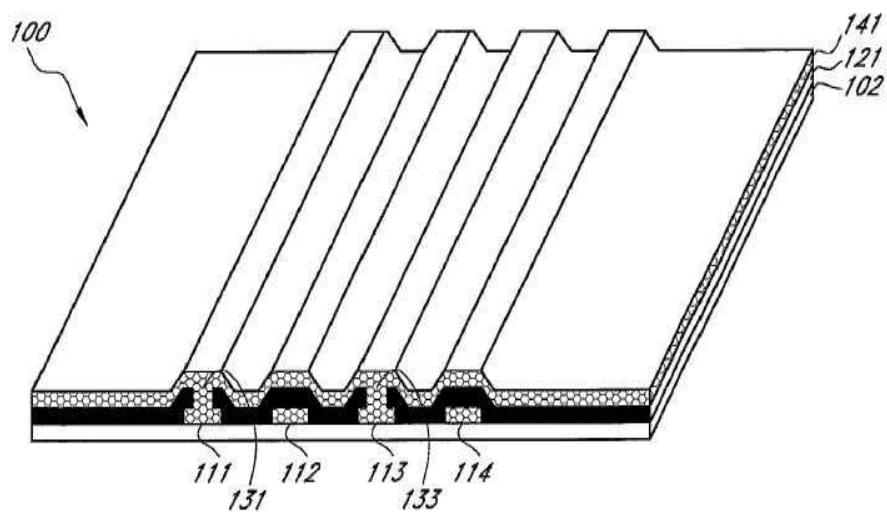

<60> 도 1E과 도 1F는, 스텝 504와 505에 의해, 가요성 회로 100의 상부에 형성된 전도성 차폐층 141과 유전층 171을 나타낸다. 상기 전도층 141은 상기 가요성 회로 100에 적용되어, 상기 교대로 접지된 트레이스 111, 113과 전기적으로 연결되도록 된다. 상기 전도층 141은, 상기 교대로 접지된 트레이스 111, 113과 상기 유전층 121에 부착할 수 있는 어떠한 전도성 물질로도 구성될 수 있다. 적절한 전도층 141 물질에는, 은 베이스 필름(silver based film)과 은 잉크(silver ink)를 포함하지만, 이에 제한되는 것은 아니다. 상기 전도층 141은, 상기 유전층 121을 가요성 회로 100에 부착하기 위해 사용된 것과 유사한 기술(예를 들면, 라미네이션)을 사용하여, 상기 가요성 회로 100에 적용된다. 다음으로, 유전층 171은 상기 가요성 회로 100에 적층되어, 상기 전도층 141의 상부에 위치하게 된다. 라미네이션과 같은 기술이 상기 유전층 171을 상기 도전층 141에 부착하기 위해 사용될 수 있다. 적절한 유전층 171 물질에는, 유전층 121을 위해 사용되는 물질들이 포함되지만, 이에 한정되지 않는다. 상기 전도층 141과 유전층 171은 위에서 설명한 것과 같이, 또는 동시에(즉, 스텝 504와 505가 한 스텝으로 행하여) 상기 가요성 회로 100에 부착될 수 있다고 생각된다. 일 실시예에서, 상기 전도층 141과 상기 유전층 171을 동시에 적용하는 것은, 전도층과 유전층으로 구성된 프리-메이드 물질을 사용해서 행하여 질 수 있다. 이러한 물질들의 예로는 Tatsuta's® PC 시리즈를 찾을 수 있다. 이러한 물질들은, 전도성 접착층(conductive adhesive layer)과 유전층 사이에 샌드위치된, 은 포일의 전도층을 구성한다. 물질들은 상기 가요성 회로 100의 상부에 위치하여, 상기 전도성 접착층이 유전층 121과 접하게 된다. 그후, 상기 물질은 라

미네이트 되거나, 아니면 상기 가요성 회로 100에 부착된다.

- <61> 도 1F 는, 스텝 506에 의해, 상기 가요성 기판 102에서, 상기 가요성 회로 100의 바닥부에 위치하고, 상기 교대로 접지된 트레이스 111, 113의 아래에 형성된, 채널 151, 152 을 나타낸다. 상기 채널 151, 152는 스텝 503에서 적용되는 테크닉과 유사한 기술(예를 들면, 레이저 어블레이션(laser ablation))을 사용하여 만들어진다. 일 실시예에서, 상기 채널들은 상기 가요성 기판 102에 형성되어, 상기 교대로 접지된 트레이스 111, 113이 트레이스의 길이 방향으로 노출된다. 다음으로, 몇몇 실시예에서, 상기 노출된 구리 트레이스 111, 113은 니켈/금 화합물을 사용하여, 산화를 막기 위해 금속화(metalize)된다.

- <62> 도 1G 는, 스텝 507에 의해, 상기 가요성 기판 102의 아래 부분에 상기 가요성 회로 100의 사이드에 적층된 상기 전도성 차폐층 161을 나타낸다. 이러한 전도성 차폐층 161은 적층되어 상기 교대로 접지된 트레이스 111, 113과 전기적으로 연결되게 된다. 스텝 508에 대하여 앞에서 설명한 바와 같이, 상기 전도성 차폐층 161 은 상기 가요성 회로 100에 라미네이트 될 수 있으며, 또한, 구리 또는 은과 같은 어떠한 전도성 물질로도 구성될 수 있다.

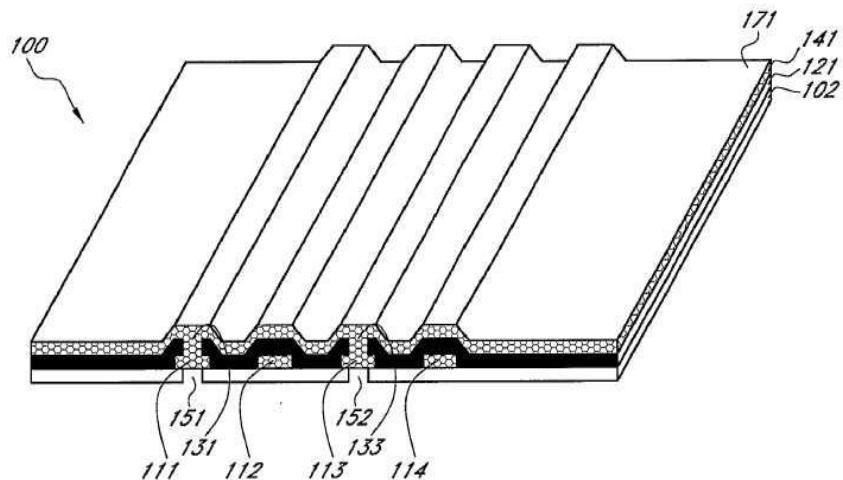

- <63> 도 1H 는, 스텝 508에 의해서, 상기 도전성 차폐층 161에 부착된 유전층 172를 나타낸다. 이러한 유전층 172는 상기 노출된 전도성 차폐층을, 전기적 간섭(interference)과 오염으로부터 보호한다. 상기 유전층 172 는 상기 가요성 회로 100에, 라미네이션과 같은 기술을 사용해서 부착될 수 있으며, 스텝 502에서 사용되는 것과 유사한 물질(예를 들면, 폴리아미드 필름)로 구성될 수 있다.

- <64> 스텝 504와 505에 관해서 설명한 바와 같이, 상기 전도성 차폐층 161과 상기 유전층 172 는, Tatsuta® PC series 를 포함하는 물질들과 같은 물질들을 사용하여, 한 스텝으로, 상기 가요성 회로 100에 적층될 수 있다.

- <65> 도 1H 에서 보는 바와 같이, 중심 구리 트레이스 112 의 모든 사이드들이 차폐된다. 첫번째로 비-전도성 유전적 물질들에 의해 차폐되고, 이후 상기 비-전도성 물질(non-conductive material)은 전도성 물질들에 의해 둘러싸인다. 특히, 상기 트레이스 112 는, 유전층 121에 의해서, 상부와 사이드에서, 상기 접지면 111, 113, 141로부터 전기적으로 절연되고, 바닥부에서 가요성 기판 102 에 의해 접지면 161로부터 전기적으로 절연된다. 이 설명에서, 상기 전도성 차폐는, 상기 트레이스 112의 상부 전도층 141, 상기 트레이스 112의 바닥부 전도층 161, 및 상기 트레이스 112의 사이드에서 상기 교대로 접지된 트레이스 111, 113 으로 구성된다.

- <66> 추가적으로, 유전층 171, 172 는, 상기 회로를 EMI 로부터 차폐하는 것이 필요하지 않다. 몇몇 실시예에서, 층 171, 172 중 하나 또는 어느 것도 적용되지 않을 수 있다.

- <67> III. "모든 트레이스가 차폐된 하나의 구리층" 실시예 ("Single Copper Layer With All Traces Shielded" Embodiments)

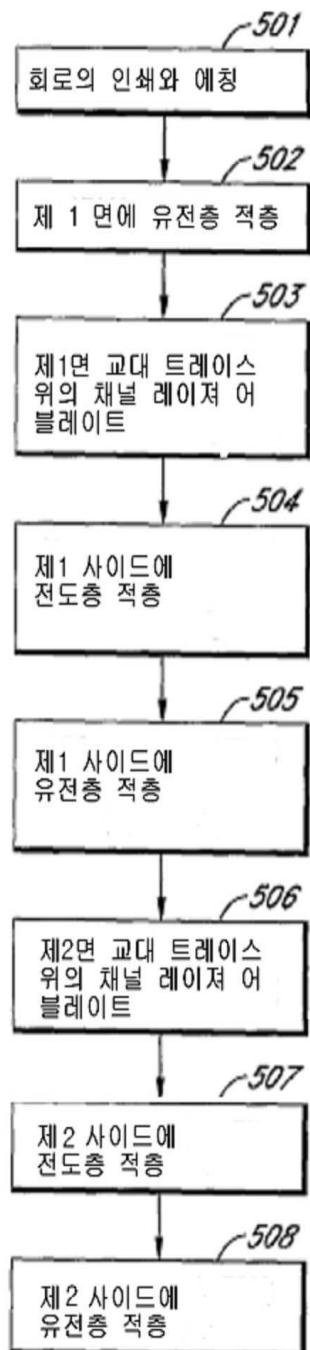

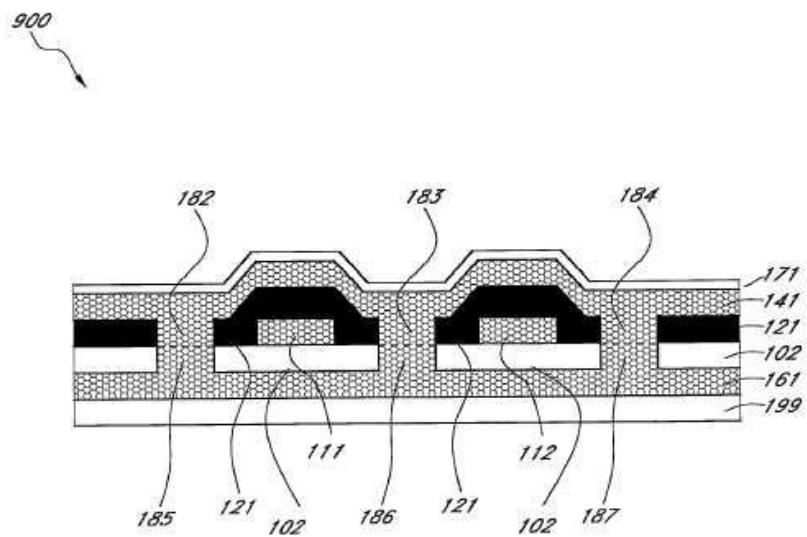

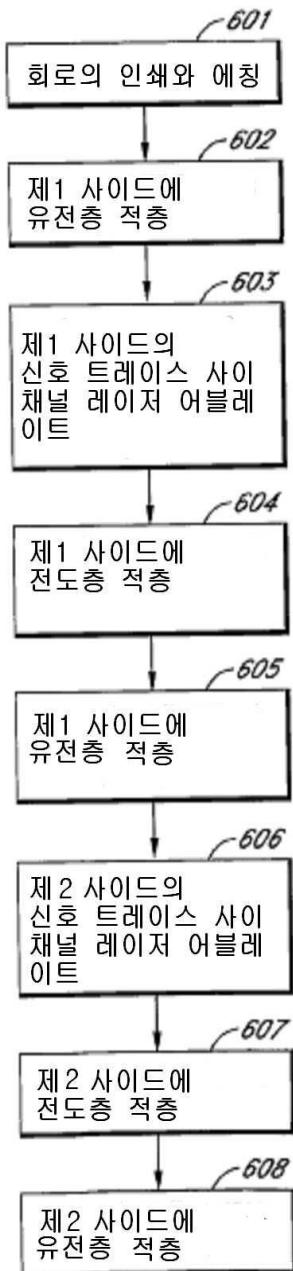

- <68> 도 3은 모든 트레이스가 차폐된 하나의 구리층의 실시예를 나타낸다. 도 4는 스텝 601 - 608 을 포함하는 도 3에 나타난 차폐된 가요성 회로 900 을 제조하는 하나의 방법에 대한 공정도(a process diagram)를 나타낸다. 여기서 설명한 바와 같이 도 4의 스텝들은 도 4에서 사용된 참조번호로써 나타내어 질 것이다.

- <69> 도 3과 도 4의 장치의 제조를 위한 장치와 방법은 도 1A-H 와 도 2에서 나타난 실시예의 특징을 공유한다. 다시 말하면, 교대로 접지된 트레이스를 갖는 하나의 구리층에 관해 제안 및/또는 적용된 많은 가능한 물질과 기술은 모든 트레이스들이 차폐된 하나의 구리층 실시예와 연결되어 사용될 수 있다. 그러나, 두가지 세트의 실시예들간의 차이점은 아래와 같다.

- <70> 또한, 이 부분에서 설명되고 있는 실시예들에 주어진 타이틀이 제한하는 것으로 생각되어서는 안된다. 모든 트레이스 111, 112가 차폐된 필요는 없는 것으로 생각된다. 그보다는, 이러한 실시예들에서, 모든 트레이스 111, 112를 차폐하는 것은 가능하다.

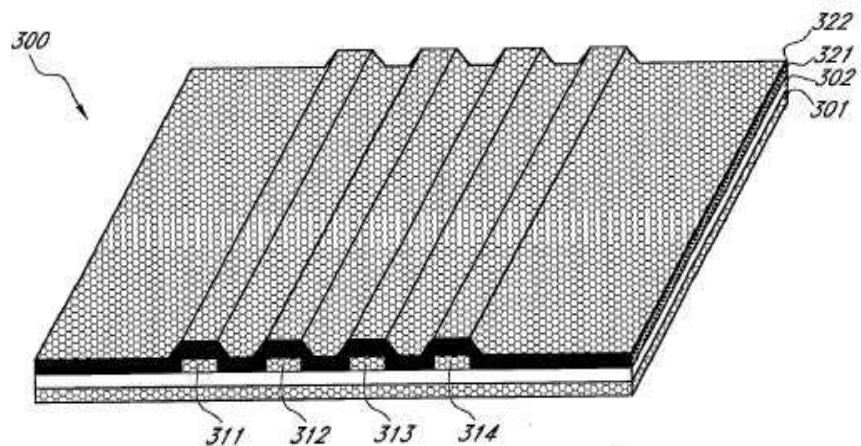

- <71> 일 실시예에서, 차폐된 가요성 회로 900을 제조하기 위한 방법은 도 1A 에 나타난 부재 100과 같은 가요성 지지부재로부터 시작된다. 도 3과 도 4를 참조하면, 활성 신호 트레이스 111, 112는 기반 전도층 101로부터, 프린트와 예칭 기술 601을 사용하여 형성된다. 유전층 121은, 스텝 604에서 적층된 차폐 141의 전도성 부분으로부터 트레이스 111, 112를 전기적으로 절연시키기 위해, 그후 트레이스 111, 112의 상부에 적층된다.

- <72> 다음으로, 스텝 603에서, 채널 182, 183, 184 는 상기 활성 신호 트레이스 111, 112 사이에 형성된다. 상기 채널 182, 183, 184 는, 상기 트레이스 111, 112 사이에 위치한 유전층 121 부분을 제거하기 위해, 레이저 어블레이션 기술(laser ablation techniques)을 사용해서 만들어진다. 도 3에서 설명된 실시예들에서, 트레이스 111,

112 는 채널들을 노출시키지는 않는다.

- <73> 결과적으로, 전도성 차폐층 141은, 스텝 604에서, 상기 유전층 121의 상부와 채널 182, 183, 184에 위치한다. 상기 전도성 차폐층 141은 스텝 604에서 상기 가요성 회로 900 의 상부에 부착되어, 가요성 기판 102와 접촉하게 된다. 다음으로, 절연층 171은, 스텝 605에서, 전도성 차폐층의 상부에 부착되게 된다. 스텝 605와 605를 수행하기 위해서, 연결된 스텝 604와 605는 a Tatsuta® PC series material을 사용하여 한번에 수행할 수 있는 것으로 생각되고 있다.

- <74> 제 2 채널 세트 185, 186, 187 은 스텝 606에서 상기 가요성 회로 900의 바닥부에 형성된다. 상기 채널 185, 186, 187은 트레이스 111, 112 사이에 위치하여, 상기 제1 채널 세트 182, 183, 184의 사이에 위치한 상기 전도성 차폐층 141을 노출한다. 상기 제2 채널 세트 185, 186, 187 은, 이러한 위치들에서의 상기 가요성 기판 102 의 부분을 제거하기 위해, 레이저 어블레이션 기술(laser ablation techniques)을 적용하여 만들어진다.

- <75> 전도성 차폐층 161은 그후 스텝 607에서 상기 가요성 회로 900의 바닥부에, 예를 들면, 라미네이션 기술을 사용하여, 부착된다. 이러한 전도성 차폐층 161은 채널 185, 186, 187에 적층되고, 전도성 차폐층 141과 전기적으로 연결되게 된다. 다음으로, 유전층 199는, 스텝 608에서, 또한 라미네이션 기술을 사용하여, 상기 전도성 차폐층 161에 부착된다. 스텝 604와 605에 대해 설명한 바와 같이, 스텝 607과 608은 차례로 수행되거나, 하나의 스텝으로 수행될 수 있다.

- <76> 추가적으로, 몇몇 실시예에서, 유전층 171과 199 중 하나 또는 모두는 전도층 141과 161을 절연하기 위해서 사용되지 않을 것이다. 유전층 171, 188의 부재는 트레이스 111, 112를 EMI로부터 차폐하기 위해 요구되지는 않을 것이다.

- <77> 또한, 몇몇 실시예에서, 방법의 스텝 606, 상기 가요성 회로 900의 바닥부의 레이저 어블레이팅 채널(laser ablating channel)185, 186, 187은 생략될 수 있다고 인식된다. 스텝 606을 생략하는 것은, 스텝 603에서, 상기 가요성 지지부재의 상부의 채널 182, 183, 184의 레이저 어블레이션(laser ablation), 유전층 121의 부분과 상기 트레이스 111, 112 사이에 위치한 폴리이미드층 102 모두가 제거되는 것을 요구한다.

- <78> 도 3에 나타난 바와 같이, 트레이스 111, 112는, 첫번째로는 유전적 차폐 (dielectric shielding)에 의해, 두 번째로는 전도성 차폐(conductive shielding)에 의해 각각 360 도 차폐된다. 각각의 트레이스 111, 112 은 모든 방향에서 상기 전도성 차폐 물질과 다른 트레이스 111, 112 로부터 절연된다. 유전층 121은 상기 트레이스 111, 112의 상부와 사이드를 접지면(the ground plane) 182로부터 전기적으로 절연하고, 가요성 기판 102는 상기 트레이스 111, 112의 바닥부를, 접지면(the ground plane) 161로부터 전기적으로 절연한다. 따라서, 각각의 트레이스 111, 112는 접지되고 전도성이 있는 차폐 물질로 둘러쌓인다. 전도층 141은, 상기 트레이스 111, 112 의 상부와 사이드에 전도성 차폐를 제공하고, 바닥부 전도 층 161은 상기 트레이스 111, 112, 113의 바닥부에 전도성 차폐를 제공한다.

- <79> IV. ."두 개의 구리층" 실시예 ("Two Copper Layer" Embodiments)

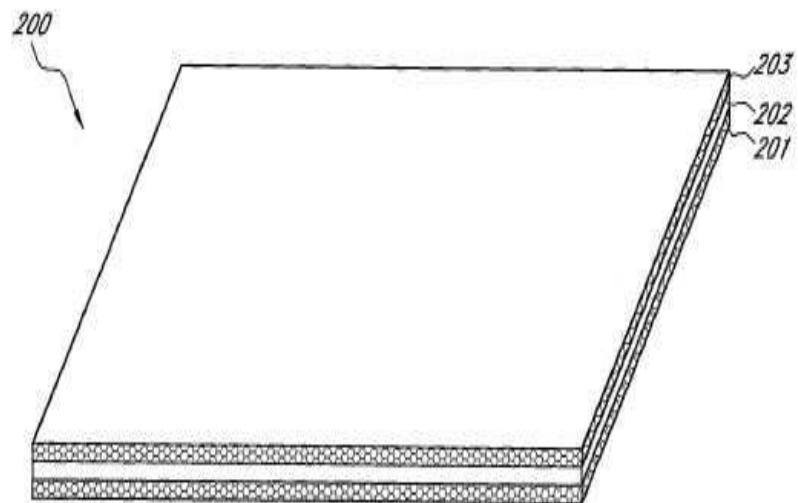

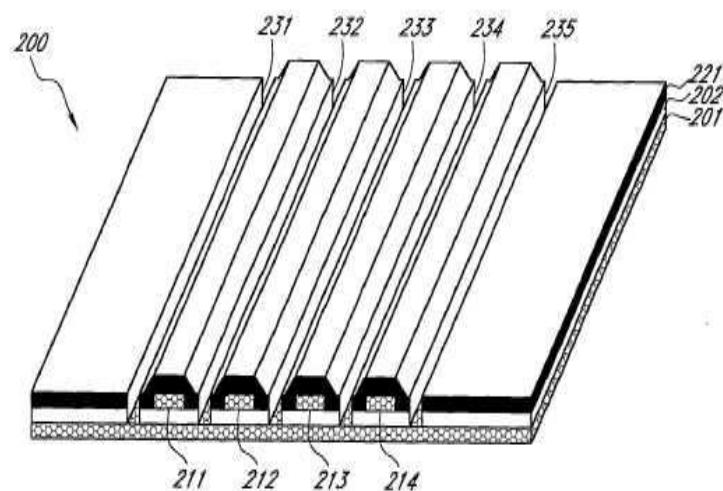

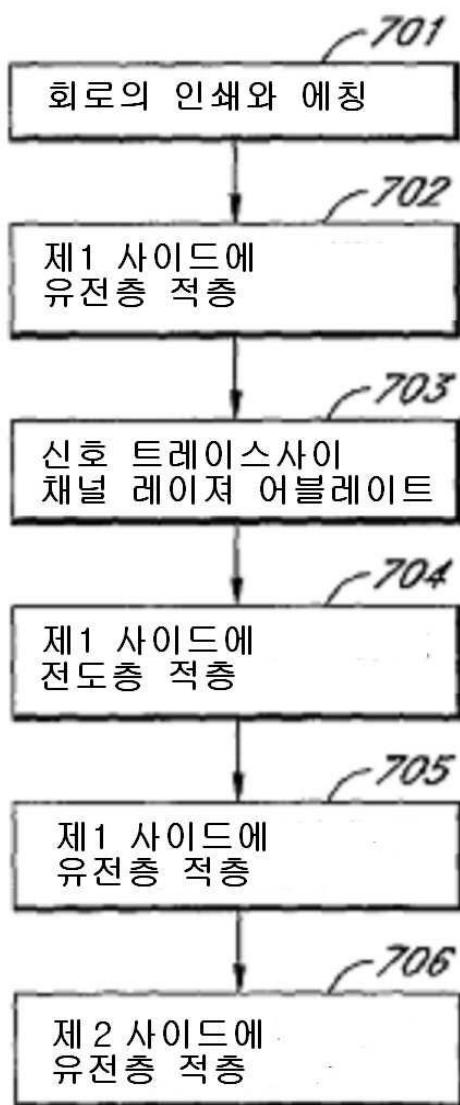

- <80> 도 5F 는 두개의 구리층이 차폐된 가요성 회로의 실시예를 나타낸다. 도 6은, 스텝 701 - 706을 포함하는, 도 5F 의 차폐된 가요성 회로를 제조하기 위한, 공정도를 나타내며, 도 5A - F 는 상기 방법의 각각의 스텝이 실행됨에 따라 상기 차폐된 가요성 회로의 구조를 나타낸다. 여기서 설명되는 바와 같이, 방법의 각각의 스텝에서의 상기 회로의 구조와 연결되어 있는 도면들이 참조로서 사용될 것이다. 이와는 대조적으로, 도 6의 공정도의 각각의 스텝은 도 6의 참조 번호를 사용하여 참조될 것이다.

- <81> 설명된 실시예에서, 차폐된 가요성 회로의 제조를 위한 방법은 도 5A 에 도시된 지지 부재 200으로부터 시작된다. 상기 가요성 지지부재 200은 3개의 층으로 구성되고, 가요성 기판 202 는 상부 전도층 203과 바닥부 전도 층 201 사이에 샌드위치되게 된다. 당업자에게 공지된 바와 같이 가요성 지지부재 200은 상업적으로 만들어지고 쉽게 구매할 수 있다. 다른 실시예에서, 상기 방법은, 플레이팅(plating), 라미네이션, 증기 증착(vapor deposition) 또는 다른 알려진 기술을 사용하여, 상부와 바닥부 전도층 201, 203을 상기 가요성 기판 202에 적층하는 것으로부터 시작된다. 여기서 기술되는 실시예들이, 구리로 구성된 상부와 바닥부 전도층 201, 203에 한정되지는 않으며, 기술된 실시예들은 구리 상부와 바닥부 전도층 201, 203을 활용한다.

- <82> 또한, 교대로 접지된 트레이스에 의한 구리 단층 차폐에 관해서 제안된 된 많은 대체 물질들과 기술들이, 상기 두개의 구리층 실시예들과 연결되어서 사용될 수 있다. 그러나, 이러한 두가지 실시예 세트에서의 차이점들이 이하에서 설명된다.

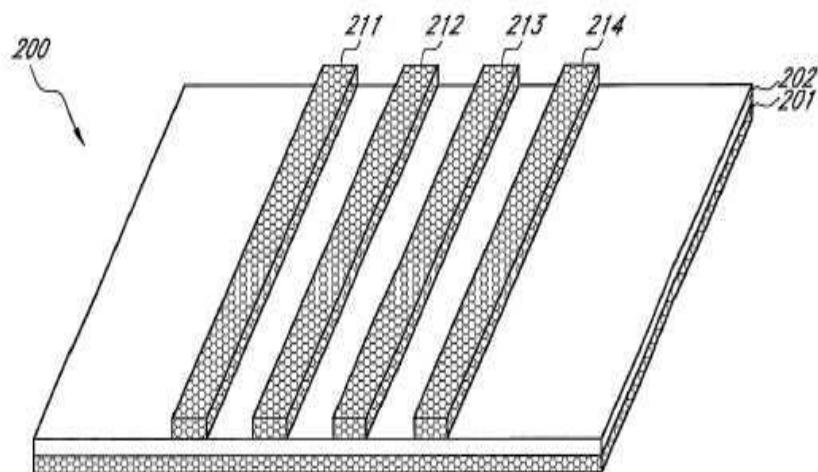

- <83> 도 5B 는, 스텝 701에서, 상부 구리층 203으로부터 프린트되거나 에칭된 후의 트레이스 211, 212, 213, 214를 나타낸다. 보는 바와 같이, 트레이스 211, 212, 213, 214 는, 도시된 실시예의 디자인 요구사항이 상기 트레이스 211, 212, 213, 214 가 서로 전기적으로 분리되어 있을 것을 요구하기 때문에, 서로 전기적으로 연결되어 있지 않다.

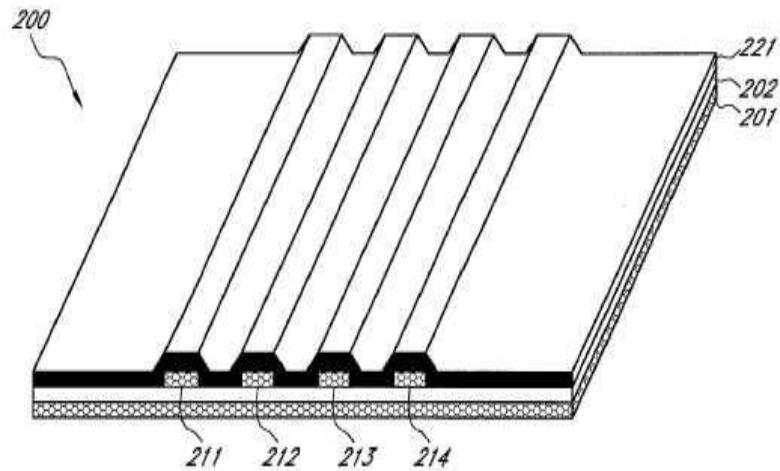

- <84> 도 5C 는, 스텝 702에서, 상기 가요성 회로 200 의 상부에 적층된 절연층 또는 유전층 221을 나타낸다. 예를 들면, 라미네이션 기술을 사용하여, 유전층 221은 상기 가요성 기판 202 과 상기 트레이스 211, 212, 213, 214 에 적층된다.

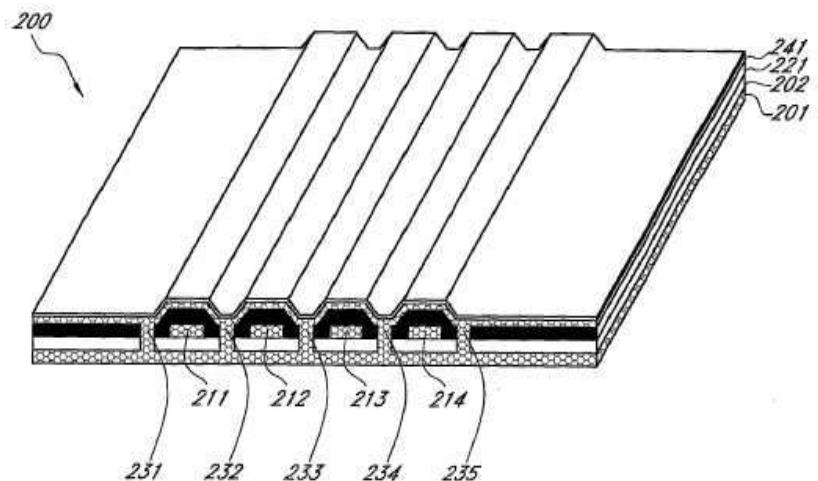

- <85> 도 5D 는, 스텝 703에서 활성 신호 트레이스 211, 212, 213, 214 사이에 만들어지는 채널 231, 232, 233, 234 을 나타낸다. 상기 채널 231, 232, 233, 234 는 상기 유전층 221의 부분과 상기 트레이스 211, 212, 213, 214 사이에 위치한 상기 가요성 기판 202를 제거하기 위해, 레이저 어블레이션(laser ablation) 또는 알려진 다른 기술들을 적용하여 만들어진다. 도시된 바와 같이 상기 채널 231, 232, 233, 234는 바닥부 구리층 201의 상부 를 노출하지만, 상기 트레이스 211, 212, 213, 214를 노출하지는 않는다.(즉, 트레이스 211, 212, 213, 214는 절연되어 있다.)

- <86> 도 5E 는, 스텝 704에서, 상기 가요성 회로 200의 상부에 적층된 전도성 차폐층 241 을 나타낸다. 상기 전도성 차폐층 241은, 상기 가요성 회로 240에 적층되어, 상기 채널 231, 232, 233, 234에 위치하게 하며, 바닥부 전도층 201과 전기적으로 연결되게 된다. 일 실시예에서, 상기 전도성 차폐층 241은 은이 채워진 잉크이다. Dupont's® CB208 product 는 은 잉크(silver ink)이며 상업적으로 이용가능하고 당업자에게 알려져 있다. 전형적으로 은 잉크(silver ink)는, 바닥부 전도층 201을 노출시키기 위해 미리 레이저 처리된 상기 유전층 221의 표면에 스크린 프린트된다. 다른 실시예에서, 요구되는 흐름 특성the requisite flow characteristics을 갖는 다른 전도성 물질이 사용될 수 있다.

- <87> 도 5F 는, 스텝 705와 706에서, 상기 가요성 회로 200의 상부와 바닥부에 적층된 절연성 또는 유전층 251, 252 를 도시한다. 몇몇 실시예에서, 유전 필름 251, 252는 상기 가요성 회로 200에 라미네이트 된다. 상기 유전층 251, 252는 상기 가요성 회로 250을 외부적 쇼팅(external shorting)으로부터 보호하는 것으로 작용할 수 있다.

- <88> 다른 실시예에서, 스텝 704는 라미네이팅 또는 전도성 필름을 상기 유전층과 상기 채널 231, 232, 233, 234에 부착하는 다른 방법으로 행하여 진다. 이러한 실시예들에서, 절연층 252는 그후, 외부적 쇼팅(external shorting)을 방지하기 위해, 상기 절연성 차폐층 251의 상부에 부착될 수 있다. 선택적으로, 상기 전도성 차폐층 241과 상기 유전층 252 는, 동시에 Tatsuta® PC series와 같은 접착 물질에 의하여, 상기 가요성 회로 250 에 적층할 수 있다.

- <89> 도 5F에 나타난 바와 같이, 상기 트레이스 211, 212, 213은 360도 차폐된다. 각각의 트레이스 211, 212, 213 은 모든 방향에서 상기 전도성 차폐물질과 다른 트레이스 211, 212, 213으로부터 절연된다. 유전층 221은 상기 트레이스 211의 상부와 사이드를, 접지면(grounded plane) 241, 212, 213으로부터 절연하고, 상기 가요성 기판 202는 상기 트레이스 211, 212, 213의 바닥부를 접지면(grounded plane) 201로부터 절연한다. 따라서, 각각의 트레이스 211, 212, 213은 접지된 차폐 물질로 둘러싸이게 된다. 전도층 241은, 상기 트레이스 211, 212, 213의 상부와 사이드부에 전도성 차폐를 제공하고, 상기 바닥 전도층 201은 상기 트레이스 211, 212, 213의 바닥부에 전도성 차폐를 제공한다.

- <90> V. "세개의 구리층" 실시예 ("Three Copper Layer" Embodiments)

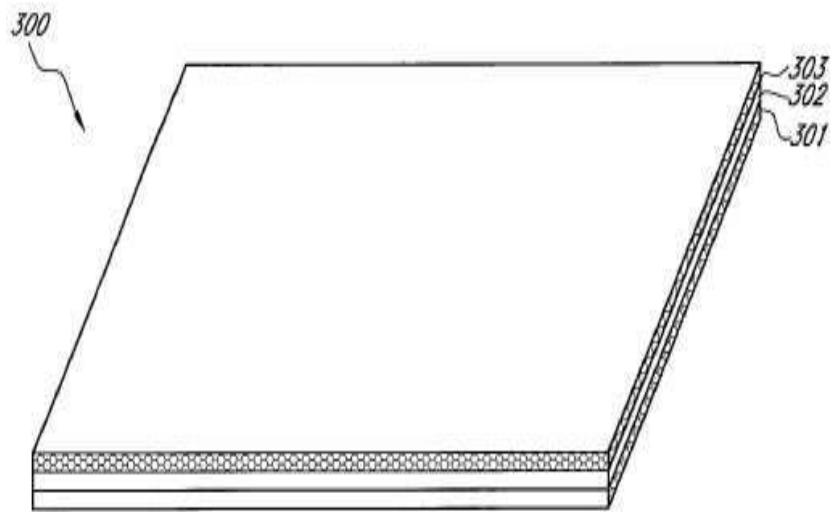

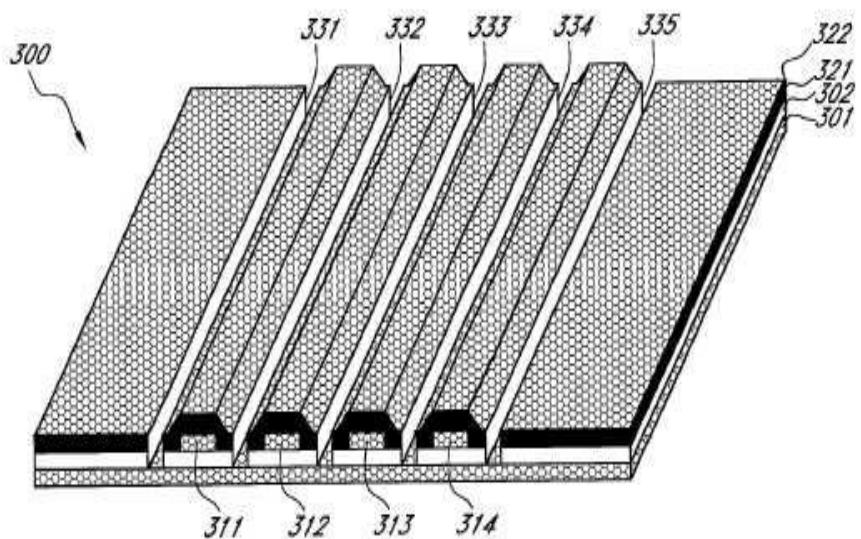

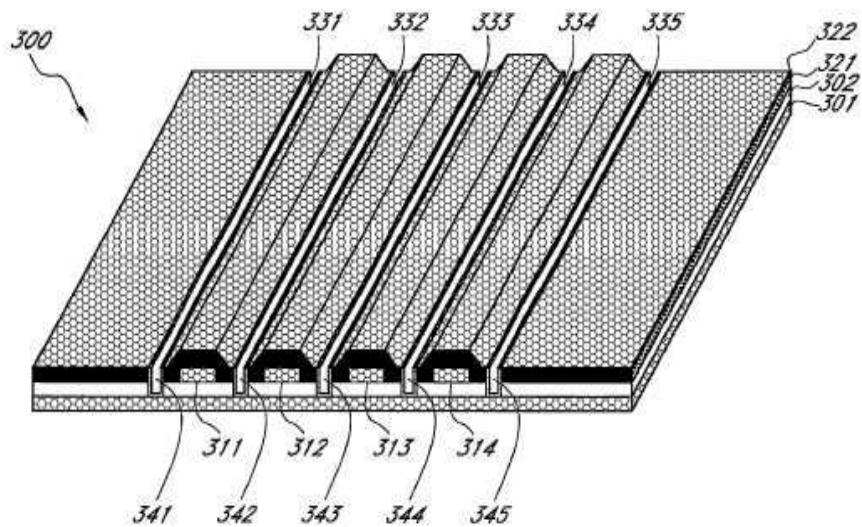

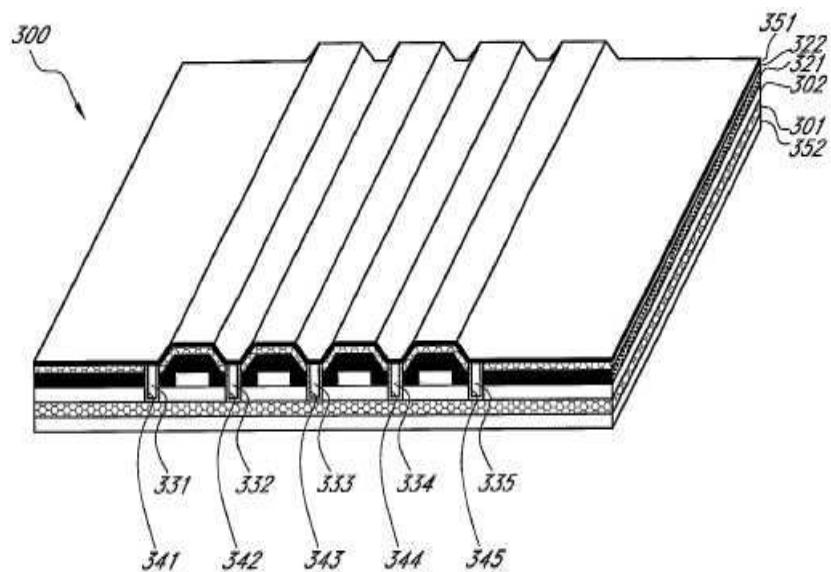

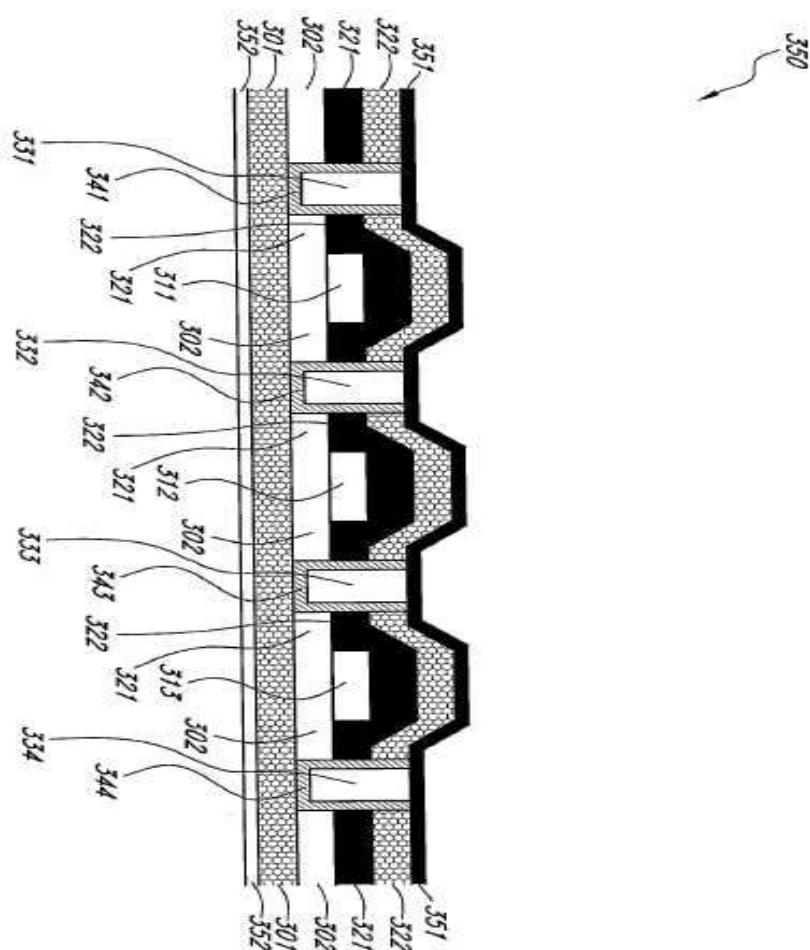

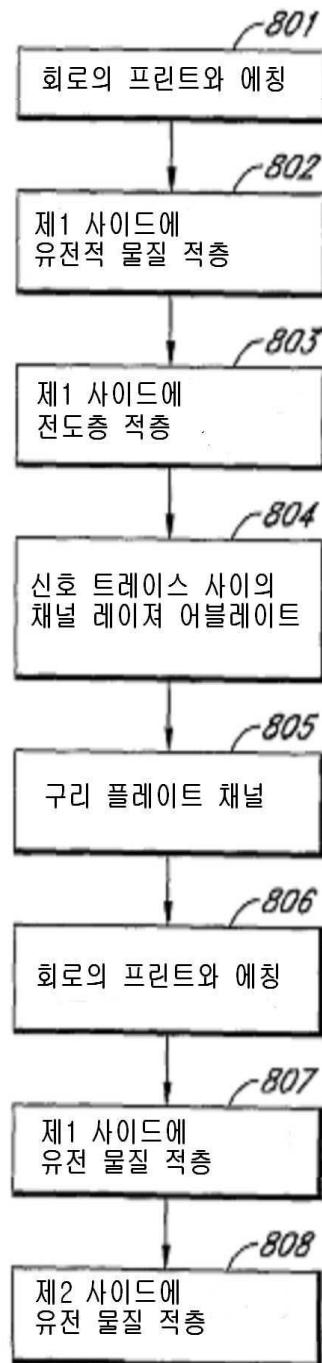

- <91> 도 7G는 세개의 구리층이 차폐된 가요성 회로의 일 실시예를 나타낸다. 도 8은, 스텝 801-808을 포함하는, 차폐된 가요성 회로의 제조를 위한 방법의 일 실시예를 위한 공정도를 나타내며, 도 7A-G 는 방법의 각각의 스텝이 실행됨에 따라 상기 차폐 가요성 회로의 구조를 나타낸다. 여기서 기술된 것과 같이, 도면들은 방법의 각각의 스텝에서의 회로의 구조와 연관되어 있는 도면들이 참조되었다. 이와는 대조적으로 도 8의 공정도의 각각의 스텝들은 도 8에서만의 참조 번호를 사용하여 참조될 것이다.

- <92> 일 실시예에서, 차폐된 가요성 회로를 제조하기 위한 방법은 도 7A 에 도시된 가요성 지지부재 300 으로부터 시작된다. 상기 가요성 지지부재 300은 3개의 구리층으로 구성되며, 가요성 기판 302는, 상부 전도층 303과 바닥부 전도층 301 사이에 샌드위치 된다. 가요성 지지부재 300이 상업적으로 제조되고 쉽게 구입할 수 있다는 것은 당업자들에게 알려져 있다. 다른 실시예에서, 상기 방법은, 플레이팅, 라미네이션, 증기 증착 또는 다른 알려진 기술을 사용하여, 상기 상부와 바닥부 베이스 전도층을 상기 가요성 기판에 적층하는 것으로부터

시작된다. 또 다른 실시예에서, 상기 상부와 바닥부 전도층은, 구리, 은, 또는 금과 같은 어떠한 전도성 물질로도 구성될 수 있다.

<93> 도 7B 는, 스텝 801에서, 프린트 되고 예칭된 후에, 전기적 신호를 전달하기 위해 사용된 트레이스 311, 312, 313, 314를 도시한다. 상기 트레이스 311, 312, 313, 314는 상부 전도층 303 으로부터 예칭된다.

<94> 도 7C 는, 스텝 802와 803 가 완료된 후의 상기 가요성 회로 300 을 도시한다. 스텝 802는, 유전성 물질 321 을 상기 가요성 회로 300의 상부에 적층하는 것을 요구한다. 상기 유전층 322는 앞서 개시된 전기적으로 절연성이 있는 어떠한 물질로도 구성될 수 있으며, 앞서 설명된 어떠한 기술을 사용하여 상기 가요성 회로에 적층될 수 있다. 스텝 803은 전도성 차폐층 322을, 유전층 321의 상부에 적층하는 것을 필요로 한다. 일 실시예에서, 상기 전도성 차폐층 322 는 구리 호일(copper foil)이다. 상기 구리 호일은, 라미네이션 기술 또는 다른 당업계에 알려진 기술을 사용하여, 상기 가요성 회로 300에 부착된다.

<95> 다른 실시예에서, 스텝 802와 803은, 전도층과 유전층을 구성하는 물질을 사용하여 동시에 진행될 수 있다. 상기 물질들은, 상기 트레이스 311, 312, 313, 314와 물리적으로 접촉하고 있는 유전층을 가진 상기 가요성 회로 300에 부착된다. 다른 실시예에서, 스텝 802와 803은, 유전적 접착제(dielectric adhesive)로 상기 가요성 회로 300에 접착하고 있는 전도성 물질을 사용하여 동시에 진행될 수 있다. 이러한 실시예에서, 상기 전도성 물질은 구리 호일이고, ADH/PI/ADH 와 같은 유전 호일 결합 접착제(dielectric foil bonding adhesives)가 사용될 수 있다.

<96> 도 7D 는, 스텝 804에서, 상기 트레이스 311, 312, 313, 314 사이에 형성된 채널 331, 332, 333, 334 를 도시한다. 상기 채널 331, 332, 333, 334 는, 상기 트레이스 311, 312, 313, 314 사이에 위치한 상기 가요성 기판 302, 상기 유전층 321, 및 상기 전도성층 322 부분을 제거하여 생성된다. 상기 채널 331, 332, 333, 334는 상기 바닥부 전도층 301을 노출시킬 수 있을 정도의 충분한 깊이이다. 위에서 설명한 바와 같이, 레이저 어블레이션(laser ablation)과 같은 기술이 상기 채널 331, 332, 333, 334 를 만들기 위해 사용될 수 있다.

<97> 도 7E 는, 스텝 805에서, 상기 채널 331, 332, 333, 334에 적층된 구리 플레이팅 341, 342, 343, 344 을 나타낸다. 상기 구리 플레이팅은 상기 전도성 차폐층 322와 바닥부 전도층 301 사이의 전기적 연결을 제공한다. 상기 채널 341, 342, 343, 344 에 구리를 플레이트하기 위해서, SHADOW® process 와 같은 일반적인 방법들이 사용될 수 있다. SHADOW® 은, 구리 플레이트 공정을 촉진하는 흑연을 기반으로 직접 금속화(metallization)하는 프로세스이다.

<98> 몇몇 실시예에서, 구리 플레이팅에 사용된 바로 그 기술과 물질들이, 상기 전도성 차폐층 322 와 바닥부 전도층 301을 전기적으로 연결시키기 위해 사용된다. 이러한 기술과 물질들은, 스크리닝 기술을 사용해서 은 잉크(silver ink)를 적용하는 것을 포함할 수 있다.

<99> 상기 전도성 차폐층 322와 상기 바닥부 전도층 301 사이에 전기적 연결이 형성된 후, 필요없는 구리들은, 스텝 806에서, 포토리소그래피와 같은 잘 알려진 기술을 사용해서, 상기 가요성 회로 300 으로부터 제거된다. 예를 들면, 전도성 차폐층 322의 상부에 우연히 놓여지게 된 구리들은 스텝 806에서 제거된다.

<100> 도 7F 는, 스텝 807에서, 상기 전도성 차폐층 322의 상부에 적층된 유전층 351과 플레이트된 채널 341, 342, 343, 344 를 나타낸다. 도 7G 는, 스텝 808 에서, 상기 바닥부 전도층 301의 바닥부에 적층된 유전층 352 를 나타낸다. 유전층 351, 352 는 상기 가요성 회로 350 을 외부 쇼팅(external shorting) 으로부터 보호할 수 있다. 그러나, 위에서 말한 바와 같이, 몇몇 실시예들은 단지 하나의 유전층 351, 352 을 적용하거나 또는 유전층을 적용하지 않는다.

<101> 도 7G 에 나타난 바와 같이, 상기 트레이스 311, 312, 313 은 360 도 차폐된다. 각각의 트레이스 311, 312, 313 은 상기 전도성 차폐 물질과 다른 트레이스 311, 312, 313 로부터 모든 방향에서 절연된다. 유전층 321은, 접지면(grounded plane) 322, 341, 342, 343, 344으로부터 상기 트레이스 311, 312, 313 의 상부와 사이드를 전기적으로 절연한다. 따라서, 각각의 트레이스 311, 312, 313 은 접지된 차폐 물질들로 둘어싸여 있다. 전도층 322는 상부 접지된 차폐 물질(top grounded shielding material)이며, 바닥부 전도층 301은 바닥부 차폐 물질이다. 상기 플레이트된 채널 341, 342, 343, 344는 상기 트레이스 311, 312, 313의 사이드들을 차폐하고, 전도층 322와 바닥부 전도층 301을 전기적으로 연결한다.

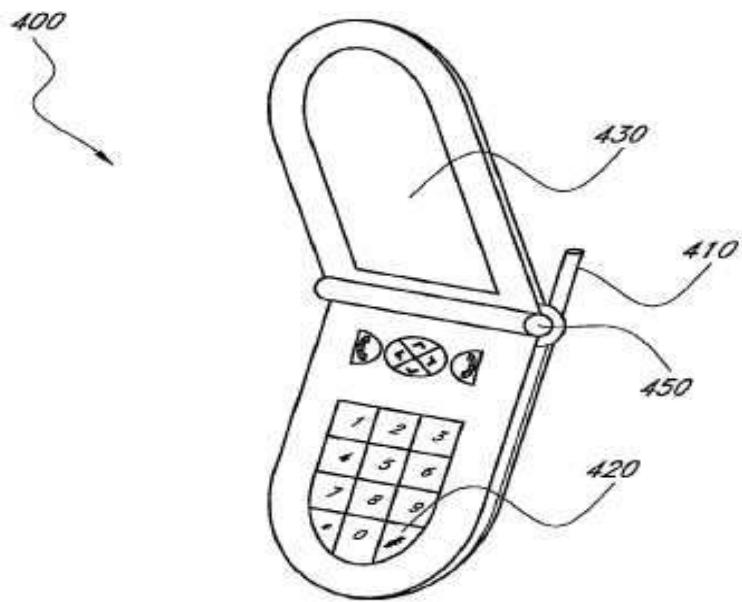

## VI. 적용예(application Example)

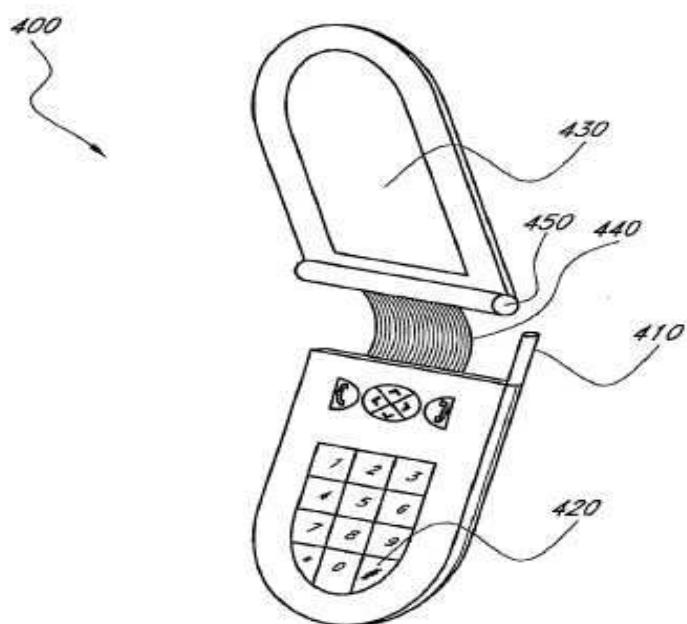

<102> 여기서 개시된 상기 차폐된 가요성 회로를 제조하는 장치와 방법은, 일예로 플립폰에 적용될 수 있다. 도 9A

는 플립폰 400의 하나의 타입을 나타낸다. 전형적인 플립폰 400은, 몸체 420, 스크린 430과 안테나 410으로 구성된다. 상기 몸체 420은, 헌지 450을 통해서 상기 스크린 430에 기계적으로 연결된다. 상기 몸체 420은, 전송되어 안테나 410로 수신된 데이터를 처리하는 회로소자로 구성된다. 따라서 전송되어 수신된 데이터에 상응하는 이미지들이 스크린 430에 디스플레이된다.

<104> 도 9B는, 몸체 420이 스크린 430으로부터 물리적으로 분리된 후의 플립폰 400을 도시한다. 보는 바와 같이, 여기서 개시된 제조 장치 및 방법에 따른 차폐된 가요성 회로 440은 상기 몸체 420과 상기 스크린 430 사이의 전기적 연결을 제공한다. 상기 차폐된 가요성 회로 440은, 상기 헌지의 회전축 450을 따라 기계적으로 가요성이 있어야 한다. 이러한 가요성은 상기 플립폰 400을 열고 닫기 위해서 필요하다. 더구나, 스트리밍 비디오(streaming video)와 같은 용도를 위해 요구되는 높은 데이터 전송 속도 때문에, 상기 차폐된 가요성 회로 440에서의 상기 트레이스는, 각각의 트레이스들을 외부 소스(external source)로부터 만들어진 EMI와 상기 가요성 회로 440의 다른 트레이스로부터 차폐할 수 있어야 한다. 따라서, 상기 차폐된 가요성 회로 440은, 상기 플립폰 400에서, 유리하게 상기 몸체 420과 상기 스크린 430 사이의 전기적 연결을 제공할 수 있다.

<105> 실시예에서는, 상기 차폐된 가요성 회로 440의 일 실시예는 EMI에 따른 실질적인 신호의 손실이나 일그러짐 없이, 데이터 전송 속도를, 2 내지 4 GHz 사이에서 조정할 수 있다. 또한, 이러한 실시예에서, 근접한 트레이스들의 중심간의 거리는 1인치의 2만분의 1 정도로 작을 수 있다.

## VII. 결론 (Conclusion)

<107> 앞에서 상기 차폐된 가요성 회로의 제조를 위한 장치와 방법들을 위한 실시예들을, 본 발명이 속하는 기술 분야의 당업자가, 이러한 구성요소를 생산하고, 이러한 방법들을 실시할 수 있도록, 자세하고, 분명하며, 정확한 용어로 설명하였다. 이러한 장치와 방법은, 그러나, 앞에서 논의된 실시예들과 완전히 일치하는 변형의 여지가 있다. 결과적으로, 이러한 장치들과 방법들은 개시된 특별한 실시예들에 한정되지 않는다. 그와는 반대로, 이러한 장치들과 방법들은 본 발명의 정신과 범위 내에서 모든 변형들을 커버한다.

### 도면의 간단한 설명

<22> 도 1A는 하나의 전도층을 갖는 가요성 회로의 일 실시예의 사시도이다.

<23> 도 1B는 에칭된 트레이스를 갖는 도 1A의 가요성 회로의 사시도이다.

<24> 도 1C는 상기 에칭된 트레이스와 절연된 유전층(dielectric layer)을 갖는 도 1B의 가요성 회로의 사시도이다.

<25> 도 1D는 상기 가요성 회로의 상부에서, 교대로 접지된 트레이스(alternate grounded traces)를 노출하는 채널을 갖는 상기 도 1C의 가요성 회로의 사시도이다.

<26> 도 1E는 상부에서 상기 교대로 접지된 트레이스와 연결된 전도성 차폐층을 가진 도 1D의 가요성 회로의 사시도이다.

<27> 도 1F는 상기 가요성 회로의 바닥부에서 교대로 접지된 트레이스를 노출하는 채널을 가진 도 1E의 가요성 회로의 사시도이다.

<28> 도 1G는 하부면에서 상기 교대로 접지된 트레이스와 연결된 전도성 차폐층을 가진 도 1F의 가요성 회로의 사시도이다.

<29> 도 1H는 교대로 접지된 트레이스를 가진 도 1G의 차폐된 가요성 회로의 하나의 구리층의 단면도이다.

<30> 도 2는 교대로 접지된 트레이스를 갖는 도 1H의 가요성 회로의 구리 단층 차폐의 제조를 위한 방법의 일 실시예를 나타내는 공정도이다.

<31> 도 3은 모든 트레이스가 차폐된 구리 단층 가요성 회로의 일 실시예의 단면도이다.

<32> 도 4는 모든 트레이스가 차폐된 도 3의 구리 단층 가요성 회로를 제조하기 위한 방법의 일 실시예를 나타내는 공정도이다.

<33> 도 5A는 두개의 전도층을 가진 가요성 회로의 일 실시예의 사시도이다.

<34> 도 5B는 에칭된 트레이스를 갖는 도 5의 가요성 회로의 상부 사시도이다.

도면

도면1A

도면1B

도면1C

도면1D

도면1E

도면1F

도면1G

도면1H

## 도면2

도면3

## 도면4

도면5A

도면5B

도면5C

도면5D

도면5E

도면6

도면7A

도면7B

도면7C

도면7D

도면7E

도면7F

도면7G

도면8

도면9A

도면9B