(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4683052号

(P4683052)

(45) 発行日 平成23年5月11日(2011.5.11)

(24) 登録日 平成23年2月18日(2011.2.18)

(51) Int.Cl.

H01C 7/10 (2006.01)

H01G 4/12 (2006.01)

F 1

H01C 7/10

H01G 4/12 4 4 5

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2008-16637 (P2008-16637)

(22) 出願日 平成20年1月28日 (2008.1.28)

(65) 公開番号 特開2009-177085 (P2009-177085A)

(43) 公開日 平成21年8月6日 (2009.8.6)

審査請求日 平成21年3月24日 (2009.3.24)

(73) 特許権者 000003067

TDK株式会社

東京都中央区日本橋一丁目13番1号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100092657

弁理士 寺崎 史朗

(72) 発明者 中野 瞳子

東京都中央区日本橋一丁目13番1号 T

D K株式会社内

(72) 発明者 小関 恭二

東京都中央区日本橋一丁目13番1号 T

D K株式会社内

最終頁に続く

(54) 【発明の名称】セラミック素子

## (57) 【特許請求の範囲】

## 【請求項 1】

内部電極層及びセラミック層を有するセラミック素体と、

当該セラミック素体の外部に前記内部電極層と電気的に接続するように設けられた下地電極と当該下地電極の外表面を覆うめっき層とを有する外部電極と、

前記セラミック素体の外表面のうち、前記外部電極によって覆われる部分以外の部分を少なくとも覆う保護層と、を備え、

前記保護層が、ケイ素酸化物、Al<sub>2</sub>O<sub>3</sub>、TiO<sub>2</sub>、ZrO<sub>2</sub>及びMgOからなる群より選ばれる少なくとも1種の絶縁性の酸化物からなる絶縁層である第1層と、該第1層と同種の絶縁性の酸化物を主成分として含有するとともに前記セラミック層を構成する元素のうち少なくとも1種と同種の元素を含有する絶縁層である第2層とを含み、

前記第1層及び前記第2層が、内側からこの順で形成されている、セラミック素子。

## 【請求項 2】

前記第1層がケイ素酸化物からなり、前記第2層が前記第1層と同種の絶縁性の酸化物としてケイ素酸化物を含有する、請求項1記載のセラミック素子。

## 【請求項 3】

前記保護層が、ケイ素を9μg/cm<sup>2</sup>以上含有する、請求項2記載のセラミック素子。

## 【請求項 4】

前記セラミック層を構成する元素に亜鉛元素が含まれ、前記第2層が亜鉛元素を含有す

10

20

る、請求項 1 ~ 3 のいずれか一項に記載のセラミック素子。

【請求項 5】

請求項 1 ~ 4 のいずれか一項に記載のセラミック素子を製造する方法であって、

バレル回転式高周波スパッタ装置に前記セラミック素体を入れ、前記絶縁性の酸化物をターゲットとしてスパッタを行うことにより、前記セラミック素体の表面に前記保護層を形成する工程と、

前記保護層が形成された前記セラミック素体の対向する両端面に前記下地電極を形成する工程と、を備え、

前記下地電極を形成する工程において、前記内部電極層が前記保護層を突き抜けることにより、前記下地電極が前記内部電極層と電気的に接続する、前記方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、セラミック素子に関する。

【背景技術】

【0002】

バリスタ、サーミスタ、インダクタ等のセラミック素子は、内部電極層及びセラミック層を有するセラミック素体と、セラミック素体の外部に、内部電極層と電気的に接続するよう設けられた外部電極とを備える。上記構成を有するセラミック素子は、プリント回路基板等に上記外部電極のはんだ付けにより固定・接続されることが多い。しかし、従来の外部電極は、そのままでははんだの熱によって溶融し易く、はんだ中に分散することによって接続不良をおこし易いものであった。そのため、従来、外部電極は、下地電極とその表面上に形成されたNi等のめっき層とを有する構成とされることで、はんだ耐熱性の向上が図られていた。このようなめっき層の形成は、製造コスト等の観点から、電気めっきにより行われることが一般的である。

20

【0003】

しかし、セラミック層が十分な絶縁抵抗性を有しない場合、このような電気めっき処理を行う際、下地電極の形成領域をはみ出してめっき層が形成される「めっき伸び」や、下地電極以外の部位にめっきが付着する「めっき付着」などの現象が生じることがあった。これらの現象は、外部電極間の短絡（ショート）を引き起こす原因として問題視されている。

30

【0004】

これら電気めっき処理時の「めっき伸び」や「めっき付着」を防止する方法として、めっき処理前に、セラミック素体の表面をガラス層及び酸化物層（又は絶縁物層）で覆う方法が開示されている（特許文献1参照）。

【特許文献1】特開2007-242995号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかし、近年のセラミック素子の小型化に伴い、外部電極間の短絡を防止する技術に対する要求は益々高まっており、従来の方法ではその要求を十分に満足することが困難になりつつある。例えば特許文献1に記載の方法によつては、外部電極間の短絡の発生原因となるめっき伸びやめっき付着を防止する効果は十分でなかった。

40

【0006】

そこで、本発明は、外部電極間の短絡の発生原因となるめっき伸びやめっき付着が抑制されたセラミック素子を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明は、内部電極層及びセラミック層を有するセラミック素体と、セラミック素体の外部に内部電極層と電気的に接続するように設けられた下地電極と下地電極の外表面を覆

50

うめっき層とを有する外部電極と、セラミック素体の外表面のうち、外部電極によって覆われる部分以外の部分を少なくとも覆う保護層とを備え、保護層が、絶縁性の酸化物を含有する絶縁層である第1層と、該第1層と同種の絶縁性の酸化物を含有するとともにセラミック層を構成する元素のうち少なくとも1種と同種の元素を含有する絶縁層である第2層とを含み、第1層及び第2層が、内側からこの順で形成されている、セラミック素子である。

#### 【0008】

上記保護層が上記特定の構成を有することにより、めっき処理時のめっき伸びやめっき付着を十分に防止することができる。そのため、本発明に係るセラミック素子は、めっき伸びやめっき付着が抑制され、外部電極間の短絡が生じにくいものとなる。10また、上述のような構成を有する保護層は、セラミック素体から剥離しにくいため、セラミック素子がプリント回路基板等に外部電極のはんだ付けにより固定・接続されるときに、はんだに含まれるフラックスがセラミック素体に接触し、セラミック素体を還元することによるセラミックス素子の表面絶縁抵抗の低下を防止することができる。

#### 【0009】

上記保護層は、上記絶縁性の酸化物としてケイ素酸化物を含有することが好ましい。これにより、保護層によるめっき伸びやめっき付着を抑制する効果がより優れたものとなる。さらに、保護層は、ケイ素を $9 \mu\text{g}/\text{cm}^2$ 以上含有することが好ましい。これにより、保護層の厚みが十分なものとなり、めっき伸びやめっき付着を抑制する効果がより一層優れたものとなる。20

#### 【0010】

上記セラミック層を構成する元素に亜鉛元素が含まれ、上記第2層が亜鉛元素を含有することが好ましい。これにより、保護層によるめっき伸びやめっき付着を抑制する効果がより優れたものとなる。

#### 【発明の効果】

#### 【0011】

本発明によれば、めっき伸びやめっき付着が抑制され、従って外部電極間の短絡を生じにくいため、セラミック素子を提供することが可能となる。また、本発明に係るセラミック素子においては、保護層が剥がれにくいため、リフロー時、はんだに含まれるフラックスがセラミック素体に接触しにくく。従って、フラックスの還元作用によるセラミック素体の表面絶縁抵抗の低下を防止することができる。30

#### 【発明を実施するための最良の形態】

#### 【0012】

以下、必要に応じて図面を参考しつつ、本発明を実施するための最良の形態について詳細に説明する。ただし、本発明は以下の実施形態に限定されるものではない。なお、図面中、同一要素には同一符号を付すこととし、重複する説明は省略する。また、図面の寸法比率は図示の比率に限られるものではない。

#### 【0013】

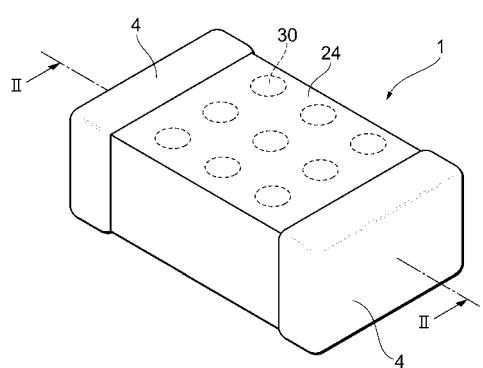

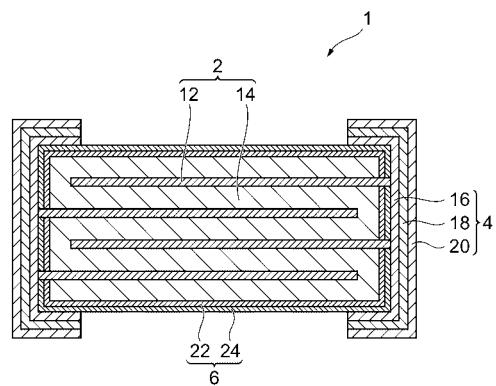

図1は、一実施形態に係るセラミック素子を示す斜視図である。図2は、図1のセラミック素子のII-II - II-II線に沿う端面図である。図1及び図2に示すセラミック素子1は、直方体状のセラミック素体2と、セラミック素体2の外部に設けられた下地電極16と下地電極16の外表面を覆うめっき層18, 20とを有する外部電極4と、セラミック素体2の外表面を覆う保護層6とから構成されるものである。40

#### 【0014】

セラミック素体2は、内部電極層12及びセラミック層14を有する。内部電極12は、例えば、銀-パラジウム合金からなる。セラミック層14は、例えば、半導体特性や磁性特性を有するものであり、酸化亜鉛等の金属酸化物から構成される。セラミック素体2は、好適には、これらの内部電極層12及びセラミック層14が4層ずつ交互に積層したものである。

#### 【0015】

10

20

30

40

50

外部電極4は、下地電極16と、下地電極16の外表面を覆うめっき層とを有する。下地電極16は、セラミック素体2の外部に、内部電極層12と電気的に接続するように設けられている。下地電極16は、例えば、Ag電極である。下地電極16の外表面を覆うめっき層は、第1めっき層18と第2めっき層20とを有する。第1めっき層18及び第2めっき層20は、内側からこの順で形成されている。例えば、第1めっき層18はNiめっき層であり、第2めっき層20はSnめっき層である。

#### 【0016】

保護層6は、セラミック素体2の外表面をほぼ全体的に覆っている。ただし、それぞれの内部電極層12の一方の端部は保護層6を貫通して保護層6の外部に露出している。保護層6は、第1層22と第2層24とを含む。

10

#### 【0017】

第1層22は、絶縁性の酸化物を含有する絶縁層である。第1層22を構成する絶縁性の酸化物は、例えば、 $\text{SiO}_2$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{TiO}_2$ 、 $\text{ZrO}_2$ 及び $\text{MgO}$ からなる群より選ばれる少なくとも1種である。第2層24は、第1層22を構成する酸化物と同種の酸化物を含有すると共に、セラミック層14を構成する元素と同種の元素を含有する。セラミック層14及び第2層24が亜鉛元素を含有することが好ましく、特に、セラミック層14及び第2層24が酸化亜鉛を含有することが好ましい。

#### 【0018】

めっき伸びやめっき付着を防止する効果が優れることから、第1層22及び第2層24は、絶縁性の酸化物として、酸化ケイ素( $\text{SiO}_2$ )などのケイ素酸化物( $\text{SiO}_x$ )を含有することが好ましい。その際、保護層6は、十分にめっき伸びやめっき付着を防止するために、ケイ素(Si)を $9 \mu\text{g}/\text{cm}^2$ 以上含有することが好ましい。一方、ケイ素の含有量は、好ましくは $106 \mu\text{g}/\text{cm}^2$ 未満、より好ましくは $67 \mu\text{g}/\text{cm}^2$ 未満、さらに好ましくは $40 \mu\text{g}/\text{cm}^2$ 未満である。ケイ素の含有量が $106 \mu\text{g}/\text{cm}^2$ 以上であると、保護層6が厚すぎて、内部電極層12が下地電極形成時の熱膨張により保護層6を貫通して下地電極16と接続することが難しくなる傾向にある。

20

#### 【0019】

なお、図1の破線で囲まれた領域30は、後述の実施例の測定方法に関するものである。

#### 【0020】

30

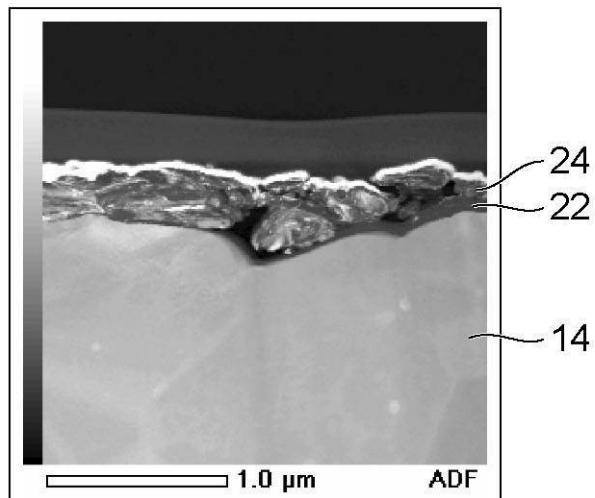

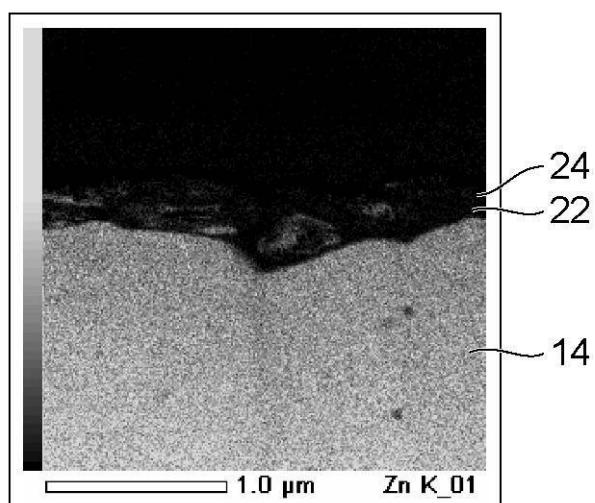

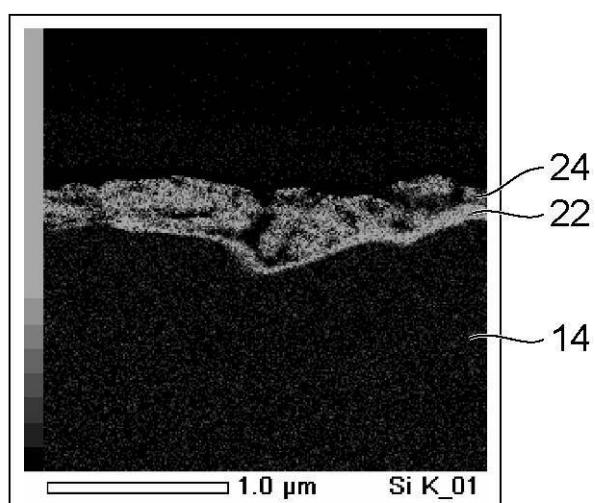

図3は、一実施形態に係るセラミック素子(バリスタ素子)断面のSTEM-EDSマッピング像である。図3は、セラミック層14を構成する元素が亜鉛元素であり、第1層22を構成する絶縁性の酸化物が酸化ケイ素であるバリスタ素子の一例を示す。図3(a)はTEM像、図3(b)はZnの分布、図3(c)はSiの分布を示す像である。図3(a)に示すように、セラミック層14の外表面を覆う保護層6は第1層22及び第2層24から構成される2層構成を有している。図3(b)から、Znは、セラミック層14及び第2層24に含有されていることが確認され、図3(c)から、Si成分は第1層22及び第2層24に含有されていることが確認される。すなわち、第2層24は、酸化ケイ素及び亜鉛元素の両方を含有している。

#### 【0021】

40

本実施形態のような、2層構造の保護層を形成する方法としては、例えば、バレル回転式RF(高周波)スパッタ装置によって第1層を構成する酸化物をターゲットとしてスパッタを行う方法がある。バレル回転数、セラミック素体の投入量、スパッタ時間等を適宜調整することにより、2層構造の保護層を形成させることができる。例えば、バレル回転数を高くする、セラミック素体の投入量を多くする、スパッタ時間を長くすると2層構造の保護膜が形成されやすい。

#### 【0022】

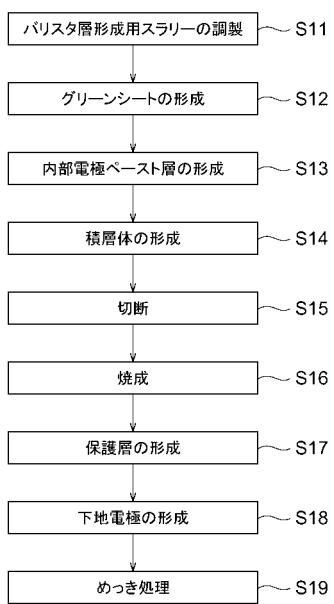

本実施形態に係るセラミック素子1は、例えば、以下に示す工程により好適に製造することができる。図4は、セラミック素子1の好適な製造工程を示すフローチャートである。

50

## 【0023】

ステップ11(S11)：セラミック層形成用スラリーの調製

主成分として酸化亜鉛(ZnO)、副成分としてコバルト(Co)、プラセオジウム(Pr)等を含む混合物を調製する。得られた混合物に、有機バインダー、有機溶剤、有機可塑剤等を加えて混合し、スラリー状とする。得られたスラリー状のものを「セラミック層形成用スラリー」とする。

## 【0024】

ステップ12(S12)：グリーンシートの形成

S11で得られたセラミック層形成用スラリーを、ドクターブレード法等の公知の方法により、ポリエチレンテレフタレート(PET)フィルム等の基材フィルム上に塗布する。塗布されたセラミック層形成用スラリーを乾燥することにより、基材フィルム上に厚さ30μm程度の膜を形成する。得られた膜を基材フィルムから剥離して、シート状のもの(以下「グリーンシート」という。)を得る。

10

## 【0025】

ステップ13(S13)：内部電極ペースト層の形成

銀-パラジウム合金(Ag-Pd合金)等の金属材料粉末に、有機バインダー等を加えて混合し、ペースト状としたもの(以下「ペースト」という。)を得る。得られたペーストを、スクリーン印刷法等により、S12で得られたグリーンシート上に印刷した後、乾燥させる。これにより、グリーンシート上に、上記ペーストからなる所定のパターン(以下「内部電極ペースト層」という。)を形成する。

20

## 【0026】

ステップ14(S14)：積層体の形成

S13で得られた、内部電極ペースト層が形成されたグリーンシートを、複数(ここでは4つ)用意する。これらを、グリーンシートと内部電極ペースト層とが交互に配置されるように積層する。さらに、内部電極ペースト層が形成されていないグリーンシートを、露出している内部電極ペースト層を覆うように積層し、全体を加圧して、積層体を形成する。

## 【0027】

ステップ15(S15)：切断

S14で得られた積層体を、所望のサイズの直方体状に切断する。得られた積層体の切断物を「グリーンチップ」とする。

30

## 【0028】

ステップ16(S16)：焼成

S15で得られたグリーンチップを、180～400にて、0.5～24時間程度加熱し、バインダーや溶剤の除去(脱バインダー)を行う。さらに、脱バインダー後のグリーンチップを1000～1400にて、0.5～8時間程度焼成することにより、グリーンチップ内の内部電極ペースト層から内部電極層12を形成し、グリーンシートからセラミック層14を形成する。このようにして、内部電極層12とセラミック層14とが交互に積層されてなる、セラミック素体2が得られる。

40

## 【0029】

ステップ17(S17)：保護層の形成

S16で得られたセラミック素体2を、バレル回転式RF(高周波)スパッタ装置に入れ、SiO<sub>2</sub>をターゲットとしてスパッタを行う。スパッタは、例えば、バレル径200mm、奥行200mmのバレル回転式RFスパッタ装置を用いて、回転数20rpmにて行うのが好ましい。このようなスパッタを行うことにより、セラミック素体2の表面に、保護層6を形成する。

## 【0030】

ステップ18(S18)：下地電極の形成

S17で得られた、保護層6が形成されたセラミック素体2の対向する両端面に、銀(Ag)を含むペースト状の金属材料を塗布した後、このペーストを550～850程度

50

で加熱する処理（焼き付け）を行う。これにより、セラミック素体2の対向する両端面に下地電極16を形成する。下地電極16は、上記加熱により膨張した内部電極層12が保護層6を突き抜けることにより、内部電極層12と接続する。

#### 【0031】

ステップ19(S19)：めっき処理

S18で形成された下地電極16の表面上に、電気めっきにより、第1めっき層18及び第2めっき層20をこの順に形成する。例えば、第1めっき層18はニッケル(Ni)めっき層であることが好ましく、第2めっき層20は錫(Sn)めっき層であることが好ましい。このようにして、下地電極16に第1めっき層18及び第2めっき層20が形成された外部電極4が得られる。

10

#### 【0032】

上記ステップS11～19により、本実施形態に係るバリスタ1が得られる。ただし、S17とS18の順序を逆にしてもよい。その場合、S19の前に、下地電極の表面に形成された保護層を除去するステップが必要となる。

#### 【実施例】

#### 【0033】

以下、実施例を挙げて本発明についてより具体的に説明する。ただし、本発明は以下の実施例に限定されるものではない。

#### 【0034】

上記ステップS11～16により、1608サイズ（約1.6mm×約0.8mm×約0.8mm）のバリスタ素体を製造した。製造したバリスタ素体は酸化亜鉛から構成されるセラミック層を有するセラミック素体である。

20

#### 【0035】

#### （実施例1）

製造したバリスタ素体2000個を、バレル径200mm、奥行200mmのバレル回転式RFスパッタ装置に入れ、SiO<sub>2</sub>をターゲットとして、バレル回転数20rpm、処理時間1.5時間の条件でスパッタを行うことにより、バリスタ素体表面に保護層を形成した。

#### 【0036】

保護層が形成されたバリスタ素体の対向する両端面に、銀(Ag)を含むペースト状の金属材料を塗布後、550～850程度で焼き付けを行うことにより、下地電極を形成した。この下地電極の外表面に対し、Niめっき処理を行い、次いで、Snめっき処を行った。このようにして、バリスタ素体に保護層、下地電極及びめっき層が形成されたバリスタを得た。

30

#### 【0037】

#### （実施例2）

バレル回転式RFスパッタ装置に一度に入れるバリスタ素体の数を25000個とし、処理時間を5時間としたこと以外は、実施例1と同様にしてバリスタを得た。

#### 【0038】

#### （比較例1）

40

バリスタ素体表面に、レーザーアブレーションによりSiO<sub>2</sub>を主成分とする保護層を形成した。次いで、実施例1と同様にして下地電極及びめっき層の形成を行い、バリスタを得た。

#### 【0039】

#### 保護層の観察

上記で作製したバリスタについて、保護層の構造をSTEM-EDSマッピングによって確認したところ、実施例では、ケイ素酸化物を含有する第1層と、ケイ素酸化物を主成分とし、亜鉛元素を含有する第2層とから構成される2層構造が形成されていた。一方、比較例ではケイ素酸化物を含有する単層の保護層が形成されていた。

#### 【0040】

50

### めっき伸び・めっき付着

実施例1～2及び比較例1で得られたバリスタの外観を観察し、下地電極の形成領域から $20\text{ }\mu\text{m}$ はみ出してめっき層が形成されている場合を「めっき伸び」、下地電極が形成されている部分以外のバリスタ素体表面に $20\text{ }\mu\text{m}$ を超える径を有してめっきが付着している場合を「めっき付着」と評価した。その結果、実施例1～2で得られたバリスタには、めっき伸びもめっき付着もほとんど認められなかつたのに対し、比較例1で得られたバリスタにはめっき伸びやめっき付着が多く認められた。

### 【0041】

#### ケイ素含有量

実施例1～2及び比較例1で得られたバリスタについて、めっき処理後の保護層におけるケイ素の含有量を、蛍光X線分析法(XRF)を用いて、測定径 $50\text{ }\mu\text{m}$ にて、試料1個につき9箇所、5試料について測定した。図1において、上記9箇所の測定箇所を、破線で囲まれた領域30により示す。表1に示されるように、実施例1～2の保護膜におけるSi含有量は $9\text{ }\mu\text{g/cm}^2$ 以上であったのに対し、比較例1の保護膜におけるSi含有量は $9\text{ }\mu\text{g/cm}^2$ 未満であった。ここで、Si含有量が多いことは、十分な厚みの保護膜が形成されていることを示すものである。

10

### 【0042】

#### 【表1】

|      | Si含有量( $\mu\text{g/cm}^2$ ) |

|------|-----------------------------|

| 実施例1 | 9-19.4                      |

| 実施例2 | 16.5-23.4                   |

| 比較例1 | 6.2-8.6                     |

20

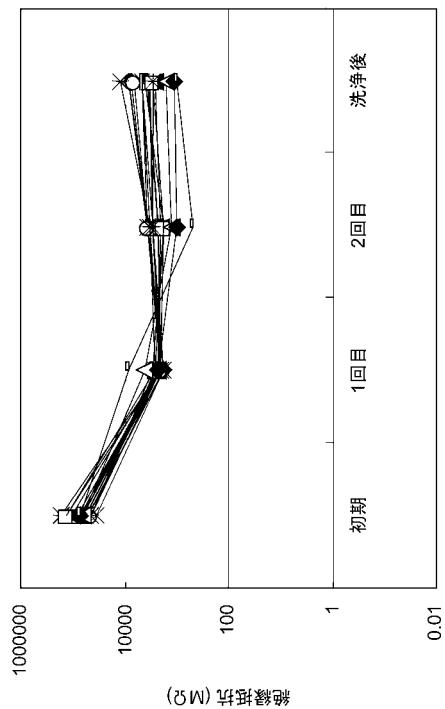

### 【0043】

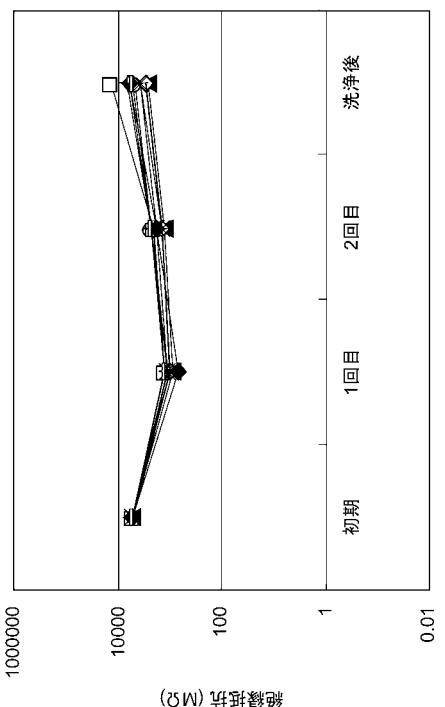

#### 絶縁抵抗変化

実施例1～2で得られたバリスタを、プリント回路基板にリフロー実装した。リフロー実装直後(初期)、実装後1回目のリフロー熱履歴後、2回目のリフロー熱履歴後、及び洗浄後のバリスタ素子の絶縁抵抗を測定し、リフロー実装による絶縁抵抗の変化を調べた。実施例1、2の結果を図5、6のグラフにそれぞれ示す。測定は複数の試料について行い、図5では $n=9$ 、図6では $n=14$ の結果を示す。グラフに示されるように、実施例1及び2で得られたバリスタ素子のリフローによる絶縁抵抗変化はほとんど見られず、バリスタ素子の表面抵抗に大きな低下はなかった。すなわち、はんだのフラックスによるバリスタ素体の還元は見られなかった。このことから、実施例1及び2で得られたバリスタにおける保護膜は剥離しにくく、リフロー時にははんだのフラックスがバリスタ素体に接触することを十分に防止できることが明らかとなった。

30

### 【産業上の利用可能性】

### 【0044】

本発明により提供されるバリスタ、サーミスタ、インダクタ等のセラミック素子は、めっき伸びやめっき付着が見られないため、小型化した場合にも短絡を生じにくい。そのため、プリント回路基板に実装される電子部品として好適に用いられる。

40

### 【図面の簡単な説明】

### 【0045】

【図1】一実施形態に係るセラミック素子を示す斜視図である。

【図2】一実施形態に係るセラミック素子を示す端面図である。

【図3】一実施形態に係るセラミック素子の保護層の2層構造を示すSTEM-EDSマッピングである。

【図4】一実施形態に係るセラミック素子の製造工程を示すフローチャートである。

【図5】実施例で作製したセラミック素子のリフローによる絶縁抵抗変化を示すグラフである。

50

【図6】実施例で作製したセラミック素子のリフローによる絶縁抵抗変化を示すグラフである。

【符号の説明】

【0046】

1 ... セラミック素子、2 ... セラミック素体、4 ... 外部電極、6 ... 保護層、12 ... 内部電極層、14 ... セラミック層、16 ... 下地電極、18 ... 第1めっき層、20 ... 第2めっき層、22 ... 第1層、24 ... 第2層

【図1】

【図2】

【図4】

【図5】

【図6】

【図3】

(a)

(b)

(c)

---

フロントページの続き

(72)発明者 相庭 尚

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 村上 幸弘

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 竹屋 和人

東京都中央区日本橋一丁目13番1号 TDK株式会社内

審査官 酒井 朋広

(56)参考文献 特開平11-219804 (JP, A)

特開平08-022901 (JP, A)

特開平03-006801 (JP, A)

特開2007-242995 (JP, A)

特開2004-088040 (JP, A)

特開平09-148108 (JP, A)

特開昭62-282410 (JP, A)

特開平01-185902 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01C 7/10

H01G 4/12