(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4191602号

(P4191602)

(45) 発行日 平成20年12月3日(2008.12.3)

(24) 登録日 平成20年9月26日(2008.9.26)

(51) Int.Cl.

F 1

H03K 19/0175 (2006.01)

H03K 19/00 1 O 1 R

H01L 21/82 (2006.01)

H01L 21/82 A

H03K 19/177 (2006.01)

H03K 19/177

請求項の数 19 (全 13 頁)

(21) 出願番号 特願2003-535333 (P2003-535333)

(86) (22) 出願日 平成14年10月2日 (2002.10.2)

(65) 公表番号 特表2005-505978 (P2005-505978A)

(43) 公表日 平成17年2月24日 (2005.2.24)

(86) 國際出願番号 PCT/EP2002/011075

(87) 國際公開番号 WO2003/032492

(87) 國際公開日 平成15年4月17日 (2003.4.17)

審査請求日 平成17年9月6日 (2005.9.6)

(31) 優先権主張番号 09/971,349

(32) 優先日 平成13年10月4日 (2001.10.4)

(33) 優先権主張国 米国(US)

(73) 特許権者 504136100

エム2000

フランス国・エフー 91570 ピブレ・

ルート デウ ジスイーホール 1 ビス

・1・パーク ピューロスペース

(74) 代理人 100064621

弁理士 山川 政樹

(72) 発明者 レブレウスキー, フレデリック

フランス国・エフー 75016 パリ・リ

ュ アントワーヌ ルシェール・2

(72) 発明者 ルパップ, オリヴィエ

フランス国・エフー 75016 パリ・リ

ュ アントワーヌ ルシェール・2

審査官 小曳 满昭

最終頁に続く

(54) 【発明の名称】スケーラブル・アキテクチャを備えた再構成可能な集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の複数の入力と、

第1の複数の出力と、

第1の1つまたは複数の機能ブロックと、そして

前記第1の複数の入力、第1の複数の出力、第1の1つまたは複数の機能ブロックに結合されて、前記第1の入力を前記第1の1つまたは複数の機能ブロックに、前記第1の1つまたは複数の機能ブロックを互いに、また前記第1の1つまたは複数の機能ブロックを前記第1の出力にそれぞれ排他的に結合する第1の複数のクロスバ・デバイスとを備え、

前記第1の1つまたは複数の機能ブロックが、前記入力、出力、1つまたは複数の機能ブロック、クロスバ・デバイスの1つまたは複数の再帰的にネストされた集合を含む少なくとも第1の機能ブロックを備え、前記第1の複数のクロスバ・デバイスが前記第1の入力を前記第1の1つまたは複数の機能ブロックに、前記第1の1つまたは複数の機能ブロックを互いに、また前記第1の1つまたは複数の機能ブロックを前記第1の出力にそれぞれ結合するのと同じように、ネストされた各集合のクロスバ・デバイスがネストされた集合の入力、出力、1つまたは複数の機能ブロックを相互に接続し、そして

前記再帰的にネストされた集合の少なくとも1つが1つまたは複数のクロスバ・デバイスに結合された1つまたは複数の再構成可能な論理ブロックを備え、前記少なくとも1つのネストされた集合の少なくとも1つの出力が前記少なくとも1つのネストされた集合の

前記論理ブロックの出力のサブセットに直接に結合されている、装置。

**【請求項 2】**

前記第1の複数のクロスバ・デバイスが、第1、第2、第3のサブセットを含み、前記第1のサブセットが前記第1の複数の入力信号を前記第1の1つまたは複数の機能ブロックの入力へ送信し、前記第2のサブセットが前記第1の1つまたは複数の機能ブロックの出力を前記第1の1つまたは複数の機能ブロックの入力へ送信し、かつ前記第3のサブセットが前記第1の1つまたは複数の機能ブロックの出力を前記第1の複数の出力へ配線する請求項1に記載の装置。

**【請求項 3】**

前記サブセットの少なくとも2つが同じサブセットである請求項2に記載の装置。 10

**【請求項 4】**

3つのサブセットがすべて同じサブセットである請求項2に記載の装置。

**【請求項 5】**

前記第1の機能ブロックが、

第2の複数の入力と、

第2の複数の出力と、

第2の1つまたは複数の機能ブロックと、

前記第2の複数の入力、第2の複数の出力、第2の1つまたは複数の機能ブロックに結合されて、前記第1の複数のクロスバ・デバイスが、前記第1の入力を前記第1の1つまたは複数の機能ブロックに、前記第1の1つまたは複数の機能ブロックを互いに、また前記第1の1つまたは複数の機能ブロックを前記第1の出力にそれぞれ結合するのと同じように、前記第2の複数の入力を前記第2の1つまたは複数の機能ブロックに、前記第2の1つまたは複数の機能ブロックを互いに、また前記第2の1つまたは複数の機能ブロックを前記第2の複数の出力にそれぞれ排他的に結合する第2の複数のクロスバ・デバイスとを備える請求項1に記載の装置。 20

**【請求項 6】**

前記第2の複数のクロスバ・デバイスが、第1、第2、第3のサブセットを含み、前記第1のサブセットが前記第2の複数の入力信号を前記第2の1つまたは複数の機能ブロックの入力へ配線し、前記第2のサブセットが前記第2の1つまたは複数の機能ブロックの出力を前記第2の1つまたは複数の機能ブロックの入力へ配線し、かつ前記第3のサブセットが前記第2の1つまたは複数の機能ブロックの出力を前記第2の複数の出力へ配線する請求項5に記載の装置。 30

**【請求項 7】**

前記サブセットの少なくとも2つが同じサブセットである請求項6に記載の装置。

**【請求項 8】**

3つのサブセットがすべて同じサブセットである請求項6に記載の装置。

**【請求項 9】**

前記第2の1つまたは複数の機能ブロックが、入力、出力、1つまたは複数の機能ブロック、クロスバ・デバイスの1つまたは複数の再帰的にネストされた集合を含む第2の機能ブロックを備え、前記第1の複数のクロスバ・デバイスが前記第1の入力を前記第1の1つまたは複数の機能ブロックに、前記第1の1つまたは複数の機能ブロックを互いに、また前記第1の1つまたは複数の機能ブロックを前記第1の出力にそれぞれ結合するのと同じように、ネストされた各集合のクロスバ・デバイスが、ネストされた集合の入力、出力、1つまたは複数の機能ブロックを相互に接続している請求項5に記載の装置。 40

**【請求項 10】**

前記第2の機能ブロックが、

第3の複数の入力と、

第3の複数の出力と、

第3の1つまたは複数の機能ブロックと、

前記第3の複数の入力、第3の複数の出力、第3の1つまたは複数の機能ブロックに結合されて、前記第2の複数のクロスバ・デバイスが前記第2の入力を前記第2の1つまたは複数の機能ブロックに、前記第2の1つまたは複数の機能ブロックを互いに、前記第2の1つまたは複数の機能ブロックを前記第2の出力にそれぞれ結合し、前記第1の複数のクロスバ・デバイスが前記第1の入力を前記第1の1つまたは複数の機能ブロックに、前記第1の1つまたは複数の機能ブロックを互いに、前記第1の1つまたは複数の機能ブロックを前記第1の出力にそれぞれ結合するのと同じように、前記第3の複数の入力を前記第3の1つまたは複数の機能ブロックに、前記第3の1つまたは複数の機能ブロックを互いに、また前記第3の1つまたは複数の機能ブロックを前記第3の複数の出力にそれぞれ排他的に結合する第3の複数のクロスバ・デバイスとを備える請求項9に記載の装置。 10

**【請求項11】**

前記装置が集積回路の形成に使用される埋込論理ブロックである請求項1に記載の装置。

**【請求項12】**

前記装置が集積回路である請求項1に記載の装置。

**【請求項13】**

前記入力、出力、1つまたは複数の機能ブロック、クロスバ・デバイスの1つまたは複数の再帰的にネストされた集合の少なくとも1つが、

それぞれの論理ブロックがn個の入力とo個の出力( $m, n$ および $o$ は整数)を有し、少なくとも1つの集合の出力として与えられる前記o出力のサブセットを持つm個の再構成可能な論理ブロックと、 20

それぞれのクロスバ・デバイスが、前記m個の再構成可能な論理ブロックの前記n個の入力に対応して結合されたm個の出力を有するn個のクロスバ・デバイスとを備え、前記m個の再構成可能な論理ブロックの出力が、最大限、前記n個のクロスバ・デバイスの入力の第1のサブセットと、前記n個のクロスバ・デバイスの入力の第2のサブセットに結合された少なくとも1つのネストされた集合の各入力とに結合されている請求項1に記載の装置。

**【請求項14】**

前記装置の各クロスバ・デバイスの出力が単一のファンアウトを有し、前記装置の各クロスバ・デバイスはその装置の別のクロスバ・デバイスに対して1つの入力だけを供給する請求項13に記載の装置。 30

**【請求項15】**

前記装置の各クロスバ・デバイスの出力が単一のファンアウトを有し、前記装置の各クロスバ・デバイスはその装置の別のクロスバ・デバイスに対して1つの入力だけを供給する請求項1に記載の装置。

**【請求項16】**

機能ブロックであって、

それぞれの論理ブロックがn個の入力とo個の出力( $n, o$ は整数)を有し、かつ、前記機能ブロックの出力がo個の出力でm個のサブセットに直接に結合されている、m個( $m$ は整数)の再構成可能な論理ブロックと、そして 40

それが、前記m個の再構成可能な論理ブロックの前記n個の入力に対応して結合されたm個の出力を有するn個のクロスバ・デバイスとを備え、

前記m個の再構成可能な論理ブロックの出力が、最大限、前記n個のクロスバ・デバイスの入力の第1のサブセットと、前記n個のクロスバ・デバイスの入力の第2のサブセットに結合された前記機能ブロックの各入力とに結合されている、

機能ブロック。

**【請求項17】**

前記機能ブロックが集積回路の形成に使用される埋込論理ブロックである請求項15に記載の機能ブロック。

10

20

30

40

50

**【請求項 18】**

前記少なくとも 1 つのネストされた集合の少なくとも 1 つの入力が前記少なくとも 1 つのネストされた集合の前記クロスバ・デバイスの入力のサブセットに直接に結合されている、請求項 1 に記載の装置。

**【請求項 19】**

前記機能ブロックの少なくとも 1 つの入力が前記少なくとも 1 つのネストされた集合の前記クロスバ・デバイスの入力のサブセットに直接に結合されている、請求項 16 に記載の機能ブロック。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は集積回路（IC）の分野に関する。さらに詳細に述べると、本発明は再構成可能な集積回路の構成に関する。

**【背景技術】****【0002】**

IC の設計および製造技術は一般に知られている。長年にわたって、IC の設計および製造技術が向上し続けているので、単一の IC にパッケージ化される電子素子の数が増加しており、これら素子間の相互接続がますます複雑になっている。密度および複雑性が増すにつれ、IC 製造マスクを作成する費用もこれに応じてかなり増加した。

**【発明の開示】**

20

**【発明が解決しようとする課題】****【0003】**

論理の全体という観点で見た場合、最近の IC 製品ファミリの異なった商品間、または連続して提供される商品間で、それらの機能が比較的わずかしか増加していないことが多い。それゆえ、新しい IC マスクのコストが高いことならびにその他の要因を考慮すると、より多くの IC 設計者が、一部を再構成することによって異なった商品間での機能の変化を吸収できる IC を得ることを望んでいる。

**【0004】**

米国特許第 5 5 7 4 3 8 8 号はエミュレーション応用向けに設計された再構成可能な集積回路を開示している。集積されたデバッグ装置を特に含むこの構成は所期の用途に特に適している。しかしながら、汎用目的の部分的に再構成可能な集積回路は別の一連の課題を提示している。1 つの望ましい特性は、使用する素子面積と配線し易さの間の柔軟性のあるトレードオフを提供するスケーラビリティである。したがって、再構成可能な集積回路構成の改良が望まれている。

30

**【課題を解決するための手段】****【0005】**

集積回路（IC）がいくつかの機能ブロックを含み、その機能ブロックの少なくとも 1 つは再構成可能な機能ブロックである。各機能ブロックは、再構成可能な機能ブロックでも、または再構成不能な機能ブロックでも、または同一構成のものと相互接続された「ネストされた」機能を附加して再帰的に拡張されたブロックでもよい。この IC はさらにいくつかの外部入力ピン、およびいくつかの外部出力ピンを備えている。

40

**【0006】**

各素子は、少なくとも IC レベルにおいて、入力信号はすべてクロスバ・デバイスの第 1 のサブセットを経由して外部入力ピンから機能ブロックに送信され、内部信号はすべてクロスバ・デバイスの第 2 のサブセットを経由して 1 つの機能ブロックから別の機能ブロックへ送信され、かつ出力信号はすべてクロスバ・デバイスの第 3 のサブセットを経由して各機能ブロックから出力ピンへ送信されるように結合されている。

**【0007】**

1 つの実施態様において、各クロスバ・デバイスの出力は単一のファンアウトを有する。さらに、各クロスバ・デバイスは別のクロスバ・デバイスに対して 1 つの入力だけを供

50

給することができる。

**【発明を実施するための最良の形態】**

**【0008】**

本発明を、添付図面に示した模範的な実施形態によって説明するが、本発明はこれに限定されるものではない。図中、同一の参照数字は同一の素子を表している。

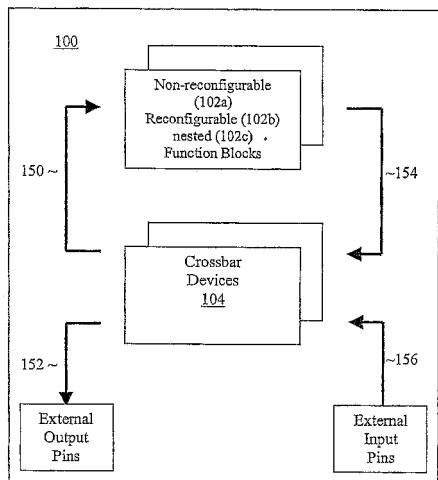

図1はスケーラブル・アーキテクチャを組み込んだ、1つの実施形態による本発明の再構成可能な集積回路の概略図である。

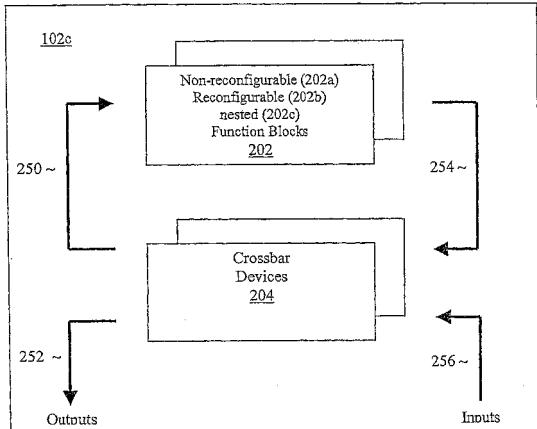

図2はスケーラブル・アーキテクチャを組み込んだ、1つの実施形態による本発明の再構成可能な集積回路の概略図である。

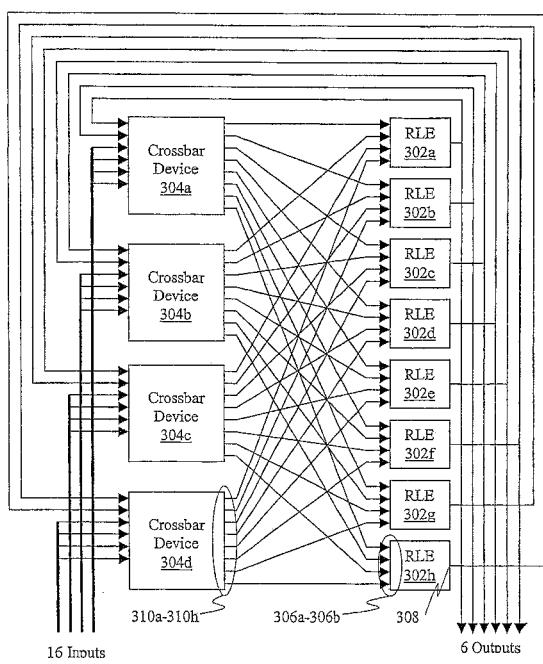

図3は1つの実施形態による、再構成可能な機能ブロックのさらに詳細な図である。 10

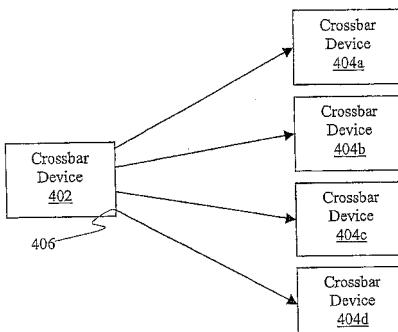

図4は1つの実施形態による、クロスバ間の相互接続を示す図である。

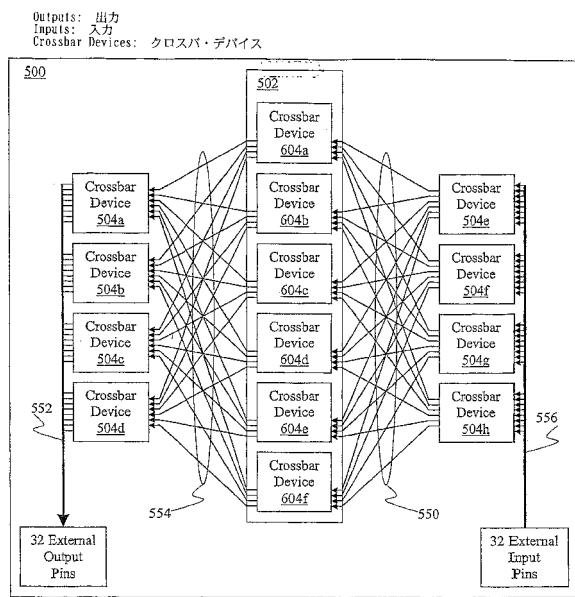

図5は図1と図2の再構成可能な集積回路の1つの実施形態をさらに詳細に示した図である。

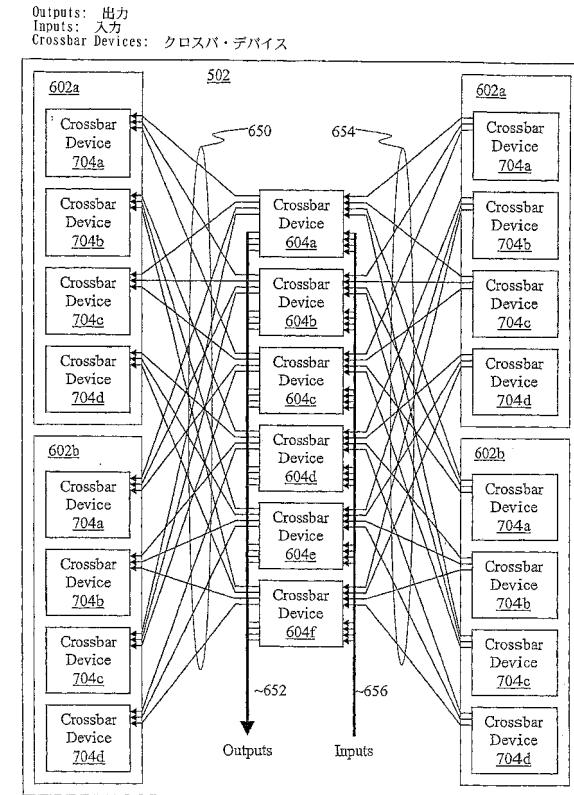

図6は図1と図2の再構成可能な集積回路の別の実施形態をさらに詳細に示した図である。

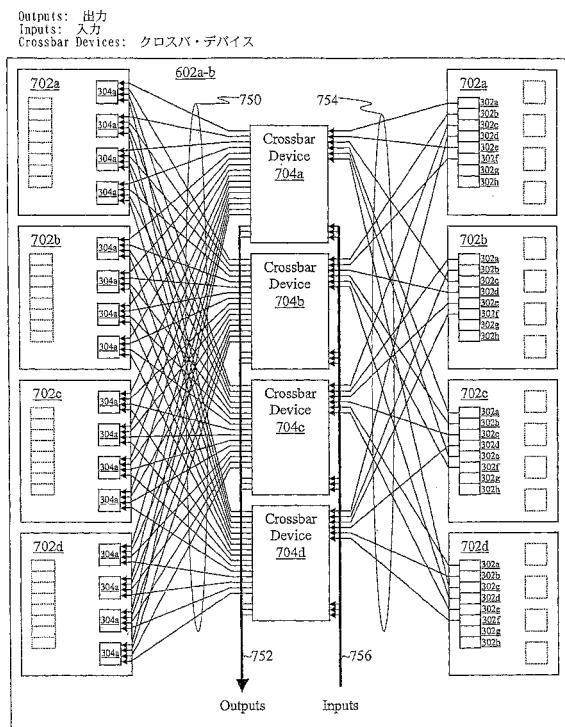

図7は図1と図2の再構成可能な集積回路の別の実施形態をさらに詳細に示した図である。

**【0009】**

以下の説明においては、本発明の完全な理解を得るために、説明上、特定の番号、材質および構成を定めておく。しかしながら、本発明は特定の詳細な説明なしでも実施できることが当業者には明白であろう。他の例では、本発明が不明瞭にならないようによく知られた特徴は省略するかまたは簡略化している。 20

**【0010】**

また、「1つの実施形態において」という語句が繰り返し使用されている。この語句は、同じ実施形態を指す場合も、別の実施形態を指す場合もある。本出願で使用されているような、「備えている」、「含む」、「有する」等の用語は同義語である。

**【0011】**

図1について説明すると、1つの実施形態による本発明の再構成可能な集積回路(100)の概要をブロック図で示す。図に示すように集積回路(IC)100はいくつかの機能ブロック102といくつかのクロスバ・デバイス104を含んでいる。IC100はさらにいくつかの外部出力ピンと入力ピンを含んでいる。機能ブロック102はIC100の論理を与え、一方、ロスバ・デバイス104は信号をIC100の内外に送信するとともに、IC100内の各機能ブロック間で送信するための信号送信経路を提供している。以下でより詳細に説明するように、有利なことには、新しいアーキテクチャにしたがって各素子がひとまとめに結合されたことにより、簡単に拡張縮小できる方法(スケーラブル方法)で所望の配線経路を達成することが可能になり、素子が使用する面積対配線し易さのトレードオフの柔軟性が増している。 30

**【0012】**

機能ブロック102は、再構成不能な機能ブロック102a、再構成可能な機能ブロック102b、および/または「ネストされた」機能ブロック102cを含む。たとえば、機能ブロック102は、プロセッサ・コア、記憶装置制御器、バス・ブリッジなどの再構成不能な機能ブロック102aを含んでいる。それに加えて、またはその代わりに、機能ブロック102は、PLDまたはFPGAで見られるものと同様の再構成可能回路、ISAバスもしくはEISAバスをサポートしているものの間、またはI2CもしくはSPIシリアル・コミュニケーション・インターフェースをサポートしているものの間などで再構成してかわりの機能をサポートするものなどの再構成可能な機能ブロック102b含んでいてもよい。「ネストされた」機能ブロック102c内の機能ブロックは、機能ブロック102、外部入力と外部出力、およびクロスバ・デバイス104をICレベル(「ルート」または「最も高い」または「最も外側の」レベルとも呼ばれる)で相互に接続するために、同一の相互接続アーキテクチャに従って体系化され、かつ一緒に相互接続されてい 40 50

る。「ネストされた」機能ブロックの各集合は、再構成不能な機能ブロック、再構成可能な機能ブロック、および／または同一の相互接続アーキテクチャに従って相互接続されている「ネストされた」機能ブロックを含むことができる。最終的に、「最も深い」ネスト・レベル（「最も低い」または「最も内側の」ネスト・レベルとも呼ばれる）で、各々の機能ブロックは、同一の相互接続アーキテクチャに従って相互接続された再構成不能な機能ブロックかまたは再構成可能な機能ブロックである。

#### 【0013】

各クロスバ・デバイス104は、数が固定した入力と数が固定した出力を有している。その出力はすべて、制約なしにどのような入力からも同時に経路を通して送信することができる（これは完全に実装されたクロスバとも呼ばれる）。クロスバ・デバイス104の他の重要な特性は、信号が常にクロスバ・デバイスを通って同じ方向に伝わる（すなわち、入力から出力へ）ことである。しかし、これは、通過トランジスタ双方向クロスバ・デバイスまたは有線ないしは一方向クロスバ・デバイスまたはバッファーとしてはたらく、一方向クロスバ・デバイスのような任意のクロスバ・デバイスで実施することができる。図1に示したように、I Cレベルにおいて、各素子は以下の方法でお互いに結合される。

a) クロスバ・デバイス104の第1のサブセットが、コネクション156とコネクション150の第1のサブセットを経由して外部入力ピンを機能ブロック102の入力の第1のサブセットに配線している。

b) 次に、クロスバ・デバイス104の第2のサブセットが、コネクション154の第1のサブセットとコネクション150の第2のサブセット経由で、機能ブロック102の出力の第1のサブセットを機能ブロック102の入力の第2のサブセットに配線している。

c) さらに、クロスバ・デバイス104の第3のサブセットが、コネクション154の第2のサブセットおよびコネクション152経由で機能ブロック102の出力の第2のサブセットを外部出力ピンに配線している。

#### 【0014】

したがって、外部入力ピンはすべて、クロスバ・デバイス104の第1のサブセットを経由して各機能ブロック102に与えられている。内部信号はすべて、クロスバ・デバイス104の第2のサブセットを経由して1つの機能ブロック102から別の機能ブロック102に送られ、また出力信号はすべて、クロスバ・デバイス104の第3のサブセットを経由して各機能ブロック102から外部出力ピンに送られる。

#### 【0015】

このクロスバ・デバイス104の第1、第2および第3のサブセットは重なる場合もあれば重ならない場合もあり、また3つのサブセットのそれぞれがクロスバ・デバイス104の集合全体を含んでいても良いことに注意する必要がある。同様に、機能ブロック102の入力の第1および第2のサブセットが重なる場合もあれば重ならない場合もあり、また2つのサブセットのそれぞれが機能ブロック102の入力の集合全体を含んでいても良い。同じように、機能ブロック102の出力の第1および第2のサブセットが重なる場合もあれば重ならない場合もあり、また2つのサブセットのそれぞれが機能ブロック102の出力の集合全体を含んでもよい。

#### 【0016】

図2に示すように、ネストされた機能ブロック102cの各集合は、いくつかの機能ブロック202（「ネストされた」機能ブロック202cの集合か、再構成不能な機能ブロック202aか、再構成可能な機能ブロック202bでよい）とクロスバ・デバイスを含んでいる。この機能ブロック202は、I Cレベルにおいてトポロジ的には機能ブロック102と類似の位置を占めており、一方、クロスバ・デバイス204は、I Cレベルにおいてトポロジ的にクロスバ・デバイス104と類似の位置を占めている。入力はI Cレベルにおいてトポロジ的に外部入力ピンと類似の位置を占めており、出力はI Cレベルにおいてトポロジ的に外部出力ピンと類似の位置を占めている。したがって、

a) クロスバ・デバイス204の第1のサブセットが、コネクション256およびコネ

10

20

30

40

50

クション 250 の第 1 のサブセット経由で入力を機能ブロック 202 の入力の第 1 のサブセットに配線する。

b) 次に、クロスバ・デバイス 204 の第 2 のサブセットが、コネクション 254 の第 1 のサブセットおよびコネクション 250 の第 2 のサブセット経由で機能ブロック 202 の出力の第 1 のサブセットを機能ブロック 202 の入力の第 2 のサブセットに配線する。

c) さらに、クロスバ・デバイス 204 の第 3 のサブセットが、コネクション 254 の第 2 のサブセットおよびコネクション 252 経由で機能ブロック 202 の出力の第 2 のサブセットを出力に配線する。

#### 【0017】

したがって、入力はすべて、クロスバ・デバイス 204 の第 1 のサブセットを経由して各機能ブロック 202 に提供されている。内部信号はすべて、クロスバ・デバイス 204 の第 2 のサブセットを経由して 1 つの機能ブロック 202 から別の機能ブロック 202 に送られ、また出力信号はすべて、クロスバ・デバイス 204 の第 3 のサブセットを経由して各機能ブロック 202 から外部出力に送られる。10

#### 【0018】

I C レベルと同様に、クロスバ・デバイス 204 の第 1 、第 2 、第 3 のサブセットは重なる場合もあれば重ならない場合もあり、また 3 つのサブセットのそれぞれがクロスバ・デバイス 204 の集合全体を含んでいても良い。同様に、機能ブロック 202 の入力の第 1 および第 2 のサブセットが重なる場合もあれば重ならない場合もあり、また 2 つのサブセットのそれぞれが機能ブロック 202 の入力の集合全体を含んでいても良い。同じように、機能ブロック 202 の出力の第 1 および第 2 のサブセットは重なる場合もあれば重ならない場合もあり、また 2 つのサブセットのそれぞれが機能ブロック 202 の出力の集合全体を含んでいても良い。20

#### 【0019】

各クロスバ・デバイス 204 は I C レベルのクロスバ・デバイス 104 と同じタイプである。

#### 【0020】

したがって、本発明のもとでは、本発明の各機能ブロック 102 をより良好な素子使用面積と配線し易さ間のトレードオフをもたらすように帰納的に拡張することができる。必要な信号送信経路が比較的少ない I C 100 を実装するためには、少数のクロスバ・デバイスと単一レベルの機能ブロックを用い、本発明の相互接続アーキテクチャに従って相互に接続すればよい。しかしながら、より多くの機能ブロックを必要とする I C 100 を実装するためには、( I C レベルで各素子を相互に接続するのと同じやり方で各ネスト・レベルの素子を相互に接続して) 1 つまたは複数の機能ブロック 102 を 1 回または複数回帰納的に拡張すればよい。それに対応して、各帰納レベルにおいて機能ブロックのいくつかの入力と出力を供給する。このように、本発明の I C 100 は、高度にスケーラビリティであり、使用面積、速度および配線し易さのバランスにおいて柔軟性がある。30

#### 【0021】

理解しやすくするために、上記の説明では I C 100 を外部入力ピンおよび外部出力ピンを有するものとしているが、本発明は、入力または出力の一方だけの外部ピン、または入力か出力になるように構成できる外部ピンとして実装することができる。40

#### 【0022】

図 3 は、図 1 の再構成可能な機能ブロック 102 b および図 2 の再構成可能な機能ブロック 202 b の 1 つの実施形態をさらに詳細に示している。この再構成可能な機能ブロックは再構成可能な論理素子 ( R L E ) の集合を含んでいる。 R L E は少数の論理ゲート ( 一般に 10 個以下 ) に相当する簡単な論理機能とフリップフロップなどの記憶機能を遂行するように構成することができる素子である。たとえば簡単な論理機能は、 4 入力 1 出力の真理値表として使用される 16 ピット RAM を使用して行なうことができる。図示するように、この実施形態に対して、再構成可能な機能ブロック 102 b は、それぞれ n 個の入力 306 a ~ 306 d ( n = 4 ) と o 個の出力 308 ( o = 1 ) とを持つ m 個の R L E 50

302a～304h (m = 8)、およびそれぞれm個の出力310a～310h (クロスバ・デバイスの出力の数はRLEの数に等しい)を持つn個のクロスバ・デバイス304a～304d (クロスバ・デバイスの数はRLE入力の数に等しい)を含んでいる。RLE302a～302hはいくつかの論理機能を遂行するために再構成すること可能である一方、クロスバ・デバイス304a～304dは、RLEへの入力信号の配線経路、および各RLE間の信号配線経路に柔軟性をもたらす。クロスバ・デバイス304a～304dの出力は、RLE302a～302hのそれぞれの入力に結合され(クロスバの出力の数はRLEの数に等しいので、各RLEはクロスバ・デバイスの各々から1つの入力を受信する)、一方、RLE302a～302hのそれぞれの出力はクロスバ・デバイス304a～304dの各々の入力に最大限に結合される。すなわち、RLEからの出力がn1個有り、クロスバ・デバイスがn2個有る場合、各々のRLEの出力が1つのクロスバ・デバイスに相互に接続され、最大の相互接続が形成されたクロスバ・デバイスへの相互接続の数と最小の相互接続が形成されたクロスバ・デバイスへの相互接続の数の差は1となる。図示した実施形態に対しては、RLE302a～302hからの出力が8つ有り、クロスバ・デバイス304a～304dが4つ有るので、各々のクロスバ・デバイスは2つのRLEから信号を受信する。

#### 【0023】

再構成可能な機能ブロックの入力はクロスバ・デバイス304a～304dの入力に直接供給され、再構成可能な機能ブロックの出力はRLEの出力のサブセット(これはRLEの出力の集合全体を含んでいてもよい)に直接供給される。図示した実施形態において、クロスバ・デバイス304a～304dの各々が4つの入力を受信し、6つのRLE302a～302fだけが出力を供給する。

#### 【0024】

図示しやすくするために、上記の説明では、8つのRLE、6つの出力、16の入力を有する再構成可能な機能ブロック102bを示している。本発明は、より多くのRLE、より多くの出力およびより多くの入力を有し、同一アーキテクチャのもので実施することができる。

#### 【0025】

図4は、IC100の1つの実施形態のクロスバ・デバイス間の結合を示している。IC100のネストされた機能ブロック102c/202cが全体として拡張された場合、IC100は、相互に接続された、再構成不能な機能ブロック102a/202a、再構成可能な機能ブロック102b/202b、クロスバ・デバイス、外部入力ピン、外部出力ピンの集合に縮小する。IC100の配線可能性を増加させるためには、機能ブロックの出力と機能ブロックの入力との間、外部入力ピンと機能ブロックの入力との間、さらには機能ブロックの出力と外部出力ピンとの間の異なった送信経路を最大数用意することが好ましい。すなわち、クロスバ・デバイス402の1つの出力だけが他のクロスバ・デバイス404a～404dの各々に接続される。さらに、より大きな速度をもたらすために、各クロスバ・デバイスの出力の容量負荷は最小限に低減すべきである。すなわち、どのようなクロスバ・デバイスの出力406も单一のクロスバ・デバイスの入力に接続される。したがって、本発明のもとでは、クロスバ・デバイス402が、最大数のクロスバ・デバイス404a～404dに入力を供給し、その結果、出力容量負荷を最小限に低減しつつ送信経路の数を最大にする。

#### 【0026】

図5～7は、図1～2の再構成可能な集積回路の1つの実施をさらに詳細に示している。図示したように、IC500は、「ネストされた」機能ブロック502の集合を1個、8個のクロスバ・デバイス504a～504h、32個の外部出力ピン、32個の外部入力ピンおよびコネクション550、552、554、556を含んでいる。クロスバ・デバイス504e～504hは、ICレベルにおけるクロスバ・デバイスの第1のサブセットであり、コネクション556、550経由で外部入力ピンをネストされた機能ブロック502の入力に配線する。クロスバ・デバイス504a～504dは、ICレベルにおけ

るクロスバ・デバイスの第3のサブセットであり、コネクション554、552経由でネストされた機能ブロック502の出力を外部出力ピンに送る。本発明において、I C レベルにおけるクロスバ・デバイスの第2のサブセットは空である。したがって、「ネスト」された機能ブロック502の集合は、I C レベルにおいてトポロジ的に機能ブロック102の位置を占め、クロスバ・デバイス504a～504hは、トポロジ的に、I C レベルのクロスバ・デバイス104の位置を占め、またコネクション550、552、554、556は、トポロジ的に、I C レベルのコネクション150、152、154、156の位置をそれぞれ占めている。クロスバ・デバイス604a～604fはネストされた機能ブロック502のクロスバ・デバイスの一部である（ネストされた機能ブロック502の他のネストされた素子は図示していない）。

10

#### 【0027】

図6はネストされた機能ブロック集合502の1つの実装を示している。ネストされた機能ブロック502は、2個のネストされた機能ブロック602a～602b（図示する目的上、入力と出力の接続パターンを明快にするために、ブロック602a～602bの表示を2回使用している）、6個のクロスバ・デバイス604a～604f、24個の入力、24個の出力、コネクション650、652、654、656を含む。クロスバ・デバイス604a～604fはネストされた機能ブロック・レベルにおけるクロスバ・デバイスの第1、第2、第3のサブセットであり、それぞれが、コネクション656、650経由で入力を機能ブロック602a～602bの入力に、コネクション654、650経由で機能ブロック602a～602bの出力を機能ブロック602a～602bの入力に、またコネクション654、652経由で機能ブロック602a～602bの出力を出力に送る。したがって、ネストされた機能ブロック602a～602bは、トポロジ的に、ネストされた機能ブロック・レベルの機能ブロック202の位置を占めており、一方、クロスバ・デバイス604a～604fは、トポロジ的に、ネストされた機能ブロック・レベルのクロスバ・デバイス204の位置を占めており、またコネクション650、652、654、656は、トポロジ的に、ネストされた機能ブロック・レベルのコネクション250、252、254、256の位置をそれぞれ占めている。クロスバ・デバイス704a～704dはネストされた機能ブロック602a～602bのクロスバ・デバイスである（ネストされた機能ブロック602a～602bの他のネストされた素子は図示していない）。

20

#### 【0028】

図7はネストされた機能ブロック602a～602bの1つの実装を示している。ネストされた機能ブロック602a～602bは4つのプログラム可能な機能ブロック702a～702d（図示する目的上、入力と出力の接続パターンを明快にするために、ブロック702a～702dの表示を2回使用している）、4つのクロスバ・デバイス704a～704d、12個の入力、12個の出力、コネクション750、752、754、756を含む。クロスバ・デバイス704a～704dはネストされた機能ブロック・レベルにおけるクロスバ・デバイスの第1、第2、第3のサブセットであり、それぞれが、コネクション756、750経由で入力を機能ブロック702a～702dの入力に、コネクション754、750経由で機能ブロック702a～702dの出力を機能ブロック702a～702dの入力に、またコネクション754、752経由で機能ブロック702a～702dの出力を出力に送る。したがって、ネストされた機能ブロック702a～702dは、トポロジ的に、ネストされた機能ブロック・レベルの機能ブロック202の位置を占めており、クロスバ・デバイス704a～704dは、トポロジ的に、ネストされた機能ブロック・レベルのクロスバ・デバイス204の位置を占めており、またコネクション750、752、754、756は、トポロジ的に、ネストされた機能ブロック・レベルのコネクション250、252、254、256の位置をそれぞれ占めている。プログラム可能な機能ブロック702a～702dは、上に述べ、図3に示したプログラム可能な機能ブロックの実施と同じものである。

30

#### 【0029】

40

50

I C 5 0 0 の各クロスバ・デバイスは、数が固定した入力と数が固定した出力を有しており、そのため、信号が常にクロスバ・デバイスを通って同じ方向に伝わることが本発明の重要な特性の1つであることに注目する必要がある。しかし、本発明は、通過トランジスタ双方向クロスバ・デバイスまたは有線ないしは一方向クロスバ・デバイスまたはバッファーとしてはたらく一方向クロスバ・デバイスのような種類のクロスバ・デバイスアーキテクチャでも実現することができる。

#### 【0030】

さらに、I C 5 0 0 の各クロスバ・デバイス間の接続はすべて、上に開示し、図4に示したルールに従って行われる。

#### 【0031】

例示と理解を容易にするために、わざわざI C 5 0 0 を少数の素子で示していることに注意する必要がある。しかしながら、当業者は、I C 5 0 0 の実装を拡張して実際的に商品に相当するようにできることを了解するだろう。たとえば、

a) I C レベルは、16個の「48入力、48出力」クロスバ・デバイス、1個の第1レベルのネストされた機能ブロック、384個の入力、384個の出力を備えることができ、

b) 第1レベルのネストされた機能ブロックは、48個の「32入力、48出力」クロスバ・デバイス、24個の第2レベルのネストされた機能ブロック、384個の入力、384個の出力を含むことができ、

c) 第2レベルのネストされたブロックは、16個の13入力、35の出力のクロスバ・デバイス、8個のプログラム可能な機能ブロック、80個の入力、48個の出力を含むことができ、

d) プログラム可能な機能ブロックは、4個の「20入力、16出力」クロスバ・デバイス、16個の「4入力、1出力」R L E、64個の入力、16個の出力を含むことができ。

#### 【0032】

したがって、I C は3092個のR L E、384個の外部出力ピンおよび384個の外部入力ピンを有する。

#### 【0033】

このように、スケーラブル・アーキテクチャを有する完全にまたは部分的に再構成可能な集積回路について説明してきた。上記例示した実施形態によって本発明の集積回路を説明したが、当業者は本発明が説明した実施形態に限定されるものではないことを了解するであろう。さらに、本発明を集積回路として説明したが、そうしないで、本発明をI C の一部を形成する埋込論理ブロックとして実現することもできる。したがって、本発明は、添付の請求範囲の精神と範囲内で変更および変形して実施することができる。それゆえこの説明は、本発明を限定するものではなく、例示するものとみなすべきである。

#### 【図面の簡単な説明】

#### 【0034】

【図1】スケーラブル・アーキテクチャを組み込んだ、1つの実装形態による本発明の再構成可能な集積回路の概略図である。

【図2】スケーラブル・アーキテクチャを組み込んだ、1つの実装形態による本発明の再構成可能な集積回路の概略図である。

#### 【図3】1つの実装形態による、再構成可能な機能ブロックのさらに詳細な図である。

#### 【図4】1つの実装形態による、クロスバ間の相互接続を示す図である。

【図5】図1と図2の再構成可能な集積回路の1つの実装形態をさらに詳細に示した図である。

【図6】図1と図2の再構成可能な集積回路の別の実施形態をさらに詳細に示した図である。

【図7】図1と図2の再構成可能な集積回路の別の実施形態をさらに詳細に示した図である。

10

20

30

40

50

【図1】

Non-reconfigurable: 再構成不能

Reconfigurable: 再構成可能

nested: ネストされた

function Blocks: 機能ブロック

Crossbar Devices: クロスバ・デバイス

External Output Pins: 外部出力ピン

External Input Pins: 外部入力ピン

【図2】

Non-reconfigurable: 再構成不能

Reconfigurable: 再構成可能

nested: ネストされた

function Blocks: 機能ブロック

Crossbar Devices: クロスバ・デバイス

Outputs: 出力

Inputs: 入力

【図3】

102b or 202b

Outputs: 出力

Inputs: 入力

Crossbar Devices: クロスバ・デバイス

【図4】

Crossbar Devices: クロスバ・デバイス

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開平11-239053(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/00