(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6004927号

(P6004927)

(45) 発行日 平成28年10月12日(2016.10.12)

(24) 登録日 平成28年9月16日(2016.9.16)

(51) Int.Cl.

G06F 12/06 (2006.01)

F 1

G06F 12/06 515H

請求項の数 8 (全 16 頁)

(21) 出願番号 特願2012-268806 (P2012-268806)

(22) 出願日 平成24年12月7日 (2012.12.7)

(65) 公開番号 特開2014-115791 (P2014-115791A)

(43) 公開日 平成26年6月26日 (2014.6.26)

審査請求日 平成27年12月2日 (2015.12.2)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】情報処理装置、その制御方法、及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

CPUを含むSOCダイと、該SOCダイ上に複数のメモリが積層状に設けられるメモリデバイスとを具備する情報処理装置であって、

ジョブを受け付ける受付手段と、

前記受付手段によって受け付けたジョブを実行するために、前記複数のメモリのうち、前記SOCダイから物理的に最も離れたメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てるメモリ制御手段と、

前記メモリ制御手段によって割り当てられたメモリ領域を使用して前記ジョブを実行する実行手段と

を備えることを特徴とする情報処理装置。

## 【請求項 2】

CPUを含むSOCダイと、該SOCダイ上に複数のメモリが積層状に設けられるメモリデバイスとを具備する情報処理装置であって、

ジョブを受け付ける受付手段と、

前記受付手段によって受け付けたジョブが実行中において、割り当てられたメモリ領域に頻繁にアクセスするジョブであるか否かを判定する判定手段と、

前記判定手段によって前記ジョブがメモリ領域に頻繁にアクセスするジョブであると判定されると、前記複数のメモリのうち、前記SOCダイから物理的に最も離れたメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てる、前記判定手

段によって前記ジョブがメモリ領域に頻繁にアクセスするジョブでないと判定されると、前記複数のメモリのうち、前記S O C ダイから物理的に最も近いメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てるメモリ制御手段と、

前記メモリ制御手段によって割り当てられたメモリ領域を使用して前記ジョブを実行する実行手段と

を備えることを特徴とする情報処理装置。

**【請求項 3】**

前記受付手段によって受け付けたジョブが実行中において、割り当てられたメモリ領域に頻繁にアクセスするジョブであるか否かをジョブごとに示すフラグを格納したテーブルをさらに備え、

前記判定手段は、前記フラグを参照して、割り当てられたメモリ領域に頻繁にアクセスするジョブであるか否かを判定することを特徴とする請求項 2 に記載の情報処理装置。

**【請求項 4】**

前記実行手段は、複数のジョブを同時に実行することを特徴とする請求項 2 又は 3 に記載の情報処理装置。

**【請求項 5】**

前記メモリ制御手段は、

1つのメモリから前記ジョブを実行するために必要なメモリ領域が確保できない場合は、複数のメモリに渡って当該メモリ領域を割り当てる特徴とする請求項 1 乃至 4 の何れか 1 項に記載の情報処理装置。

**【請求項 6】**

C P U を含む S O C ダイと、該 S O C ダイ上に複数のメモリが積層状に設けられるメモリデバイスとを具備する情報処理装置の制御方法であって、

受付手段が、ジョブを受け付ける受付ステップと、

メモリ制御手段が、前記受付ステップにおいて受け付けたジョブを実行するために、前記複数のメモリのうち、前記 S O C ダイから物理的に最も離れたメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てるメモリ制御ステップと、

実行手段が、前記メモリ制御ステップにおいて割り当てられたメモリ領域を使用して前記ジョブを実行する実行ステップと

を実行することを特徴とする情報処理装置の制御方法。

**【請求項 7】**

C P U を含む S O C ダイと、該 S O C ダイ上に複数のメモリが積層状に設けられるメモリデバイスとを具備する情報処理装置の制御方法であって、

受付手段が、ジョブを受け付ける受付ステップと、

判定手段が、前記受付ステップにおいて受け付けたジョブが実行中において、割り当てられたメモリ領域に頻繁にアクセスするジョブであるか否かを判定する判定ステップと、

メモリ制御手段が、前記判定ステップにおいて前記ジョブがメモリ領域に頻繁にアクセスするジョブであると判定されると、前記複数のメモリのうち、前記 S O C ダイから物理的に最も離れたメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当て、前記判定ステップにおいて前記ジョブがメモリ領域に頻繁にアクセスするジョブでないと判定されると、前記複数のメモリのうち、前記 S O C ダイから物理的に最も近いメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てるメモリ制御ステップと、

実行手段が、前記メモリ制御ステップにおいて割り当てられたメモリ領域を使用して前記ジョブを実行する実行ステップと

を実行することを特徴とする情報処理装置の制御方法。

**【請求項 8】**

請求項 6 又は 7 に記載された情報処理装置の制御方法における各ステップを、コンピュータに実行させるためのプログラム。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、C P Uを含むS O Cダイに積層されるW i d e I Oメモリデバイスを具備する情報処理装置、その制御方法、及びプログラムに関するものである。

**【背景技術】****【0002】**

現行の情報処理装置では、O Sや各種アプリケーションを実行するためのデータの保存や、画像処理を実行するための一時データ保存のために、D R A M ( D y n a m i c R a n d o m A c c e s s M e m o r y )を用いることが一般的である。このD R A Mは、C P UやS O C等に接続され使用される。また、近年、情報処理装置の多機能化・高機能化に伴い、D R A Mのメモリ帯域が増加している。このメモリ帯域を増加させるために、D D R 3やD D R 4等の規格ではデータアクセスのクロック周波数を増大させ帯域を増加させている。また、C P UやA S I Cに接続する複数のD R A Mチャネルを有することで帯域を確保している。

**【0003】**

しかし、クロックの高周波数化や複数のメモリチャネルによる構成では、消費電力が増加するという新たな問題が発生する。そこで現在注目されているのが次世代D R A M規格であるW i d e I Oである。W i d e I OはT S V ( T h r o u g h S i l i c o n V i a )による3 D積層技術を使い、S O Cダイの上にD R A Mチップを重ねるメモリ技術である。特徴としては、5 1 2 b i tの広いデータ幅で最大1 2 . 8 G B / s e c以上の高帯域であるとともに、アクセス周波数を低く抑えているので低消費電力であることが挙げられる。また、T S Vを採用したことで、従来のP o P ( P a c k a g e o n P a c k a g e )に比べてパッケージサイズも薄く小さくすることができる。さらに詳細な特徴として、S O Cパッケージ内に積層することで熱対策として、温度センサを内蔵し温度によってセルフリフレッシュ率を変化させる。また、データ幅5 1 2 b i tを1 2 8 b i t単位の4チャネルに分割し、各チャネルを独立制御する特徴を有する。例えば、チャネル1とチャネル2とをセルフリフレッシュ状態でチャネル3とチャネル4を通常使用するなどの使い方ができる。特許文献1には、このようなW i d e I Oの基本的な構造や基本アクセス方法に関する技術が提案されている。

**【先行技術文献】**

30

**【特許文献】****【0004】**

【特許文献1】米国特許公開2 0 1 2 / 0 0 1 8 8 8 5号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、上記従来技術には以下に記載する問題がある。W i d e I Oの積層化構造は、構造的に熱の影響を受けやすい。例えば、ダイの特定領域と、この特定領域の上層部に位置するW i d e I OのD R A Mを同時に活性化すると、活性化された部分が局所的に温度上昇を引き起こす。これにより、温度に対して指數関数的に上昇する半導体のリーク電流が増大し、消費電力が大きくなってしまう。また、D R A Mは各セルに備えられたコンデンサに電荷を保存することでデータの記憶を行っているが、このコンデンサは半導体のリーク電流により自然に放電を行うため、D R A Mはリフレッシュ動作によりコンデンサの電荷の充電を行う必要がある。この電荷の放電は温度に依存し、温度が高いほど放電スピードが速い。したがって、温度が高くなると、リフレッシュ頻度を増加させる必要があり、リフレッシュによる消費電力の増加やリフレッシュ中はD R A MにアクセスできないことによるD R A Mのアクセス性能の低下を引き起こしてしまう。

**【0006】**

特にS O Cダイに一番近いメモリ層はS O Cダイと直接密接し、非常に高温になるため、S O Cダイに一番近いメモリ層に対してメモリアクセスすると、上記消費電力の増加や

40

50

、アクセス性能の低下といった悪影響は更に大きくなる。よって、上記温度が高くなることによる悪影響を軽減するため、温度が低いメモリ層を優先してアクセスする制御が必要になる。

#### 【0007】

本発明は、上述の問題に鑑みて成されたものであり、S O C ダイとメモリ層との位置関係から S O C ダイの熱の影響が小さいメモリ層を優先的に使用し、D R A M のリフレッシュ頻度やリーク電流を低減する仕組みを提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

本発明は、C P U を含む S O C ダイと、該 S O C ダイ上に複数のメモリが積層状に設けられるメモリデバイスとを具備する情報処理装置であって、ジョブを受け付ける受付手段と、前記受付手段によって受け付けたジョブを実行するために、前記複数のメモリのうち、前記 S O C ダイから物理的に最も離れたメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てるメモリ制御手段と、前記メモリ制御手段によって割り当てられたメモリ領域を使用して前記ジョブを実行する実行手段とを備えることを特徴とする。

#### 【0009】

また、本発明は、C P U を含む S O C ダイと、該 S O C ダイ上に複数のメモリが積層状に設けられるメモリデバイスとを具備する情報処理装置であって、ジョブを受け付ける受付手段と、前記受付手段によって受け付けたジョブが実行中において、割り当てられたメモリ領域に頻繁にアクセスするジョブであるか否かを判定する判定手段と、前記判定手段によって前記ジョブがメモリ領域に頻繁にアクセスするジョブであると判定されると、前記複数のメモリのうち、前記 S O C ダイから物理的に最も離れたメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当て、前記判定手段によって前記ジョブがメモリ領域に頻繁にアクセスするジョブでないと判定されると、前記複数のメモリのうち、前記 S O C ダイから物理的に最も近いメモリからの順に従って、該ジョブを実行するためのメモリ領域を優先して割り当てるメモリ制御手段と、前記メモリ制御手段によって割り当てられたメモリ領域を使用して前記ジョブを実行する実行手段とを備えることを特徴とする。

#### 【発明の効果】

#### 【0010】

本発明は、例えば、S O C ダイとメモリ層との位置関係から S O C ダイの熱の影響が小さいメモリ層を優先的に使用し、D R A M のリフレッシュ頻度やリーク電流を低減する仕組みを提供できる。

#### 【図面の簡単な説明】

#### 【0011】

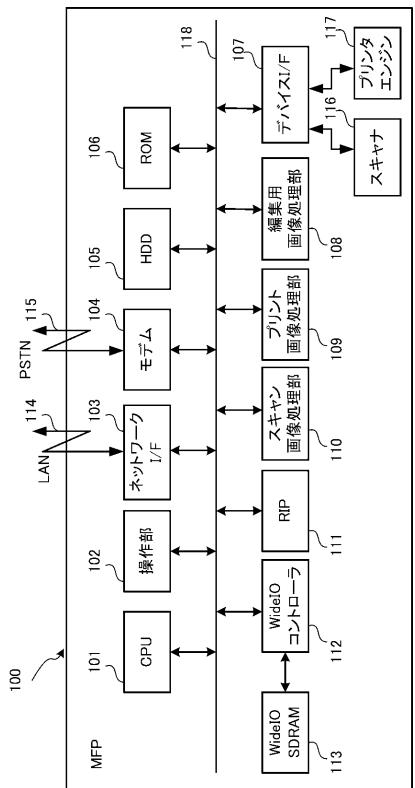

【図1】第1の実施形態に係るM F P (デジタル複合機)の全体構成を示すブロック図。

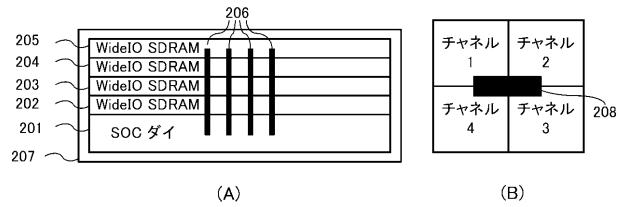

【図2】第1の実施形態に係るW i d e I O - S D R A M の構造を示す模式図。

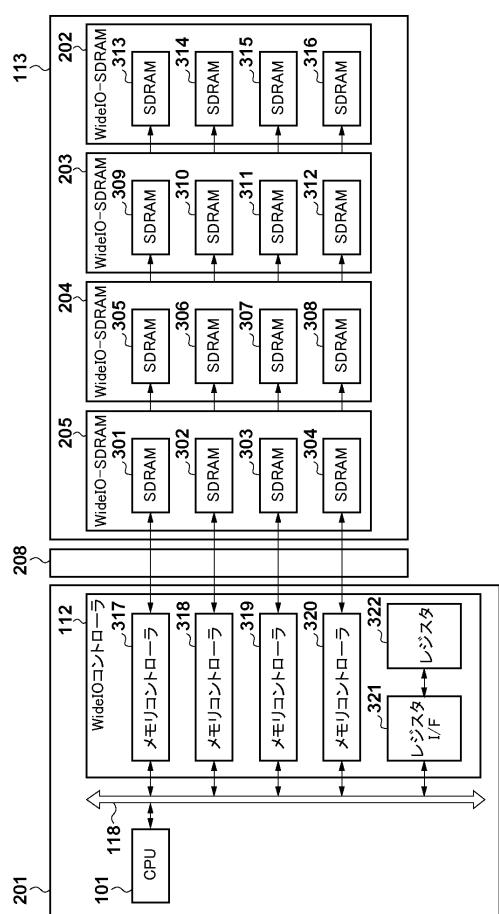

【図3】第1の実施形態に係るW i d e I O コントローラ112の構成を示すブロック図。

。

【図4】第1の実施形態に係るレジスタ322の構成を示すブロック図。

【図5】第1の実施形態に係るW i d e I O - S D R A M の割当てアドレスを示す模式図。

。

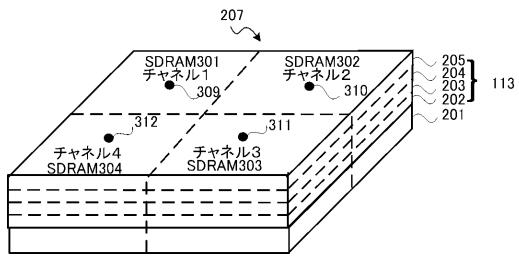

【図6】第1の実施形態に係るW i d e I O - S D R A M のパッケージ構成を示す模式図

。

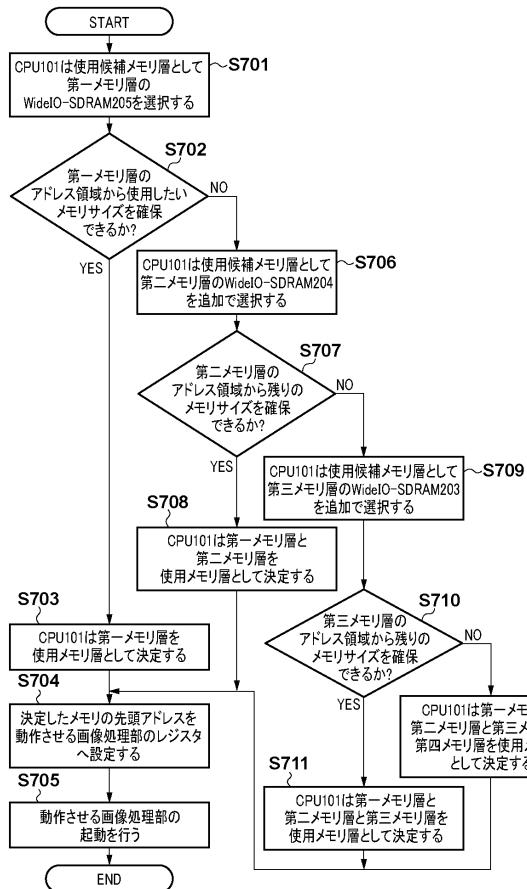

【図7】第1の実施形態に係る処理フローを示すフローチャート。

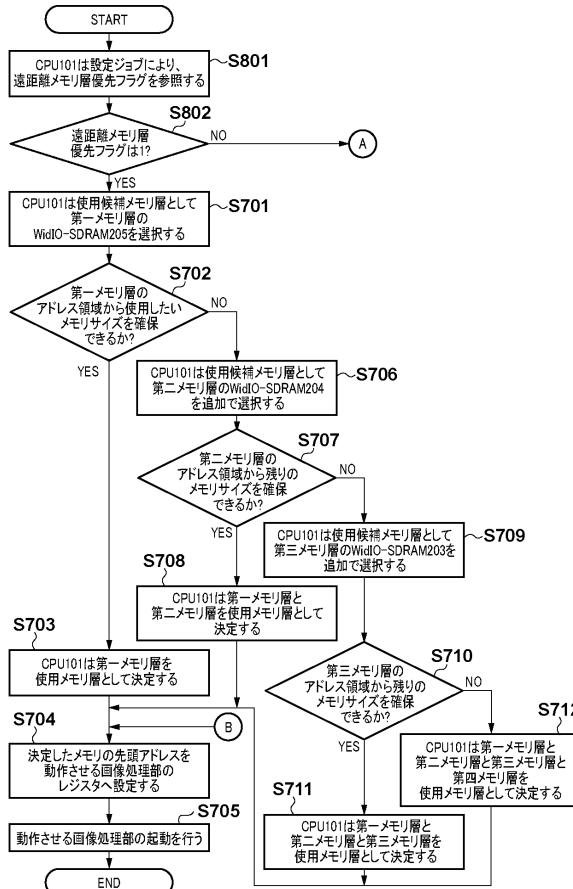

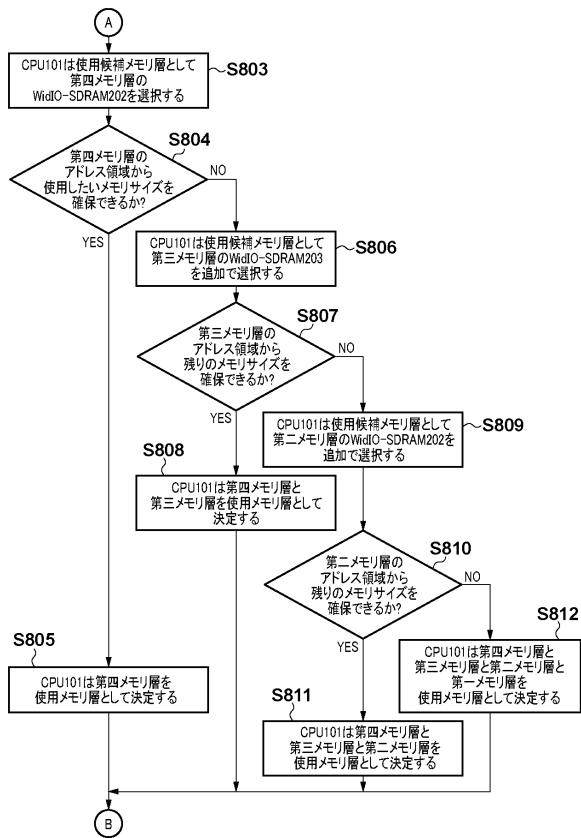

【図8 A】、

【図8 B】第2の実施形態に係る処理フローを示すフローチャート。

#### 【発明を実施するための形態】

#### 【0012】

10

20

30

40

50

以下、添付図面を参照して本発明の実施形態を詳しく説明する。尚、以下の実施形態は特許請求の範囲に係る本発明を限定するものでなく、また本実施形態で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。尚、本実施形態に係るWideIOを備える情報処理装置として、スキャナ、プリンタ、コピーなどの複数の機能を有するMFP（デジタル複合機）を例に説明する。

#### 【0013】

＜第1の実施形態＞

＜情報処理装置の構成＞

まず、図1を参照して、本実施形態に係るMFP（デジタル複合機）の全体構成について説明する。本実施形態では、情報処理装置として、MFP（Multi Functional Peripheral）を例に説明する。MFP100は、画像入力デバイスであるスキャナ116と画像出力デバイスであるプリンタエンジン117とを有し、これらはデバイスインターフェース（I/F）107を介してシステムバス118に接続されている。そしてCPU101の制御の下に、スキャナ116による原稿の画像の読み取りや、プリンタエンジン117による印刷を行うことができる。またMFP100は、LAN114や公衆回線（PSTN）115と接続しており、これらを介してLANや公衆回線に接続された外部機器のデバイス情報や画像データの入出力を行うことができる。

10

#### 【0014】

CPU101は、ROM106に記憶されたブートプログラムによりHDD105からWideIO-SDRAM113に展開されたプログラムを実行することにより、このMFP100の動作を制御している。操作部102は、キーボードやタッチパネル等の入力部や表示部を有し、ユーザからの指示を受付け、また表示部によりユーザへのメッセージや処理の結果などを表示する。ネットワークI/F103は、例えばLANカード等で実現され、LAN114を介して外部機器との間でデバイス情報や画像データの入出力を行う。モジュール104は、公衆回線115を介して外部機器との間で制御情報や画像データの入出力を行う。HDD105はハードディスクドライブであり、OSや各種アプリケーションプログラム等を記憶し、また入力された画像データ等を格納する。ROM106は、ブートプログラムや各種データを記憶している。デバイスI/F107は、スキャナ116やプリンタエンジン117と接続し、これらスキャナ116やプリンタエンジン117とシステムバス118との間で画像データの転送処理を行う。

20

#### 【0015】

編集用画像処理部108は、画像データの回転や変倍、色処理、トリミング・マスキング、2値変換、多値変換、白紙判定等の各種画像処理を行う。プリント画像処理部109は、プリンタエンジン117に出力する画像データに対して、そのプリンタエンジン117に応じた画像処理等を行う。スキャナ画像処理部110は、スキャナ116から入力される画像データに対して、補正、加工、編集等の各種処理を行う。RIP（ラスタイメージプロセッサ）111は、ページ記述言語（PDL）コードをイメージデータに展開する。WideIOコントローラ112は、メモリ制御手段として機能し、例えばCPU101や各画像処理部からのメモリアクセスコマンドをWideIO-SDRAM113が解釈可能なコマンドに変換して、WideIO-SDRAM113に対してアクセスを行う。WideIO-SDRAM113は、CPU101により実行されるプログラムを格納し、またCPU101が動作するためのシステムワークメモリを提供している。また、入力された画像データを一時記憶するための画像メモリもある。システムバス118は上述した各部とCPU101とを接続し、制御信号やデータ等を転送している。

30

#### 【0016】

＜WideIO-SDRAMの構成＞

次に、図2を参照して、本実施形態に係るWideIOメモリデバイスとしてWideIO-SDRAM113の構造について説明する。図2（A）はWideIO-SDRAMとSOCダイを側面から見た側面図であり、図2（B）は上側から見た上面図である。

40

#### 【0017】

50

SOCダイ201は、本第1の実施形態では例えばCPU101やデバイスI/F107, RIP111、各画像処理部108～110等を備えるものである。WideIO-SDRAM202～205はSOCダイ201の上に積層され、シリコン貫通ビア(TSV)206によりSOCダイ201と接続されている。WideIO-SDRAMは、必要とするメモリ容量に応じて最大4層まで積層することができ、図2(A)は4層を積層した例を示す。SOCパッケージ207は、SOCダイ201とWideIO-SDRAM202～205とを1つのパッケージに収容したものである。WideIO-SDRAMI/F208は、図2(B)に示されるようにSOCダイ201やWideIO-SDRAM202～205の中央部に配置される。

## 【0018】

10

## &lt;WideIOコントローラの構成&gt;

次に、図3を参照して、本実施形態に係るWideIOコントローラ112の内部構成について説明する。図3において、WideIOコントローラ112は、図1に示したようにシステムバス118とWideIO-SDRAM113との間に接続されている。なお、図3では、WideIO-SDRAM205がSOCダイ201に物理的に最も近いように見えるが、図3では物理的な位置関係に従って図示していない。WideIO-SDRAM205、204、203、202とSOCダイとの物理的な位置関係については図6を用いて後述する。

## 【0019】

20

SDRAM301～304、305～308、309～312、313～316は、WideIO-SDRAM205、204、203、202にそれぞれ備えられる4つのメモリであり、図示されている通り、各々が専用IFを備える。これらの専用IFは上述したようにSOCダイに積層されるWideIO-SDRAM202～205の各4チャネルに相当し、WideIO-SDRAMIF208のことである。メモリコントローラ317～320は、システムバス118からのメモリアクセスコマンドを図示されているように対となるSDRAMに対して、SDRAMが解釈可能なコマンドに変換してアクセスを行う。

## 【0020】

メモリコントローラ317は、WideIO-SDRAM202～205のチャネル1に対応するSDRAM301、305、309、313を制御するメモリコントローラであり、WideIO-SDRAMIF208のチャネル1を介して接続される。メモリコントローラ318は、WideIO-SDRAM202～205のチャネル2に対応するSDRAM302、306、310、314を制御するメモリコントローラであり、WideIO-SDRAMIF208のチャネル2を介して接続される。メモリコントローラ319は、WideIO-SDRAM202～205のチャネル3に対応するSDRAM303、307、310、315を制御するメモリコントローラであり、WideIO-SDRAMIF208のチャネル3を介して接続される。メモリコントローラ320は、WideIO-SDRAM202～205のチャネル4に対応するSDRAM304、308、312、316を制御するメモリコントローラであり、WideIO-SDRAMIF208のチャネル4を介して接続される。レジスタI/F321は図示しないレジスタアクセス専用バスを経由してCPU101からのレジスタアクセスを受け付けるためのインターフェース部である。レジスタ322はCPU101から設定されるメモリコントローラ317～320の各動作モード設定情報を記憶する。

30

## 【0021】

40

## &lt;レジスタの構成&gt;

次に、図4を参照して、レジスタ322におけるレジスタの構成例について説明する。レジスタ322は、メモリコントローラ動作モード設定レジスタ401～416から構成される。メモリコントローラ動作モード設定レジスタ401～416はメモリコントローラ317～320の動作モードを設定するためのレジスタである。メモリコントローラ動作モード設定レジスタ401～416は、それぞれSDRAM301～316に対応して

50

いる。

【0022】

<WideIO-SDRAMの割り当てアドレス領域>

次に、図5を参照して、SDRAM301～316に対して割り当てられたアドレス領域について説明する。本実施形態においては、図5に示すように、SDRAM301～316はそれぞれアドレス領域1～16を割り当てられているものとする。

【0023】

アドレス領域0x0000\_0000～0x2000\_0000にはSOCダイ201より物理的に最も離れているメモリ層(第1メモリ層又は最上位メモリ層)のWideIO-SDRAM205のSDRAM301～304が割り当てられている。アドレス領域0x2000\_0000～0x4000\_0000にはSOCダイ201より二番目に離れているメモリ層(第2メモリ層)のWideIO-SDRAM204のSDRAM305～308が割り当てられている。アドレス領域0x4000\_0000～0x6000\_0000にはSOCダイ201より三番目に離れているメモリ層(第3メモリ層)のWideIO-SDRAM203のSDRAM309～312が割り当てられている。アドレス領域0x6000\_0000～0x8000\_0000にはSOCダイ201より四番目に離れているメモリ層(第4メモリ層又は最下位メモリ層)のWideIO-SDRAM202のSDRAM313～316が割り当てられている。ただし、各アドレス領域のサイズは図5に図示したものに限定されるものではない。

【0024】

<SOCパッケージ>

次に、図6を参照して、SOCパッケージ207におけるWideIO-SDRAM202～205とSOCダイ201との物理的な位置関係について説明する。SOCダイ201は、CPU101やデバイスI/F107、各画像処理部108～110等を含んでいる。SOCパッケージの平面を4分割した時の左上、右上、右下、左下がそれぞれ図2(B)のチャネル1～4に相当する。また、同様に、図3のSDRAM301～304、305～308、309～312、313～316にも相当している。

【0025】

図6に示した通り、WideIO-SDRAM113は、SOCダイ上に複数のメモリが積層状に設けられる。また、本実施形態においては、SDRAM301～304、305～308、309～312、313～316の各デバイスは、図6のようにSOCダイ201の各上部にそれぞれ4層構成で積層されているものとする。SOCダイ201と、WideIO-SDRAM202～205との物理的な位置関係は、SOCダイ201とWideIO-SDRAM202とが最も近い位置に配置される。また、WideIO-SDRAM203、204、205の順でSOCダイ201から遠ざかるように配置される。

【0026】

<メモリ割り当て領域の決定フローチャート>

次に、図7を参照して、コピーやプリント等のジョブを受け付けた後に、該当ジョブを実行するために動作させる必要がある画像処理部に対して、割り当てるメモリ領域を決定する処理フローについて説明する。即ち、本フローチャートはCPU101がジョブを受け付けた後、かつジョブの実行を行う前に行われるものである。なお、以下で説明する処理は、CPU101がROM106、HDD105等に予め格納された制御プログラムをWideIO-SDRAM113に読み出して実行することにより実現される。

【0027】

S701において、CPU101は、使用候補のメモリ層として第1メモリ層のWideIO-SDRAM205を選択する。つまり使用候補のメモリ層として、SOCダイ201より最も離れたメモリ層(本実施例では最上位メモリ層)のWideIO-SDRAM205を選択する。続いて、S702において、CPU101は、第1メモリ層のSDRAMのアドレス領域から現在動作させたい画像処理部が必要とするメモリサイズだけメ

10

20

30

40

50

モリ領域を確保できるか否かを判定する。即ち、WideIO-SDRAM205に割り当てられた $0 \times 0000_0000 \sim 0 \times 2000_0000$ の領域から画像処理部が必要とするメモリサイズを確保できるか否かを判定する。確保できると判定するとS703に進み、確保できないと判定するとS706に進む。

#### 【0028】

ここで、メモリ割り当て領域の管理（空き領域の確認）について説明する。本実施形態における実行するジョブが使用するメモリ領域の割り当て管理は、CPU101により行われる。CPU101は、選択されたメモリ層のアドレス領域の全アドレスについて、既に割り当て済のジョブによって、割り当てられているか否かをチェックする。本実施形態におけるメモリ領域の割り当て管理は、一般的に行われているようにソフトウェアにより全アドレスに対する割り当てテーブルを作成し、当該割り当てテーブルによりアドレスの割り当て状況を確認しながら行われる。CPU101は、当該割り当てテーブルを参照しながら、割り当て状況をチェックし、動作させたい画像処理部が必要なメモリ領域分のアドレスがまだ割り当てられていない場合には、メモリサイズを確保できると判断する。具体的には、CPU101は、必要なサイズだけWideIO-SDRAM205に割り当てられたメモリ領域からメモリを確保することができると判定した場合、S703において、CPU101は第1メモリ層を使用するメモリ層として決定する。

#### 【0029】

ここで、メモリ割り当て領域の管理（使用メモリの決定）について説明する。本実施形態における使用するメモリ層の決定は、CPU101により行われる。CPU101は、使用候補のメモリ層のアドレス領域からメモリサイズを確保できると判断すると、使用候補のメモリ層を使用するメモリ層として決定する。まず初めに、CPU101は、第1メモリ層のアドレス領域からメモリサイズを確保する。CPU101は、上記割り当てテーブルを参照し、現在割り当てられていないアドレス領域の中から、使用するアドレスについて割り当てるよう割り当てテーブルを更新する。続いて、CPU101は、決定したメモリ層へメモリアクセスするようにメモリコントローラ317～320のメモリコントローラ動作モード設定レジスタ401～416に対して設定を行う。S703では、CPU101は、WideIO-SDRAM205に対応するメモリコントローラ動作モード設定レジスタ401～404に対して設定を行い、SDRAM301～304がメモリアクセス可能な状態にする。

#### 【0030】

次に、S704において、CPU101は、確保したメモリ領域の先頭アドレスを動作させたい画像処理部のレジスタへ設定する。ここで、画像処理部においてメモリ領域を使用する処理について簡単に説明する。画像処理部にはスムージング処理や像域判定処理等で行われる各種フィルタ処理等が備えられる。フィルタ処理は、通常ラスターフォーマットで入力される画像データをフィルタのウインドウ幅のライン数だけ、画像データを貯める必要がある。この所定ラインを貯めるためのバッファを本実施形態ではWideIO-SDRAMの領域を用いて実現するように構成する。続いて、S705において、CPU101は、動作させたい画像処理部を起動し、操作部等から指定されたジョブに必要な画像処理等を実施する。画像処理部の起動とは、例えば、画像処理部に備えられるイネーブルレジスタの設定値をイネーブル状態にすることである。

#### 【0031】

一方、S702において、CPU101は、必要なサイズだけWideIO-SDRAM205に割り当てられたメモリ領域からメモリを確保することができないと判定した場合、S706へ進む。S706において、CPU101は、使用候補のメモリ層として第2メモリ層のWideIO-SDRAM204を追加で選択する。続いて、S707において、CPU101は、第2メモリ層のアドレス領域から現在動作させたい画像処理部が必要とするメモリサイズより第1メモリ層で確保可能なサイズを減算した残りのメモリサイズだけメモリ領域を確保できるか否かを判定する。即ち、WideIO-SDRAM204に割り当てられた $0 \times 2000_0000 \sim 0 \times 4000_0000$ の領域から画像

10

20

30

40

50

処理部が必要とする残りのメモリサイズを確保できるか否かを判定する。

【0032】

CPU101は、必要なサイズだけWideIO-SDRAM204に割り当てられたメモリ領域からメモリを確保することができると判定した場合、S708に進み、第1及び第2メモリ層を使用するメモリ層として決定する。なお、第1メモリ層の全ての領域が確保できない場合には、第2メモリ層のみを使用するメモリ層として決定する。S708において、CPU101は、WideIO-SDRAM204、205に対応するメモリコントローラ動作モード設定レジスタ401～408に対して設定を行い、SDRAM301～308がメモリアクセス可能な状態にする。以降、S704及びS705に進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。

10

【0033】

一方、S707において、CPU101は、必要なサイズだけWideIO-SDRAM204に割り当てられたメモリ領域からメモリを確保することができないと判定した場合、S709へ進む。S709において、CPU101は使用候補のメモリ層として第3メモリ層のWideIO-SDRAM203を追加で選択する。S710において、CPU101は、第3メモリ層のアドレス領域から現在動作させたい画像処理部が必要とするメモリサイズより第1及び第2メモリ層で確保可能なサイズを減算した残りのメモリサイズだけメモリ領域を確保できるか判定する。即ち、WideIO-SDRAM203に割り当てられた0x4000\_0000～0x6000\_0000の領域から画像処理部が必要とする残りのメモリサイズを確保できるかを判定する。

20

【0034】

CPU101は必要なサイズだけWideIO-SDRAM203に割り当てられたメモリ領域からメモリを確保することができると判定した場合、S711に進み、第1、第2、第3メモリ層を使用するメモリ層として決定する。なお、第1メモリ層の全ての領域や第2メモリ層の全ての領域が確保できない場合には、第1及び第3メモリ層、第2及び第3メモリ層、又は、第3メモリ層のみを使用するメモリ層として決定する。S711では、CPU101は、WideIO-SDRAM203～205に対応するメモリコントローラ動作モード設定レジスタ401～412に対して設定を行い、SDRAM301～312がメモリアクセス可能な状態にする。以降、S704及びS705と進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。

30

【0035】

一方、S710において、CPU101は、必要なサイズだけWideIO-SDRAM203に割り当てられたメモリ領域からメモリを確保することができないと判定した場合、S712にフローが進む。S712において、CPU101は第1、第2、第3、及び第4メモリ層を使用するメモリ層として決定する。なお、第1メモリ層の全ての領域、第2メモリ層の全ての領域や第3メモリ層の全ての領域が確保できない場合には、S711で説明したように、領域が確保可能なメモリ層の組み合わせに決定する。S712では、CPU101は、WideIO-SDRAM202～205に対応するメモリコントローラ動作モード設定レジスタ401～416に対して設定を行い、SDRAM301～316がメモリアクセス可能な状態にする。CPU101はWideIO-SDRAM202に割り当てられた0x6000\_0000～0x8000\_0000の領域から画像処理部が必要とする残りのメモリサイズを確保する。以降、S704及びS705と進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。

40

【0036】

以上説明したように、本実施形態によれば、ジョブを実行するために動作させる必要がある画像処理部が必要とするメモリ領域を、SOCダイ201より最も離れたメモリ層から優先的に確保するようにした。このため、本実施形態では、複数のWideIO-SDRAMの中からより低温なWideIO-SDRAMを使用してデータ処理を行うことができるため、消費電力の低減やメモリアクセスの性能低下の抑制が可能となる。つまり、SOCの熱の影響が最も小さく、ヒートシンク等の冷却効果が最も大きいメモリ層を使用

50

することができ、局所的に高温状態になるD R A Mが減少し、D R A Mのリフレッシュ頻度の低減やリーク電流の低減を行うことができる。したがって、消費電力の低減と、W i d e I OのD R A Mのアクセス性能の低下を極力抑制することが可能となる。

#### 【0037】

＜第2の実施形態＞

次に、図8A及び図8Bを参照して、本発明の第2の実施形態について説明する。上記第1の実施形態では、データ処理装置に設定されたジョブを実行する際に、S O Cダイ201から物理的に最も離れたメモリ層（W i d e I O - S D R A M 2 0 5）より優先的に使用する形態について説明した。しかしながら、設定されたジョブの内容によって、メモリの使用頻度が変わるために、メモリアクセスによって生じる消費電力や、処理速度（パフォーマンス）は変わってくる。要求される消費電力や処理速度は、ジョブの内容によって異なるため、設定されたジョブ処理に応じて、使用するメモリ層を使い分ける制御が必要なケースが想定される。

#### 【0038】

例えば、W i d e I O - S D R A M 2 0 2 ~ 2 0 5の記憶容量には限りがあるため、同時に複数のジョブを処理しなければならない場合には、使用するメモリ領域を、全てS O Cダイ201より最も離れたメモリ層に割り当たらない可能性がある。このようなケースを想定し、本実施形態では、ジョブの内容によって最も離れたメモリ層（W i d e I O - S D R A M 2 0 5）より優先して使用するか、又は最も近いメモリ層（W i d e I O - S D R A M 2 0 2）より優先して使用するかを制御する。

#### 【0039】

図8A及び図8Bを参照して、本実施形態におけるメモリ領域を決定する処理フローについて説明する。説明を簡略化するために、上記第1の実施形態と同じ処理を行うステップに関しては同一のステップ番号を付し説明を省略する。なお、以下で説明する処理は、C P U 1 0 1がR O M 1 0 6、H D D 1 0 5等に予め格納された制御プログラムをW i d e I O - S D R A M 1 1 3に読み出して実行することにより実現される。

#### 【0040】

S 8 0 1において、C P U 1 0 1は、設定ジョブの内容によって、遠距離メモリ層優先フラグを参照する。遠距離メモリ層優先フラグは、遠距離メモリ層優先フラグテーブルに格納されている。遠距離メモリ層優先フラグテーブルは、ジョブ毎にS O Cダイ201より最も離れたメモリ層より優先して使用するか否かを判定する1ビットの遠距離メモリ層優先フラグの情報を保持するテーブルである。遠距離メモリ層優先フラグには、最も離れたメモリ層（W i d e I O - S D R A M 2 0 5）より優先して使用する場合には1、最も近いメモリ層（W i d e I O - S D R A M 2 0 2）より優先して使用する場合には0が設定される。本実施形態の場合は、ジョブの実行中においてメモリ使用頻度の高いジョブの場合には遠距離メモリ層優先フラグは1、ジョブの実行中においてメモリ使用頻度の低いジョブの場合には遠距離メモリ層優先フラグは0が予め設定されている。メモリ使用頻度の高いジョブは、実行中において割り当たられたメモリ領域に頻繁にアクセスするため、本実施形態では、最も離れたメモリ層から優先的にメモリ領域を割り当てる。

#### 【0041】

次に、S 8 0 2において、C P U 1 0 1は、遠距離メモリ層優先フラグの値が1であるか否かによって、次に行う処理を切り換える。C P U 1 0 1は、遠距離メモリ層優先フラグが1の場合にはS 7 0 1の処理へ進み、0の場合にはS 8 0 3の処理へ進むように制御する。S 7 0 1 ~ S 7 1 2の処理内容は、上記第1の実施形態で説明した図7のS 7 0 1 ~ S 7 1 2と同様であるため説明を省略する。

#### 【0042】

一方、遠距離メモリ層優先フラグが0の場合、S 8 0 3（図8B）において、C P U 1 0 1は、使用候補のメモリ層として第4メモリ層のW i d e I O - S D R A M 2 0 2を選択する。つまり、使用候補のメモリ層として、S O Cダイ201より最も近いメモリ層（最下位メモリ層）のW i d e I O - S D R A M 2 0 2を選択する。続いて、S 8 0 4にお

10

20

30

40

50

いて、CPU101は、第4メモリ層のSDRAMのアドレス領域から現在動作させたい画像処理部が必要とするメモリサイズだけメモリ領域を確保できるか否かを判定する。即ち、WideIO-SDRAM202に割り当てられた $0 \times 6000_0000 \sim 0 \times 8000_0000$ の領域から画像処理部が必要とするメモリサイズを確保できるか否かを判定する。

#### 【0043】

CPU101は必要なサイズだけWideIO-SDRAM202に割り当てられたメモリ領域からメモリを確保することができると判定した場合、S805において、CPU101は、第4メモリ層を使用するメモリ層として決定する。CPU101は、使用候補のメモリ層のアドレス領域からメモリサイズを確保できると判定すると、使用候補のメモリ層を使用するメモリ層として決定する。S805では、CPU101は、さらに、WideIO-SDRAM202に対応するメモリコントローラ動作モード設定レジスタ413～416に対して設定を行い、SDRAM313～316がメモリアクセス可能な状態にする。以降、S704及びS705とフローが進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。

10

#### 【0044】

S804で必要なサイズだけWideIO-SDRAM202に割り当てられたメモリ領域からメモリを確保することができないと判定した場合、S806へ進む。S806において、CPU101は、使用候補のメモリ層として第3メモリ層のWideIO-SDRAMを追加で選択する。つまり、本実施形態では、第3メモリ層のWideIO-SDRAM203を追加で選択する。

20

#### 【0045】

S807において、CPU101は、第3メモリ層のアドレス領域から現在動作させたい画像処理部が必要とするメモリサイズより第4メモリ層で確保可能なサイズを減算した残りのメモリサイズだけメモリ領域を確保できるか判定する。即ち、WideIO-SDRAM203に割り当てられた $0 \times 4000_0000 \sim 0 \times 6000_0000$ の領域から画像処理部が必要とする残りのメモリサイズを確保できるかを判定する。CPU101は、必要なサイズだけWideIO-SDRAM203に割り当てられたメモリ領域からメモリを確保することができると判定した場合、S808において、第3及び第4メモリ層を使用するメモリ層として決定する。S808において、CPU101は、WideIO-SDRAM202、203に対応するメモリコントローラ動作モード設定レジスタ409～416に対して設定を行い、SDRAM309～316がメモリアクセス可能な状態にする。以降、S704及びS705とフローが進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。

30

#### 【0046】

S807において、CPU101は、必要なサイズだけWideIO-SDRAM203に割り当てられたメモリ領域からメモリを確保することができないと判定した場合、S809へ進む。S809において、CPU101は使用候補のメモリ層として第2メモリ層のWideIO-SDRAMを追加で選択する。つまり本実施形態では、第2メモリ層のWideIO-SDRAM204を追加で選択する。

40

#### 【0047】

次に、S810において、CPU101は第2メモリ層のアドレス領域から現在動作させたい画像処理部が必要とするメモリサイズより第3及び第4メモリ層で確保可能なサイズを減算した残りのメモリサイズだけメモリ領域を確保できるか判定する。即ち、WideIO-SDRAM204に割り当てられた $0 \times 2000_0000 \sim 0 \times 4000_0000$ の領域から画像処理部が必要とする残りのメモリサイズを確保できるかを判定する。

#### 【0048】

CPU101は必要なサイズだけWideIO-SDRAM204に割り当てられたメモリ領域からメモリを確保することができると判定した場合、S811において、CPU50

101は第2、第3、及び第4メモリ層を使用するメモリ層として決定する。S811では、CPU101は、WideIO-SDRAM202～204に対応するメモリコントローラ動作モード設定レジスタ405～416に対して設定を行い、SDRAM305～316がメモリアクセス可能な状態にする。以降、S704及びS705とフローが進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。

#### 【0049】

S810において、CPU101は必要なサイズだけWideIO-SDRAM204に割り当てられたメモリ領域からメモリを確保することができないと判定した場合、S812にフローが進む。S812において、CPU101は第1、第2、第3及び第4メモリ層を使用するメモリ層として決定する。S812では、CPU101は、WideIO-SDRAM202～205に対応するメモリコントローラ動作モード設定レジスタ401～416に対して設定を行い、SDRAM301～316がメモリアクセス可能な状態にする。

10

#### 【0050】

CPU101はWideIO-SDRAM205に割り当てられた0×0000\_0000～0×2000\_0000の領域から画像処理部が必要とするメモリサイズより第2、第3、第4メモリ層で確保可能なサイズを減算した残りのメモリサイズを確保する。以降、S704及びS705とフローが進むが、S704及びS705の処理は上述した通りであるため、説明は省略する。なお、S803、S806、S809においては、対象のメモリ層に確保するメモリ領域が無ければ、当該対象のメモリを使用候補メモリ層として選択しなくともよい。

20

#### 【0051】

以上説明したように、本実施形態によれば、ジョブを実行するために動作させる必要がある画像処理部が必要とするメモリ領域を、ジョブの内容を参照して、遠いメモリ層又は近いメモリ層のどちらから優先的に確保するかを切り替えられることができる。この為、メモリアクセス速度のパフォーマンスが要求されないジョブや、アクセス頻度が少なく熱の影響による消費電力がほとんど問題とならないジョブは、近いメモリ層に優先的に割り当たられるよう制御される。

#### 【0052】

よって、WideIOSDRAMを使用する様々なジョブが混在する場合でも、アクセス頻度が高く、熱の影響を受け易いジョブを、より優先的にSOCダイ201より遠いメモリ層へ割り当てることができる。このため、本実施形態では、複数のWideIOSDRAMの中からより低温なWideIOSDRAMを使用してデータ処理を行うことができるため、消費電力の低減やメモリアクセスの性能低下の抑制が可能となる。

30

#### 【0053】

<その他の実施形態>

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（又はCPUやMPU等）がプログラムを読み出して実行する処理である。

40

【 四 1 】

【図2】

( 3 )

〔 4 〕

|                          |      |

|--------------------------|------|

| メモリコントローラ動作モード<br>設定レジスタ | ～401 |

| メモリコントローラ動作モード<br>設定レジスタ | ～402 |

| メモリコントローラ動作モード<br>設定レジスタ | ～403 |

| メモリコントローラ動作モード<br>設定レジスタ | ～404 |

| メモリコントローラ動作モード<br>設定レジスタ | ～405 |

| メモリコントローラ動作モード<br>設定レジスタ | ～406 |

| メモリコントローラ動作モード<br>設定レジスタ | ～407 |

| メモリコントローラ動作モード<br>設定レジスタ | ～408 |

| メモリコントローラ動作モード<br>設定レジスタ | ～409 |

| メモリコントローラ動作モード<br>設定レジスタ | ～410 |

| メモリコントローラ動作モード<br>設定レジスタ | ～411 |

| メモリコントローラ動作モード<br>設定レジスタ | ～412 |

| メモリコントローラ動作モード<br>設定レジスタ | ～413 |

| メモリコントローラ動作モード<br>設定レジスタ | ～414 |

| メモリコントローラ動作モード<br>設定レジスタ | ～415 |

| メモリコントローラ動作モード<br>設定レジスタ | ～416 |

【図5】

【図6】

【図7】

【図8 A】

【図 8 B】

---

フロントページの続き

(72)発明者 美馬 賀

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 酒井 恭信

(56)参考文献 特表2009-537072 (JP, A)

米国特許出願公開第2007/0290333 (US, A1)

国際公開第2009/017070 (WO, A1)

米国特許出願公開第2012/0256679 (US, A1)

特開2012-221540 (JP, A)

特開2003-150394 (JP, A)

特開2014-044527 (JP, A)

特開2014-106917 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12/06