(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4050109号

(P4050109)

(45) 発行日 平成20年2月20日(2008.2.20)

(24) 登録日 平成19年12月7日(2007.12.7)

(51) Int.Cl.

F 1

H04L 1/00 (2006.01)

H04L 1/00

1/00

D

H04L 1/20 (2006.01)

H04L 1/20

C

H04L 1/20

請求項の数 4 (全 19 頁)

(21) 出願番号

特願2002-242894 (P2002-242894)

(22) 出願日

平成14年8月23日 (2002.8.23)

(65) 公開番号

特開2003-87226 (P2003-87226A)

(43) 公開日

平成15年3月20日 (2003.3.20)

審査請求日

平成17年8月18日 (2005.8.18)

(31) 優先権主張番号

944740

(32) 優先日

平成13年8月31日 (2001.8.31)

(33) 優先権主張国

米国(US)

(73) 特許権者 399117121

アジレント・テクノロジーズ・インク

A G I L E N T T E C H N O L O G I E

S, I N C.アメリカ合衆国カリフォルニア州サンタク

ララ スティーブンス・クリーク・ブルー

バード 5301

(74) 代理人 100105913

弁理士 加藤 公久

(72) 発明者 リー・エー・バーフォード

アメリカ合衆国カリフォルニア州サンノゼ

、ミトン・ドライブ2931

審査官 小曳 满昭

最終頁に続く

(54) 【発明の名称】 ビット誤り率のテスト方法、及び、ビット誤り率のテストシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

ビット誤り率テストを実施する方法であって、

(d) 測定された誤りのあるビットの累積数に基づいてビット誤り率の事後累積分布関数を計算するステップと、

(e) 前記事後累積分布関数の計算値が、前記ビット誤り率がビット誤り率テスト限界未満である所望の確率以上であるか否かを判定するステップと、

(f) 前記事後累積分布関数の計算値が前記所望の確率以上であるという判定に応答して、テストが合格したことを明示し、テストを停止するステップと、

(g) 1から前記事後累積分布関数の計算値を引いた値が前記所望の確率以上か否かを判定するステップと、

(h) 1から前記事後累積分布関数の計算値を引いた値が前記所望の確率以上であるという判定に応答して、テストが不合格になったことを明示し、テストを停止するステップと、

(i) テスト時間が最長テスト時間を超えたという判定に応答して、テストが不合格になったことを明示し、テストを停止するステップと、

(j) 前記事後累積分布関数の計算値が前記所望の確率未満で、1から前記事後累積分布関数の計算値を引いた値が前記所望の確率未満であるという判定に応答して、上記のステップ(d)からステップ(i)を反復するステップと、が含まれている方法。

## 【請求項 2】

10

20

さらに、

- (a) 複数のビットを測定するステップと、

- (b) 測定された誤りのあるビットの累積数を求めるステップと、

- (c) 前記ステップ (b) に応答して、前記ステップ (a) 及び前記ステップ (b) を反復するステップと、

- を含み、

前記複数の測定ビット数が、前記ステップ (a) 及び前記ステップ (b) の実施時間量が前記ステップ (d) から前記ステップ (i) の最悪ケースの実施時間にほぼ等しくなるように設定され、

前記複数のビットを測定するステップが、テストビットレートを設定するステップと、

前記テストビットレートに前記最悪ケースの実施時間を乗じることにより前記複数の測定ビット数を求めるステップとを含む、

ことを特徴とする請求項 1 に記載の方法。

【請求項 3】

さらに、

- (a) 複数のビットを測定するステップと、

- (b) 測定された誤りのあるビットの累積数を求めるステップと、

- (c) 前記ステップ (b) に応答して、前記ステップ (a) 及び前記ステップ (b) を反復するステップと、

- (k) 前記テスト限界を設定するステップと、

- (l) 前記所望の確率を設定するステップと、

- (m) 前記ビット誤り率の事前平均を設定するステップと、

- (n) 前記ビット誤り率の事前標準偏差を設定するステップと、

- (o) 前記最長テスト時間を設定するステップと、

- (p) 次式で表される値 a 及び値 b を計算するステップと

【数 1】

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

20

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

30

を含み、

上記  $\mu$  が前記ビット誤り率の事前平均であり、

上記  $\sigma$  が前記ビット誤り率の事前標準偏差であり、

前記ステップ (k) から前記ステップ (o) が前記ステップ (a) の実施前に実施されることを特徴とする請求項 1 に記載の方法。

【請求項 4】

40

ビット誤り率テストを実施するシステムであって、

被測定物にビット・シーケンスを入力するビット・シーケンス発生器と、

前記ビット・シーケンス発生器に接続された遅延発生器と、

前記被測定物及び前記遅延発生器に接続され、前記遅延発生器の出力と前記被測定物の出力を比較するコンパレータと、

前記コンパレータに接続されて、誤りのあるビットの累積数であるコンパレータの出力をカウントするカウンタと、

前記カウンタに接続された制御コンピュータと、

を備え、

前記コンピュータが、

50

- (d) 誤りのあるビットの累積数に基づいてビット誤り率の事後累積分布関数を計算し、

- (e) 前記事後累積分布関数の計算値が、ビット誤り率がビット誤り率テスト限界未満である、所望の確率以上であるか否かを判定し、

- (f) 前記事後累積分布関数の計算値が前記所望の確率以上であるという判定に応答し、テストが合格したことを明示し、そのテストを停止し、

- (g) 1から前記事後累積分布関数の計算値を引いた値が前記所望の確率以上か否かを判定し、

- (h) 1から前記事後累積分布関数の計算値を引いた値が前記所望の確率以上であるという判定に応答し、テストが不合格になったことを明示して、そのテストを停止し、

- (i) テスト時間が最長テスト時間を超えたという判定に応答し、テストが不合格になったことを明示して、そのテストを停止し、

- (j) 前記事後累積分布関数の計算値が前記所望の確率未満で、1から前記事後累積分布関数の計算値を引いた値が前記所望の確率以上であるという判定に応答して、上記のステップ(d)からステップ(i)を反復する、

- ことを特徴とするシステム。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、一般に、ビット誤り率テストの分野に関するものであり、とりわけ、それに制限するわけではないが、一例として、統計分析を利用したビット誤り率テストに関するものである。

## 【0002】

## 【従来の技術】

被測定物(DUT)のビット誤り率の測定には、制限するわけではないが、製造に関連した装置のテストを含む、多くの用途がある。被測定物は、例えば、ディジタル通信装置、システム、または、チャネルとすることが可能である。被測定物のビット誤りの測定には、一般に、被測定物からビット誤り数を求めるため、被測定物にビット・シーケンスを入力して、被測定物の出力と既知の正しい結果を比較することが必要とされる。典型的なビット誤りテスト・システムは、被測定物によるある数のビット(N)の正確な伝送をテストして、Nビットの伝送から生じる誤りのある受信ビット数(R)をカウントする。

## 【0003】

いくつかのビット誤り率テスト手法が開発されている。第1のこうした手法には、固定数のビットのテストが必要になる。この手法の場合、テストのためにNビットが選択される。Rの誤りのあるビットがカウントされる。次に、ビット誤り率推定値がR/Nとして計算される。R/Nがビット誤り率テスト限界(L)以下の場合、テストに合格したものとみなされる。R/NがLを超えると、テストに不合格とみなされる。

## 【0004】

この手法の欠点は、Nに関して選択される値とビット誤り率推定値R/Nの正確度の間には直接的な関係がないということである。不可避的に、経験に基づく方法を用いて、Nを選択することになるが、このため、テスト時間が不必要に長くなったり、あるいは、ビット誤り率推定値が不正確になる。

## 【0005】

ビット誤り率テストの第2の手法には、固定数のエラーがカウントされるまで、被測定物をテストすることが必要とされる。この手法では、Rの誤りのあるビットをカウントするか、または、最長テスト時間(T)に達するまで、ビットがカウントされる。この手法は、第1の手法と同じ不都合がある。やはり、R及びTとテストの正確度の間に直接的な関係がない。不可避的に、経験に基づく方法を用いて、R及びTを選択することになるが、このため、テスト時間が不必要に長くなったり、あるいは、テスト結果が不正確になる。

## 【0006】

10

20

30

40

50

ビット誤り率テストの第3の手法には、密度推定と補外が含まれる。この手法の場合、被測定物へのビット伝送と被測定物からのビットの読み取りとの間の時間遅延が、0から0.5ビット時間の間で変動させられる。異なるビット時間オフセットにおける誤りのあるビット数がカウントされ、それを利用して、オフセットの関数としてビット誤り率の確率密度推定値を得ることが可能である。

#### 【0007】

密度推定は、0.5ビット時間に近い領域では正確である。密度推定は、補外によってゼロ・オフセットに戻され、その結果、ビット誤り率の推定値が得られる。第3の手法の欠点は、測定データが得られるにはほど遠い推定関数の補外に依存している点である。従って、正確性が疑わしい。さらに、実際の用途にとって十分な迅速さで完全な密度推定を計算することは不可能である。従って、例えば、ガウス近似によるただ1つの密度モードの近似といった、さまざまな近似法が利用される。密度推定及び補外法は、テスト基準で要求されるので、よく用いられる。

10

#### 【0008】

上述の手法には、それぞれ、ビット誤り率が十分に低いか否かに関して十分に正確な判定を得るのに、ビット誤りをどれだけの時間にわたって測定すべきかが分からぬという欠点がある。従って、上述の手法のどれを利用してても、テスト時間が不必要に長くなったり、あるいは、テスト結果が不正確になる場合が多い。さらに、テスト時間が長すぎるか否か、あるいは、テスト結果が不正確であるか否かを知るのは不可能である。上述の手法のもう1つの欠点は、測定時間を最短にし、スループットを最大にするのに、ビット誤り率に関する事前の情報を考慮することができないという点である。上述の手法のもう1つの欠点は、ビット誤り率テストの正確さを確立する直接的な手段が得られないという点である。

20

#### 【0009】

##### 【発明が解決しようとする課題】

従って、本発明の目的は、先行技術に関連した以上の及びその他の欠点を解消する最短時間のビット誤り率テスト方法及びシステムを提供することにある。

#### 【0010】

##### 【課題を解決するための手段】

先行技術の以上の及びその他の欠点は、本発明によって克服される。本発明の第1の実施態様では、ビット誤り率テストの実施方法が得られる。この実施態様には、測定された誤りのあるビットの累積数に基づいて、ビット誤り率の事後累積分布関数( $p_{cdf}$ )を計算するステップと、 $p_{cdf}$ が、ビット誤り率がビット誤り率テスト限界( $L$ )未満である、所望の確率( $C$ )以上であるか否かを判定するステップが含まれている。 $p_{cdf}$ が $C$ 以上であるとする判定に応答して、テストは合格になり、停止される。 $1 - p_{cdf}$ が $C$ 以上であると判定されると、テストは不合格になり、停止される。また、テストに要する時間量が最長テスト時間( $T$ )を超えるとする判定に応答して、テストは不合格になり、停止される。上述のステップは、 $p_{cdf}$ が $C$ 未満であり、 $1 - p_{cdf}$ が $C$ 未満であるとする判定に応答して、反復される。

30

#### 【0011】

本発明のもう1つの実施態様では、ビット誤り率テストを実施する製品に、少なくとも1つのコンピュータ可読媒体と、少なくとも1つのコンピュータ可読媒体に納められたプロセッサ命令が含まれている。プロセッサ命令は、少なくとも1つのプロセッサによって少なくとも1つのコンピュータ可読媒体から読み取ることができるように構成されている。この命令によって、少なくとも1つのプロセッサが、測定された誤りのあるビットの累積数に基づいて、ビット誤り率の事後累積分布関数( $p_{cdf}$ )を計算し、 $p_{cdf}$ が、ビット誤り率がビット誤り率テスト限界( $L$ )未満である、所望の確率( $C$ )以上であるか否かを判定することになる。

40

#### 【0012】

プロセッサは、 $p_{cdf}$ が $C$ 以上であるとする判定に応答して、テストに合格したことを

50

明示し、テストを停止する働きもさせられる。プロセッサは、さらに、 $1 \text{ p c d f} \geq C$  以上であるか否かの判定を行い、 $1 - \text{p c d f} \geq C$  以上であるとする判定に応答して、テストが不合格であったことを明示し、テストを停止する働きもする。プロセッサは、また、テスト時間が最長テスト時間 ( $T$ ) を超えたとする判定に応答して、テストが不合格であったことを明示し、テストを停止する働きもする。プロセッサは、 $\text{p c d f} < C$  未満であり、 $1 - \text{p c d f} < C$  未満であるとする判定に応答して、上述のステップを反復する働きもする。

#### 【 0 0 1 3 】

本発明のさらにもう 1 つの実施態様では、ビット誤り率テストを実施するようになっているシステムには、被測定物 (DUT) にビット・シーケンスを入力するようになっているビット・シーケンス発生器と、ビット・シーケンス発生器に相互運用できるように接続された遅延発生器が含まれている。DUT 及び遅延発生器には、コンパレータが相互運用できるように接続されている。コンパレータは、遅延発生器の出力と DUT の出力を比較するようになっている。コンパレータには、カウンタが相互運用できるように接続されており、コンパレータの出力をカウントするようになっている。出力は、誤りのあるビットの累積数である。

#### 【 0 0 1 4 】

カウンタには、制御コンピュータが相互運用できるように接続されており、誤りのあるビットの累積数に基づいて、ビット誤り率の事後累積分布関数 ( $\text{p c d f}$ ) を計算するようになっている。制御コンピュータは、 $\text{p c d f} \geq C$  以上であるか否かの判定も行う。制御コンピュータは、 $\text{p c d f} < C$  以上であるとする判定に応答して、テストが合格であるか否かを明示し、テストを停止する。制御コンピュータは、 $1 - \text{p c d f} \geq C$  以上であるか否かを判定し、 $1 - \text{p c d f} < C$  以上であるとする判定に応答して、テストが不合格であったことを明示し、テストを停止する。制御コンピュータは、テスト時間が最長テスト時間 ( $T$ ) を超えたとする判定に応答し、テストが不合格であったことを明示して、テストを停止し、また、 $\text{p c d f} < C$  未満であり、 $1 - \text{p c d f} < C$  未満であるとする判定に応答して、上述のステップを反復する。

#### 【 0 0 1 5 】

本発明の上述の及びその他の特徴については、添付の図面に示す説明に役立つ例に関連して、詳述される。当業者には明らかなように、解説の実施態様は、例証によって、理解が得られるようにするために示されたものであり、この特許出願においては、さまざまな同等実施態様も企図されている。

#### 【 0 0 1 6 】

##### 【発明の実施の形態】

下記の説明では、制限のためではなく、解説のため、本発明の実施態様を完全に理解するために、特定の詳細が明らかにされる。しかし、当業者には明らかなように、本発明は、これら特定の詳細から逸脱した他の実施態様において実施することが可能である。他の例については、不必要的詳細によって本発明の実施態様に関する説明が不明瞭にならないように、周知の方法、装置、論理コード（例えば、ハードウェア、ソフトウェア、ファームウェア）等の詳細な説明は省略される。本発明の望ましい実施態様及びその利点は、図面中の図 1 から 3 を参照することによって最も明らかになる。

#### 【 0 0 1 7 】

統計、データ分析、及び、人工知能に対するベイズ (Bayes) の方法の適用は、革命であった。ベイズの方法は、次第に、不確実な情報に基づいて、正しい演繹を可能にする強力な技法として認識されるようになってきた。ベイズの方法は、正統的な統計的推論手法に比べて、適用が容易である場合が多い。さらに、ベイズの方法によれば、演繹を行うのに、事前知識を正しく、十分に適用することが可能になる。

#### 【 0 0 1 8 】

多くの測定及びテスト用途では、本質的に不確実な情報（例えば、測定結果及びテスト結

10

20

30

40

50

果)を受け取り、それに基づいて情報の計算を行う。ベイズの方法では、複数の測定結果、テスト結果、及び、事前知識を統合する一貫した枠組みが得られる。こうして演繹される情報には、それ自体の不確実性に関するさらなる情報を伴っている。

#### 【0019】

伝統的な確率及び統計学では、確率は、反復実験におけるさまざまな事象の発生頻度の測度とみなされる。対照的に、ベイズの統計では、確率は、不確実な知識の利用可能な全ての関連構成要素が与えられたとした場合に、客観的推論者が特定の推定に関して有している知識状態の不確実性の測度とみなされる。換言すると、ベイズの統計では、確率は、与えられた不確実な知識について推論するための論理であるとみなされる。

#### 【0020】

ベイズの統計学的計算は、計算論的に集約形とすることが可能である。しかし、処理能力がコストの関数として連続的指数成長を遂げたことにより、それらは、従来可能であったものに比べると、物理的測定や、信号及び画像処理のさまざまな領域における多種多様なデータ分析問題にとって、はるかに実用的なものになった。ベイズの統計学的方法では論理として確率論を利用するので、装置を順次テストするのに計算論的に効率の良いアプローチが得られることになり、この結果、十分な確信をもって、被測定物のビット誤り率が十分に低いと分かること、すぐにテストを終了することが可能になる。予測テスト時間を最短にするため、利用可能な事前知識を十分に考慮するのが、最も一般的である。

10

#### 【0021】

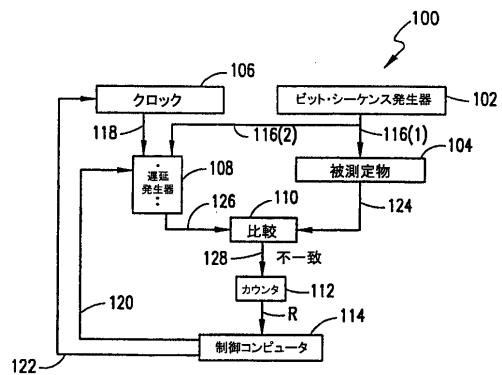

図1は、本発明の実施態様によるビット誤り率テスト・システム100を例示したブロック図である。システム100には、ビット・シーケンス発生器102、被測定物(DUT)104、クロック106、遅延発生器108、コンパレータ110、カウンタ112、及び、制御コンピュータ114が含まれている。

20

#### 【0022】

ビット・シーケンス発生器102は、被測定物104にNビットのストリーム116(1)を入力する。ビット・シーケンス発生器102は、さらに、遅延発生器108に対して、被測定物104に供給されるのと同じNビットのストリーム116(2)を供給する。遅延発生器108は、また、システム100の同期を維持し、遅延発生器108によって導入される遅延の制御コンピュータ114による制御を維持するため、クロック106からの入力118も受信する。制御コンピュータ114は、遅延調整のため、接続120を介して遅延発生器108に相互運用できるように接続され、また、接続122を介してクロック106に相互運用できるように接続されている。

30

#### 【0023】

ビット・シーケンス発生器102によるNビット・ストリーム116(1)の入力に応答して、被測定物104は、コンパレータ110に対してNビット・ストリーム124を出力する。遅延発生器108は、コンパレータ110に対して、ビット・ストリーム発生器102からのNビット・ストリーム116(2)の遅延バージョンであるビット・ストリーム126を出力する。コンパレータ110は、被測定物104からのNビット・ストリーム124と遅延発生器108からのNビット・ストリーム126を比較して、被測定物104からのその対応するビットと一致しない、遅延発生器108からの各遅延ビットに対応する出力128を、カウンタ112に対して生成する。これらの不一致は、被測定物104によるビット誤りの総数(R)を表している。カウンタ112は、ビット誤りの合計Rをカウントし、この合計Rを制御コンピュータ114に対して出力する。

40

#### 【0024】

図1に例示のように、Nビット・ストリームが、被測定物に入力され、被測定物の出力と比較される。ビット誤りが、コンパレータによって求められ、ビット誤り合計Rがカウンタによってカウントされる。カウンタは、制御コンピュータに対して合計Rを出力する。

#### 【0025】

本発明の実施態様によるビット誤り率の測定法は、図1に例示のようなシステムを用いることが可能である。図1に示すものと同様のシステム例としては、アジレント社の812

50

50 Parallel Bit-Error Rate Tester がある。例えば、図1に例示のような一般に用いられるビット誤りテスト・システムによれば、固定数のビットを測定することが可能になるが、ここで、Nは、テストを受けるビット数を表し、Rはカウントされた誤りのあるビット数を表している。ビット誤り率 及びその信頼区間は、本発明の実施態様を利用して計算することが可能である。本発明の実施態様によれば、 をある所定の信頼区間に内に設定するのに必要な時間が最短化される。

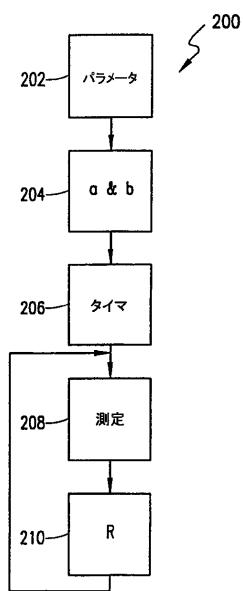

【0026】

図2は、フローチャートである。本発明の実施態様によるビット誤り率テストに関連してビット誤り測定を例示したフローチャートである。フロー200は、ステップ202から始まり、テスト・パラメータが設定される。これらのテスト・パラメータには、例えば、ビット誤り率テスト限界 (L) 、各被測定物のビット誤り率がL未満である所望の確率 (C) 、ビット誤り率の事前平均 ( $\mu$ ) 及び事前標準偏差 ( ) 、被測定物がテストされることになるビット・レート (B) 、及び、最長テスト時間 (T) を含むことが可能である。Bは、通常、ビット/秒で測定される。  $\mu$  及び  $\sigma$  /または  $\sigma$  を推定することができない場合、 $\mu = 0.5$  及び  $\sigma = 0.1$  を利用するのが望ましい。

【0027】

実行は、ステップ202からステップ204に進む。ステップ204では、係数a及びbが計算されるが、ここで、 $a = s\mu$  、  $b = s(1 - \mu)$  であり：

【数2】

$$s = \frac{\mu(1 - \mu) - \sigma^2}{\sigma^2} \quad (1)$$

実行は、ステップ204からステップ206に進む。ステップ206において、最長テスト時間Tの経過時点を確認するために用いられるタイマが起動される。

【0028】

実行は、ステップ206からステップ208に進む。ステップ208では、例えば、システム100のようなシステムを利用して、複数nビットが測定される。ステップ208の測定によって、ビット誤り数が得られる。実行は、ステップ208からステップ210に進む。ステップ210では、ステップ208で分かったビット誤り数が、例えば、システム100のカウンタ112によってカウントされ、R値が得られる。実行は、ステップ210からステップ208に移行し、第2のnビットが測定される。実行は、ステップ208からステップ210に進む。ステップ210では、ステップ208の2回目の実施で得られたビット誤り数を前回のR値に加えることによって、R値が更新され、Rはテスト中にカウントされた累積ビット誤り数を表すことになる。フロー200から得られる測定ビット・レートは、R/Nで表すことが可能であるが、ここで、 $N = n \times$  あり、 $\times$  は、テスト中に実施されたステップ208の回数である。

【0029】

図2に例示のように、パラメータの入力、及び、係数a及びbの計算が済むと、タイマが起動される。タイマの起動後、nビットが測定され、Rのビット誤りが得られる。ビット誤り数Rがカウントされ、その後、第2のnビットが測定され、第2のnビットからのビット誤り数を前回のR値に加えることによって、Rが更新される。ビット誤りの測定及び累算サイクルは、テスト全般にわたって続行される。

【0030】

ビット誤り率は、確率であるため、0から1の間でなければならない。被測定物のビット誤り率の事前  $\mu$  及び事前  $\sigma$  が、例えば、多くの同様の装置が測定された製造状況におけるように既知の場合、本発明に従って事前  $\mu$  及び事前  $\sigma$  を利用することにより、ビット誤り率テストの実施に必要な時間量を短縮することが可能である。事前  $\mu$  及び  $\sigma$  は、例えば、測定値とすることもできるし、あるいは、被測定物または同様の装置に習熟したエンジニア

10

20

30

40

50

アまたは他の専門家から得られる推定値とすることも可能である。

【0031】

$\mu$ または $\mu$ にわずかな誤りがあったとしても、測定時間への影響はほんのわずかであるため、事前 $\mu$ 及び $\mu$ は、本発明の実施態様に関連して利用することが可能であり、テスト結果に悪影響を及ぼす恐れがほとんどない。さらに、 $\mu$ または $\mu$ がかなり不正確な場合でも、最終的には、正しいピット誤り率測定値が得されることになる。事前知識を適用すると、ピット誤り率の信頼区間幅が狭められる場合が多い。反復実験の測定時間は、一般に、所望の正確度の向上に対して2次的伸びを示すので、事前知識を適用すると、ある特定の所望の正確度レベルを得るための測定時間が短縮される場合が多い。

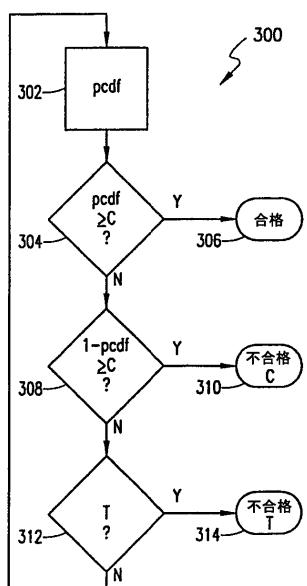

【0032】

図3は、本発明の実施態様による、ピット誤り率テストに関連したピット誤り率統計分析を例示したフローチャートである。フロー300は、フロー200から得られる累積測定ピット誤り数( $R$ )に基づいて、ピット誤り率の事後累積分布関数( $pcdf$ )を計算するために利用される。望ましい実施態様の場合、フロー300は、フロー200のステップ208及び210と並行して行われる。ステップ208で測定される複数のピット( $n$ )は、1つのブロックに相当するのが望ましいが、ここで、 $n$ は、フロー300の最悪のケースの実施時間にピット・レート( $B$ )を掛けた値に等しく、これによって、ステップ208及び210とフロー300のパイプラインが得されることになる。この望ましい実施態様によれば、フロー300が実施される毎に、ステップ208において、新たな $n$ ピット・ブロックが測定され、 $R$ が更新された。望ましい実施値用の場合、フロー300は、制御コンピュータ114によって実施される。

10

【0033】

ステップ208及び210が、テストで始めて実施された後、フロー300がステップ302から開始され、 $pcdf$ の計算が行われる。望ましい実施態様の場合、 $pcdf$ は、下記に等しい：

【0034】

【数3】

$$pcdf = \int_0^L \Pr(\rho|N, R, I, J) = \int_0^L \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / \text{Beta}(R+a, N-R+b) \quad (2)$$

30

【0035】

( $a$ 、 $b$ )は、当該技術において周知のガウスのベータ関数である。 $pcdf$ は、ピット誤り率が $L$ 未満である確率の計算を表している。 $pcdf > C$ の場合、ピット誤り率が $L$ 未満である確率は、少なくともテスト限界 $C$ と同じである。同様に、 $1 - pcdf > C$ の場合、ピット誤り率が $L$ を超える確率は、所望の確率であると判定された。

【0036】

表1から明らかなように、 $N$ はテストを受けたピット数であり、 $R$ はカウントされた誤りのあるピット数である。 $\mu$ は、ピット誤り率であり、 $I$ は、ピットの誤りが、確率 $\mu$ で生じる独立同一分布ランダム事象であるという仮定を表している。 $K$ は、 $\mu$ の事前平均( $\mu$ )及び事前標準偏差( $\sigma$ )が、既知の $\mu$ の標準偏差( $a$ )であるという仮定である。 $K$ は $0 < \sigma < 1$ という仮定である。 $\Phi(x, y)$ は、ガウスのベータ関数である。

40

【0037】

【表1】

| シンボル       | 意味                              |

|------------|---------------------------------|

| N          | テストビット数                         |

| R          | 誤りビット数                          |

| $\rho$     | ビット誤り率                          |

| I          | 独立同一分布ランダム事象である<br>という仮定        |

| J          | 既知 $\rho$ の事前平均および事前偏差<br>という仮定 |

| K          | $\rho \in (0, 1)$               |

| Beta(x, y) | ガウスベータ関数                        |

10

## 【0038】

p c d f の典型的な 2 つの計算方法は、方程式 (2) の数値積分及びオフ・ザ・シェルフ・ライブラリ関数を利用した計算である。数学的ライブラリの中には、不完全なベータ関数を実施するものもあり、不完全な  $(z; c, d)$  は下記のように定義される：

## 【0039】

20

## 【数4】

$$\text{不完全なBeta}(z; c, d) = \frac{\int_0^z u^{c-1} (1-u)^{d-1} du}{Beta(c, d)} \quad (3)$$

## 【0040】

方程式 (3) のライブラリの実施が利用可能であれば、p c d f (すなわち、方程式 2) は、次のように計算することが可能である

30

## 【数5】

$$pcdf = \text{不完全なBeta}(L; R + a, N - R + b) \quad (4)$$

不完全なベータ関数ルーチンの例が、C ライブラリ c e p h e s からのルーチン i n c b e t であり、これらについては、www.netlib.org. で知ることが可能である。実験データが示すように、不完全なベータ関数を利用した p c d f の計算は、直交符号を利用した p c d f の計算よりも大幅に速くなる。

## 【0041】

40

理論上、ステップ 302 における p c d f の計算を含むフロー 300 は、各個別ビットの測定後に実施することが可能である。しかし、実際には、p c d f の計算にかかる時間は、単一ビットの計算に要する時間よりもはるかに長い。p c d f の計算に必要な時間量は、ビット測定数によって左右されないので、フロー 300 の実施に必要とされる時間中に、できるだけ多くのビットをテストするのが望ましい。これによって、上述のように、測定及び累算ステップ 208 及び 210 とフロー 300 のパイプライン化が可能になる。

## 【0042】

もう一度図 3 を参照すると、実行は、ステップ 302 からステップ 304 に進む。ステップ 304 では、p c d f が C 以上であるか否かの判定が行われる。C 以上であると判定されると、実行はステップ 306 に進み、テストが停止されて、合格と明示される。ステッ

50

プ304において、C以上ではないと判定されると、実行はステップ308に進む。

【0043】

ステップ308では、 $1 - p c d f > C$ か否かの判定が行われる。C以上であると判定されると、実行はステップ310に進み、テストは、Cによる不合格と明示されて、停止される。Cによる不合格は、所望の確率に対して、ピット誤り率がテスト限界以上であると判定されたことを意味するものである。ステップ308において、C以上ではないと判定されると、実行はステップ312に進む。ステップ312では、ステップ206で起動されたタイマがTを超えたか否かの判定が行われる。超えたと判定されると、実行はステップ314に進む。ステップ314において、テストは、時間による不合格と明示されて、停止される。時間による不合格は、Cによる合格または不合格が生じたとは判定されずには、テストがTを超えたことを表している。望ましい実施態様の場合、Tは、少なくとも、フロー300の最悪のケースの実施時間にピット・レート(B)を掛けた値の1500倍になる。ステップ306、ステップ310、ステップ314のどれかにおいてテストが停止されると、必ず、フロー300とフロー200の両方が停止され、T、N、及び、Rに関する任意の記憶値がクリアされる。ステップ206で起動されたタイマがTを超えていない場合、実行は、ステップ312からステップ302に移行する。

【0044】

本発明の実施態様によれば、所望の確率に対して、ピット誤り率が十分に低いか否かの結論を引き出すことができると、即座に、ピット誤り率テストが停止するので、必要な最短時間内においてピット誤り率を求めることが可能である。ピットの測定数が最少であれば、測定時間が最短になり、テスト・スループットが最大になる。スループットの最大化は、とりわけ、ピット誤り率テストが潜在的に製造ラインの障害になる可能性がある、製造テストにおいて重要である。ピット誤り率の予測通常範囲に関する事前の情報が得られる場合、本発明では、この情報が、テストの実施時間に関する判定プロセスに組み込まれるので、測定時間が短縮され、スループットが増大する。

【0045】

添付の図面及び上記説明においては、本発明の望ましい実施態様が解説及び例示されたが、もちろん、本発明は、開示の実施態様に制限されるものではなく、付属の請求項に記載され、定義されている本発明の精神及び範囲を逸脱することなく、さまざまな再構成、修正、及び、置換を施すことが可能である。本明細書で開示した発明の実施の形態について以下に列挙する。

【0046】

- (実施態様1) ピット誤り率テストを実施する方法であって、

- (d) 測定された誤りのあるピットの累積数に基づいてピット誤り率の事後累積分布関数( $p c d f$ )を計算するステップと、

- (e)  $p c d f$ が、ピット誤り率がピット誤り率テスト限界( $L$ )未満である所望の確率( $C$ )以上であるか否かを判定するステップと、

- (f)  $p c d f$ がC以上であるという判定に応答して、合格したテストを明示し、そのテストを停止するステップと、

- (g)  $1 - p c d f$ がC以上か否かを判定するステップと、

- (h)  $1 - p c d f$ がC以上であるという判定に応答して、不合格になったテストを明示し、そのテストを停止するステップと、

- (i) テスト時間が最長テスト時間( $T$ )を超えたという判定に応答して、不合格になったテストを明示し、そのテストを停止するステップと、

- (j)  $p c d f$ がC未満で、 $1 - p c d f$ がC未満であるという判定に応答して、ステップ(d)から(i)を反復するステップが含まれている、

- 方法。

- (実施態様2) さらに、

- (a) 複数のピットを測定するステップと、

- (b) 測定された誤りのあるピットの累積数を求めるステップと、

(c) ステップ (b) に応答して、ステップ (a) 及び (b) を反復するステップが含まれている。

実施態様 1 に記載の方法。

(実施態様 3) 複数の測定ビット数が、ステップ (a) 及び (b) の実施時間量がステップ (d) から (i) の最悪のケースの実施時間にほぼ等しくなるように設定されることを特徴とする、実施態様 2 に記載の方法。

(実施態様 4) さらに、

L を設定するステップと、

C を設定するステップと、

前記ビット誤り率の事前平均 ( $\mu$ ) を設定するステップと、

10

前記ビット誤り率の事前標準偏差 ( ) を設定するステップと、

T を設定するステップが含まれており、前記設定ステップが、ステップ (a) の実施前に実施されることを特徴とする、

実施態様 2 に記載の方法。

(実施態様 5) さらに、

テスト・ビット・レートを設定するステップと、

前記テスト・ビット・レートに前記最悪のケースの時間を掛けて、前記複数の測定ビット数を求めるステップが含まれることを特徴とする、

20

実施態様 3 に記載の方法。

(実施態様 6) ステップ (a) 及び (b) の最初の実施後に、ステップ (a) 及び (b) が、ステップ (d) から (i) と並行して実施されることを特徴とする、実施態様 3 に記載の方法。

(実施態様 7) 事前平均及び事前標準偏差が、履歴データまたは推定に基づくことを特徴とする、実施態様 2 に記載の方法。

(実施態様 8) 事前平均及び事前標準偏差が、それぞれ、0.5 及び 0.1 に設定されることを特徴とする、実施態様 2 に記載の方法。

(実施態様 9) さらに、値 a 及び b を計算するステップが含まれることと、ここで：

【数 6】

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

30

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

であることと；

$\mu$  が事前平均であり、 がビット誤り率の事前標準偏差であることを特徴とする、実施態様 1 に記載の方法。

40

(実施態様 10)

【数 7】

$$pcdf = \int_0^1 \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / Beta(R+a, N-R+b)$$

であることと特徴とする、実施態様 9 に記載の方法。

(実施態様 11) さらに、値 a 及び b を計算するステップが含まれることと、ここで：

50

## 【数8】

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

10

であることと；

$\mu$  が事前平均であり、 $\sigma$  がビット誤り率の事前標準偏差であることを特徴とする、実施態様 4 に記載の方法。

(実施態様 12)

## 【数9】

$$pcdf = \int_0^1 \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / Beta(R+a, N-R+b)$$

であることと特徴とする、実施態様 1 に記載の方法。

20

(実施態様 13) (a, b) がガウスのベータ関数であることを特徴とする、実施態様 10 に記載の方法。

(実施態様 14) 前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 1 に記載の方法。

(実施態様 15) 前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 10 に記載の方法。

(実施態様 16) 前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 11 に記載の方法。

(実施態様 17) 前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 14 に記載の方法。

30

(実施態様 18) 前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 15 に記載の方法。

(実施態様 19) 前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 16 に記載の方法。

(実施態様 20) ビット誤り率テストを実施するための製品であって、

少なくとも 1 つのコンピュータ可読媒体と、

前記少なくとも 1 つのコンピュータ可読媒体に納められたプロセッサ命令が含まれていて、前記プロセッサ命令が、少なくとも 1 つのプロセッサによって、前記少なくとも 1 つのコンピュータ可読媒体から読み取ることができるよう構成されており、それによって、前記少なくとも 1 つのプロセッサに、

40

(d) 測定された誤りのあるビットの累積数に基づいてビット誤り率の事後累積分布関数 (p c d f) を計算し、

(e) p c d f が、ビット誤り率がビット誤り率テスト限界 (L) 未満である、所望の確率 (C) 以上であるか否かを判定し、

(f) p c d f が C 以上であるという判定に応答し、合格したテストを明示して、そのテストを停止し、

(g) 1 - p c d f が C 以上か否かを判定し、

(h) 1 - p c d f が C 以上であるという判定に応答し、不合格になったテストを明示して、そのテストを停止し、

(i) テスト時間が最長テスト時間 (T) を超えたという判定に応答し、不合格になつ

50

たテストを明示して、そのテストを停止し、

( j )  $p c d f$  が  $C$  未満で、 $1 - p c d f$  が  $C$  未満であるという判定に応答して、ステップ ( d ) から ( i ) を反復するといった、

働きをさせるようになっていることを特徴とする、

製品。

( 実施態様 21 ) さらに、前記少なくとも 1 つのコンピュータ可読媒体に納められたプロセッサ命令が含まれていて、前記プロセッサ命令が、少なくとも 1 つのプロセッサによって、前記少なくとも 1 つのコンピュータ可読媒体から読み取ることができるように構成されており、それによって、前記少なくとも 1 つのプロセッサに、

( a ) 複数のビットを測定し、

10

( b ) 測定された誤りのあるビットの累積数を求め、

( c ) ステップ ( b ) に応答して、ステップ ( a ) 及び ( b ) を反復するといった、

働きをさせるようになっていることを特徴とする、

実施態様 20 に記載の製品。

( 実施態様 22 ) 前記複数の測定ビット数が、ステップ ( a ) 及び ( b ) の実施時間量がステップ ( d ) から ( i ) の最悪のケースの実施時間にほぼ等しくなるように設定されることを特徴とする、実施態様 21 に記載の製品。

( 実施態様 23 ) さらに、前記少なくとも 1 つのコンピュータ可読媒体に納められたプロセッサ命令が含まれていて、前記プロセッサ命令が、少なくとも 1 つのプロセッサによって、前記少なくとも 1 つのコンピュータ可読媒体から読み取ことができるように構成されており、それによって、前記少なくとも 1 つのプロセッサに、

20

$L$  を設定し、

$C$  を設定し、

前記ビット誤り率の事前平均を設定し、

前記ビット誤り率の事前標準偏差を設定し、

$T$  を設定するといった、

働きをさせるようになっていることと、ここで、 $L$ 、 $C$ 、事前平均、事前標準偏差、及び、 $T$  が、( a ) の実施前に設定されることを特徴とする、

実施態様 21 に記載の製品。

( 実施態様 24 ) さらに、前記少なくとも 1 つのコンピュータ可読媒体に納められたプロセッサ命令が含まれていて、前記プロセッサ命令が、少なくとも 1 つのプロセッサによって、前記少なくとも 1 つのコンピュータ可読媒体から読み取ことができるように構成されており、それによって、前記少なくとも 1 つのプロセッサに、

30

テスト・ビット・レートを設定し、

前記テスト・ビット・レートに前記最悪のケースの時間を掛けて、前記複数の測定ビット数を求めるといった、

働きをさせるようになっていることを特徴とする、

実施態様 22 に記載の製品。

( 実施態様 25 ) ステップ ( a ) 及び ( b ) の最初の実施後に、ステップ ( a ) 及び ( b ) が、ステップ ( d ) から ( i ) と並行して実施されることを特徴とする、実施態様 22 に記載の製品。

40

( 実施態様 26 ) 事前平均及び事前標準偏差が、履歴データまたは推定に基づくことを特徴とする、実施態様 21 に記載の製品。

( 実施態様 27 ) 事前平均及び事前標準偏差が、それぞれ、0.5 及び 0.1 に設定されることを特徴とする、実施態様 21 に記載の製品。

( 実施態様 28 ) さらに、前記少なくとも 1 つのコンピュータ可読媒体に納められたプロセッサ命令が含まれていて、前記プロセッサ命令が、少なくとも 1 つのプロセッサによって、前記少なくとも 1 つのコンピュータ可読媒体から読み取ことができるように構成されており、それによって、前記少なくとも 1 つのプロセッサに、

値  $a$  及び  $b$  を計算するといった、

50

働きをさせるようになっていることと、ここで：

【数10】

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

10

であることと；

$\mu$  が事前平均であり、 $\sigma$  がビット誤り率の事前標準偏差であることを特徴とする、実施態様20に記載の製品。

(実施態様29)

【数11】

$$pcdf = \int_0^t \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / Beta(R+a, N-R+b)$$

20

であることを特徴とする、実施態様28に記載の製品。

(実施態様30) さらに、前記少なくとも1つのコンピュータ可読媒体に納められたプロセッサ命令が含まれていて、前記プロセッサ命令が、少なくとも1つのプロセッサによって、前記少なくとも1つのコンピュータ可読媒体から読み取ることができるように構成されており、それによって、前記少なくとも1つのプロセッサに、

値a及びbを計算するといった、

働きをさせるようになっていることと、ここで：

【数12】

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

30

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

であることと；

$\mu$  が事前平均であり、 $\sigma$  がビット誤り率の事前標準偏差であることを特徴とする、実施態様23に記載の製品。

(実施態様31)

【数13】

$$pcdf = \int_0^t \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / Beta(R+a, N-R+b)$$

40

であることを特徴とする、実施態様20に記載の製品。

(実施態様32) 前記pcdfの計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様20に記載の製品。

(実施態様33) 前記pcdfの計算ステップが、目的書き込みコードを利用して実

50

施されることを特徴とする、実施態様 29 に記載の製品。

(実施態様 34) 前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 30 に記載の製品。

(実施態様 35) 前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 32 に記載の製品。

(実施態様 36) 前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 33 に記載の製品。

(実施態様 37) 前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 34 に記載の製品。

(実施態様 38) ビット誤り率テストを実施するようになっているシステム (100) 10 ) であって、

被測定物 (DUT) (104) にビット・シーケンス (116(1)) を入力するようになっているビット・シーケンス発生器 (102) と、

前記ビット・シーケンス発生器 (102) に相互運用できるように接続された遅延発生器 (108) と、

前記DUT (104) 及び前記遅延発生器 (108) に相互運用できるように接続されて、前記遅延発生器 (108) の出力 (126) と前記DUT (104) の出力 (124) ) を比較するようになっている、コンパレータ (110) と、

前記コンパレータ (110) に相互運用できるように接続されて、誤りのあるビットの累積数であるコンパレータ (110) の出力 (128) をカウントするようになっているカウンタ (112) と、

前記カウンタ (112) に相互運用できるように接続された制御コンピュータ (114) ) が含まれてあり、前記コンピュータ (114) が、

(d) 誤りのあるビットの累積数に基づいてビット誤り率の事後累積分布関数 (p c d f ) を計算し、

(e) p c d f が、ビット誤り率がビット誤り率テスト限界 (L) 未満である、所望の確率 (C) 以上であるか否かを判定し、

(f) p c d f が C 以上であるという判定に応答し、合格したテストを明示して、そのテストを停止し、

(g) 1 - p c d f が C 以上か否かを判定し、

(h) 1 - p c d f が C 以上であるという判定に応答し、不合格になったテストを明示して、そのテストを停止し、

(i) テスト時間が最長テスト時間 (T) を超えたという判定に応答し、不合格になったテストを明示して、そのテストを停止し、

(j) p c d f が C 未満で、1 - p c d f が C 以上であるという判定に応答して、ステップ (d) から (i) を反復するようになっていることを特徴とする、

システム。

(実施態様 39) 前記コンピュータ (114) が、さらに、

(a) 複数のビットを測定し、

(b) 測定された誤りのあるビットの累積数を求め、

(c) ステップ (b) に応答して、ステップ (a) 及び (b) を反復するようになっていることを特徴とする、

実施態様 38 に記載のシステム (100)。

(実施態様 40) 前記複数の測定ビット数が、(a) 及び (b) の実施時間量が (d) ) から (i) の最悪のケースの実施時間にほぼ等しくなるように設定されることを特徴とする、実施態様 39 に記載のシステム (100)。

(実施態様 41) 前記コンピュータ (114) が、さらに、

L を設定し、

C を設定し、

前記ビット誤り率の事前平均を設定し、

10

20

30

40

50

前記ビット誤り率の事前標準偏差を設定し、

Tを設定するようになっていることと、ここで、L、C、事前平均、事前標準偏差、及び、Tが、(a)の実施前に設定されることを特徴とする、

実施態様39に記載のシステム(100)。

(実施態様42)前記コンピュータ(114)が、さらに、

テスト・ビット・レートを設定し、

前記テスト・ビット・レートに前記最悪のケースの時間を掛けて、前記複数の測定ビット数を求めるようになっていることを特徴とする、

実施態様40に記載のシステム(100)。

(実施態様43)(a)及び(b)の最初の実施後に、(a)及び(b)が、(d) 10

から(i)と並行して実施されることを特徴とする、実施態様40に記載のシステム(100)。

(実施態様44)事前平均及び事前標準偏差が、履歴データまたは推定に基づくことを特徴とする、実施態様39に記載のシステム(100)。

(実施態様45)事前平均及び事前標準偏差が、それぞれ、0.5及び0.1に設定されることを特徴とする、実施態様39に記載のシステム(100)。

(実施態様46)前記コンピュータ(114)が、さらに、値a及びbを計算するようになっていることと、ここで：

【数14】

20

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

であることと；

30

$\mu$ が事前平均であり、がビット誤り率の事前標準偏差であることを特徴とする、実施態様38に記載のシステム(100)。

(実施態様47)

【数15】

$$pcdf = \int_0^1 \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / Beta(R+a, N-R+b)$$

であることと特徴とする、実施態様46に記載のシステム(100)。

40

(実施態様48)

(a、b)がガウスのベータ関数であることを特徴とする、実施態様47に記載のシステム(100)。

(実施態様49)前記コンピュータ(114)が、さらに、値a及びbを計算するようになっていることと、ここで：

【数16】

$$a = \mu \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

$$b = (1-\mu) \left[ \frac{\mu(1-\mu) - \sigma^2}{\sigma^2} \right]$$

10

であることと；

$\mu$  が事前平均であり、 $\sigma$  がビット誤り率の事前標準偏差であることを特徴とする、実施態様 4 1 に記載のシステム（100）。

（実施態様 5 0）

【数 1 7】

$$pcdf = \int_0^1 \rho^{R+a-1} (1-\rho)^{N-R+b-1} d\rho / Beta(R+a, N-R+b)$$

であることを特徴とする、実施態様 3 8 に記載のシステム（100）。

20

（実施態様 5 1）前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 3 8 に記載のシステム（100）。

（実施態様 5 2）前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 4 7 に記載のシステム（100）。

（実施態様 5 3）前記 p c d f の計算ステップが、目的書き込みコードを利用して実施されることを特徴とする、実施態様 4 9 に記載のシステム（100）。

（実施態様 5 4）前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 5 1 に記載のシステム（100）。

（実施態様 5 5）前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 5 2 に記載のシステム（100）。

30

（実施態様 5 6）前記目的書き込みコードが、不完全なベータ関数であることを特徴とする、実施態様 5 3 に記載のシステム（100）。

【図面の簡単な説明】

【図 1】ビット誤り率テスト・システムを例示したブロック図である。

【図 2】本発明の実施態様によるビット誤り率テストに関連したビット誤り測定を例示したフローチャートである。

【図 3】本発明の実施態様によるビット誤り率に関連したビット誤り率統計分析を例示したフローチャートである。

【符号の説明】

1 0 0 テスト・システム

40

1 0 2 ビット・シーケンス発生器

1 0 4 被測定物

1 0 8 遅延発生器

1 1 0 コンパレータ

1 1 2 カウンタ

1 1 4 制御コンピュータ

1 1 6 ビット・シーケンス

1 2 4 , 1 2 8 出力

【図1】

【図2】

【図3】

---

フロントページの続き

(56)参考文献 特表2004-524783(JP, A)

米国特許第5606563(US, A)

(58)調査した分野(Int.Cl., DB名)

H04L 1/00

H04L 1/20