(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-347369

(P2005-347369A)

(43) 公開日 平成17年12月15日(2005.12.15)

(51) Int.Cl.<sup>7</sup>

H01L 23/50

H01L 25/00

F 1

H01L 23/50

H01L 25/00

テーマコード(参考)

X 5FO67

B

審査請求 未請求 請求項の数 19 O L (全 22 頁)

(21) 出願番号

特願2004-162854 (P2004-162854)

(22) 出願日

平成16年6月1日(2004.6.1.)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 佐々木 敏夫

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 伊藤 富士夫

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 鈴木 博通

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5F067 AB03 BA03 CD00

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】チップ部品を有する半導体装置における小型化を図る。

【解決手段】半導体チップ3と、半導体チップ3の周囲に配置された複数のインナリード5aと、インナリード5aの端部と絶縁性の接着剤を介して接続し、かつ半導体チップ3と接着剤を介して接続するシート部材8と、それぞれインナリード5aに一体で繋がる複数のアウタリード5bと、半導体チップ3のパッド3cと複数のインナリード5aとをそれぞれ接続する複数のワイヤ6と、半導体チップ3と複数のインナリード5aとの間の領域において複数のインナリード5aのリード列に沿って配置されたバーリード5cとを有し、表面実装部品であるチップ部品が、半導体チップ3と複数のインナリード5aとの間の領域において、ワイヤ6の下部に配置されているとともに、バーリード5c上に搭載されており、チップ部品を有するQFP1の小型化を図ることができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数のリードと、

前記複数のリードそれぞれの端部と接続するシート部材と、

その正面に半導体素子および複数の電極を有しており、前記複数のリードの内側に配置され、さらに前記シート部材と接続する半導体チップと、

前記半導体チップの電極と前記複数のリードとをそれぞれ電気的に接続する導電性の複数のワイヤと、

前記半導体チップと前記複数のリードとの間の領域において前記ワイヤの下部に配置された表面実装部品であるチップ部品とを有することを特徴とする半導体装置。 10

**【請求項 2】**

請求項 1 記載の半導体装置において、前記半導体チップと前記複数のリードとの間の領域に 1 本または複数の共通リードが前記複数のリード列に沿って配置され、前記共通リード上に前記チップ部品が搭載されていることを特徴とする半導体装置。

**【請求項 3】**

請求項 2 記載の半導体装置において、前記チップ部品は、前記共通リードと半田接続で電気的に接続されていることを特徴とする半導体装置。

**【請求項 4】**

請求項 2 記載の半導体装置において、前記チップ部品は、前記共通リードと絶縁性接着剤を介して接続されていることを特徴とする半導体装置。 20

**【請求項 5】**

請求項 1 記載の半導体装置において、前記半導体チップと前記複数のリードとの間の領域に複数の共通リードが前記複数のリード列に沿って配置されており、さらに前記複数の共通リードのうち最も内側に配置された共通リードと前記半導体チップとの間の領域に前記チップ部品が配置されていることを特徴とする半導体装置。

**【請求項 6】**

請求項 1 記載の半導体装置において、前記チップ部品は、抵抗素子、インダクタ素子およびコンデンサ素子の何れかを有していることを特徴とする半導体装置。

**【請求項 7】**

請求項 1 記載の半導体装置において、前記チップ部品は、ESD 保護素子を有していることを特徴とする半導体装置。 30

**【請求項 8】**

請求項 1 記載の半導体装置において、前記チップ部品は、EMC 保護素子を有していることを特徴とする半導体装置。

**【請求項 9】**

請求項 1 記載の半導体装置において、前記チップ部品は、バイパスコンデンサ素子を有していることを特徴とする半導体装置。

**【請求項 10】**

請求項 1 記載の半導体装置において、前記チップ部品は、ダンピング抵抗素子を有していることを特徴とする半導体装置。 40

**【請求項 11】**

複数のリードと、

前記複数のリードそれぞれの端部と接続するシート部材と、

その正面に半導体素子および複数の電極を有しており、前記複数のリードの内側に配置され、さらに前記シート部材と接続する半導体チップと、

前記半導体チップの電極と前記複数のリードとをそれぞれ電気的に接続する導電性の複数のワイヤと、

前記半導体チップおよび前記複数のワイヤを封止する封止体と、

前記半導体チップの外部で、かつ前記封止体の内部に配置されており、インダクタ素子を備えた第 1 の受動部品とを有することを特徴とする半導体装置。 50

**【請求項 1 2】**

請求項 1 1 記載の半導体装置において、コンデンサ素子を有する第 2 の受動部品が前記半導体チップの外部で、かつ前記封止体の内部に配置されており、前記第 1 の受動部品と前記第 2 の受動部品とを含む降圧回路を有していることを特徴とする半導体装置。

**【請求項 1 3】**

請求項 1 1 記載の半導体装置において、コンデンサ素子を有する第 2 の受動部品が前記半導体チップの外部で、かつ前記封止体の内部に配置されており、前記第 1 の受動部品と前記第 2 の受動部品とを含む昇圧回路を有していることを特徴とする半導体装置。

**【請求項 1 4】**

請求項 1 1 記載の半導体装置において、コンデンサ素子を有する第 2 の受動部品が前記半導体チップの外部で、かつ前記封止体の内部に配置されており、前記半導体チップと前記複数のリードとの間の領域に 1 本または複数の共通リードが前記複数のリードのリード列に沿って配置され、前記共通リード上に前記第 1 および第 2 の受動部品が搭載されていることを特徴とする半導体装置。 10

**【請求項 1 5】**

請求項 1 1 記載の半導体装置において、コンデンサ素子を有する第 2 の受動部品が前記半導体チップの外部で、かつ前記封止体の内部に配置されており、前記半導体チップと前記複数のリードとの間の領域に複数の共通リードが前記複数のリードのリード列に沿って配置されており、さらに前記複数の共通リードのうち最も内側に配置された共通リードと前記半導体チップとの間の領域に前記第 1 および第 2 の受動部品が配置されていることを特徴とする半導体装置。 20

**【請求項 1 6】**

複数のリードと、前記複数のリードの端部に接合するシート部材とを有するリードフレームを用いて組み立てられる半導体装置の製造方法であって、

( a ) 前記シート部材と前記複数のリードの端部とが絶縁性接着剤を介して接合された前記リードフレームを準備する工程と、

( b ) 前記シート部材におけるチップ搭載部の外側で、かつ前記複数のリードより内側の領域に表面実装部品であるチップ部品を搭載する工程と、

( c ) 前記 ( b ) 工程の後、前記シート部材の前記チップ搭載部に半導体チップを搭載する工程と、 30

( d ) 前記半導体チップの正面の複数の電極と前記複数のリードそれぞれを導電性の複数のワイヤでそれぞれ電気的に接続する工程と、

( e ) 前記半導体チップおよび前記複数のリードを樹脂封止して封止体を形成する工程と、

( f ) 前記リードフレームから前記複数のリードを分離して個片化する工程とを有することを特徴とする半導体装置の製造方法。 40

**【請求項 1 7】**

請求項 1 6 記載の半導体装置の製造方法において、前記 ( a ) 工程で、前記シート部材の前記チップ搭載部の外側で、かつ前記複数のリードより内側の領域に、前記複数のリードのリード列に沿って 1 本または複数の共通リードが配置された前記リードフレームを準備した後、前記 ( b ) 工程で、前記共通リード上に前記チップ部品を搭載することを特徴とする半導体装置の製造方法。 40

**【請求項 1 8】**

請求項 1 6 記載の半導体装置の製造方法において、前記 ( b ) 工程で、銀ペーストを介して前記チップ部品を搭載し、前記搭載後、ベーク処理を行うことを特徴とする半導体装置の製造方法。

**【請求項 1 9】**

請求項 1 6 記載の半導体装置の製造方法において、前記 ( b ) 工程で、半田ペーストを介して前記チップ部品を搭載し、前記搭載後、リフロー処理を行うことを特徴とする半導体装置の製造方法。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置およびその製造方法に関し、特に、チップ部品を有する半導体装置およびその製造方法に適用して有効な技術に関する。

**【背景技術】****【0002】**

従来の電子装置（半導体装置）では、第1の電気回路を構成する集積回路構成素子と非集積回路構成素子とは互いに接続され、次に被覆成形層により被覆成形されることにより標準パッケージを形成している（例えば、特許文献1参照）。 10

**【0003】**

また、従来の電源装置は、所定のタイミングでエネルギーを供給するエネルギー供給回路と、エネルギー供給回路から供給されるエネルギーを受け取り、そのエネルギーを保存するエネルギー保存回路とを備えている（例えば、特許文献2参照）。

**【0004】**

さらに、従来の半導体装置は、半導体チップ内の回路部ごとにバスバーを分離して接続することにより、前記回路部ごとに電源を供給することができ、さらにインナリードのピッチに無関係にバスバーへ接続できる特徴を生かして、パッドのピッチをインナリードのピッチより小さくしたり、パッドを千鳥配置にするなどして、電源用のパッドを増やしたり、従来電源用に使用していたリードを信号用などに利用する（例えば、特許文献3参照）。 20

**【特許文献1】特開平10-209365号公報（図1）****【特許文献2】特開2002-305248号公報（図1）****【特許文献3】WO 03/105226 A1公報（図56）****【発明の開示】****【発明が解決しようとする課題】****【0005】**

一般に、半導体チップと外部素子を組み合わせた回路では、寄生素子（R/C/L）が大きくなるため、そのロス分を配慮した大きな実装面積が必要となる。つまり、寄生素子によって性能が低下するのを防ぐために実装に大きな面積が必要となる。 30

**【0006】**

本発明者は、チップ部品を有する半導体装置の小型化について検討した。その結果、汎用タイプの半導体装置内にチップ部品を組み込むのは、困難であるとともに、パッケージサイズが特殊なものになるという問題を見出した。

**【0007】**

特に、外部素子がインダクタ素子の場合、半導体チップ上にインダクタ素子を形成すると、インダクタ素子の占有面積が大きくなつて半導体チップが大型化し、これにより、半導体チップの歩留りが低下したり、半導体チップの取り数が減少して結果的にコスト高を招くという問題を見出した。

**【0008】**

なお、前記特許文献1（特開平10-209365号公報）には、チップ部品と半導体チップを混載する構造についての開示はあるが、パッケージ内のスペースの有効活用を図る技術についての記載はない。 40

**【0009】**

また、前記特許文献2（特開2002-305248号公報）には、半導体チップ上にインダクタ素子を形成したDC-DC変換器を搭載して変換効率の向上を図る技術についての開示はあるが、半導体チップの大型化を防ぐ技術についての記載はない。

**【0010】**

さらに、前記特許文献3（WO 03/105226 A1公報）には、チップ-インナリード間にリング状のバスバーを配置した構造についての記載はあるが、パッケージ内

にチップ部品を埋め込んだ構造についての記載はない。

【0011】

本発明の目的は、チップ部品を有する半導体装置において小型化を図ることができる半導体装置およびその製造方法を提供することにある。

【0012】

また、本発明の他の目的は、チップ部品を有する半導体装置において電気的特性の向上を図ることができる半導体装置およびその製造方法を提供することにある。

【0013】

さらに、本発明の他の目的は、実装工程の簡略化を図ることができる半導体装置およびその製造方法を提供することにある。

【0014】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0016】

すなわち、本発明は、複数のリードと、前記複数のリードそれぞれの端部と接続するシート部材と、その主面に半導体素子および複数の電極を有しており、前記複数のリードの内側に配置され、さらに前記シート部材と接続する半導体チップと、前記半導体チップの周囲に配置された複数のリードと、前記半導体チップの電極と前記複数のリードとをそれぞれ電気的に接続する導電性の複数のワイヤと、前記半導体チップと前記複数のリードとの間の領域において前記ワイヤの下部に配置された表面実装部品であるチップ部品とを有するものである。

【0017】

さらに、本発明は、複数のリードと、前記複数のリードそれぞれの端部と接続するシート部材と、その主面に半導体素子および複数の電極を有しており、前記複数のリードの内側に配置され、さらに前記シート部材と接続する半導体チップと、前記半導体チップの周囲に配置された複数のリードと、前記半導体チップの電極と前記複数のリードとをそれぞれ電気的に接続する導電性の複数のワイヤと、前記半導体チップおよび前記複数のワイヤを封止する封止体と、前記半導体チップの外部で、かつ前記封止体の内部に配置されており、インダクタ素子を備えた第1の受動部品とを有するものである。

【0018】

また、本発明は、シート部材と複数のリードの端部とが絶縁性接着剤を介して接合されたリードフレームを準備する工程と、前記シート部材におけるチップ搭載部の外側で、かつ前記複数のリードより内側の領域に表面実装部品であるチップ部品を搭載する工程と、前記チップ部品搭載後、前記シート部材の前記チップ搭載部に半導体チップを搭載する工程と、前記半導体チップの主面の複数の電極と前記複数のリードそれぞれを導電性の複数のワイヤでそれぞれ電気的に接続する工程と、前記半導体チップおよび前記複数のリードを樹脂封止して封止体を形成する工程と、前記リードフレームから前記複数のリードを分離して個片化する工程とを有するものである。

【発明の効果】

【0019】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0020】

チップ部品を有する半導体装置において、前記チップ部品が半導体チップと複数のリードとの間の領域で、かつワイヤの下部に配置されていることにより、ワイヤの下部の空きスペースを有效地に利用することができる。これにより、チップ部品を有する半導体装置の

小型化を図ることができる。また、半導体装置の封止体の内部にチップ部品を配置することにより、半導体装置の外側にチップ部品を実装した場合に比較して寄生素子（R / C / L）によるロスを低減することができ、回路の高性能化を図ることができる。

【発明を実施するための最良の形態】

【0021】

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0022】

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

10

【0023】

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

【0024】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

20

【0025】

（実施の形態1）

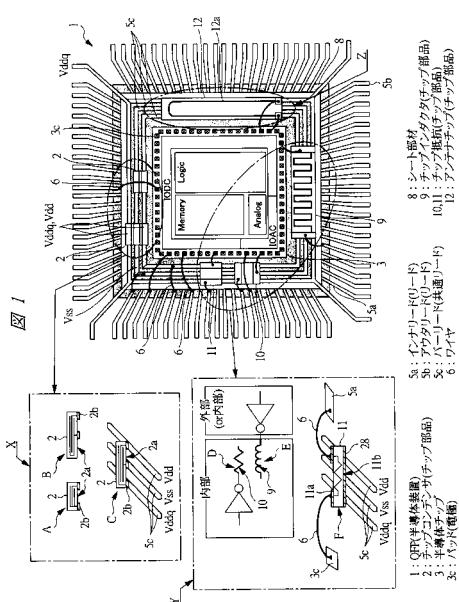

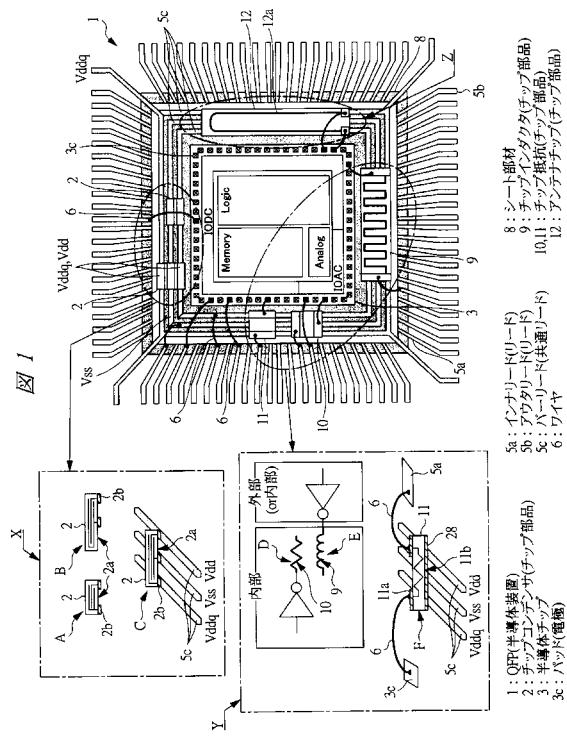

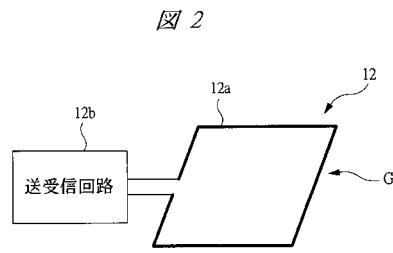

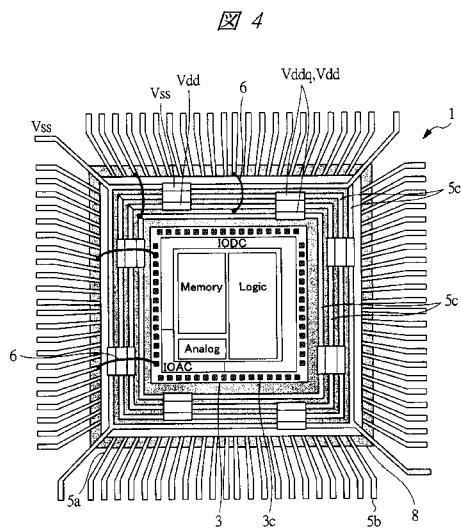

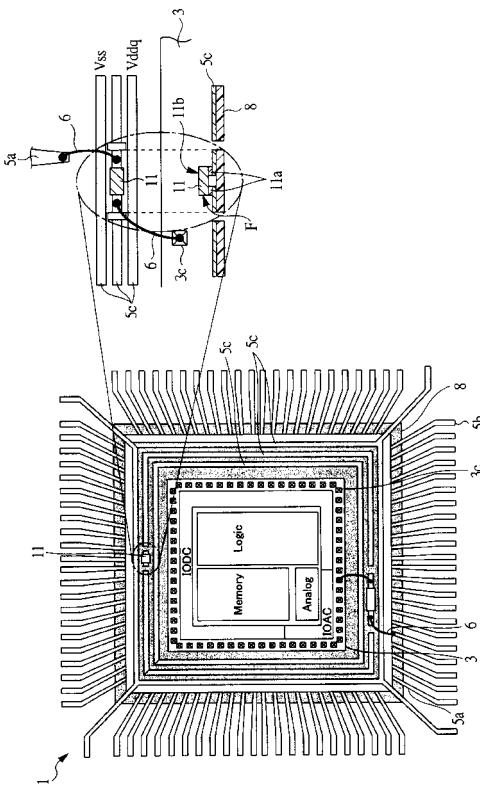

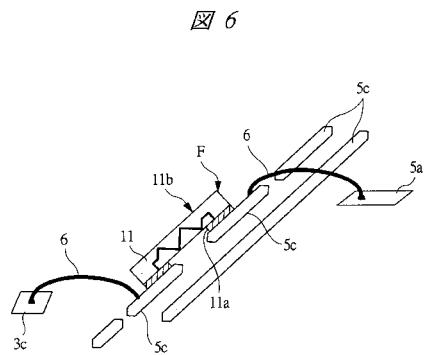

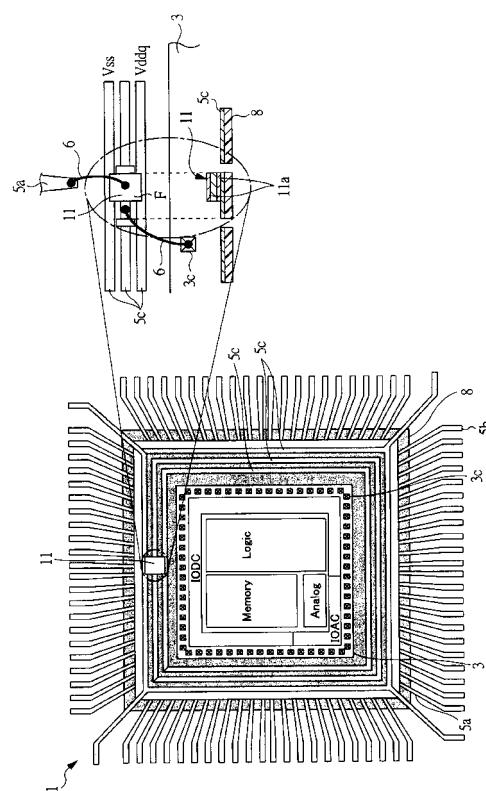

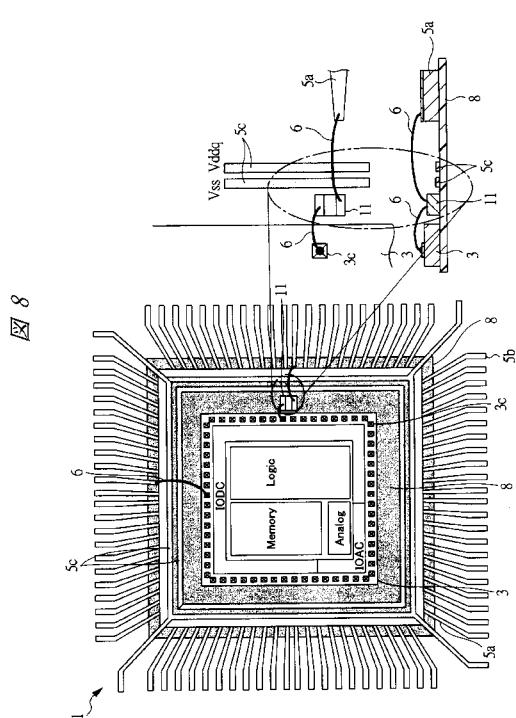

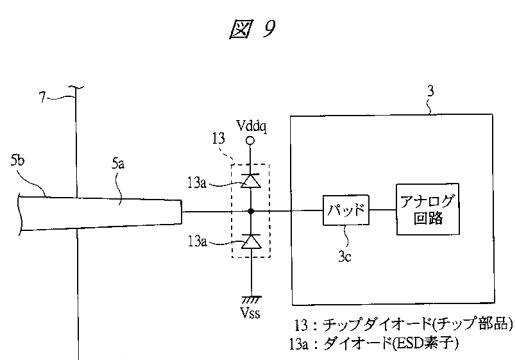

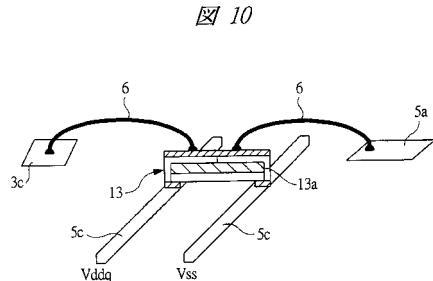

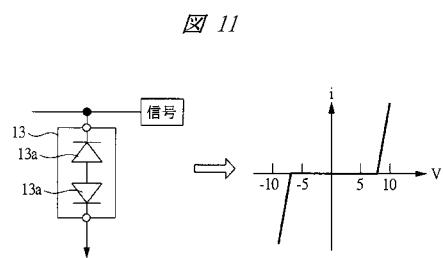

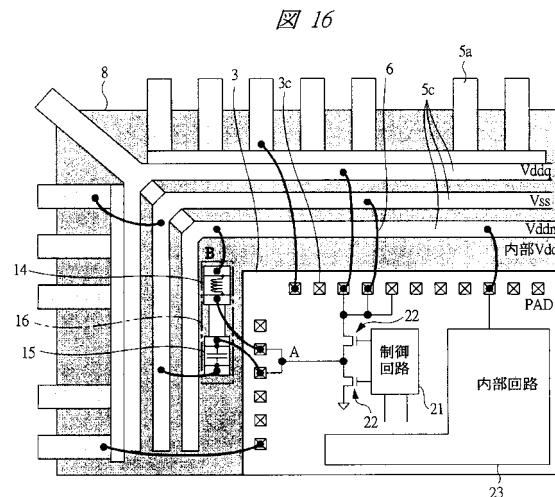

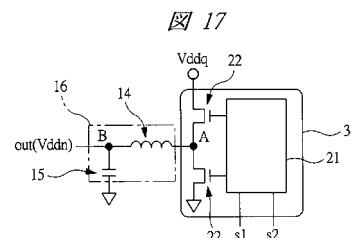

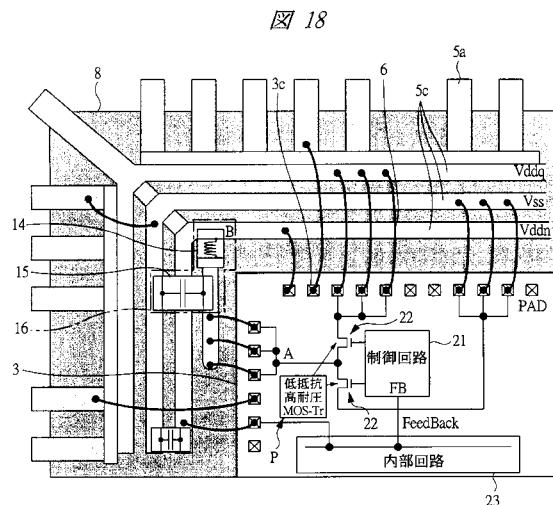

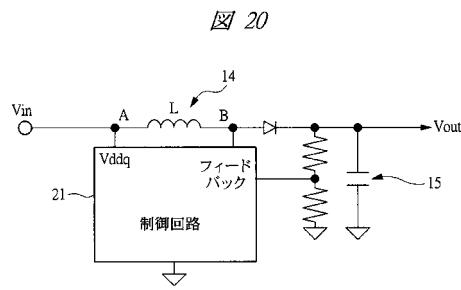

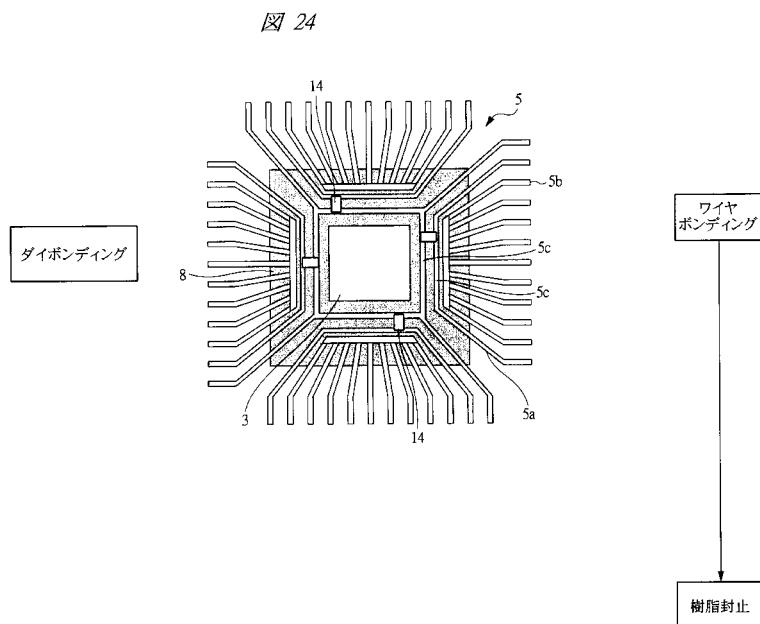

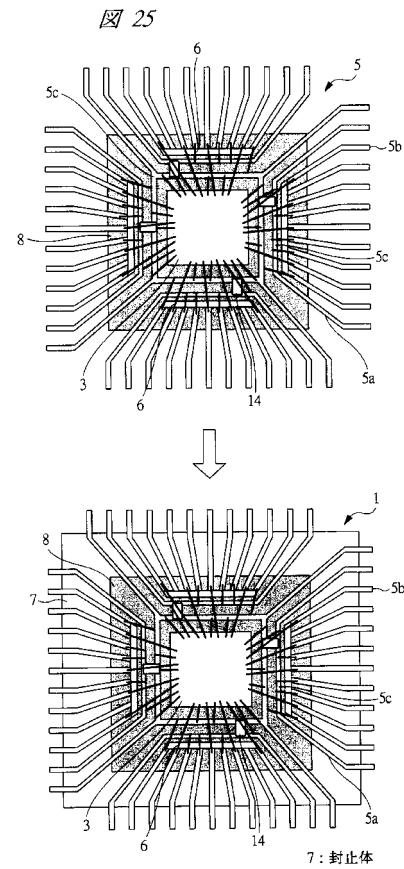

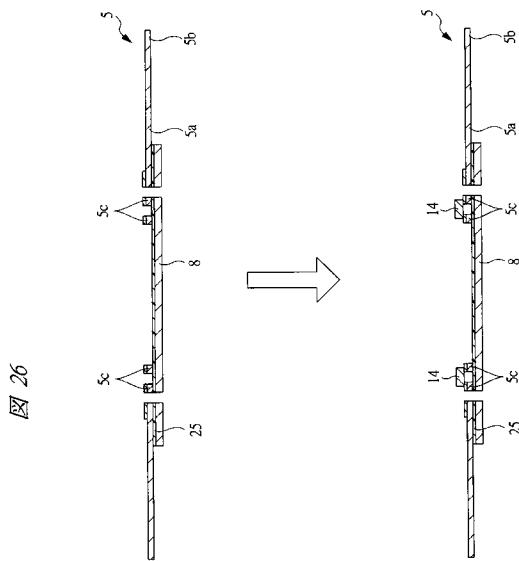

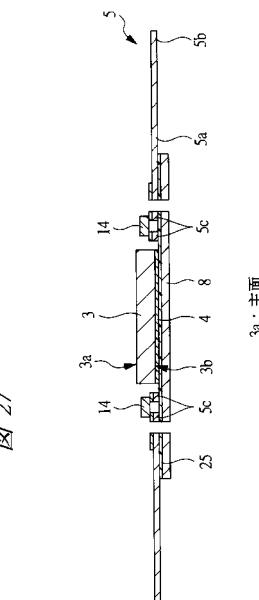

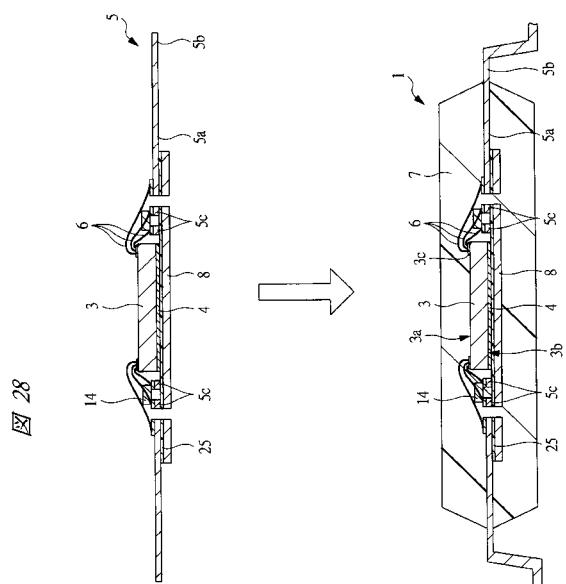

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図およびチップ部品の拡大接続図、図2は図1に示すZ部のチップ部品の構成図、図3は図1に示すZ部のチップ部品の変形例の構成図、図4は本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図、図5は本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図およびチップ部品の拡大接続図、図6は図5に示すチップ部品の接続状態を示す構成図、図7は本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図およびチップ部品の拡大接続図、図8は本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図およびチップ部品の拡大接続図、図9は本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す拡大部分平面図、図10は図9に示すチップ部品の接続状態を示す構成図、図11は図10に示すチップ部品の回路図および特性図、図12は図10に示す他のチップ部品の回路図、図13は本発明の実施の形態1の変形例の半導体装置におけるチップ部品の接続状態を示す平面図、図14は図13に示す半導体装置の回路構成を示す回路ロック図、図15は図14に示す回路構成における降圧回路の一例を示す回路接続図、図16は図15に示す降圧回路の一例を用いた等価回路図、図17は図16に示す回路構成における回路接続図、図18は図15に示す降圧回路の変形例を用いた等価回路図、図19は図18に示す回路構成における回路接続図、図20は図14に示す回路構成における昇圧回路の一例を示す回路接続図、図21は図20に示す昇圧回路の一例を用いた等価回路図、図22は図21に示す回路構成における回路接続図、図23は図1に示す半導体装置の組み立てにおけるリードフレームの構造とチップ部品付け状態の一例を示す平面図、図24は図1に示す半導体装置の組み立てにおけるダイボンディング完了時の構造の一例を示す平面図、図25は図1に示す半導体装置の組み立てにおけるワイヤボンディング完了時と樹脂封止完了時の構造の一例を示す平面図、図26は図1に示す半導体装置の組み立てにおけるリードフレームの構造とチップ部品付け状態の一例を示す断面図、図27は図1に示す半導体装置の組み立てにおけるダイボンディング完了時の構造の一例を示す断面図、図28は図1に示す半導体装置の組み立てにおけるワイヤボンディング完了時と樹脂封止完了時の構造の一例を示す断面図である。

30

40

50

## 【0026】

図1に示す本実施の形態1の半導体装置は、チップ部品が半導体チップ3の外側で、かつ封止体7(図25参照)の内部に配置された樹脂封止型の多ピンの半導体パッケージであり、ここでは、封止体7の4辺それぞれに複数のアウタリード5bが突出し、かつ各アウタリード5bがガルウィング状に曲げ成形されたQFP(Quad Flat Package)1を一例として取り上げて説明する。

## 【0027】

多ピンのQFP1の場合、各インナリード5aのチップ側の端部は、半導体チップ3に近づくにつれてその1本当たりの配置可能面積が小さく、リード密度が高くなるため、各インナリード5aの端部が半導体チップ3に近づける距離には限界があり、その結果、各インナリード5aの端部と半導体チップ3との間には、空き領域ができる傾向にある。そこで、本実施の形態1のQFP1は、多ピンのQFP1において、各インナリード5aの端部と半導体チップ3との間の空き領域を有効に活用するものであり、チップ部品を半導体チップ3とインナリード5aの端部との間の空き領域に配置することにより、QFP1の小型化や高性能化を図るものである。

## 【0028】

なお、本実施の形態1では、半導体チップ3とインナリード5aの端部との間の空き領域に、共通リードであるバーリード5cが設けられている場合を説明する。

## 【0029】

QFP1の詳細構成について説明すると、図28に示すように、その主面3aに半導体素子および複数の電極であるパッド3cを有しており、Memory(メモリ)、Logic(ロジック)、Analog(アナログ)、I0AC、I0DCなどの集積回路が形成された半導体チップ3と、半導体チップ3の周囲に配置された複数のリードであるインナリード5aと、インナリード5aの端部と絶縁性接着剤25を介して接続し、かつ半導体チップ3の裏面3bと銀ペースト4などの接着剤を介して接続する絶縁性のシート部材8と、それぞれインナリード5aに一体で繋がり、外部に露出する複数のアウタリード5bと、半導体チップ3のパッド3cと複数のインナリード5aそれぞれとを電気的に接続する導電性の複数のワイヤ6と、半導体チップ3と複数のインナリード5aとの間の領域において複数のインナリード5aのリード列に沿って配置された複数のリング状のバーリード(共通リード)5cとを有し、表面実装部品であるチップ部品が、半導体チップ3と複数のインナリード5aとの間の領域において、ワイヤ6の下部に配置されるとともに、バーリード5c上に搭載されている。

## 【0030】

例えば、図1に示すQFP1では、チップ-インナリード間に3本のバーリード5cが配置されている。なお、図1のX部に示すチップ部品は、チップコンデンサ2であり、その大きい方(B)の一般的なサイズは、0.6mm×0.3mmである。また、小さい方(A)の一般的なサイズは、0.4mm×0.2mmである。そこで、バーリード5cのリード幅を、例えば、0.25mm、リード間の隙間を0.15mmとすると、(0.25mm+0.15mm)×3=1.2mmとなり、大きい方のチップコンデンサ2の長手方向(0.6mm)であっても3本のバーリード5c上に十分に配置可能である。

## 【0031】

図1のX部に示すように、3本のバーリード5cは、例えば、Vddq、Vss、Vddであり、X部のAおよびBのチップコンデンサ2は、例えば、VssおよびVddとそれぞれ接続する。また、X部のCのチップコンデンサ2は、Vddq、VssおよびVddとそれぞれ接続する。その際、チップコンデンサ2それぞれの主面2aの電極2bと、それぞれのバーリード5cとを、直接半田接続によって電気的に接続することが好ましい。

## 【0032】

このように、Vdd-Vss間で接続するバイパスコンデンサ素子を有したチップ部品を、動作回路の近傍の端部に配置し、かつその際、直接半田接続によってバーリード5c

10

20

30

40

50

に接続することにより、電源 / GND の安定化を図ることができる。

#### 【0033】

次に、図 1 の Y 部に示すように、D のチップ抵抗 10 と E のチップインダクタ 9 を半導体チップ 3 の外側に配置してレギュレータなどの昇圧回路 (DC コンバータ) 用としてもよい。

#### 【0034】

また、図 1 の Y 部の F のチップ部品のように、ダンピング抵抗素子を有したチップ抵抗 11 をバーリード 5c 上に配置してこのチップ抵抗 11 の電極 11a と半導体チップ 3 のパッド 3c、およびインナリード 5a をそれぞれワイヤ 6 で接続して信号波形のバウンスを緩和させることができる。すなわち、信号の波形の乱れを緩和したり、放射ノイズを低減することができる。10

#### 【0035】

なお、チップ抵抗 11 は、バーリード 5c に絶縁性接着剤 28 を介して接続されている。すなわち、チップ抵抗 11 の電極 11a とその下部のバーリード 5c とは、絶縁されていなければならないため、チップ抵抗 11 はその裏面 11b が絶縁性接着剤 28 を介して接続されている。このようにバーリード 5c 上にチップ抵抗 11 などのチップ部品を配置してチップ - インナリード間のスペースを有効に活用することができる。

#### 【0036】

次に、図 1 の Z 部のチップ部品は、図 2 に示すアンテナ素子 12a を有した G のアンテナチップ 12 などであり、アンテナ素子 12a と送受信回路 12b を接続して送受信アンテナとして活用することができる。また、図 1 の Z 部のチップ部品は、図 3 に示すように、そのアンテナ素子 12a を充電制御系 12c と接続した H のアンテナチップ 12 とすることにより、電波受信による起電力発生手段として活用することができる。20

#### 【0037】

次に、図 4 の変形例は、チップ - インナリード間に配置するバーリード 5c の数を 4 本とするものであり、Vddq、Vss、Vdd の接地電位を交互に配置している。この場合、チップ部品は、ワイヤ接続ではなく、半田などを用いた直接接続が好ましい。

#### 【0038】

また、図 5 の変形例は、図 1 の Y 部の F のチップ部品のように、ダンピング抵抗素子を有するチップ抵抗 11 をバーリード 5c 上に配置する際に、ワイヤ高さを低くする構造を示したものである。30

#### 【0039】

すなわち、図 6 に示すように、チップ抵抗 11 の電極 11a を、分割されて相互に絶縁された 2 つのバーリード 5c に別々に直接半田付け（銀ペースト付けでもよい）などで接続し、さらに、チップ抵抗 11 の電極 11a に対してワイヤ接続するのではなく、これらの電極 11a と個々に接続され、かつ相互に絶縁された 2 つのバーリード 5c に対して別々に半導体チップ 3 のパッド 3c とインナリード 5a とをワイヤ接続するものである。

#### 【0040】

したがって、この場合のチップ抵抗 11 には、その表裏面のうちの何れか一方の片面に電極 11a が形成されればよく、必ずしも表裏両面に電極 11a が形成されていなくてもよい。40

#### 【0041】

これにより、半導体チップ 3 とインナリード 5a とのワイヤ接続の途中に、ダンピング抵抗素子を有したチップ抵抗 11 を介在させるため、信号波形のバウンスを緩和させることができるとともに、それぞれのバーリード 5c に対してワイヤ接続を行うため、図 1 の Y 部の F のチップ抵抗 11 のワイヤ高さに比較してワイヤ高さを低くすることができる。

#### 【0042】

その結果、バーリード上へのチップ部品の実装において高さを低く抑えた構造を実現することができる。

#### 【0043】

また、図7に示す変形例は、チップ抵抗11の表裏両面に電極11aが形成されている場合であり、その際、表面側の電極11aをインナリード5aとワイヤ6で接続し、裏面側の電極11aをバーリード5cと半田接続し、さらにこのバーリード5cがワイヤ6を介して半導体チップ3のパッド3cと接続されている。

#### 【0044】

このように、チップ抵抗11の表裏両面に電極11aが形成されている場合であっても、これら電極11aとインナリード5aやパッド3cとをワイヤ6で接続することができる。

#### 【0045】

次に、図8に示す変形例は、その拡大平面図および拡大断面図に示すように、チップ-インナリード間のバーリード5cが配置されていない空き領域のシート部材8上にチップ部品を搭載するものである。すなわち、半導体チップ3と複数のインナリード5aとの間の領域に、複数のバーリード5cが複数のインナリード5aのリード列に沿って配置されており、これら複数のバーリード5cのうち最も内側に配置されたバーリード5cと半導体チップ3との間の領域のシート部材8上にチップ部品が配置されているものである。チップ-インナリード間に配置されるバーリード5cの本数が1~2本で比較的少ない場合に、最も内側のバーリード5cと半導体チップ3との間の領域を有効に活用するものである。その場合、例えば、チップ部品として、ダンピング抵抗素子を有したチップ抵抗11を配置することにより、チップ-インナリード間の信号波形のバウンスを緩和させることができる。

10

20

30

40

#### 【0046】

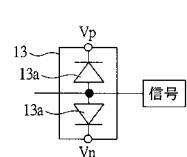

次に、図9に示す変形例は、チップ部品が保護素子を有している場合であり、チップ-インナリード間に、ダイオード13aなどの保護素子を有したチップ部品であるチップダイオード13を、図10に示すように各バーリード5cと半田付けなどで電気的に接続させて配置する。保護素子がE S D (Electro Static Discharge) 保護素子の場合、図11や図12の例に示すように、範囲外の電圧によるノイズをチップ-インナリード間の信号にのらないように保護することができる。例えば、インナリード5aから電源電位よりも高い電圧が入力された時に、正か負かによってチップダイオード13でノイズ電位を逃がすことができる。チップダイオード13は、+側サージからの保護、または-側サージからの保護などで用途を使い分ける。

#### 【0047】

なお、E S D 保護素子は、抵抗素子であってもよい。

#### 【0048】

また、保護素子は、例えば、フェライトチップからなるE M C (Electro Magnetic Compatibility) 保護素子であってもよく、同様に、電源 / 信号ノイズの対策として使用する。

#### 【0049】

次に、インダクタ素子を有するチップ部品が組み込まれた変形例の半導体装置について説明する。

#### 【0050】

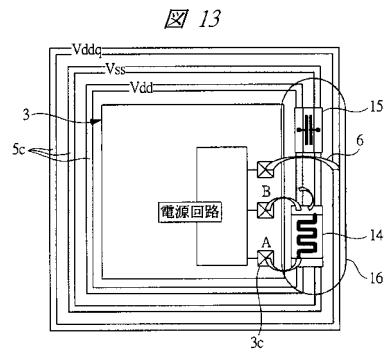

半導体装置においてチップ上にインダクタ素子を形成しようとすると、チップ面積が大きくなり歩留りが低下する。したがって、チップ上にはインダクタ素子を形成せず、図13に示す本実施の形態1の半導体装置のように、半導体チップ3の外側で、かつ封止体7(図25参照)の内部にチップインダクタ14を配置する。さらに、チップコンデンサ15も同様の位置に配置して、チップインダクタ14とチップコンデンサ15との組み合わせでL C フィルタ16を形成する。

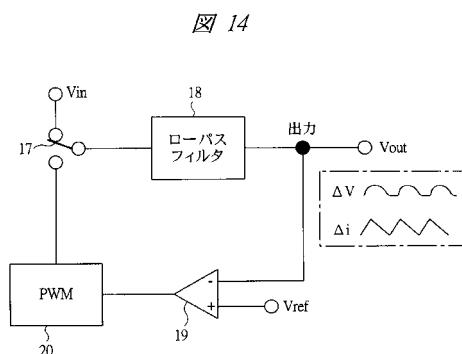

#### 【0051】

図14は電源レギュレータの回路図であり、S W 17、ローパスフィルタ18、エラーアンプ19、P W M (パルス幅変換制御スイッチングレギュレータ) 20などから構成され、ローパスフィルタ18にチップインダクタ14やチップコンデンサ15を使用する際

50

に、チップ上にチップインダクタ14やチップコンデンサ15を形成しようとすると、半導体チップ3が非常に大きくなり、したがって、図13に示す半導体装置のように、半導体チップ3の外側で、かつ封止体7(図25参照)の内部に、チップ部品によるチップインダクタ14とチップコンデンサ15とを配置することにより、電気抵抗を低減し、かつ応答性を向上させた半導体装置を実現できる。

#### 【0052】

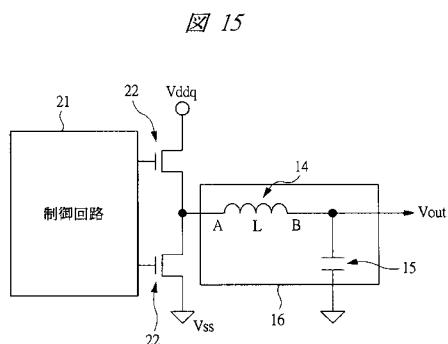

次に、図15は、チップインダクタ14とチップコンデンサ15とからなるLCフィルタ16が、チップ-インナリード間に配置されたDC-DCコンバータ(降圧回路)の回路図である。制御回路21に接続されたハイサイド/ロウサイドそれぞれのトランジスタ22のスイッチングによって発生する電流がパルス状となり、インダクタンス/容量負荷のL/Cに対して、脈流状の電流として印加されるが、その際の電流は、 $I = I_0(DC) - (V_0/L) \times t$ (脈流)となり、Lが大きいと脈流の電流は小さくなる。

#### 【0053】

また、tが短い(周波数高い)と同様に脈流の電流が小さくなる。そこで、LやCをパッケージ内に組み込むことで寄生素子を小さくし、大きな負荷を駆動できる程度に周波数を高くすることにより、内部組み込みによって大きなLを確保できない分をカバーする。さらに、出力に接続するコンデンサ(C)は、電源用のバーリード5cの空間をチップ容量Cにあてることで、C値を大きく確保することができ、さらに、脈流を低くして平滑化することができる。

#### 【0054】

図15に示す回路構成を本実施の形態1の半導体装置に組み込んだ降圧回路の一例を図16および図17に示す。

#### 【0055】

図16に示す半導体装置は、半導体チップ3の外部に配置されているとともに、封止体7(図25参照)の内部に配置され、かつインダクタ素子を備えた第1の受動部品であるチップインダクタ14と、チップインダクタ14と同様の領域に配置され、かつコンデンサ素子を有する第2の受動部品であるチップコンデンサ15とを含む降圧回路を有している。さらに、チップインダクタ14とチップコンデンサ15は、3本のバーリード5cのうち最も内側に配置されたバーリード5cと半導体チップ3との間の領域のシート部材8上に配置されている。また、3本のバーリード5cのうち最も内側のVddnはワイヤ6を介して半導体チップ3の内部回路23と接続されている。

#### 【0056】

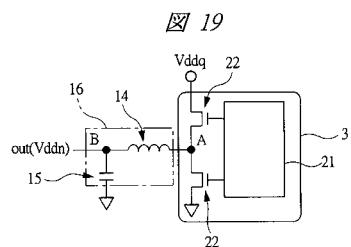

これに対して図18および図19に示す半導体装置の降圧回路では、電源用のバーリード5c上にチップインダクタ14とチップコンデンサ15が搭載されており、電源の供給能力を強化したものである。したがって、チップインダクタ14やチップコンデンサ15のバーリード5cとの接続を、ワイヤ6を使用せずに直接半田接続としている。さらに、図18のP部に示すトランジスタ22には、低抵抗で、かつ高耐圧のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)を使用している。

#### 【0057】

さらに、図19に示すように、制御回路21がチップ内部に組み込まれているため、周波数を上げることも可能であり、フィードバック(Feed Back)も頻繁に行うことができる。すなわち、トランジスタ22によるON/OFF制御を高速化できる。

#### 【0058】

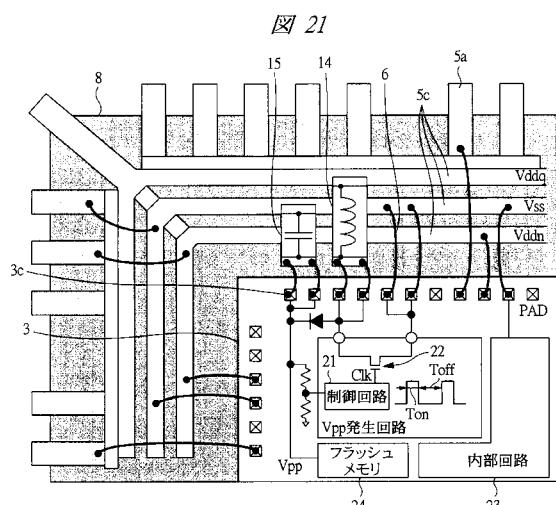

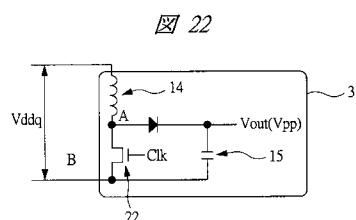

次に、図20は、チップインダクタ(第1の受動部品)14とチップコンデンサ(第2の受動部品)15とを含む昇圧回路の一般的な回路図であり、この昇圧回路の構成を、本実施の形態1の半導体装置に組み込んだ昇圧回路の一例を図21および図22に示す。

#### 【0059】

図21に示す構成においても、チップインダクタ14とチップコンデンサ15の両者は、半導体チップ3の外部に配置されているとともに、封止体7(図25参照)の内部に配置され、かつ両者ともバーリード5c上に搭載されている。図21および図22に示すV

10

20

30

40

50

$V_{pp}$  は、フラッシュメモリ 24 の書き込み用の高電圧であり、クロックオン  $T_{on}$  時間レベルをフィードバックすることにより、 $V_{pp}$  レベルを調整することができる。また、この昇圧回路によれば、 $V_{out}$  は、入力電源に対して、 $V_{out} = ((T_{on} + T_{off}) / T_{off}) \times V_{ddq}$  となり、 $V_{ddq}$  の何倍かの  $V_{out}$  を出力することができる。

#### 【0060】

以上のように本実施の形態 1 の半導体装置によれば、チップ部品を有する QFP 1 において、前記チップ部品が半導体チップ 3 と複数のインナリード 5a との間の領域で、かつ図 28 に示すように、ワイヤ 6 の下部に配置されていることにより、ワイヤ 6 の下部の空きスペースや、半導体チップ 3 とインナリード 5a との間の空きスペースを有効に利用することができる。10

#### 【0061】

これにより、チップ部品を有する QFP 1 の小型化を図ることができる。

#### 【0062】

また、QFP 1 の封止体 7 の内部にチップ部品を配置することにより、QFP 1 の外側にチップ部品を実装した場合に比較して寄生素子 (R / C / L) によるロスを低減することができ、回路の高性能化を図ることができる。

#### 【0063】

その結果、チップ部品を有する QFP 1 の電気的特性の向上を図ることができる。

#### 【0064】

また、半導体チップ 3 の外側で、かつ封止体 7 の内部にチップ部品を配置することにより、半導体チップ 3 の大型化を抑制できるとともに、実装基板への部品搭載数の低減化を図ることができる。20

#### 【0065】

これにより、QFP 1 の実装工程の簡略化を図ることができる。

#### 【0066】

また、インダクタ素子を有する第 1 の受動部品であるチップインダクタ 14 を、半導体チップ 3 の外側で、かつ封止体 7 の内部に配置することにより、製品仕様の変更に伴うインダクタ素子の変更を容易に行うことができる。30

#### 【0067】

さらに、インダクタ素子を有するチップインダクタ 14 を、半導体チップ 3 の外側で、かつ封止体 7 (図 25 参照) の内部に配置することにより、半導体チップ 3 の大型化を阻止することができ、その結果、半導体チップ 3 の歩留りの低下や半導体チップ 3 の取り数が減少することを抑制できる。

#### 【0068】

これにより、半導体チップ 3 のコスト高を招くことを阻止できる。

#### 【0069】

なお、QFP 1 において、半導体チップ 3 は、例えば、シリコンによって形成され、さらに、ワイヤ 6 は、例えば、金線である。

#### 【0070】

また、封止体 7 は、例えば、熱硬化性のエポキシ樹脂によって形成されている。さらに、インナリード 5a、アウタリード 5b およびバーリード 5c は、例えば、銅合金による薄板部材によって形成されている。40

#### 【0071】

また、シート部材 8 は、例えば、ガラスエポキシ樹脂やセラミックなどの絶縁性の薄板部材によって形成されたものであるが、これに限らず、例えば、薄い金属板 (ヒートスプレッダ) に絶縁性の接着層が形成されている部材などを用いてもよい。

#### 【0072】

次に、本実施の形態 1 の QFP 1 の製造方法について説明する。

#### 【0073】

10

20

30

40

50

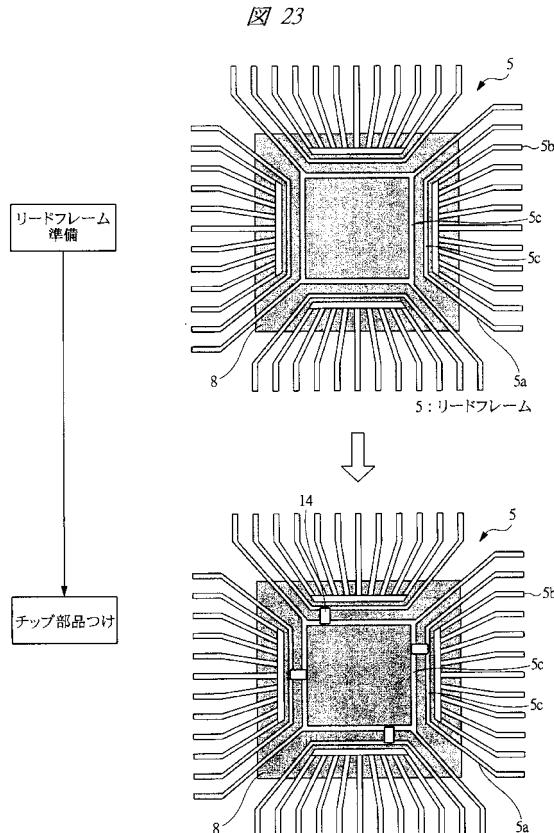

まず、複数のリードであるインナリード 5 a およびアウタリード 5 b と、薄いシート部材 8 を有する図 2 3 および図 2 6 に示すリードフレーム 5 を準備する。すなわち、シート部材 8 と複数のインナリード 5 a の端部とが絶縁性接着剤 2 5 を介して接合されたリードフレーム 5 を準備する。

【0074】

なお、シート部材 8 は、ポリイミドテープなどから形成された絶縁性のものであってもよいし、また、金属製のヒートスプレッダなどであってもよい。

【0075】

さらに、本実施の形態 1 のリードフレーム 5 には、シート部材 8 のチップ搭載部の外側で、かつ複数のインナリード 5 a の端部より内側の領域に、複数のインナリード 5 a のリード列に沿って複数の共通リードであるバーリード 5 c が配置されている。10

【0076】

その後、図 2 3 および図 2 6 に示すチップ部品つけを行う。すなわち、シート部材 8 におけるチップ搭載部の外側で、かつ複数のインナリード 5 a の端部より内側の領域に表面実装部品であるチップ部品を搭載する。ここでは、チップ部品の一例として、チップインダクタ 1 4 をバーリード 5 c 上に搭載する。

【0077】

その際、チップインダクタ 1 4 などのチップ部品をバーリード 5 c 上にこれと絶縁させて接続する場合には、絶縁性の接着剤などを用いてチップインダクタ 1 4 をバーリード 5 c に接続する。また、チップインダクタ 1 4 などのチップ部品をバーリード 5 c 上にこれと電気的に接続させて搭載する場合には、銀ペーストや半田ペーストなどの導電性のペースト材を用いてチップインダクタ 1 4 をバーリード 5 c に接続する。20

【0078】

なお、銀ペーストを介してチップ部品を搭載した場合、チップ部品搭載後、半導体チップ 3 の搭載前に前記銀ペーストのベーク処理を行う。一方、半田ペーストを介してチップ部品を搭載した場合、チップ部品搭載後、半導体チップ 3 の搭載前に前記半田ペーストのリフロー処理を行う。

【0079】

その後、図 2 4 および図 2 7 に示すように、シート部材 8 のチップ搭載部に半導体チップ 3 を搭載するダイボンディングを行う。30

【0080】

このように、本実施の形態 1 では、チップ部品の搭載を終えた後に半導体チップ 3 を搭載することにより、チップ部品の接着後のベーク処理やリフロー処理を、半導体チップ 3 を搭載する前に行うため、半導体チップ 3 が汚染することを防止できる。

【0081】

さらに、チップ部品を半導体チップ 3 より先にリードフレーム 5 上に搭載することにより、リードフレームの安定化を図ることができ、ワイヤショートおよびワイヤ切断などの不良発生のポテンシャルを低減してワイヤ 6 の損傷を防ぐことができる。

【0082】

その後、図 2 5 および図 2 8 に示すようにワイヤボンディングを行う。すなわち、半導体チップ 3 の主面 3 a の複数のパッド 3 c と複数のインナリード 5 a それぞれを導電性の複数のワイヤ 6 でそれぞれ電気的に接続する。40

【0083】

その際、図 2 8 に示すように、複数のワイヤ 6 のうちの少なくともいずれか 1 本は、チップ部品上を飛び越えさせてインナリード 5 a と接続する。

【0084】

その後、図 2 5 および図 2 8 に示すように樹脂封止を行う。すなわち、半導体チップ 3 、複数のインナリード 5 a および複数のワイヤ 6 を樹脂封止して封止体 7 を形成する。

【0085】

その後、リードフレーム 5 から複数のアウタリード 5 b を切断・分離して個片化すると50

ともに、各アウタリード 5 b をガルウィング状に曲げ成形して QFP 1 の組み立てを完了する。

【0086】

(実施の形態2)

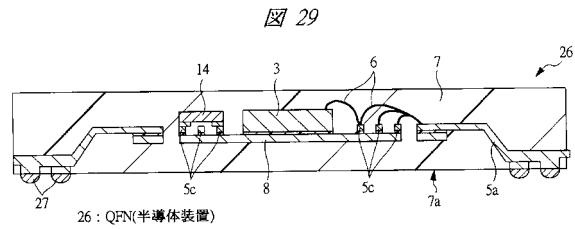

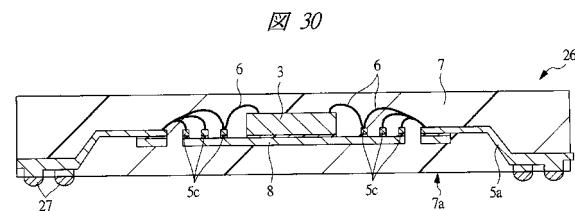

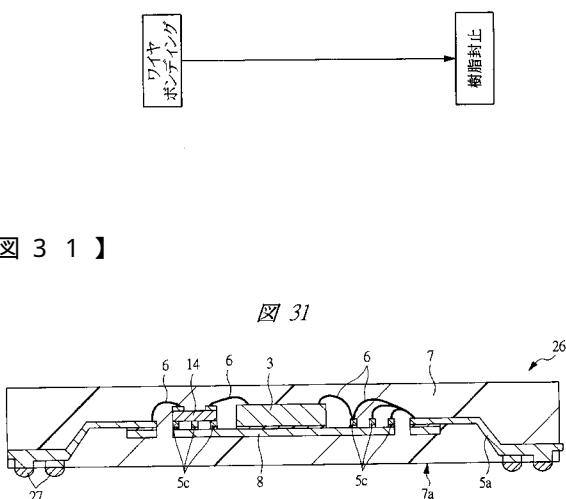

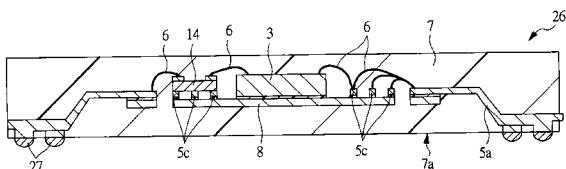

図29は本発明の実施の形態2の半導体装置の構造の一例を示す断面図、図30は図29に示す半導体装置においてチップ部品が搭載されていない箇所を切断した構造の一例を示す断面図、図31は本発明の実施の形態2の変形例の半導体装置の構造を示す断面図である。

【0087】

図29および図30に示す本実施の形態2の半導体装置は、封止体7の裏面7aの周縁部に外部端子である複数の半田めっき部27が並んで配置されたQFN(Quad Flat Non-leaded Package)26である。すなわち、各インナリード5aの一部が封止体7の裏面7aの周縁部に露出しており、この露出した箇所に半田めっき部27が形成されている。

【0088】

本実施の形態2のQFN26においても、実施の形態1のQFP1と同様に、半導体チップ3とインナリード5aの端部との間の空き領域にチップインダクタ14などのチップ部品が搭載されており、実施の形態1のQFP1と同様の効果を得ることができる。

【0089】

なお、図29に示すQFN26は、チップインダクタ14などのチップ部品がバーリード5c上に直接半田などで電気的に接続されたものであり、また、図31に示すQFN26は、チップ部品が絶縁性の接着剤などを介してバーリード5c上にこれと絶縁されて固定されたものであり、したがって、図31に示すQFN26の場合、チップ部品はワイヤ6を介してインナリード5aや半導体チップ3と電気的に接続されている。

【0090】

本実施の形態2のQFN26におけるその他の構造については、実施の形態1のQFP1と同様であるため、その重複説明は省略する。

【0091】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0092】

例えば、前記実施の形態1,2で説明した半導体装置におけるチップ部品の取り付けについては、半田や銀ペーストを用いた電気的、かつ直接的な接続であってもよく、あるいは、絶縁性の接着材を用いた接続であってもよい。

【0093】

また、前記実施の形態1,2で説明した半導体装置は、半導体チップ3とインナリード5aとの間の領域に、少なくとも1つのチップ部品が搭載されればよく、前記チップ部品は、コンデンサ、抵抗もしくはインダクタなどのいずれの表面実装部品であってもよい。

【0094】

また、前記実施の形態1,2では、半導体装置において、半導体チップ3とインナリード5aの端部との間に共通リードであるバーリード5cが配置されている場合を説明したが、前記半導体装置には、バーリード5cなどの共通リードは必ずしも配置されていなくてもよい。

【0095】

さらに、前記実施の形態1,2では、半導体装置において、半導体チップ3とインナリード5aとバーリード5cの間にチップインダクタ14などのチップ部品が配置されている場合を説明したが、チップインダクタ14などの前記チップ部品は、シート部材8において、バーリード5cをチップ側に近づけ、シート部材8の周囲側に空間を設け、バーリード5cとインナリード5aの間に配置しても良い。

10

20

30

40

50

**【産業上の利用可能性】****【0096】**

本発明は、電子装置および半導体装置とその製造方法に好適である。

**【図面の簡単な説明】****【0097】**

【図1】本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図およびチップ部品の拡大接続図である。

【図2】図1に示すZ部のチップ部品の構成図である。

【図3】図1に示すZ部のチップ部品の変形例の構成図である。

【図4】本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図である。 10

【図5】本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図およびチップ部品の拡大接続図である。

【図6】図5に示すチップ部品の接続状態を示す構成図である。

【図7】本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図およびチップ部品の拡大接続図である。

【図8】本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す平面図およびチップ部品の拡大接続図である。

【図9】本発明の実施の形態1の変形例の半導体装置の構造を封止体を透過して示す拡大部分平面図である。 20

【図10】図9に示すチップ部品の接続状態を示す構成図である。

【図11】図10に示すチップ部品の回路図および特性図である。

【図12】図10に示す他のチップ部品の回路図である。

【図13】本発明の実施の形態1の変形例の半導体装置におけるチップ部品の接続状態を示す平面図である。 30

【図14】図13に示す半導体装置の回路構成を示す回路ブロック図である。

【図15】図14に示す回路構成における降圧回路の一例を示す回路接続図である。

【図16】図15に示す降圧回路の一例を用いた等価回路図である。

【図17】図16に示す回路構成における回路接続図である。

【図18】図15に示す降圧回路の変形例を用いた等価回路図である。 30

【図19】図18に示す回路構成における回路接続図である。

【図20】図14に示す回路構成における昇圧回路の一例を示す回路接続図である。

【図21】図20に示す昇圧回路の一例を用いた等価回路図である。

【図22】図21に示す回路構成における回路接続図である。

【図23】図1に示す半導体装置の組み立てにおけるリードフレームの構造とチップ部品付け状態の一例を示す平面図である。

【図24】図1に示す半導体装置の組み立てにおけるダイボンディング完了時の構造の一例を示す平面図である。 40

【図25】図1に示す半導体装置の組み立てにおけるワイヤボンディング完了時と樹脂封止完了時の構造の一例を示す平面図である。

【図26】図1に示す半導体装置の組み立てにおけるリードフレームの構造とチップ部品付け状態の一例を示す断面図である。

【図27】図1に示す半導体装置の組み立てにおけるダイボンディング完了時の構造の一例を示す断面図である。

【図28】図1に示す半導体装置の組み立てにおけるワイヤボンディング完了時と樹脂封止完了時の構造の一例を示す断面図である。

【図29】本発明の実施の形態2の半導体装置の構造の一例を示す断面図である。

【図30】図29に示す半導体装置においてチップ部品が搭載されていない箇所を切断した構造の一例を示す断面図である。

【図31】本発明の実施の形態2の変形例の半導体装置の構造を示す断面図である。 50

## 【符号の説明】

## 【0098】

|      |                    |    |

|------|--------------------|----|

| 1    | QFP (半導体装置)        |    |

| 2    | チップコンデンサ (チップ部品)   |    |

| 2 a  | 正面                 |    |

| 2 b  | 電極                 |    |

| 3    | 半導体チップ             |    |

| 3 a  | 正面                 |    |

| 3 b  | 裏面                 |    |

| 3 c  | パッド (電極)           | 10 |

| 4    | 銀ペースト              |    |

| 5    | リードフレーム            |    |

| 5 a  | インナリード (リード)       |    |

| 5 b  | アウタリード (リード)       |    |

| 5 c  | バーリード (共通リード)      |    |

| 6    | ワイヤ                |    |

| 7    | 封止体                |    |

| 7 a  | 裏面                 |    |

| 8    | シート部材              |    |

| 9    | チップインダクタ (チップ部品)   | 20 |

| 10   | チップ抵抗 (チップ部品)      |    |

| 11   | チップ抵抗 (チップ部品)      |    |

| 11 a | 電極                 |    |

| 11 b | 裏面                 |    |

| 12   | アンテナチップ (チップ部品)    |    |

| 12 a | アンテナ素子             |    |

| 12 b | 送受信回路              |    |

| 12 c | 充電制御系              |    |

| 13   | チップダイオード (チップ部品)   |    |

| 13 a | ダイオード (ESD素子)      | 30 |

| 14   | チップインダクタ (第1の受動部品) |    |

| 15   | チップコンデンサ (第2の受動部品) |    |

| 16   | L C フィルタ           |    |

| 17   | S W                |    |

| 18   | ローパスフィルタ           |    |

| 19   | エラーアンプ             |    |

| 20   | P W M              |    |

| 21   | 制御回路               |    |

| 22   | トランジスタ             |    |

| 23   | 内部回路               |    |

| 24   | フラッシュメモリ           | 40 |

| 25   | 絶縁性接着剤             |    |

| 26   | QFN (半導体装置)        |    |

| 27   | 半田めっき部             |    |

| 28   | 絶縁性接着剤             |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

14: チップインダクタ(第1の受動部品)

15: チップコンデンサ(第2の受動部品)

【図14】

【図15】

【図16】

【図17】

【図18】

【図20】

【図19】

【図21】

【図23】

【図22】

【図24】

【図25】

【図26】

【図27】

【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

フロントページの続き

【要約の続き】