### (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

HO1L 21/77 (2006.01) HO1L 21/60 (2006.01)

(21) 출원번호

10-2008-0115952

(22) 출원일자

2008년11월20일

심사청구일자

2013년11월18일

(65) 공개번호

10-2009-0071367

(43) 공개일자

2009년07월01일

(30) 우선권주장

11/965,160 2007년12월27일 미국(US)

(56) 선행기술조사문헌

US4384899 A

US20050184219 A1

KR100701531 B1

JP58087812 A

(45) 공고일자

2016년03월31일

(11) 등록번호 10-1608084

(24) 등록일자

2016년03월25일

(73) 특허권자

스태츠 칩팩, 엘티디.

싱가포르, 569059, 테크포인트 #05-17/20, 65 앙 모 키오 스트리트 10

(72) 발명자

카마초, 지그먼드 알.

싱가포르, 싱가포르 789096, #02-01, 불리온 파크 타워 4, 렌터 루프 비엘케이 164

타이, 리오넬 치엔 후이

싱가포르, 싱가포르 560413, #09-903, 앙 모 키오 에버뉴 10 비엘케이 413

(뒷면에 계속)

(74) 대리인

강명구, 김현석

전체 청구항 수 : 총 15 항

심사관 :

### (54) 발명의 명칭 광학 센서를 구비한 반도체 소자 및 그 소자의 프론트 및 백사이드상에 상호접속 구조체를 형 성하는 방법

#### (57) 요 약

반도체 패키지는 빛을 전기적 신호로 변환시키는 광학적 액티브 영역을 구비한 반도체 다이를 갖는다. 확장 영역 이 반도체 다이 주위에 형성된다. 관통 홀 비어(THV)가 상기 확장 영역에 형성된다. 도전 재료가 THV에 융착된다. 패시베이션층이 반도체 다이 위에 형성된다. 패시베이션층은 빛이 반도체 다이 액티브 영역으로 통과 하도록 한다. 글래스층이 패시베이션층에 인가된다. 제 1 RDL이 THV 및 반도체 다이 접촉 패드 사이에 전기적으 로 연결된다. 추가적인 RDL이 반도체 다이의 프론트 및 백사이드에 형성된다. 언더 범프 메탈라이제이션(UBM)이 중간 도전층 위에 형성되어 그것과 전기적으로 연결된다. 솔더 재료가 UBM상에 융착되고 리플로우되어 솔더 범프 를 형성한다.

#### 대 표 도 - 도1

### (72) 발명자

### 바탄, 헨리 디.

싱가포르, 싱가포르 730352, #06-737, 우드랜즈 에 버뉴 1 비엘케이 352

### 트라스포르토, 아넬 세노사

싱가포르, 싱가포르 730349, #12-57, 우드랜즈 에 버뉴 3 비엘케이349

## 명세서

## 청구범위

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

#### 청구항 25

반도체 소자를 제조하는 방법에 있어서,

각각 광학적 액티브 영역을 갖는 다수의 반도체 다이를 포함하는 반도체 웨이퍼를 제공하는 단계;

상기 반도체 다이의 상기 광학적 액티브 영역에 빛의 통과를 위한 투명한 부분을 갖는 패시베이션층을 상기 반도체 웨이퍼의 전체 표면 위에 형성하는 단계;

상기 패시베이션층의 전체 표면 위에 글래스 웨이퍼를 장착하는 단계;

각각 상기 글래스 웨이퍼의 일부와 상기 패시베이션층의 투명한 부분을 갖는 개별적인 반도체 다이로 상기 반도 체 웨이퍼를 싱귤레이팅하는 단계;

상기 반도체 다이의 사이에 분리부를 구비한 캐리어에 상기 반도체 다이를 장착하는 단계;

상기 반도체 다이의 주변 주위에 팽창 영역을 형성하도록 상기 캐리어 위와 상기 분리부 내에 캡슐화제를 증착 시키는 단계;

상기 팽창 영역, 글래스 웨이퍼, 및 패시베이션층을 관통하는 제 1 비어를 형성하는 단계;

상기 반도체 다이 상의 접촉 패드에 상기 글래스 웨이퍼 및 패시베이션층을 관통하여 제 2 비어를 형성하는 단계; 및

상기 제 1 비어 및 제 2 비어에 도전 재료를 충진시키는 단계;를 포함하는 반도체 소자 제조 방법.

#### 청구항 26

제 25항에 있어서,

상기 제 1 비어 및 제 2 비어의 상기 도전 재료의 사이에 도전층을 형성하는 단계; 및

상기 도전층 위에 상호접속 구조체를 형성하는 단계;를 더 포함하는 반도체 소자 제조 방법.

#### 청구항 27

제 25항에 있어서,

상기 제 1 비어의 도전 재료와 전기적으로 연결된 도전층을 상기 광학적 액티브 영역의 맞은 편의 상기 반도체 다이의 표면 위에 형성하는 단계; 및

상기 도전층 위에 상호접속 구조체를 형성하는 단계;를 더 포함하는 반도체 소자 제조 방법.

#### 청구항 28

제 25항에 있어서,

상기 패시베이션층을 상기 반도체 웨이퍼의 전체 표면 위에 형성하는 단계가

프린팅, 라미네이션, 또는 스핀 코팅을 사용함을 더 포함하는 반도체 소자 제조 방법.

#### 청구항 29

제 25항에 있어서,

상기 팽창 영역을 형성하는 단계는,

상기 캐리어에 장착된 상기 반도체 다이의 주위에 인클로저(enclosure)를 형성하는 단계; 및

상기 인클로저에 상기 캡슐화제를 충진시키는 단계;를 더 포함하는 반도체 소자 제조 방법.

#### 청구항 30

반도체 소자를 제조하는 방법에 있어서,

각각 광학적 액티브 영역을 갖는 다수의 반도체 다이를 포함하는 반도체 웨이퍼를 제공하는 단계;

상기 반도체 다이의 상기 광학적 액티브 영역에 빛의 통과를 위한 투명한 부분을 갖는 패시베이션층을 상기 반 도체 웨이퍼 위에 형성하는 단계;

상기 반도체 웨이퍼를 개별적인 반도체 다이로 싱귤레이팅하는 단계;

상기 반도체 다이의 사이에 분리부를 구비한 캐리어에 상기 반도체 다이를 장착하는 단계;

상기 반도체 다이의 주위에 팽창 영역을 형성하도록 상기 캐리어 위와 상기 분리부 내에 캡슐화제를 증착시키는 단계; 및

상기 팽창 영역을 관통하는 제 1 도전 비어를 형성하는 단계;를 포함하는 반도체 소자 제조 방법.

### 청구항 31

제 30항에 있어서,

상기 반도체 웨이퍼의 성귤레이션 이전에 상기 패시베이션층 위에 글래스 웨이퍼를 장착시키는 단계를 더 포함하는 반도체 소자 제조 방법.

### 청구항 32

제 30항에 있어서,

상기 패시베이션층의 투명한 부분 위에 글래스 다이를 장착시키는 단계를 더 포함하는 반도체 소자 제조 방법.

#### 청구항 33

제 30항에 있어서,

상기 광학적 액티브 영역과 공통하는 상기 반도체 다이의 표면 위에 상기 제 1 도전 비어와 전기적으로 연결된 도전층을 형성하는 단계를 더 포함하는 반도체 소자 제조 방법.

### 청구항 34

제 30항에 있어서,

상기 패시베이션층을 관통하는 제 2 도전 비어를 상기 반도체 다이에 형성하는 단계를 더 포함하는 반도체 소자 제조 방법.

#### 청구항 35

반도체 소자에 있어서,

반도체 다이(54);

상기 반도체 다이 위에 배치된 클리어 패시베이션층(74)으로서, 클리어 패시베이션층(74) 내에 레이저 형성 개구를 가지며, 레이저 형성 개구가 반도체 다이로 연장되고, 상기 클리어 패시베이션층이 상기 반도체 다이의 광학적 액티브 영역으로 빛의 통과를 위한 투명한 부분을 포함하는 상기 클리어 패시베이션층(74);

상기 반도체 다이의 주위에 증착된 패시베이션층(86); 및

상기 클리어 패시베이션층(74) 내의 상기 레이저 형성 개구로 연결되는 상기 반도체 다이 위에 형성된 상호접속 구조체(interconnect structure)를 포함하는 반도체 소자.

#### 청구항 36

제 35항에 있어서,

상기 상호접속 구조체는 상기 클리어 패시베이션층(74)을 관통한 레이저 형성 도전 비어를 포함하는 반도체 소자.

### 청구항 37

제 35항에 있어서,

상기 상호접속 구조체는 상기 반도체 다이를 관통한 레이저 형성 도전 비어를 포함하는 반도체 소자.

#### 청구항 38

제 35항에 있어서,

상기 상호접속 구조체는 상기 반도체 다이와 전기적으로 연결되고, 상기 반도체 다이 및 클리어 패시베이션층 (74) 위에 형성된 도전층을 포함하는 반도체 소자.

#### 청구항 39

제 35항에 있어서,

상기 반도체 다이는 광학적 액티브 영역을 포함하는 반도체 소자.

### 발명의 설명

[0001]

### 발명의 상세한 설명

#### 기술분야

본 발명은 일반적으로 반도체 소자, 특히 광학 센서를 구비한 반도체 소자 및 그 소자의 프론트 및 백사이드상 에 상호접속 구조체를 형성하는 방법에 관한 것이다.

#### 배경기술

[0002]

반도체 소자들은 오락, 통신, 네트워크, 컴퓨터, 그리고 가정용 마켓 분야 제품들에서 발견된다. 반도체 소자들은 또한 군사, 우주 항공, 자동차, 산업용 콘트롤러 및 사무용 장비에서 발견된다. 반도체 소자들은 이들 응용 분야들 각각에 필요한 다양한 전기적 기능들을 수행한다.

[0003]

반도체 소자들의 제조는 다수 다이를 갖는 하나의 웨이퍼 형성을 포함한다. 각 반도체 다이는 수백 내지 수천의 트랜지스터, 다양한 전기적 기능을 수행하는 다른 액티브 및 패시브 장치들을 포함한다. 주어진 하나의 웨이퍼에 대해서, 그 웨이퍼로부터의 각 다이는 전형적으로 동일한 적기적 기능을 수행한다. 프론트-엔드(frontend) 제조는 일반적으로 웨이퍼 상에 반도체 소자를 형성하는 것을 의미한다. 최종 웨이퍼는 트랜지스터 및 다른 액티브 및 패시브 부품들을 포함하는 액티브 사이드(active side)를 갖는다. 백-엔드(back-end) 제조는 최종 웨이퍼를 개별적인 다이로 컷팅 또는 싱귤레이팅(singulating)하고 구조적 지지 및/또는 환경적 분리를 위해서 패키징하는 것을 의미한다.

[0004]

반도체 제조의 한 가지 목표는 신속하고, 신뢰성 있으며, 소형이고 보다 고 밀도의 직접 회로(IC)에 적절한 패키지를 저렴한 비용으로 생산하는 것이다. 플립 칩 패키지(flip chip package) 또는 웨이퍼 레벨 칩 스케일 패키지(wafer level chip scale package)(WLCSP)는 고속, 고밀도 그리고 큰 핀 수(count)를 요망하는 IC에 이상적으로 적합하다. 플립 칩 스타일 패키징은 다이의 액티브 사이드를 칩 캐리어 기판 또는 프린트 회로 기판(PCB)를 향해 아래로 접하도록 장착시키는 것을 포함한다. 다이상의 액티브 장치들과 캐리어 기판 상의 도전트랙들 사이의 전기적 및 기계적 상호접속은 다수의 도전성 술더 범프 또는 볼들을 포함하는 하나의 술더 범프 구조체를 통해서 달성된다. 그 솔더 범프들은 반도체 기판에 위치된 접촉 패드상에 융착된 솔더 재료에 인가되는 리플로우(reflow) 공정에 의해 형성된다. 이어서 그 솔더 범프들은 캐리어 기판에 솔더된다. 플립 칩 반도체 패키지는, 신호 전파를 감소시키고, 보다 낮은 캐패시턴스 및 전반적으로 양호한 회로 성능을 달성하기 위해서, 다이상의 액티브 장치로부터 캐리어 기판까지의 짧은 전기 도전 경로를 제공한다.

[0005]

많은 응용에서, WLCSP들을 적충하는 것이 요구된다. 적절한 전기적 상호접속이 완전한 장치 집적을 위해 제공되어야 한다. 그 전기적 상호접속은 관통 실리콘 비어(through silicon via, TSV)가 액티브 회로들과 간섭할 수 있는 다이의 액티브 영역에 TSV를 드릴닝함으로써 달성되어 왔다.

[0006]

일부 반도체 소자는 다이 중앙의 액티브 영역에 광학 센서를 갖는다. 이 같은 광학 센서는 빛 에너지를 전기적 신호로 변경시킨다. 그 전기적 신호들은 반도체 다이를 관통하여 다이 상호접속 구조체로 루팅(route)된다. 광학 센서는 상호접속 구조체에 추가적인 공간 제한을 가하는데, 전형적으로 상호접속 리루팅(rerouting)을 위해 사용되는 RDL이 글래스 또는 다이의 광-수용 사이드를 통과할 수 없기 때문이다. 따라서, 광학 센서를 갖는 반도체를 위한 최적의 웨이퍼 레벨 집적과 상호접속을 달성하는 것이 어렵다.

#### 발명의 내용

### 해결 하고자하는 과제

[0007]

적정한 웨이퍼 레벨 집적과 광학 센서를 갖는 반도체 소자 및 상호접속 형성 방법을 제공하는 것을 목적으로 한다.

#### 과제 해결수단

[8000]

하나의 실시예에서, 본 발명은, 빛을 전기적 신호로 변환시키는 광학적 액티브 영역을 갖는 반도체 다이를 제공하는 단계, 상기 반도체 다이 주위에 확장영역을 형성하는 단계, 상기 확장 영역에 관통 홀 비어(THV)를 형성하는 단계, 상기 THV에 도전 재료를 융착시키는 단계, 그리고 상기 반도체 다이 위에 패시베이션층을 형성하는 단계를 포함하는 반도체 소자 제조 방법을 제공한다. 패시베이션층은 빛이 반도체 다이의 광학적 액티브 영역으로의 통과하도록 한다. 본 방법은 또한, THV와 반도체 다이의 접촉 패드 사이에 전기적으로 연결된 제 1 중간 도전층을 형성하는 단계, 상기 제 1 중간 도전층 위에 제 1 언더 범프 메탈라이제이션(UBM)을 형성하고 그것과 전기적으로 연결시키는 단계, 상기 제 1 UBM상에 솔더 재료를 융착시키는 단계, 그리고 상기 솔더 재료를 리플로우시키어 제 1 솔더 범프를 형성하는 단계를 포함한다.

[0009]

다른 하나의 실시예에서, 본 발명은, 빛을 전기적 신호로 변환시키는 광학적 액티브 영역을 갖는 반도체 다이를 제공하는 단계, 상기 반도체 다이 주위에 확장영역을 형성하는 단계, 상기 확장 영역에 관통 홀 비어(THV)를 형성하는 단계, 상기 THV에 도전 재료를 융착시키는 단계, 그리고 상기 반도체 다이 위에 패시베이션층을 형성하는 단계를 포함하는 반도체 소자 제조 방법을 제공한다. 패시베이션층은 빛이 반도체 다이의 광학적 액티브 영

역으로의 통과하도록 한다. 본 방법은 또한, THV와 반도체 다이의 접촉 패드 사이에 전기적으로 연결된 제 1 중간 도전층을 형성하는 단계, 그리고 상기 제 1중간 도전층 위에 제 1 언더 범프 메탈라이제이션(UBM)을 형성하고 그것과 전기적으로 연결시키는 단계를 포함한다.

[0010] 다른 하나의 실시예에서, 본 발명은, 빛을 전기적 신호로 변환시키는 광학적 액티브 영역을 갖는 반도체 다이를 제공하는 단계, 그리고 상기 반도체 다이 위에 패시베이션층을 형성하는 단계를 포함하는 반도체 패키지 제조 방법을 제공한다. 패시베이션층은 빛이 반도체 다이의 광학적 액티브 영역으로의 통과하도록 한다. 본 방법은 또한, 반도체 다이의 접촉 패드 및 반도체 패키지의 프론트 및 백사이드 사이에 전기적 연결을 제공하는 상호접속 구조체를 형성하는 단계를 포함한다.

다른 하나의 실시예에서, 본 발명은, 빛을 전기적 신호로 변환시키는 광학적 액티브 영역을 갖는 반도체 다이를 포함하는 반도체 패키지를 제공한다. 패시베이션층이 반도체 다이 위에 형성된다. 패시베이션층은 빛이 반도체 다이의 광학적 액티브 영역으로의 통과하도록 한다. 상호접속 구조체가 반도체 다이의 접촉 패드 및 반도체 패키지의 프론트 및 백사이드 사이에 전기적 연결을 제공한다.

#### 直 과

적정한 웨이퍼 레벨 집적과 광학 센서를 갖는 반도체 소자 및 상호접속 형성 방법을 제공할 수 있다.

#### 발명의 실시를 위한 구체적인 내용

본 발명은 유사한 번호가 동일 또는 유사한 성분들을 나타내는 도면들을 참조하는 다음의 설명에 있는 하나 이상의 실시예들에서 기술될 것이다. 본 발명이 본 발명의 목적을 달성하기 위한 최선 모드 관점에서 기술되지만, 당업자는 첨부된 청구범위와 다음의 설명 및 도면에 의해 지지되는 그들의 균등물에 의해 한정되는 본 발명의 정신 및 범위내에 포함되는 변형, 변화 및 치환물을 커버하는 의도라는 것을 이해할 것이다.

반도체 소자들의 제조는 다수 다이를 갖는 웨이퍼 형성을 포함한다. 각 다이는 수백 내지 수천의 트랜지스터 및 하나 이상의 전기적 기능들을 수행하는 다른 액티브 및 패시브 장치들을 포함한다. 주어진 하나의 웨이퍼에 대해서, 그 웨이퍼로부터의 각 다이는 동일한 전기적 기능을 수행한다. 프론트-엔드(front-end) 제조는 일반적으로 웨이퍼 상에 반도체 소자를 형성하는 것을 의미한다. 최종 웨이퍼는 트랜지스터 및 다른 액티브 및 패시브 장치들을 포함하는 액티브 사이드를 갖는다. 백-엔드(back-end) 제조는 최종 웨이퍼를 개별적인 다이로 컷팅 및 싱귤레이팅(singulating)하고 구조적 지지 및/또는 환경적 분리를 위해서 패키징하는 것을 의미한다.

반도체 웨이퍼는 일반적으로 그곳에 놓이는 반도체 소자를 갖는 액티브 표면과, 실리콘과 같은 벌크(bulk) 반도체 재료로 형성된 백사이드 표면을 갖는다. 그 액티브 사이드 표면은 다수 반도체 다이를 포함한다. 그 액티브 표면은 적충, 패터닝, 도핑 및 열처리를 포함하는 다수 반도체 공정들에 의해 형성된다. 그 적충 공정에서, 반도체 재료는 열적 산화, 질화, 화학적 중착, 증발 및 스퍼터링을 포함하는 기술들에 의해 기판상에서 성장되거나 또는 융착된다. 포토리소그래피(phtolithograpy)는 표면 영역을 마스킹하고 바람직하지 않은 재료를 에칭제거하여 특수한 구조를 형성하는 것을 포함한다. 도핑 공정은 도펀트(dopant) 재료 농축물을 열확산 또는 이온주입에 의해 주입한다.

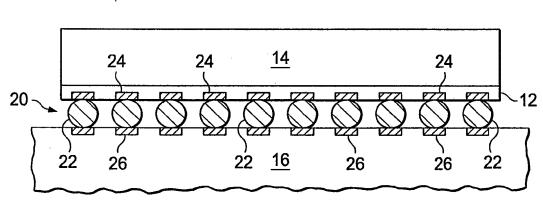

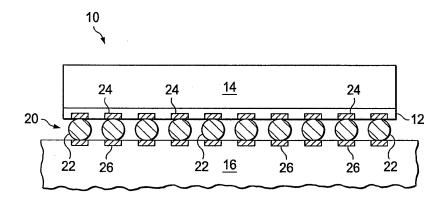

플립 칩 반도체 패키지(flip chip semiconductor package) 또는 웨이퍼 레벨 패키지(wafer level package, WLP)는 통상적으로 고속, 고밀도 및 큰 핀(pin) 수를 요구하는 집적 회로(IC)에 일반적으로 사용된다. 플립 칩스타일 반도체 소자(10)는 도 1에 도시된 바와 같이, 다이(14)의 액티브 영역(12)을 칩 캐리어 기판 또는 프린트 회로 보드(16)(PCB)를 향하여 아래로 접하도록 장착시키는 것을 포함한다. 그 액티브 영역(12)은 다이의 전기적 설계에 따른 액티브 및 패시브 장치들, 도전층들 및 절연층들을 포함한다. 아날로그 회로들이 액티브 영역(12)내에 형성된 하나 이상의 패시브 장치의 조합에 의해 생성되고 전기적으로 상호접속될 수 있다. 예를 들면, 하나의 아날로그 회로는 액티브 영역(12)내에 형성된 하나 이상의 인덕터, 캐패시터 그리고 레지스터를 포함할수 있다. 전기적 및 기계적 상호 접속들이 다수의 개별적인 도전성 솔더 범프들 또는 볼(22)들을 포함하는 솔더범프 구조체(20)를 통해서 달성된다. 솔더 범프들은 액티브 영역(12)상에 놓인 범프 패드들 또는 상호접속 사이트(24)상에 형성된다. 범프 패드(24)들은 액티브 영역(12)의 도전 트랙들에 의해 액티브 회로에 연결된다. 솔더범프(22)들은 솔더 리플로우(reflow) 공정에 의해 캐리어 기판(16)상의 접촉 패드 또는 상호접속 사이트(26)에전기적 또는 기계적으로 연결된다. 신호 전과를 감소시키고, 캐패시턴스를 낮추고, 전반적으로 양호한 회로 성능을 달성하기 위해서 플립 칩 반도체 소자는 다이(14)상의 액티브 장치로부터 캐리어 기판(16)의 도전 트랙까지의 짧은 전기 도전 통로를 제공한다.

[0012]

[0011]

[0013]

[0014]

[0015]

[0016]

[0017]

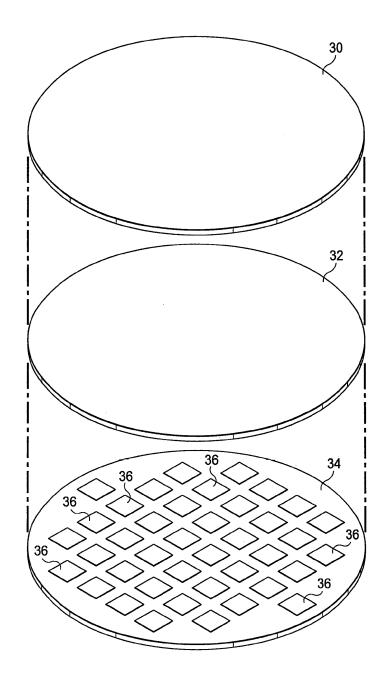

도 2a는 다수 반도체 다이(36)를 포함하는 이미지 센서 반도체 웨이퍼(34)를 도시하고 있다. 웨이퍼(34)는 실리 콘 또는 갈륨 비소(GaAs)일 수 있다. 반도체 다이(36)는 전술한 바와 같은 통상적인 집적 최로 공정들을 이용하여 반도체 웨이퍼(34)상에 형성된다. 각 반도체 다이(36)는, 빛을 감지하여 빛 에너지를 하나 이상의 전자 회로에 의한 또 다른 처리를 위해 전기 신호로 변환하는 전자 회로들, 그리고 광학 센서 또는 감광 영역 또는 광학적 액티브 영역을 포함한다. 전기 회로들은 전형적으로 상보성 금속 산화막 반도체(complementary metal oxide semiconductor, CMOS) 소자 및 광학 장치들은 전하결합 소자(charge-coupled device, CCD)일 수 있다. 광학적 액티브 반도체 다이의 예들은 오토포커스(autofocus) 콘트롤러, 디지털-아날로그 컨버터, 디지털 신호포로세서 및 이미지 프로세서를 포함한다.

[0018]

클리어 패시베이션층(clear passivation layer)(32)이 프린팅, 적층 또는 스핀 코팅에 의해 웨이퍼(34) 위에 형성된다. 글래스(glass) 웨이퍼(30)가 클리어 패시베이션층(32)에 인가된다. 글래스 웨이퍼(30)는 10-100 마이크로미터(ᡣ)의 두께와 낮은 굴절율을 갖는 광학 그래이드(grade) 글래스이다. 글래스 웨이퍼(30)는 전형적으로웨이퍼(34)와 동일한 형상 및 크기이다. 클리어 패시베이션층(32)과 글래스 웨이퍼(30)는 투광 또는 투명하여빛을 반도체 다이(36)의 광학 센서 또는 감광 영역 또는 광학적 액티브 영역까지 통과시킨다.

[0019]

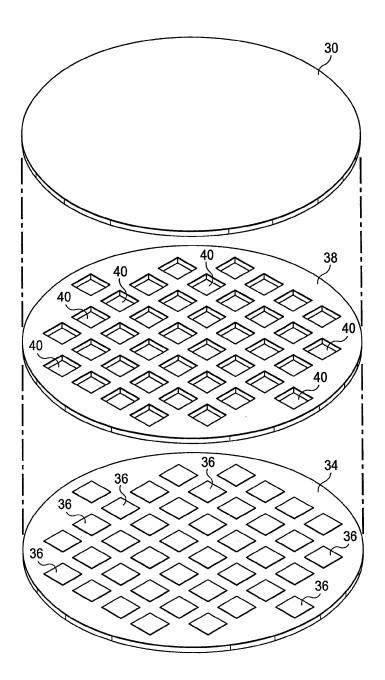

도 2b에서, 패시베이션층(38)이 반도체 다이(36)의 광학적 액티브 영역들 위에 정열될 윈도우(40)를 통하여 빛을 통과시킨다. 패시베이션층(38)은 프린팅 또는 적층에 의해 웨이퍼(34) 위에 형성될 수 있다. 글래스 웨이퍼(30)는 패시베이션층(38)에 인가된다. 윈도우(40) 및 글래스 웨이퍼(30)는 투광 또는 투명하여 빛을 반도체 다이(36)의 광학 센서 또는 선택적 감광 영역 또는 선택적 액티브 영역까지 통과시킨다.

[0020]

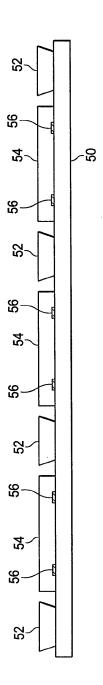

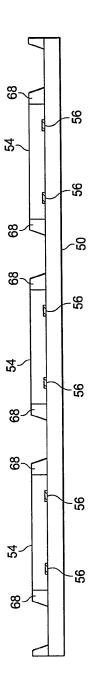

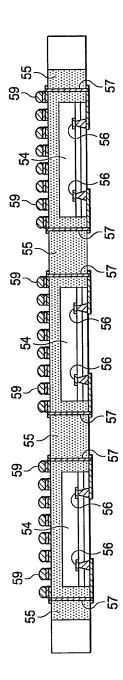

도 3a-3c는 웨이퍼 레벨 칩 스케일 패키지(wafer level chip scale package, WLCSP)용의 비-전도성 패시베이션 충 또는 폴리머 다이 확장 영역을 형성하는 공정을 도시하고 있다. 전술한 반도체 웨이퍼가 다이싱되어 반도체 다이를 개개의 유니트로 분리시킨다. 그 반도체 다이는 임시의 칩 캐리어상으로 운송된다. 도 3a는 커버래이 (coverlay) 테이프(50)에 고정된 몰드 캐버티 클램프(mold cavity clamp, 52)를 도시하고 있다. 반도체 다이 (54)는 웨이퍼로부터 운송되고, 반도체 다이의 액티브 표면과 접촉 패드(56)가 몰드 캐버티 클램프(52) 사이의 테이프를 아래로 접하여 향하도록 테이프(50)에 고정된다. 반도체 다이(54)는 또한 포스트 웨이퍼 쏘우 테이프 운송체(post wafer saw tape transfer)를 사용하여 커버래이 테이프(50)에 장착될 수 있다.

[0021]

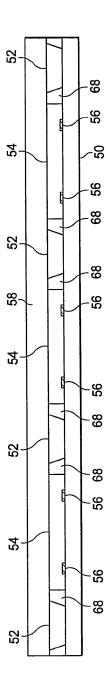

도 3b에서, 탑 몰드 클램프 덮개(58)가 몰드 캐버티 클램프(52) 위에 인가되어 반도체 다이(54) 주위에 덮개 또는 캐버티를 만든다. 그 캐버티는 커버래이 테이프(50) 까지 폴리머 몰딩 화합물로 충진된다. 그 폴리머 몰딩 화합물은 반도체 다이(54) 주위에 비-전도성 다이 확장 영역(68)을 형성한다. 충진 공정은 몰딩을 운송 및 주입시키는 것에 의해 수행될 수 있다. 또한, 충분한 연성, 부피 및 두께를 갖는 소프트 적층 필름이 다이를 캡슐화하기 위해 사용될 수 있다. 또한, 액상 에폭시 몰딩 및 압축 몰딩이 다이 확장 영역을 형성하도록 사용될 수 있다. 몰드 클램프 덮개(52, 58)가 도 3c에서 제거되었다. 커버래이 테이프가 벗겨져서 접촉 패드 및 반도체 다이(54)의 액티브 프론트 사이드가 노출된다.

[0022]

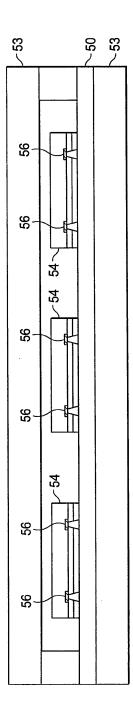

도 4a-4d는 반도체 다이 주위의 확장 영역 형성에 대한 다른 실시예를 도시하고 있다. 도 4a에서, 패시베이션 및 글래스층들을 구비한 반도체 다이(54)가 커버래이 테이프(50)에 장착된다. 반도체 다이(54)가 몰드 클램프(53)에 의해 감싸진다. 도 4b에서, 몰드 클램프(53)에 의해 형성된 덮개들은 몰딩 화합물(55)로 충진된다. 그 몰딩 화합물(55)은 반도체 다이(54)를 감싸서 반도체 다이 주위에 다이 확장 영역을 형성한다. 몰드 클램프(53)가 도 4c에서 제거되었다. 상호접속 구조체가 반도체 다이(54)상에 형성된다. THV(57)가 다이 확장 영역을 관통하여 형성된다. RDL이 다이 프론트 및 백사이드상에 형성된다. UBM 및 솔더 범프(59)가 또한 RDL 및 THV와 전기적 접촉관계로 형성된다.

[0023]

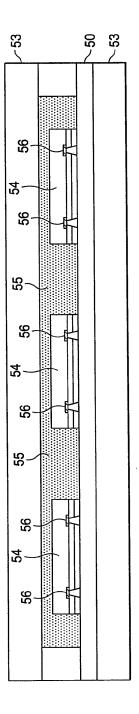

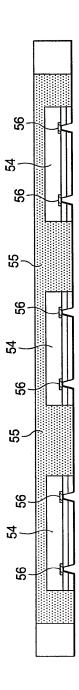

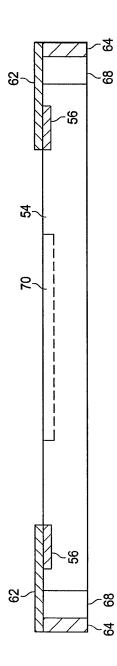

도 5a에서, 반도체 다이(54)는 전도되어 접촉 패드 및 다이의 액티브 프론트 사이드가 상향으로 된다. 다수의 관통 홀 비어(through hole via, THV)(64)이 에칭 또는 드릴닝에 의해 반도체 다이(54) 사이의 다이 확장 영역 (68)에 형성된다. 전기적 도전 재료가 증발, 전해 도금, 무전해 도금,또는 스크린 프린팅 공정을 사용하여 THV(64)에 융착된다. 그 도전 재료는 알루미늄(A1), 구리(Cu), 주석(Sn), 니켈(Ni), 금(Au) 또는 은(Ag)일 수 있다. 도 5a는 다이 확장 영역(58)의 에지에 형성된 하프-비어(half-via) THV(64)를 도시하고 있다. 리디스트 리뷰션층(redistribution layer, RDL)(62)이 THV(64) 및 반도체 다이(52)의 접촉 패드(56) 사이에 형성된다. RDL(62)은 알루미늄(A1), 알루미늄 구리 합금(AlCu), 구리(Cu) 또는 구리(Cu) 합금으로 이루어질 수 있다. RDL(62)은 THV(64) 및 접촉 패드(56) 사이에서 전기적 신호를 루팅하기 위한 중간 도전층으로서 작용한다. 광학적 액티브 영역(70)이 반도체 다이(54)의 내부 영역에 위치된다.

[0024]

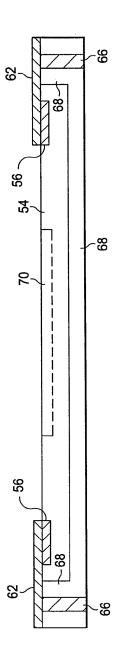

도 5b에서, THV(66)가 에칭 및 레이저 드릴닝에 의해 반도체 다이(54) 사이의 다이 확장 영역에 형성된다. 이

경우에, THV(66)들은 확장 영역(68)의 내부 영역에 형성된 풀(full) 비어인데, 즉, THV(66)이 확장 영역에 의해 완전히 감싸진다. 확장 영역(68)의 폴리머 몰딩 화합물은 또한 반도체 다이 액티브 표면 맞은 편의, 반도체 다이(54)의 백사이드를 커버한다. 도 5a에서 기술된 바와 같이, 전기적 도전 재료가 증발, 전해 도금, 무전해 도금, 또는 스크린 프린팅 공정을 사용하여 THV(66)에 융착된다. 그 도전 재료는 알루미늄(Al), 구리(Cu), 주석(Sn), 니켈(Ni), 금(Au) 또는 은(Ag)일 수 있다. RDL(62)이 THV(66) 및 반도체 다이(54)의 접촉 패드(56) 사이에 형성된다. RDL(62)은 THV(66) 및 접촉 패드(56) 사이에서 전기적 신호를 루팅하기 위한 중간 도전층으로서 작용한다. 광학적 액티브 영역(70)이 반도체 다이(54)의 내부 영역에 위치된다.

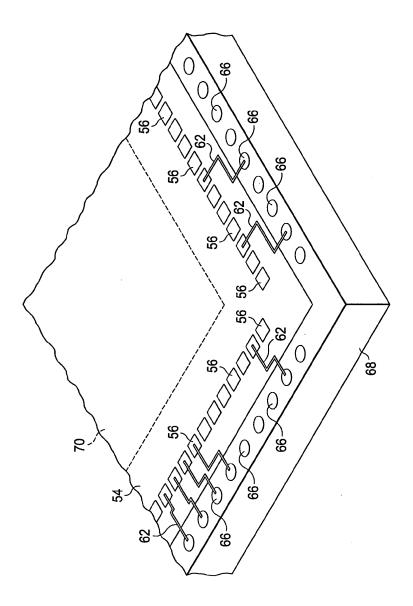

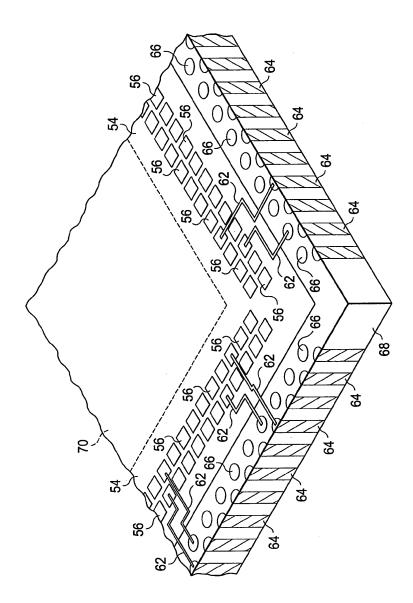

[0025] 도 5c는 반도체 다이(54)의 사시도이다. THV(66)는 다이 확장 영역(68)의 내부 영역에 형성된 풀(full) 비어이다. 확장 영역(68)은 THV(66)를 완전히 감싼다. RDL(62)은 접촉 패드(56)를 THV(66)에 전기적으로 연결시킨다. 액티브 회로들의 전기적 상호접속에 따라서, 접촉 패드(56)들의 일부는 인접한 THV(66)로부터 분리되는데, 즉, 어떤 접속 RDL도 형성되지 않는다. 광학적 액티브 영역(70)이 반도체 다이(54)의 내부 영역에 위치된다.

도 5d는 반도체 다이의 다른 사시도이다. 이 경우에, 하프-비어 THV(64) 및 풀-비어 THV(66)가 다이 확장 영역 (68)에 형성된다. 확장 영역(68)은 THV(66)를 완전히 감싼다. RDL(62)은 접촉 패드(56)를 THV(64, 66)에 연결시킨다. 액티브 회로들의 전기적 상호접속에 따라서, 접촉 패드(56)들의 일부는 인접한 THV(64, 66)로부터 분리되는데, 즉, 어떤 접속 RDL도 형성되지 않는다. 선택적으로 액티브 영역(70)이 반도체 다이(54)의 내부 영역에 위치된다.

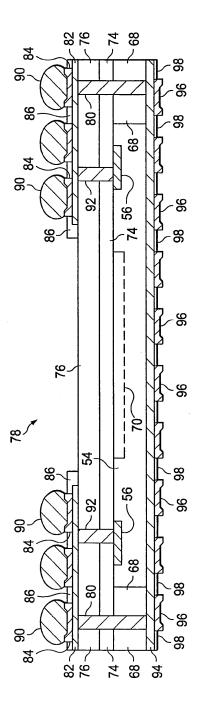

도 6을 참조하면, 클리어 패시베이션층(74)이 반도체 다이(54)의 액티브 표면상에 도시되었다. 글래스층(76)이 클리어 패시베이션층(74)에 인가되는 것으로 도시되었다. 글래스층(76)은 방전을 위해 접지될 수 있고, 그것의 표면상에 더스트(dust) 집적을 감소시킬 수 있다. THV(80)가 레이저 드릴닝에 의해 다이 확장 영역(68), 클리어 패시베이션층(74) 및 글래스층(76)을 관통하여 형성된다. RDL(82)이 글래스층(76)상에 형성된다. THV(80)가 RDL(82)를 반도체 패키지(78)의 백사이드상의 RDL(94)에 전기적으로 연결시킨다. RDL(82, 94)은 알루미늄(A1), 알루미늄 구리 합금(A1Cu), 구리(Cu) 또는 구리(Cu) 합금으로 이루어질 수 있다. RDL(82, 94)은 반도체 다이 (54)의 전기적 기능을 위해 필요한 것으로서 전기적 신호들을 루팅하는 중간 도전층으로서 작용한다. RDL(82)은 또한 THV(92)를 관통하여 접촉 패드(56)에 전기적으로 연결시킨다. THV(92)는 레이저 드릴닝에 의해 클리어 패시베이션층(74) 및 글래스층(76)을 관통하여 형성된다.

언더 범프 메탈라이제이션(under bump metalization, UBM)(84)이 RDL(82)을 전기적으로 연결시키기 위해 융착되고 패턴화된다. 하나의 실시예에서, UBM(84)은 웨팅(wetting)층, 배리어층, 그리고 부착층을 포함할 수 있다. 패시베이션층(86)이 구조적 지지 및 환경적 분리를 위해서 RDL(82) 위에 그리고 UBM(84)사이에 형성된다. 패시베이션층(86)은 이산화실리콘(SiO2), 산질화실리콘(SiON)질화실리콘(SixNy), 폴리미드(PI), 벤조사이클로뷰텐(BCB), 폴리벤조옥사졸(PBO), 또는 다른 절연재료로 이루어질 수 있다.

전기적 도전성 솔더 재료가 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 트린팅 공정을 통해서 UBM(84)위에 융착된다. 그 솔더 재료는 주석(Sn), 납(Pb), 니켈(Ni), 금(Au), 은(Ag), 구리(Cu), 비스무트(Bi) 및 그들의 합금과 같은 어떤 금속 또는 전기적 도전재료일 수 있다. 하나의 실시예에서, 그 솔더 재료는 Sn 63 중량 퍼센트 및 Pb 37중량 퍼센트일 수 있다. 그 솔더 재료는 구형 볼 또는 범프(90)를 형성하도록 도전 재료를 그것의 융점 이상으로 가열하여 리플로우(reflow)된다. 일부 응용에서, 솔더 범프(90)는 두 번 리플로우되어 UBM(84)과의 전기적 접촉을 개선시킨다. UBM(84) 및 솔더 범프(90)는 상호접속 구조체의 한 형태를 나타낸다.

반도체 다이(54)의 백사이드상에 UBM(96)이 융착되고 패턴화되어 RDL(94)을 전기적으로 연결시킨다. 하나의 실시예에서, UBM(96)은 웨팅층, 배리어층, 그리고 부착층을 포함할 수 있다. 패시베이션층(98)이 구조적 지지 및 환경적 분리를 위해서 RDL(94) 위에 형성된다. 패시베이션층(98)은 이산화실리콘(SiO2), 산질화실리콘(SiON), 질화실리콘(SixNy), 폴리이미드(PI), 벤조사이클로뷰텐(BCB), 폴리벤조옥사졸(PBO), 또는 다른 절연재료로 이루어질 수 있다.

빛이 글래스층(76) 및 클리어 패시베이션층(74)를 관통하여 광학 센서 또는 광학적 액티브 영역(70)까지 통과하는데, 이것들은 반도체 다이(54)내의 전자 회로들에 의한 또 다른 처리를 위해 빛 에너지를 전기적 신호들로 변환시킨다. 전기적 신호들은 접촉 패드들(56)을 관통하여 THV(80, 92)까지, RDL(82, 94)을 관통하여 UBM(84, 96)까지 그리고 솔더 범프(90)까지 루팅된다. 상호접속 구조체는 광학적 반도체 패키지(78)의 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

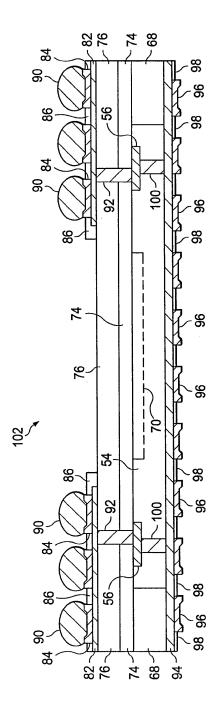

도 7에서, 클리어 패시베이션층(74)이 반도체 다이(54)의 액티브 표면상에 도시되었다. 글래스층(76)이 클리어

[0027]

[0026]

[0028]

[0029]

[0030]

[0031]

[0032]

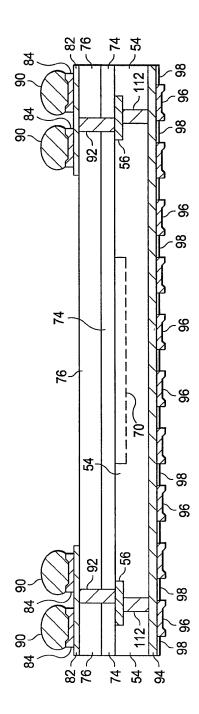

패시베이션층(74)에 인가되는 것으로 도시되었다. THV(92)가 레이저 드릴닝에 의해 클리어 패시베이션층(74) 및 글래스층(76)을 관통하여 형성된다. RDL(82)이 글래스층(76)상에 형성된다. THV(92)가 접촉 패드(56)을 RDL(82)에 전기적으로 연결시킨다. UBM(84)이 RDL(82)에 전기적으로 연결시키도록 융착되고 패턴화된다. 패시베이션층(86)이 구조적 지지 및 환경적 분리를 위해서 RDL(82) 위에 형성된다. 전기적 도전 솔더 재료가 증발, 전해도금, 무전해도금, 볼 드롭 또는 스크린 프린팅 공정을 통해서 UBM(84)위에 융착된다. 그 솔더 재료는 구형 볼 또는 범프(90)를 형성하도록 도전 재료를 그것의 융점 이상으로 가열하여 리플로우(reflow)된다.

- [0033]

- 접촉 패드(56)가 또한 관통 실리콘 비어(through silicon via, TSV)(100)를 경유하여 반도체 패키지(102)의 백사이드상의 RDL(94)에 전기적으로 연결된다. 이 실시예에서, 어떤 THV도 다이 확장 영역(68)에 형성되지 않는다. 대신에, TSV(100)이 에칭 또는 레이저 드릴닝에 의해 반도체 다이(54)의 액티브 영역을 관통하여 형성된다. UBM(96)은 융착되고 패턴화되어 RDL(94)에 전기적으로 연결된다. 패시베이션층(98)이 구조적 지지 및 환경적 분리를 위해서 RDL(94) 위에 형성된다.

- [0034]

- 빛이 글래스층(76) 및 클리어 패시베이션층(74)를 관통하여 광학적 액티브 영역(70)까지 통과하는데, 이것들은 반도체 다이(54)내의 전자 회로들에 의한 또 다른 처리를 위해 및 에너지를 전기적 신호들로 변환시킨다. 전기적 신호들은 접촉 패드들(56)을 관통하여 THV(92, 100)까지, RDL(82, 94)을 관통하여 UBM(84, 96)까지 그리고 솔더 범프(90)까지 루팅된다. 상호접속 구조체는 광학적 반도체 패키지(102)의 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

- [0035]

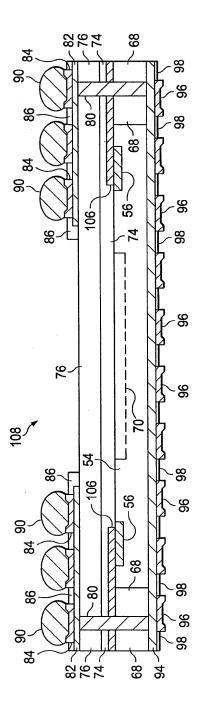

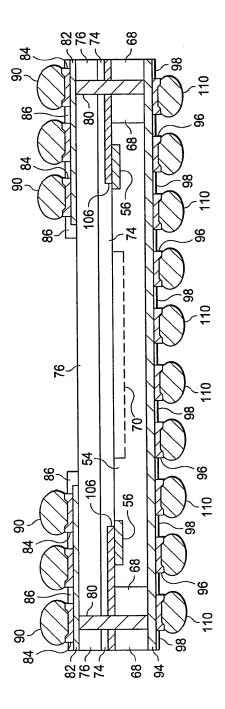

- 도 8에서, 클리어 패시베이션층(74)이 반도체 다이(54)의 액티브 표면상에 도시되었다. 글래스층(76)이 클리어 패시베이션층(74)에 인가되는 것으로 도시되었다. THV(80)가 레이저 드릴닝에 의해 다이 확장 영역(68), 클리어 패시베이션층(74) 및 글래스층(76)을 관통하여 형성된다. RDL(82)이 글래스층(76)상에 형성된다. RDL(106)이 THV(80)로 접촉 패드(56)에 전기적으로 연결되고, 차례로, RDL(82, 94)에 전기적으로 연결된다. UBM(84)이 융착되고 패턴화되어 RDL(82)에 전기적으로 연결된다. 패시베이션층(86)이 구조적 지지 및 환경적 분리를 위해서 RDL(82)위에 형성된다. 전기적 도전 솔더 재료가 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 프린팅 공정을 통해서 UBM(84)위에 융착된다. 그 솔더 재료는 구형 볼 또는 범프(90)를 형성하도록 도전 재료를 그것의 융점 이상으로 가열하여 리플로우(reflow)된다. UBM(96)이 융착되고 패턴화되어 RDL(94)에 전기적으로 연결된다. 패시베이션층(98)이 구조적 지지 및 환경적 분리를 위해서 RDL(94)위에 형성된다.

- [0036]

- 빛이 글래스층(76) 및 클리어 패시베이션층(74)를 관통하여 광학적 액티브 영역(70)까지 통과하는데, 이것들은 반도체 다이(54)내의 전자 회로들에 의한 또 다른 처리를 위해 빛 에너지를 전기적 신호들로 변환시킨다. 전기적 신호들은 접촉 패드들(56)을 관통하여, RDL(106), THV(80, 82), RDL(82, 94), 그리고 마지막으로 UBM(84, 96) 그리고 솔더 범프(90)까지 루팅된다. 상호접속 구조체는 광학적 반도체 패키지(108)의 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

- [0037]

- 도 9는 UBM(96)상에 형성된 선택적인 솔더 범프(110)를 구비한 도 6-8과 비슷하다. 전기적 도전 솔더 재료가 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 프린팅 공정을 통해서 UBM(96)위에 융착된다. 그 솔더 재료는 구형 볼 또는 범프(110)를 형성하도록 도전 재료를 그것의 융점 이상으로 가열하여 리플로우(reflow)된다.

- [0038]

- 도 10은 접촉 패드(56)를 RDL(82)에 전기적으로 연결시키는 THV(92)와, 접촉 패드(56)를 RDL(94)에 전기적으로 연결시키는 TSV(112)를 도시하고 있다. 다른 부품들은 전술한 것과 유사한 기능들을 갖는다.

- [0039]

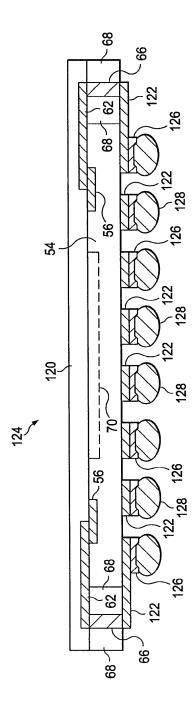

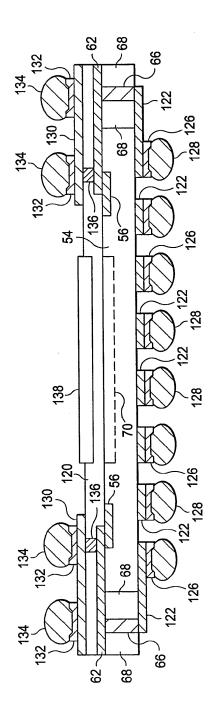

- 도 11에서, 클리어 패시베이션층(120)이 반도체 다이(54)의 액티브 표면상에 도시되었다. THV(66)가 다이 확장 영역(68)을 관통하여 형성된다. RDL(62)이 접촉 패드(56)를 THV(66)에 전기적으로 연결되고, 차례로, 반도체 패키지(124)의 백사이드상의 RDL(122)에 전기적으로 연결된다. UBM(126)이 RDL(122)상에 융착되고 패턴화된다. 전기적 도전 솔더 재료가 증발, 전해 도금, 무전해 도금, 볼 드롭 또는 스크린 프린팅 공정을 통해서 UBM(126)위에 융착된다. 그 솔더 재료는 구형 볼 또는 범프(128)를 형성하도록 도전 재료를 그것의 융점 이상으로 가열하여 리플로우(reflow)된다.

- [0040]

- 빛이 클리어 패시베이션층(120)을 관통하여 광학적 액티브 영역(70)까지 통과하는데, 이것들은 반도체 다이 (54)내의 전자 회로들에 의한 또 다른 처리를 위해 빛 에너지를 전기적 신호들로 변환시킨다. 전기적 신호들은 접촉 패드들(56)을 관통하여 RDL(62)까지, 그리고 THV(66)을 관통하여 RDL(122) 및 UBM(126), 그리고 마지막으로 솔더 범프(128)까지 루팅된다. 상호접속 구조체는 광학적 반도체 패키지(124)의 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

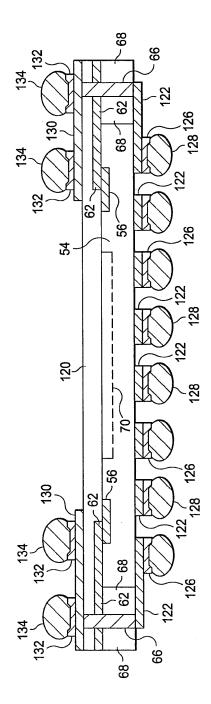

- [0041] 도 12는 도 6-11과 유사하고, 추가적으로 클리어 패시베이션층(120)을 관통하여 RDL(130)까지 확장하는 THV(6 6)를 갖는다. UBM(132)이 RDL(130)상에 형성된다. 솔더 범프(134)가 UBM(132)상에 형성된다.

- [0042] 도 13은 도 6-12와 유사하고, 클리어 패시베이션층(120)을 관통하여 형성되고 RDL(62, 130)를 전기적으로 연결 시키는 THV(136)을 갖는다. 글래스 다이(138)가 클리어 패시베이션층(120)상에 형성된다. 글래스 다이(138)는 센서안으로 통과하는 빛의 왜곡 및 바람직하지 않은 굴절을 바로 잡기 위한 이미지 센서의 최종 표면 한정 소자이다. 일부 경우에, 클리어 패시베이션은 어떤 왜곡을 야기시킬 수 있는 표면 플랫트니스(flatness)에서 제한을 갖는다. 글래스 다이의 추가는 글래스에 의해 한정되는 필요한 플랫트니스를 제공한다. 그 글래스는 굴절에서 일부 교정을 제안한다. 그 글래스는 자외선 필터를 갖는다.

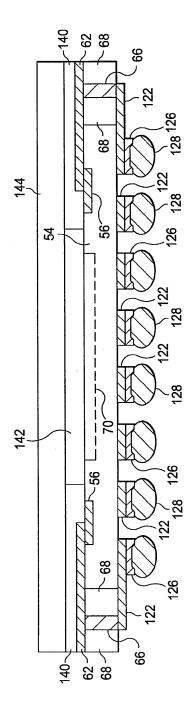

- [0043] 도 14는 도 6-13과 유사하고, 반도체 다이(54)상에 형성된 윈도우(142)를 구비한 클리어 패시베이션층(140)을 갖는다. 윈도우(142)는 패시베이션이 없고, 빛을 통과시킨다. 글래스층(144)이 클리어 패시베이션층(140) 위에 형성된다.

- [0044] 빛이 글래스층(144) 및 윈도우(142)를 관통하여 광학적 액티브 영역(70)까지 통과하는데, 이것들은 반도체 다이 (54)내의 전자 회로들에 의한 또 다른 처리를 위해 빛 에너지를 전기적 신호들로 변환시킨다. 전기적 신호들은 접촉 패드들(56)을 관통하여 RDL(62)까지, THV(66)를 관통하여 RDL(122) 및 UBM(126), 그리고 마지막으로 솔더 범프(128)까지 루팅된다. 상호접속 구조체는 반도체 패키지의 광학적 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

- [0045] 도 15 및 도 16은 다양한 이미지 센서 응용에 사용된 반도체 패키지를 도시하고 있다. 반도체 패키지는 이미지 센서 다이들을 패키징하는 비교적 낮은 비용의 방법을 제공한다. 패키지는 소형화를 지지한다. 그 패키지 구성은 강하고, 높은 신뢰도를 가지며, 습분과 관련한 손상에 저항력이 있다.

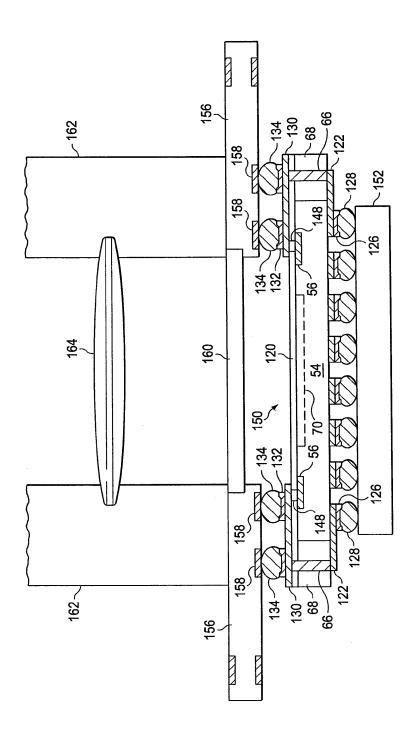

- [0046] 도 15는 도 6-14와 유사하게, 광학적 액티브 영역(70)을 구비한 반도체 다이(54)를 포함한 반도체 패키지(150)의 응용을 도시하고 있다. THV(148)는 접촉 패드(56)와 RDL(130)을 전기적으로 연결시킨다. 반도체 패키지(150)는 볼 그리드 어래이(BGA), 플립 칩 또는 WLSCP로서 솔더 범프(128)를 통해 PCB 또는 칩 캐리어 기판(152)에 장착되고 전기적으로 연결된다. 반도체 패키지(150)는 또한 접촉 패드(158)에 접촉하는 솔더 범프(134)로 기판(156)에 장착되고 전기적으로 연결된다. 보호 글래스(160)가 기판(156)에 의해 지지되고, 클리어 패시베이션층(120) 및 광학적 액티브 영역(70)위에 놓인다. 렌즈 조립체(162)가 렌즈(164)를 지지하는데, 렌즈는 빛을 보호 글래스(160)및 클리어 패시베이션층(120)을 관통하여 광학적 액티브 영역(70)으로 모은다. 빛에너지는 반도체 다이(54)내의 전자 회로들에 의한 또 다른 처리를 위해서 전기 신호로 변환된다. 전기적 신호들은 접촉 패드들 (56)을 관통하여 RDL(130, 122)까지, THV(66)를 관통하여 RDL(132, 122) 및 UBM(126), 그리고 마지막으로 솔더 범프(128, 134)까지 루팅된다. 상호접속 구조체는 반도체 패키지(150)의 광학적 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

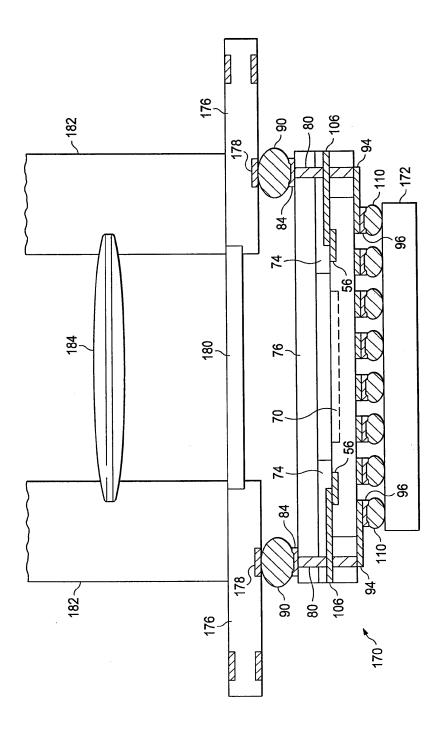

- [0047] 도 16은 도 6-14와 유사하게, 광학적 액티브 영역(70)을 구비한 반도체 다이(54)를 포함한 반도체 패키지(170)의 응용을 도시하고 있다. 반도체 패키지(170)는 볼 그리드 어래이(BGA), 플립 칩 또는 WLSCP로서 솔더 범프 (110)를 통하여 PCB 또는 칩 캐리어 기판(172)에 장착되고 전기적으로 연결된다. 반도체 패키지(170)는 또한 접 촉 패드(178)에 접촉하는 솔더 범프(176)로 기판(176)에 장착되고 전기적으로 연결된다. 보호 글래스(180)가 기판(176)에 의해 지지되고, 글래스층(76) 및 광학적 액티브 영역(70) 위에 놓인다. 렌즈 조립체(182)가 렌즈 (184)를 지지하는데, 렌즈는 빛을 보호 글래스(180) 및 글래스층(76)을 관통하여 광학적 액티브 영역(70)으로 모은다. 빛 에너지는 반도체 다이(54)내의 전자 회로들에 의한 또 다른 처리를 위해서 전기 신호로 변환된다. 전기적 신호들은 접촉 패드들(56)을 관통하여 RDL(106, 94)까지, THV(80)를 관통하여 UBM(84, 96), 그리고 마지막으로 솔더 범프(90, 110)까지 루팅된다. 상호접속 구조체는 반도체 패키지(170)의 광학적 프론트 및 백사이드까지 완전한 신호 루팅을 제공한다.

- [0048] 본 발명의 하나 이상의 실시예들이 상세히 기술되었지만, 다음의 청구범위에 기술된 본 발명의 범위를 이탈하지 않는 한 그 실시예들에 변형과 변화가 가능함을 이해할 것이다.

### 도면의 간단한 설명

[0049] 도 1은 다이 액티브 영역 및 칩 캐리어 기판 사이에 전기적 상호 접속을 제공하는 솔더 범프를 구비한 플립 칩 반도체 소자를 도시하는 도면;

| [0050] | 도 2a-2b는 클리어 패시베이션층 그리고 차례로 이미지 센서 웨이퍼 위에 놓이는 글래스 웨이퍼를 도시하는 도 |

|--------|---------------------------------------------------------------|

|        | 면;                                                            |

- [0051] 도 3a-3c는 반도체 다이 주위에 확장 영역을 형성하는 것을 도시하는 도면;

- [0052] 도 4a-4d는 반도체 다이 주위에 확장 영역의 다른 형성을 도시하는 도면;

- [0053] 도 5a-5d는 RDL에 전기적으로 연결된 다이 확장 영역을 관통하는 하프-비어 및 풀-비어 THV 형성을 도시하는 도 면;

- [0054] 도 6은 다이 확장 영역, 클리어 패시베이션층, 그리고 글래스층을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0055] 도 7은 다이 확장 영역, 클리어 패시베이션층, 그리고 글래스층을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 다른 반도체 패키지를 도시하는 도면;

- [0056] 도 8은 다이 확장 영역, 클리어 패시베이션층, 그리고 글래스 층을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 다른 반도체 패키지를 도시하는 도면;

- [0057] 도 9는 다이 확장 영역을 관통하여 형성되고 RDL 및 솔더 범프에 전기적으로 연결된 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0058] 도 10은 반도체 다이, 클리어 패시베이션층, 그리고 글래스 층을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0059] 도 11은 다이 확장 영역을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0060] 도 12는 다이 확장 영역과 클리어 패시베이션층을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0061] 도 13은 다이 확장 영역과 클리어 패시베이션층을 관통하여 형성되고 RDL에 전기적으로 연결된 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0062] 도 14는 다이 확장 영역을 관통하여 형성되고 RDL에 전기적으로 연결되며, 클리어 패시베이션충들과 글래스충 오버래이 사이에 패시베이션이 없는 영역을 갖는 THV를 구비한 반도체 패키지를 도시하는 도면;

- [0063] 도 15는 오버헤드 렌즈 조립체를 구비한 반도체 패키지를 도시하는 도면; 그리고

- [0064] 도 16은 오버헤드 렌즈 조립체를 구비한 반도체 패키지를 도시하는 도면이다.

- [0065] <도면의 주요 부분에 대한 부호의 간단한 설명>

- [0066] 10 : 반도체 소자 12 : 액티브 영역

- [0067] 14 : 다이 16 : 프린트 회로 보드

- [0068] 24 : 범프 패드 36 : 반도체 다이

- [0069] 30 : 글래스 웨이퍼 32 : 클리어 패시베이션층

- [0070] 40 : 윈도우 50 : 커버레이 테이프

## 도면2a

## 도면2b

## 도면3a

## 도면3b

# 도면3c

## 도면4a

## *도면4b*

# 도면4c

# 도면4d

# 도면5a

# 도면5b

# *도면5c*

## 도면5d

도면15