(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6103825号

(P6103825)

(45) 発行日 平成29年3月29日(2017.3.29)

(24) 登録日 平成29年3月10日(2017.3.10)

(51) Int.Cl.

F 1

G06F 1/24 (2006.01)

G06F 1/24

B

G06F 1/26 (2006.01)

G06F 1/26

334 B

H03K 17/22 (2006.01)

H03K 17/22

B

請求項の数 12 (全 16 頁)

(21) 出願番号

特願2012-129885 (P2012-129885)

(22) 出願日

平成24年6月7日(2012.6.7)

(65) 公開番号

特開2013-254376 (P2013-254376A)

(43) 公開日

平成25年12月19日(2013.12.19)

審査請求日

平成27年5月25日(2015.5.25)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 佐々木 充

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 白石 圭吾

最終頁に続く

(54) 【発明の名称】半導体集積回路、情報処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

供給される電源が制御される電源制御対象部と、

前記電源制御対象部に供給する電源を制御する電源制御手段と、

前記電源制御手段によって前記電源制御対象部へ供給される電源の電圧を計測し、計測された前記電圧が前記電源制御対象部を動作させるための規定電圧まで達したかを検出する検出手段と、

計測された前記電圧が前記規定電圧まで達したことが検出された場合、前記電源制御対象部を初期化するためのクロック供給が開始されるように制御する初期化手段とを有することを特徴とする半導体集積回路。

10

## 【請求項 2】

前記初期化手段は、初期化する期間を示す値を保持する保持手段と、前記クロック供給の開始から当該保持手段の示す期間、前記電源制御対象部に対してリセット信号を発行し続けるリセット手段とを備えることを特徴とする請求項1に記載の半導体集積回路。

## 【請求項 3】

前記電源制御手段を操作する指示を前記電源制御手段へ出力する指示手段を更に備え、前記検出手段は、前記指示手段の出力する指示に応じて前記電源制御対象部へ供給される電源の電圧の測定を開始することを特徴とする請求項1又は2に記載の半導体集積回路。

## 【請求項 4】

前記初期化手段は、前記クロック供給が開始されるようにイネーブル信号を発行する発

20

行手段と、当該イネーブル信号に基づいて前記電源制御対象部へ伝達するクロックのゲーティングを解除するゲーティング手段とを備えることを特徴とする請求項1乃至3のいずれか1項に記載の半導体集積回路。

【請求項5】

前記ゲーティング手段は、ゲーティングクロックバッファであることを特徴とする請求項4に記載の半導体集積回路。

【請求項6】

前記検出手段は、前記電源制御対象部へ供給される電源の電圧を計測する計測手段と、予め設定された期間をカウントする計時手段と、前記計測手段と前記計時手段のどちらかの出力を選択する選択手段と、をさらに備えることを特徴とする請求項1乃至5のいずれか1項に記載の半導体集積回路。 10

【請求項7】

前記検出手段によって、計測された前記電圧が前記規定電圧まで達したことが検出された場合、前記電源制御対象部に供給するクロックを分周する分周手段を更に有することを特徴とする請求項1乃至6のいずれか1項に記載の半導体集積回路。

【請求項8】

供給される電源が制御される電源制御対象部と、

前記電源制御対象部に供給する電源を制御する電源制御手段と、

前記電源制御手段によって前記電源制御対象部へ供給される電源の電圧が、前記電源制御対象部を動作させるための規定電圧まで達したことを検出する検出手段と、 20

前記検出手段の検出に基づいて前記電源制御対象部を初期化するためのクロック供給が開始されるように制御する初期化手段と、を有し、

前記初期化手段は、前記電源制御対象部に対するクロック供給を開始するためのイネーブル信号と、前記電源制御対象部に対するリセット信号とを遅延させる遅延手段とを備えることを特徴とする半導体集積回路。

【請求項9】

供給される電源が制御される電源制御対象部と、

前記電源制御対象部に供給する電源を制御する電源制御手段と、

前記電源制御手段によって前記電源制御対象部へ供給される電源の電圧が、前記電源制御対象部を動作させるための規定電圧まで達したことを検出する検出手段と、 30

前記検出手段の検出に基づいて前記電源制御対象部を初期化するためのクロック供給が開始されるように制御する初期化手段と、を有し、

前記初期化手段は、前記電源制御対象部に対するクロック供給を開始するためのイネーブル信号と、前記電源制御対象部に対するリセット信号とを同期させる同期手段とを備えることを特徴とする半導体集積回路。

【請求項10】

前記電源制御手段は、スイッチを備えることを特徴とする請求項1乃至9のいずれか1項に記載の半導体集積回路。

【請求項11】

前記電源制御対象部はリセット信号をカスケード分配する複数段のレジスタを備え、前記初期化手段は前記レジスタの段数に対応する回数の立ち上がりエッジを有するクロックを前記電源制御対象部に供給するように制御することを特徴とする請求項1乃至10のいずれか1項に記載の半導体集積回路。 40

【請求項12】

供給される電源が制御される電源制御対象部と、

前記電源制御対象部に供給する電源を制御する電源制御手段と、

前記電源制御手段によって前記電源制御対象部へ供給される電源の電圧を計測し、計測された前記電圧が前記電源制御対象部を動作させるための規定電圧まで達したかを検出する検出手段と、

計測された前記電圧が前記規定電圧まで達したことが検出された場合、前記電源制御対 50

象部を初期化するためのクロック供給が開始されるように制御する初期化手段とを有することを特徴とする情報処理装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路内の電源制御対象部（パワードメイン）を電源遮断状態から復帰させる技術に関するものである。

【背景技術】

【0002】

近年、環境問題に配慮した省エネルギー化の流れから、半導体集積回路に対し低電力化が求められている。例えば、消費電力を削減するために、半導体集積回路の一部のサブシステム（電源制御対象部）の機能を使つていなければ、そのサブシステムへ供給する電源を一時的に遮断する方法がある。10

【0003】

ここで、電源を遮断したサブシステムを復帰させる際には電力を供給した後に初期化が必要であり、通常動作に入る前に初期化を行う。特許文献1では電源が遮断され且つリセット信号（RS）をアクティブにした状態から、電源を復帰させるために、電源供給とクロック供給とを同時に開始（再開）する。ここで、予め動作クロック周波数に応じたりセット時間（リセット時間）をカウンタに設定しておき、電源供給とクロック供給とを開始してから設定されたリセット時間を計時してからリセット信号を解除して、通常の動作状態に復旧している20。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002-312073号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

初期化動作中はサブシステム内部のフリップフロップなどの記憶素子に対して信号変化を起こさせることにより状態を初期化するため、初期化動作中はサブシステム全体へクロックを供給した状態で回路を動作させる必要がある。従って、初期化動作中（特許文献1の復旧期間）の間の消費電力は通常動作時に比べても大きくなることが多い。ここで、初期化動作中はサブシステムへの電源電圧が安定した状態でクロックを供給することが重要であるが、特許文献1のように電圧が不安定な状態からクロックを供給してしまうと、消費電力が大きくなってしまう。30

【0006】

また、電源供給を開始してから電源電圧が安定するまでに要する時間は、電源供給を開始しようとする電源制御対象箇所の規模（大きさ、形状、位置、個数、ゲート数、プロセス種別）や、他の電源制御対象の状態等の要因によって変わる。しかし、特許文献1の手法では、サブシステムへのクロック供給を開始する前に動作クロック周波数に基づいてリセット時間を設定する手法であるので、前述の種々の要因を考慮するとリセット時間を大きめに設定する必要があり消費電力を削減し難い。40

【課題を解決するための手段】

【0007】

上記課題を鑑みて本発明は、供給される電源が制御される電源制御対象部と、前記電源制御対象部に供給する電源を制御する電源制御手段と、前記電源制御手段によって前記電源制御対象部へ供給される電源の電圧を計測し、計測された前記電圧が前記電源制御対象部を動作させるための規定電圧まで達したかを検出する検出手段と、計測された前記電圧が前記規定電圧まで達したことが検出された場合、前記電源制御対象部を初期化するためのクロック供給が開始されるように制御する初期化手段とを有することを特徴とする。50

**【発明の効果】****【0008】**

本発明によれば、電源制御対象部の電圧の状態を検出して、検出結果に応じてクロック供給を開始するので、効率的にクロックを供給し、初期化動作中の消費電力の削減が可能になる。

**【図面の簡単な説明】****【0009】**

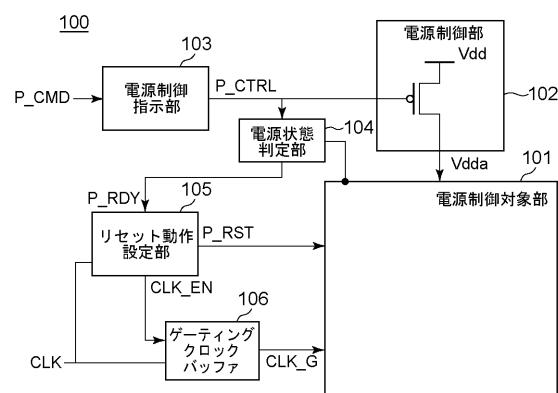

【図1】リセット回路を含む半導体集積回路内部の概略構成を示すブロック図である。

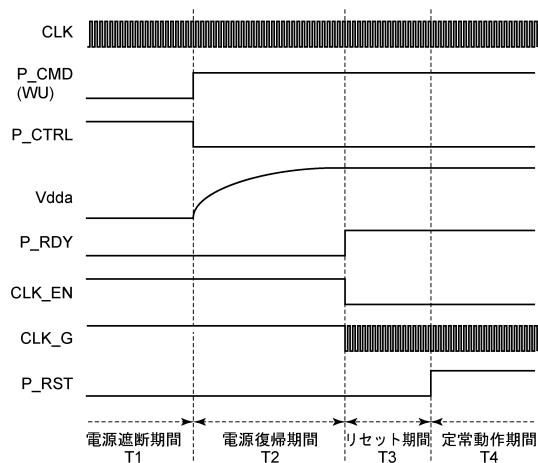

【図2】リセット回路を含む半導体集積回路のタイミングチャートである。

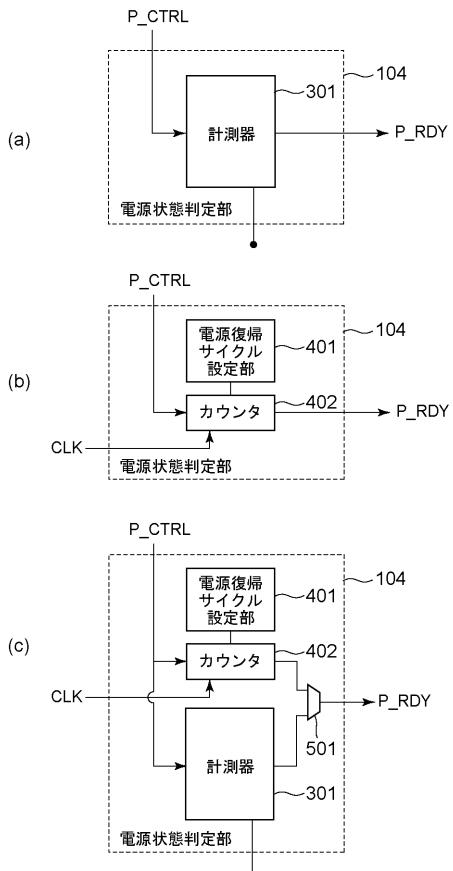

【図3】(a) 電源状態計測による電源状態判定部の構成を示すブロック図であり、(b) 電源状態予測による電源状態判定部の構成を示すブロック図であり、(c) 電源状態予測と電源状態計測を選択的に使用する電源状態判定部の構成を示すブロック図である。 10

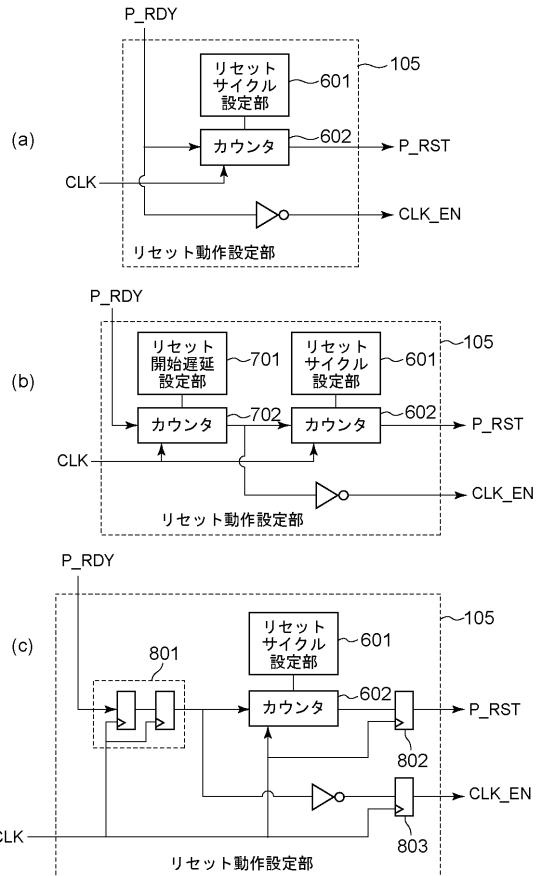

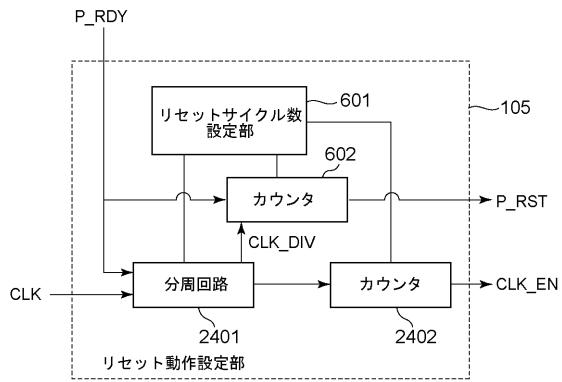

【図4】(a) リセット動作設定部の概略構成を示すブロック図であり、(b) リセット開始時間の遅延機構を付与したリセット動作設定部の構成を示すブロック図であり、(c) 信号の制御対象への同期化機構を付与したリセット動作設定部の構成を示すブロック図である。

【図5】複数の電源制御対象部のリセット回路の構成を示すブロック図である。

【図6】複数の電源制御対象部のリセット回路のフロアプランを示す概略図である。

【図7】(a) 複数の電源制御対象部のクロックイネーブル信号を同期化する構成を示すブロック図であり、(b) 複数の電源制御対象部のリセット信号を同期化する構成を示すブロック図である。 20

【図8】外部からのクロックイネーブル信号の入力があるリセット回路の構成を示すブロック図である。

【図9】外部からクロックイネーブル信号の入力があるリセット動作設定部の構成を示すブロック図である。

【図10】(a) 内部リセットより先に外部クロックイネーブルを有効にした場合のタイミングチャートであり、(b)、内部リセットより後で外部クロックイネーブルを有効にした場合のタイミングチャートである。

【図11】(a) 外部からリセット信号の入力があるリセット回路の構成を示すブロック図であり、(b) 外部からのリセット信号の入力があるリセット動作設定部の構成を示すブロック図である。 30

【図12】(a) 内部リセットより先に外部リセットが解除されるタイミングチャートであり、(b) 内部リセットより後で外部リセットが解除されるタイミングチャートである。

【図13】電源制御対象部のリセット信号をカスケード分配する構成を示すブロック図である。

【図14】外部からのリセット信号が入力されている状態であっても電源制御対象部のリセット信号のカスケード分配を含む初期化動作に要する最小限のクロックを発生させた場合のタイミングチャートである。

【図15】(a) 分周回路を含むリセット動作設定部の構成を示すブロック図であり、(b) リセット中のクロックを分周するタイミングチャートである。 40

**【発明を実施するための形態】****【0010】**

## &lt;実施形態1&gt;

まず、初期化動作中の消費電力を低減させる本発明の実施形態1の概略について説明する。

**【0011】**

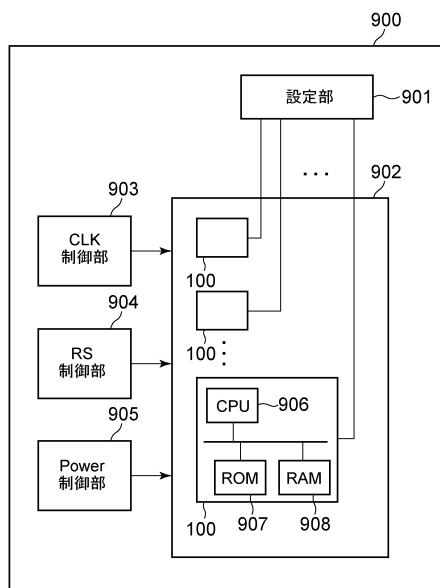

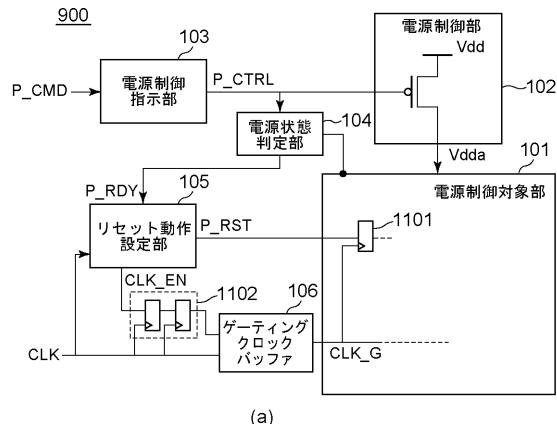

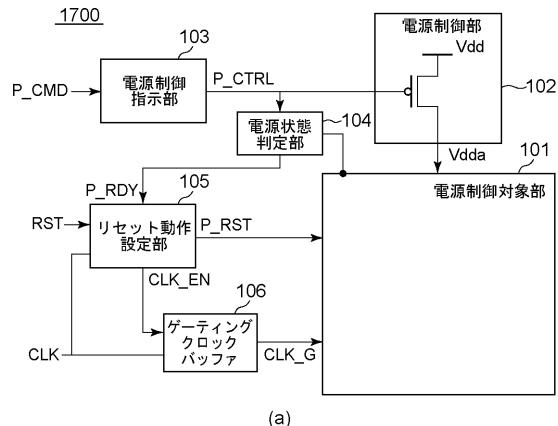

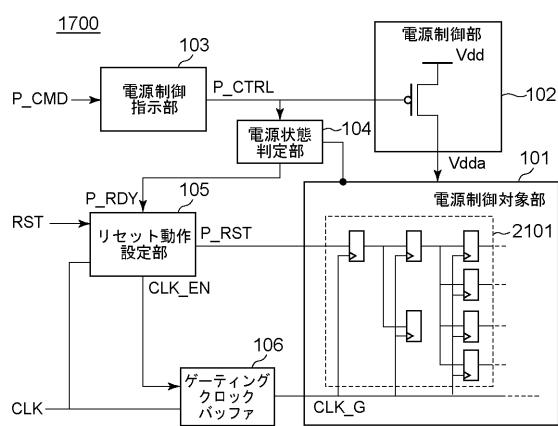

図1は、本発明の実施形態1に係る半導体集積回路100の電源制御対象部101とそのリセット構成の概略を示すブロック図である。電源制御対象部101は電源ドメインや電圧ドメインと呼称されることが多い。ここで、電源ドメインとは同一（複数組みであつ 50

てもよい)の電力制御素子(例えば、PMOSスイッチ、FET)によって電源の供給を止められる集積回路上の一領域を示し、チップ上の漏れ電流(リーク電流)を抑制するためのものである。なお、電源ドメインとはこの定義を満たす回路ブロックや、機能モジュール、集積回路、サブシステムなどであってもよい。また、1つの電源ドメインに複数の機能モジュールやサブシステムを包含させてもよい。

#### 【0012】

図1において、電源制御対象部101へ入力される電源電圧となる電源Vddaは、電源スイッチなどの電源制御部102を介して電源Vddに接続されている。アプリケーションプログラムやユーザによる外部電源スイッチの操作に応じて発行される電源制御指示(P\_CMDと表記する)に基づいて、電源制御部102を操作するための操作指示(P\_CTRLと表記する)を電源制御指示部103が発行する。10

#### 【0013】

電源状態判定部104は、電源制御対象部101の電源Vddaの状態を検出し、電源対象部101が安定して動作可能な電源電圧で有れば、そのことを示すパワーレディ信号(P\_RDYと表記する)をリセット動作設定部105に送信する。リセット動作設定部105は、アクティブなパワーレディ信号を受信したことに応じて、ゲーティングクロックバッファ106に対してゲーティングを解除するクロックバイナブル信号(CLK\_ENと表記する)を送信する。なお、リセット動作設定部105はクロックバイナブル信号を送信するとともに、電源制御対象部101に対して設定された期間だけリセット信号(P\_RSTと表記する)を送信して初期化動作を実施する。20

#### 【0014】

なお、本明細書では初期化動作とは、電源制御対象部101を初期化するために、安定した電源電圧が供給されている電源制御対象部101に対して、クロック(CLK\_Gと表記する)とアクティブなリセット信号(P\_RST)とを供給し続ける動作を示すものとする。

#### 【0015】

なお、図1の電源制御部102は、PMOSからなる電源スイッチを用いた構成であるが、NMOSとPMOSを含む相補スイッチ等、電源電圧を制御するものであれば本発明に適用することができる。また、図1のゲーティングクロックバッファ106はOR型論理によりクロック伝搬をネガートする構成であるが、AND型論理であってもよい。以降の説明では簡便のためPMOSとOR型論理を用いて説明する。30

#### 【0016】

なお、図1に記載の電源制御部102から電源制御対象部101に向けて記した矢印は電源Vddaの供給経路を示している。また、図1に記載の電源状態判定部104から電源制御対象部101に向けて線と丸端子で記した箇所は、電源状態判定部104が電源状態を検知する計測器により構成されている場合のセンシングの端子を示している。電源状態判定部104、リセット動作設定部105の詳細については後述する。

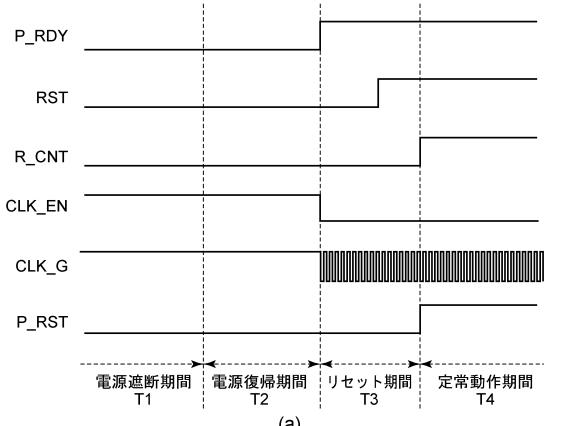

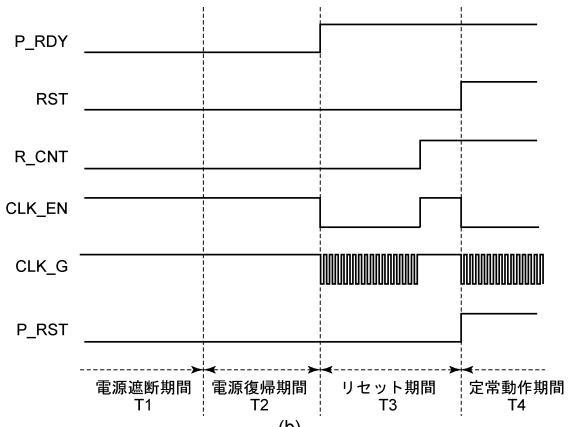

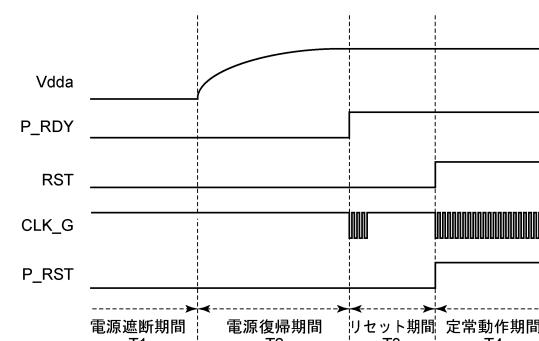

#### 【0017】

図2は、実施形態1に係る半導体集積回路100のリセット構成に関する各種信号について電源を復帰させる際のタイミングチャートを示している。詳細には、電源制御対象部101への電源供給が停止している電源遮断期間T1、電源供給を行う電源復帰期間T2、電源が安定したことを検出した後に初期化動作を実施するリセット期間T3、さらに正常動作期間T4を順に移行する様子を示している。40

#### 【0018】

CLKは半導体集積回路100に供給されるシステムクロックである。このCLKは半導体集積回路100内のクロックジェネレータが発生させたものであってもよい。

#### 【0019】

P\_CMD、P\_CTRL、Vdda、P\_RDY、CLK\_EN、CLK\_G、P\_RSTについては図1に示す信号と対応しており、図2のチャートでデジタル信号はロー・アクティブ(負極性)として示しているが、論理回路との対応がとれていれば正極性で50

あっても本発明を適用できる。

**【0020】**

本実施形態では電源制御指示 (P\_CMD) が有効になって、電源復帰期間 T\_2 に遷移しても、電源電圧 V\_dda が安定したことと示す通知として P\_RDY が有効になるまでリセット動作設定部 105 はクロック制御信号 (CLK\_EN) を有効にはしない。本実施形態のリセット動作設定部は、電源状態判定部 104 がパワーレディ信号 (P\_RDY) を有効へ遷移させたことをトリガにして CLK\_EN を有効にして、予め設定された期間 (サイクル数) だけ初期化動作を行う。

**【0021】**

以降は、実施形態 1 の各種構成について詳細を説明する。

10

**【0022】**

<電源状態判定部>

図 3 (a) ~ (c) の其々は、実施形態 1 の電源状態判定部 104 の詳細を示している。

**【0023】**

図 3 (a) は、電源制御対象部 101 の電圧状態を直接検知する構成である。すなわち、操作指示 (P\_CTRL) の入力に応じて電源電圧を計測する計測器 301 によって、電源制御対象部 101 が安定して動作する規定電圧に V\_dda が達したことを検出することで、電源制御対象部 101 の電源復帰タイミングの正確な検知が可能となる。図 3 に記載の電源状態判定部 104 から外部に向けて線と丸端子で記した箇所は、電源制御対象部 101 の電源 V\_dda の状態をセンシングする端子を示している。なお、計測器 301 は電流や電圧比較など、電圧と対応して変化する他の物理量を測定することで電源 V\_dda が安定したことを検出してもよし、CMOS ランジスタの信号の変化点を利用して電源電圧を検知してもよい。さらに、操作指示を計測開始のトリガとしなくてもよい、不図示の CPU 等からの指示によって計測を開始してもよい。

20

**【0024】**

図 3 (b) は、電源供給開始から規定電圧に復帰するまでの期間が予め分っており、この期間を計数することで、安定動作可能な電圧状態であることを検知する構成である。不図示の CPU 等から電源復帰にかかる期間に相当する値 (サイクル数など) を受けてカウンタ 402 に設定する電源復帰サイクル設定部 401 と、操作指示 (P\_CTRL) の入力に応じて、設定された電源復帰期間を計数するカウンタ 402 を備える電源状態判定部 104 の構成を示す。なお、電源復帰サイクル設定部 401 は、CPU 等によるレジスタ設定以外にも、予め固定値を保持する構成であっても、設定をメモリ等から読み出す構成でもよい。

30

**【0025】**

図 3 (c) は、図 3 (a) の構成と図 3 (b) の構成とを選択的に動作できるようにした電源状態判定部 104 である。不図示のレジスタや外部からの入力に応じて、2つの構成を切り替えるセレクタ 501 をさらに備える。例えば、通常は計測器 301 によって V\_dda の状態を計測し、V\_dda のふらつきが許容できない場合などにはカウンタ 402 を用いた構成を切り替えるように用いることができる。

40

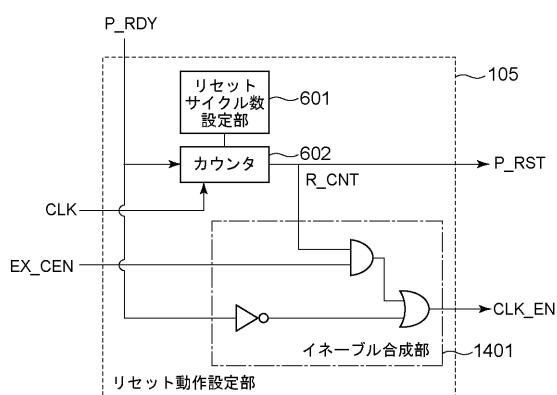

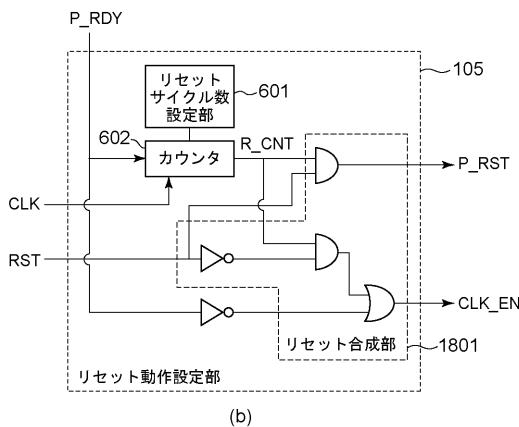

**【0026】**

<リセット動作設定部>

図 4 (a) ~ (c) の其々は、実施形態 1 のリセット動作設定部 105 の詳細を示している。図 4 (a) は、リセットに必要なサイクル数を設定するリセットサイクル設定部 601 と、電源状態判定部 104 から送信されるパワーレディ信号 (P\_RDY) をトリガに動作を開始するカウンタ 602 を備える、リセット動作設定部 105 を示す。リセット動作設定部 105 はカウンタ 602 でカウント (計時) を開始するとともにクロックイネーブル信号 (CLK\_EN) の出力を開始し、カウントが終了するとともにリセット信号 (P\_RST) の送信を終了する。なお、リセットサイクル設定部 601 は予め固定値を保持していてもよいし、不図示の CPU 等によるレジスタ設定でカウント値を保持しても

50

よいし、メモリ等からカウント値を読み出す構成であってもよい。

#### 【0027】

図4(b)は、図4(a)の構成に、クロックイネーブル信号やリセット信号を遅延させるカウンタ702を追加したリセット動作設定部105を示している。この構成ではパワーレディ信号の入力を受けて、予めリセット開始遅延設定部701により設定した期間(値、サイクル数)だけカウンタ702によりカウントさせ、カウンタ702のカウント中はパワーレディ信号の伝播を待機させる。カウンタ702が設定された期間カウントし終えると、クロックイネーブル信号(CLK\_EN)の出力を開始し、パワーレディ信号をカウンタ602に伝播させる。その後段の構成や機能は図4(a)の構成や機能と同様なので、説明を省略する。

10

#### 【0028】

図4(c)は、リセット動作設定部105を電源制御対象部101と、より同期して動作させるために信号同期化回路801を追加している。例えば、電源状態判定部104が、図3(a)、図3(c)のように電源Vddの状態を測定する場合、パワーレディ信号は必ずしもリセット回路100に同期して入力されるとは限らない。他にも、電源状態判定部104とリセット動作設定部105とを、半導体集積回路100のレイアウトを決定する段階で同期設計することが困難であることも考えられる。なお、リセット動作設定部105からの出力信号(リセット信号、クロックイネーブル信号)に関しても同様に同期信号出力回路802、803としてフリップフロップを配置している。

20

#### 【0029】

なお、図3(a)～(c)の電源状態判定部104のいずれかと図4(a)～(c)のリセット動作設定部105のいずれかを組み合わせれば、実施形態1の効果を得ることはできる。

#### 【0030】

以上のとおり、本実施形態では図2のタイミングチャートに示す通り、電源電圧が安定してから初期化動作を開始するため、特許文献1の技術と比べて効率的に初期化動作を実施するとともに消費電力を低減させることができる。

#### 【0031】

##### <実施形態2>

本実施形態では、実施形態1の電源制御構成を、半導体集積回路100(以下、サブモジュールとして説明する)をN個(Nは2以上の整数)備える半導体集積回路900に拡張した構成について説明する。なお、本実施形態の説明に用いる図面について、実施形態1の構成と変わらない構成については同じ符号を付すと共に、機能も変わらない場合にはその説明を省略する。

30

#### 【0032】

図5は、実施形態1で半導体集積回路100として説明したサブモジュール100をN個備える半導体集積回路900の概略構成を示す。CLK制御部903は、各サブモジュールに供給するクロックを個別に制御する。RS制御部904は各サブモジュールに供給するリセット信号を個別に制御する。Power制御部905は各サブモジュールに対して電源制御指示を個別に出力する。なお、本実施形態では、Power制御部905で集中制御された各サブモジュールの電源制御指示(P\_CMD)を各サブモジュールの電源制御指示部103に送信する形態を取っているが、Power制御部905と各サブモジュールの電源制御指示部103の機能を併せた一つのブロックとして実装する構成でもよい。この場合、Power制御部905と各サブモジュールの電源制御指示部103を併せたブロックから直接、操作指示(P\_CTRL)が電源制御部102と電源状態判定部104に送信する構成となる。

40

#### 【0033】

図5に示す構成ではサブモジュールのすくなくとも1つがCPU906、ROM907、RAM908を備えているが、各サブモジュールでCPU906、ROM907、RAM908などを分担して備えていてもよい。設定部901は各サブモジュールの備える各

50

種カウンタや電源復帰サイクル設定部 401 に電源復帰などに関わるパラメータを設定する。

#### 【0034】

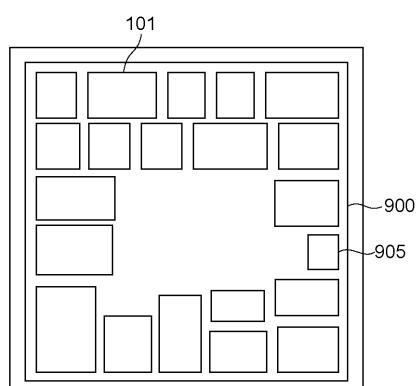

図 6 は、図 5 に示した半導体集積回路 900 について、20 個の電源制御対象部 101 と電源制御指示部 905 を配置するフロアプランの概略を示している。図 6 に図示するように、電源制御対象部 101 によっては大きさや配置が異なっている。この図ではリセット動作設定部 105 や電源状態判定部 104、ゲーティングクロックバッファ 106 については省略している。本実施形態では電源制御対象部 101 への電源供給を制御する際に、電源制御対象部 101 を複数のパワースイッチによって囲んでいるので、電源制御対象部 101 を囲む枠に沿って電源制御部 102 が配置される。また、本実施形態では基本的に電源制御領域は集積回路上で領域が重ならないように構成される。

10

#### 【0035】

ここで、図 6 の構成について、電源制御指示部 103 や電源状態判定部 104 やリセット動作設定部 105 を電源制御対象部 101 やゲーティングクロックバッファ 106 と同期させることができることが困難になることが予想される。そのような場合に備えて、図 7 (a) や図 7 (b) に示すように電源制御対象部 101 やゲーティングクロックバッファ 106 に同期化の機構を設けてもよい。図 7 (a) に示す構成では、ゲーティングクロックバッファ 106 の前段に信号同期化回路 1102 を設け、クロックイネーブル信号 (CLK\_EN) 1 とリセット動作設定部 105 との同期性を高めることができる。なお、ここで中継レジスタ 1101 は電源制御対象部 101 内部にリセット信号 (P\_RST1) を分配する。

20 図 7 (b) に示す構成では、電源制御対象部 101 の内部にリセット信号を分配する中継レジスタ 1101 を設け、その前段に信号同期化回路 1201 を設けている。

#### 【0036】

以上のとおり、本実施形態では複数の電源制御構成を好ましく制御することができる。

#### 【0037】

##### < 実施形態 3 >

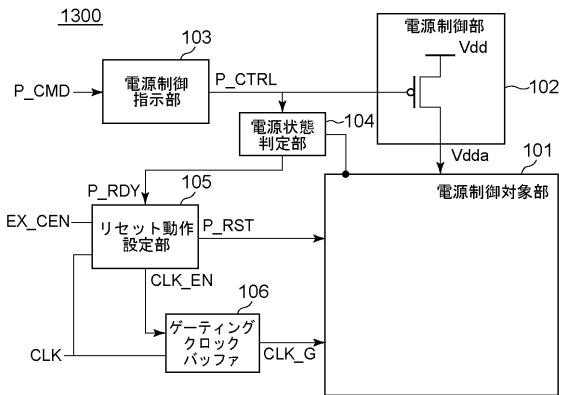

本実施形態では、実施形態 1、2 の構成について電源ドメイン制御とクロックドメイン制御（クロック遮断による省電力制御）を両立できるように拡張した構成について説明する。クロックドメイン制御は、クロックを遮断しダイナミック電流を削減する省電力方法である。なお、本実施形態の説明に用いる図面について、実施形態 1、2 の構成と変わらない構成については同じ符号を付すと共に、機能も変わらない場合にはその説明を省略する。

30

#### 【0038】

図 8 は、実施形態 1、実施形態 2 のリセット動作設定部 105 にクロックドメイン制御用の第 2 クロックイネーブル信号 (EX\_CEN と表記する) を入力し、クロックドメイン制御ができるようにしたものである。なお、本実施形態の説明では CLK\_EN を第 1 クロックイネーブル信号と呼称する。ここで、第 2 クロックイネーブル信号は、動作状態にある電源制御対象部 101 へのクロック供給の遮断の有無を切り替えるためのものであるが、初期化動作の期間は電源遮断対象 101 へのクロック供給に影響しないように構成する必要がある。

40

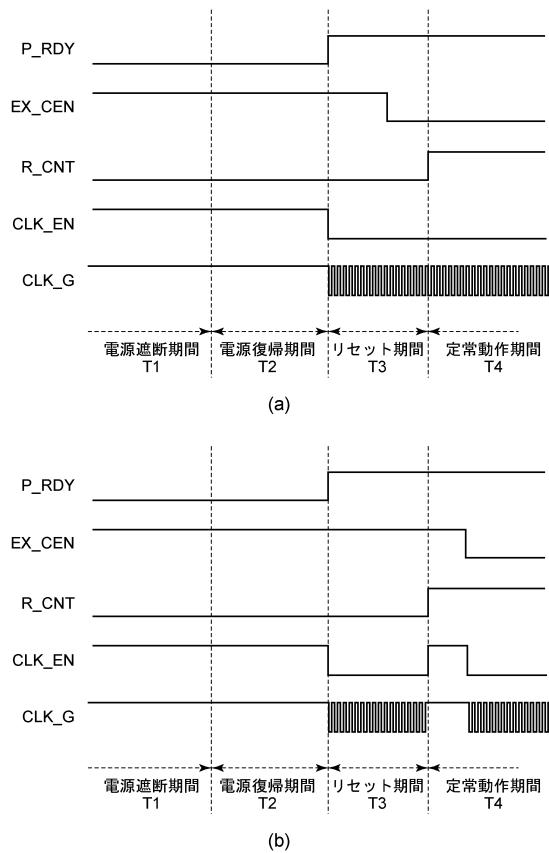

#### 【0039】

図 9 は、本実施形態のリセット動作設定部 105 の構成を示したブロック図である。図 9 の構成では初期化動作のためのクロック供給制御に影響を与えないように第 2 クロックイネーブル信号を合成し、第 1 クロックイネーブル信号を出力するイネーブル合成部 1401 を追加している。なお、カウンタ 602 はイネーブル合成部 1401 に対して内部信号 (R\_CNT) を供給する。この構成によって、電源ドメインについて動作状態となっている電源制御対象部 101 へのクロックを遮断することによる省電力制御を効率的に実施しつつ、初期化動作のためクロック供給を遮断しないようにすることができます。

#### 【0040】

図 10 (a)、図 10 (b) は、図 9 に示したリセット動作設定部 105 に関する各種

信号のタイミングチャート（EX\_CEN、CLK\_ENは負極性）を示す。

#### 【0041】

図10(a)は、電源復帰後のリセット期間T3の間に、リセット動作設定部105に入力される第2クロックイネーブル信号(EX\_CEN)が有効にされた場合を示している。図10(a)に示すように、図9の構成では電源復帰に伴う初期化動作のための第1クロックイネーブル信号(CLK\_EN)を設定された期間だけ電源制御対象部101へクロック供給するようにしている。従って、リセット期間T3終了後に電源制御対象部101は直ちに通常動作が可能である。

#### 【0042】

図10(b)は、電源復帰後のリセット期間T3が終了した後で第2クロックイネーブル信号(EX\_CEN)が有効にされた場合を示している。すなわち、図10(b)に示すように、リセット期間T3終了後であれば、第2クロックイネーブル信号によって直ぐに電源制御対象部101へのクロックを停止し省電力が可能である。

10

#### 【0043】

以上のとおり、本実施形態では電源制御対象部101への初期化動作に影響を与えない様にクロックドメイン制御をして消費電力を低減させる制御をすることができる。すなわち、本実施形態によれば電源ドメイン制御とクロックドメイン制御とを効率的に両立させることができる。

#### 【0044】

##### <実施形態3の変形例1>

20

本実施形態では、実施形態1～3の構成について電源ドメイン制御と電源ドメイン制御に関わらないリセット制御とを両立させるように拡張した構成について説明する。なお、本実施形態の説明に用いる図面について、実施形態1、2の構成と変わらない構成については同じ符号を付すと共に、機能も変わらない場合にはその説明を省略する。

#### 【0045】

図11(a)は、リセット動作設定部105に外部からリセット信号が入力される構成を示している。図11(a)において、リセット動作設定部105は、電源状態判定部104からのパワーレディ信号以外に、外部からのリセット信号である外部リセット信号(RST)に基づいてリセットの動作を行う。ここで、外部リセット信号は、電源制御対象部101へのリセットを制御するためのものであるが、電源を復帰させた際の初期化動作のための電源遮断対象101へのリセット信号の供給には影響しないように構成する必要がある。

30

#### 【0046】

図11(b)は、本実施形態のリセット動作設定部105の構成を示したブロック図である。図11(b)に示す構成では、図4(a)のリセット動作設定部105に初期化動作のためのリセット信号の供給制御に影響を与えないように外部リセット信号を合成し、第1クロックイネーブル信号を出力するリセット合成部1801を追加している。

#### 【0047】

図12(a), 図12(b)は、図11(b)に示したリセット動作設定部105に関する各種信号のタイミングチャート(RST、CLK\_EN、P\_RSTは負極性)を示す。図12(a), 図12(b)は図10(a), 図10(b)の第2クロックイネーブル信号(EX\_CEN)を反転させ外部リセット信号(RST)とした様なタイミングチャートとなっているので、詳細な説明は省略する。

40

#### 【0048】

以上のとおり、本実施形態では電源ドメイン制御と電源ドメイン制御に関わらないリセット制御とを効率的に両立させることができる。

#### 【0049】

##### <実施形態3の変形例2>

本実施形態では、実施形態3の変形例1の電源制御対象部101にリセット伝播機構を設けるように拡張した構成について説明する。なお、本実施形態の説明に用いる図面につ

50

いて、実施形態 1、2、3 の構成と変わらない構成については同じ符号を付すと共に、機能も変わらない場合にはその説明を省略する。

#### 【0050】

図13に示す電源制御対象部101は、リセット信号を伝播させるために、カスケード状に階層的に分配されている複数のレジスタを有する。図13に示す構成では、電源制御対象部101の内部でリセット信号を多数のレジスタに分配させる際に、分配されたリセット信号を安定させるために、リセット信号の伝達経路に伝搬回路2101を配置している。図13の電源制御対象部101は、3段のレジスタによるカスケード分配の後、リセット対象のレジスタ類に接続されている。この構成によると、リセット開始後、4サイクル目でリセット対象のレジスタのリセットが完了する。すなわち、リセット対象のレジスタを含めてk段(複数段)のカスケード分配のレジスタ(図示しているものはk-1段)を備える電源制御対象部101について、初期化動作中にレジスタの段数に対応する回数(k回)の立ち上がりエッジを有するクロック信号CLK\_Gを電源制御対象部101へ送信することで初期化動作を実現することができる。10

#### 【0051】

図14は、図13に示す構成において電源を復旧させる際の各種信号のタイミングチャートを示す。

#### 【0052】

図14は、4つの立ち上がりエッジを持つクロック信号CLK\_Gをリセット期間T3の最初に送信している。このような動作はリセット動作設定部105内部のリセットサイクル数設定部601に設定することで実現できる。20

#### 【0053】

なお、図11に示す外部からのリセット信号を用いた構成を説明したが、図8に示す外部からのクロックイネーブル信号を用いた構成でも同様に本実施形態を実現できる。

#### 【0054】

以上のとおり、本実施形態では電源制御対象部101にカスケード分配を備える際にカスケード分配に対応して効率的に初期化動作のためのクロックを供給するため、初期化動作中の消費電力をさらに低減することができる。

#### 【0055】

##### <実施形態4>

本実施形態では、実施形態1~3の構成について初期化動作中に電源制御対象部101に供給するクロックを分周する構成を設けるように拡張した構成について説明する。30

#### 【0056】

図15(a)は、クロック周波数を落として動作率を下げるリセット動作設定部105の構成を示している。図15(a)の構成では、リセット動作設定部105の分周回路2401がクロック信号CLKを低い周波数に変換する。次に、分周回路2401は変換したクロック信号CLKとエッジの揃ったクロック信号CLK\_DIVを、カウンタ602とカウンタ2402とへ個別に送信する。カウンタ2402は電源制御対象部101に入力されるクロック信号CLK\_Gの立ち上がりエッジをクロックゲーティングで間引いて間欠クロックを発生させるための信号CLK\_ENを作る。40

#### 【0057】

図15(a)は、図15(b)のリセット動作設定部105を用いて電源制御対象部101の電源を復旧させる際の各種信号のタイミングチャートを示している。カウンタ2402による間引き動作により分周されたクロック信号CLK\_Gによって初期化動作(リセット期間T3)をした後で定常動作期間T4へと移行している。

#### 【0058】

以上のとおり、本実施形態では初期化動作中に電源制御対象部101へ供給するクロックを分周することで、初期化動作中の消費電力をさらに低減させることができる。

#### 【0059】

上述の各実施形態では説明の簡便のため、実施形態毎の図面を用意して説明したが、複

数の実施形態を組み合わせても本発明を実施できる。その場合、各実施形態の効果に対応する複数の課題を解決していることに相当する。また、上述の各実施形態では半導体集積回路を用いて説明したが、本発明はクロックゲーティングが可能なハードワイヤードロジックを備える情報処理装置に適用することもできる。

### 【0060】

上述の実施形態では、複数の電源ドメインを並列に備える場合についてだけ例示しているが、電源ドメイン1つの内部にさらに図5のような構成を設けて複数の電源ドメインを階層構造にしてもよい。電源ドメインの数が増加すると、一括して管理することが困難なことがある、そのような場合、上流の階層では大雑把な機能グループについて設定されている電源ドメインを制御させ、下流の階層では詳細な機能について電源ドメインを制御させ、分散的に電源ドメインの制御をすることができる。

10

### 【符号の説明】

#### 【0061】

- 100 リセット回路

- 101 電源制御対象部

- 102 電源制御部

- 103 電源制御指示部

- 104 電源状態判定部

- 105 リセット動作設定部

- 106 ゲーティングクロックバッファ

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

(a)

【図12】

(a)

(b)

(b)

【図13】

【図14】

【図 1 5】

(a)

(b)

---

フロントページの続き

(56)参考文献 特開2009-064456(JP,A)

特開2006-048570(JP,A)

特開2002-312073(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 2 4

G 06 F 1 / 2 6

H 03 K 1 7 / 2 2