(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第3669919号 (P3669919)

(45) 発行日 平成17年7月13日(2005.7.13)

(24) 登録日 平成17年4月22日 (2005.4.22)

| (51) Int.C1. <sup>7</sup> | FΙ       |            |

|---------------------------|----------|------------|

| HO1L 21/336               | HO1L 29/ | 78 3 O 1 P |

| HO1 L 21/28               | HO1L 21/ | 28 L       |

| HO1L 21/768               | HO1L 21/ | '90 C      |

| HO1L 29/78                | HO1L 29/ | 78 301G    |

請求項の数 5 (全 18 頁)

(21) 出願番号 特願2000-368661 (P2000-368661) (22) 出願日 平成12年12月4日 (2000.12.4) (65) 公開番号 特開2002-170953 (P2002-170953A) (43) 公開日 平成14年6月14日 (2002.6.14) 審査請求日 平成15年1月31日 (2003.1.31) (73)特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

||(74)代理人 100065248

弁理士 野河 信太郎

(72) 発明者 徳重 信明

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

|(72)発明者 金子 誠二

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 松嶋 秀忠

最終頁に続く

#### (54) 【発明の名称】半導体装置の製造方法

# (57)【特許請求の範囲】

#### 【請求項1】

(a) 半導体基板上にゲート絶縁膜を介してダミーゲートパターンを形成する工程と、(b) 該ダミーゲートパターンの側壁にサイドウォール絶縁膜を形成する工程と、(c) 少なくともコンタクトプラグ形成領域に前記ダミーゲートパターンと同一材料の膜を形成する工程と、(d) 該ダミーゲートパターンと同一材料の膜の周囲の前記半導体基板上に層間絶縁膜を形成する工程と、(e) ダミーゲートパターンと、前記コンタクト形成領域上に配置されるダミーゲートパターンと同一材料の膜とを同時に除去して前記層間絶縁膜に溝を形成する工程と、(f) 導電材を、溝を含む半導体基板上全面に形成し、導電材の表面を、層間絶縁膜が露出するまで平坦化して、導電材を溝内に埋め込んでゲート電極とコンタクトプラグとを形成する工程を順次、独立して実施することを特徴とする半導体装置の製造方法。

【請求項2】

(a')半導体基板上にゲート絶縁膜を介して所定形状の導電膜と、該導電膜上にダミーゲートパターンとを形成する工程と、(b')該導電膜及びダミーゲートパターンの側壁にサイドウォール絶縁膜を形成する工程と、(c)少なくともコンタクトプラグ形成領域に前記ダミーゲートパターンと同一材料の膜を形成する工程と、(d)該ダミーゲートパターンと同一材料の膜の周囲の前記半導体基板上に層間絶縁膜を形成する工程と、(e)ダミーゲートパターンと、前記コンタクト形成領域上に配置されるダミーゲートパターンと同一材料の膜とを同時に除去して前記層間絶縁膜に溝を形成する工程と、(f')導

電材を、溝を含む半導体基板上全面に形成し、層間絶縁膜が露出するまで平坦化して、<u>該</u> 満内に導電材を埋め込んで、コンタクトプラグと、前記導電膜及び導電材からなるゲート 電極とを形成する工程を順次、独立して実施することを特徴とする半導体装置の製造方法

#### 【請求項3】

溝を形成する<u>前に、</u>サイドウォール絶縁膜の上部を平坦化する請求項1<u>または2</u>に記載の方法。

# 【請求項4】

導電材が、金属又は高融点金属である請求項1~3のいずれか1つに記載の方法。

#### 【請求項5】

ダミーゲートパターンがシリコン窒化膜であり、サイドウォール絶縁膜がシリコン酸化膜である請求項 1 ~ 4 のいずれか 1 つに記載の方法。

#### 【発明の詳細な説明】

[0001]

#### 【発明の属する技術分野】

本発明は、半導体装<u>置の</u>製造方法に関し、より詳細には<u>、本発明は、</u>半導体プロセスにおけるゲート電極と配線のショートを防止する半導体装置の製造方法に関する。

シリコン酸化膜をゲート絶縁膜として用いるMOSトランジスタでは、ゲート絶縁膜に対

#### [0002]

# 【従来の技術】

する信頼性はトランジスタの性能を向上させる上で重要な役割を果たしている。しかし、ゲート絶縁膜を、例えば、4nm程度以下と薄膜化すると、ゲート電極への不純物のドーピング時やゲート電極加工時等のプラズマダメージ、チャネル領域及びソース/ドレイン領域へのイオン注入時等のイオンダメージ等、プロセス中のゲート絶縁膜の信頼性劣化(TDDB劣化、リーク電流の増大、耐圧の劣化など)を引き起こす原因となる。このような問題に対する解決策の一つとして、ダミーゲートパターンを用いたゲート電極の形成方法が提案されている(例えば、特開平11・74508号公報)。

#### [0003]

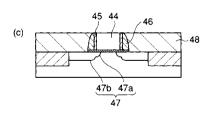

この方法では、まず、例えば、反応イオンエッチング(RIE)法を用いてシリコン基板 4 1 に溝を掘り、その溝に絶縁膜を埋め込んで、いわゆるトレンチ素子分離層 4 2 (トレンチ深さ約 0 . 2  $\mu$  m程度のSTI (Shallow Trench Isolarion))を形成する。続いて、厚さ 5 n m程度のSiO2からなるパッド酸化膜(ダミー絶縁膜) 4 3 を熱酸化により、さらにパッド酸化膜 4 3 上にダミーゲートパターン用のアモルファスシリコン膜を 3 0 n m程度の膜厚で堆積する。アモルファスシリコン膜を、通常のリソグラフィ工程で形成したレジストをマスクとして用いてRIE法などによりエッチングし、後の工程でゲート電極を形成するために除去されるダミーゲートパターン 4 4 を形成する(図 1 1 (a))。

#### [0004]

次に、図11(b)に示すように、ダミーゲートパターン44の表面を、例えば850の酸素雰囲気で熱酸化して、約10nm程度の膜厚の酸化膜45を形成する。LDD(Lightly Doped Drain)構造を形成するため、ダミーゲートパターン44及び熱酸化膜45をマスクとして用いて、nチャネルトランジスタの場合には、例えばリン( $P^+$ )イオンの注入を70keV、4×10 $^{13}$  c  $m^{-2}$  程度イオン注入して $n^-$  型拡散領域47aを形成する。

#### [0005]

続いて、図11(c)に示すように、得られたシリコン基板41上全面に、 $Si_3N_4$ 膜(又は $SiO_2$ 膜)を堆積し、RIE法によりエッチバックしてダミーゲートパターン44の側壁にサイドウォール絶縁膜46を形成する。このサイドウォール絶縁膜46は、ダミーゲートパターン44の側壁にある熱酸化膜45上に膜厚20nm程度とする。ダミーゲートパターン44及びサイドウォール絶縁膜46をマスクとして用いて、例えば砒素(A

10

20

30

40

$s^+$ )イオンの注入を 3 0 k e V 、 5  $\times$  1 0 15 c  $m^{-2}$  程度イオン注入して、  $n^+$  型拡散領域 4 7 b を形成する。その後、シリコン基板 4 1 上全面に S i O 2 からなる層間絶縁膜 4 8 を形成し、層間絶縁膜 4 8 の表面を C M P (Chemical Mechanical Polishing) により平 坦化し、ダミーゲートパターン 4 4 の表面を露出させる。

#### [0006]

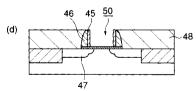

次に、図11(d)に示すように、ダミーゲートパターン44を、CDE(Chemical Dry Etching)法やKOH溶液を用いたウェットエッチング法などにより選択的に除去し、溝部50を形成する。その後、所望の領域に形成したレジストパターン(図示せず)、層間絶縁膜48、サイドウォール絶縁膜46及び熱酸化膜45をマスクとして用いて、所望のチャネル領域にのみチャネル・イオン注入を行う。nチャネルトランジスタの場合、例えば0.7V程度のしきい値電圧(Vth)を設定するためには、ボロン(B<sup>+</sup>)を10keV、5×10 $^{12}$ cm $^{-2}$ 程度イオン注入し、チャネル領域にのみ選択的にp型チャネル不純物領域(図示せず)を形成する。

## [0007]

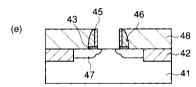

次いで、図12( e )に示すように、溝部50の底部のパッド酸化膜43を除去する。 さらに、図12( f )に示すように、全面にCVD-SiO $_2$  膜(膜厚は約3nm程度) や高誘電体膜(例えばTa $_2$ О $_5$  膜、膜厚は20nm程度)からなるゲート絶縁膜49を堆積する。

## [0008]

次に、図12(g)に示すように、例えばメタル膜(Ru膜、TiN膜、W膜、タングステンナイトライド膜(WN $_x$ )又はW膜/TiN膜のような単層膜又は積層膜)を全面に堆積する。その後、CMP法によりメタル膜及び層間絶縁膜48上に配置するゲート絶縁膜49を除去し、溝部50内にゲート電極50を形成する。

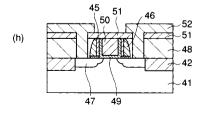

#### [0009]

続いて、図12(h)に示すように、シリコン基板41上全面に $SiO_2$ からなる層間絶縁膜51を約200nm程度の厚さに堆積し、ソース / ドレイン領域47及びゲート電極50へのコンタクト孔を開口し、さらにA1層を堆積してコンタクト孔を埋め、パターニングして配線52を形成する。

その後、全面にパッシベーション膜(図示せず)を堆積し、トランジスタの基本構造を作 製する。

#### [0010]

# 【発明が解決しようとする課題】

しかし、上記のように形成されたトランジスタのソース/ドレイン領域47を、コンタクト孔を介して配線52に接続する場合、コンタクト孔は、通常、フォトリソグラフィ工程を用いて形成されるため、ゲート電極50との間でアライメントずれが生じ、配線52とゲート電極50とがショートすることがある。つまり、ダミーゲートパターンとコンタクト孔との形成のためのアライメントが別工程なので、半導体装置の微細化によりゲート電極とコンタクト孔との間隔がより狭くなり、少しのアライメントずれでもショートを引き起こす。その結果、形成されたトランジスタは、特性劣化を招くのみならず、本来の動作をしなくなる。

# [0011]

#### 【課題を解決するための手段】

本発明によれば、(a) 半導体基板上にゲート絶縁膜を介してダミーゲートパターンを形成する工程と、(b) 該ダミーゲートパターンの側壁にサイドウォール絶縁膜を形成する工程と、(c) 少なくともコンタクトプラグ形成領域に前記ダミーゲートパターンと同一材料の膜を形成する工程と、(d) 該ダミーゲートパターンと同一材料の膜の周囲の前記半導体基板上に層間絶縁膜を形成する工程と、(e) ダミーゲートパターンと、前記コンタクト形成領域上に配置されるダミーゲートパターンと同一材料の膜とを除去して前記層間絶縁膜に溝を形成する工程と、(f) 導電材を、溝を含む半導体基板上全面に形成し、導電材の表面を、層間絶縁膜が露出するまで平坦化して、導電材を溝内に埋め込んでゲ

10

20

30

40

30

40

50

ート電極とコンタクトプラグとを形成する工程を<u>順次、独立して実施する</u>ことを特徴とする半導体装置の製造方法が提供される。

# [0012]

また、本発明によれば、(a')半導体基板上にゲート絶縁膜を介して所定形状の導電膜と、該導電膜上にダミーゲートパターンとを形成する工程と、(b')該導電膜及びダミーゲートパターンの側壁にサイドウォール絶縁膜を形成する工程と、(c)少なくともコンタクトプラグ形成領域に前記ダミーゲートパターンと同一材料の膜を形成する工程と、(c)少なくとも、(d)該ダミーゲートパターンと同一材料の膜の周囲の前記半導体基板上に層間絶縁膜を形成する工程と、(e)ダミーゲートパターンと、前記コンタクト形成領域上に配置されるダミーゲートパターンと同一材料の膜とを同時に除去して前記層間絶縁膜に溝を形成する工程と、(f')導電材を、溝を含む半導体基板上全面に形成し、層間絶縁膜が露出するまで平坦化して、該溝内に導電材を埋め込んで、コンタクトプラグと、前記導電膜及び導電材からなるゲート電極とを形成する工程を順次、独立して実施することを特徴とする半導体装置の製造方法が提供される。

#### [0017]

#### 【発明の実施の形態】

本発明の半導体装置の製造方法は、工程(a)において、半導体基板上にゲート絶縁膜を介してダミーゲートパターンを形成する。ここで、本発明で使用することができる半導体基板としては、通常、半導体装置に使用されるものであれば特に限定されるものではなく、例えば、シリコン、ゲルマニウム等の元素半導体、GaAs、InGaAs、ZnSe等の化合物半導体が挙げられる。また、SOI基板又は多層SOI基板等の種々の基板を用いてもよい。さらに、エピタキシャル半導体層を表面に成長させたいわゆるエピタキシャル基板でもよい。なかでもシリコン基板が好ましい。この半導体基板上には、素子分離領域が形成されていることが好ましく、さらにトランジスタ、キャパシタ、抵抗等の素子、層間絶縁膜、これらによる回路、半導体装置等が組み合わせられて、シングル又はアチレイヤー構造で形成されていてもよい。なお、素子分離領域は、LOCOS膜、トレンチ酸化膜、STI膜等種々の素子分離膜により形成することができる。なかでもSTI膜が好ましい。また、この半導体基板の表面には、1以上のn型又はp型の高濃度不純物領域(ウェル)が形成されていてもよい。

# [0018]

ゲート絶縁膜は、通常トランジスタのゲート絶縁膜として機能し得る絶縁膜、例えば、シリコン酸化膜( $CVD-SiO_2$ 膜、熱- $SiO_2$ 膜)又はシリコン窒化膜等の絶縁膜、 $Ta_2O_5$ 等の高誘電体膜、又はこれらの積層膜等を用いることができる。膜厚は、特に限定されるものではなく、例えば、絶縁膜は0.1~20nm程度、高誘電体膜は5~50nm程度が挙げられる。ゲート絶縁膜は、熱酸化法、CVD法、スパッタ法、蒸着法、陽極酸化法等又はこれらの組み合わせにより形成することができる。

# [0019]

ダミーゲートパターンは、ゲート電極を形成する領域に予備的に形成しておくパターンを意味し、その形状、膜厚等は、得ようとするゲート電極の機能、このゲート電極から構成される半導体装置の特性及び機能等により適宜調整することができる。例えば、ダミーゲートパターンの膜厚としては、200~600mm程度が挙げられる。また、ダミーゲートパターンは、ゲート電極を形成する前に、除去されるパターンであるため、除去する条件等に応じてその材料を適宜選択することができる。例えば、ポリシリコン、アモルファスシリコン等の半導体;アルミニウム、ニッケル等の金属又は合金;タンタル、タングステン等の高融点金属;シリコン酸化膜(熱酸化膜、低温酸化膜:LTO膜等、高温酸化膜:HTO膜)、シリコン窒化膜、SOG膜、PSG膜、BSG膜、BPSG膜等の絶縁膜;PZT、PLZT、強誘電体膜又は反強誘電体膜等の誘電体;の単層膜又は積層膜等が挙げられる。なかでも、絶縁膜、とくにシリコン窒化膜、シリコン酸化膜が好ましく、シリコン窒化膜がより好ましい。

ダミーゲートパターンの形成は、半導体基板上全面にダミーゲートパターンを形成する材

30

40

50

料膜を堆積し、公知の方法、例えばフォトリソグラフィ及びエッチング工程により、所望の形状にパターニングすることにより形成することができる。

#### [0020]

工程(b)において、ダミーゲートパターンの側壁にサイドウォール絶縁膜を形成する。サイドウォール絶縁膜は、例えば、上述した絶縁膜の単層膜又は積層膜により形成することができる。なかでも、ダミーゲートパターンを構成する膜とは異なる膜、特に、後工程でダミーコンタクトパターンを除去する際に、ダミーゲートパターンとの選択比が大きくなる材料を選択することが好ましい。具体的には、ダミーゲートパターンがシリコン窒化膜の場合には、シリコン酸化膜等が挙げられる。サイドウォール絶縁膜は、公知の方法、例えば、絶縁膜を、得られた半導体基板上全面に形成し、RIE等の異方性エッチングによってエッチバックして形成することができる。

#### [0021]

なお、サイドウォール絶縁膜の膜厚は、後に形成されるゲート電極とコンタクトプラグとを電気的に分離することができる程度で、かつ所望の機能が得られる L D D 領域を形成することができるように設定することが好ましい。例えば、ダミーゲートパターン側壁上のサイドウォール絶縁膜の最も厚膜部分での膜厚は、10~50nm程度が挙げられる。

#### [0022]

工程(c)少なくともコンタクトプラグ形成領域にダミーゲートパターンと同一材料の膜を形成する。

コンタクトプラグ形成領域とは、半導体基板、つまりソース / ドレイン領域とゲート電極より上層の配線とを接続するための領域であり、通常、ソース / ドレイン領域上の領域を意味する。

ダミーゲートパターンと同一材料の膜は、材料が同一であるのみならず、同一の方法で形成した同質の膜であることが好ましい。この膜の膜厚は、ダミーゲートパターンよりも薄膜であってもよいが、ダミーゲートパターンと同程度又はそれ以上であることが好ましい

## [0023]

例えば、この膜は、ダミーゲートパターン及びサイドウォール絶縁膜に隣接してこれらの外周を囲む領域のみに;このような外周を囲む領域を含む領域に;あるいは後述する工程(d)で形成する層間絶縁膜をかねて、得られた半導体基板上全面に形成してもよい。なお、この膜は、ダミーゲートパターンを完全に被覆しないように、好ましくは、ダミーゲートパターンの表面が露出するように、ダミーゲートパターンの上面と面一になるように平坦化することが好ましい。このような領域への膜の形成は、得られた半導体基板上全面に膜を堆積し;任意にフォトリソグラフィ及びエッチング工程によりパターニングし;任意にCMP法等により表面を平坦化することにより形成することができる。

#### [0024]

工程(d)において、ダミーゲートパターンと同一材料の膜の周囲の半導体基板上に層間絶縁膜を形成する。層間絶縁膜としては、上層配線と下層配線とを電気的に分離することができる膜であれば、その材料及び膜厚は特に限定されるものではなく、例えば、上述の絶縁膜の中から選択することができ、ダミーゲートパターンの膜厚と同等又は厚膜とすることができる。層間絶縁膜は、得られた半導体基板上全面に形成し、CMP法等により層間絶縁膜の表面を、ダミーゲートパターン及びその外周の同一材料の膜の表面が露出するまで平坦化することが好ましく、さらに、サイドウォール絶縁膜の上が平面状になるまで、層間絶縁膜、ダミーゲートパターン、同一材料の膜及びサイドウォール絶縁膜を平坦化することが好ましい。

# [0025]

工程(e)において、ダミーゲートパターンとコンタクト形成領域上に配置されるダミーゲートパターンと同一材料の膜とを除去して層間絶縁膜に溝を形成する。ダミーゲートパターン及びこれと同一材料の膜を除去する方法としては、例えば、ふっ酸、熱リン酸、硝酸、硫酸等を用いたウェットエッチング、スパッタリング法、反応性イオンエッチング法

、プラズマエッチング法等のドライエッチング法等種々の方法が挙げられる。

#### [0026]

なお、層間絶縁膜が、ダミーゲートパターンと同一材料の膜と、1工程で一体的に形成されている場合には、ダミーゲートパターン、サイドウォール絶縁膜及びコンタクトプラグ形成領域であり、かつサイドウォール絶縁膜に隣接するこれらを囲む外周領域に開口を有するレジストパターンをマスクとして用いて、上述のウェットエッチング又はドライエッチングにより除去することができる。

また、先の工程においてサイドウォール絶縁膜の上が平坦化されていない場合は、溝を形成した後、サイドウォール絶縁膜の上を平坦化してもよい。

#### [0027]

工程(f)において、溝内に導電材を埋め込んでゲート電極とコンタクトプラグとを形成する。ここで使用することができる導電材は、アルミニウム、ルテニウム、銅、金、銀、ニッケル等の金属、タンタル、タングステン、チタン等の高融点金属、TiN、WNx等の窒化物、ポシリコン、高融点金属のシリサイド又はポリサイド、等の単独又は合金の単層関又は積層膜等が挙げられる。これらは、蒸着法、スパッタ法、CVD法、EB法等の種々の方法で形成することができる。導電材の膜厚は特に限定されるものではないが、溝を完全に埋め込むことができる膜厚が好ましく、例えば、100~600mm程度が挙げられる。

## [0028]

導電材を溝内に埋め込んでゲート電極とコンタクトプラグとを形成する方法としては、導電材を、溝を含む半導体基板上全面に形成し、導電材の表面を、例えば、CMP法により層間絶縁膜が露出するまで平坦化する方法が挙げられる。

また、本発明の半導体装置の別の製造方法として、工程(a')において、まず、半導体基板上にゲート絶縁膜を介して所定形状の導電膜と、この導電膜上にダミーゲートパターンを形成する。この工程でのゲート絶縁膜の形成は、実質的に工程(a)と同様に行うことができる。ここで使用することができる導電膜としては、導電材として上記したものと同様のものが挙げられる。なかでもポリシリコン膜が好ましい。導電膜の膜厚は特に限定されるものではなく、得ようとするゲート電極の膜厚等を考慮して適宜調整することができる。この工程におけるダミーゲートパターンは、工程(a)に準じて、導電膜上に形成し、導電膜と同時にパターニングすることにより形成することができる。

#### [0029]

工程( b ')において、導電膜及びダミーゲートパターンの側壁にサイドウォール絶縁膜を形成する。この工程は、工程( b )と同様に行うことができる。

工程(f ')において、溝内に導電材を埋め込む。導電材を埋め込む方法は、工程(f)と同様に行うことができる。これにより、コンタクトプラグと、導電材 / 導電膜の積層構造からなるゲート電極とを形成することができる。

さらに、本発明の半導体装置の別の製造方法では、工程(a")において、半導体基板上にゲート絶縁膜を介して複数のダミーゲートパターンを形成する。この工程は、工程(a)と実質的に同様に行うことができる。

#### [0030]

工程(c")において、ダミーゲートパターン間であって、コンタクトプラグ形成領域に、ダミーコンタクトパターンをセルフアラインで形成する。ここで、ダミーコンタクトパターンとは、コンタクトプラグを形成する領域に予備的に形成しておくパターンを意味し、その形状、膜厚等は、得ようとするコンタクトプラグの機能等により適宜調整することができる。また、ダミーコンタクトパターンは、コンタクトプラグを形成する前に除去されるパターンであるため、除去する条件等によって、ダミーゲートパターンとして上述した材料の中から適宜選択することができる。例えば、ダミーコンタクトパターンがダミーゲートパターンと同様の膜厚とする場合には、同一材料であることが好ましい。また、ダミーコンタクトパターンとして、ダミーゲートパターンと異なる材料、具体的には、エッチングされにくい材料を選択する場合には、ダミーゲートパターンとの選択比を考慮して

10

30

20

40

30

40

50

、ダミーゲートパターンよりも薄膜で形成することが好ましい。ダミーコンタクトパター ンがダミーゲートパターンと同様の膜厚、同一材料で形成されることがより好ましい。

#### [0031]

ダミーコンタクトパターンは、半導体基板上全面にダミーコンタクトパターンを形成する材料膜を堆積し、ダミーゲートパターンの表面が露出するまでCMP法等によって平坦化することにより、ダミーゲートパターンの間にサイドウォール絶縁膜を介して自己整合的に埋め込み、形成することができる。

#### [0032]

工程( e ")は、工程( e )と実質的に同様の方法で行うことができる。

さらに、本発明の半導体装置の別の製造方法では、上記の各製造方法中の工程を任意の組み合わせとする、すなわち、工程(a')、(b')、(c")、(d")及び(f')を組み合わせることにより、実現することができる。

また、本発明の半導体装置のさらに別の製造方法では、工程(aa)において、半導体基板上に複数のダミーゲートパターンを形成する。ここでのダミーゲートパターンは、工程(aa)でのダミーゲートパターンの形成と同様に行うことができる。

#### [0033]

工程(cc)において、ダミーゲートパターン間であって、コンタクトプラグ形成領域に導電材を埋め込んでコンタクトプラグを形成する。ここでの導電材の種類及び埋め込み方法は、実質的に工程(f)と同様に行うことができる。

工程(dd)において、ダミーゲートパターンを除去して溝を形成する。この工程は、実質的に工程(e)及び(e")と同様に行うことができる。

工程(ee)において、少なくとも溝底面にゲート絶縁膜を形成する。ここでゲート絶縁膜の形成は、工程(a)におけるゲート絶縁膜の形成と実質的に同様に行うことができる。なお、ゲート絶縁膜は、溝底面のみならず、コンタクトプラグ、サイドウォール絶縁膜を含む基板上全面に形成してもよい。

#### [0034]

工程(ff)において、溝内に導電材を埋め込んでゲート電極を形成する。この工程は、実質的に(f)と同様に行うことができる。

なお、本発明の半導体記憶装置の製造方法においては、所望の工程前、中、後に、低濃度及び/又は高濃度不純物層を形成するためのイオン注入を行うことが好ましい。イオン注入は、不純物層の形成位置、不純物濃度、イオン注入方法等に応じて、基板に対して垂直な方向から又は所定角度傾斜させて行ってもよい。このようなイオン注入により、シングル構造、LDD構造、DDD構造等のソース/ドレイン領域等を形成することができる。また、半導体装置を形成するための公知の方法により、任意に、閾値調整のためのイオン注入、熱処理、サリサイド工程、絶縁膜の形成、絶縁膜の緻密化、コンタクトホールの形成及び/又は配線層の形成等を行うことが好ましい。例えば、熱処理は、大気中、酸素雰囲気又は窒素雰囲気下で、600~900 程度の温度範囲で、1秒間~5分間程度、炉アニール、RTA(Rapid Thermal Anneal)法等により、不純物の活性化、絶縁膜の緻密化又は平坦化等として行うことができる。

以下、本発明の半導体装置及びその製造方法の実施の形態を図面を参照して詳細に説明する。

#### [0035]

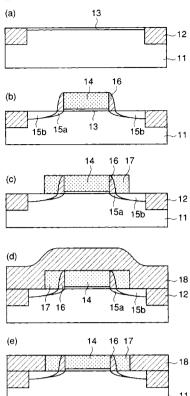

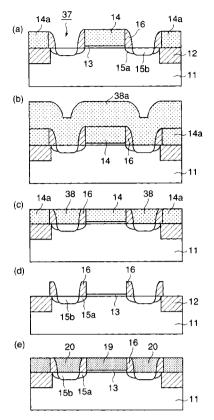

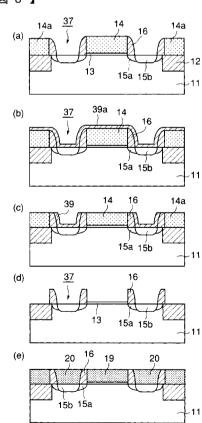

# 実施の形態 1

まず、図1(a)に示すように、不純物濃度  $5 \times 10^{15}$  c  $m^{-3}$  程度の p 型シリコン基板 1 1 の ( 1 0 0 ) 面に、 n チャネルトランジスタ形成領域には p ウエル(図示せず)を、 p チャネルトランジスタ形成領域には n ウエル(図示せず)をそれぞれ形成する。 その後、 R I E 法によりシリコン基板 1 1 に溝を掘り、その溝に絶縁膜を埋め込んで、いわゆるトレンチ素子分離層 1 2 ( トレンチ深さ約 0 . 2  $\mu$  m 程度の S T I )を形成する。 得られたシリコン基板 1 1 上全面に C V D - S i O 2 膜もしくは熱 - S i O 2 膜(膜厚は約 3 n m程度)、又は高誘電体膜(例えば T a 2 O 5 膜、膜厚は 2 0 n m 程度)からなるゲート絶縁膜

13を堆積する。

#### [0036]

次に、図1(b)に示すように、このゲート絶縁膜13上にダミーゲートパターン用のシリコン窒化膜を400nm程度の膜厚に堆積し、これをリソグラフィ工程で形成したレジストパターン(図示せず)をマスクとして用いてRIE法によりエッチングし、ダミーゲートパターン14を形成する。

L D D 構造を形成するため、ダミーゲートパターン 1 4 をマスクとして用いて、 n チャネルトランジスタの場合には、例えばリン(  $P^+$  ) イオンを 7 0 k e V 、 4 x 1  $0^{13}$  c m<sup>-2</sup> 程度注入し、 n  $^-$ 型拡散領域 1 5 a を形成する。

#### [0037]

続いて、 $SiO_2$ 膜を全面に堆積し、全面のRIE法によるエッチバックを行い、ダミーゲートパターン 1 4 の側壁に膜厚 2 0 n m程度のサイドウォール絶縁膜 1 6 を形成する。その後、ダミーゲートパターン 1 4 及びサイドウォール絶縁膜 1 6 をマスクとして用いて、例えば砒素( $As^+$ )イオンを 3 0 k e V、 $5 \times 10^{15}$  c m  $^{-2}$ 程度注入し、 $n^+$ 型拡散領域 1 5 b を形成する。

#### [0038]

次に、図1(c)に示すように、シリコン基板11上にシリコン窒化膜を400nm程度の膜厚に堆積し、平坦化を行った後、シリコン窒化膜をリソグラフィエ程で形成したレジストをマスクとして用いてRIE法によりエッチングし、サイドウォール絶縁膜16を囲み、後の工程でコンタクト孔を形成するために除去されるダミーコンタクトパターン17を形成する。

#### [0039]

次いで、図1(d)に示すように、シリコン基板11上全面にCVD-SiO $_2$ 膜からなる層間絶縁膜18を、例えば400nm程度堆積し、800 程度のN $_2$ 雰囲気下で30分間程度、緻密化する。ここでの熱処理は、ソース/ドレイン領域におけるイオン注入領域の活性化をも兼ねている。

## [0040]

その後、図1(e)に示すように、層間絶縁膜18の表面をCMP法により平坦化し、さらに、ダミーゲートパターン14の表面を露出させる。この際、ゲート電極とコンタクトとのショートを防ぐため、サイドウォール絶縁膜16の上部も平坦化してもよい。この場合、ダミーゲートパターン14及びダミーコンタクトパターン17の表面が露出した時点で熱燐酸あるいはRIEによりダミーゲートパターン14及びダミーコンタクトパターン17の表面をエッチングすることでシリコン窒化膜を後退させ、再度CMPによりサイドウォール絶縁膜16の上部も平坦化する。

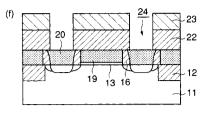

## [0041]

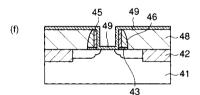

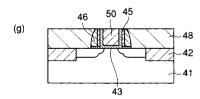

続いて、図 2 ( f )に示すように、熱燐酸あるいはRIEによりダミーゲートパターン 1 4 及びダミーコンタクトパターン 1 7 を選択的に除去する。次いで、チャネル・イオン注入を行う。 n チャネルトランジスタの場合、例えば 0 . 7 V程度のしきい値電圧( $V_{th}$ )を設定するためには、例えば、ボロン( $B^+$ )を 1 0 ke V、 5 × 1  $0^{12}$  c  $m^{-2}$  程度イオン注入し、p 型チャネル不純物領域(図示せず)を形成する。その後、例えばRTAを用いて 8 0 0 、 1 0 秒間程度の熱処理を行う。これにより、この後工程では高温の熱処理工程がないので、トランジスタのショート・チャネル効果を抑えることができるようにチャネル領域の不純物プロファイルを最適化できる。

# [0042]

さらに、図2(g)に示すように、例えば、A1膜を全面に堆積し、CMP法により表面を平坦化し、ゲート電極19及びコンタクトプラグ20を形成する。この際、サイドウォール絶縁膜16及び層間絶縁膜18がCMPのストッパーとしての役割を果たす。

#### [0043]

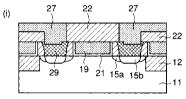

次に、図 2 ( h )に示すように、得られたシリコン基板 1 1 上全面に、プラズマTEOS 法によるSiO $_2$ 膜からなる層間絶縁膜 2 2 を、約 3 0 0 n m程度の膜厚で堆積し、リソ

10

20

30

40

グラフィエ程により形成したレジストパターン 2 3 をマスクとして用いて R I E 法により、コンタクトプラグ 2 0 へのコンタクト孔 2 4 及びゲート電極 1 9 へのコンタクト孔 (図示せず)を形成する。

次いで、レジストパターン 2 3 を除去し、図 2 ( i ) に示すように、いわゆるデュアルダマシン法で配線を形成する。つまり、リソグラフィ工程により、配線パターンを形成する領域に開口を有するレジストパターン 2 6 を形成し、R I E 法により、層間絶縁膜 2 2 に深さ 0 . 2 5  $\mu$  m 程度の溝 2 5 を形成する。

#### [0044]

その後、レジストパターン 2 6 を除去する。図 2 ( j )に示すように、コンタクト孔 2 4 及び溝 2 5 に、例えば A 1 - C u 膜を高温スパッタなどでリフローして埋め込み、 C M P 法で平坦化し、配線 2 7 を形成する。

このような半導体装置の製造方法により、コンタクトプラグ20をゲート電極19に隣接して自己整合的に形成することができ、配線のコンタクトとゲート電極とをショートさせないように確実に分離することができ、しかも、サイドウォール絶縁膜16の膜厚を調整することにより、所望の間隔、つまり、最小限の間隔を有して形成することができる。よって、実質的なゲート電極・コンタクト間の距離を近づけることができ、ソース/ドレイン領域における寄生抵抗を低減できるとともに、トランジスタの素子特性を向上させることができる。

## [0045]

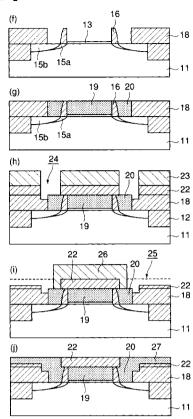

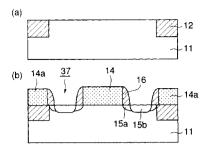

#### 実施の形態 2

まず、実施の形態 1 と実質的に同様に、図 3 ( a ) に示すように、トレンチ素子分離層 1 2 を有するシリコン基板 1 1 上に、TaO₂からなるゲート絶縁膜 1 3、С V D - S i O₂ 膜からなるダミーゲートパターン 1 4 を形成し、さらに、 n 型拡散領域 1 5 a、シリコン室化膜からなるサイドウォール絶縁膜 1 6 及び n  $^{+}$ 型拡散領域 1 5 b を形成する。

次に、図3(b)に示すように、実施の形態1と実質的に同様に、シリコン基板11上に CVD-Si〇₂膜からなる層間絶縁膜18を形成し、緻密化する。

続いて、図3(c)に示すように、層間絶縁膜18の表面をCMP法により平坦化し、ダミーゲートパターン14の表面を露出させる。

# [0046]

次いで、図3(d)に示すように、リソグラフィ工程で形成したレジストパターン28をマスクとして用いて、サイドウォール絶縁膜16を囲み、後の工程でコンタクトを形成する領域の層間絶縁膜18と、ダミーゲートパターン14とを選択的に除去する。

その後の工程は、実施の形態1と同様に行うことができる。

このような半導体装置の製造方法により、実施の形態1と同様の効果を得ることができる

#### [0047]

#### 実施の形態3

まず、実施の形態1と同様に、トレンチ素子分離層12を有するシリコン基板11上にゲート絶縁膜13を堆積する。

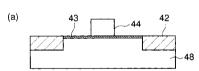

次いで、図4(a)に示すように、ゲート絶縁膜13上にゲート電極となるポリシリコン膜32を200mm堆積し、ドーピングを行い、さらにダミーゲートパターン用のシリコン窒化膜を200mm程度の膜厚に堆積し、これらをリソグラフィ工程で形成したレジストパターン(図示せず)をマスクとして用いてRIE法などによりエッチングしてポリシリコン膜32をパターニングするとともに、後の工程でゲート電極を形成するために除去されるダミーゲートパターン33を形成する。

# [0048]

次に、ダミーゲートパターン 3 3 をマスクとして用いて、実施の形態 1 と同様に、n 2型拡散領域 1 5 a を形成する。続いて、実施の形態 1 と同様に、サイドウォール絶縁膜 1 6 を形成する。その後、ダミーゲートパターン 1 3 及び側壁膜 1 6 をマスクとして用いて、実施の形態 1 と同様に、n 4型拡散領域 1 5 b を形成する。

20

30

10

50

30

40

50

次いで、図4(b)に示すように、サイドウォール絶縁膜16を囲むように、実施の形態1と同様に、ダミーコンタクトパターン17を形成する。

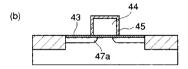

続いて、図4(c)に示すように、実施の形態1と同様に、全面に層間絶縁膜18を形成し、図4(d)に示すように、実施の形態1と同様に、その表面を平坦化してダミーゲートパターン33の表面を露出させる。

#### [0049]

その後、図4(e)に示すように、実施の形態1と同様に、ダミーゲートパターン33及びダミーコンタクトパターン17を選択的に除去する。この際、ダミーゲートパターン33下のポリシリコン膜32は除去されずに残存する。

次いで、Ti、Ta、TaN、W、TiNなどのバリアメタルを形成した後(図示せず)、図4(f)に示すように、実施の形態1と同様に、例えばA1膜35を形成し、その表面を平坦化して、ポリシリコン膜32とA1膜35とからなるゲート電極36及びA1膜35からなるコンタクトプラグ20を形成する。

## [0050]

その後、実施の形態 1 と同様に、デュアルダマシン法により、配線 2 7 を形成する。この半導体装置の製造方法によれば、ゲート絶縁膜 1 3 上にはポリシリコン膜 3 2 が存在するので、オーバーエッチされることがなく、ゲート絶縁膜 1 3 の劣化を防止することができる。

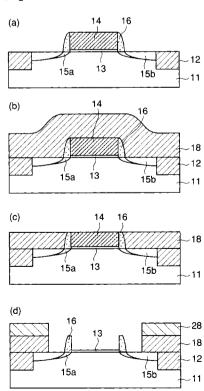

# [0051]

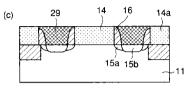

## 実施の形態 4

まず、実施の形態1と同様に、トレンチ素子分離層12を有するシリコン基板11上にゲート絶縁膜13を堆積する。

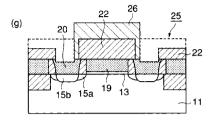

次に、図5(a)に示すように、ゲート絶縁膜13上にダミーゲートパターン用のシリコン窒化膜を300mm程度の膜厚に堆積し、これをリソグラフィ工程で形成したレジストをマスクとして用いてRIE法によりエッチングし、ダミーゲートパターン14を形成する。この際、同時に素子分離層12上にダミーゲートパターン14aを形成し、後工程におけるセルフアラインのダミーコンタクトパターンを形成する領域に溝37を形成する。

#### [0052]

次に、ダミーゲートパターン 1.4、 1.4 a をマスクとして用いて、実施の形態 1 と同様に、 $n^{-}$ 型拡散領域 1.5 a を形成する。続いて、実施の形態 1 と同様に、ダミーゲートパターン 1.4、 1.4 a の側壁にサイドウォール絶縁膜 1.6 を形成する。その後、ダミーゲートパターン 1.4、 1.4 a 及びサイドウォール絶縁膜 1.6 をマスクとして用いて、実施の形態 1.6 と同様に、1.4 に、1.4 な 領域 1.5 b を形成する。

# [0053]

次いで、図 5 ( b ) に示すように、溝 3 7 を含むシリコン基板 1 1 上に、シリコン窒化膜 3 8 a を膜厚 4 0 0 n m程度で形成し、例えば、7 5 0 程度の $N_2$ 雰囲気下、6 0 分間程度のアニール処理を行い、ソース / ドレイン注入によるダメージの回復を行い、さらに 1 0 0 0 程度の $N_2$ 雰囲気下、1 0 秒間程度の $N_2$  R T A 処理を行う。

続いて、図5(c)に示すように、CMP法によってシリコン窒化膜38aを平坦化し、ダミーゲートパターン14、14aの表面を露出させることにより、溝37内にダミーコンタクトパターン38を形成する。

#### [0054]

次いで、図5(d)に示すように、実施の形態1と同様にダミーゲートパターン14、14a及びダミーコンタクトパターン38を選択的に除去し、実施の形態1と同様にチャネル・イオン注入を行う。

さらに、図 5 ( e )に示すように、実施の形態 1 と同様に、例えば A 1 膜を全面に堆積し、 C M P 法により表面を平坦化してゲート電極 1 9 及びコンタクトプラグ 2 0 を形成する

#### [0055]

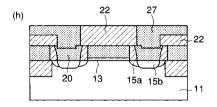

次に、図6(f)に示すように、実施の形態1と同様に、得られたシリコン基板11上全

面に層間絶縁膜22を形成し、レジストパターン23をマスクとして用いてコンタクト孔 2.4 及びゲート電極19へのコンタクト孔(図示せず)を形成する。

次いで、レジストパターン23を除去し、図6(g)に示すように、実施の形態1と同様 に層間絶縁膜22に、深さ0.25μm程度の溝25を形成し、レジストパターン26を 除去する。

#### [0056]

その後、図6(h)に示すように、実施の形態1と同様に、コンタクト孔24及び溝25 に、例えばA1-Cu膜を埋め込み、平坦化して配線27を形成する。

このような半導体装置の製造方法により、実施の形態1と同様の効果を得ることができる とともに、さらに、ダミーコンタクトパターン38を、フォトリソグラフィエ程を利用し てサイドウォール絶縁膜16を囲むようにパターニングする必要がなくなるため、フォト 工程を1回省略することができ、実施の形態1よりもさら製造工程の簡略化を図ることが できる。

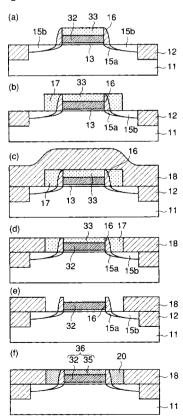

# [0057]

#### 実施の形態 5

まず、実施の形態1と同様に、トレンチ素子分離層12を有するシリコン基板11上にゲ ート絶縁膜13を堆積する。

次いで、図7(a)に示すように、実施の形態3と同様に、膜厚200nm程度のポリシ リコン膜32及び膜厚200nm程度のシリコン窒化膜33を堆積し、これらをパターニ ングしてダミーゲートパターン33を形成する。この際、実施の形態4と同様に、溝37 を形成する。

#### [0058]

次に、ダミーゲートパターン33をマスクとして用いて、実施の形態1と同様に、n<sup>-</sup>型 拡散領域15aを形成する。続いて、実施の形態1と同様に、サイドウォール絶縁膜16 を形成する。その後、ダミーゲートパターン13及びサイドウォール絶縁膜16をマスク として用いて、実施の形態1と同様に、n<sup>+</sup>型拡散領域15bを形成する。

次いで、図7(b)に示すように、実施の形態4と同様に、溝37を含むシリコン基板1 1上に、シリコン窒化膜38aを形成し、熱処理を行う。

# [0059]

続いて、図7(c)に示すように、実施の形態4と同様に、シリコン窒化膜38aを平坦 化し、ダミーゲートパターン33、33aの表面を露出させることにより、溝37内にダ ミーコンタクトパターン38を形成する。

その後、図7(d)に示すように、実施の形態1と同様に、ダミーゲートパターン33、 3 3 a 及びダミーコンタクトパターン 3 8 を選択的に除去する。

#### [0060]

次いで、図7(e)に示すように、実施の形態3と同様に、例えばA1膜35を形成し、 その表面を平坦化して、ポリシリコン膜32とA1膜35とからなるゲート電極36及び A 1 膜 3 5 からなるコンタクトプラグ 2 0 を形成する。

その後、実施の形態1と同様に、デュアルダマシン法により、配線27を形成する。

この半導体装置の製造方法によれば、実施の形態4と同様の効果が得られるとともに、さ らに、ゲート絶縁膜13上にはポリシリコン膜32が存在するので、オーバーエッチされ ることがなく、ゲート絶縁膜13の劣化を防止することができる。

#### [0061]

# 実施の形態 6

図8(a)に示すように、実施の形態1及び4と同様に、トレンチ素子分離層12を有す るシリコン基板11上に、ゲート絶縁膜13、膜厚300nm程度のダミーゲートパター ン 1 4 、 1 4 a 、 溝 3 7 、 n ˙型拡散領域 1 5 a 、 n ˙型拡散領域 1 5 b 及びサイドウォー ル絶縁膜16を形成する。

# [0062]

次いで、図8(b)に示すように、得られたシリコン基板11上に、ダミーゲートパター

20

30

40

ン14、14aを構成する膜とは異なる膜、例えば、シリコン酸化膜39を膜厚5nm程度で形成する。ここでのシリコン酸化膜39の膜厚は、後工程でのダミーゲートパターン14、14aのエッチング法によって調整することができ、この実施の形態では、ダミーゲートパターン14、14aを構成するシリコン窒化膜とシリコン酸化膜39との選択比が約60程度であることを想定して決定している。その後、実施の形態1又は4と同様に、熱処理を行う。

#### [0063]

その後、図8(c)に示すように、実施の形態1に準じて、シリコン酸化膜39をCMP 法により平坦化し、ダミーゲートパターン14、14aの表面を露出させる。

次いで、図8(d)に示すように、実施の形態1と同様に、ダミーゲートパターンを除去し、チャネル注入、熱処理等を行う。この際、溝37内のシリコン酸化膜39も完全に除去される。

#### [0064]

続いて、図8(e)に示すように、実施の形態1及び4と同様に、ゲート電極19及びコンタクトプラグ20を形成し、実施の形態1と同様に、デュアルダマシン法により、配線27を形成する。

このような半導体装置の製造方法により、実施の形態 4 及び 5 を同様の効果を得ることができる。

#### [0065]

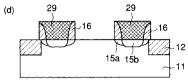

#### 実施の形態 7

図 9 (a)に示すように、実施の形態 1 と実質的に同様に、シリコン基板 1 1 上に、トレンチ素子分離層 1 2 を形成する。

次いで、図 9 ( b ) に示すように、実施の形態 4 と同様に、得られたシリコン基板 1 1 上に、ダミーゲートパターン 1 4 、 1 4 a 、溝 3 7 、  $n^{-}$ 型拡散領域 1 5 a 、  $n^{+}$ 型拡散領域 1 5 b 及びサイドウォール絶縁膜 1 6 を形成する。

#### [0066]

続いて、図9(c)に示すように、得られたシリコン基板11上全面に、Cu膜を形成し、CMP法により平坦化し、ダミーゲートパターン14、14aの表面を露出させることにより、コンタクトプラグ29を形成する。その後、実施の形態1又は4と同様に熱処理を行う。

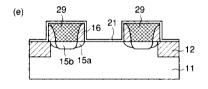

次いで、図9(d)に示すように、実施の形態1と実質的に同様に、ダミーゲートパターン14、14aを選択的に除去し、実施の形態1又は4と同様に、チャネル・イオン注入、熱処理等を行う。

## [0067]

続いて、図9(e)に示すように、実施の形態1と実質的に同様に、得られたシリコン基板11上全面にゲート絶縁膜21を形成する。

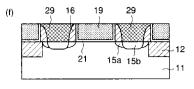

ゲート絶縁膜21上に、図10(f)に示すように、実施の形態1と同様に、例えば、A 1膜を全面に堆積し、平坦化することによりゲート電極19を形成する。

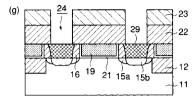

さらに、図10(g)に示すように、実施の形態1と同様に、得られたシリコン基板11 上全面に層間絶縁膜22を堆積し、レジストパターン23をマスクとして用いてコンタクトプラグ29へのコンタクト孔24及びゲート電極19へのコンタクト孔(図示せず)を 形成する。

#### [0068]

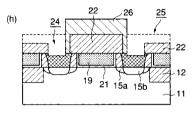

次いで、レジストパターン 2 3 を除去し、図 1 0 (h)に示すように、実施の形態 1 と同様に、いわゆるデュアルダマシン法で配線を形成する。つまり、レジストパターン 2 6 を利用して溝 2 5 を形成する。

その後、レジストパターン 2 6 を除去する。図 1 0 (i)に示すように、実施の形態 1 と同様に、コンタクト孔 2 4 及び溝 2 5 に A 1 - C u 膜を埋め込み、平坦化し、配線 2 7 を形成する。

このような半導体装置の製造方法により、実施の形態1と同様の効果を得ることができる

20

30

50

。また、ゲート絶縁膜を、ゲート電極を形成する直前に形成するため、さらにゲート絶縁 膜の劣化を防止することができ、信頼性の高いゲート絶縁膜を得ることができる。

#### [0069]

#### 【発明の効果】

本発明の半導体装置の製造方法によれば、コンタクトプラグをゲート電極に対して自己整合的に形成できるため、コンタクトプラグとゲート電極とのアライメントずれに起因するショートを防止することができる。また、コンタクトプラグとゲート電極との距離は、実質的にサイドウォール絶縁膜の膜厚により制御することができるため、サイドウォール絶縁膜の膜厚を薄膜化することにより、素子の占有面積をより縮小化することができ、集積度を上げることができる。

[0070]

また、ダミーゲートパターンの形成の前に、予め導電膜を形成する場合には、ゲート絶縁膜がプロセス中導電膜に被覆され、露出することがないため、ゲート絶縁膜の劣化をより抑制することができる。

さらに、ダミーゲートパターンを複数形成する場合には、ダミーコンタクトパターンは、ダミーゲートパターン間に形成することができるため、ダミーコンタクトパターンを形成するためのフォトリソグラフィ工程を省略することができ、より製造方法の簡略化を図ることができる。

[ 0 0 7 1 ]

さらに、ゲート絶縁膜をプロセスのより後工程とすることにより、ゲート絶縁膜の劣化を さらに防止することができ、非常に信頼性の高い半導体装置を製造することが可能となる

また、溝を形成する前又は後にサイドウォール絶縁膜の上部を平坦化する場合には、ゲート電極とコンタクトプラグとの接触をより確実に防止することができ、ゲート電極とコンタクトプラグとのショートを回避することが可能となる。

[0072]

さらに、高温熱工程をゲート電極の形成前に行うため、融点が低い導電材をゲート電極として用いることができるため、高速化等、素子特性の向上を図ることが可能となる。また、ダミーゲートパターンが又はダミーゲートとダミーコンタクトパラーンとがシリコン窒化膜であり、サイドウォール絶縁膜がシリコン酸化膜である場合には、溝を形成する際に、ダミーゲートパターンを容易に選択的に除去することができ、半導体装置を簡便に製造することが可能となる。

[0073]

さらに、ゲート電極とコンタクトプラグとの間に、サイドウォール絶縁膜とゲート絶縁膜とを配置し、ゲート電極の上面をコンタクトプラグの上面と同一高さとする場合には、ゲート電極とコンタクトプラグとの平坦性が保たれるため、後工程のメタル形成工程のプロセスマージン、特にフォトマージンを確保することができる。

さらに、本発明の半導体装置によれば、最小面積で確実に素子内又は素子間のショートを防止することができ、さらにゲート絶縁膜の劣化が抑制された信頼性の高い半導体装置を提供することが可能となる。

【図面の簡単な説明】

【図1】本発明における半導体装置の製造方法の第1の実施形態を示す概略工程断面図である。

【図2】本発明における半導体装置の製造方法の第1の実施形態を示す概略工程断面図である。

【図3】本発明における半導体装置の製造方法の第2の実施形態を示す概略工程断面図で ある。

【図4】本発明における半導体装置の製造方法の第3の実施形態を示す概略工程断面図である。

【図5】本発明における半導体装置の製造方法の第4の実施形態を示す概略工程断面図で

10

30

20

40

ある。

- 【図6】本発明における半導体装置の製造方法の第5の実施形態を示す概略工程断面図で

- 【図7】本発明における半導体装置の製造方法の第5の実施形態を示す概略工程断面図で

- 【図8】本発明における半導体装置の製造方法の第6の実施形態を示す概略工程断面図で

- 【図9】本発明における半導体装置の製造方法の第7の実施形態を示す概略工程断面図で ある。

- 【図10】本発明における半導体装置の製造方法の第7の実施形態を示す概略工程断面図 である。

- 【図11】従来の半導体装置の製造方法を示す概略工程断面図である。

- 【図12】従来の半導体装置の製造方法を示す概略工程断面図である。

# 【符号の説明】

- 11 シリコン基板(半導体基板)

- 12 トレンチ素子分離層

- 13、21 ゲート絶縁膜

- 14、14a、33、33a ダミーゲートパターン

- 1 5 a n 型拡散領域

- 1 5 b n <sup>+</sup>型拡散領域

- 16 サイドウォール絶縁膜

- 17、38 ダミーコンタクトパターン

- 18 層間絶縁膜

- 19、36 ゲート電極

- 20、29 コンタクトプラグ

- 22 層間絶縁膜

- 23、26、28 レジストパターン

- 2 4 コンタクト孔

- 25、37 溝

- 2 7 配線

- 32 ポリシリコン膜

- 3 5 A l 膜

- 3 8 a シリコン窒化膜

- 3 9 シリコン酸化膜

10

20

【図1】

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

【図7】

【図8】

# 【図9】

# 【図10】

# 【図11】

# 【図12】

# フロントページの続き

# (56)参考文献 特開平11-238885(JP,A)特開平11-177089(JP,A)特開平11-177089(JP,A)特開平11-026757(JP,A)特開平08-335701(JP,A)特開平06-053237(JP,A) 特開昭63-031122(WO,A1)特開昭61-161721(JP,A)

# (58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 29/78

H01L 21/336

H01L 21/28

H01L 21/768

H01L 21/3205

H01L 21/3213