(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-500759

(P2006-500759A)

(43) 公表日 平成18年1月5日(2006.1.5)

| (51) Int.C1.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>HO1L 21/768 (2006.01)</b>  | HO1L 21/90 | C 4M104     |

| <b>HO1L 21/28 (2006.01)</b>   | HO1L 21/28 | K 5FO33     |

| <b>HO1L 21/8234 (2006.01)</b> | HO1L 27/08 | 1O2D 5FO48  |

| <b>HO1L 27/088 (2006.01)</b>  | HO1L 27/08 | 321F        |

| <b>HO1L 21/8238 (2006.01)</b> |            |             |

審査請求 有 予備審査請求 有 (全 13 頁) 最終頁に続く

|               |                              |            |                                                                                                       |

|---------------|------------------------------|------------|-------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2003-539091 (P2003-539091) | (71) 出願人   | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国テキサス州 78729, オ<br>ースティン, ウエスト・パーマー・レーン<br>7700 |

| (86) (22) 出願日 | 平成14年9月27日 (2002.9.27)       | (74) 代理人   | 100116322<br>弁理士 桑垣 衛                                                                                 |

| (85) 翻訳文提出日   | 平成16年5月28日 (2004.5.28)       | (72) 発明者   | リーバー、ダグラス エム.<br>アメリカ合衆国 78727 テキサス州<br>オースティン トゥループス トレイル<br>13114                                   |

| (86) 國際出願番号   | PCT/US2002/030337            | F ターム (参考) | 4M104 BB01 DD82 DD90 FF30 GG09<br>GG10 GG14                                                           |

| (87) 國際公開番号   | W02003/036702                |            |                                                                                                       |

| (87) 國際公開日    | 平成15年5月1日 (2003.5.1)         |            |                                                                                                       |

| (31) 優先権主張番号  | 09/986,232                   |            |                                                                                                       |

| (32) 優先日      | 平成13年10月22日 (2001.10.22)     |            |                                                                                                       |

| (33) 優先権主張国   | 米国(US)                       |            |                                                                                                       |

最終頁に続く

(54) 【発明の名称】基板への相互接続を有する集積回路およびその製造方法

## (57) 【要約】

ソース/ドレイン(20)とゲート(26)との間の接点(32)が、ゲート誘電体(46)の選択部分(35)へ埋設物を注入することによりゲート誘電体(46)の選択部分(35)を導電性にすることで行われる。ゲート材料は集積回路全体(10)の上の層に位置する。ゲート(26)がソース/ドレイン(20)に接続する領域(32)が識別され、この識別位置(35)においてゲート誘電体(46)が導電性となるよう埋設物が注入される。ソース/ドレイン(20)が導電性ゲート誘電体(35)のそのような導電性領域の下を延び、該位置で埋設物が注入されたゲート誘電体(35)がゲート(26)をソース/ドレイン(20)に短絡するようになり、ソース/ドレイン(20)は形成される。これによって集積回路(10)上のスペースが節約され、相互接続層の必要性が低減され、露出したシリコン基板上にポリシリコンを堆積およびエッチングさせることに付随する問題を回避することができる。

## 【特許請求の範囲】

## 【請求項 1】

電気接点を形成する方法であって、

半導体基板を提供するステップと、

前記半導体基板上に誘電体層を形成するステップと、

前記誘電体層上に導電層を形成するステップと、

導電性ドープ誘電体を形成するために、前記誘電体層の第1の部分に第1の種を注入するステップと、

パターン化した誘電体層を形成するために、前記誘電体層をパターン化するステップであって、前記パターン化した誘電体層が、前記導電性ドープ誘電体を備えるステップと、

パターン化された導電層を形成するために、前記導電層をパターン化するステップであって、前記パターン化された導電層の一部が前記導電性ドープ誘電体と電気的に接触するステップとを含む方法。 10

## 【請求項 2】

前記誘電体層の第1の部分に第1の種を注入するステップが、

前記導電層上にパターン化したフォトレジスト層を形成するステップと、

前記導電層を通して埋設物を注入するステップとを含む、請求項1に記載の方法。

## 【請求項 3】

前記第1の種を前記第1の部分に注入する間に、ドープ基板領域を形成するために、前記導電性ドープ誘電体の下で、前記半導体基板のある領域に前記第1の種を注入するステップと、 20

前記導電層をパターン化する時に、第1のゲート電極を形成するステップと、

前記第1のゲート電極に隣接して、前記半導体基板内に第1の導電領域を形成するステップと、

前記第1のゲート電極に隣接して、前記半導体基板内に第2の導電領域を形成するステップであって、前記第2の導電領域の一部が、前記ドープ基板領域の一部と重なるステップとをさらに含む、請求項1に記載の方法。 25

## 【請求項 4】

前記第2の導電領域を形成するステップが、さらに、前記第2の導電領域に前記第1の種を注入するステップを含む、請求項3に記載の方法。 30

## 【請求項 5】

前記第2の導電領域を形成するステップが、さらに、前記第2の導電領域に前記第2の種を注入するステップを含み、前記第2の種が、前記第1の種とは異なる導電性を有する、請求項3に記載の方法。

## 【請求項 6】

半導体デバイスであって、

第1のトランジスタと、

第2のトランジスタとを備え、

前記第1のトランジスタが、

前記第1のゲート誘電体上に形成された第1のゲート電極と、

基板内に前記第1のゲート誘電体に隣接して形成された第1の導電領域と、 40

前記基板内に前記第1のゲート誘電体に隣接して形成された第2の導電領域と、

前記基板上に形成された第1のゲート誘電体とを備え、

前記第2のトランジスタが、

前記第1のゲート誘電体上に形成された第2のゲート電極と、

前記基板内に前記第2のゲート誘電体に隣接して形成された第3の導電領域と、

前記基板内に前記第2のゲート誘電体に隣接して形成された第4の導電領域と、

前記基板上に形成された第2のゲート誘電体とを備え、

前記第2のゲート電極が導電層の一部であり、

前記導電層が、導電性ドープ誘電体に電気的に接触し、 50

前記導電性ドープ誘電体が、前記第1の導電領域に電気的に接続するデバイス。

【請求項7】

前記導電層の一部が、前記導電性ドープ誘電体上に位置する、請求項6に記載のデバイス。

【請求項8】

前記第1の導電領域が、前記第3および第4の導電領域から電気的に分離される、請求項6に記載のデバイス。

【請求項9】

前記導電性ドープ誘電体が、高濃度にドープされた酸化物層である、請求項6に記載の半導体デバイス。

【請求項10】

前記導電性ドープ誘電体が二酸化シリコンであり、リン、ホウ素、アルミニウム、ガリウム、ゲルマニウム、インジウム、ヒ素、タンゲステンおよびシリコンからなるグループから選択した元素によりドープされる、請求項9に記載のデバイス。

【請求項11】

前記第1のトランジスタがn型井戸内にあり、前記第2のトランジスタがp型井戸内にある、請求項6に記載のデバイス。

【請求項12】

前記導電性ドープ誘電体の下に、前記半導体基板のドープ領域をさらに備え、前記導電性ドープ誘電体および前記ドープ領域が第1の導電性を有する種でドープされ、前記ドープ領域が前記第1の導電領域に重なる、請求項6に記載のデバイス。

【請求項13】

前記第1の導電領域が、前記ドープ領域とは異なる導電性にドープされる、請求項12に記載のデバイス。

【請求項14】

前記第1の導電性がp型である、請求項12に記載のデバイス。

【請求項15】

前記第1の導電性がn型である、請求項12に記載のデバイス。

【請求項16】

前記第1の導電領域が、前記ドープ領域より高濃度にドープされる、請求項12に記載のデバイス。

【請求項17】

半導体デバイスであって、

第1の能動領域と、

第2の能動領域と、

前記能動領域の第1の部分上の第1の誘電体層と、

前記第1の誘電体層上の第1の導電層と、

前記第2の能動領域上の第2の誘電体層と、

前記第2の誘電体層上の第2の導電層の第1の部分と、

前記第1の能動領域の第2の部分上の導電性ドープ誘電体と、

前記導電性ドープ誘電体と前記第1の能動領域上の、前記第2の導電層の第2の部分とを備えるデバイス。

【請求項18】

前記第1の誘電体層および前記第1の導電層に隣接している導電領域に、第3の誘電体層が電気的に接続する、請求項17に記載のデバイス。

【請求項19】

前記導電領域がソース／ドレイン領域である、請求項17に記載のデバイス。

【請求項20】

前記導電性ドープ誘電体が二酸化シリコンであり、ドーパントが、リン、ホウ素、アルミニウム、ガリウム、ゲルマニウム、インジウム、ヒ素、タンゲステンおよびシリコンか

10

20

30

40

50

らなるグループから選択される、請求項 1 7 に記載のデバイス。

【請求項 2 1】

サリサイドが前記第 1 および第 2 の導電層上に形成される、請求項 1 7 に記載のデバイス。

【請求項 2 2】

集積回路であって、

第 1 の井戸領域を有する基板と、

前記第 1 の井戸領域内の第 1 のソース / ドレイン領域と第 2 のソース / ドレイン領域とを有する前記第 1 の井戸領域内に形成されたトランジスタと、

前記第 1 のソース / ドレイン領域上を延び、導電性の埋設物が注入された誘電体によって前記第 1 のソース / ドレインから物理的に分離されている導電性電極を有する回路フィーチャとを備え、

前記導電性の埋設物注入誘電体が、前記導電性電極を前記第 1 のソース / ドレイン領域に電気的に短絡する、集積回路。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、集積回路に関し、特に相互接続と基板間の接触の形成に関する。

【背景技術】

【0 0 0 2】

集積回路は、相互接続層により相互に接続している能動領域内に形成されたトランジスタを備える。通常、これらの相互接続層は、基板上の複数の層内に形成されるポリシリコンまたは金属である。能動領域は基板自体に形成される。集積回路内で通常必要とされる比較的簡単な接続は、他のトランジスタのゲートに接続している 1 つのトランジスタのソース / ドレインである。通常、このような接続は、ゲート上に位置する層からの接続を行う相互接続層を提供することにより行われる。そうするためには、集積回路上にスペースが必要であり、このスペースは集積回路全体の大きさのうちの 1 つの要因である。今まで使用されてきたもう 1 つのタイプの接続は埋設接觸として知られており、埋設接觸では、典型的なゲート材料であるポリシリコンが、ソース / ドレインとゲートとの間の接觸を行うために、基板に直接接觸する。

【0 0 0 3】

埋設接觸に関連する難点および問題のうちの 1 つは、基板が、基板と接觸していたポリシリコンと直接隣接する領域またはポリシリコンの縁部の領域で過度にエッティングされるという傾向があることである。このような過度のエッティングの原因是、基板への開口部、すなわちソース / ドレインへの開口部を、ポリシリコンを堆積する前に形成しなければならないからである。それ故、接觸のために使用されるポリシリコンのエッティングは、基板を過度にエッティングするという問題を生じさせる恐れがある。

【0 0 0 4】

それ故、上のレベルの相互接続のスペースと同じスペースを必要とせず、埋設接觸に付随する問題を有さない接觸が切望されている。

【発明を実施するための最良の形態】

【0 0 0 5】

ゲートへのドレインの標準的な接続は、基板内に形成されたソース / ドレインと他のトランジスタのゲートとの間を接続するために、ゲート誘電体材料内へ埋設物を注入することにより行われる。ゲート材料と基板、すなわちソース / ドレインとの間の接続は、その領域内のゲート材料に埋設物を注入することにより行われ、その結果、ゲート誘電体はその位置で導電性になる。図面を参照しながら下記の説明を読めば、このことをより深く理解することができるだろう。

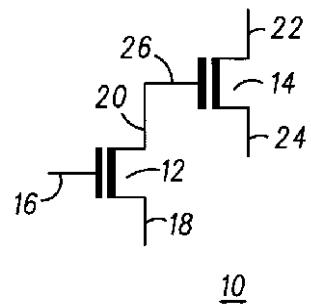

【0 0 0 6】

図 1 は、従来技術では周知の、集積回路内のごく普通の回路 1 0 であるが、従来技術の

10

20

30

40

50

回路とは異なる方法で、異なる構成に形成されている回路 10 である。回路 10 は、トランジスタ 12 およびトランジスタ 14 を備える。トランジスタ 12 は、ゲート 16、ソース／ドレイン 18、およびソース／ドレイン 20 を有する。本明細書で使用する場合、ソース／ドレインは、所与の回路での使用方法によりソースであってもドレインであってもよい、ゲートに隣接するドープ領域である。トランジスタ 14 は、ソース／ドレイン 22 およびソース／ドレイン 24 を有する。ソース／ドレイン 18、22 および 24 は、図では接続していないが、完成した回路においては、他の回路または電源端末に接続する。同様に、ゲート 16 も、他の回路または基準または信号に接続する。ソース／ドレイン 20 は、トランジスタ 14 のゲート 26 に接続する。ソース／ドレインからゲートへの接続は、集積回路においてはごく普通のものである。

10

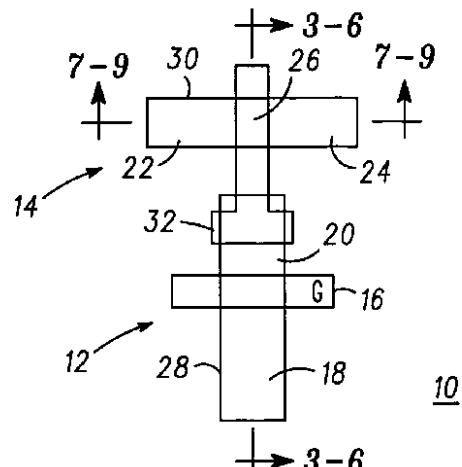

## 【0007】

図 2 は、本発明の 1 実施形態による配置図における回路 10 である。回路 10 は、能動領域 28 および能動領域 30 を備える。能動領域 28 は、トランジスタ 12 を形成するためのものであり、能動領域 30 は、トランジスタ 14 を形成するためのものである。ゲート 26 は、能動領域 30 の上に位置しており、接点 32 のところでトランジスタ 14 のソース／ドレイン領域 20 と接続している。能動領域 28 は、その上に位置するゲート 16 を有すると共に、ソース／ドレイン領域 18 および 20 を含む。能動領域 30 はソース／ドレイン領域 22 および 24 を含む。接点 32 は、その領域の少なくとも一部に埋設物を注入することにより形成され、そのため、ゲート誘電体材料はその領域において導電性になる。それ故、能動領域 18 の上を延びるゲート 26 は、接点 32 を通してドレイン 20 と接触する。

20

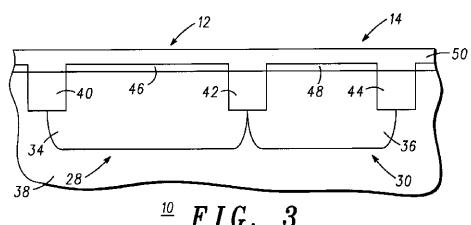

## 【0008】

図 3 は、処理の比較的初期の段階でのトランジスタ 12 および 14 を示す断面図である。処理のこの段階は従来のものである。回路 10 は、P 型井戸 34 および N 型井戸 36 を有する P 型である基板 38 を備える。基板 38 は、図では、P 型井戸 34 および N 型井戸 36 の上の導電性材料 50 と、上に位置するゲート誘電体材料 46 および 48 とを有するものとして示されている。P 型井戸 34 は、分離領域 40 および 42 の間に位置する。N 型井戸 36 は、図 3 に示すように、分離領域 42 および 44 の間に位置する。図 3 の場合、分離領域 40 と 42 との間にゲート誘電体材料 46 が位置しており、分離領域 42 と 44 との間にゲート誘電体材料 48 が位置している。ゲート誘電体材料 46 および 48 の上には、ポリシリコン層 50 が位置している。基板 38 は、また、絶縁体上シリコン (SOI) であってもよく、その場合、絶縁体上に半導体層が位置する。井戸 34 および 36 は半導体層内に位置し、分離領域 40、42 および 44 は絶縁体へと延びる。

30

## 【0009】

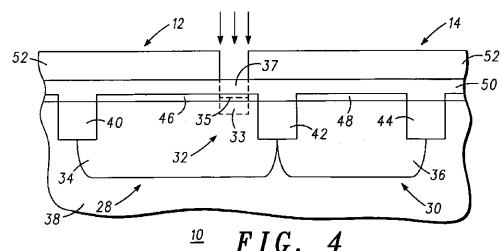

図 4 は、能動領域 28 内の接点 32 のための位置のところに開口部ができるようにフォトレジスト 52 を堆積し、パターン化した後の回路 10 である。この図は、誘電体材料 46 の接触領域 32 のところに、その中心深さを有する埋設物を示す。その結果、P 型井戸 34 内のドープ領域 33、埋設物が注入されたゲート誘電体 35、および埋設物が注入されたポリシリコン領域 37 ができる。効果的なドーパント材料としては、誘電体材料 46 を接点 32 のところで高度に導電性にするためのホウ素がある。ゲート誘電体材料としては、他の材料を使用することができ、ポリシリコンの代わりに、他の材料でゲート電極を形成することができる。そのような場合には、ゲート誘電体材料と上に位置するゲート材料との間に必要な導通および短絡を形成するために、ホウ素以外の異なるドーパント材料を提供することが望ましい。そのようなドーパントの 1 つとしてアルミニウムがあり、他のドーパントとしてはリンがある。P 型井戸に埋設物を注入した場合、N 型の導電性にするリンを使用するのが有利であり得る。酸化シリコン以外のゲート誘電体材料としては、酸化ハフニウムがある。他の材料も同様に選択することができる。それ故、短絡を形成する前にポリシリコンをエッチングしなくても、ポリシリコンに短絡が形成される。従来の埋設接触の場合には、接触のための井戸または領域を開き、その後ポリシリコンを堆積する必要があった。以降のエッチングは、シーケンスの点で面倒であったばかりでなく、基

40

50

板を露出した後で、ポリシリコンをエッチングする領域に隣接して、基板の過度にエッチングされた領域を形成する恐れがあった。

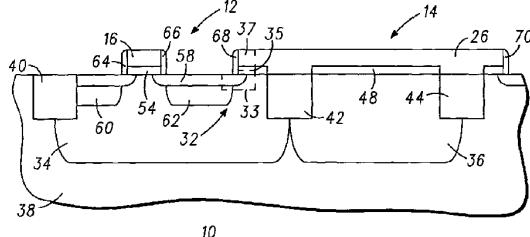

【0010】

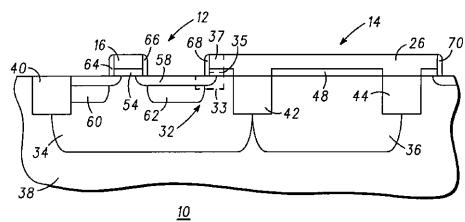

図5は、ゲート誘電体材料46で形成されたゲート誘電体54上にゲート16を残すようにパターン化エッチングした後のポリシリコン50およびゲート材料46を示す。また、ソース／ドレイン延長部56およびソース／ドレイン延長部58は、ゲート16をマスクとして使用することにより形成される。ソース／ドレイン延長部56および58は、ヒ素およびリンの組み合わせを注入することにより形成されたN型のものである。埋設物を注入するためのこの特定の種および種の組み合わせは、必要に応じて変えることができる。また、接触領域32に延びるゲート26が残る。それ故、ゲート26は、埋設物を注入されたゲート誘電体材料の領域上に位置する。埋設物を注入されたゲート誘電体の一部は、ゲート26とドレイン20との間に最終的に接点を形成する部分であるので、この埋設物を注入されたゲート材料のうちの一部は、ポリシリコン50をエッチングした後でも残っていなければならない。延長部56および58の前に、ホウ素およびインジウム・ハロの組み合わせの埋設物を有することが望ましい場合があるが、このハロ埋設物は図示していない。何故なら、ハロ埋設物は、当業者にとって周知のものなので、図面が不必要にわかりにくくなるのを避けるためである。

【0011】

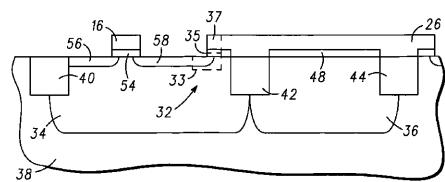

図6は、高濃度にドープしたソース／ドレイン領域60および62を形成するために側壁を形成し、ヒ素とリンの埋設物を組み合わせた後の回路10である。ゲート16は、側壁スペーサ64および66を有する。ゲート26は、側壁スペーサ68および70を有する。この図は、Nチャネル型の完成したトランジスタ12、およびPチャネル型の完成したトランジスタ14を示す。ゲート26は、接点32のところでドレイン20に接続している。ドレイン20は、高濃度にドープされた領域62および延長領域58からなる。接触領域32にリンが注入されると、接触領域は、図6に示すように、ソース／ドレイン延長部58を越えて延びることができる。しかし、接触領域32がP型領域を形成するホウ素でドープされた場合には、接触領域32は、ソース／ドレイン延長部分58を越えて横方向に延びてはならない。ゲート誘電体材料のドープ領域は導電性で、そのため、その下のドープ領域と接触する。このドープされたゲート誘電体が、ソース／ドレインとだけ接触するのであれば、ドレイン20へとゲート26を短絡するが、井戸34へは短絡しない。ゲート誘電体のドープした部分が、ドレイン20を越えて横方向に延びると、上記ドープした部分は、井戸34に対向する導電型のドープした領域と接触しなければならないし、それ故、図6に示すゲート誘電体の埋設物は、N型の領域を形成しなければならない。

【0012】

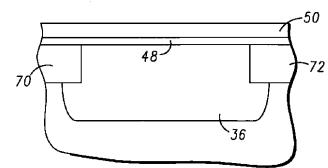

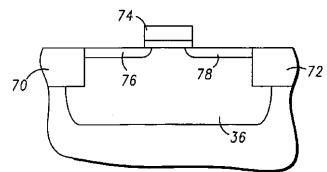

図7は、図3の段階と同じ処理段階のトランジスタ14を示す。この断面図では、図7は、N型井戸36および分離領域70および72、ならびにゲート誘電体材料48を示す。

【0013】

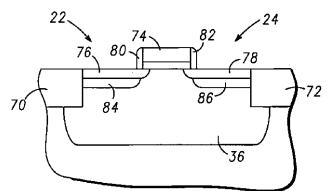

図8は、ゲート74およびソース／ドレイン領域延長部76および78を形成するため、ポリシリコン50がエッチングされた後のトランジスタ14である。これらの延長部は、図5の方法に類似の方法であるが、異なるプロセスステップで形成される。何故なら、トランジスタ12およびトランジスタ14に対するドーピングの種類が異なっているからである。これらのソース／ドレイン延長部は、ヒ素およびホウ素の組み合わせを使用して埋設物の注入により形成される。図8のために必要なステップは、図5のステップの前または後のどちらに行ってもよい。

【0014】

図9は、ホウ素の組み合わせにより形成されたソース／ドレイン領域22およびソース／ドレイン領域24の形成を完了するため、高濃度にドープされたソース／ドレイン領域84および86を形成するためのマスクを提供する、側壁スペーサ80および82を形成した後の完成したトランジスタ14である。

10

20

30

40

50

## 【0015】

それ故、断面図3～6および断面図7～9に示すように、完成した回路10は、完成したトランジスタ12と、トランジスタ12のドレインがトランジスタ14のゲートに接続している完成したトランジスタ14とを示す。この場合、接触を行うためにソース／ドレイン上に導電性材料を塗布する必要がない。こうすることにより、埋設接触に付随する問題を回避することができ、あるトランジスタのドレインと他のトランジスタのゲートとの間に、非常にコンパクトな相互接続を提供することができる。このことは、もっと高いレベルの相互接続の必要性を低減する効果があり、そのため処理の複雑さおよび欠陥が発生する機会を低減する効果がある。それ故、面積が狭くなり、チップ面積全体が小さくなり、プロセスを複雑にしないでコストを下げる機会が提供される。

10

## 【0016】

また、抵抗のようなトランジスタ以外の回路フィーチャによっても、類似の利点を達成することができる。もう1つの回路フィーチャは、ソース／ドレイン上を延び、図4、図5および図6の領域35のような導電性の埋設物を注入した誘電体により、ソース／ドレインへの電気接触を行う、ポリシリコンゲート26のような電極を有することができる。

## 【0017】

効果、他の利点および課題解決策を、特定の実施形態に関して上述した。しかしながら、任意の効果、利点または解決策を生じさせ得るかそれ自体より顕著になり得る、そのような効果、利点、課題解決策は、任意またはすべての請求項の重要な、必要な、または必須の特徴もしくは要素と解釈すべきではない。本明細書で使用する場合、用語「～成る、含む、備える（comprise）」やその変形は、非排他的な包含物をその範囲内に入れるものとし、ある要素のリストを含むプロセス、方法、物、または装置は、その要素のみを含むわけではなく、明示的に列挙されていない他の要素やそのようなプロセス、方法、物、または装置に固有の要素を含みうる。

20

## 【図面の簡単な説明】

## 【0018】

【図1】従来技術の周知の回路の回路図。

【図2】本発明のある実施形態により製造された図1の回路の平面図。

【図3】図2の回路の一部を処理する際の逐次的な断面図。

30

【図4】図2の回路の一部を処理する際の逐次的な断面図。

【図5】図2の回路の一部を処理する際の逐次的な断面図。

【図6】図2の回路の一部を処理する際の逐次的な断面図。

【図7】図2の回路の他の一部を処理する際の逐次的な断面図。

【図8】図2の回路の他の一部を処理する際の逐次的な断面図。

【図9】図2の回路の他の一部を処理する際の逐次的な断面図。

【図1】

-PRIOR ART-

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図6】

FIG. 6

【図5】

FIG. 5

【図7】

FIG. 7

【図8】

14 FIG. 8

【図9】

14 FIG. 9

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                 |                |

|-----------------|----------------|

| Interns         | Application No |

| PCT/US 02/30337 |                |

|                                     |

|-------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER |

| IPC 7 H01L21/285 H01L21/768         |

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                              | Relevant to claim No. |

|------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X          | EP 0 342 778 A (NORTHERN TELECOM LTD)<br>23 November 1989 (1989-11-23)<br>column 5, line 51 -column 7, line 4;<br>figures 4,6,7 | 6,8-11                |

| A          | ---                                                                                                                             | 1-5,7,<br>12-22       |

| X          | US 5 087 589 A (CHAPMAN GLENN H ET AL)<br>11 February 1992 (1992-02-11)<br>the whole document                                   | 17,19,<br>20,22       |

| A          | ---                                                                                                                             | 1-16                  |

| X          | US 6 262 486 B1 (FARRAR PAUL A)<br>17 July 2001 (2001-07-17)<br>the whole document                                              | 22                    |

| A          | ---                                                                                                                             | 1-21                  |

|            | ---                                                                                                                             | ---                   |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

|                                                           |                                                    |

|-----------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search | Date of mailing of the international search report |

|-----------------------------------------------------------|----------------------------------------------------|

4 June 2003

13/06/2003

|                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Name and mailing address of the ISA                                                                                                             |

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016 |

Authorized officer

Ploner, G

## INTERNATIONAL SEARCH REPORT

|                 |                |

|-----------------|----------------|

| Internal        | Application No |

| PCT/US 02/30337 |                |

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                        |                       |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                     | Relevant to claim No. |

| A                                                    | OKUMURA T ET AL: "A SiO <sub>x</sub> resistor load<br>SRAM process for ASIC applications"<br>PROCEEDINGS OF THE IEEE CUSTOM INTEGRATED<br>CIRCUITS CONFERENCE,<br>16 - 19 May 1988, pages 25.6.1-25.6.4,<br>XP010075765<br>the whole document<br>----- | 1-5                   |

Form PCT/ISA/210 (continuation of second sheet) (July 1992)

## INTERNATIONAL SEARCH REPORT

Internal Application No

PCT/US 02/30337

| Patent document cited in search report |    | Publication date |                                              | Patent family member(s)                                                                                 |  | Publication date                                                                                             |

|----------------------------------------|----|------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--------------------------------------------------------------------------------------------------------------|

| EP 0342778                             | A  | 23-11-1989       | CA<br>US<br>EP<br>JP                         | 1276314 A1<br>4868618 A<br>0342778 A1<br>2010775 A                                                      |  | 13-11-1990<br>19-09-1989<br>23-11-1989<br>16-01-1990                                                         |

| US 5087589                             | A  | 11-02-1992       | US<br>JP<br>AT<br>CA<br>DE<br>EP<br>JP<br>WO | 4843034 A<br>3224234 A<br>112100 T<br>1286795 A1<br>3851612 D1<br>0319575 A1<br>2504092 T<br>8810008 A1 |  | 27-06-1989<br>03-10-1991<br>15-10-1994<br>23-07-1991<br>27-10-1994<br>14-06-1989<br>22-11-1990<br>15-12-1988 |

| US 6262486                             | B1 | 17-07-2001       | US<br>US<br>US                               | 6017829 A<br>2001045659 A1<br>6432844 B1                                                                |  | 25-01-2000<br>29-11-2001<br>13-08-2002                                                                       |

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

**H 0 1 L 27/092 (2006.01)**

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT, BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW, ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES, FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,N O,NZ,OM,PH,PL,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

F ターム(参考) 5F033 JJ01 LL02 LL04 QQ08 QQ09 QQ58 QQ59 QQ60 QQ68 RR04

5F048 AC01 AC03 BA01 BA16 BB05 BC06 BE03 BF01 BF02 BF03

BF15 BF16 BG13 DA23