(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5563257号

(P5563257)

(45) 発行日 平成26年7月30日(2014.7.30)

(24) 登録日 平成26年6月20日(2014.6.20)

(51) Int.Cl.

H01L 27/14 (2006.01)

H01L 31/10 (2006.01)

F 1

H01L 27/14

H01L 31/10D

G

請求項の数 10 (全 14 頁)

(21) 出願番号 特願2009-199017 (P2009-199017)

(22) 出願日 平成21年8月28日 (2009.8.28)

(65) 公開番号 特開2011-49503 (P2011-49503A)

(43) 公開日 平成23年3月10日 (2011.3.10)

審査請求日 平成24年7月25日 (2012.7.25)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】光電変換装置、撮像システム、及び光電変換装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部をそれぞれ含む複数の画素が配列された画素配列領域と前記画素配列領域の周辺に配された周辺領域とを有する光電変換装置であって、

半導体基板の上に配され、前記画素配列領域の配線層の数よりも前記周辺領域の配線層の数が多い多層配線構造と、

前記画素配列領域における前記多層配線構造の上に配された複数の層内レンズと、を備え、

前記複数の層内レンズのそれぞれは、

前記半導体基板の表面から離れる方向へ膨出した曲面を含む上面を有する第1の絶縁体と、

10

前記第1の絶縁体の上に配され、前記第1の絶縁体より高い屈折率を有し、前記第1の絶縁体の前記曲面に沿った曲面を含む上面を有する第2の絶縁体と、を含み、

前記複数の層内レンズのそれぞれにおける前記第1の絶縁体と、前記多層配線構造における前記周辺領域の層間絶縁膜とは、同じ材料で形成されていることを特徴とする光電変換装置。

## 【請求項 2】

前記複数の層内レンズのそれぞれにおける前記第1の絶縁体と、前記多層配線構造における前記周辺領域の層間絶縁膜とは、シリコン酸化物からなる

ことを特徴とする請求項1に記載の光電変換装置。

20

## 【請求項 3】

前記第1の絶縁体は、前記光電変換部の上方に設けられていることを特徴とする請求項1又は2に記載の光電変換装置。

## 【請求項 4】

前記第2の絶縁体は、前記第1の絶縁体の前記曲面の全体を覆っていることを特徴とする請求項1から3のいずれか1項に記載の光電変換装置。

## 【請求項 5】

光電変換部をそれぞれ含む複数の画素が配列された画素配列領域と前記画素配列領域の周辺に配された周辺領域とを有する光電変換装置であって、

半導体基板の上に配され、前記画素配列領域の配線層の数よりも前記周辺領域の配線層の数が多い多層配線構造と、

前記画素配列領域における前記多層配線構造の上に配された複数の層内レンズと、を備え、

前記複数の層内レンズのそれぞれは、

前記半導体基板の表面に垂直な面に沿った断面が矩形の第1の絶縁体と、

前記第1の絶縁体の上に配され、前記第1の絶縁体より高い屈折率を有し、前記断面が矩形の前記第1の絶縁体の側面および上面にそれぞれ沿った側面および上面を有する第2の絶縁体と、を含み、

前記複数の層内レンズのそれぞれにおける前記第1の絶縁体と、前記多層配線構造における前記周辺領域の層間絶縁膜とは、同じ材料で形成されていることを特徴とする光電変換装置。

## 【請求項 6】

前記画素配列領域における最上の配線層と前記周辺領域における最上の配線層とを覆う保護膜をさらに備え、

前記第2の絶縁体と前記保護膜とは、同じ材料で形成されている

ことを特徴とする請求項1から5のいずれか1項に記載の光電変換装置。

## 【請求項 7】

前記第2の絶縁体と前記保護膜とは、シリコン窒化物からなることを特徴とする請求項6に記載の光電変換装置。

## 【請求項 8】

前記複数の層内レンズのそれぞれは、前記第1の絶縁体と前記第2の絶縁体との間に反射抑制膜をさらに含む

ことを特徴とする請求項1から7のいずれか1項に記載の光電変換装置。

## 【請求項 9】

請求項1から8のいずれか1項に記載の光電変換装置と、

前記光電変換装置の撮像面へ像を形成する光学系と、

前記光電変換装置から出力された信号を処理して画像データを生成する信号処理部と、を備えたことを特徴とする撮像システム。

## 【請求項 10】

光電変換部をそれぞれ含む複数の画素が配列された画素配列領域と前記画素配列領域の周辺に配された周辺領域とを有する光電変換装置の製造方法であって、

半導体基板の上方における前記画素配列領域及び前記周辺領域に絶縁層を形成する第1の工程と、

前記絶縁層をパターニングすることにより、前記画素配列領域における第1の絶縁体と、多層配線構造における前記周辺領域の最上の層間絶縁膜とを形成する第2の工程と、

前記第1の絶縁体の上に、前記第1の絶縁体より高い屈折率を有した材料で第2の絶縁体を形成する第3の工程と、を含み、

前記第2の工程で形成される前記第1の絶縁体は、前記半導体基板の表面から離れる方向へ膨出した曲面を含む上面を有し、

前記第3の工程で形成される前記第2の絶縁体は、前記第1の絶縁体の前記曲面に沿った

10

20

30

40

50

曲面を含む上面を有し、

前記第1の絶縁体および前記第2の絶縁体によって層内レンズが構成される

ことを特徴とする光電変換装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置、撮像システム、及び光電変換装置の製造方法に関する。

【背景技術】

【0002】

近年、光電変換装置としてMOSトランジスタを用いたMOS型光電変換装置が盛んに開発されている。そのような光電変換装置において多画素化にともなう画素寸法の縮小化が進んでいる。画素寸法の縮小化が進むと、配線層の開口面積や各画素における光電変換部（例えば、フォトダイオード）の受光面の面積が小さくなるため、光電変換部の感度が低下する可能性がある。光電変換部の感度の低下を抑制するため、光電変換部とオンチップレンズとの間にさらにレンズとして機能する層内レンズを形成することがある。また、配線層の膜厚はプロセスルールに制限されるため、受光面における配線層の開口のアスペクト比が高くなってしまう。

特許文献1には、光電変換部の層間膜の膜厚を周辺回路部の保護膜を含む層間膜の膜厚より薄く形成して、受光部とオンチップレンズとの距離を短くすることで、オンチップレンズの集光効率を向上させる構成が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000-150846号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

一方、特許文献1には、層内レンズの製造方法については検討されていない。

【0005】

本発明の目的は、複数の層内レンズと多層配線構造とを少ない工程で製造することに適した光電変換装置を提供することにある。

【課題を解決するための手段】

【0006】

本発明の1つの側面に係る光電変換装置は、光電変換部をそれぞれ含む複数の画素が配列された画素配列領域と前記画素配列領域の周辺に配された周辺領域とを有する光電変換装置であって、半導体基板の上に配され、前記画素配列領域の配線層の数よりも前記周辺領域の配線層の数が多い多層配線構造と、前記画素配列領域における前記多層配線構造の上に配された複数の層内レンズと、を備え、前記複数の層内レンズのそれぞれは、前記半導体基板の表面から離れる方向へ膨出した曲面を含む上面を有する第1の絶縁体と、前記第1の絶縁体の上に配され、前記第1の絶縁体より高い屈折率を有し、前記第1の絶縁体の前記曲面に沿った曲面を含む上面を有する第2の絶縁体と、を含み、前記複数の層内レンズのそれぞれにおける前記第1の絶縁体と、前記多層配線構造における前記周辺領域の層間絶縁膜とは、同じ材料で形成されていることを特徴とする。

【発明の効果】

【0007】

本発明によれば、複数の層内レンズと多層配線構造とを少ない工程で製造することに適した光電変換装置を提供することができる。

【図面の簡単な説明】

【0008】

【図1】実施形態に係る光電変換装置の構成を示す図。

10

20

30

40

50

【図2】実施形態に係る光電変換装置の断面構成を示す図。

【図3】実施形態に係る光電変換装置の製造方法を示す図。

【図4】実施形態の変形例に係る光電変換装置の断面構成を示す図。

【図5】実施形態の変形例に係る光電変換装置の断面構成を示す図。

【図6】実施形態に係る光電変換装置を適用した撮像システムの構成図。

【発明を実施するための形態】

【0009】

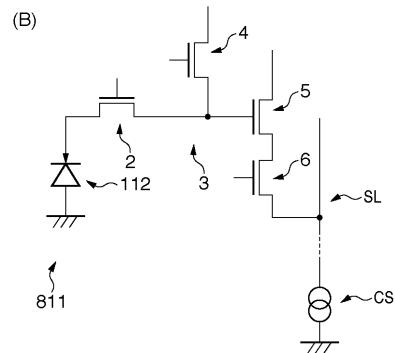

実施形態に係る光電変換装置800の概略構成を、図1を用いて説明する。図1(A)は、光電変換装置800の構成を示す図である。図1(B)は、画素811の構成を示す図である。光電変換装置800は、画素配列領域PARと周辺領域PPRとを有する。画素配列領域PARには、画素配列PAが配されている。周辺領域PPRには、画素配列PAを制御するための回路が配されている。画素配列PAを制御するための回路は、例えば、垂直走査回路813、信号処理回路812、及び水平走査回路814を含む。

10

【0010】

具体的には、画素配列PAでは、複数の画素811が2次元的に(行に沿った方向及び列に沿った方向に)配列されている。図1(A)には、3行3列の画素811で画素配列PAが構成された場合が例示的に示されている。なお、画素配列PAでは、複数の画素811が1次元的に配列されていて良い。また、画素とは、1つの光電変換部で発生した信号を読み出すための構成要素の集まりの単位を示すものとする。隣接する光電変換部において、画素の構成要素を共有することも可能であるが、この場合にも1つの光電変換部の信号を読み出すための構成要素の集まりの単位を画素と呼ぶこととする。

20

【0011】

画素配列PAにおける各画素811は、図1(B)に示すように、光電変換部112、転送部2、電荷電圧変換部3、リセット部4、出力部5、及び選択部6を含む。光電変換部112は、受けた光に応じた電荷を発生させる。光電変換部112は、例えば、フォトダイオードである。転送部2は、光電変換部112で発生した電荷を電荷電圧変換部3へ転送する。転送部2は、例えば、転送トランジスタであり、後述の垂直走査回路813からアクティブルレベルの転送制御信号をゲートに受けた際にオンすることにより、光電変換部112で発生した電荷を電荷電圧変換部3へ転送する。電荷電圧変換部3は、転送された電荷を電圧に変換する。電荷電圧変換部3は、例えば、フローティングディフュージョンである。リセット部4は、電荷電圧変換部3をリセットする。リセット部4は、例えば、リセットトランジスタであり、垂直走査回路813からアクティブルレベルのリセット制御信号をゲートに受けた際にオンすることにより、電荷電圧変換部3をリセットする。出力部5は、電荷電圧変換部3の電圧に応じた信号を信号線SLへ出力する。出力部5は、例えば、增幅トランジスタであり、信号線SLに接続された電流源負荷CSとともにソースフォロワ動作を行うことにより、電荷電圧変換部3の電圧に応じた信号を信号線SLへ出力する。すなわち、出力部5は、リセット部4により電荷電圧変換部3がリセットされた状態で、電荷電圧変換部3の電圧に応じたノイズ信号を信号線SLへ出力する。出力部5は、転送部2により光電変換部112の電荷が電荷電圧変換部3へ転送された状態で、電荷電圧変換部3の電圧に応じた光信号を信号線SLへ出力する。選択部6は、画素811を選択状態/非選択状態にする。選択部6は、例えば、選択トランジスタであり、垂直走査回路813からアクティブルレベルの選択制御信号をゲートに受けた際にオンすることにより、画素811を選択状態にする。選択部6は、例えば、垂直走査回路813からノンアクティブルレベルの選択制御信号をゲートに受けた際にオフすることにより、画素811を非選択状態にする。

30

40

【0012】

なお、各画素811は、選択部6が省略された構成であっても良い。選択部6が省略された構成では、リセット部4が画素811を選択状態/非選択状態にする。この場合、リセット部4は、第1の電位(例えば、Hレベル)がドレインに供給され、アクティブルレベルのリセット制御信号がゲートに供給された際にオンして電荷電圧変換部3を第1の電位

50

にリセットすることにより、画素 811 を選択状態にする。リセット部 4 は、第 2 の電位（例えば、L レベル）がドレインに供給され、アクティブルレベルのリセット制御信号がゲートに供給された際にオンして電荷電圧変換部 3 を第 2 の電位にリセットすることにより、画素 811 を非選択状態にする。ここで、リセット部 4 がリセットすべき電位は垂直走査回路 813 が制御する。

#### 【0013】

垂直走査回路 813 は、画素配列 PA を垂直方向（列に沿った方向）に走査することにより、画素配列 PA における信号を読み出すべき行（読み出し行）を選択し、選択された読み出し行から信号が複数の信号線 SL へ出力されるようにする。垂直走査回路 813 は、例えば、垂直シフトレジスタを含む。

10

#### 【0014】

信号処理回路 812 は、読み出し行から複数の信号線 SL を介して出力された信号を処理する。例えば、信号処理回路 812 は、列ごとに、読み出し行から異なるタイミングで信号線 SL へ出力されたノイズ信号と光信号とをそれぞれ増幅する処理を行う。あるいは、例えば、信号処理回路 812 は、列ごとに、読み出し行から異なるタイミングで信号線 SL へ出力されたノイズ信号と光信号との差分をとることによりノイズ信号が除去された画像信号を生成する CDS 処理を行ってもよい。あるいは、例えば、信号処理回路 812 は、読み出し行から出力された複数列の信号における垂直走査回路 813 により選択された各列の信号を順次に出力線 815 へ出力するパラレル・シリアル変換処理を行っても良い。あるいは、例えば、信号処理回路 812 は、読み出し行から出力された各列の信号を A/D 変換する A/D 変換処理を行ってもよい。

20

#### 【0015】

水平走査回路 814 は、信号処理回路 812 を水平方向（行に沿った方向）に走査することにより、信号処理回路 812 に保持された各列の信号が順次に出力線 815 へ出力されるようにする。水平走査回路 814 は、例えば、水平シフトレジスタを含む。

#### 【0016】

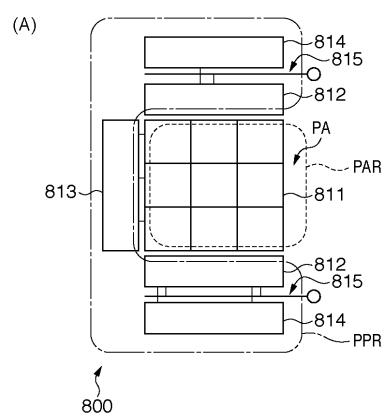

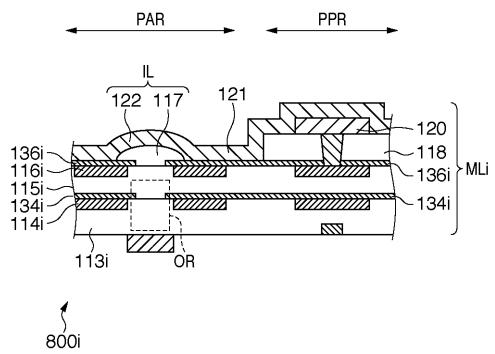

次に、実施形態に係る光電変換装置 800 の断面構成を、図 2 を用いて説明する。図 2 では、説明の簡略化のために、画素配列領域 PAR における 1 画素に対応した構成と周辺領域 PPR における 1 つのトランジスタに対応した構成とを並べて示している。

#### 【0017】

30

光電変換装置 800 は、図 2 に示すように、半導体基板 SB、多層配線構造 ML、複数の層内レンズ IL、及び保護膜 121 を備える。なお、実際には、複数の層内レンズ IL、及び保護膜 121 の上には、下部平坦化膜、カラーフィルタ層、上部平坦化膜、及び複数のマイクロレンズなどがさらに配されるが、簡略化のため、図 2 における図示及び説明を省略している。

#### 【0018】

半導体基板 SB には、画素配列領域 PAR において複数の光電変換部 112 が配されている。例えば、半導体基板 SB には、複数の画素 811 の配列に対応して、複数の光電変換部 112 が 2 次元的に（行に沿った方向及び列に沿った方向に）配列されている。光電変換部 112 は、電荷（例えば、電子）に応じた第 1 の導電型（例えば、N 型）の不純物を高濃度に含む電荷蓄積領域を有する。また、半導体基板 SB には、周辺領域 PPR において、半導体基板 SB の上に配されたゲート 123 に隣接した位置に、トランジスタのソース又はドレインとなるべき半導体領域 124, 125 が配されている。半導体領域 124, 125 は、電荷（例えば、電子）に応じた第 1 の導電型（例えば、N 型）の不純物を高濃度に含む。また、半導体基板 SB における光電変換部 112 及び半導体領域 124, 125 のそれぞれの周囲には、第 1 の導電型と反対導電型である第 2 の導電型（例えば、P 型）の不純物を低濃度に含むウエル領域 111 が配されている。

40

#### 【0019】

多層配線構造 ML は、半導体基板 SB の上に配されている。多層配線構造 ML では、画素配列領域 PAR の配線層の数よりも周辺領域 PPR の配線層の数が多い。多層配線構造

50

M Lでは、例えば、図2に示すように、画素配列領域P A Rの配線層の数が2であり、周辺領域P P Rの配線層の数が3である。多層配線構造M Lは、ゲート123、層間絶縁膜113、配線層114、層間絶縁膜115、配線層116、層間絶縁膜118、配線層120、及びビアプラグ119を含む。なお、層間絶縁膜113、層間絶縁膜115などにもコンタクトプラグ、あるいはビアプラグが存在するがここでは省略する。

#### 【0020】

ゲート123は、周辺領域P P Rにおける半導体基板S Bの上に配されている。ゲート123は、半導体領域124, 125とともにM O Sトランジスタを構成している。ゲート123は、多層配線構造M Lにおける最下の配線層とすることもできる。ゲート123は、例えば、ポリシリコンで形成されている。層間絶縁膜113は、半導体基板S B及びゲート123と配線層114とを絶縁するように、画素配列領域P A R及び周辺領域P P Rに配されている。層間絶縁膜113は、半導体基板S B及びゲート123を覆っている。層間絶縁膜113は、例えば、シリコン酸化物で形成されている。配線層114は、画素配列領域P A R及び周辺領域P P Rにおける層間絶縁膜113の上に配されている。画素配列領域P A Rにおける配線層114は、光電変換部112の上方における開口領域O Rを規定している。配線層114は、例えば、アルミニウムを主成分とする金属又は金属間化合物で形成されている。

#### 【0021】

層間絶縁膜115は、配線層114と配線層116とを絶縁するように、画素配列領域P A R及び周辺領域P P Rに配されている。層間絶縁膜115は、画素配列領域P A R及び周辺領域P P Rにおける配線層114及び層間絶縁膜113を覆っている。層間絶縁膜115は、多層配線構造M Lにおける画素配列領域P A Rの最上の層間絶縁膜である。層間絶縁膜115は、例えば、シリコン酸化物で形成されている。配線層116は、画素配列領域P A Rにおける最上の配線層である。配線層116は、画素配列領域P A R及び周辺領域P P Rにおける層間絶縁膜115の上に配されている。画素配列領域P A Rにおける配線層116は、光電変換部112の上方における開口領域O Rを規定している。配線層116は、例えば、アルミニウムを主成分とする金属又は金属間化合物で形成されている。なお、開口領域O Rは配線層116に加えて、配線層114や配線層116によって規定される場合もある。

#### 【0022】

層間絶縁膜118は、配線層116と配線層120とを絶縁するように、周辺領域P P Rに配されている。層間絶縁膜118は、画素配列領域P A Rに配されていない。すなわち、層間絶縁膜118は、周辺領域P P Rにおける配線層116及び層間絶縁膜115を覆っており、画素配列領域P A Rにおける配線層116及び層間絶縁膜115を覆っていない。層間絶縁膜118は、多層配線構造M Lにおける周辺領域P P Rの最上の層間絶縁膜である。層間絶縁膜118は、例えば、シリコン酸化物で形成されている。配線層120は、周辺領域P P Rにおける最上の配線層である。配線層120は、周辺領域P P Rにおける層間絶縁膜118の上に配されている。配線層120は、例えば、アルミニウムを主成分とする金属又は金属間化合物で形成されている。ビアプラグ119は、配線層116と配線層120とを接続している。ビアプラグ119は、例えば、タンゲステンを主成分とする金属又は金属間化合物で形成されている。

#### 【0023】

複数の層内レンズI Lは、画素配列領域P A Rにおける多層配線構造M Lの上に配されている。複数の層内レンズI Lのそれぞれは、光電変換部112へ光を導く。各層内レンズI Lは、第1の絶縁体117及び第2の絶縁体122を含む。

#### 【0024】

第1の絶縁体117は、層間絶縁膜115における光電変換部112の上方に位置する部分の表面115aを覆っている。第1の絶縁体117は、半導体基板S Bの表面S B aに垂直な方向から透視した場合に開口領域O Rを覆うように配されている。例えば、第1の絶縁体117は、層間絶縁膜115の表面115aを覆うとともに配線層116における

10

20

30

40

50

る開口領域 O R 近傍の縁部 116 b を覆っている。第 1 の絶縁体 117 は、半導体基板 S B の表面 S B a から離れる方向へ凸形状である。例えば、第 1 の絶縁体 117 は、略半球状の形状を有しており、半導体基板 S B の表面 S B a から離れる方向へ膨出した曲面を上面 117 a として有する。第 1 の絶縁体 117 の上面 117 a は、画素配列領域 P A R における最上の配線層 116 の表面 116 a よりも半導体基板 S B の表面 S B a から高くなっている。また、第 1 の絶縁体 117 は、層間絶縁膜 118 と同じ材料で形成されている。第 1 の絶縁体 117 は、例えば、シリコン酸化物で形成されている。

#### 【 0 0 2 5 】

第 2 の絶縁体 122 は、第 1 の絶縁体 117 を覆うように配されている。第 2 の絶縁体 122 は、第 1 の絶縁体 117 が半導体基板 S B の表面 S B a から離れる方向へ凸形状であることに応じて、半導体基板 S B の表面 S B a から離れる方向へ凸形状である。例えば、第 2 の絶縁体 122 は、第 1 の絶縁体 117 が半導体基板 S B の表面 S B a から離れる方向へ膨出した曲面を上面 117 a として有することに応じて、半導体基板 S B の表面 S B a から離れる方向へ膨出した曲面を上面 122 a として有する。また、第 2 の絶縁体 122 は、第 1 の絶縁体 117 より高い屈折率を有した材料であって保護膜 121 と同じ材料で形成されている。つまり、第 2 の絶縁体 122 は第 1 の絶縁体 117 よりも誘電率が大きい材料である。第 2 の絶縁体 122 は、例えば、シリコン窒化物で形成されている。

#### 【 0 0 2 6 】

ここで、各層内レンズ I L では、第 1 の絶縁体 117 より大きな屈折率を有する第 2 の絶縁体 122 が凸形状の第 1 の絶縁体 117 を覆っている。また、第 1 の絶縁体 117 と第 2 の絶縁体 122 との界面が半導体基板 S B の表面 S B a から離れる方向へ膨出した曲面になっている。これにより、半導体基板 S B の表面 S B a の法線に対して大きな入射角で第 2 の絶縁体 122 における縁部 122 b へ入射した光は、界面で光電変換部 112 へ向かう方向へ屈折されて第 1 の絶縁体 117 における縁部 117 b を通過する。すなわち、第 2 の絶縁体 122 における縁部 122 b の近傍を通過しようとする光は、光電変換部 112 の方に曲げられ、吸い込まれるような振る舞いをする。これにより、第 2 の絶縁体 122 及び第 1 の絶縁体 117 は、層内レンズ I L として機能する。

#### 【 0 0 2 7 】

保護膜 121 は、画素配列領域 P A R における最上の配線層 116 と周辺領域 P P R における最上の配線層 120 とを覆っている。これにより、保護膜 121 は、多層配線構造 M L 及び半導体基板 S B を保護している。保護膜 121 は、例えば、シリコン窒化物で形成されている。

#### 【 0 0 2 8 】

このように、複数の層内レンズ I L のそれぞれにおける第 1 の絶縁体 117 と、多層配線構造 M L における周辺領域 P P R の最上の絶縁膜（層間絶縁膜 118）とは、同じ材料で形成されている。また、第 1 の絶縁体 117 と層間絶縁膜 118 とは、いずれも層間絶縁膜 115 を覆っている。これにより、第 1 の絶縁体 117 と層間絶縁膜 118 とは、同じ工程で形成することに適した構造となっている。さらに、第 2 の絶縁体 122 と保護膜 121 とは、連続した膜となっているとともに、同じ材料で形成されている。これにより、第 2 の絶縁体 122 と保護膜 121 とは、同じ工程で形成することに適した構造となっている。したがって、本実施形態によれば、複数の層内レンズと多層配線構造とを少ない工程で製造することに適した光電変換装置を提供することができる。

#### 【 0 0 2 9 】

本実施形態（図 2 参照）では、層内レンズ I L が、画素配列領域 P A R における最上の配線層 116 とその下の配線層 114 との間の層間絶縁膜 115 を覆うように配されている。これにより、層内レンズ I L と光電変換部 112 の受光面 112 a との距離を低減することが容易である。すなわち、本実施形態によれば、層内レンズと光電変換部との距離を低減できる光電変換装置を提供することができる。この結果、画素配列領域 P A R の入射光量に対する光電変換部 112 の受光光量の割合である集光効率の低下を容易に抑制できる。

10

20

30

40

50

## 【0030】

また、本実施形態（図2参照）では、複数の層内レンズILのそれぞれにおける第1の絶縁体117と、多層配線構造MLにおける周辺領域PPRの最上の絶縁膜（層間絶縁膜118）とを例えればシリコン酸化物で形成することができる。層間絶縁膜118をシリコン酸化物で形成した場合、層間絶縁膜118を誘電率の高いシリコン窒化物で形成した場合に比べて、周辺領域PPRにおける配線層間の寄生容量を低減でき回路動作を高速化できる。

## 【0031】

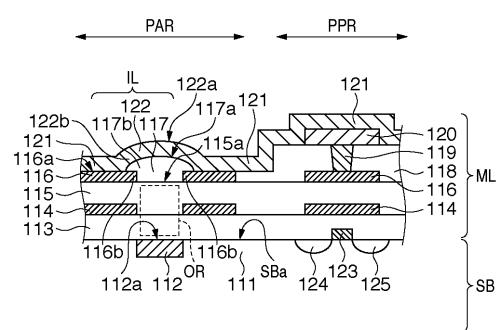

次に、本実施形態に係る光電変換装置の製造方法を、図3及び図2を用いて説明する。

## 【0032】

図3（A）の工程では、半導体基板SBを準備する。半導体基板SBは、例えれば、シリコンで形成されている。半導体基板SBに第2の導電型（例えれば、P型）の不純物を低濃度で注入することにより、ウエル領域111を形成する。半導体基板SBに、ウエル領域111におけるアクティブ領域を規定するための、複数の光電変換部112や複数のトランジスタ（123, 124, 125）を互いに電気的に分離すべき素子分離部（図示せず）を形成する。所定のレジストパターンをマスクとして第2の導電型と反対導電型である第1の導電型（例えれば、N型）の不純物を注入することにより、画素配列領域PARにおける半導体基板SBに複数の光電変換部112を形成する。また、半導体基板SBの上にトランジスタのゲート123を形成する。ゲート123は、例えれば、ポリシリコンで形成する。そのゲート123及び所定のレジストパターンをマスクとして第1の導電型の不純物を注入することにより、周辺領域PPRにおける半導体基板SBに半導体領域124, 125を形成する。そして、半導体基板SB及びゲート123を覆うようにCVD法（化学蒸着堆積法）により絶縁膜を堆積し、CMP法（化学的機械的研磨法）により平坦化する。この絶縁膜は、例えれば、シリコン酸化物で形成する。これにより、画素配列領域PAR及び周辺領域PPRにおける半導体基板SBの上に層間絶縁膜113を形成する。この層間絶縁膜113の上に金属層を形成する。金属層は、例えれば、アルミニウムを主成分とする金属または金属間化合物で形成する。その金属層をパターニングすることにより、配線層114を形成する。

## 【0033】

図3（B）の工程では、配線層114及び層間絶縁膜113を覆うようにCVD法により絶縁膜を形成し、CMP法により平坦化する。この絶縁膜は、例えれば、シリコン酸化物で形成する。これにより、画素配列領域PAR及び周辺領域PPRにおける半導体基板SBの上方に層間絶縁膜115を形成する。この層間絶縁膜115の上に金属層を形成する。金属層は、例えれば、アルミニウムを主成分とする金属または金属間化合物で形成する。その金属層をパターニングすることにより、配線層116を形成する。

## 【0034】

図3（C）の工程（第1の工程）では、配線層116及び層間絶縁膜115を覆うようにCVD法により絶縁物を堆積し、CMP法により平坦化する。この絶縁物は、例えれば、シリコン酸化物である。これにより、画素配列領域PAR及び周辺領域PPRにおける半導体基板SBの上方に絶縁層132を形成する。この絶縁層132は、画素配列領域PARにおける第1の絶縁体117と周辺領域PPRにおける層間絶縁膜118とになるべき絶縁物の層である。そして、周辺領域PPRにおいて、絶縁層132にピアホールを形成して導電体を埋め込むことにより、ピアブレグ119を形成する。導電体は、例えれば、タンクステンを主成分とする金属又は金属間化合物で形成されている。絶縁層132の上に金属層を形成する。金属層は、例えれば、アルミニウムを主成分とする金属または金属間化合物で形成する。その金属層をパターニングすることにより、配線層120を形成する。

## 【0035】

図3（D）の工程（第2の工程）では、画素配列領域PARにおける絶縁層132をリソグラフィ技術、及びドライエッティング技術などを用いてパターニングすることにより、上側に凸型である第1の絶縁体117と層間絶縁膜118とを形成する。具体的には、画

10

20

30

40

50

素配列領域 P A R における半導体基板 S B の表面 S B a に垂直な方向から透視した場合に光電変換部 1 1 2 を覆う島状パターンと、周辺領域 P P R の全体を覆うパターンとを有するフォトレジストパターンを形成する。そのフォトレジストパターンを熱処理（リフロー）することにより、フォトレジストパターンにおける島状パターンを略半球状の凸型パターンにする。このフォトレジストパターンをマスクとしてエッチングを行うことにより、画素配列領域 P A R における半導体基板 S B の表面 S B a から離れる方向へ凸形状である第 1 の絶縁体 1 1 7 と、多層配線構造 M L における周辺領域 P P R の最上の層間絶縁膜 1 1 8 とを形成する。すなわち、フォトレジストパターンにおける略半球状の凸型パターンに応じて、半導体基板 S B の表面 S B a から離れる方向へ膨出した曲面を上面 1 1 7 a として有する第 1 の絶縁体 1 1 7 を形成する。それとともに、フォトレジストパターンにおける周辺領域 P P R の全体を覆うパターンに応じて、周辺領域 P P R における配線層 1 1 6 及び層間絶縁膜 1 1 5 を覆っている層間絶縁膜 1 1 8 を形成する。層間絶縁膜 1 1 8 は、画素配列領域 P A R における配線層 1 1 6 及び層間絶縁膜 1 1 5 を覆っていない。

#### 【 0 0 3 6 】

なお、画素配列領域 P A R と周辺領域 P P R との全面を覆うフォトレジストパターンを形成した後に上記のフォトレジストパターンを重ねて形成し、これらのフォトレジストパターンをマスクとしてエッチングを行ってもよい。この場合、第 1 の絶縁体 1 1 7 と層間絶縁膜 1 1 8 とを、連続した膜として形成することができる。また、層間絶縁膜 1 1 8 の一部が、画素配列領域 P A R に設けられていてもよい。しかし、画素配列領域 P A R から層間絶縁膜 1 1 8 を除去することで、層間絶縁膜 1 1 8 の段差が画素配列領域 P A R からなくなるため、画素配列領域 P A R の平坦性を保つことが容易となる。

#### 【 0 0 3 7 】

図 2 の工程（第 3 の工程）では、第 1 の絶縁体 1 1 7 、配線層 1 1 6 、層間絶縁膜 1 1 8 、及び配線層 1 2 0 を覆うように、絶縁膜を形成する。この絶縁膜は、例えば、シリコン窒化物で形成する。すなわち、第 1 の絶縁体 1 1 7 を覆うように配された第 2 の絶縁体 1 2 2 と、画素配列領域 P A R における配線層 1 1 6 と周辺領域 P P R における配線層 1 2 0 とを覆う保護膜 1 2 1 とを、第 1 の絶縁体 1 1 7 より高い屈折率を有した材料で形成する。以上の工程によって、図 2 の構造が形成される。その後、下部平坦化膜、カラーフィルタ層、上部平坦化膜、及び複数のマイクロレンズなどがさらに形成されるが詳細は省略する。

#### 【 0 0 3 8 】

このように、層内レンズ I L における第 1 の絶縁体 1 1 7 と多層配線構造 M L における周辺領域 P P R の層間絶縁膜 1 1 8 とが同じ工程で形成される。また、層内レンズ I L における第 2 の絶縁体 1 2 2 と保護膜 1 2 1 とが同じ工程で形成される。これにより、複数の層内レンズと多層配線構造とを少ない工程で製造することができる。ここで、例えば、図 3 ( D ) の工程において、絶縁層 1 3 2 を凸形状にせず、画素配列領域 P A R の絶縁層 1 3 2 を除去し、絶縁膜で凸形状を形成する方法も考えられる。しかし、本実施形態の製造方法に比べて、絶縁膜を凸形状にする工程が増加してしまう。従って、本実施形態によれば、少ない工程で、かつ配線間の寄生容量を増加させることなく、かつ層間絶縁膜の総膜厚を厚膜化することができないため入射光量の低下を低減可能な光電変換装置及びその製造方法を提供することが可能となる。

#### 【 0 0 3 9 】

なお、光電変換装置における複数の層内レンズ I L のそれぞれは、第 1 の絶縁体 1 1 7 と第 2 の絶縁体 1 2 2 との界面における光の反射を抑制する反射抑制膜（図示せず）を第 1 の絶縁体 1 1 7 と第 2 の絶縁体 1 2 2 との間にさらに含んでもよい。反射抑制膜は、第 1 の絶縁体 1 1 7 の屈折率と第 2 の絶縁体 1 2 2 の屈折率との間の屈折率を有する材料で形成する。反射抑制膜は、例えば、第 1 の絶縁体 1 1 7 がシリコン酸化物で形成され第 2 の絶縁体 1 2 2 がシリコン窒化物で形成されている場合、シリコン酸化物で形成することができる。さらに、層間絶縁膜 1 1 3 と半導体基板 S B との間に、層間絶縁膜 1 1 3 と半導体基板 S B との界面における入射光の反射を抑制するために反射抑制膜を設けても

10

20

30

40

50

良い。この反射抑制膜は、層間絶縁膜 113 の屈折率と半導体基板 SB の屈折率との間の屈折率を有する材料で形成する。反射抑制膜は、例えば、層間絶縁膜 113 がシリコン酸化物で形成され半導体基板 SB がシリコンで形成されている場合、シリコン酸窒化物で形成することができる。

【0040】

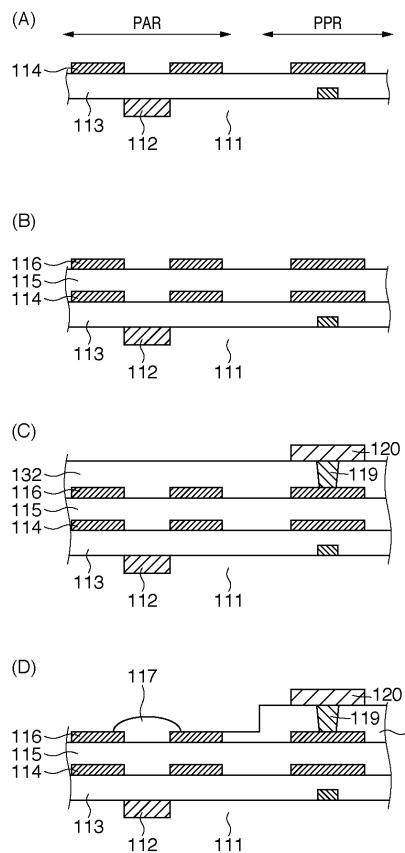

また、図 4 に示すように、光電変換装置 800i の多層配線構造 MLiにおいて、配線層 114i 及び配線層 116i がダマシン構造を有していても良い。すなわち、配線層 114i は、層間絶縁膜 113i に形成された溝に導電体が埋め込まれることにより形成されても良い。導電体は、例えば、銅を主成分とする金属又は金属間化合物で形成されている。また、導電体は前述の金属又は金属間化合物に加えてバリアメタルを含む積層構造であってもよい。この場合、配線層 114i の材料が層間絶縁膜 115i 中に拡散することを抑制するために、配線層 114i を覆う拡散抑制膜 134i が形成される。拡散抑制膜 134i は、開口領域 OR に対応した部分に開口を有する。また、配線層 116i は、層間絶縁膜 115i に形成された溝に導電体が埋め込まれることにより形成されても良い。導電体は、例えば、配線層 114i と同様の材料でよい。この場合、配線層 116i の材料が層間絶縁膜 118i 中に拡散することを抑制するために、配線層 116i を覆う拡散抑制膜 136i が形成される。拡散抑制膜 136i は、開口領域 OR に対応した部分に開口を有する。一方、多層配線構造 MLiにおいて、周辺領域 PPR における最上の配線層 120 は、上記の実施形態と同様の構造、すなわち、エッチングによりパターニングされた配線構造とすべきである。これは、配線層 120 が外部と電気的に接続するためのボンディングパッドを含んでおり、ダマシン構造の配線材料に比べて、上記の実施形態と同様の構造の配線材料の方がボンディングパッドとの接続（接合）を容易に形成できるからである。

【0041】

ここで、図 4 の構成における層内レンズ IL の製造方法は図 2 の構成の製造方法と同様の方法でよい。また、第 1 の絶縁体 117、層間絶縁膜 118 とを形成した後に、ビアプラグを形成し、配線層 120 を形成してもよい。この場合、拡散抑制膜 136i は、ビアプラグの導電体、配線層 120 の導電体を除去する際のエッチングストップ膜として機能することが出来る。

【0042】

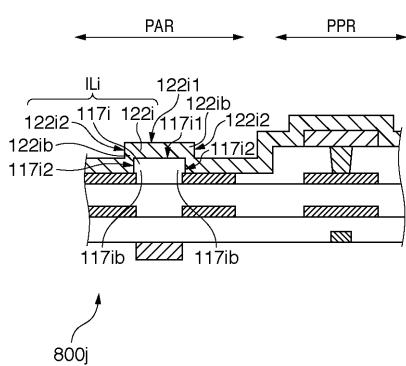

さらに、図 5 に示すように、光電変換装置 800j の各層内レンズ ILi において、第 1 の絶縁体 117i は、半導体基板 SB の表面 SBa に垂直な方向の断面が矩形であってもよい。ここで、「矩形」とは、いわゆる矩形の形状に加えて、矩形の基本的な形状を保ちながらその角に丸みを持たせた形状も含む。この場合、第 1 の絶縁体 117i は、上面 117i1 及び側面 117i2 を有していても良い。上面 117i1 は、半導体基板 SB の表面 SBa に沿って延びている。側面 117i2 は、上面 117i1 の縁から半導体基板 SB の表面 SBa に近づくように延びている。この場合、第 2 の絶縁体 122i は、第 1 の絶縁体 117i が上面 117i1 及び側面 117i2 を有することに応じて、上面 122i1 及び側面 122i2 を有する。上面 122i1 は、半導体基板 SB の表面 SBa に沿って延びている。側面 122i2 は、上面 117i1 の縁から半導体基板 SB の表面 SBa に近づくように延びている。この場合でも、各層内レンズ IL では、第 1 の絶縁体 117i より大きな屈折率を有する第 2 の絶縁体 122i が第 1 の絶縁体 117i を覆っている。これにより、半導体基板 SB の表面 SBa の法線に対して大きな入射角で第 2 の絶縁体 122i における縁部 122ib へ入射した光は、界面で光電変換部 112 へ向かう方向へ屈折されて第 1 の絶縁体 117i における縁部 117ib を通過する。すなわち、第 2 の絶縁体 122i における縁部 122ib の近傍を通過しようとする光は、光電変換部 112 の方に曲げられ、吸い込まれるような振る舞いをする。これにより、第 2 の絶縁体 122i 及び第 1 の絶縁体 117i は、層内レンズ ILi として機能する。この層内レンズ ILi における第 1 の絶縁体 117i 及び第 2 の絶縁体 122i は、図 3 (D) の工程において熱処理（リフロー）の処理を省略することにより、得ることができる。すな

10

20

30

40

50

わち、上記の実施形態に比べて、エッティングにおけるフォトレジストマスクを形成する際の熱処理の工程が不要なため、工数を削減することが可能である。

#### 【0043】

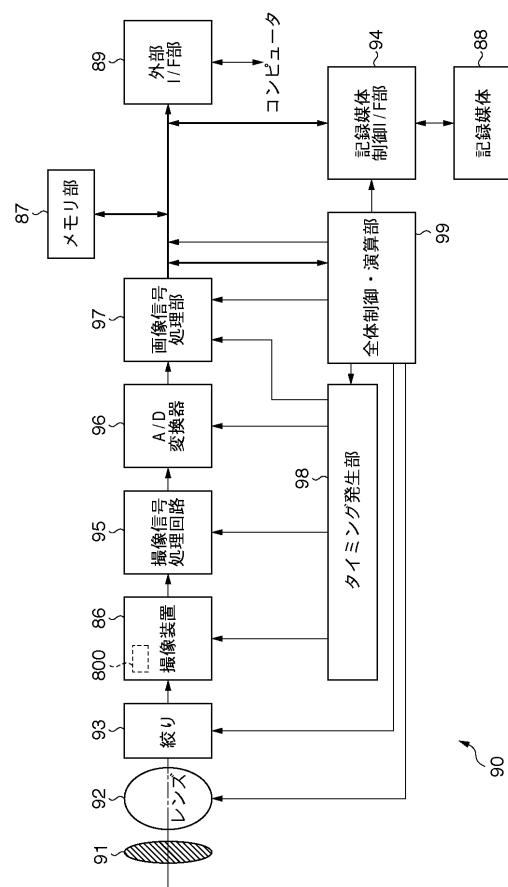

次に、本発明の光電変換装置を適用した撮像システムの一例を図6に示す。撮像システム90は、図6に示すように、主として、光学系、撮像装置86及び信号処理部を備える。光学系は、主として、シャッター91、レンズ92及び絞り93を備える。撮像装置86は、光電変換装置800を含む。信号処理部は、主として、撮像信号処理回路95、A/D変換器96、画像信号処理部97、メモリ部87、外部I/F部89、タイミング発生部98、全体制御・演算部99、記録媒体88及び記録媒体制御I/F部94を備える。なお、信号処理部は、記録媒体88を備えなくても良い。

10

#### 【0044】

シャッター91は、光路上においてレンズ92の手前に設けられ、露出を制御する。レンズ92は、入射した光を屈折させて、撮像装置86の光電変換装置800の撮像面に被写体の像を形成する。絞り93は、光路上においてレンズ92と光電変換装置800との間に設けられ、レンズ92を通過後に光電変換装置800へ導かれる光の量を調節する。

#### 【0045】

撮像装置86の光電変換装置800は、光電変換装置800の撮像面に形成された被写体の像を画像信号に変換する。撮像装置86は、その画像信号を光電変換装置800から読み出して出力する。

#### 【0046】

撮像信号処理回路95は、撮像装置86に接続されており、撮像装置86から出力された画像信号を処理する。A/D変換器96は、撮像信号処理回路95に接続されており、撮像信号処理回路95から出力された処理後の画像信号（アナログ信号）を画像信号（デジタル信号）へ変換する。

20

#### 【0047】

画像信号処理部97は、A/D変換器96に接続されており、A/D変換器96から出力された画像信号（デジタル信号）に各種の補正等の演算処理を行い、画像データを生成する。この画像データは、メモリ部87、外部I/F部89、全体制御・演算部99及び記録媒体制御I/F部94などへ供給される。

#### 【0048】

メモリ部87は、画像信号処理部97に接続されており、画像信号処理部97から出力された画像データを記憶する。

30

#### 【0049】

外部I/F部89は、画像信号処理部97に接続されている。これにより、画像信号処理部97から出力された画像データを、外部I/F部89を介して外部の機器（パソコン等）へ転送する。

#### 【0050】

タイミング発生部98は、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97に接続されている。これにより、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97へタイミング信号を供給する。そして、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97がタイミング信号に同期して動作する。

40

#### 【0051】

全体制御・演算部99は、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94に接続されており、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94を全体制的に制御する。

#### 【0052】

記録媒体88は、記録媒体制御I/F部94に取り外し可能に接続されている。これにより、画像信号処理部97から出力された画像データを、記録媒体制御I/F部94を介して記録媒体88へ記録する。

50

## 【 0 0 5 3 】

以上の構成により、光電変換装置 800 において良好な画像信号が得られれば、良好な画像（画像データ）を得ることができる。

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 成瀬 裕章

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 三島 隆一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 中内 大介

(56)参考文献 特開2009-194340 (JP, A)

特開2009-059824 (JP, A)

特開2008-016722 (JP, A)

特開2004-304148 (JP, A)

特開2005-260242 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14

H01L 31/10