(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4644696号

(P4644696)

(45) 発行日 平成23年3月2日(2011.3.2)

(24) 登録日 平成22年12月10日(2010.12.10)

(51) Int.Cl.

F 1

H01L 27/148 (2006.01)

H01L 27/146 (2006.01)H01L 27/14

H01L 27/14B

A

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2007-143804 (P2007-143804)

(22) 出願日 平成19年5月30日 (2007.5.30)

(65) 公開番号 特開2008-300551 (P2008-300551A)

(43) 公開日 平成20年12月11日 (2008.12.11)

審査請求日 平成22年2月12日 (2010.2.12)

早期審査対象出願

(73) 特許権者 306037311

富士フィルム株式会社

東京都港区西麻布2丁目26番30号

(74) 代理人 100115107

弁理士 高松 猛

(74) 代理人 100132986

弁理士 矢澤 清純

(72) 発明者 宇家 真司

宮城県黒川郡大和町松坂平1丁目6番地

富士フィルムフォトニックス株式会社内

審査官 柴山 将隆

最終頁に続く

(54) 【発明の名称】裏面照射型撮像素子及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子であって、前記半導体基板の裏面上に形成された前記裏面側の素子を構成する裏面側素子構成層と、

前記半導体基板の表面上に形成された前記表面側の素子を構成する表面側素子構成層と、

前記表面側素子構成層上方に形成された支持基板と、

前記半導体基板と前記支持基板との間隔を均一にするためのスペーサであって、前記表面側素子構成層に一端が接触し、前記支持基板に他端が接触する複数のスペーサと、

前記複数のスペーサによって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に充填された接着材とを備え、

前記複数のスペーサは、前記表面側素子構成層上又は前記支持基板上に成膜された材料をフォトリソグラフィ及びエッチングによってパターニングして形成されたものであり、

前記表面側素子構成層表面には、前記複数のスペーサの各々と対応する位置に前記半導体基板の表面からの距離が均一な底面を有する複数の凹部が形成され、

前記スペーサの一端が当該スペーサに対応する位置の前記凹部の底面に接触している裏面照射型撮像素子。

## 【請求項 2】

10

請求項 1 記載の裏面照射型撮像素子であって、

前記支持基板が前記裏面照射型撮像素子の実装基体である裏面照射型撮像素子。

**【請求項 3】**

半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、

前記半導体基板の表面上に、前記表面側の素子を構成する表面側素子構成層を形成する表面側素子構成層形成工程と、

前記半導体基板を支持するための支持基板を用意し、前記支持基板上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして前記支持基板上の特定の位置に複数の凸部を形成する凸部形成工程と、

前記複数の凸部を前記表面側素子構成層に接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、

前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程とを備え、

前記表面側素子構成層形成工程では、前記表面側素子構成層表面の前記特定の位置と対応する位置に、前記半導体基板の表面からの距離が均一な底面を有する凹部を形成し、

前記貼り合わせ工程では、前記凸部を前記凹部の底面に接触させた状態で接着材の充填を行う裏面照射型撮像素子の製造方法。

**【請求項 4】**

半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、

前記半導体基板の表面上に前記表面側の素子を構成する表面側素子構成層であって、表面の特定の位置に、前記半導体基板の表面からの距離が均一な底面を有する複数の凹部を有する表面側素子構成層を形成する表面側素子構成層形成工程と、

前記表面側素子構成層上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして、前記表面側素子構成層の前記複数の凹部の各々の底面上に凸部を形成する凸部形成工程と、

前記半導体基板を支持するための支持基板を用意し、前記支持基板に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、

前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程とを備える裏面照射型撮像素子の製造方法。

**【請求項 5】**

請求項 4 記載の裏面照射型撮像素子の製造方法であって、

前記裏面側素子構成層形成工程の後、前記支持基板を前記接着材と共に前記表面側素子構成層から剥離する支持基板剥離工程と、前記裏面照射型撮像素子の実装基体を用意し、前記実装基体に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記実装基体との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記実装基体を接着する工程とを備える裏面照射型撮像素子の製造方法。

**【請求項 6】**

半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、

10

20

30

40

50

前記半導体基板の表面上に前記表面側の素子を構成する表面側素子構成層であって表面が平坦な表面側素子構成層を形成する表面側素子構成層形成工程と、

前記表面側素子構成層上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして前記表面側素子構成層上に複数の凸部を形成する凸部形成工程と、

前記半導体基板を支持するための支持基板を用意し、前記支持基板に前記複数の凸部を接觸させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、

前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程と、

前記裏面側素子構成層形成工程の後、前記支持基板を前記接着材と共に前記表面側素子構成層から剥離する支持基板剥離工程と、前記裏面照射型撮像素子の実装基体を用意し、前記実装基体に前記複数の凸部を接觸させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記実装基体との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記実装基体を接着する工程とを備える裏面照射型撮像素子の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子に関する。

【背景技術】

【0002】

半導体基板の裏面側から光を照射し、この光に応じて半導体基板内で発生した電荷を、半導体基板の表面側に形成された電荷蓄積領域に蓄積し、ここに蓄積された電荷に応じた信号を、半導体基板の表面側に形成された C C D や C M O S 回路等によって外部に出力して撮像を行う裏面照射型撮像素子が提案されている。

【0003】

20

裏面照射型撮像素子における半導体基板（光電変換領域）の厚さは、可視光をほとんど吸収させるために  $10 \mu m$  程度必要である。このため、裏面照射型撮像素子を製造する際には、まず、厚みのある半導体基板の表面に電荷蓄積領域や C C D 等の構造物を形成した後、その構造物上に接着材によって支持基板を貼り付け、その後、半導体基板を例えば  $10 \mu m$  の厚さとなるまで裏面側からエッチングし、エッチング後は、半導体基板の表面側に形成した構造物に合わせて、半導体基板の裏面上にカラーフィルタやマイクロレンズ等の構造物を形成するといった手順をとる必要がある。

【0004】

特許文献 1 には、半導体基板に接着材によって支持基板を貼り付けてから、半導体基板を裏面側からエッチングする技術が開示されている。

30

【0005】

【特許文献 1】特開 2005-285988 号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

半導体基板を支持基板に貼り付ける為には通常、有機材料の接着材（エポキシ樹脂）などが利用される。支持基板と半導体基板を直接接合する技術もあるが、装置が高価であり半導体基板の表面がほぼ理想的に平坦になっている必要がある。そのため、C M P を使った平坦化工程が必要となる上に、ディッシング現象を低減する為のダミーパターンの導入やダミーパターン形状の最適化等、面倒な課題を抱えることになる。したがって、有機接

40

50

着材を利用することが製造コストの点で有利である。

【0007】

一方で、裏面照射型撮像素子の場合、支持基板の半導体基板に接着されていない側を基準にして、半導体基板の裏面上にカラーフィルタやマイクロレンズ等を高い位置精度で形成する必要がある。高い位置精度を実現するためには、半導体基板に貼り合わせた支持基板の外形がステッパー等のフォトリソ装置に掛けられるだけの平坦度を有している必要がある。支持基板自体は半導体基板と同程度の平坦度を実現することができるため問題にはならないが、双方の間に有機接着層を挟む場合、支持基板と半導体基板との間に微小なアオリ（ウェーハー間の水平度の誤差）が発生する可能性がある。微細なパターンを刻めるフォトリソ装置ほど焦点面の凹凸にはマージンが小さく、最小線幅0.2μm程度のフォトリソ装置では、ウェーハ面内で数μm程度の凹凸が発生すれば、装置によって形成されるフォトレジスト形状は大きく異なる結果になる。したがって、表面側の構造物と裏面側の構造物とを高い位置精度で形成するためには、支持基板と半導体基板との貼り合わせが、双方の間の空間が均一の厚みとなるように高い精度で実現される必要がある。特許文献1に開示された方法では、半導体基板と支持基板との間の空間の厚みが均一になっているという保障がなく、表面側の構造物と裏面側の構造物との位置ずれによる特性の劣化や歩留まりの低下、カラーフィルタやマイクロレンズ形状の変形等による混色の増加等の問題が懸念される。

【0008】

本発明は、上記事情に鑑みてなされたものであり、素子特性の向上、歩留まりの向上、及び混色の低減等を実現することが可能な裏面照射型撮像素子を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の裏面照射型撮像素子は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子であって、前記半導体基板の裏面上に形成された前記裏面側の素子を構成する裏面側素子構成層と、前記半導体基板の表面上に形成された前記表面側の素子を構成する表面側素子構成層と、前記表面側素子構成層上方に形成された支持基板と、前記半導体基板と前記支持基板との間隔を均一にするためのスペーサであって、前記表面側素子構成層に一端が接触し、前記支持基板に他端が接触する複数のスペーサと、前記複数のスペーサによって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に充填された接着材とを備え、前記複数のスペーサは、前記表面側素子構成層上又は前記支持基板上に成膜された材料をフォトリソグラフィ及びエッチングによってパターニングして形成されたものであり、前記表面側素子構成層表面には、前記複数のスペーサの各々と対応する位置に前記半導体基板の表面からの距離が均一な底面を有する複数の凹部が形成され、前記スペーサの一端が当該スペーサに対応する位置の前記凹部の底面に接触しているものである。

【0010】

また、本発明の裏面照射型撮像素子は、前記支持基板が前記裏面照射型撮像素子の実装基体であるものを含む。

【0011】

本発明の裏面照射型撮像素子の製造方法は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、前記半導体基板の表面上に、前記表面側の素子を構成する表面側素子構成層を形成する表面側素子構成層形成工程と、前記半導体基板を支持するための支持基板を用意し、前記支持基板上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして前記支持基板上の特定の位置に複数の凸部を形成する凸部形成工程と、前記複数の凸部を前記表面側素子構成層に接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記

10

20

30

40

50

支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程とを備え、前記表面側素子構成層形成工程では、前記表面側素子構成層表面の前記特定の位置と対応する位置に、前記半導体基板の表面からの距離が均一な底面を有する凹部を形成し、前記貼り合わせ工程では、前記凸部を前記凹部の底面に接触させた状態で接着材の充填を行うものである。

#### 【0012】

本発明の裏面照射型撮像素子の製造方法は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、前記半導体基板の表面上に前記表面側の素子を構成する表面側素子構成層であって、表面の特定の位置に、前記半導体基板の表面からの距離が均一な底面を有する複数の凹部を有する表面側素子構成層を形成する表面側素子構成層形成工程と、前記表面側素子構成層上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして、前記表面側素子構成層の前記複数の凹部の各々の底面上に凸部を形成する凸部形成工程と、前記半導体基板を支持するための支持基板を用意し、前記支持基板に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程とを備えるものである。

#### 【0013】

また、本発明の裏面照射型撮像素子の製造方法は、前記裏面側素子構成層形成工程の後、前記支持基板を前記接着材と共に前記表面側素子構成層から剥離する支持基板剥離工程と、前記裏面照射型撮像素子の実装基体を用意し、前記実装基体に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記実装基体との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記実装基体を接着する工程とを備えるものである。

#### 【0014】

本発明の裏面照射型撮像素子の製造方法は、半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、前記半導体基板の表面上に前記表面側の素子を構成する表面側素子構成層であって表面が平坦な表面側素子構成層を形成する表面側素子構成層形成工程と、前記表面側素子構成層上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして前記表面側素子構成層上に複数の凸部を形成する凸部形成工程と、前記半導体基板を支持するための支持基板を用意し、前記支持基板に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程と、前記裏面側素子構成層形成工程の後、前記支持基板を前記接着材と共に前記表面側素子構成層から剥離する支持基板剥離工程と、前記裏面照射型撮像素子の実装基体を用意し、前記実装基体に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記実装基体との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記実装基体を接着する工程とを備えるものである。

#### 【発明の効果】

#### 【0017】

本発明によれば、素子特性の向上、歩留まりの向上、及び混色の低減等を実現すること

10

20

30

40

50

が可能な裏面照射型撮像素子を提供することができる。

【発明を実施するための最良の形態】

【0018】

以下、本発明の実施形態について図面を参照して説明する。

【0019】

(第一実施形態)

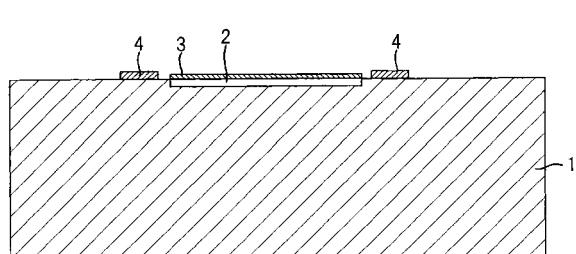

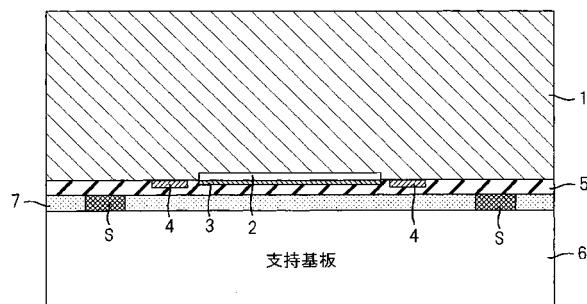

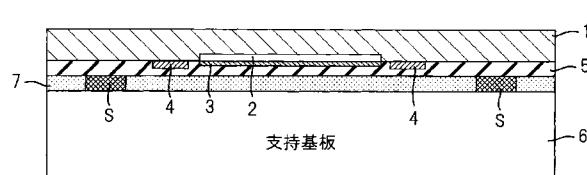

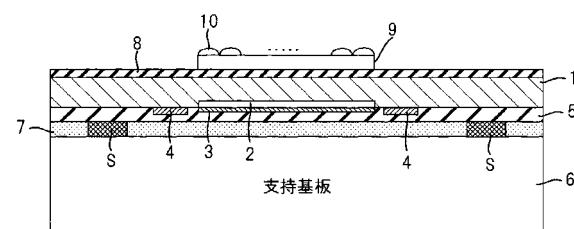

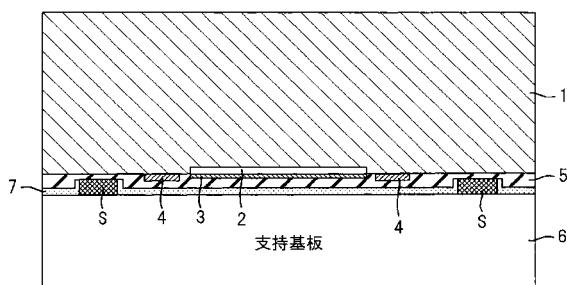

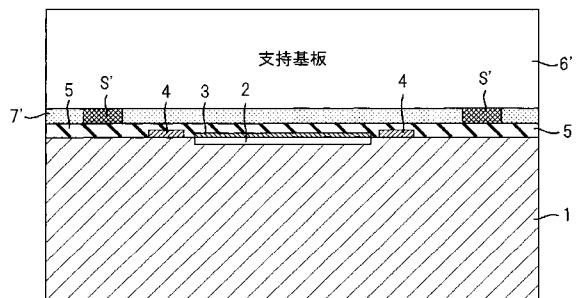

図1～図7は、本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図である。

本実施形態の裏面照射型撮像素子の概略構成は、図7に示すような構成であり、半導体基板の一例であるシリコン基板1の表面側には、シリコン基板1で発生した電荷を蓄積するための多数の電荷蓄積領域や各電荷蓄積領域に蓄積された電荷を転送するCCDを構成する転送チャネル等の素子構造物2、転送チャネルを駆動する駆動電極や各種配線等の素子構造物3、電極パッド4、及びこれらを保護する保護層や平坦化層として機能する絶縁層5等を含む表面側素子構成層が形成されている。又、シリコン基板1の裏面側には、平坦化層8、各電荷蓄積領域に入射させる光を分光するカラーフィルタ9、及び各電荷蓄積領域に光を集光するためのマイクロレンズ10等を含む裏面側素子構成層が形成されている。表面側素子構成層にはスペーサSの一端が接触し、スペーサSの他端には支持基板6が接触している。そして、表面側素子構成層と支持基板6との間の空間には接着材7が充填されており、これによってシリコン基板1と支持基板6とが貼りあわされている。

【0020】

図7に示す裏面照射型撮像素子は、シリコン基板1の裏面側から光を入射して用いるものである。マイクロレンズ10で集光され、カラーフィルタ9で分光された光はシリコン基板1に入射する。そして、ここで発生した電荷は電荷蓄積領域に蓄積され、CCDによって転送された電荷がアンプによって外部に出力される。本明細書では、シリコン基板1の表面及び裏面を規準として、各構成要素の位置関係を定義するものとする。例えば、シリコン基板1の表面を規準としたときは、光の入射方向を該表面の上方向と定義し、シリコン基板1の裏面を規準としたときは、光の入射方向とは反対方向を該裏面の上方向と定義する。

【0021】

このような定義にしたがい、本実施形態の裏面照射型撮像素子は、シリコン基板1と、シリコン基板1の表面上に形成された表面側素子構成層(素子構造物3、電極パッド4、絶縁層5)と、表面側素子構成層の絶縁層5上方に形成されたガラス等の支持基板6と、表面側素子構成層の絶縁層5に一端が接触し、支持基板6に他端が接触したスペーサSと、スペーサSによって形成された絶縁層5と支持基板6との間に充填された接着材7と、シリコン基板1の裏面上に形成された平坦化層8、平坦化層8上に形成されたカラーフィルタ9、及びカラーフィルタ9上に形成されたマイクロレンズ10を含む裏面側素子構成層とを備えた構成となっている。

【0022】

以下、このような構成の裏面照射型撮像素子の製造方法を図1～図7を参照して説明する。

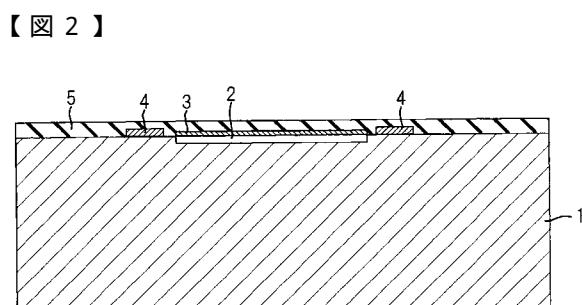

まず、図1に示すように、シリコン基板1表面を上にして固定し、表面内に素子構造物2を形成し、表面上に素子構造物3や電極パッド4を公知のプロセスによって形成する。次に、図2に示すように、シリコン基板1表面上に絶縁材料を成膜後、これを平坦化して絶縁層5を形成する。

【0023】

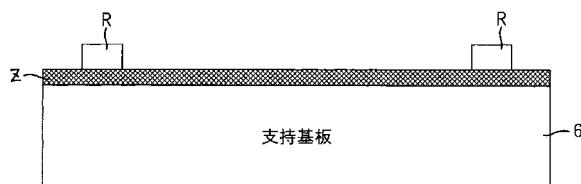

次に、図3に示すように、支持基板6を用意し、支持基板6上に支持基板6とは異なる材料(例えば金属材料)をCVDやPVD法等の膜厚均一性のよい成膜方法で成膜し、その上の特定の位置にのみレジストパターンRを露光及び現像工程(フォトリソグラフィ)によって形成する。次に、図4に示すように、レジストパターンRをマスクにして金属材料膜Zのエッチングを行い、レジストパターンR下方の金属材料7以外を除去して、スペ

10

20

30

40

50

ーサ S を形成する。尚、支持基板 6 にスペーサ S を形成する工程は、図 2 に示す状態の素子を作る前に行つても良いし、同時に行つても良い。

【 0 0 2 4 】

このスペーサ S は、シリコン基板 1 と支持基板 6 の間の空間の厚みを均一にするためのものである。このため、スペーサ S は、シリコン基板 1 の表面側素子構成層にスペーサ S を介して支持基板 6 を接触させたときに、双方が安定して平行になる程度の数及び位置を適宜決めておけば良い。

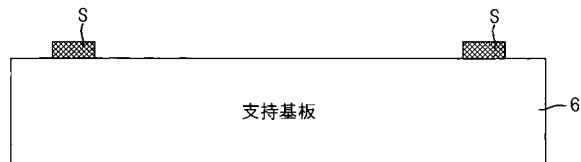

【 0 0 2 5 】

次に、図 5 に示すように、スペーサ S の支持基板 6 との接触面とは反対面にシリコン基板 1 の絶縁層 5 が接触するように、該反対面上にシリコン基板 1 を載置する。スペーサ S は、CVD や PVD 法等の膜厚均一性のよい成膜方法で成膜した材料をフォトリソグラフィ及びエッチングによってパターニングすることで形成されているため、その高さは均一となっている。一方で、スペーサ S が接触する絶縁層 5 の面は平坦化されている、つまり、該面はシリコン基板 1 表面からの距離が均一な面となっている。このため、図 5 に示した状態で、シリコン基板 1 と支持基板 6 との間の空間の厚みはどの場所においても均一なものとなる。そして、この状態でシリコン基板 1 の裏面から圧力をかけながら、スペーサ S によって形成された絶縁層 5 と支持基板 6 との間の空間に、接着材として有機材料の接着材（例えばエポキシ樹脂）7 を充填することで、シリコン基板 1 と支持基板 6 とを貼り合わせる。

【 0 0 2 6 】

尚、接着材 7 は、シリコン基板 1 と支持基板 6 とが貼り合わされれば充分であるため、絶縁層 5 と支持基板 6 との間の空間の全てに充填しなくとも良く、この空間の少なくとも一部に充填しておけば良い。

【 0 0 2 7 】

次に、図 6 に示すように、支持基板 6 を固定した状態で、シリコン基板 1 の厚みが例えば 10 μm 程度となるまでシリコン基板 1 を裏面側からエッチングする。次に、図 7 に示すように、樹脂等の絶縁材料をシリコン基板 1 の裏面上に成膜して平坦化層 8 を形成する。次に、平坦化層 8 上に、カラーフィルタ 9 を公知のプロセスによって形成し、カラーフィルタ 9 上にマイクロレンズ 10 を公知のプロセスによって形成する。そして、図 7 に示した構成の素子をパッケージングして、裏面照射型撮像素子の製造を完了する。

【 0 0 2 8 】

以上のような方法によれば、シリコン基板 1 と支持基板 6 との距離がどの場所でもほぼ均一となっているため、特許文献 1 に示した素子と比べて、裏面側素子構成層の各構成要素の位置及び形状の精度を向上させることができる。したがって、素子特性の向上、歩留まりの向上、及び混色の低減等を実現することが可能となる。

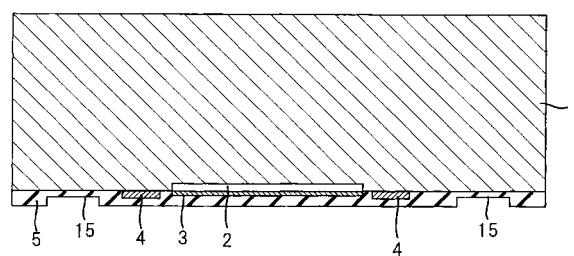

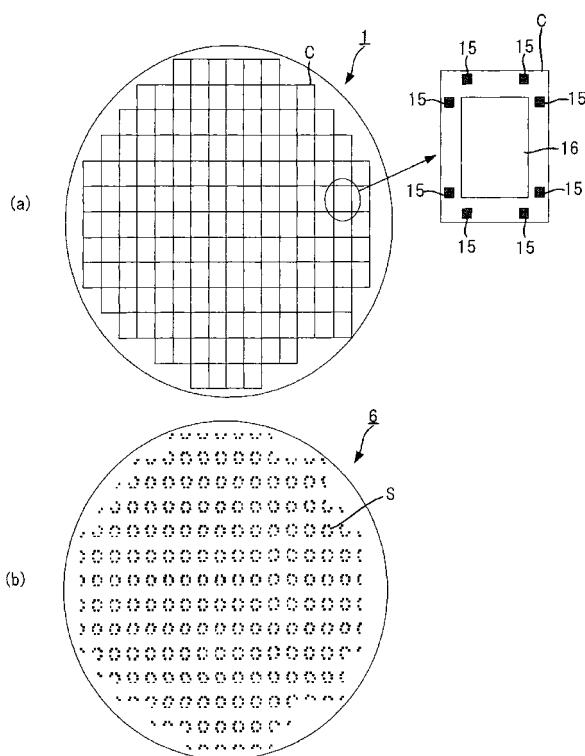

【 0 0 2 9 】

尚、本実施形態では、表面側素子構成層の表面が平坦となっているが、これが平坦になつていないので有りうる。この場合は、表面側素子構成層を形成するときに、例えば図 8 に示すように、表面側素子構成層の表面の特定の位置にシリコン基板 1 の表面からの距離が均一となる面 15 が形成されるように、表面側素子構成層内の構造を設計しておけば良い。そして、図 9 に示すように、支持基板 6 に形成したスペーサ S が面 15 に接触するように、支持基板 6 のスペーサ S 上にシリコン基板 1 を載置し、圧力をかけながら接着材 7 を充填して貼り合わせを行えば良い。

【 0 0 3 0 】

図 10 は、シリコン基板及び支持基板の全体を示した平面模式図であり、(a) はシリコン基板 1 を表面側から見た図であり、(b) は支持基板 6 をスペーサ S の形成面側から見た図である。

図 10 (a) に示すように、裏面照射型撮像素子を形成すべき領域であるチップ領域 C の中央に表面側素子構成層 16 を形成した場合には、それを取り囲むように面 15 を形成しておき、支持基板 6 には、図 10 (b) に示すように、面 15 に対応する位置にスペー

10

20

30

40

50

サSを形成しておく。そして、図10(a)に示したシリコン基板1と図10(b)に示した支持基板6とを貼り合わせて接着することで、シリコン基板1と支持基板6とを平行にすることができる。

#### 【0031】

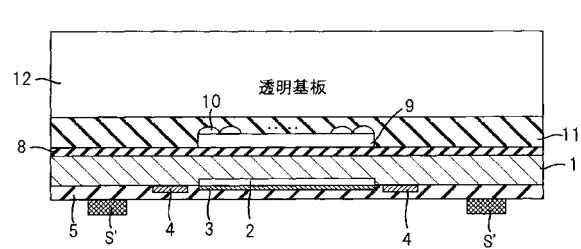

##### (第二実施形態)

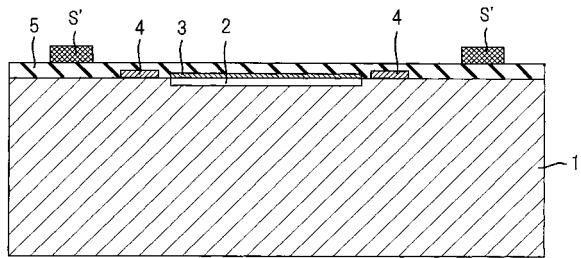

図11～図15は、本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図である。

まず、第一実施形態で説明した方法と同様の方法で図2に示した状態の素子を形成する。次に、図11に示すように、絶縁層5上の特定の位置にフォトリソグラフィ及びエッチングによってスペーサS'（凸部のパターン）を形成する。つまり、絶縁層5上に絶縁層5とは異なる材料（例えば金属材料）をCVDやPVD法等の膜厚均一性のよい成膜方法で成膜し、金属材料膜上に露光及び現像工程によってレジストのマスクパターンを形成し、このマスクパターンを介して金属材料膜をエッチングすることで、スペーサS'を形成する。

#### 【0032】

次に、図12に示すように、スペーサS'の絶縁層5との接触面とは反対面にガラス等の支持基板6'が接触するように、該反対面上に支持基板6'を載置する。スペーサS'はCVDやPVD法等の膜厚均一性のよい成膜方法で成膜した膜をフォトリソグラフィ及びエッチングによってパターニングすることで形成されているため、その高さは均一となっている。又、スペーサS'が接触する絶縁層5の面は平坦化されている、つまり、該面はシリコン基板1表面からの距離が均一な面となっている。このため、図12に示した状態で、シリコン基板1と支持基板6'との間の空間の厚みはどの場所においても均一なものとなる。そして、この状態で支持基板6'に圧力をかけながら、スペーサS'によって形成された絶縁層5と支持基板6'との間の空間に、接着材として有機材料の接着材（例えばエポキシ樹脂）7'を充填することで、シリコン基板1と支持基板6'とを貼り合わせる。

#### 【0033】

尚、接着材7は、シリコン基板1と支持基板6'とが貼り合わされれば充分であるため、絶縁層5と支持基板6'との間の空間の全てに充填しなくとも良く、この空間の少なくとも一部に充填しておけば良い。

#### 【0034】

このスペーサS'は、スペーサSと同様、シリコン基板1と支持基板6'の間の空間の厚みを均一にするためのものである。このため、スペーサS'は、シリコン基板1と支持基板6'とをスペーサS'を介して接触させたときに、双方が安定して平行になる程度の数及び位置を適宜決めておけば良い。

#### 【0035】

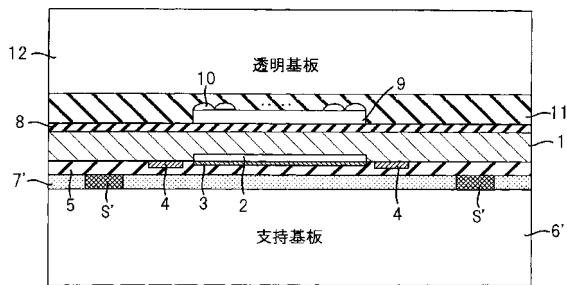

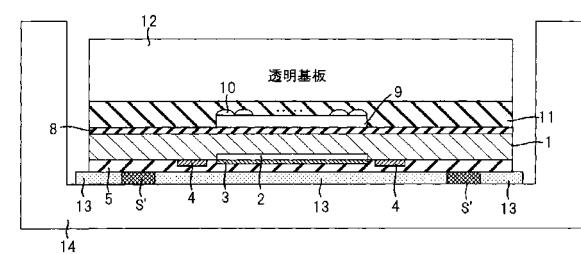

次に、第一実施形態で説明した方法と同様に、シリコン基板1の裏面をエッチングして厚みを10μmとし、シリコン基板1の裏面上に平坦化層8を形成し、平坦化層8上にカラーフィルタ9を形成し、カラーフィルタ9上にマイクロレンズ10を形成する。次に、図13に示すように、カラーフィルタ9及びマイクロレンズ10を保護するための透明な樹脂材料等からなる保護層11を形成し、保護層11上に有機材料の接着材を塗布し、この接着材を介して、保護層11にガラス等の透明基板12を貼り付ける。

#### 【0036】

次に、図14に示すように、支持基板6'を接着材7'と共に絶縁層5から剥離する。次に、図15に示すように、裏面照射型撮像素子を収容するためのパッケージ本体又は裏面照射型撮像素子を駆動する駆動回路や信号処理回路が作りこまれた回路基板等の実装基体14を用意し、実装基体14にスペーサS'を接触させた状態で、スペーサS'によって形成された絶縁層5と実装基体14との間の空間に接着材として有機材料の接着材（例えばエポキシ樹脂）13を充填することで、シリコン基板1を実装基体14に接着する。

#### 【0037】

10

20

30

40

50

尚、接着材13は、シリコン基板1と実装基体14とが接着されれば充分であるため、絶縁層5と実装基体14との間の空間の全てに充填しなくとも良く、この空間の少なくとも一部に充填しておけば良い。

【0038】

以上のような方法によれば、シリコン基板1と支持基板6'との距離がどの場所でもほぼ均一となった状態で裏面側素子構成層を形成することができるため、特許文献1に示した素子と比べて、裏面側素子構成層の各構成要素の位置及び形状の精度を向上させることができる。したがって、素子特性の向上、歩留まりの向上、及び混色の低減等を実現することが可能となる。

【0039】

又、以上のような方法によれば、シリコン基板1と実装基体14とを、スペーサS'を介して接着材13により接着することができるため、シリコン基板1を実装基体14の素子載置面に対して平行にすることができる、裏面照射型撮像素子をカメラに実装した場合のカメラ光学系とのずれ等をなくすことができる。

【0040】

尚、図13に示した状態の素子を形成後、この素子をパッケージングして裏面照射型撮像素子を完成させることも可能であるが、この場合、支持基板6'を実装基体に接着する際に、支持基板6'が実装基体の素子載置面に対して傾いてしまう恐れがある。このような事態を回避するために上述した方法を採用することは有効である。

【0041】

又、本実施形態においても、表面側素子構成層の表面が平坦となっていない場合は、表面側素子構成層を形成するときに、例えば図8に示すように、表面側素子構成層の表面の特定の位置にシリコン基板1の表面からの距離が均一となる面15が形成されるように、表面側素子構成層内の構造を設計しておき、面15上にスペーサS'を形成する方法を採用すれば良い。

【0042】

第一実施形態及び第二実施形態では、裏面照射型撮像素子がCCD型である例を示したが、CMOS型であっても良い。この場合は、表面側素子構成層をCMOS型に必要な素子からなる層とすれば良い。

【図面の簡単な説明】

【0043】

【図1】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図2】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図3】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図4】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図5】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図6】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図7】本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図8】本発明の第一実施形態である裏面照射型撮像素子の製造工程の変形例を示した断面模式図

【図9】本発明の第一実施形態である裏面照射型撮像素子の製造工程の変形例を示した断面模式図

【図10】本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における

10

20

30

40

50

**断面模式図**

【図11】本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図12】本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図13】本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図14】本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

【図15】本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図

10

**【符号の説明】****【0044】**

1 シリコン基板

2, 3, 4, 5 表面側素子構成層

6 支持基板

7 接着材

8, 9, 10 裏面側素子構成層

S スペーサ

**【図1】****【図3】****【図4】**

【 图 5 】

【図6】

【 义 7 】

( 8 )

【 四 9 】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 国際公開第00/062344 (WO, A1)

特開平11-067823 (JP, A)

特開2001-308092 (JP, A)

特開2004-296825 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14

H01L 27/146

H01L 27/148