(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3647166号

(P3647166)

(45) 発行日 平成17年5月11日(2005.5.11)

(24) 登録日 平成17年2月18日(2005.2.18)

(51) Int.C1.<sup>7</sup>

F 1

H02M 3/28

H02M 3/28

H

H02M 3/28

C

H02M 3/28

V

請求項の数 7 (全 30 頁)

(21) 出願番号

特願平8-261208

(22) 出願日

平成8年9月11日(1996.9.11)

(65) 公開番号

特開平10-94251

(43) 公開日

平成10年4月10日(1998.4.10)

審査請求日

平成15年9月10日(2003.9.10)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100081880

弁理士 渡部 敏彦

(72) 発明者 関谷 利幸

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 川端 修

最終頁に続く

(54) 【発明の名称】電源回路

## (57) 【特許請求の範囲】

## 【請求項 1】

負荷電流を検出する負荷電流検出手段と、該負荷電流検出手段からの出力に応じて変圧器の入力電圧または駆動 PWM (パルス幅変調) のオン時間もしくはオンデューティを制御して前記負荷電流が所定値となるように出力電圧を制御する出力電圧制御手段とを有する電源回路において、

前記出力電圧制御手段による定電流制御の開始後所定期間は目標出力電流制御値より大きい出力電流制御値を設定する出力電流制御値設定手段と、

前記出力電流制御値設定手段により設定された出力電流制御値での制御開始から一定時間後に設定された前記出力電流制御値を前記目標出力電流値に再設定する出力電流制御値再設定手段と

を具備したことを特徴とする電源回路。

## 【請求項 2】

負荷電流を検出する負荷電流検出手段と、該負荷電流検出手段からの出力に応じて変圧器の入力電圧または駆動 PWM (パルス幅変調) のオン時間もしくはオンデューティを制御して前記負荷電流が所定値となるように出力電圧を制御する定電流制御手段と、前記出力電圧を検出する出力電圧検出手段と、前記出力電圧検出手段からの出力に基づいて前記変圧器の入力電圧または駆動 PWM のオン時間もしくはオンデューティを制御して出力電圧が所定値となるように制御する出力電圧制御手段とを有する電源回路において、

前記出力電圧制御手段の起動 / 停止を制御する起動 / 停止制御手段と、

所定の出力電流制御値を設定する出力電流制御値設定手段とを具備し、所望の電圧が得られるように初めに前記起動／停止制御手段により前記出力電圧制御手段を起動させ、前記出力電圧検出手段により検出される電圧が前記所望の電圧に到達した後、前記起動／停止制御手段により前記出力電圧制御手段の動作を停止させると共に、出力電流制御値設定手段により目標出力電流制御値を設定し、前記定電流制御手段により定電流制御を開始することを特徴とする電源回路。

【請求項3】

負荷電流を検出する負荷電流検出手段と、該負荷電流検出手段からの出力に応じて変圧器の入力電圧または駆動PWM(パルス幅変調)のオン時間もしくはオンデューティを制御して前記負荷電流が所定値となるように出力電圧を制御する出力電圧制御手段と、前記負荷電流を検出する負荷電流検出手段とを有する電源回路において、

前記出力電圧制御手段の定電流制御動作が開始して所定時間経過後も前記負荷電流検出手段の検出値が所定値以下である場合、前記出力電圧制御手段の動作を停止または中断するように制御する出力動作制御手段を具備したことを特徴とする電源回路。

【請求項4】

前記出力電圧制御手段の定電流制御動作が開始して所定時間経過後も前記負荷電流検出手段の検出値が所定値以下である場合、その旨を電源回路の動作を指示する外部装置に通知する通知手段を具備したことを特徴とする請求項3記載の電源回路。

【請求項5】

一端を所定の直流電圧入力とし且つ他端を所定状態にオン／オフ動作させる一次巻線と前記一次巻線のオフ時にエネルギーを取り出す少なくとも1つのフライバック巻線と前記一次巻線のオン時にエネルギーを取り出す少なくとも1つのフォワード巻線と前記一次巻線のオフ時及びオン時の全周期に亘ってエネルギーを取り出す高圧出力巻線とを含むトランジスと、前記フライバック巻線の整流出力電圧を検出する電圧検出手段と、該電圧検出手段の検出結果により前記一次巻線のオン動作時間を制御し且つ前記フライバック巻線の整流出力電圧を所定値に制御する主制御手段と、前記フォワード巻線の出力の整流平滑電圧を比較用基準電圧と比較し、前記フォワード巻線に設けられたスイッチング素子を制御することにより前記整流平滑電圧を目標値に制御する副制御手段とを有する電源回路において、

前記副制御手段は、前記主制御手段の起動時に前記フライバック巻線の整流出力電圧が所定値を超えるまで前記フォワード巻線の出力の1サイクル中の導通時間を所定値以下に抑制することにより、前記主制御手段が正常な制御状態になった後に前記フォワード巻線の出力の整流平滑電圧をオン／オフ制御可能とするように制御することを特徴とする電源回路。

【請求項6】

前記副制御手段は、前記主制御手段の起動時に前記フライバック巻線の整流出力電圧が所定値を超えると前記比較用基準電圧を徐々に増加させることを特徴とする請求項5記載の電源回路。

【請求項7】

前記副制御手段は、前記フォワード巻線の出力の整流平滑電圧と比較用基準電圧との比較出力を所定のパターン信号と比較する比較手段を有し、前記主制御手段の起動時に前記フライバック巻線の整流出力電圧が所定値を超えるまで、前記フォワード巻線の出力の整流平滑電圧と比較用基準電圧との比較出力を制限することを特徴とする請求項5記載の電源回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、トランス(多出力巻線トランス或いは高圧トランス)を含む電源回路に関する。

【0002】

10

20

30

40

50

### 【従来の技術】

従来、複写機等の静電方式画像形成装置の電源システムとして、装置の論理回路動作用またはモーター、ソレノイド等の電力供給用低圧出力と静電方式画像形成用高圧出力を1つのトランスで動作させるものが提案及び実用化されている。

### 【0003】

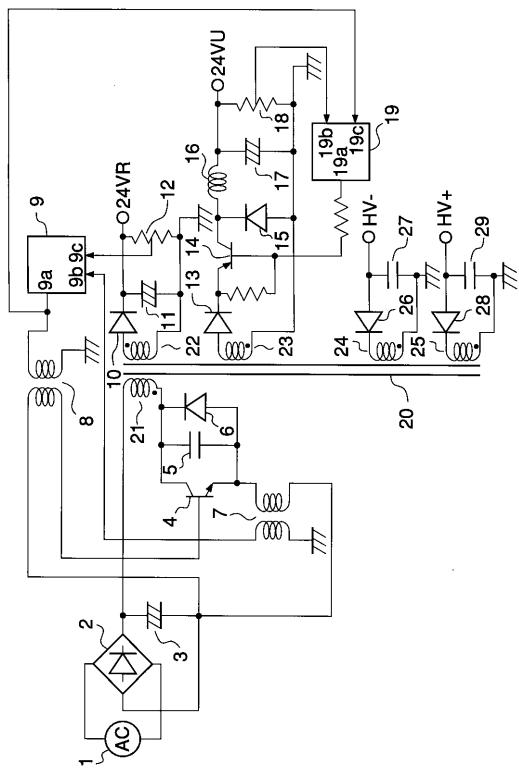

以下、この種の電源システムの従来例として、複写機に搭載される複合型電源回路のブロック構成を図18に示す。同図において、1は商用AC電源、2は整流ブリッジ、3は第1の平滑コンデンサ、4は入力巻線駆動用スイッチング素子、5は共振コンデンサで、後述する複合型トランス20の入力インダクタンス成分とにより電圧共振を発生させる役割を持つ。6はクランプダイオード、7はカレントトランスで、入力巻線駆動用のスイッチング素子4、共振コンデンサ5及びクランプダイオード6を流れる電流をモニターするためのトランスである。8はドライブトランスで、二次側にある主制御部9からのスイッチング素子駆動信号を一時側に伝達するためのトランスである。主制御部9は、低圧用フライバック巻線22の整流出力電圧の検出結果に基づいて一次巻線21のオン動作時間を制御し、該低圧用フライバック巻線22の整流出力電圧を所定値に制御するものである。主制御部9は、スイッチング素子4の駆動信号出力部9a、一次側駆動電流検出信号入力部9b及び24VR平滑電圧検出信号入力部9cを有している。

10

### 【0004】

また、図18において、10は低圧用フライバック巻線22の出力を整流するダイオード、11は平滑コンデンサである。本例における本出力は24Vに制御するものとし、24VRと称する。12は24VRの電圧を検出するための電圧検出抵抗、13は低圧用フォワード巻線23の出力を整流するダイオード、14はスイッチング素子で、低圧用フォワード巻線23の平滑出力が所定値となるようにオン／オフ動作する。本例における本出力は24Vに制御するものとし、24VUと称する。15はフライホイールダイオード、16は整流用インダクタンス、17は平滑コンデンサ、18は24VU出力を検出するための出力検出抵抗、19は副制御部で、24VU出力が所定値となるようにスイッチング素子14の導通角を制御するものである。副制御部19は、24VU用スイッチング素子14の駆動信号出力部19a、24VU平滑出力検出信号入力部19b及びスイッチング素子4の駆動信号入力部19cを有している。

20

### 【0005】

30

更に、図18において、20は複合型トランスで、一次巻線21、低圧用フライバック巻線22、低圧用フォワード巻線23及び高圧用巻線24、25を有している。26はダイオードで、高圧用巻線24の出力を負電圧に整流する。27は平滑コンデンサ、28はダイオードで、高圧用巻線25の出力を正電圧に整流する。29は平滑コンデンサである。

### 【0006】

次に、上記構成の電源回路の動作を説明する。

### 【0007】

商用AC電源1からの電流は整流ブリッジ2及び平滑コンデンサ3により整流平滑されて複合型トランス20の一次巻線21の一端に入る。スイッチング素子4がオンの間、該スイッチング素子4に流れる電流は複合型トランス20の入力インダクタンスに反比例した傾きで直線的に増加する。また、24VU巻線出力のスイッチング素子14がオンとなっている期間は、その巻線電流が巻数比に反比例して一次側スイッチング素子4に重畠される。

40

### 【0008】

次に、一次側スイッチング素子4がオフすると、その際の電流エネルギーを基に、一次側インダクタンスと共に共振コンデンサ5によるLC共振が発生する。共振コンデンサ5の電圧は概略正弦波となり、増加し、ピークを迎えた後、減少する。このときクランプダイオード6によって負側はダイオード順方向電圧に制限される。主制御部9は、この様子をカレントトランス7によりモニターし、負側に電流が流れ込むのを検知した瞬間、スイッチング素子4に対して再びオン信号を発生する。複合型トランス20の低圧用フライバック巻線

50

22は、この共振ピーク値側の位相で整流平滑され、この電圧が主制御部9によりモニターされる。二次側にある主制御部9は、24Vよりも低い場合は、スイッチング素子4のオン幅を増やし、高い場合は減らす。

#### 【0009】

以上により、スイッチング素子4に対しては常に0ボルトでのスイッチングが実現され、また低圧用フライバック巻線22の整流平滑電圧が24Vに制御される。一方、他の出力巻線は、複合型トランス20の巻数比に応じた出力電圧が出力される。

#### 【0010】

以上のように、複合型トランス20の入力側においてLCフライバック電圧共振を発生させ、出力側にて1つの低圧用フライバック巻線22の出力のピーク整流値を所定値に制御することにより、複合型トランス20の高圧出力巻線24, 25にはフライバック側のピーク値を一定値に制御した高圧出力が発生することとなる。

10

#### 【0011】

なお、主制御部9は、一般的には24VRの制御目標電圧を時間的に漸次上昇させ、24VRの最終目標値への立ち上がりに所定時間をかける、所謂ソフトスタート機能を付加し、関係各部品の過渡的な電流、電圧負担を軽減するのが通例である。

#### 【0012】

24VU巻線出力は、所謂フォワード側の出力を平滑する向きとなっており、一般的には24VRに比べ出力電圧を大きくとることができると、複合型トランス20の各巻線のフォワード側電圧はAC入力電圧の平滑電圧に概略比例するため、出力電圧に対する要求制度によっては二次側での個別の電圧制御が必要となる。24VU電圧制御部(副制御部)19は、24VU電流電圧をモニターし、スイッチング素子14の導通率を変化させ、所定の電圧に制御する。

20

#### 【0013】

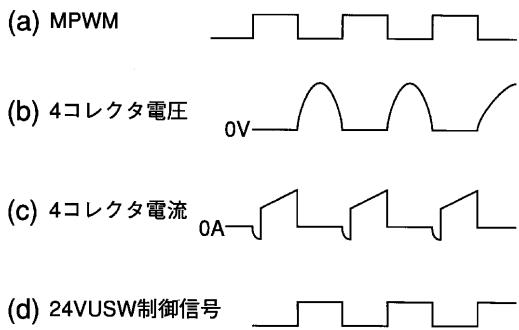

定常時の主要な動作波形を図19に示す。同図は、24VUの外部負荷がオン状態になった際の定常動作を示す。

#### 【0014】

図19において、(a)はMPWMの動作波形、(b)はスイッチング素子4のコレクタ電圧の動作波形、(c)はスイッチング素子4のコレクタ電流の動作波形、(d)は24VUSW(スイッチング素子14)制御信号の動作波形である。

30

#### 【0015】

また、従来より、複写機等の静電方式の電子写真画像形成装置においては、感光体への帶電、現像、転写紙への転写、転写紙の感光体からの分離等の目的で、数百ボルト(v)から数十キロボルト(kv)程度の出力を行う数種の高圧電源回路を具備している。

#### 【0016】

これらは、その目的に応じて外部制御装置より所定のオン/オフ信号、出力電圧制御信号、出力電流制御信号を受け取り出力の制御を行うが、近年、画像形成条件のよりきめ細かな最適化の流れとして、帶電装置、転写装置等、それぞれの高圧出力負荷の電気的なインピーダンスによって出力電圧値をより最適な値へと切り換えるという要求が新たに生まれている。つまり、環境条件、経時変化等によるそれらの電気的インピーダンスの変動に積極的に対応しようというものである。

40

#### 【0017】

その目的を達成するために、画像形成期間外に、まず所定の定電流値で高圧出力をを行い、その際の出力電圧を検知することにより、負荷抵抗値を算出し、その結果に応じて画像形成期間の出力電圧値、もしくは出力電流値を決定するようにした高圧電源回路が実用化されている。

#### 【0018】

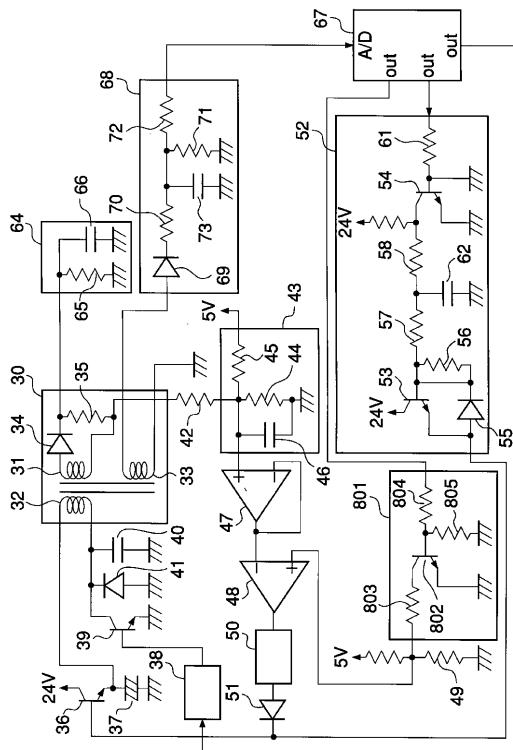

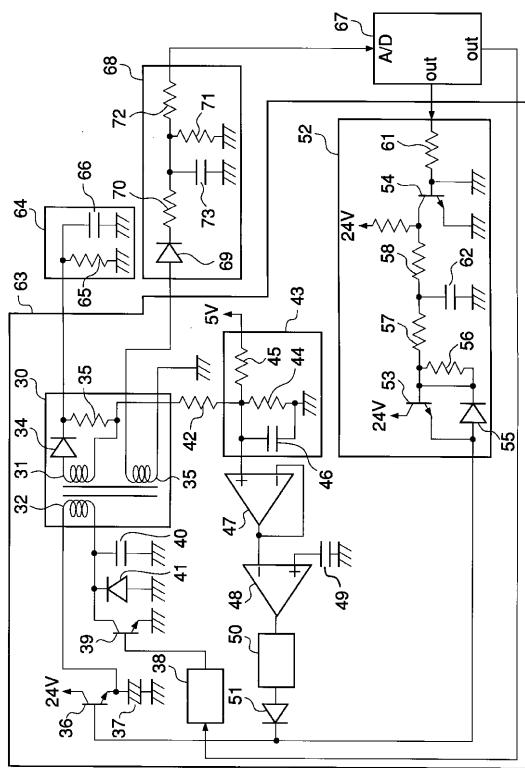

図23に、この種の従来の高圧電源回路のブロック構成を示す。同図において、30は高圧トランスで、本例では内部に出力巻線31、入力巻線32、検出巻線33、出力巻線31に接続される高耐圧整流ダイオード34及びブリーダ抵抗35を有している。36は制

50

御回路の比較結果に対応した電圧を高圧トランス30の入力部に伝送するためのフォロワトランジスタ、37は高圧トランス30の入力巻線に安定した直流電圧を供給する平滑コンデンサ、38は高圧トランス30を駆動する高周波信号を発生する発振器、39はスイッチングトランジスタ、40は高圧トランス20の入力インダクタンスとLCフライバック共振を発生させる共振コンデンサ、41は共振波形の負側への潜り込みを制限するクランプダイオードである。

#### 【0019】

また、図23において、42は負荷への電流を検出するための出力(シリーズ)抵抗で、数Mから数10M程度の高低抗値の抵抗が選ばれる。また、43は負荷への電流を検出するための負荷電流検出回路で、抵抗44、45及びコンデンサ46を有している。47は負荷電流検出回路43の電圧を高入力抵抗で後段に接続するためのバッファ回路、48は電流検出値と目標設定値とを比較する演算增幅器、49は制御目標設定電圧、50は制御ループを所望の周波数特性にするためのフィルター回路、51はフィルター回路50の出力電圧を高圧トランス20の入力部に伝送するダイオード、52は定電圧制御ブロックで、フィルター回路50の出力よりも大きい電圧が出力された場合に定電圧制御ループとして機能する。定電圧制御ブロック52は、トランジスタ53、54、ダイオード55、抵抗56、57、58、59、60、61及びコンデンサ62を有している。

#### 【0020】

以上により高圧回路ユニット63が構成されている。

#### 【0021】

また、図23において、64は高圧回路ユニット63の出力に接続される負荷で、電気的特性として抵抗65と容量66の並列回路を想定する。67は電源コントローラで、高圧電源回路全体の動作を司るコントローラ機能を有するが、その動作については、高圧電源回路全体の動作を制御する外部制御ユニットによって支配される。68は整流平滑回路で、ダイオード69、抵抗70、71、72及びコンデンサ73を有している。

#### 【0022】

次に、上記構成の高圧回路ユニット63の動作を説明する。

#### 【0023】

まず、外部制御ユニット(高圧回路ユニット63の動作をリモート制御する、高圧電源回路全体のコントローラで、図示省略)から負荷抵抗測定値モード開始の信号(図示省略)を受け取る。これを受け定電圧制御ブロック52の出力電圧をオフした状態にて、高圧出力イネーブル信号を発振器38に送出する。これにより発振器38は、所定の周波数、デューティで発振を開始し、スイッチングトランジスタ39をスイッチング動作させる。そして、スイッチングトランジスタ39がオンの期間、入力電圧とオン時間及び高圧トランス20の入力インダクタンスに応じて所定のエネルギーが高圧トランス20に蓄積される。一方、スイッチングトランジスタ39がオフの期間には、そのエネルギーが高圧トランス20の入力インダクタンスと共振コンデンサ40とによってLC共振を起こし、スイッチングトランジスタ39のコレクタには、所謂フライバック電圧が発生する。この電圧は、巻数に応じて他の巻線にも伝達され、巻数の大きい出力巻線には高い電圧が発生する。これが整流ダイオード36を通じて外部負荷53に供給されることになる。一般的には、外部負荷64の容量66の成分により出力巻線のほぼピーク値V<sub>o</sub>がホールドされ、直流の高圧出力が外部負荷64に供給される。この時の外部負荷電流I<sub>d</sub>は、下記(1)式により求められる。

#### 【0024】

$$I_d = V_o / (R_1 + R_2 + R_3) \dots (1)$$

ここで、R1は抵抗65の抵抗値、R2は抵抗42の抵抗値、R3は負荷電流検出回路43の合成インピーダンスをそれぞれ示す。

#### 【0025】

この外部負荷電流により電流検出ポイントV<sub>det</sub>の値は、その分下がる。この電流検出ポイントV<sub>det</sub>の値が制御目標設定電圧49の値よりも大きい場合、演算增幅器48の

10

20

30

40

50

出力電圧は上がり、高圧トランス 2 0 の入力電圧が上がる。これにより、高圧トランス 2 0 の出力電圧は上がり、負荷電流が増加し、電流検出ポイント V d e t の値を小さくする方向へと動作する。逆に制御目標設定電圧 4 9 の値に対して電流検出ポイント V d e t の値が低くなれば、演算増幅器 4 8 の出力電圧は下がり、高圧トランス 2 0 の入力電圧が下がる。

【 0 0 2 6 】

以上により、負荷電流が設定した値と等しくなるように高圧トランス 2 0 の出力電圧が調整されることとなる。この状態で出力電圧検出巻線 3 3 の出力を整流平滑回路 6 8 を通し、電源コントローラ 6 7 の A / D ポートより入力し、高圧出力電圧を演算する。

【 0 0 2 7 】

以上により負荷電流、電圧が分かるので、負荷インピーダンスが分かり、その値に応じて最適な高圧出力値を演算により決定する。

【 0 0 2 8 】

その後、外部制御ユニットから画像域用高圧出力オンの信号（図示省略）を受けるのに応じて、先に決定された最適出力電圧が出力されるように、定電圧出力制御ブロック 5 2 の出力電圧を設定する。但し、本例では定電流制御ループは、ダイオード 5 1 により常に閉じられているため、定電流出力した際の出力電圧よりも大きい出力電圧のみが設定可能となる構成になっている。出力電圧は検出巻線 3 3 の電圧を逐次監視し、演算することによってフィードバック制御され、結果的には定電圧制御が行われることとなる。

【 0 0 2 9 】

更に、従来より複写機等の静電方式の電子写真画像形成装置においては、感光体への帯電、現像、転写紙への転写、転写紙の感光体からの分離等の目的で、数百ボルト ( v ) から数十キロボルト ( k v ) 程度の出力をを行う数種の高圧電源回路を具備している。

【 0 0 3 0 】

これらは、その目的に応じて外部制御装置より所定のオン / オフ信号、出力電圧制御信号、出力電流制御信号を受け取り出力の制御を行う。

【 0 0 3 1 】

このうち、例えば、負荷電流を所定の値に制御したいというような高圧出力の場合、電源回路内には負荷電流検出手段が具備され、その出力値に応じて変圧装置への入力電力を制御して、負荷電流が所望の一定値となるように制御される。

【 0 0 3 2 】

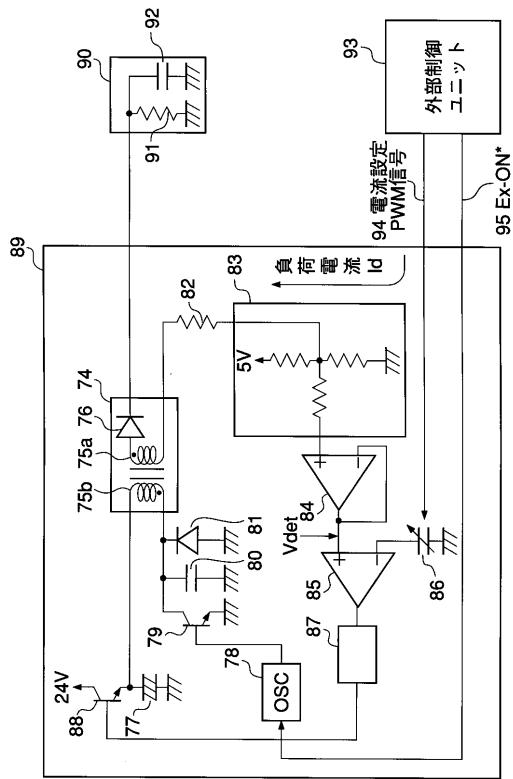

図 2 4 にこのような制御を行う従来の電源回路のブロック構成を示す。同図において、7 4 は高圧トランスで、本例では内部に出力巻線 7 5 a、入力巻線 7 5 b 及び出力巻線 7 5 a に接続される高耐圧整流ダイオード 7 6 を有している。7 7 は高圧トランス 7 4 の入力巻線 7 5 b に直流電圧を供給する平滑コンデンサ、7 8 は高圧トランス 7 4 を駆動する高周波信号を発生する発振器 ( O S C ) 、7 9 はスイッチングトランジスタ、8 0 は高圧トランス 7 4 の入力インダクタンスと L C フライバック共振を発生させる共振コンデンサ、8 1 は共振波形の負側への潜り込みを制限するクランプタイオード、8 2 は負荷への電流を検出するための抵抗で、特に出力 ( シリーズ ) 抵抗として、数 M から数 1 0 M 程度の高低抗値の抵抗が選ばれる。8 3 は負荷への電流を検出する負荷電流検出回路、8 4 は負荷電流検出回路 8 3 の電圧を高入力抵抗で後段に接続するためのバッファ回路、8 5 は電流検出値と制御目標設定電圧値とを比較する演算増幅器、8 6 は制御目標設定電圧、8 7 は制御ループを所望の周波数特性とするためのフィルター回路、8 8 はフィルター回路 8 7 の出力電圧を高圧トランス 7 4 の入力部に伝送するエミッタフォロアトランジスタである。

【 0 0 3 3 】

以上が高圧回路ユニット 8 9 を構成する。

【 0 0 3 4 】

また、図 2 4 において、9 0 は高圧回路ユニット 8 9 の出力部に接続される負荷で、例えば電子写真の場合、帯電器等が該当するが、電気的特性として抵抗 9 1 と容量 9 2 の並列

10

20

30

40

50

回路を想定する。93は外部制御ユニットで、電源回路全体の動作を司るコントローラ機能を有する。94は外部制御ユニット93から高圧回路ユニット89へ負荷電流の設定値を送信するための信号線で、演算増幅器85の制御目標電圧値となる電圧を設定するためのもので、種々の伝送方式が考えられるので、ここでは特に言及しない。95は外部制御ユニット93から高圧回路ユニット89への出力オン／オフを設定するための信号線で、本例では、発振器78に対して発振開始、停止の信号を伝送することとする。

#### 【0035】

次に、上記構成の高圧回路ユニット89において、定電流動作させる際の動作を説明する。

#### 【0036】

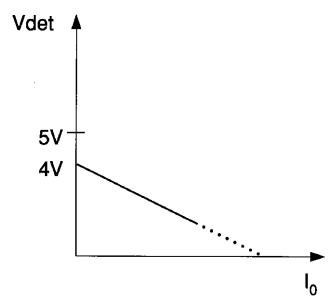

まず、外部制御ユニット93から高圧回路ユニット89に対して電流設定値を設定する。本例では、負荷電流検出回路83は図25に示すような電流電圧特性を持つように構成されているものとする。つまり、負荷電流が0の場合、4ボルト(V)でそこから負荷電流が流れるに伴って、小さい電圧値に直線的に変化していく。従って、電流設定を行う場合、4Vより小さい値を演算増幅器85の制御目標電圧値として設定することとなる。

10

#### 【0037】

次に、出力オン／オフ信号をオンにする。すると、発振器78は所定の周波数、デューティで発振を開始し、スイッチングトランジスタ79をスイッチング動作させる。そして、スイッチングトランジスタ79がオンの期間、入力電圧とオン時間及び高圧トランス74の入力インダクタンスに応じて所定のエネルギーが高圧トランス74に蓄積される。一方、スイッチングトランジスタ79がオフの期間には、そのエネルギーが高圧トランス74の入力インダクタンスと共振コンデンサ80とによってLC共振を起こし、スイッチングトランジスタ88のコレクタには、所謂フライバック電圧が発生する。この電圧は、巻数に応じて他の巻線にも伝達され、巻数の大きい出力巻線75aには高い電圧が発生する。これが整流ダイオード76を通じて外部負荷90に供給されることになる。一般的には、外部負荷90の容量92の成分により出力巻線のほぼピーク値Voがホールドされ、直流の高圧出力が外部負荷90に供給される。この時の外部負荷電流Idは、下記(1)式により求められる。

20

#### 【0038】

$$Id = Vo / (R1 + R2 + R3) \dots (1)$$

30

ここで、R1は抵抗91の抵抗値、R2は抵抗82の抵抗値、R3は負荷電流検出回路83の合成インピーダンスをそれぞれ示す。

#### 【0039】

この外部負荷電流により電流検出ポイントVdetの値は、その分下がる。この電流検出ポイントVdetの値が制御目標設定電圧86の値よりも大きい場合、演算増幅器85の出力電圧は上がり、高圧トランス74の入力電圧が上がる。これにより、高圧トランス74の出力電圧は上がり、負荷電流が増加し、電流検出ポイントVdetの値を小さくする方向へと動作する。逆に制御目標設定電圧86の値に対して電流検出ポイントVdetの値が低くなれば、演算増幅器85の出力電圧は下がり、高圧トランス74の入力電圧が下がる。

40

#### 【0040】

以上により、負荷電流が設定した値と等しくなるように高圧トランス74の出力電圧が調整されることとなる。

#### 【0041】

以上の例では高圧トランス74の入力電圧の大きさを増減することにより、高圧出力電流一定制御を実現するものであるが、高圧トランス74のスイッチング駆動におけるオンタイムの量を増減させ、高圧出力電流一定制御を実現するものもある。

#### 【0042】

##### 【発明が解決しようとする課題】

しかしながら、上記図18に示す従来例においては、以下のような問題点があった。

50

## 【0043】

(1) 一次側のスイッチング素子4の駆動電流には二次側のフォワード巻線の出力電流が巻数比に逆比例して重畠されるため、24VUの平滑コンデンサの電圧が小さく、充電電流が大きい立ち上がり期間では一次側のスイッチング素子4に非常に大きな駆動電流を重畠してしまい、関係回路素子に負担をかける。

## 【0044】

(2) 主たる制御の駆動源となる一次側LC電圧共振が安定な0ボルトスイッチによる発振状態に移行する以前から、上記状態が発生するため、安定な共振状態へ移行するまでの過渡期間が延び、より長い期間、関係回路素子に負担をかける。

## 【0045】

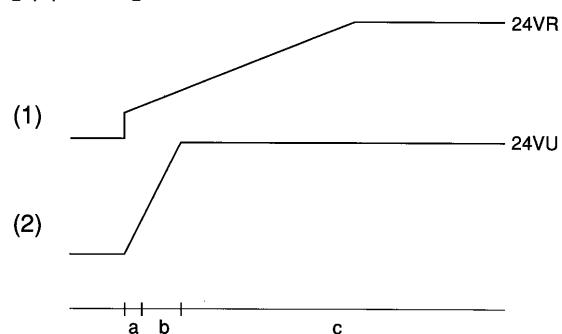

この様子を図20及び図21を用いて説明する。

10

## 【0046】

図20は、24VRと24VUの電圧立ち上がり波形を模式的に表わす図であり、同図の(1)24VRの電圧立ち上がり波形、(2)24VUの電圧立ち上がり波形、(3)は期間である。

## 【0047】

24VRは主制御部により主制御パルス(24VUスイッチング素子制御信号)19aのオン時間の緩やかな拡大、又は制御用比較基準値の緩やかな上昇等によるソフトスタート制御が機能し、所定時間をかけて最終目標値まで到達するように制御される。一方、24VUについては、その巻線元出力がフォワード側であるという性格上、24VRがソフトアップ中もほぼ最終値に近い波高値をもった出力が巻線より供給され、その結果、いち早く最終目標値に到達してしまう。

20

## 【0048】

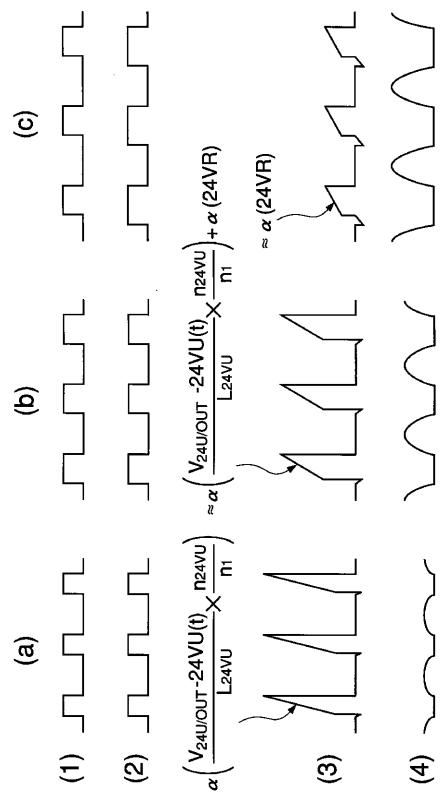

図21は、図20のa, b, cのそれぞれの期間の24VU制御信号の波形、主制御信号(24VR制御信号)の波形、一次側スイッチング素子4の駆動電流の波形、コレクタ電圧の波形をそれぞれ示す図であり、同図の(1)は24VU制御信号の波形、(2)は主制御信号(24VR制御信号)の波形、(3)は一次側スイッチング素子4の駆動電流の波形、(4)はコレクタ電圧の波形である。

## 【0049】

期間aは24VRの立ち上がりの初期の様子を示している。主制御信号はソフトスタート機能により狭いオン期間をもったPWM信号でスタートしている。一方、24VUの制御信号は24VUが目標値よりもずっと低いためにフォワード側オンの期間、完全オン状態となる(主制御信号とほぼ同一のPWM信号となる)。このとき、前述のように24VUのフォワード側巻線出力は既に最終値である。一次側の直流入力電圧の巻数比換算分( $V_{24Uout}$ )になっており、また、虹側出力コンデンサの充電電圧(24VU(t))が低いため、そのほとんどが平滑用インダクタンス( $L_{24U}$ )に印加され、大きな巻線出力電流(及びその大きな時間傾き)を発生させることとなる。この二次側電流は巻数比に応じて一次側のスイッチング素子4の駆動電流となる。

30

## 【0050】

期間b, cと時間推移するごとに24VUの出力コンデンサの電圧は上昇し、当然、二次側の巻線出力電流は減少し、最終的には24VUの外部負荷がオンしない状態であればほぼ0となる。このとき、一次側電流は24VRのライバックエネルギーを蓄積するためだけの駆動電流となる(高圧巻線の負荷電流は一般に極めて微小であるため無視してよい)。このときの一次側の電流増加の傾きは、ほぼ高圧トランス20の一次インダクタンスと直流入力電圧で決まる値となる。bにおいては、その中間状態にある期間となる。

40

## 【0051】

ここで、特にaの期間では、設計条件によっては一次側の駆動電流が、定常時(24VUの定格外部負荷電流が流れている状態)の最大値に比して、同等さらにはより大きくなってしまうことがある。そのような場合には、一次側スイッチング素子4の駆動電流を検出して過電流保護をかけるような保護回路構成(図示省略)が実現できないか、又は保護レ

50

ベルを定格負荷から期待されるものよりはるかに緩やかなものにせざるを得ない状況となる。

【0052】

以上は主に上記問題点(1)に関して述べたが、次に、上記問題点(2)に関して図22を用いて説明する。

【0053】

図22は、一次側のスイッチング素子4の駆動電流とコレクタ電圧の波形を起動時の3つの期間について模式的に示す図であり、同図の(1)は駆動電流の波形、(2)はコレクタ電圧の波形である。また、aは主制御パルスが output 開始した直後の期間を示す。共振コンデンサに一次巻線の他端に印加された直流電圧が完全充電された状態から主制御パルスがスタートする。パルス幅は最も細い状態から開始するように制御される(ソフトスタート)が、共振コンデンサの充電負荷をスイッチング素子4がショートする形となるため、この期間、図示のように時間的には短いが非常に大きい電流が流れる。この期間は当然、L C 共振を発生させるための十分なトランジスタ駆動電流が流れてもおらず、フライバック波形が0ボルトまでは全く跳ね返ることができない。

10

【0054】

その後、期間cのような完全な0ボルトスイッチによる電圧共振波形が得られるようになる前に、期間bのようにフライバック波形が徐々に成長しつつも、依然としてフライバックエネルギーが低く、正常な0ボルトスイッチが実現できない過渡期間を送る。この期間に24VUの充電電流が重畠されると、同図の上側のような一次側電流波形となり、共振コンデンサの残電圧をスイッチング素子4がショートする電流と二次側からの重畠電流が合わされ、大きな電流負荷をスイッチング素子4にかけることとなる。

20

【0055】

他、主たる制御は、上述したように一次側の駆動電流が正から負に切り換わった瞬間を検出して、次のオン動作を開始するような制御アルゴリの場合、24VUの充電電流が正の方向として一次側に重畠される過渡期間には、フライバック共振波形が0ボルトまで振れ込むことを、より一層阻害する形となり、正常な0ボルトスイッチによる電圧共振制御状態への移行が一層遅れてしまうこととなる。

【0056】

また、上記図23に示す従来例においては、定電流出力iには出力電圧が小さく、負荷の抵抗分流れる電流に対して容量成分を充電する電流が総負荷電流の大部分を占める期間は、出力電圧はほぼ下記(2)式

30

$$(i \times t) / c \dots (2)$$

となり、定電流値に比例した傾きをもって時間と共に直線状に増加していく波形となる。また、並列にある抵抗成分rも含めて考えた場合は、最終出力に対する時間変化は  $c r$  を時定数とした  $\{1 - e \times p(-t / c r)\}$  で表わされる。その際、出力負荷の抵抗成分、容量成分の値によっては最終出力値に到達するのにかなりの時間を要する場合がある。例えば、付加容量を200pF、負荷抵抗を500MΩとした場合、 $c r$  時定数は、100ms程度となり、最終値に対して更に近い割合の出力を得るためにには当然それ以上の時間を要することとなる。

40

【0057】

先に、負荷インピーダンスの測定は画像形成期間以外において実施すると述べたが、例えば、画像形成期間の前に負荷インピーダンスの測定を行う場合、複写動作の前処理シーケンスによっては、所謂ファーストコピータイムに負荷インピーダンス測定期間をそのまま追加して考慮しなければならない場合も考えられ、ユーザーに対してファーストコピーの速さを商品価値としてアピールするような装置の場合には、その様なレベルの処理時間も無視することができず、より速やかな測定方法が求められることとなる。

【0058】

更に、図24に示す従来例においては、外部負荷回路の抵抗値が何等かの原因で非常に高抵抗となった場合、例えば、高圧電源ユニットの出力から外部負荷への給電経路に不良が

50

発生した場合や、何等かの目的で接続ケーブルが外された場合等には、負荷電流が流れないために、定電流制御ループが回路ユニットの持つ最大能力まで高圧トランスの入力電圧を上昇させる、もしくはオンタイムを増加させることになり、通常の負荷において求められる最高出力を大きく越えて出力してしまうこととなる。

【0059】

本発明は上記従来技術の有する問題点を解消するためになされたもので、その第1の目的とするところは、可能な限り迅速に負荷への出力を定常状態にすることができる電源回路を提供することである。

【0060】

また、本発明の第2の目的とするところは、負荷に印加される電圧が過大になることを防止することができる電源回路を提供することである。

10

【0061】

また、本発明の第3の目的とするところは、トランスの一時側に大きな電流が流れてしまうことを防止することができる電源回路を提供することである。

【0062】

【課題を解決するための手段】

上記第1の目的を達成するために本発明の請求項1記載の電源回路は、負荷電流を検出する負荷電流検出手段と、該負荷電流検出手段からの出力に応じて変圧器の入力電圧または駆動PWM(パルス幅変調)のオン時間もしくはオンデューティを制御して前記負荷電流が所定値となるように出力電圧を制御する出力電圧制御手段とを有する電源回路において、前記出力電圧制御手段による定電流制御の開始後所定期間は目標出力電流制御値より大きい出力電流制御値を設定する出力電流制御値設定手段と、前記出力電流制御値設定手段により設定された出力電流制御値での制御開始から一定時間後に設定された前記出力電流制御値を前記目標出力電流値に再設定する出力電流制御値再設定手段とを具備したことを特徴とするものである。

20

【0065】

また、上記第1の目的を達成するために本発明の請求項2記載の電源回路は、負荷電流を検出する負荷電流検出手段と、該負荷電流検出手段からの出力に応じて変圧器の入力電圧または駆動PWM(パルス幅変調)のオン時間もしくはオンデューティを制御して前記負荷電流が所定値となるように出力電圧を制御する定電流制御手段と、前記出力電圧を検出する出力電圧検出手段と、前記出力電圧検出手段からの出力に基づいて前記変圧器の入力電圧または駆動PWMのオン時間もしくはオンデューティを制御して出力電圧が所定値となるように制御する出力電圧制御手段とを有する電源回路において、前記出力電圧制御手段の起動/停止を制御する起動/停止制御手段と、所定の出力電流制御値を設定する出力電流制御値設定手段とを具備し、所望の電圧が得られるように初めに前記起動/停止制御手段により前記出力電圧制御手段を起動させ、前記出力電圧検出手段により検出される電圧が前記所望の電圧に到達した後、前記起動/停止制御手段により前記出力電圧制御手段の動作を停止させると共に、出力電流制御値設定手段により目標出力電流制御値を設定し、前記定電流制御手段により定電流制御を開始することを特徴とするものである。

30

【0067】

また、上記第2の目的を達成するために本発明の請求項3記載の電源回路は、負荷電流を検出する負荷電流検出手段と、該負荷電流検出手段からの出力に応じて変圧器の入力電圧または駆動PWM(パルス幅変調)のオン時間もしくはオンデューティを制御して前記負荷電流が所定値となるように出力電圧を制御する出力電圧制御手段と、前記負荷電流を検出する負荷電流検出手段とを有する電源回路において、前記出力電圧制御手段の定電流制御動作が開始して所定時間経過後も前記負荷電流検出手段の検出値が所定値以下である場合、前記出力電圧制御手段の動作を停止または中断するように制御する出力動作制御手段を具備したことを特徴とするものである。

40

【0068】

また、上記第2の目的を達成するために本発明の請求項4記載の電源回路は、請求項3

50

記載の電源回路において、前記出力電圧制御手段の定電流制御動作が開始して所定時間経過後も前記負荷電流検出手段の検出値が所定値以下である場合、その旨を電源回路の動作を指示する外部装置に通知する通知手段を具備したことを特徴とするものである。

#### 【0070】

また、上記第3の目的を達成するために本発明の請求項5記載の電源回路は、一端を所定の直流電圧入力とし且つ他端を所定状態にオン／オフ動作させる一次巻線と前記一次巻線のオフ時にエネルギーを取り出す少なくとも1つフライバック巻線と前記一次巻線のオン時にエネルギーを取り出す少なくとも1つのフォワード巻線と前記一次巻線のオフ時及びオン時の全周期に亘ってエネルギーを取り出す高圧出力巻線とを含むトランスと、前記フライバック巻線の整流出力電圧を検出する電圧検出手段と、該電圧検出手段の検出結果により前記一次巻線のオン動作時間を制御し且つ前記フライバック巻線の整流出力電圧を所定値に制御する主制御手段と、前記フォワード巻線の出力の整流平滑電圧を比較用基準電圧と比較し、前記フォワード巻線に設けられたスイッチング素子を制御することにより前記整流平滑電圧を目標値に制御する副制御手段とを有する電源回路において、前記副制御手段は、前記主制御手段の起動時に前記フライバック巻線の整流出力電圧が所定値を超えるまで前記フォワード巻線の出力の1サイクル中の導通時間を所定値以下に抑制することにより、前記主制御手段が正常な制御状態になった後に前記フォワード巻線の出力の整流平滑電圧をオン／オフ制御可能とすることを特徴とするものである。

#### 【0071】

また、上記第3の目的を達成するために本発明の請求項6記載の電源回路は、請求項5記載の電源回路において、前記副制御手段は、前記主制御手段の起動時に前記フライバック巻線の整流出力電圧が所定値を超えると前記比較用基準電圧を徐々に増加させることを特徴とするものである。

#### 【0072】

また、上記第3の目的を達成するために本発明の請求項7記載の電源回路は、請求項5記載の電源回路において、前記副制御手段は、前記フォワード巻線の出力の整流平滑電圧と比較用基準電圧との比較出力を所定のパターン信号と比較する比較手段を有し、前記主制御手段の起動時に前記フライバック巻線の整流出力電圧が所定値を超えるまで、前記フォワード巻線の出力の整流平滑電圧と比較用基準電圧との比較出力を制限することを特徴とするものである。

#### 【0075】

##### 【発明の実施の形態】

以下、本発明の各実施の形態を図1～図17に基づき説明する。

#### 【0076】

##### (第1の実施の形態)

まず、本発明の第1の実施の形態を図1～図3に基づき説明する。尚、本実施の形態に係る電源回路の定電圧制御回路を除く基本的な構成は、上述した従来の図18に示す構成と同一であるから、同図を流用して説明する。

#### 【0077】

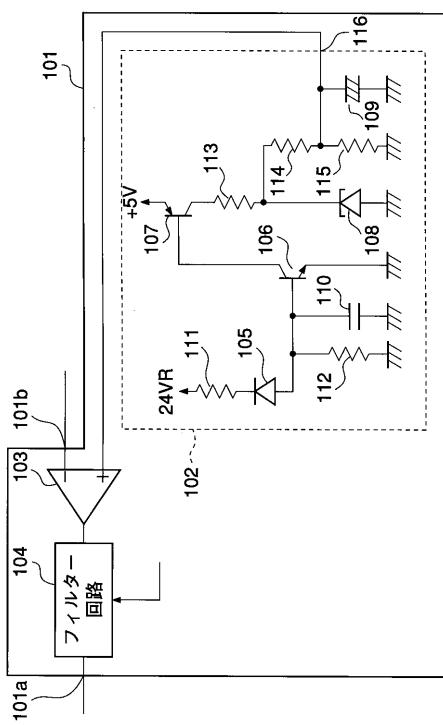

図1は、本発明の第1の実施の形態に係る電源回路における定電圧制御回路の構成を示すプロック図であり、同図中、101は定電圧制御回路で、制御用比較電圧生成回路102、比較器103、フィルター回路104を有している。

#### 【0078】

制御用比較電圧生成回路102は、ツエナーダイオード105、トランジスタ106, 107、基準電圧発生素子108、コンデンサ109, 110、抵抗111, 112, 113, 114, 115を有している。尚、101aは24V用スイッチング素子14の駆動信号出力部、101bは24V平滑出力検出信号入力部である。

#### 【0079】

ツエナーダイオード105は、24VRの電圧を検出するための素子で、本実施の形態ではオン電圧を16ボルト(V)とする。電源起動時、主制御対象であるフライバック出力

10

20

30

40

50

(以下、24VRと称する)が16Vを越えたところで、ツェナーダイオード105がオンし、後段のトランジスタ106, 107をオンさせる。この結果、基準電圧発生素子108に電圧が供給され、24VUの定電圧制御用比較電圧116が後段の比較器103に送られ、また、この比較器103には24VU平滑出力検出入力部101bを介して24VU平滑出力検出信号が送られる。そして、この比較器103により24VUの定電圧制御用比較電圧116と24VU平滑出力検出信号とが比較される。ここで、比較電圧116の出力部には所定の時定数回路が構成されており、所定の傾きを持ってソフトアップすることとなる。

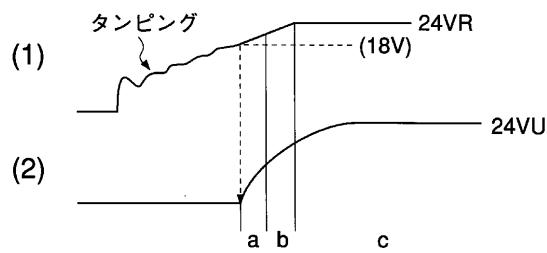

#### 【0080】

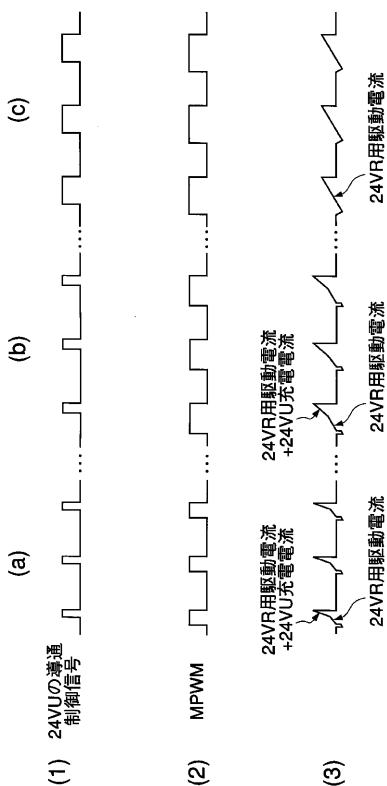

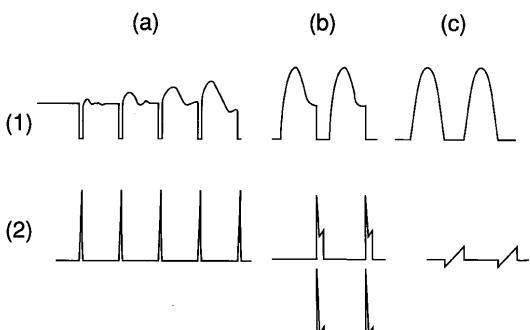

この様子を図2に示し、同図の(1)は24VRの出力、(2)は24VUの出力を示す。上述したように24VUの比較電圧値がソフトアップするため、24VUの出力電圧値も定電圧制御によって同型のソフトアップとなる。図2中、a, b, cの各期間の主制御ループのPWM信号、24VUの導通制御信号(24VU用スイッチング素子14の駆動信号)及び一次側スイッチング素子4の駆動電流の出力タイミングを図3に示す。同図の(1)は24VUの導通制御信号、(2)は主制御ループのPWM信号、(3)は一次側スイッチング素子の駆動電流である。

#### 【0081】

24VRを制御するための主制御信号MPWMは期間a, b, cと時間推移するのに伴って目標電圧値がソフトアップされるため徐々にオンデューティが増加していく。一方、24VUの導通制御信号は上述したように24VRが16Vを越えたところから制御電圧値がソフトアップするという違いはあるが、やはり期間a, b, cと時間推移するのに伴って徐々にオンデューティが増加していく。これにより、24VUの出力電圧が低く、24VUの巻線出力電流及びその時間上昇率が大きくなる期間aでも、24VUの導通制御素子であるスイッチング素子14のオン期間は短く絞られているために、一次側の最大ピーク電流は所定値以下に押さえられる。図3において、一次側スイッチング素子4の駆動電流に2つの傾きがあるのは、24VRのライバックエネルギー用の駆動信号のみ流れている期間と、24VUの導通制御素子であるスイッチング素子14がオンし、24VUの出力平滑コンデンサ17への充電電流分が重畠される期間があるためである。24VUの出力平滑コンデンサ17への充電電流の傾きは、24VUの電圧が大きくなるのに伴って小さくなり、最終的にはほぼ0となるため(24VUの外部負荷9がオンしていない期間内の説明であり、もちろん、外部負荷9がオンすれば、その電流分が重畠される)、24VRの駆動電流のみとなる。

#### 【0082】

以上のように、本実施の形態に係る電源回路によれば、24VUの制御用比較電圧値を、24VRを監視して所定値以上になったところからソフトアップスタートするようにすることで、常に主制御ループが正常な制御状態に入ったところからフォワード巻線23の制御を開始することができ、また、フォワード巻線23の起動時の大きな充電電流値をソフトアップすることができ、一次側駆動電流の電流負荷を軽減することができる。

#### 【0083】

(第2の実施の形態)

次に、本発明の第2の実施の形態を図4及び図5に基づき説明する。尚、本実施の形態に係る電源回路の定電圧制御回路を除く基本的な構成は、上述した従来の図18に示す構成と同一であるから、同図を流用して説明する。

#### 【0084】

上述した第1の実施の形態では24VUの制御用比較電圧をソフトアップさせることができたが、本実施の形態では、目標電圧値と検出電圧値との比較結果に対して、所定の条件下で二次側フォワード巻線32の最大導通期間を制限できるようにしたことを特徴とするものである。

#### 【0085】

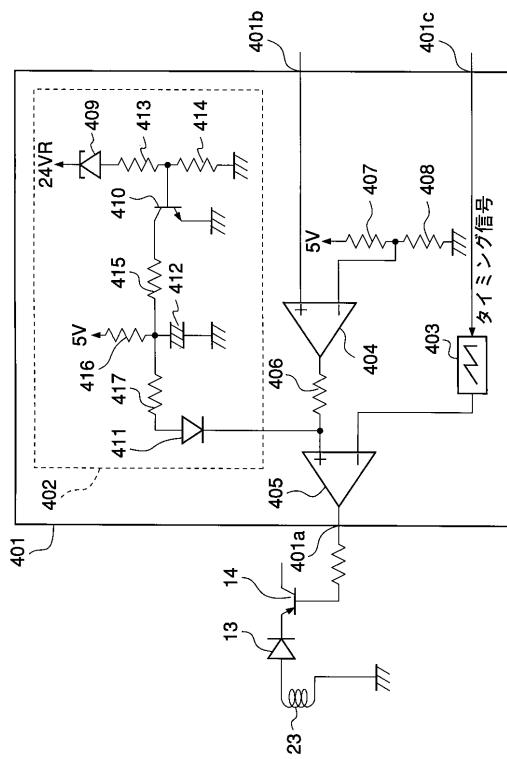

図4は、本発明の第2の実施の形態に係る電源回路における定電圧制御回路の構成を示す

10

20

30

40

50

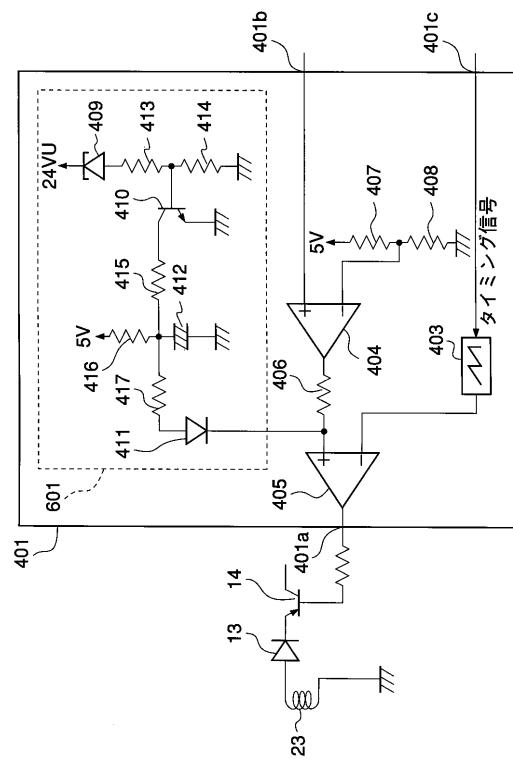

ブロック図であり、同図において、401は定電圧制御回路で、スライスレベルの制限回路402、三角波生成回路403、比較器404、405、抵抗406、407、408を有している。尚、401aは24VU用スイッチング素子14の駆動信号出力部、401bは24VU平滑出力検出信号入力部、401cはスイッチング素子4の駆動信号入力部である。

#### 【0086】

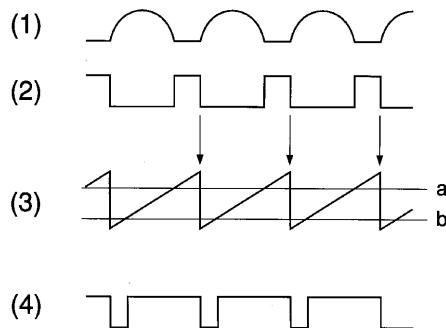

三角波生成回路403は、スイッチング素子4の駆動信号入力部401cから入力する一次側フライバック波形のゼロクロスタイミング信号を基準にして図5に示すような位相で三角波を生成する。図5の(1)はトランスの一次側の信号、(2)はスイッチング素子4のベースに入る駆動信号、(3)は三角波生成回路403により生成された三角波、(4)は24VU用スイッチング素子14の駆動信号出力部401aから出力する駆動信号である。

10

#### 【0087】

比較器404は、比較電圧と24VU平滑出力検出信号入力部401bを介して入力する検出電圧とを比較する。比較器405は、三角波生成回路403の出力と比較器404の出力とを比較し、24VU巻線の導通制御用PWM信号(24VU用スイッチング素子14の駆動信号)を生成する。定常状態においては、比較器404の出力は、所定のアナログレベルに安定し、三角波をスライスし、24VU巻線の導通制御用PWM信号を発生させる。

#### 【0088】

20

次に、本実施の形態の特徴である制限回路402がどのように機能するかを説明する。

#### 【0089】

制限回路402は、ツエナーダイオード409、トランジスタ410、ダイオード411、コンデンサ412、抵抗413、414、415、416、417を有している。ツエナーダイオード409は、24VRの電圧をモニターするための素子で、本実施の形態では16Vとする。24VRが16V以下のレベルではトランジスタ410はオフとなり、時定数回路のコンデンサ412には5Vの電圧が充電されている。この状態では、24VUの電圧が立ち上がる前で、比較電圧と検出電圧との比較結果がLに張り付いた状態であっても比較器404の出力抵抗406と時定数回路の出力抵抗416及びダイオード411の順電圧のバランスにより、24VUの巻線出力の導通期間を0もしくは所定値以下になるようにスライスレベルを強制的に規定するような機能を実現する。

30

#### 【0090】

この様子を表わす図が図5であり、比較器404のみの上述した第1の実施の形態の場合のスライスレベルがbであり、本実施の形態の場合のスライスレベルがaである。

#### 【0091】

ここで、24VRが起動し、16Vを超えたところでトランジスタ410がオンし、時定数回路の出力レベルを漸次下げていく比較器404からの出力電圧以下となったところで、制限回路402の動作は終了する。時定数回路は24VUの立ち上がり速度を考慮に入れ、適切な時定数を設定する。

#### 【0092】

40

以上により、上述した第1の実施の形態の図3と同様に、24VRの起動状態と連係し、フォワード巻線23の導通角が所定のソフトアップを行うようにすることができる。

#### 【0093】

##### (第3の実施の形態)

次に、本発明の第3の実施の形態を図6に基づき説明する。尚、本実施の形態に係る電源回路の定電圧制御回路を除く基本的な構成は、上述した従来の図18に示す構成と同一であるから、同図を流用して説明する。

#### 【0094】

本実施例の特徴は、スライスレベルの制限回路において監視する電圧を24VU自身にしたことである。

50

## 【0095】

図6は、本発明の第3の実施の形態に係る電源回路における定電圧制御回路の構成を示すブロック図であり、同図において、上述した第2の実施の形態における図4と同一構成部分には同一符号が付してある。図6において図4と異なる点は、制限回路の構成である。即ち、本実施の形態における制限回路601は、監視する電圧を24VU自身にしたことにより、24VUが所定値以下の場合はスライスレベルを強制的にシフトさせ、24VU巻線の導通角を起動時には所定の時間に制限することができる。

## 【0096】

本実施の形態の場合は、第2の実施の形態の場合に比べて時定数回路の時定数設計が容易であるという利点がある。つまり、本実施の形態では24VUの立ち上がり時間によらず、24VU自身が所定値まで上昇するまでは強制的に24VU巻線の導通角を所定値以下に制限するため、電源ユニットへの入力電圧（例えば、商用AC電源電圧）の大きさ、24VUの外部負荷の容量の大きさ、また、起動中にも外部負荷がオンする場合には、その負荷電流値の大きさ等の差による実際の24VUの立ち上がり速度差を考慮に入れる必要がなくなる。

## 【0097】

## (第4の実施の形態)

次に、本発明の第4の実施の形態を図7に基づき説明する。尚、本実施の形態に係る電源回路の定電圧制御回路を除く基本的な構成は、上述した従来の図18に示す構成と同一であるから、同図を流用して説明する。

## 【0098】

本実施例の特徴は、スライスレベルの制限回路において、スライスレベル制限機能のオン／オフを主制御部9から入力するようにしたことである。

## 【0099】

図7は、本発明の第4の実施の形態に係る電源回路における出力制限回路の構成を示すブロック図であり、同図において、上述した第3の実施の形態における図6と同一構成部分には同一符号が付してある。本実施の形態における制限回路701は、図6の制限回路601の構成からツェナーダイオード409及び抵抗414を削除したもので、スライスレベル制限機能のオン／オフが主制御部9から入力される。主制御部9は、24VRの制御を行っており、24VRの制御状態（オン、オフ、起動中等）認識できるので、例えば、24VRが所定の電圧になった後、所定時間経過後、制限回路701の機能を抑制する等の処理が可能である。

## 【0100】

## (第5の実施の形態)

次に、本発明の第5の実施の形態を図8～図10に基づき説明する。

## 【0101】

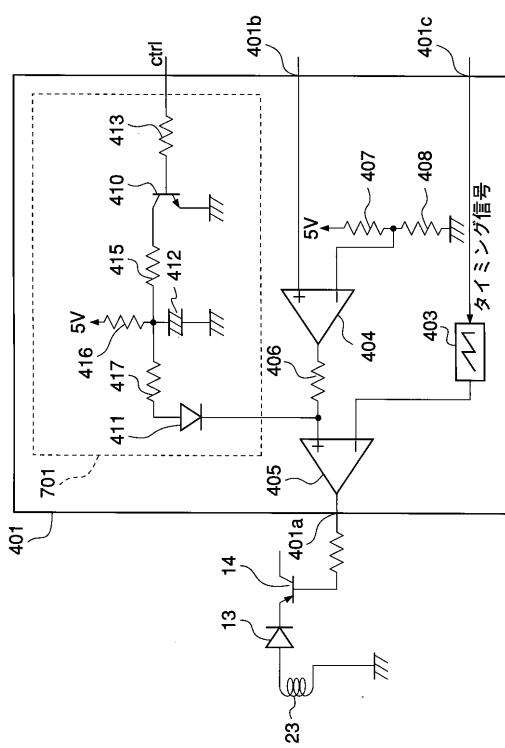

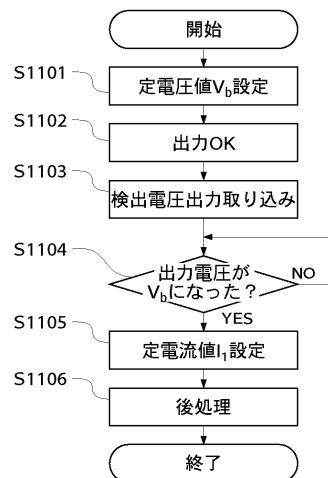

図8は、本発明の第5の実施の形態に係る電源回路の構成を示すブロック図である。同図において、上述した従来の図23と同一構成部分には同一符号が付してある。図8において、図23と異なる点は、図23の構成に定電流設定値切換回路801を付加し、定電流制御回路の電流設定値を定電流設定値切換回路801を通して、電源コントローラ67より2段階に設定可能としたことである。定電流設定値切換回路801は、トランジスタ802、抵抗803、804、805を有している。

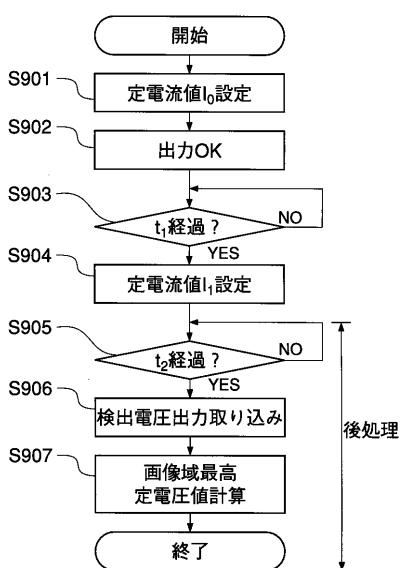

## 【0102】

次に、本実施の形態に係る電源回路の動作を図8、図9及び図10を用いて説明する。図9は、本実施の形態に係る電源回路の動作制御手順を示すフローチャート、図10は、本実施の形態に係る電源回路の動作概要を示すための出力電圧の時間変化を示す曲線図である。図10の例では、定電流制御回路による負荷容量に対する充電速度を主たる議論の中心とするために、電圧立ち上がり波形は、起動後の適当期間を直線的に表わし、その後、 $e \times p$ に近い曲線で近似したものと考える。

## 【0103】

10

20

30

40

50

まず、外部コントローラより負荷抵抗測定開始命令を受け取る。すると、定電流制御回路の電流設定値を最終目標電流  $I_1$  よりも 2 倍大きい  $I_0$  に設定する（ステップ S 901）。本実施の形態では電源コントローラ 67 が定電流設定値切換回路 801 のトランジスタ 802 をオンする信号を出力することに対応する。その後、発振回路 38 に対してオン信号を出力し、高圧出力を開始する（ステップ S 902）。このとき、出力電圧は図 10 の a のように、最終目標  $I_1$  でスタートさせた場合の立ち上がり b より 2 倍の傾きで出力電圧を上昇させる。

#### 【0104】

次いでステップ S 903 で電源コントローラ 67 では、出力開始後の経過時間を計測し、その計測結果に基づいて予め決められた時間  $t_1$  が経過したか否かを経過するまで判断する（ステップ S 903）。そして、予め決められた時間  $t_1$  が経過したところで、定電流設定値を  $I_1$  に切り換え設定する（ステップ S 904）。最終的な出力電圧は、最終的な出力定電流値と負荷の抵抗成分の変動が通常ある範囲内の中で変動すると考えて良く、本実施の形態では図 10 の V a から V b までと想定する。

10

#### 【0105】

今、最終出力電圧が V a となるような負荷を考えると、切り換えたときの出力電圧値 V c h からは電圧の傾きが 1/2 程度に落ちて上昇が始まり、ゆっくりと曲線を描きつつ、最終値に到達していく。そして、出力開始後の経過時間計測結果に基づいて予め決められた時間  $t_2$  が経過したか否かを経過するまで判断する（ステップ S 905）。そして、予め決められた時間  $t_2$  が経過したところで、検出巻線出力が取り込まれ（ステップ S 906）、画像域最高定電圧値が計算された後、本処理動作を終了する。これにより、ほぼ負荷容量は完全に充電され、出力電圧は、ほぼ一定となる。

20

#### 【0106】

初めの定電流値を  $I_0$  とした場合と  $I_1$  とした場合とで V c h を得るために必要な期間は、約 2 倍程度の差が生じるため、最終電圧値を得るために時間は、本実施の形態においては、概ね  $t_1$  程度短縮することが可能となる。

#### 【0107】

最終出力が V b となるような負荷の場合には、切り換え後に図 10 の c のような直線になり、このときは電圧変化の時定数に高圧トランス 30 内部のブリーダ抵抗の放電部分が加味されて、より速い応答となり、すばやく最終値に到達する。

30

#### 【0108】

##### （第 6 の実施の形態）

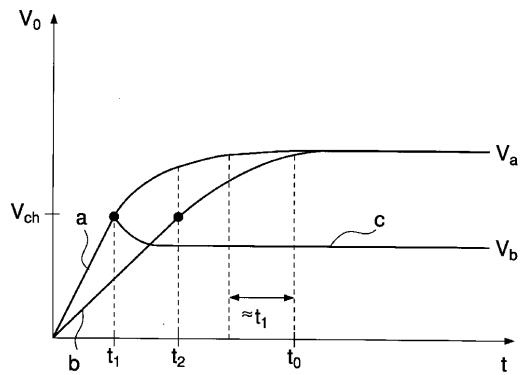

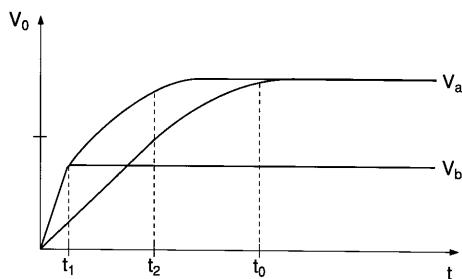

次に、本発明の第 6 の実施の形態を図 11 及び図 12 に基づき説明する。尚、本実施の形態に係る電源回路の基本的な構成は、上述した第 5 の実施の形態の図 8 と同一であるから、同図を流用して説明する。

#### 【0109】

図 11 は、本実施の形態に係る電源回路の動作制御手順を示すフローチャート、図 12 は、本実施の形態に係る電源回路の動作概要を示すための出力電圧の時間変化を示す曲線図である。

#### 【0110】

まず、外部コントローラより負荷抵抗測定開始命令を受け取る。すると、図 11 において、まず、電源回路は定電圧値を V b に設定し（ステップ S 1101）、出力電圧を V b 一定とするような定電圧制御モードによる制御を開始する。その後、発振回路 38 に対してオン信号を出力し（ステップ S 1102）、出力電圧 V b に対応した検出巻線電圧が得られるように、逐次検出巻線出力を取り込み（ステップ S 1103）、整流平滑回路 68 を通して A/D 入力し、出力電圧が V b になったか否かを、V b になるまで判断する（ステップ S 1104）。その判断結果に基づいて定電圧制御回路 52 からの出力電圧のレベルを出力ポートのオン / オフ率を切り換えることにより実現する。このとき、回路動作は、負荷電流に無関係に、目標電圧値に向かって電源回路がもつ最大の出力能力で出力電圧を上昇させていくと考えて良い。そして、出力電圧が V b なったところで、定電流設定値を

40

50

I 1に切り換え設定し(ステップS 1105)、電源回路を定電流モードに切り換えるべく、定電圧制御回路52の出力をオフ(0ボルト)とする。すると、Vbから目的の定電流値を得るべく定電流制御ループが機能し、上述した第5の実施の形態における図9のステップS 905～ステップS 907までと同様の後処理を行う(ステップS 1106)。

#### 【0111】

本実施の形態に係る電源回路によれば、Vbまでは電源回路がもつ最大出力能力により、出力電圧を上昇させるため、切り換え前の電圧上昇を最速とすることができる。Vbとしては通常の負荷変動域のうち最も低い抵抗値に対して、所望の定電流をかけた電圧を設定することによって、過渡的な電圧オーバーシュートを非常に小さくできる。

#### 【0112】

##### (第7の実施の形態)

次に、本発明の第7の実施の形態を図13及び図14に基づき説明する。図13は、本発明の第7の実施の形態に係る電源回路における出力制限回路の構成を示すブロック図である。

#### 【0113】

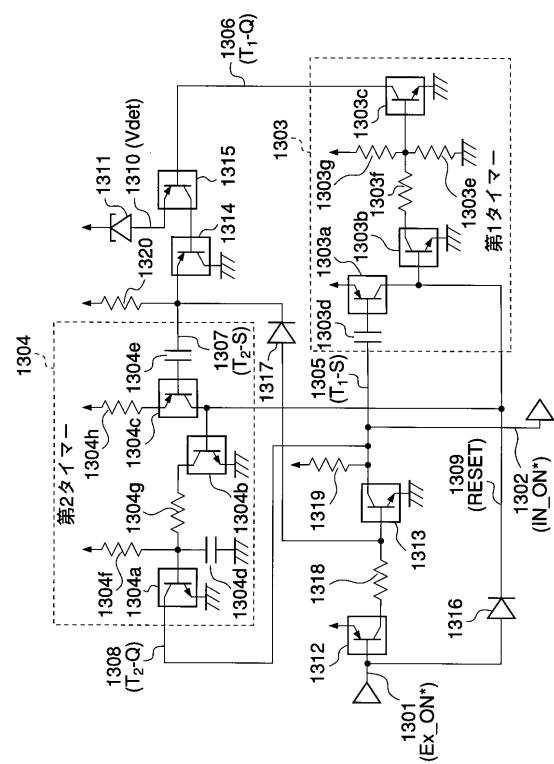

図13において、1301は外部制御ユニットから電源回路内に高圧の出力オン／オフを指令する外部信号で、本図ではEX-ON\*と表わし、H(ハイレベル)で出力オフ、L(ローレベル)で出力オンを命令するものと論理規定する。1302はEX-ON\*信号を受けて、高圧回路の動作を実際にオン／オフさせる内部信号で、IN-ON\*と表わし、H(ハイレベル)で出力オフ、L(ローレベル)で出力オンを命令するものと論理規定する。1303は第1タイマーで、EX-ON\*がLとなったことを受け、IN-ON\*がLになった時刻から所定の時間、内部オン\*をLにさせるために時間を計測する。この第1タイマー1303は、トランジスタ1303a、1303b、1303c、コンデンサ1303d、1303e、抵抗1303f、1303gを有している。

#### 【0114】

また、図13において、1304は第2のタイマーで、第1タイマー1303により所定時間、IN-ON\*がLになった後、負荷電流検出手段から負荷電流が所定値しか流れていなことを検知した際に、所定の時間IN-ON\*をHにさせるものである。この第2のタイマー1304は、トランジスタ1304a、1304b、1304c、コンデンサ1304d、1304e、抵抗1304f、1304g、1304hを有している。

#### 【0115】

また、図13において、1305は第1タイマー1303をスタートさせる信号(T1-S)、1306は第1タイマー1303の計測結果信号(T1-Q)、1307は第2タイマー1304をスタートさせる信号(T2-S)、1308は第2タイマー1304の計測結果信号(T2-Q)、1309は第1タイマー1303及び第2タイマー1304の時間計測動作をリセットさせる信号(RESET)、1310は負荷電流検出手段からの出力信号(Vdet)で、本実施の形態では上述した従来例の図24に示したような電圧・電流特性を持つものを想定する。1311は負荷電流が所定値以下か、以上かを判別するための電圧判別手段で、本実施の形態では2.4Vにてオンするツェナーダイオードである。

#### 【0116】

また、図13において、1312、1313、1314、1315はトランジスタ、1316、1317はダイオード、1318、1319、1320は抵抗である。

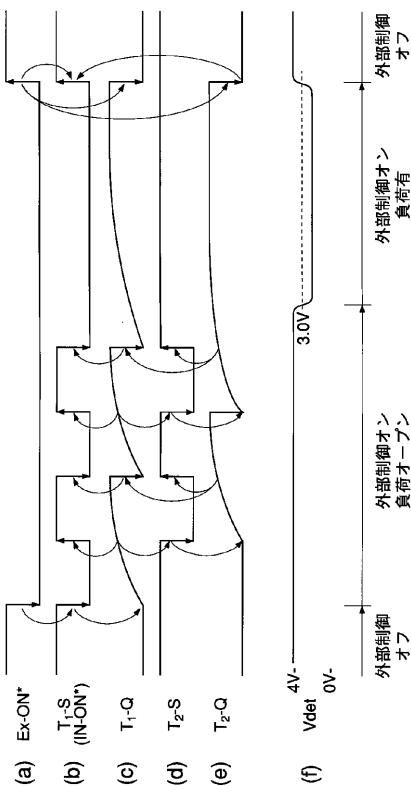

#### 【0117】

図14は、図13における各信号の出力タイミングを示すタイムチャートである。同図の(a)はEX-ON\*、(b)はT1-S(IN-ON\*)、(c)はT1-Q、(d)はT2-S、(e)はT2-Q、(f)はVdetをそれぞれ示す。

#### 【0118】

次に、上記構成の電源回路における出力制限回路の動作を、図13及び図14を用いて説明する。

10

20

30

40

50

## 【0119】

まず、外部制御信号EX-ON\*がHで、高圧出力オフの定常状態を考える。EX-ON\*=Hのため、RESET=Hとなり、第1タイマー1303及び第2タイマー1304は共にリセット状態となり、T1-Q、T2-Qは共にオープン状態となる。IN-ON\*はもちろんHとなり、高圧出力はオフ状態となる。

## 【0120】

次に、負荷電流値が設定され(図14のタイムチャートには図示せず)、その後、EX-ON\*がLになった場合を考える。EX-ON\*=Lになったことを受け、両タイマー1303, 1304へのRESETはLとなり、リセット状態は解放される。そして、IN-ON\*=Lとなり、高圧出力回路が所定の負荷電流が得られるまで出力電圧を上昇させる動作を開始する。これと同時にT1-SはLになり、これをトリガーに第1タイマー1303がIN-ON\*=Lの時間計測を開始する。

10

## 【0121】

第1タイマー1303がタイムアップするとT1-Q=Lとなり、このとき、もし負荷電流が所定値以上流れていらない場合(本実施の形態ではVdetが約3V以下になっていない場合)、これを受け電圧検出手段が1311が導通し、2段のトランジスタ1314, 1315をオンさせる。これを受けIN-ON\*の前段のトランジスタ1313のベース入力をダイオード1317を介してLにし、IN-ON\*を強制的にHに戻し、高圧出力動作を中断させる。また、これと同時に第2タイマー1304のT2-SがLになり、高圧出力を中断させる時間の計測を開始させる。

20

## 【0122】

第2タイマー1304がタイムアップするとT2-QがLになり、IN-ON\*を再びLにし、高圧出力をオンさせると共に、T1-SがLになり、これをトリガーに第1タイマー1303がIN-ON\*=Lの時間計測を開始する。負荷ケーブルが抜かれる等、何等かの理由で負荷抵抗が所定値以上の値になっている状態では、外部制御信号EX-ON\*がLである間、以上の動作を繰り返すこととなる。通常の負荷が正常に接続された場合、負荷電流検出手段からの出力が所定値以下となり、電圧判別手段1311がオフとなり、高圧出力動作の中止シーケンスは回避される。また、外部制御信号EX-ON\*がHとなつた場合には初期状態に戻り、高圧出力オフとなる。

30

## 【0123】

以上のように、本実施の形態に係る電源回路によって、負荷ケーブルの引き抜き等により負荷抵抗の値が通常の値に比して非常に大きくなつた場合には、出力動作を電源回路内で独立に間欠動作とすることができます。

## 【0124】

## (第8の実施の形態)

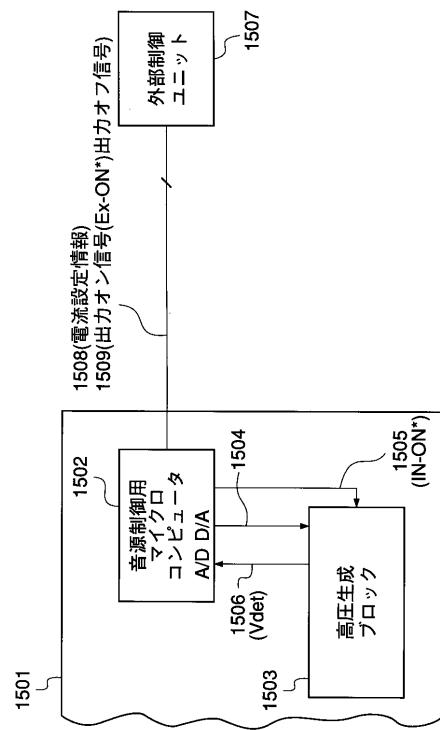

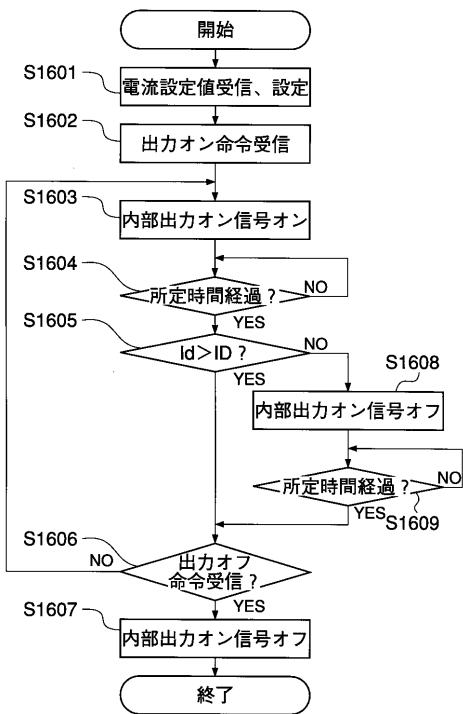

次に、本発明の第8の実施の形態を図15及び図16に基づき説明する。本実施の形態に係る電源回路は、他の機能ブロック、例えば低圧電源回路、蛍光灯インバータ回路、ヒータ制御回路等を含み、それらの複雑なシーケンス制御を行う必要がある場合等に適用される。

## 【0125】

図15は、本発明の第8の実施の形態に係る電源回路の構成を示すブロック図であり、同図において、1501は電源回路で、電源制御用マイクロコンピュータ(以下、電源コントローラと称する)1502、高圧生成ブロック1503を有している。電源コントローラ1502は、電源回路1501全体の制御を行う。高圧生成ブロック1503は、電源コントローラ1502のD/Aポートから出力される出力負荷電流設定信号(情報)1504及び内部出力オン信号(IN-ON\*)1505を受け、高圧生成動作を行う。高圧生成ブロック1503から電源コントローラ1502のA/Dポートに負荷電流検出手段からの出力電圧Vdetが取り込まれる。また、電源コントローラ1502には外部制御ユニット1507が接続され、該外部制御ユニット1507から電源コントローラ1502に負荷電流の設定情報1508や出力オン信号(EX-ON\*)/出力オフ信号1509

40

50

9が送られる。

【0126】

次に、本実施の形態に係る電源回路における電源コントローラ1502の動作を、図16のフローチャートに基づき説明する。

【0127】

まず、外部制御ユニット1507から通信により（プロトコルその他の詳細構成は各種考えられるので、ここではとくに言及しない）、電源コントローラ1502に対して負荷電流の設定信号1504及び内部出力オン信号（IN-ON\*）1505が伝えられる。これを受けた高圧生成ブロック1503に対して電源コントローラ1502のD/Aポートから対応する負荷電流制御用目標電圧1504が設定される（ステップS1601及びステップS1602）。

【0128】

本実施の形態では、「D/Aポートより」と記述したが、例えば、所定の周波数及びデューティを持つPWM（パルス幅変調）信号を出力ポートより出力し、これをローパスフィルタに通し、アナログ電圧を得ること等の方法も考えられる。

【0129】

次に、高圧生成ブロック1503に対して出力動作のオンを伝える内部出力オン信号（IN-ON\*）=Lが出力される（ステップS1603）。以上により高圧生成ブロック1503は負荷電流が所定値となるべく、出力電圧を上昇させる。その後、電源コントローラ1502内の時間管理によって、所定時間が経過したか否かを経過するまで判別する（ステップS1604）。後、負荷電流検出手段からの出力電圧Vdetを電源コントローラ1502のA/Dポートより取り込み、負荷電流Idが所定値ID以上になっているか否か判別する（ステップS1605）。そして、負荷電流Id > IDの場合は、出力オフ信号を外部制御ユニット1507から受信したか否かを判別し（、受信した場合には、内部出力オン信号（IN-ON\*）をオフとして高圧出力動作を終了する。また、出力オフ信号を外部制御ユニット1507から受信しない場合には、再び所定時間経過後、負荷電流の判別を行うために、先のステップS1603における内部出力オン信号（IN-ON\*）=オンのシーケンスに戻る。

【0130】

一方、前記負荷電流Id < IDの場合は、内部出力オン信号（IN-ON\*）を所定時間の間一旦オフした後（ステップS1608）、同様に外部制御ユニット1507から出力オフ信号を受信したか否かの判別シーケンスに入り、電源コントローラ1502内の時間管理によって、所定時間が経過したか否かを経過するまで判別する（ステップS1609）。その後、同様に外部制御ユニット1507から出力オフ命令信号を受信したか否かの判別シーケンスに入り、上記と同様な手順を踏むものである。

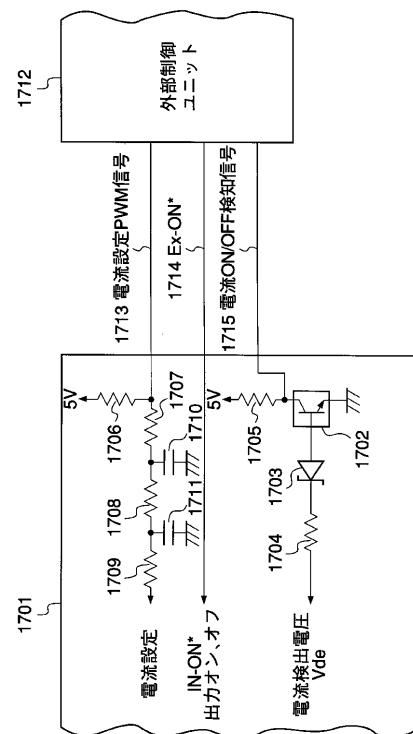

【0162】

（第9の実施の形態）

次に、本発明の第9の実施の形態を図17に基づき説明する。図17は、本発明の第9の実施の形態に係る電源回路の構成を示すブロック図であり、同図において、1701は電源回路で、トランジスタ1702、ツエナーダイオード1703、抵抗1704, 1705, 1706, 1707, 1708, 1709、コンデンサ1710, 1711を有している。そして、外部制御ユニット1712から電流設定PWM（パルス幅変調）信号1713、及び外部オン信号（EX-ON\*）1714が電源回路1701に入力される。また、電源回路1701から電流オン/オフ検知信号1715が入力される。

【0163】

本実施の形態に係る電源回路1701は、電源回路1701側に上述した第8の実施の形態で述べたような電源コントローラを具備しないような構成の場合に効果的である。

【0164】

次に、本実施の形態に係る電源回路1701の動作を説明する。

【0165】

10

20

30

40

50

まず、外部制御ユニット 1712 より電源コントローラに対して負荷電流の設定情報が伝えられる。本実施の形態では、電源回路 1701 に対して所定の周波数及びデューティを持つ PWM (パルス幅変調) 信号を外部制御ユニット 1712 の出力ポートから出力し、これをローパスフィルタを用いてフィルタリングしてアナログ電圧を得る構成例を示している。次に、出力動作のオンを伝える EX-ON\*=L が出力される。以上によって、電源回路は負荷電流が所定値となるべく出力電圧を上昇させる。

#### 【0166】

その後、外部制御ユニット 1712 での時間管理によって、所定時間が経過した後、負荷電流検出手段からの出力を読み込み、負荷電流 ID が所定値 ID 以上になっているか否かを判別する。

10

#### 【0167】

$I_d < ID$  の場合、EX-ON\* を H として高圧出力動作を一旦中断させる。その後、必要に応じて同じ手順で出力命令を出し、所定時間経過後、負荷電流をチェックするシーケンスを繰り返す。更に、必要であれば、最大繰り返し回数を設定し、所定回数、再出力命令を発行しても負荷電流が所定値以上を示さない場合は、高圧負荷以上として、装置としてのエラー処理に移行する等の処置も外部制御ユニット 1712 のシーケンス構成により可能である。また、 $I_d > ID$  の場合は、出力中断手順をスキップする。

#### 【0168】

以上のように本実施の形態に係る電源回路 1701 によれば、電源回路 1701 にマイクロコンピュータ等の電源コントローラが具備されていない場合にも、負荷電流値の判別結果のみをシーケンス制御手段を利用し、出力動作を間欠動作させるか、または出力動作を強制的に終了させ、装置としてのエラーシーケンス々移行する等の高度の保護処理が可能である。

20

#### 【0169】

#### 【発明の効果】

以上詳述したように本発明の請求項 1 及び 2 に記載の電源回路によれば、可能な限り迅速に負荷への出力を定常状態にすることができる。

#### 【0170】

また、本発明の請求項 3 及び 4 に記載の電源回路によれば、負荷に印加される電圧が過大になることを防止することができる。

30

#### 【0171】

更に、本発明の請求項 5 乃至 7 に記載の電源回路によれば、トランスの一時側に大きな電流が流れてしまうことを防止することができる。

#### 【図面の簡単な説明】

【図 1】本発明の第 1 の実施の形態に係る電源回路における定電圧制御回路の構成を示すブロック図である。

【図 2】同実施の形態に係る電源回路における信号出力状態を示す図である。

【図 3】同実施の形態に係る電源回路における各信号及び駆動電流の出力タイミングを示す図である。

【図 4】本発明の第 2 の実施の形態に係る電源回路における定電圧制御回路の構成を示すブロック図である。

40

【図 5】図 4 に示す定電圧制御回路における各信号波形を示す図である。

【図 6】本発明の第 3 の実施の形態に係る電源回路における定電圧制御回路の構成を示すブロック図である。

【図 7】本発明の第 4 の実施の形態に係る電源回路における出力制限回路の構成を示すブロック図である。

【図 8】本発明の第 5 の実施の形態に係る電源回路の構成を示すブロック図である。

【図 9】同実施の形態に係る電源回路の動作制御手順を示すフローチャートである。

【図 10】同実施の形態に係る電源回路の動作概要を示す図である。

【図 11】本発明の第 6 の実施の形態に係る電源回路の動作制御手順を示すフローチャー

50

トである。

【図12】同実施の形態に係る電源回路の動作概要を示す図である。

【図13】本発明の第7の実施の形態に係る電源回路における出力制限回路の構成を示すブロック図である。

【図14】同実施の形態に係る電源回路における各信号の出力タイミングを示す図である。

【図15】本発明の第8の実施の形態に係る電源回路の構成を示すブロック図である。

【図16】同実施の形態に係る電源回路の動作制御手順を示すフローチャートである。

【図17】本発明の第9の実施の形態に係る電源回路の構成を示すブロック図である。

【図18】従来の電源回路の構成を示すブロック図である。

10

【図19】図18に示す従来の電源回路における定常時の主要な動作波形を示す図である。

【図20】図18に示す従来の電源回路における電圧立ち上がり波形を示す図である。

【図21】図20のa～cの各期間における各信号波形を示す図である。

【図22】図18に示す従来の電源回路における一次側スイッチング素子の波形を示す図である。

【図23】図18と異なる従来の電源回路の構成を示すブロック図である。

【図24】図18及び図23と異なる従来の電源回路の構成を示すブロック図である。

【図25】図24に示す従来の電源回路における負荷検出回路の電流電圧特性を示す図である。

20

【符号の説明】

1 商用A C電源

2 整流ブリッジ

3 第1の平滑コンデンサ

4 第1のスイッチング素子

5 共振コンデンサ

6 クランプダイオード

7 カレントランス

8 ドライブトランス

9 主制御部

30

10 第1のダイオード

11 第2の平滑コンデンサ

12 電圧検出抵抗

13 第2のダイオード

14 第2のスイッチング素子

15 フライホイールダイオード

16 整流用インダクタンス

17 第3の平滑コンデンサ

18 出力検出抵抗

19 副制御部

40

20 複合型トランス

21 一次巻線

22 低圧用フライバック巻線

23 低圧用フォワード巻線

24 高圧用巻線

25 高圧用巻線

26 第3のダイオード

27 第4の平滑コンデンサ

28 第4のダイオード

29 第5の平滑コンデンサ

50

|       |              |    |

|-------|--------------|----|

| 3 0   | 高圧トランス       |    |

| 3 1   | 出力巻線         |    |

| 3 2   | 入力巻線         |    |

| 3 3   | 検出巻線         |    |

| 3 4   | 高耐圧整流ダイオード   |    |

| 3 5   | ブリーダ抵抗       |    |

| 3 6   | フォロワトランジスタ   |    |

| 3 7   | 平滑コンデンサ      |    |

| 3 8   | 発信器          |    |

| 3 9   | スイッチングトランジスタ | 10 |

| 4 0   | 共振コンデンサ      |    |

| 4 1   | クランプダイオード    |    |

| 4 2   | 出力(シリーズ)抵抗   |    |

| 4 3   | 負荷電流検出回路     |    |

| 4 4   | 抵抗           |    |

| 4 5   | 抵抗           |    |

| 4 6   | コンデンサ        |    |

| 4 7   | バッファ回路       |    |

| 4 8   | 演算増幅器        |    |

| 4 9   | 制御目標設定電圧     | 20 |

| 5 0   | フィルター回路      |    |

| 5 1   | ダイオード        |    |

| 5 2   | 定電圧制御ブロック    |    |

| 5 3   | トランジスタ       |    |

| 5 4   | トランジスタ       |    |

| 5 5   | ダイオード        |    |

| 5 6   | 抵抗           |    |

| 5 7   | 抵抗           |    |

| 5 8   | 抵抗           |    |

| 5 9   | 抵抗           | 30 |

| 6 0   | 抵抗           |    |

| 6 1   | 抵抗           |    |

| 6 2   | コンデンサ        |    |

| 6 3   | 高圧電源回路       |    |

| 6 4   | 外部負荷         |    |

| 6 5   | 抵抗           |    |

| 6 6   | コンデンサ        |    |

| 6 7   | 電源コントローラ     |    |

| 6 8   | 整流平滑回路       |    |

| 6 9   | ダイオード        | 40 |

| 7 0   | 抵抗           |    |

| 7 1   | 抵抗           |    |

| 7 2   | 抵抗           |    |

| 7 3   | コンデンサ        |    |

| 7 4   | 高圧トランス       |    |

| 7 5 a | 出力巻線         |    |

| 7 5 b | 入力巻線         |    |

| 7 6   | 高耐圧整流ダイオード   |    |

| 7 7   | 平滑コンデンサ      |    |

| 7 8   | 発信器          | 50 |

|       |                |    |

|-------|----------------|----|

| 7 9   | スイッチングトランジスタ   |    |

| 8 0   | 共振コンデンサ        |    |

| 8 1   | クランプダイオード      |    |

| 8 2   | 出力(シリーズ)抵抗     |    |

| 8 3   | 負荷電流検出回路       |    |

| 8 4   | バッファ回路         |    |

| 8 5   | 演算増幅器          |    |

| 8 6   | 制御目標設定電圧       |    |

| 8 7   | フィルター回路        |    |

| 8 8   | エミッタフォロワトランジスタ | 10 |

| 8 9   | 高圧電源回路         |    |

| 9 0   | 外部負荷           |    |

| 9 1   | 抵抗             |    |

| 9 2   | コンデンサ          |    |

| 9 3   | 外部制御ユニット       |    |

| 9 4   | 信号線            |    |

| 9 5   | 信号線            |    |

| 1 0 1 | 定電圧制御回路        |    |

| 1 0 2 | 制御用比較電圧生成回路    |    |

| 1 0 3 | 比較器            | 20 |

| 1 0 4 | フィルター回路        |    |

| 1 0 5 | ツエナーダイオード      |    |

| 1 0 6 | トランジスタ         |    |

| 1 0 7 | トランジスタ         |    |

| 1 0 8 | 基準電圧発生素子       |    |

| 1 0 9 | コンデンサ          |    |

| 1 1 0 | コンデンサ          |    |

| 1 1 1 | 抵抗             |    |

| 1 1 2 | 抵抗             |    |

| 1 1 3 | 抵抗             | 30 |

| 1 1 4 | 抵抗             |    |

| 1 1 5 | 抵抗             |    |

| 1 1 6 | 定電圧制御用比較電圧     |    |

| 4 0 1 | 定電圧制御回路        |    |

| 4 0 2 | 制御回路           |    |

| 4 0 3 | 三角波生成回路        |    |

| 4 0 4 | 第1の比較器         |    |

| 4 0 5 | 第2の比較器         |    |

| 4 0 6 | 抵抗             |    |

| 4 0 7 | 抵抗             | 40 |

| 4 0 8 | 抵抗             |    |

| 4 0 9 | ツエナーダイオード      |    |

| 4 1 0 | トランジスタ         |    |

| 4 1 1 | ダイオード          |    |

| 4 1 2 | コンデンサ          |    |

| 4 1 3 | 抵抗             |    |

| 4 1 4 | 抵抗             |    |

| 4 1 5 | 抵抗             |    |

| 4 1 6 | 抵抗             |    |

| 4 1 7 | 抵抗             | 50 |

|           |               |    |

|-----------|---------------|----|

| 6 0 1     | 制限回路          |    |

| 7 0 1     | 制限回路          |    |

| 8 0 1     | 定電流設定値切換回路    |    |

| 8 0 2     | トランジスタ        |    |

| 8 0 3     | 抵抗            |    |

| 8 0 4     | 抵抗            |    |

| 8 0 5     | 抵抗            |    |

| 1 3 0 1   | 外部信号 (EX-ON*) |    |

| 1 3 0 2   | 内部信号 (IN-ON*) |    |

| 1 3 0 3   | 第1タイマー        | 10 |

| 1 3 0 3 a | トランジスタ        |    |

| 1 3 0 3 b | トランジスタ        |    |

| 1 3 0 3 c | トランジスタ        |    |

| 1 3 0 3 d | コンデンサ         |    |

| 1 3 0 3 e | コンデンサ         |    |

| 1 3 0 3 f | 抵抗            |    |

| 1 3 0 3 g | 抵抗            |    |

| 1 3 0 4   | 第2タイマー        |    |

| 1 3 0 4 a | トランジスタ        |    |

| 1 3 0 4 b | トランジスタ        | 20 |

| 1 3 0 4 c | トランジスタ        |    |

| 1 3 0 4 d | コンデンサ         |    |

| 1 3 0 4 e | コンデンサ         |    |

| 1 3 0 4 f | 抵抗            |    |

| 1 3 0 4 g | 抵抗            |    |

| 1 3 0 4 h | 抵抗            |    |

| 1 3 0 5   | 信号 (T1-S)     |    |

| 1 3 0 6   | 計測結果信号 (T1-Q) |    |

| 1 3 0 7   | 信号 (T2-S)     |    |

| 1 3 0 8   | 計測結果信号 (T2-Q) | 30 |

| 1 3 0 9   | 信号 (RESET)    |    |

| 1 3 1 0   | 信号            |    |

| 1 3 1 1   | 電圧判別手段        |    |

| 1 3 1 2   | トランジスタ        |    |

| 1 3 1 3   | トランジスタ        |    |

| 1 3 1 4   | トランジスタ        |    |

| 1 3 1 5   | トランジスタ        |    |

| 1 3 1 6   | ダイオード         |    |

| 1 3 1 7   | ダイオード         |    |

| 1 3 1 8   | 抵抗            | 40 |

| 1 3 1 9   | 抵抗            |    |

| 1 3 2 0   | 抵抗            |    |

| 1 5 0 1   | 電源回路          |    |

| 1 5 0 2   | 電源コントローラ      |    |

| 1 5 0 3   | 高圧生成ブロック      |    |

| 1 5 0 4   | 出力負荷電流設定信号    |    |

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【 四 6 】

【図7】

【 図 8 】

【 図 9 】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

【図15】

【 図 1 6 】

【 図 17 】

【図18】

【図19】

【図20】

【図21】

【図22】

【 図 2 3 】

【 図 2 4 】

【 図 2 5 】

---

フロントページの続き

(56)参考文献 特開昭63-302727(JP,A)

特開昭59-010168(JP,A)

特開平08-214550(JP,A)

特開平08-051779(JP,A)

特開平08-022205(JP,A)

特開平06-335243(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H02M 3/28