(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6306704号

(P6306704)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/78 652J

H01L 29/12 (2006.01)

H01L 29/78 652T

H01L 21/336 (2006.01)

H01L 29/78 652C

H01L 29/78 656Z

H01L 29/78 658A

請求項の数 13 (全 14 頁)

(21) 出願番号

特願2016-533399 (P2016-533399)

(86) (22) 出願日

平成26年8月6日(2014.8.6)

(65) 公表番号

特表2016-529720 (P2016-529720A)

(43) 公表日

平成28年9月23日(2016.9.23)

(86) 国際出願番号

PCT/US2014/049941

(87) 国際公開番号

W02015/021154

(87) 国際公開日

平成27年2月12日(2015.2.12)

審査請求日 平成29年4月4日(2017.4.4)

(31) 優先権主張番号

13/962,295

(32) 優先日

平成25年8月8日(2013.8.8)

(33) 優先権主張国

米国(US)

(73) 特許権者 592054856

クリー インコーポレイテッド

C R E E I N C .

アメリカ合衆国 ノースカロライナ州 2

7703 ダラム シリコン ドライブ

4600

(74) 代理人 110000578

名古屋国際特許業務法人

(72) 発明者 パーラ ヴィビンダス

アメリカ合衆国 ノースカロライナ州 2

7560 モリスビル クウェイル ハイ

ブルバード 3611

最終頁に続く

(54) 【発明の名称】縦型パワートランジスタデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

トランジスタデバイスであって、

基板と、

前記基板上のドリフト層と、

前記ドリフト層上のN型にドープされた拡散層であって、前記ドリフト層に隣接する第1の表面と該第1の表面とは反対側の第2の表面との間に複数の層を備え、該複数の層の各層のドーピング濃度が、前記第2の表面からの距離に比例して減少する、拡散層と、

2つの接合インプラントの間の接合ゲート電界効果トランジスタ(JFET)領域であつて、前記第2の表面に隣接するJFET領域と、

前記接合インプラントが、P型にドープされた深ウェル領域とP型にドープされたベース領域とを含むことと、

ゲート、ドレイン、及びソースと、

を備え、前記トランジスタデバイスのチャネル幅が3ミクロン未満であり、前記トランジスタデバイスのON抵抗が、少なくとも定格電圧600Vにおいて $1.8 \text{ m}^2 / \text{cm}^2$ 以下である、トランジスタデバイス。

## 【請求項 2】

前記トランジスタデバイスのON抵抗が、定格電圧1200Vにおいて約 $2.2 \text{ m}^2 / \text{cm}^2$ 以下である、請求項1に記載のトランジスタデバイス。

## 【請求項 3】

10

20

前記トランジスタデバイスが炭化ケイ素を含む、請求項 1 に記載のトランジスタデバイス。

**【請求項 4】**

縦型配置の金属酸化物半導体電界効果トランジスタ（MOSFET）である、請求項 1 に記載のトランジスタデバイス。

**【請求項 5】**

前記拡散層の厚さが 1 . 0 ~ 2 . 5 ミクロンである、請求項 1 に記載のトランジスタデバイス。

**【請求項 6】**

前記拡散層の前記第 1 の表面におけるドーピング濃度が  $5 \times 10^{16} \text{ cm}^{-3}$  であり、

前記拡散層の前記第 2 の表面におけるドーピング濃度が  $2 \times 10^{17} \text{ cm}^{-3}$  である、請求項 1 に記載のトランジスタデバイス。

10

**【請求項 7】**

トランジスタデバイスであって、

基板と、

前記基板上のドリフト層と、

前記ドリフト層上の N 型にドープされた 拡散層であって、前記ドリフト層に隣接する第 1 の表面と該第 1 の表面とは反対側の第 2 の表面との間に複数の層を備え、該複数の層の各層のドーピング濃度が、前記第 2 の表面からの距離に比例して減少する、拡散層と、

2 つの接合インプラントの間の接合ゲート電界効果トランジスタ（JFET）領域であ

つて、前記第 2 の表面に隣接する JFET 領域と、

20

前記接合インプラントが、P 型にドープされた深ウェル領域と P 型にドープされたベ

ース領域とを含むことと、

ゲート、ドレイン、及びソースと、

を備えるトランジスタデバイス。

**【請求項 8】**

前記拡散層の厚さが 1 . 0 ~ 2 . 5 ミクロンである、請求項 7 に記載のトランジスタデバイス。

**【請求項 9】**

前記トランジスタデバイスが炭化ケイ素を含む、請求項 7 に記載のトランジスタデバイス。

30

**【請求項 10】**

縦型配置の金属酸化物半導体電界効果トランジスタ（MOSFET）である、請求項 7 に記載のトランジスタデバイス。

**【請求項 11】**

前記拡散層の前記第 1 の表面におけるドーピング濃度が  $5 \times 10^{16} \text{ cm}^{-3}$  であり、

前記拡散層の前記第 2 の表面におけるドーピング濃度が  $2 \times 10^{17} \text{ cm}^{-3}$  である、請求項 7 に記載のトランジスタデバイス。

**【請求項 12】**

前記トランジスタデバイスのチャネル幅が 3 ミクロン未満であり、前記トランジスタデバイスの ON 抵抗が、少なくとも定格電圧 600Vにおいて  $1 . 8 \text{ m}^2 / \text{cm}^2$  以下である、請求項 7 に記載のトランジスタデバイス。

40

**【請求項 13】**

前記トランジスタデバイスの ON 抵抗が、少なくとも定格電圧 1200Vにおいて  $2 . 2 \text{ m}^2 / \text{cm}^2$  以下である、請求項 12 に記載のトランジスタデバイス。

**【発明の詳細な説明】**

**【発明の詳細な説明】**

**【0001】**

**【技術分野】**

本開示は、パワートランジスタデバイスに関し、詳細には、パワー金属酸化物半導体電

50

界効果トランジスタ（MOSFET）に関する。

【背景技術】

パワー金属酸化物半導体電界効果トランジスタ（MOSFET）は、高出力用途において使用するのに適合するタイプのトランジスタである。一般に、パワーMOSFETデバイスは縦型構造を有し、ソース及びゲートコンタクトは、基板上に形成されたドリフト層によってドレインコンタクトから分離されるMOSFETデバイスの第1の表面上に位置する。縦型MOSFETは、縦型拡散MOSFET（VDMOSFET）又は二重拡散MOSFET（DMOSFET）と呼ばれることがある。その縦型構造に起因して、パワーMOSFETの定格電圧は、ドーピングとドリフト層の厚さの関数である。したがって、高電圧パワーMOSFETは、比較的小さな設置面積で達成することができる。

10

【0002】

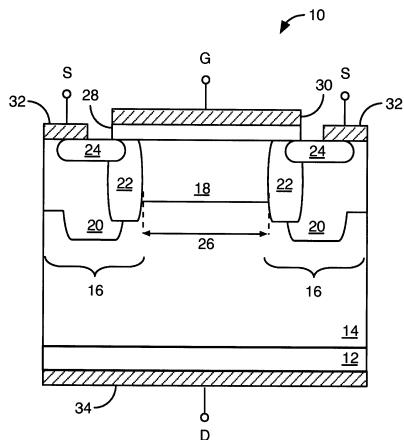

図1は従来のパワーMOSFETデバイス10を示す。従来のパワーMOSFETデバイス10は、基板12と、基板12の上方に形成されたドリフト層14と、基板とは反対側のドリフト層14の表面の1つ又は複数の接合インプラント16と、各接合インプラント16の間の接合ゲート電界効果トランジスタ（JFET）領域18とを備える。各接合インプラント16は、イオン注入プロセスによって形成され、深ウェル領域20、ベース領域22、及びソース領域24を備える。各深ウェル領域20は、基板12とは反対側のドリフト層14の角から、基板12に向かって下方に、かつ、ドリフト層14の中央に向かって内方に延在する。深ウェル領域20は、均一に形成してもよく、あるいは図1に示すように1つ又は複数の突出領域を含んでいてもよい。各ベース領域22は、基板12とは反対側のドリフト層14の表面から垂直方向に、各深ウェル領域20の内縁の一部分に沿って基板12に向かって下方に形成される。各ソース領域24は、基板12とは反対側のドリフト層14の表面上の浅い部分に形成され、かつ、横方向に延在して、深ウェル領域20及びベース領域22の全体にわたって延在しない状態で、深ウェル領域20及びベース領域22の一部分と重なり合う。JFET領域18は、各接合インプラント16の間にチャネル幅26を画定する。

20

【0003】

ゲート酸化物層28は、基板12とは反対側のドリフト層14の表面上に位置し、各ソース領域24の表面の一部分の間で横方向に延在し、それにより、ゲート酸化物層28は、接合インプラント16内の各ソース領域24の表面と部分的に重なり合い、該表面の間を延びる。ゲートコンタクト30は、ゲート酸化物層28の上面に位置する。2つのソースコンタクト32はそれぞれ、基板12とは反対側のドリフト層14の表面上に位置し、それにより、各ソースコンタクト32は、接合インプラント16の一つのソース領域24及び深ウェル領域20の両方とそれぞれ部分的に重なり合い、ゲート酸化物層28又はゲートコンタクト30には接触しない。ドレインコンタクト34は、ドリフト層14とは反対側の基板12の表面上に位置する。

30

【0004】

動作時、バイアス電圧がゲートコンタクト30に印加されずに、ドレインコンタクト34が正にバイアスされるときに、各深ウェル領域20とドリフト層14との間の接合部が逆バイアスされ、それにより、従来のパワーMOSFET10をOFF状態にする。従来のパワーMOSFET10のOFF状態においては、ソースコンタクトとドレインコンタクトとの間の電圧はドリフト層14によって支持される。従来のパワーMOSFET10の縦型構造に起因して、デバイスに損傷を与えることなく、ソースコンタクト32とドレインコンタクト34との間に大きな電圧をかけることができる。

40

【0005】

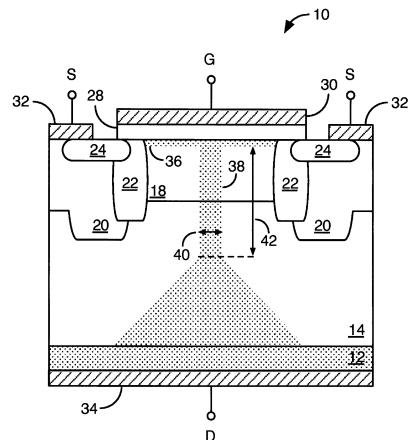

図2は、デバイスがON状態にあるときの従来のパワーMOSFET10の動作を示す。従来のパワーMOSFET10のゲートコンタクト30に正バイアスが印加されると、反転層チャネル36がゲートコンタクト30の真下のドリフト層14の表面に形成され、それにより、従来のパワーMOSFET10をON状態にする。従来のパワーMOSFET10のON状態において、電流（図2の影付き領域で示す）は、各ソースコンタクト3

50

2から反転層チャネル36を通ってドリフト層14のJFET領域18内に流れることを許容される。JFET領域18内に入ると、電流は、ドリフト層14を通って下方に、ドレインコンタクト34に向かって流れる。深ウェル領域20と、ベース領域22と、ドリフト層14との間に形成される接合部によって生じる電界は、JFET領域18内の電流を、JFETチャネル幅40を有するJFETチャネル38に入るよう制限する。反転層チャネル36からのある拡散距離42において、接合インプラント16によって生じる電界が減少すると、電流は、図2に示すように、ドリフト層14内で横方向に分布するか又は分散する。JFETチャネル幅40及び拡散距離42は、パワーMOSFET10の内部抵抗を決定し、それにより、デバイスの性能を左右する。従来のパワーMOSFET10は、デバイスの適切な動作のために適切なJFETチャネル幅40及び拡散距離42を持続させるため3ミクロン以上のチャネル幅26を一般に必要とする。

#### 【0006】

深ウェル領域20と、ベース領域22と、ドリフト層14との間の接合部によって形成される電界は、ゲート酸化物層28を通して放出され、それにより、ゲート酸化物層28を経時に物理的に劣化させる。最終的に、電界は、ゲート酸化物層28を絶縁破壊させることになり、従来のパワーMOSFET10が機能しなくなることになる。

#### 【0007】

したがって、低いON状態抵抗を維持し、改善された寿命を持ちながら、OFF状態において高電圧を扱うことが可能であるパワーMOSFETが必要とされている。

#### 【発明の概要】

本開示は、基板と、基板上方のドリフト層と、ドリフト層上方の拡散層(spread ing layer)とを含むトランジスタデバイスに関する。拡散層は、接合ゲート電界効果(JFET)領域によって分離された一対の接合インプラントを含む。各接合インプラントは、深ウェル領域と、ベース領域と、ソース領域とを含むことができる。トランジスタデバイスは、ゲート酸化物層、ゲートコンタクト、一対のソースコンタクト、及びドレインコンタクトを更に備えることができる。ゲート酸化物層は拡散層の一部上にあり、ゲート酸化物層は、各接合インプラントの各ソース領域と部分的に重なり合い、各ソース領域の間を延びる。ゲートコンタクトは、ゲート酸化物層の上面に位置する。各ソースコンタクトは、拡散層の一部上にあり、それにより、各ソースコンタクトは、各接合インプラントのソース領域と深ウェル領域の両方とそれぞれ部分的に重なり合う。ドレインコンタクトは、ドリフト層とは反対側の基板の表面上にある。

#### 【0008】

一実施形態によれば、拡散層は、拡散層内の地点のJFET領域からの距離に比例して拡散層のドーピング濃度が減少するように、漸変ドーピングプロファイルを有する。

更なる実施形態によれば、拡散層は複数の層を含み、複数の層はそれぞれ、層のJFET領域からの距離に比例して徐々に減少する、異なるドーピング濃度を有する。

#### 【0009】

拡散層をドリフト層の上方に配置することによって、各接合インプラントの間の空間又はJFET領域の長さが減少し得るが、その一方で同時に、デバイスのON抵抗を維持するか、又は減少させることができる。各接合インプラントの間の空間を減少させることによって、トランジスタデバイスの逆バイアス中に生成される電界の大部分は、各接合インプラントによって打切られ、それにより、ゲート酸化物層が出会う電界を減少させ、デバイスの寿命を増加させる。

#### 【0010】

当業者であれば、添付図面に関連して好ましい実施形態の以下の詳細な説明を読んだ後に、本開示の範囲を理解し、本開示の更なる態様を理解するであろう。

本明細書に組込まれ、かつ本明細書の一部を構成する添付図面は、本開示の幾つかの態様を示し、説明と共に、本開示の原理を説明するのに役立つ。

#### 【図面の簡単な説明】

#### 【0011】

10

20

30

40

50

【図1】従来のパワーMOSFETデバイスの概略図である。

【図2】図1に示す従来のパワーMOSFETデバイスの動作の詳細を示す図である。

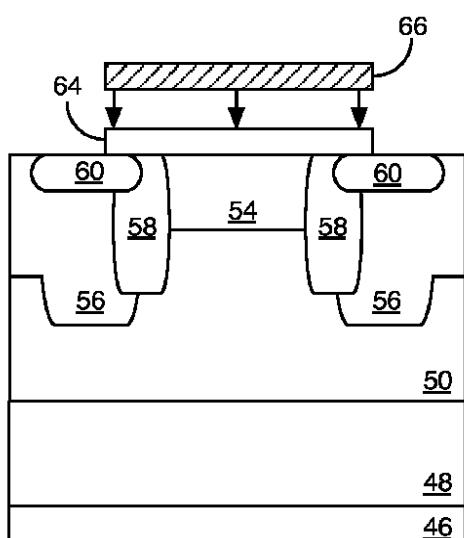

【図3】本開示の一実施形態によるパワーMOSFETデバイスを示す図である。

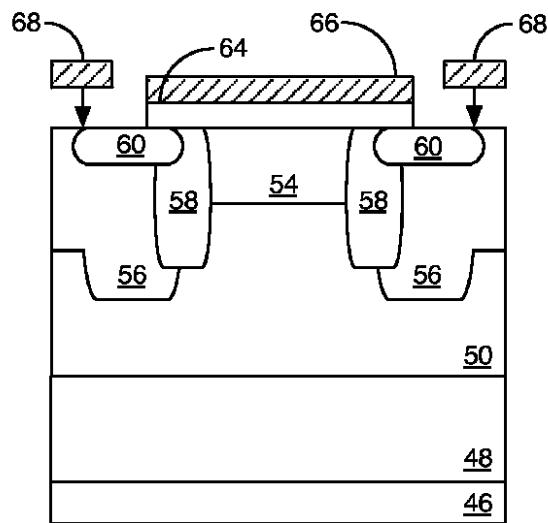

【図4】本開示の一実施形態による図3に示すパワーMOSFETデバイスの動作の詳細を示す図である。

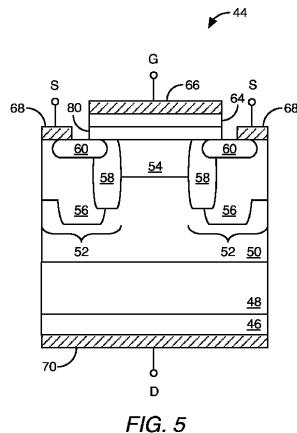

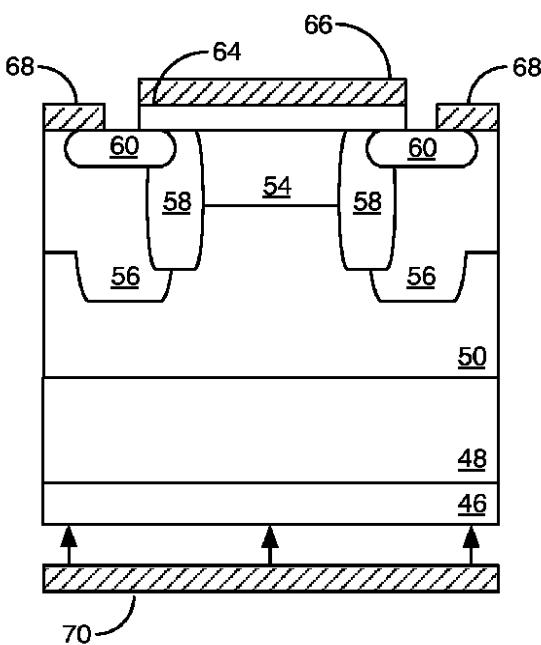

【図5】図3に示すパワーMOSFETデバイスの代替の実施形態を示す図である。

【図6】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図7】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

10

【図8】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図9】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図10】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図11】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図12】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

20

【図13】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図14】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

【図15】図3に示すパワーMOSFETデバイスを製造するためのプロセスを示す図である。

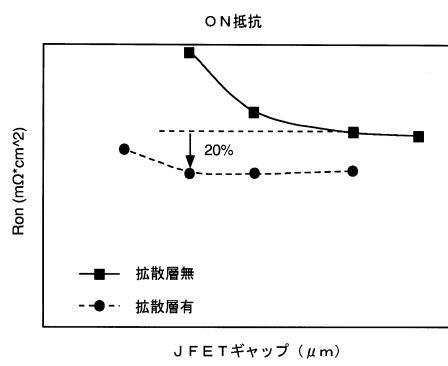

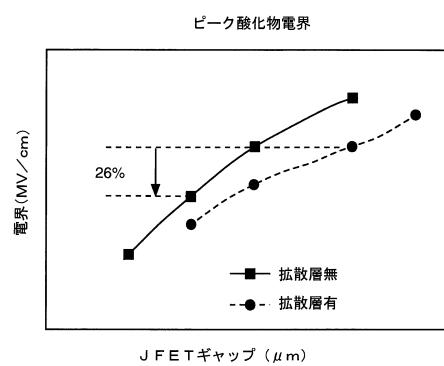

【図16】図3に示すパワーMOSFETデバイスによって達成される性能改善を示すグラフである。

【図17】図3に示すパワーMOSFETデバイスによって達成される寿命改善を示すグラフである。

30

【発明を実施するための形態】

【0012】

[詳細な説明]

以下で述べる実施形態は、当業者が実施形態を実施することを可能にするために必要な情報を示し、実施形態を実施するまでのベストモードを示す。添付図面を考慮して以下の説明を読むと、当業者は、本開示の概念を理解することになり、また、本明細書で具体的に記載されていないこれらの概念の応用を認識することになる。これらの概念及び応用が本開示及び添付の特許請求の範囲の範囲内に入ることが理解されるべきである。

【0013】

種々の要素を説明するために、第1、第2等の用語を本明細書で使用している場合があるが、これらの要素はこれらの用語によって限定されねばならないことが理解されるであろう。これらの用語は、ある要素を別の要素と区別するために使用されるにすぎない。例えば、本開示の範囲から逸脱することなく、第1の要素は第2の要素と呼ばれる可能性があり、同様に、第2の要素は第1の要素と呼ばれる可能性がある。本明細書で使用する場合、用語「及び／又は（and/or）」は、関連する記載項目の1つ又は複数の記載項目のうちのいずれか又は全ての組み合わせを含む。

【0014】

層、領域、又は基板等の要素が、別の要素「の上に（on）」位置する又は「の上に（onto）」延在するとして言及される場合、当該要素は、他の要素の上に直接位置していてもよく、又は上に直接延在していてもよく、あるいは、介在する要素が存在してもよ

40

50

いことが理解されるであろう。対照的に、要素が、別の要素「の上に直接 (directly on)」位置しているか、又は「の上に直接 (directly onto)」延在するとして言及される場合には、介在要素が存在しない。同様に、層、領域、又は基板等の要素が、別の要素「上方に (over)」位置しているか又は「の全体にわたって (over)」延在するとして言及される場合、当該要素は、他の要素の上に直接位置しているか又は上に直接延在してもよく、あるいは、介在する要素が存在していてもよいことが理解されるであろう。対照的に、要素が、別の要素「の上に直接 (directly over)」位置しているか又は「の上に直接 (directly over)」延在するとして言及される場合には、介在要素が存在しない。要素が、別の要素に「接続される (connected)」又は「結合される (coupled)」として言及される場合、要素は、他の要素に直接接続又は結合されていてもよく、あるいは、介在要素が存在していてもよいことも理解されるであろう。対照的に、要素が、別の要素に「直接接続される (directly connected)」又は「直接結合される (directly coupled)」として言及される場合には、介在要素が存在しない。

#### 【0015】

「下方の (below)」又は「上方の (above)」及び「上の (upper)」又は「下の (lower)」又は「水平の (horizontal)」又は「垂直の (vertical)」等の相対的用語は、ある要素、層、又は基板の別の要素、層、又は基板に対する図面に示すような位置関係を述べるために、本明細書で使用する場合がある。これらの用語及び先に論じたものが、図面に示す向きに加えて、デバイスの異なる向きを包含することを意図されることが理解されるであろう。

#### 【0016】

本明細書で使用する用語は特定の実施形態を説明する目的で使用されるにすぎず、本開示を制限することを意図するものではない。本明細書で使用される場合、単数形「1つの (a)」、「1つの (an)」、及び「その (the)」は、文脈が別途明確に示さない限り、複数形も含むことを意図される。用語「備える (comprise)」、「備えている (comprising)」、「含む (includes)」、及び「含んでいる (including)」は、本明細書で使用する場合、述べた特徴、整数、ステップ、動作、要素、及び / 又は部品の存在を記述するが、1つ又は複数の他の特徴、整数、ステップ、動作、要素、部品、及び / 又はそれらのグループの存在を排除しないことが更に理解されるであろう。

#### 【0017】

別途定義されない限り、本明細書で使用する全ての用語（技術的及び科学的用語を含む）は、本開示の技術分野における当業者によって一般的に理解される意味と同じ意味を有する。本明細書で使用する用語は、本明細書及び関連する技術分野の文脈における意味と一貫性がある意味を有するものと解釈されるべきであり、本明細書で明示的に定義されない限り、理想的な又は過度に形式的な意味で解釈されないことが更に理解されるであろう。

#### 【0018】

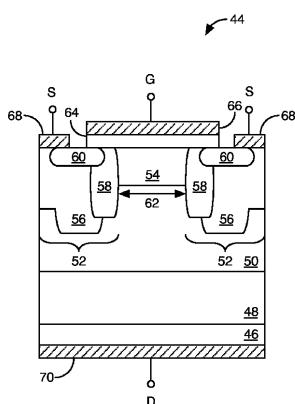

ここで図3を参照すると、本開示の一実施形態によるパワーMOSFETデバイス44が示されている。パワーMOSFETデバイス44は、基板46と、基板46の上方に形成されたドリフト層48と、ドリフト層48の上方に形成された拡散層50と、ドリフト層48とは反対側の拡散層50の表面にある1つ又は複数の接合インプラント52と、各接合インプラント52の間の接合ゲート電界効果トランジスタ(JFET)領域54とを備える。各接合インプラント52は、イオン注入プロセスによって形成することができ、深ウェル領域56、ベース領域58、及びソース領域60を含むことができる。各深ウェル領域56は、ドリフト層48とは反対側の拡散層50の角から、ドリフト層48に向かって下方に、かつ、拡散層50の中央に向かって内方に延在する。深ウェル領域56は、均一に形成されてもよく、あるいは1つ又は複数の突出領域を含んでいてもよい。各ベース領域58は、ドリフト層48とは反対側の拡散層50の表面から垂直に、それぞれの深

10

20

30

40

50

ウェル領域 5 6 の内縁の一部分に沿ってドリフト層 4 8 に向かって下方に形成される。各ソース領域 6 0 は、ドリフト層 4 8 とは反対側の拡散層 5 0 の表面上の浅い部分に形成され、かつ、横方向に延在して、深ウェル領域 5 6 及びベース領域 5 8 の全体にわたって延在しない状態で、深ウェル領域 5 6 及びベース領域 5 8 の一部分と重なり合う。J F E T 領域 5 4 は、各接合インプラント 5 2 の間にチャネル幅 6 2 を画定する。

#### 【 0 0 1 9 】

ゲート酸化物層 6 4 は、ドリフト層 4 8 とは反対側の拡散層 5 0 の表面上に位置し、各ソース領域 6 0 の表面の一部分の間で横方向に延在しており、ゲート酸化物層 6 4 は、接合インプラント 5 2 の各ソース領域 6 0 の表面と部分的に重なり合い、該表面の間を延びる。ゲートコンタクト 6 6 は、ゲート酸化物層 6 4 の上面に配置される。2つのソースコンタクト 6 8 はそれぞれ、ドリフト層 4 8 とは反対側の拡散層 5 0 の表面上に配置され、それにより、各ソースコンタクト 6 8 は、接合インプラント 5 2 のソース領域 6 0 及び深ウェル領域 5 6 の両方とそれぞれ部分的に重なり合い、ゲート酸化物層 6 4 又はゲートコンタクト 6 6 に接触しない。ドレインコンタクト 7 0 は、ドリフト層 4 8 とは反対側の基板 4 6 の表面上に配置される。10

#### 【 0 0 2 0 】

動作時、バイアス電圧がゲートコンタクト 6 6 に印加されず、ドレインコンタクト 7 0 が正にバイアスされるときに、各深ウェル領域 5 6 と拡散層 5 0 との間の接合部が逆バイアスされ、それにより、パワーMOSFET 4 4 をOFF 状態にする。パワーMOSFET 4 4 のOFF 状態において、ソースコンタクトとドレインコンタクトとの間の電圧はドリフト層 4 8 及び拡散層 5 0 によって支持される。パワーMOSFET 4 4 の縦型構造に起因して、デバイスに損傷を与えることなく、ソースコンタクト 6 8 とドレインコンタクト 7 0 との間に大きな電圧をかけることができる。20

#### 【 0 0 2 1 】

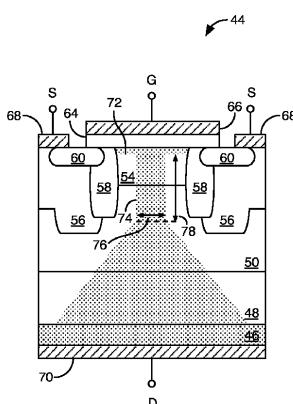

図 4 は、デバイスがON 状態にあるときのパワーMOSFET 4 4 の動作を示す。パワーMOSFET 4 4 のゲートコンタクト 6 6 に正バイアスが印加されると、反転層チャネル 7 2 がゲートコンタクト 6 6 の真下の拡散層 5 0 の表面に形成され、それにより、パワーMOSFET 4 4 をON 状態にする。パワーMOSFET 4 4 のON 状態において、電流（図 4 において影付き領域で示す）は、各ソースコンタクト 6 8 から反転層チャネル 7 2 を通って J F E T 領域 5 4 内に流れることを許容される。J F E T 領域 5 4 内に入ると、電流は、拡散層 5 0 を通って下方に、ドレインコンタクト 7 0 に向かって流れる。深ウェル領域 5 6 と、ベース領域 5 8 と、拡散層 5 0 との間に形成される接合部によって生じる電界は、J F E T 領域 5 4 内の電流を、J F E T チャネル幅 7 6 を有する J F E T チャネル 7 4 に入るよう制限する。30

#### 【 0 0 2 2 】

反転層チャネル 7 2 からのある拡散距離 7 8 において、接合インプラント 5 2 によって生じる電界が減少すると、電流は、図 4 に示すように、拡散層 5 0 内で横方向に分布するか又は拡散する。拡散層 5 0 は、拡散層 5 0 内の抵抗を減少させるためにドープされ、それにより、J F E T チャネル幅 7 6 を増加させ、拡散距離 7 8 を減少させることによって、電界の作用を軽減する。J F E T チャネル幅 7 6 を増加させ、拡散距離 7 8 を減少させることによって、拡散層 5 0 は、パワーMOSFET 4 4 のON 抵抗を著しく減少させる。例えば、パワーMOSFET 4 4 のON 抵抗は、デバイスが 1200 V を扱うように定格付けされるときに約  $2.2 \text{ m}^2 / \text{cm}^2$  、デバイスが 600 V を扱うように定格付けされるときに約  $1.8 \text{ m}^2 / \text{cm}^2$  とすることができます。40

#### 【 0 0 2 3 】

パワーMOSFET 4 4 のON 抵抗を減少させることによって、拡散層 5 0 は、各接合インプラント 5 2 の間のチャネル幅 6 2 の減少を可能にする。パワーMOSFET 4 4 のチャネル幅 6 2 を減少させることは、デバイスの設置面積だけでなく寿命も改善する。各接合インプラント 5 2 が互いに近づくにつれて、深ウェル領域 5 6 と、ベース領域 5 8 と、拡散層 5 0 との間の接合部によって生成される電界の大部分は、反対側の接合インプラ50

ント52によって打切られる。したがって、ゲート酸化物層64が出会う電界が著しく減少し、それにより、パワーMOSFET44の寿命が改善されることになる。一実施形態によれば、パワーMOSFET44のチャネル幅62は3ミクロン未満である。

#### 【0024】

パワーMOSFET44は、例えば、炭化ケイ素(SiC)デバイス、ヒ化ガリウム(GaAs)デバイス、又は窒化ガリウム(GaN)デバイスとすることができます。当業者であれば、本開示の概念が任意の材料系に適用可能であることを理解するであろう。パワーMOSFET44の基板46は約180~350ミクロン厚とすることができます。ドリフト層48は、パワーMOSFET44の電圧定格に応じて、約3.5~12ミクロン厚とすることができます。拡散層50は約1.0~2.5ミクロン厚とすることができます。各接合インプラント52は約1.0~2.0ミクロン厚とすることができます。JFET領域54は約0.75~1.5ミクロン厚とすることができます。10

#### 【0025】

一実施形態によれば、拡散層50は、約 $2 \times 10^{17} \text{ cm}^{-3}$ ~ $5 \times 10^{16} \text{ cm}^{-3}$ のドーピング濃度を有するNドープ層である。拡散層50は、ドリフト層48に最も近い拡散層50の部分が、約 $5 \times 10^{16} \text{ cm}^{-3}$ のドーピング濃度を有し、拡散層50が上方に延在するにつれてその濃度が約 $2 \times 10^{17} \text{ cm}^{-3}$ のドーピング濃度まで徐々に変化するように、漸変する。更なる実施形態によれば、拡散層50は複数の層を備えることができる。ドリフト層48に最も近い拡散層50の層は約 $5 \times 10^{16} \text{ cm}^{-3}$ のドーピング濃度を有することができる。拡散層の各付加的な層のドーピング濃度は、JFET領域54からのその層の距離に比例して減少してもよい。ドリフト層48に最も近い拡散層50の層は $2 \times 10^{17} \text{ cm}^{-3}$ のドーピング濃度を有することができる。20

#### 【0026】

JFET領域54は、約 $1 \times 10^{16} \text{ cm}^{-3}$ ~ $2 \times 10^{17} \text{ cm}^{-3}$ のドーピング濃度を有するNドープ層とすることができます。ドリフト層48は、約 $6 \times 10^{15} \text{ cm}^{-3}$ ~ $1.5 \times 10^{16} \text{ cm}^{-3}$ のドーピング濃度を有するNドープ層とすることができます。深ウェル領域56は、約 $5 \times 10^{17} \text{ cm}^{-3}$ ~ $1 \times 10^{20} \text{ cm}^{-3}$ のドーピング濃度を有する高濃度Pドープ領域とすることができます。ベース領域58は、約 $5 \times 10^{16} \text{ cm}^{-3}$ ~ $1 \times 10^{19} \text{ cm}^{-3}$ のドーピング濃度を有するPドープ領域とすることができます。ソース領域60は、約 $1 \times 10^{19} \text{ cm}^{-3}$ ~ $1 \times 10^{21} \text{ cm}^{-3}$ のドーピング濃度を有するNドープ領域とすることができます。Nドーピング物質は、当業者によって認識されるように、窒素、亜リン酸、又は任意の他の適した元素とすることができます。Pドーピング物質は、当業者によって認識されるように、アルミニウム、ホウ素、又は任意の他の適した元素とすることができます。30

#### 【0027】

ゲートコンタクト66、ソースコンタクト68、及びドレインコンタクト70は複数の層を備えることができる。例えば、それぞれのコンタクトは、ニッケル又はニッケル-アルミニウムの第1の層と、第1の層上方のチタンの第2の層と、第2の層上方のチタン-ニッケルの第3の層と、第3の層上方のアルミニウムの第4の層とを含むことができる。当業者であれば、ゲートコンタクト66、ソースコンタクト68、及びドレインコンタクト70が任意の適した材料で形成することができることを理解するであろう。40

#### 【0028】

図5は、本開示の更なる実施形態によるパワーMOSFET44を示す。図5に示すパワーMOSFET44は、図3のパワーMOSFET44と実質的に同様であるが、ゲート酸化物層64と拡散層50との間にチャネル再成長層80を更に含む。チャネル再成長層80は、パワーMOSFET44の閾値電圧を下げるために設けられる。特に、深ウェル領域56は、高レベルのドーピングに起因して、パワーMOSFET44の閾値電圧を、最適性能を抑制するレベルまで上げる可能性がある。したがって、チャネル再成長層80は、パワーMOSFET44の閾値電圧を下げるために、深ウェル領域56の作用を相殺してもよい。チャネル再成長層80は、約 $1 \times 10^{15} \text{ cm}^{-3}$ ~ $1 \times 10^{17} \text{ cm}^{-3}$ 50

<sup>3</sup> のドーピング濃度を有するNドープ領域とすることができます。

#### 【0029】

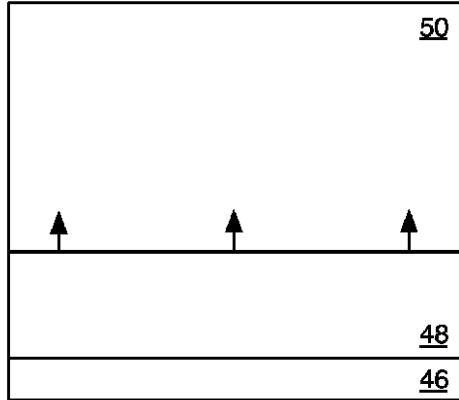

図6～15は、図3に示すパワーMOSFET44を製造するためのプロセスを示す。最初に、図6に示すように、ドリフト層48が基板46の上面で成長させられる。当業者であれば、本開示の原理から逸脱することなく、任意の適した成長プロセスを使用してドリフト層48を生成することができますことを認識するであろう。例えば、化学気相堆積法を使用してドリフト層48を生成することができます。

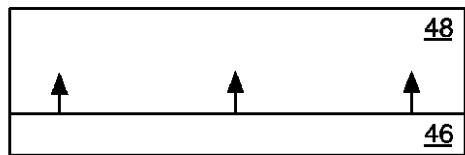

#### 【0030】

次に、図7で示すように、拡散層50がドリフト層48の上面で成長させられる。先に論じたように、本開示の原理から逸脱することなく、任意の適した成長プロセスを使用して拡散層50を作成することができます。一実施形態によれば、拡散層50は、漸変ドーピングプロファイルを有するように成長させられる。10

#### 【0031】

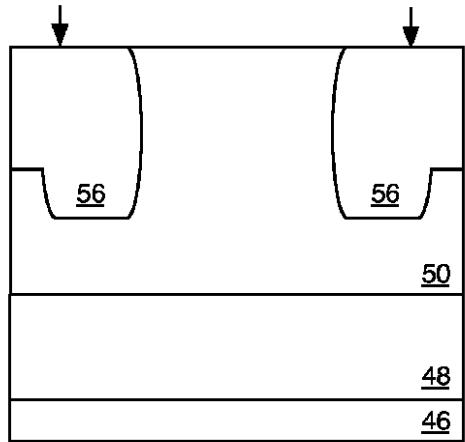

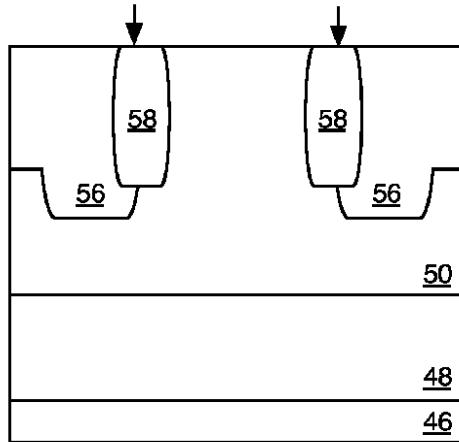

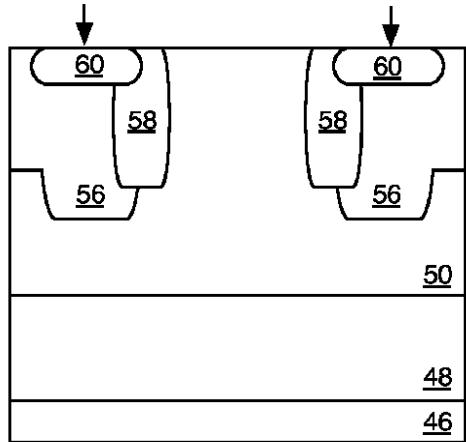

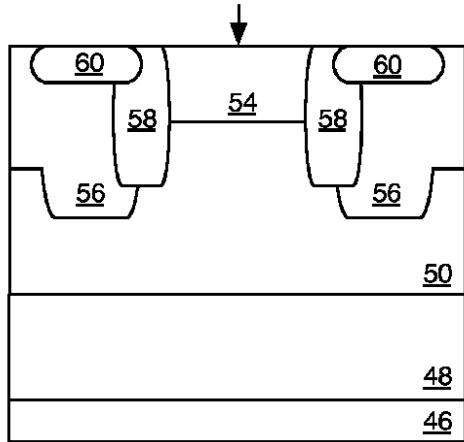

次に、図8に示すように、各接合インプラント52の深ウェル領域56が、拡散層50に注入される。当業者によって理解されるように、深ウェル領域56は、任意の適した注入プロセスによって注入することができる。例えば、深ウェル領域56を形成するために、イオン注入法を使用することができる。その後、ベース領域58が図9に示すように注入され、それに続いて、ソース領域60が図10に示すように注入される。

#### 【0032】

次に、図11に示すように、JFET領域54が注入される。先に論じたように、本開示の原理から逸脱することなく、JFET領域54を作成するために、任意の適した注入プロセスを使用することができる。更に、図示しないが、JFET領域54は、代替的に成長プロセスによって作成してもよい。20

#### 【0033】

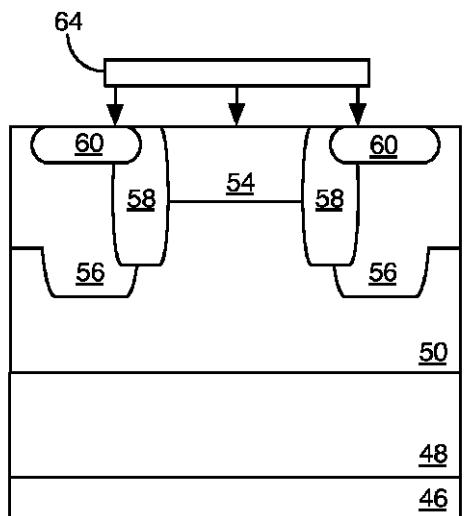

次に、図12で示すように、ゲート酸化物層64が拡散層50の上面に形成され、それにより、ゲート酸化物層64は、接合インプラント52のそれぞれのソース領域60の表面と部分的に重なり合い、該表面の間を延びる。図13において、ゲートコンタクト66がゲート酸化物層64の上面に形成される。その後、ソースコンタクト68が拡散層50の表面上に形成され、それにより、図14に示すように、各ソースコンタクト68は、接合インプラント52のソース領域60及び深ウェル領域56の両方にそれぞれ部分的に重なり合うが、ゲート酸化物層64又はゲートコンタクト66には接触しない。最後に、図15において、ドレインコンタクト70が、ドリフト層48とは反対側の基板46の表面上に設けられる。30

#### 【0034】

図16は、パワーMOSFET44のON抵抗に対する拡散層の50の作用を示すグラフである。図示するように、拡散層は、デバイスのON抵抗において約20%の減少を提供する。

#### 【0035】

図17は、ゲート酸化物層64が出会う電界に対する拡散層50の作用を示すグラフである。拡散層50が、パワーMOSFET44の性能を妨げることなくチャネル幅62の減少を可能にするため、ゲート酸化物層64が出会う電界の最大26%が、対向する接合インプラント52によって打切られ、それにより、デバイスの寿命を著しく増加させる。40

#### 【0036】

当業者は、本開示の好ましい実施形態に対する改善及び改変を認識するであろう。全てのこうした改善及び改変は、本明細書に開示される概念及び添付の特許請求の範囲内にあると考えられる。

【図1】

FIG. 1

(関連技術)

【図2】

FIG. 2

(関連技術)

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

【図7】

【図6】

FIG. 6

【図8】

【図9】

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

【図 13】

FIG. 13

【図14】

FIG. 14

【図15】

FIG. 15

【図16】

FIG. 16

【図17】

FIG. 17

---

フロントページの続き

(72)発明者 アガーワル アナント クマール

アメリカ合衆国 ヴァージニア州 22202 アーリントン サウス イーズ ストリート 1

600 アパートメント 526エヌ

(72)発明者 チエン リン

アメリカ合衆国 ノースカロライナ州 27514 チャペル ヒル サウス クラブツリー ノ

ールズ 103

(72)発明者 リヒテンヴァルナー ダニエル ジエンナー

アメリカ合衆国 ノースカロライナ州 27603 ローリー ホライズン ハイク コート 2

308

(72)発明者 パーマー ジョン ウィリアムズ

アメリカ合衆国 ノースカロライナ州 27511 ケーリー デボンブルック レーン 231

審査官 棚田 一也

(56)参考文献 特開平6-5867(JP,A)

再公表特許第2008/069309(JP,A1)

特開2013-149837(JP,A)

特開2013-102245(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336

H01L 29/12