(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-204927

(P2011-204927A)

(43) 公開日 平成23年10月13日(2011.10.13)

(51) Int.Cl.

H01L 21/822 (2006.01)

H01L 27/04 (2006.01)

F 1

H01L 27/04

C

テーマコード(参考)

5FO38

審査請求 未請求 請求項の数 5 O L (全 9 頁)

(21) 出願番号

特願2010-71085 (P2010-71085)

(22) 出願日

平成22年3月25日 (2010.3.25)

(71) 出願人 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 井上 亜矢子

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

(72) 発明者 斎藤 直人

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】高温熱処理をせずに形成可能、かつ、信頼性劣化が少なく、かつ、従来のトレンチキャパシタと同様に、安定した容量値の供給、及び、大容量化が可能な、半導体キャパシタ、及び、その製造方法を提供する。

【解決手段】半導体基板の表面にLOCOS法およびウエットエッティングを用いて台形状トレンチを設け、台形状トレンチ表面に下部電極層5を形成し、下部電極層の上に容量絶縁膜6と上部電極7を順次積層する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

第1導電型半導体基板と、

前記第1導電型半導体基板の表面に形成された台形状トレンチを有する容量素子形成領域と、

前記容量素子領域の台形状トレンチに沿って前記第1導電型半導体基板の表面近傍に設けられた第2導電型下部電極層と、

前記下部電極層の表面に形成された容量絶縁膜と、

前記容量絶縁膜の表面に形成された第2導電型上部電極と、

からなる半導体装置。

10

**【請求項 2】**

前記台形状トレンチは、平行に複数配置されている請求項1記載の半導体装置。

**【請求項 3】**

第1導電型半導体基板上にLOCOS法により厚い酸化膜領域と薄い酸化膜領域を形成する工程と、

前記厚い酸化膜領域と前記薄い酸化膜領域の酸化膜を前記半導体基板から除去する工程と、

前記台形状トレンチの表面に第2導電型不純物を導入して下部電極層を形成する工程と、

前記下部電極層上に容量絶縁膜を形成する工程と、

前記容量絶縁膜上に上部電極となる多結晶シリコン膜を堆積する工程と、

前記上部電極となる多結晶シリコンに第2導電型不純物を導入し、所定の形状とすることで上部電極とする工程と、

からなる半導体装置の製造方法。

20

**【請求項 4】**

前記容量絶縁膜を形成する工程は、熱酸化による酸化膜形成工程である請求項3記載の半導体装置の製造方法。

**【請求項 5】**

前記容量絶縁膜を形成する工程は、減圧CVDによるシリコン窒化膜形成工程である請求項3記載の半導体装置の製造方法。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体キャパシタを有する半導体装置およびその製造方法に関する。

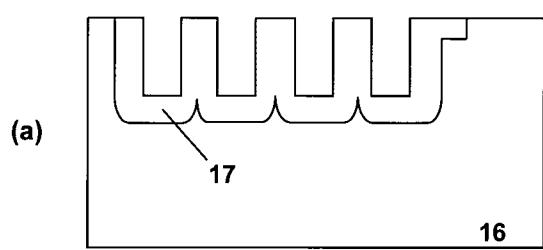

**【背景技術】****【0002】**

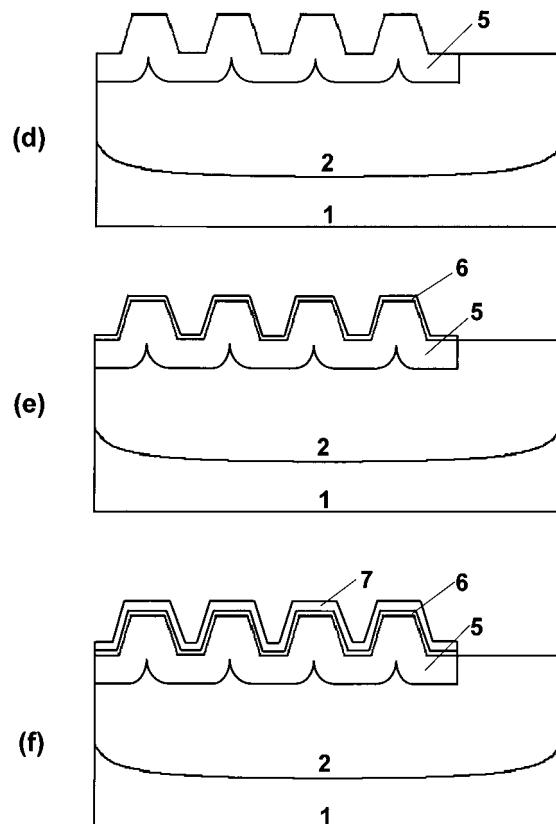

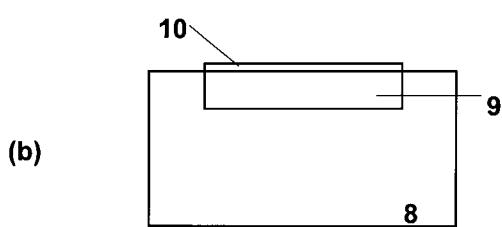

半導体キャパシタは、半導体回路の重要な構成要素の一つで、多種多様なICに組み込まれてあり、様々な構造の半導体キャパシタが使用されている。従来の半導体キャパシタの一つとして、プレーナー型キャパシタがある。プレーナー型キャパシタの代表的な構造、および、その製造方法を、P型半導体基板上に形成したキャパシタを例に図3(a)~(c)の製造工程断面図を用いて説明する。

40

**【0003】**

まず、図3(a)に示すように、P型半導体基板8表面にN型不純物をイオン注入してから、熱処理することで下部電極層9を形成する。次に、図3(b)に示すように、下部電極層9の表面を熱酸化することで容量絶縁膜10を形成する。次に、図3(c)に示すように、上部電極11となる多結晶シリコン膜を容量絶縁膜10上にCVD等で堆積させ、N型不純物のイオン注入および熱処理を施し、更にパターニングすることによって形成する。以上が、従来のプレーナー型キャパシタの代表的な構造、及び、その製造方法である。プレーナー型キャパシタは、通常使用されるトランジスタの製造工程を利用して低コストで、かつ、簡単に形成できるので、広く使われている。

50

## 【0004】

しかし、プレーナー型キャパシタの場合は、入力電圧によっては下部電極層表面の空乏層幅が変化する。空乏層幅が変化することによって容量値も変化してしまい、安定した容量値を得ることができないという弱点を有している。

## 【0005】

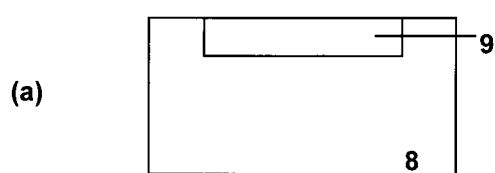

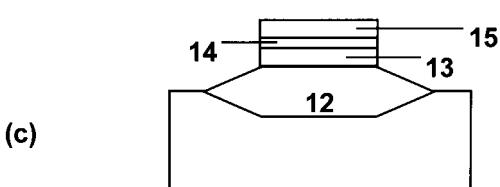

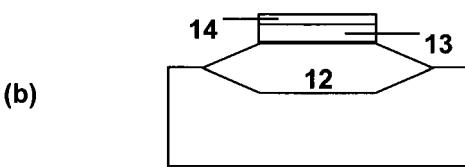

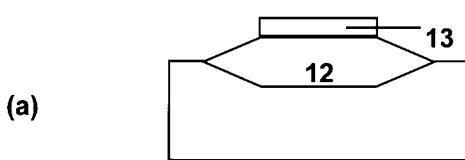

上記弱点を受けて考えられた、従来使用されている半導体キャパシタの一つとして、積層（P I P）型キャパシタがある。上記積層（P I P）型キャパシタの代表的な構造、及びその製造方法をフィールド酸化膜上に形成したキャパシタを例に図4（a）～（c）の製造工程断面図を用いて説明する。

## 【0006】

まず、図4（a）に示すように、下部電極13となる多結晶シリコン膜をフィールド酸化膜12上にCVD等で堆積し、多結晶シリコンにN型不純物をイオン注入後、熱処理をし、更にパターニングすることで下部電極13を形成する。次に、図4（b）に示すように、下部電極13上に容量絶縁膜14をCVDで堆積させて形成する。次に、図4（c）に示すように、上部電極15となる多結晶シリコン膜を容量絶縁膜14上にCVD等で堆積させ、N型不純物のイオン注入および熱処理をし、更にパターニングすることによって形成する。以上が、従来の積層（P I P）型キャパシタの代表的な構造、及び、その製造方法である。積層型キャパシタは、上記プレーナー型キャパシタと比較して、下部電極、及び、上部電極に高濃度の不純物が添加されている多結晶シリコンを使用しているので、入力電圧による空乏層幅の変化が少なく、安定した容量値を得ることができる。

10

20

## 【0007】

しかし、上記積層型キャパシタの問題は多結晶シリコン上に形成する容量絶縁膜の形成方法にある。一般的に、多結晶シリコンを熱酸化するときには、高温で酸化を行った方が酸化膜の膜質を良くすることができます。しかし、高温で熱酸化を行うと、酸化工程中の熱によって不純物が拡散してしまい、他の素子（例えば、トランジスタ等）の特性変化および信頼性劣化の原因となりうる。以上の理由から、一般的に、積層（P I P）型キャパシタの容量絶縁膜の形成方法として、比較的低温で酸化膜を形成できるCVD法が採用されている。しかし、CVD法による酸化膜の膜質は、単結晶シリコン上に形成された熱酸化膜と比較すると特性が良くない。そのため、CVD法による酸化膜の膜厚を薄くすることは耐圧劣化や信頼性劣化の原因となるため容量絶縁膜の膜厚を薄くすることはできない。その結果、積層（P I P）型キャパシタは、容量値を大きくすることができないという弱点がある。

30

## 【0008】

プレーナー型キャパシタや積層型キャパシタの上記弱点を受けて提案された半導体キャパシタの一つとして、トレンチ型キャパシタがある。

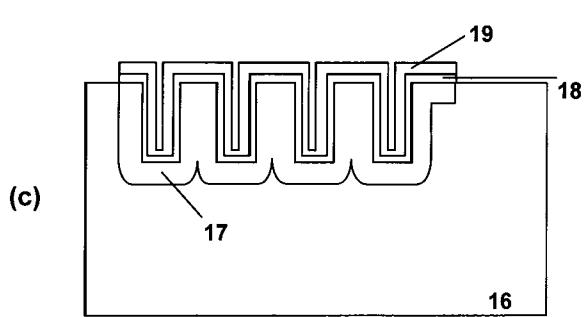

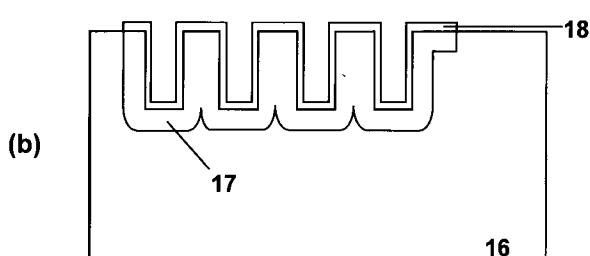

トレンチ型キャパシタの代表的な構造およびその製造方法をP型半導体基板上に形成したキャパシタを例にして、図5（a）～（c）の製造工程断面図を用いて説明する。

## 【0009】

まず、図5（a）に示すように、トレンチが形成されたP型半導体基板16上に、下部電極となる下部電極層17を、N型不純物をイオン注入、及び、熱処理によって形成する。次に、図5（b）に示すように、下部電極層17が形成されたトレンチ基板表面上に、容量絶縁膜18を、熱酸化によって形成する。次に、図5（c）に示すように、容量絶縁膜18上に上部電極19となる多結晶シリコン膜をCVD等で堆積させ、N型不純物のイオン注入および熱処理をし、更に、パターニングすることで上部電極19を形成する。以上が、従来のトレンチ型キャパシタの代表的な構造、及び、その製造方法である。

40

## 【0010】

トレンチ型キャパシタは、図5（c）に示すように、下部電極層を複数個のトレンチが形成されているトレンチ基板表面上に形成することによって、下部電極層表面にできる空乏層幅の広がりを、下部電極層濃度、及び、トレンチのアスペクト比や各トレンチ間距離を調整することにより、抑制、または、制限することができる。その結果、プレーナー型

50

キャパシタで問題となっている入力電圧の変化による、容量値の変化を抑制することができる。また、トレンチ型キャパシタは、単結晶シリコン基板上に容量絶縁膜を形成するので、熱酸化による酸化膜の形成が可能となり、膜厚を薄くすることができる。そのため、容量値を大きくすることが可能となり、積層型キャパシタよりも有利となる。更に、トレンチのアスペクト比や数を調整することで大容量化が可能である。

#### 【0011】

しかし、トレンチ型キャパシタは、トレンチの開口部、及び、底部が角張っている。そのため、トレンチ上に形成した、容量絶縁膜、及び、上部電極の多結晶シリコンの膜厚が、トレンチの開口部、及び、底部の角で膜厚が薄くなってしまう。その結果、トレンチ型キャパシタは、膜厚が薄くなるトレンチの開口部、及び、底部の角で、電界集中による絶縁破壊を生じやすくなり、信頼性が低下するという弱点がある。10

#### 【0012】

上記弱点を受けて、トレンチの開口部、及び、底部を丸くする方法を提案されている（例えば、特許文献1参照）。トレンチの開口部、及び、底部を丸くする方法を図6（a）～（c）に示した工程断面図を用いて説明する。特許文献1では、トレンチ基板上に、MOSFETを形成する場合が記載されているが、ソース、及び、ドレイン領域の形成過程を省略し、ゲート酸化膜を容量絶縁膜に置き換えることによって、上記トレンチの開口部、及び、底部を丸くする方法を適用することができると考えられる。20

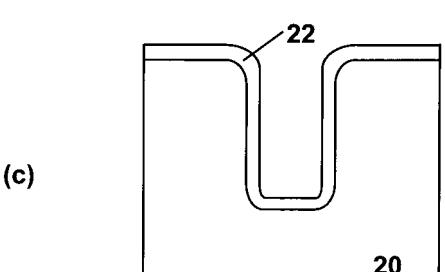

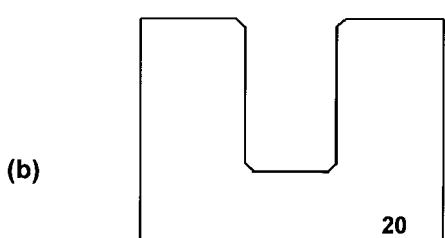

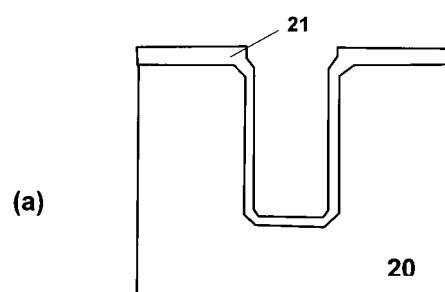

#### 【0013】

半導体基板20表面を酸化した後、部分的に基板表面の酸化膜を除去し、次いで、半導体基板20にトレンチを設ける。その後、熱酸化してトレンチ内に犠牲酸化膜21を形成した時の断面が図6（a）に示されている。次いで、図6（b）に示すように、上記犠牲酸化膜21を除去する。そして、図6（c）に示すように、上記犠牲酸化膜21を除去した半導体基板表面に、酸化膜22（特許文献の場合はゲート酸化膜）を、1000以上（例えば1215）の酸素雰囲気に熱酸化を施すことによって形成する。20

#### 【0014】

特許文献1によれば、トレンチを形成した後、1000以上の酸素雰囲気で熱酸化を行って酸化膜を形成し、そして、熱酸化によって形成した酸化膜を除去する工程を、1～2回繰り返すことにより、トレンチの開口部、及び、底部を丸くすることができる。トレンチの開口部、及び、底部を丸くすることによって、トレンチの角で生じる電界集中を回避することができる。30

#### 【先行技術文献】

#### 【特許文献】

#### 【0015】

【特許文献1】特開平7-263692号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0016】

しかし、上記の方法では、トレンチの開口部、及び、底部を丸くするために、1000以上という高温の酸素雰囲気で、酸化膜を形成、及び、除去する工程が1～2回必要とするが、高温での熱処理は、基板に転移等のダメージが生じやすくなってしまうという課題を有している。また、高温での熱処理は、すでに形成してある不純物層の再分布を引き起こすため、濃度のばらつきを増大させる可能性が高くなるという課題もある。40

そこで、本発明の目的は、高温熱処理をせずに形成可能であり、かつ、信頼性劣化が少なく、かつ、従来のトレンチキャパシタと同様に、安定した容量値の供給、及び、大容量化が可能な、半導体キャパシタ、及び、その製造方法を提供することである。

#### 【課題を解決するための手段】

#### 【0017】

本発明では、上記目的を達成するために、次の手段を用いた。

まず、第1導電型半導体基板表面に形成された台形状トレンチを有する容量素子形成領50

域と、前記容量素子領域の台形状トレンチに沿って設けられた第2導電型下部電極層と、少なくとも前記下部電極層の表面に形成された容量絶縁膜と、前記容量絶縁膜の表面に形成された第2導電型上部電極とからなることを特徴とする半導体装置とした。

#### 【0018】

また、前記台形状トレンチは、複数であることを特徴とする半導体装置とした。

また、第1導電型半導体基板上にLOCOS法により厚い酸化膜領域と薄い酸化膜領域を形成する工程と、前記厚い酸化膜領域と前記薄い酸化膜領域の酸化膜を前記半導体基板から除去する工程と、前記台形状トレンチの表面に第2導電型不純物を導入して下部電極層を形成する工程と、少なくとも前記下部電極層上に容量絶縁膜を形成する工程と、前記容量絶縁膜上に上部電極となる多結晶シリコン膜を堆積する工程と、前記上部電極となる多結晶シリコンに第2導電型不純物を導入し、所定の形状とすることで上部電極とする工程とからなることを特徴とする半導体装置の製造方法を用いた。

10

#### 【0019】

また、前記容量絶縁膜を形成する工程は、熱酸化による酸化膜形成工程であることを特徴とする半導体装置の製造方法を用いた。

そして、前記容量絶縁膜を形成する工程は、減圧CVDによるシリコン窒化膜形成工程であることを特徴とする半導体装置の製造方法を用いた。

#### 【発明の効果】

#### 【0020】

本発明によれば、既存の素子分離技術であるLOCOS (Local Oxidation of Silicon) 法を応用し、LOCOS型トレンチ基板を形成することによって、高温熱処理をせずに形成でき、かつ、信頼性劣化が少なく、かつ、従来のトレンチキャパシタと同様に、安定した容量値の供給、及び、大容量化が可能な、半導体キャパシタ、及び、その製造方法を提供することができる。

20

#### 【図面の簡単な説明】

#### 【0021】

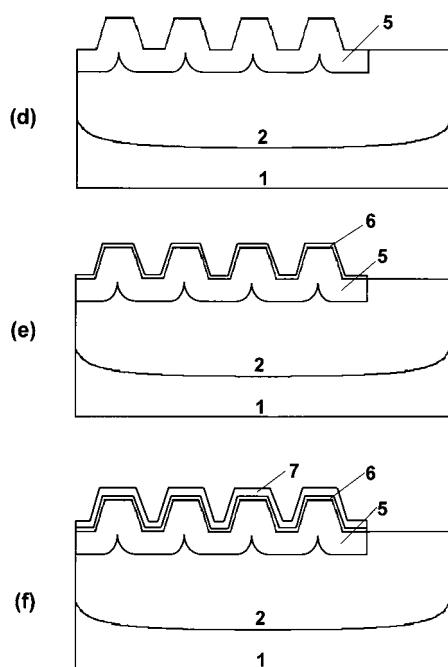

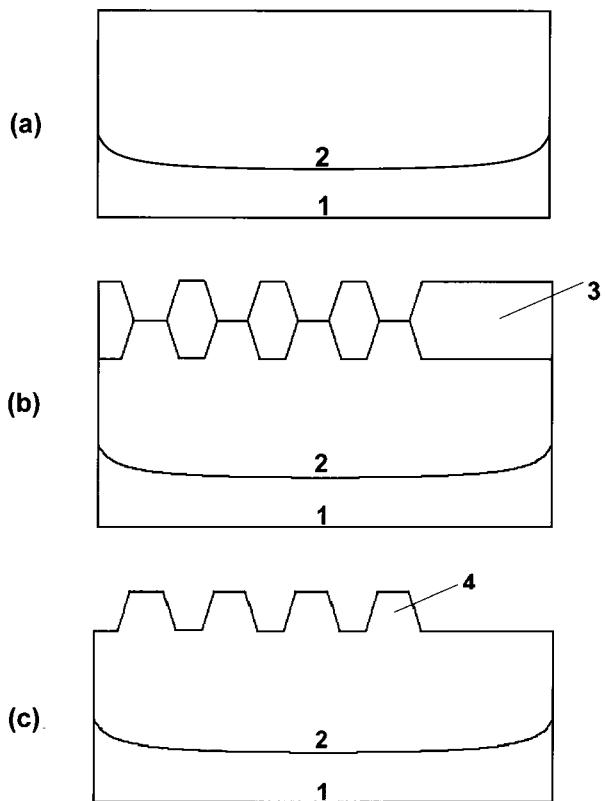

【図1】本発明の半導体キャパシタの構造、及び、その製造過程を模式的に示す工程断面図である。

【図2】図1に続く、本発明の半導体キャパシタの構造、及び、その製造過程を模式的に示す工程断面図である。

30

【図3】従来のプレーナー型キャパシタの構造、及び、その製造過程を模式的に示す工程断面図である。

【図4】従来の積層型キャパシタの構造、及び、その製造過程を模式的に示す工程断面図である。

【図5】従来のトレンチ型キャパシタの構造、及び、その製造過程を模式的に示す工程断面図である。

【図6】特許文献1に記載の、トレンチの開口部、及び、底部を丸くする方法を模式的に示す工程断面図である。

30

#### 【発明を実施するための形態】

#### 【0022】

以下、本発明の実施の形態について詳細に説明する。

図1(a)～(c)および図2(d)～(f)は、本実施の形態の半導体装置、及び、その製造方法を説明するための工程断面図である。本実施の形態では、P型半導体基板を使用した容量素子を例に説明するが、本発明の本質は、基板の導電型、及び、不純物の種類、及び、その導電型に依存しないので、基板の導電型、及び、不純物の種類、及び、その導電型が異なっても同様に実施することが可能である。

40

#### 【0023】

以下、本実施の形態を、図1(a)～(c)および図2(d)～(f)に示す工程断面図を用いて、本実施の形態の半導体装置の構造、及び、その製造方法を説明する。

まず、図1(a)に示すように、P型不純物(例えばボロン)を添加した抵抗率20

50

cm ~ 3.0 cm の不純物濃度の P 型半導体基板 1 上に、 P 型ウェル 2 を、 P 型不純物（例えば、ボロン）をドーズ量  $1 \times 10^{11} \sim 1 \times 10^{13}$  atoms/cm<sup>2</sup> でイオン注入、及び、熱処理して拡散させることにより形成する。上記ウェルの有無は、本実施の形態の本質に関係ないので、ウェルを形成しないで容量素子を半導体基板上に直接形成することも可能である。

#### 【0024】

次に、図 1 ( b ) に示すように、上記 P 型ウェル 2 の形成された基板表面の一部に、既存の素子分離技術である LOCOS 法を用いて、厚い酸化膜 3 を 0.2 mm ~ 4.0 mm の膜厚で熱酸化することで形成し、厚い酸化膜領域と薄い酸化膜領域を平行に隣接して設ける。このとき、厚い酸化膜 3 が形成されない領域（薄い酸化膜領域）の数、及び、その間隔の大きさは製造する容量素子の容量、及び、空乏層幅の広がりを抑制する程度に合わせて決定する。

10

#### 【0025】

次に、図 1 ( c ) に示すように、 Wet エッティングにより表面の酸化膜を全て除去して、シリコン基板表面に、複数の台形状の LOCOS トレンチ型の容量素子形成領域 4 を形成する。

#### 【0026】

次に、図 2 ( d ) に示すように、下部電極層 5 を、高濃度の N 型不純物（例えば、砒素）をドーズ量  $5 \times 10^{13} \sim 1 \times 10^{15}$  atoms/cm<sup>2</sup> で容量素子形成領域の基板表面にイオン注入することによって形成する。このとき、下部電極層 5 は半導体基板 1 上に形成された P 型ウェル 2 表面の容量素子形成領域 4 に、半導体基板表面の台形状のトレンチに沿って設けられる。

20

#### 【0027】

次に、図 2 ( e ) に示すように容量絶縁膜 6 となる酸化膜を、下部電極層 5 の表面に熱酸化により、例えば、膜厚数十 nm ~ 1 μm となるように形成する。容量絶縁膜 6 は熱酸化膜に限ることではなく、シリコン窒化膜であっても良いが、その場合は台形状トレンチ表面を一様に覆うように減圧 CVD による成膜が好ましい。

#### 【0028】

次に、図 2 ( f ) に示すように、容量素子の上部電極 7 を、容量絶縁膜 6 表面に多結晶シリコンを堆積させ、N 型不純物（例えば、リン）をドーズ量  $1 \times 10^{15} \sim 10^{16}$  atoms/cm<sup>2</sup> でイオン注入し、パターニングによって形成する。なお、不純物導入工程は、イオン注入の代わりにプリデポジションで行っても良い。上部電極 7 を形成した後の、電極配線以降（金属配線や保護膜の形成過程）の工程は、一般的な半導体装置の製造方法と同様であるので、詳細な説明は割愛する。以上が、本実施の形態の半導体装置の構造、及び、その製造方法である。

30

#### 【0029】

以上に説明した、本実施の形態により次のような効果を得ることができる。

既存の素子分離技術である、 LOCOS ( Local Oxidation of Silicon ) 法と Wet エッティングを用いて形成された、 LOCOS 型トレンチは従来のトレンチと比較して、トレンチの開口部、及び、底部の角は急峻ではないので、角部での電界集中による絶縁破壊等の信頼性劣化を緩和することができる。また、上記 LOCOS 型トレンチは、トレンチの角を丸くする必要がないため、基板に転移等のダメージを生じさせる原因となる高温での熱処理使わずに、本半導体キャパシタを形成することが可能である。

40

#### 【0030】

また、下部電極層濃度、及び、上記 LOCOS 型トレンチの間隔を調整することによって、入力電圧による空乏層幅の変化を抑えることができ、その結果、安定した容量値を得ることができる。

#### 【0031】

更に、容量絶縁膜は単結晶シリコン基板上に形成するので、膜質の良い熱酸化膜の使用

が可能なので、膜厚を薄くでき、積層（P I P）型と比較して容量を大きくすることが可能となる。

また、LOCOS型トレンチの数、及び、深さを調整することで大容量化も可能となる。

### 【符号の説明】

#### 【0032】

- 1 P型半導体基板

- 2 P型ウェル

- 3 厚い酸化膜

- 4 容量素子形成領域

- 5 下部電極層

- 6 容量絶縁膜

- 7 上部電極

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

F ターム(参考) 5F038 AC03 AC05 AC10 EZ15 EZ16 EZ20