(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년04월29일

(11) 등록번호 10-1389626

(24) 등록일자 2014년04월21일

(51) 국제특허분류(Int. Cl.)

H01L 23/485 (2006.01) H01L 21/60 (2006.01)

(21) 출원번호 10-2012-7015587

(22) 출원일자(국제) 2010년11월11일

심사청구일자 2012년06월15일

(85) 번역문제출일자 2012년06월15일

(65) 공개번호 10-2012-0095426

(43) 공개일자 2012년08월28일

(86) 국제출원번호 PCT/US2010/056310

(87) 국제공개번호 WO 2011/084235

국제공개일자 2011년07월14일

(30) 우선권주장

12/653,710 2009년12월17일 미국(US)

(56) 선행기술조사문헌

US20080149384 A1\*

US20090174065 A1

JP2001053191 A

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

인텔 코포레이션

미국 캘리포니아주 95054 산타클라라 미션 칼리지

볼바드 2200

(72) 발명자

마 펭

미국 캘리포니아주 95070 사라토가 스컬리 애비뉴

12540

라오 밸러리 알

미국 캘리포니아주 95070 사라토가 엘 키토 웨이

15115

(뒷면에 계속)

(74) 대리인

제일특허법인

전체 청구항 수 : 총 16 항

심사관 : 정구원

(54) 발명의 명칭 집적 회로 장치들을 위한 유리 코어 기판 및 그 제조 방법

**(57) 요약**

집적 회로(IC) 장치를 위한 유리 코어 기판의 실시예들이 개시된다. 유리 코어 기판은 유리 코어, 및 유리 코어의 대향하는 면들 상의 빌드업 구조물을 포함한다. 유리 코어 기판의 양면 상에 전기 전도성 단자들이 형성될 수 있다. IC 다이는 기판의 한 면의 단자들과 연결될 수 있는 반면, 반대 면의 단자들은 회로 보드와 같은 다음 레벨 컴포넌트와 연결될 수 있다. 유리 코어는 도전체들이 형성되어 있는 단 한 개의 유리를 포함하거나, 유리 코어는 함께 결합된 둘 이상의 유리 부분을 포함할 수 있는데, 각각의 부분은 도전체들을 갖는다. 도전체들은 유리 코어를 관통하여 연장되며, 도전체들 중 하나 이상은 유리 코어 위에 배치된 빌드업 구조물들과 전기 연결될 수 있다. 다른 실시예들이 설명되고 청구된다.

**대 표 도**

(a)

(72) 발명자

트랜 쿠안 에이

미국 캘리포니아주 94539 프레몬트 고메스 로드

1901

산크만 로버트 엘

미국 아리조나주 85044 피닉스 사우스 34번 웨이

13202

스완 조안나 엠

미국 아리조나주 85255 스코츠데일 노스 84번 웨이

19815

---

## 특허청구의 범위

### 청구항 1

비결정질 고체 유리(amorphous solid glass)로 구성되되, 제1 표면 및 대향하는 제2 표면을 가지는 비결정질 고체 유리 코어와,

상기 제1 표면으로부터 상기 제2 표면까지 상기 비결정질 고체 유리 코어를 관통하여 연장되는 복수의 도전체 - 상기 복수의 도전체는 전도성 물질로 채워진, 상기 비결정질 고체 유리 코어를 관통하는 개구(opening)를 포함함 - 와,

상기 비결정질 고체 유리 코어의 상기 제1 표면에 배치된 적어도 하나의 유전체층 및 적어도 하나의 금속층 - 상기 제1 표면의 상기 적어도 하나의 금속층은 상기 도전체 중 적어도 하나에 전기적으로 연결됨 - 과,

상기 비결정질 고체 유리 코어의 상기 제2 표면에 배치된 적어도 하나의 유전체층 및 적어도 하나의 금속층 - 상기 제2 표면의 상기 적어도 하나의 금속층은 상기 도전체 중 적어도 하나에 전기적으로 연결됨 - 을 포함하는 기판.

### 청구항 2

제1항에 있어서,

상기 비결정질 고체 유리 코어는 단일의 유리를 포함하는 기판.

### 청구항 3

제1항에 있어서,

상기 비결정질 고체 유리 코어는 함께 결합된 둘 이상의 유리 부분을 포함하는 기판.

### 청구항 4

제1항에 있어서,

상기 도전체 각각은 상기 비결정질 고체 유리 코어 내에 형성된 홀 및 상기 홀 내에 배치된 전기 전도성 물질을 포함하는 기판.

### 청구항 5

제4항에 있어서,

상기 홀의 벽에 배치된 습윤층(wetting layer)을 더 포함하는 기판.

### 청구항 6

제4항에 있어서,

상기 전기 전도성 물질은 금속을 포함하는

기판.

#### 청구항 7

제4항에 있어서,

상기 홀의 벽은 상기 홀의 중심선에 대하여 비스듬히 테이퍼져(tapered) 있는

기판.

#### 청구항 8

제1항에 있어서,

상기 도전체 각각은 상기 비결정질 고체 유리 코어 내에 내장된 금속 와이어를 포함하는

기판.

#### 청구항 9

제1항에 있어서,

상기 비결정질 고체 유리 코어의 상기 제1 표면에 배치된 상기 적어도 하나의 금속층은 상기 제1 표면에 바로 인접하여 배치되어, 상기 비결정질 고체 유리 코어의 상기 제2 표면에 배치된 상기 적어도 하나의 금속층은 상기 제2 표면에 바로 인접하여 배치되는

기판.

#### 청구항 10

제1항에 있어서,

상기 비결정질 고체 유리 코어의 제1 면에 배치되는 제1 세트의 단자 - 상기 제1 세트의 단자는 집적 회로(IC) 다이 상의 대응하는 단자의 어레이와 짹을 이룸 - 와,

상기 비결정질 고체 유리 코어의 제2 면 상에 배치되는 제2 세트의 단자 - 상기 제2 세트의 단자는 다음-레벨 컴포넌트(a next-level component) 상의 대응하는 단자의 어레이와 짹을 이룸 - 를 더 포함하는

기판.

#### 청구항 11

비결정질 고체 유리판 내에 복수의 홀을 형성하는 단계 - 상기 비결정질 고체 유리판은 제1 표면 및 상기 제1 표면에 실질적으로 평행한 대향하는 제2 표면을 갖고, 각각의 홀은 상기 제1 표면으로부터 상기 제2 표면까지 연장되며, 상기 홀은 임프린팅(imprinting), 샌드 블라스팅(sand blasting) 및 캐스팅(casting)을 포함하는 그룹으로부터 선택되는 공정에 의해 형성됨 - 와,

각각의 홀 내에 도전체를 형성하기 위해 상기 홀 각각에 전기 전도성 물질을 배치하는 단계와,

상기 비결정질 고체 유리판의 상기 제1 표면에 적어도 하나의 유전체층 및 적어도 하나의 금속층을 배치하며,

상기 제1 표면의 상기 적어도 하나의 금속층을 상기 도전체 중 적어도 하나와 전기적으로 연결하는 단계와,

상기 비결정질 고체 유리판의 상기 제2 표면에 적어도 하나의 유전체층 및 적어도 하나의 금속층을 배치하며, 상기 제2 표면의 상기 적어도 하나의 금속층을 상기 도전체 중 적어도 하나와 전기적으로 연결하는 단계를 포함하는

방법.

### 청구항 12

제11항에 있어서,

상기 전기 전도성 물질을 배치하는 단계 전에, 각각의 홀의 벽에 습윤 층을 배치하는 단계를 더 포함하는 방법.

### 청구항 13

제12항에 있어서,

상기 전기 전도성 물질은 금속을 포함하는

방법.

### 청구항 14

제11항에 있어서,

각각의 홀의 벽은 상기 홀의 중심선에 대하여 비스듬히 테이퍼드(tapered) 있는

방법.

### 청구항 15

제11항에 있어서,

상기 비결정질 고체 유리판의 상기 제1 표면에 배치된 상기 적어도 하나의 금속층은 상기 제1 표면에 바로 인접하여 배치되며, 상기 비결정질 고체 유리판의 상기 제2 표면에 배치된 상기 적어도 하나의 금속층은 상기 제2 표면에 바로 인접하여 배치되는

방법.

### 청구항 16

제11항에 있어서,

상기 비결정질 고체 유리판의 제1 면에 제1 세트의 단자를 배치하는 단계 - 상기 제1 세트의 단자는 집적 회로 (IC) 다이 상의 대응하는 단자의 어레이와 짹을 이름 - 와,

상기 유리판의 제2 면에 제2 세트의 단자를 배치하는 단계 - 상기 제2 세트의 단자는 다음 레벨 컴포넌트 상의 대응하는 단자의 어레이와 짹을 이름 - 를 더 포함하는

방법.

### 청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

## 명세서

### 기술분야

[0001] 개시된 실시예들은 일반적으로 집적 회로 장치를 위한 기판들에 관한 것으로서, 특히 유리 코어를 갖는 기판에 관한 것이다.

### 배경기술

[0002] 집적 회로(IC) 다이는 다이를 지지하기 위해서뿐만 아니라 다이와 마더보드, 메인보드 또는 다른 회로 보드와 같은 다음 레벨 컴포넌트 사이의 전기 접속들을 형성하는 것을 돋기 위해서 패키지 내에 배치될 수 있다. 패키지는 전형적으로 다이가 기계적 그리고 전기적으로 연결되는 기판을 포함한다. 예를 들어, IC 다이는 상호접속부들의 어레이에 의해 플립 칩 배열로 기판에 연결될 수 있으며, 이 경우 언더필(underfill) 층이 그 상호접속부들 주위 및 기판과 다이 사이에 배치된다. 상호접속부들 각각은 기판 상의 짹을 이루는 단자(예를 들어 패드, 필러(pillar), 스터드 범프 등)에 (예를 들어 리플로우된 솔더에 의해) 전기 연결되는 다이 위의 단자(예를 들어 본드 패드, 구리 필러 또는 스터드 범프 등)를 포함할 수 있다. 대안적으로, 다른 예로서, IC 다이는 다이 부착 접착층에 의해 기판에 부착될 수 있으며, 복수의 와이어 본드가 다이와 기판 사이에 형성될 수 있다.

[0003] IC 다이는 기판의 한 면에 배치되며, 복수의 전기 전도성 단자가 기판의 반대면에 배치된다. 기판의 반대면 상의 단자들은 다음 레벨 컴포넌트(예를 들어 회로 보드)와의 전기 접속들을 형성하기 위해 이용될 것이고, 이러한 전기 접속들은 다이에 전력을 전달하며 다이로 및 다이로부터 입력/출력(I/O) 신호들을 송신하기 위해 이용

될 수 있다. 기판의 반대면 상의 전기 전도성 단자들은 펈, 패드, 랜드, 컬럼, 범프 등의 어레이를 포함할 수 있으며, 이러한 단자들은 회로 보드 또는 다른 다음 레벨 컴포넌트 상의 대응하는 단자 어레이에 전기 연결될 수 있다. 패키지 기판의 반대 면 상의 단자들은 예를 들어 소켓(및 리텐션 기구)을 이용하여 또는 솔더 리플로우 공정에 의해 다음 레벨 보드에 연결될 수 있다.

### 도면의 간단한 설명

[0004]

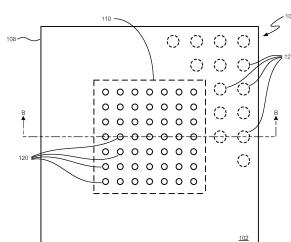

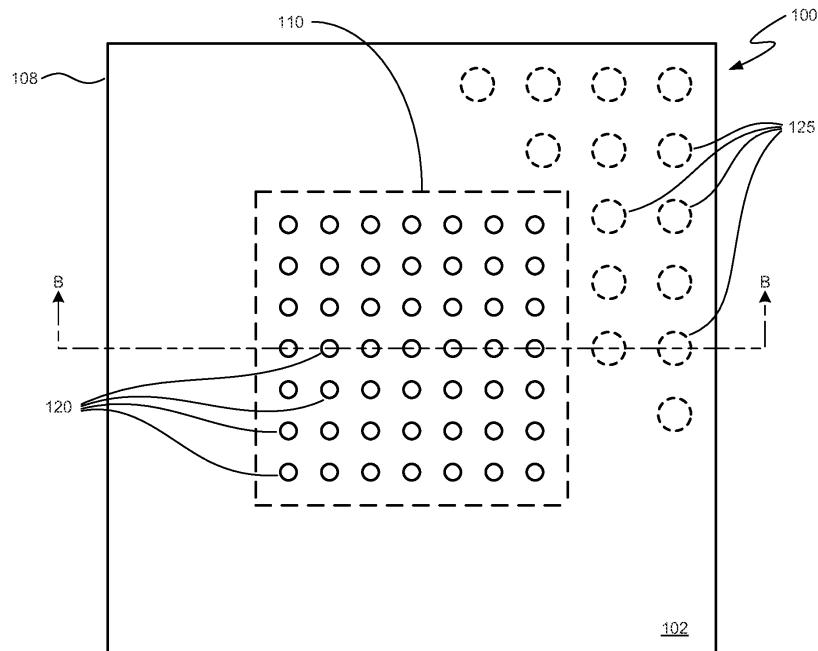

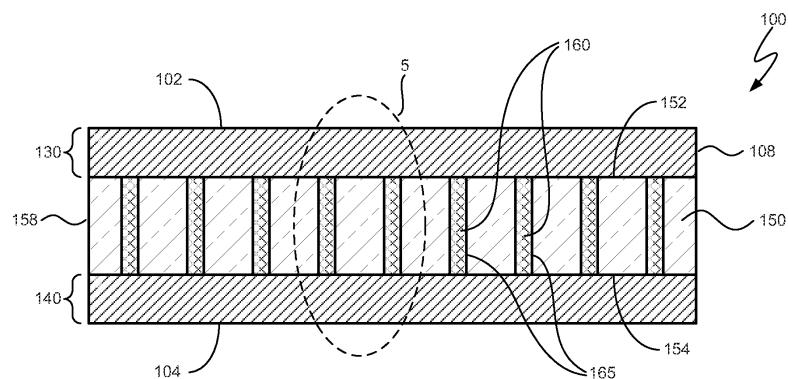

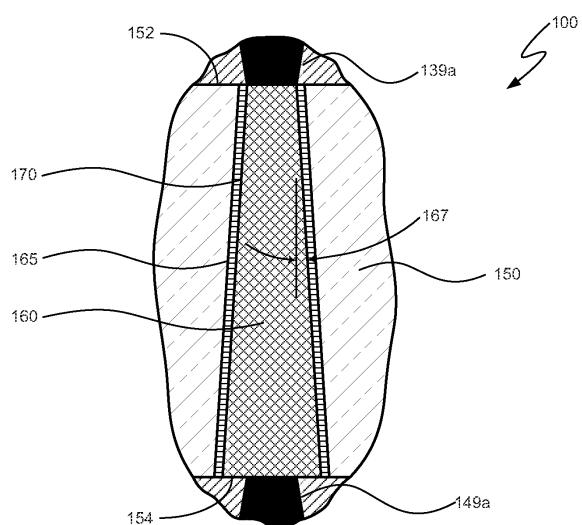

도 1a는 유리 코어 기판의 일 실시예의 평면도를 도시한 개략도이다.

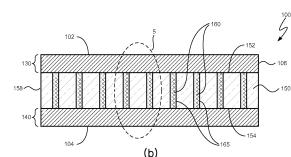

도 1b는 도 1a의 선 B-B에 따른 도 1a의 유리 코어 기판의 단면 정면도를 보여주는 개략도이다.

도 1c는 도 1b의 단면 정면의 일부분을 보여주며 유리 코어 기판의 다른 실시예를 도시하는 개략도이다.

도 1d는 도 1b의 단면 정면의 일부분을 보여주며 유리 코어 기판의 추가 실시예를 도시하는 개략도이다.

도 1e는 도 1b의 단면 정면의 일부분을 보여주며 유리 코어 기판의 또 다른 실시예를 도시하는 개략도이다.

도 1f는 도 1e의 일부분을 보여주며 유리 코어 기판의 또 다른 실시예를 도시하는 개략도이다.

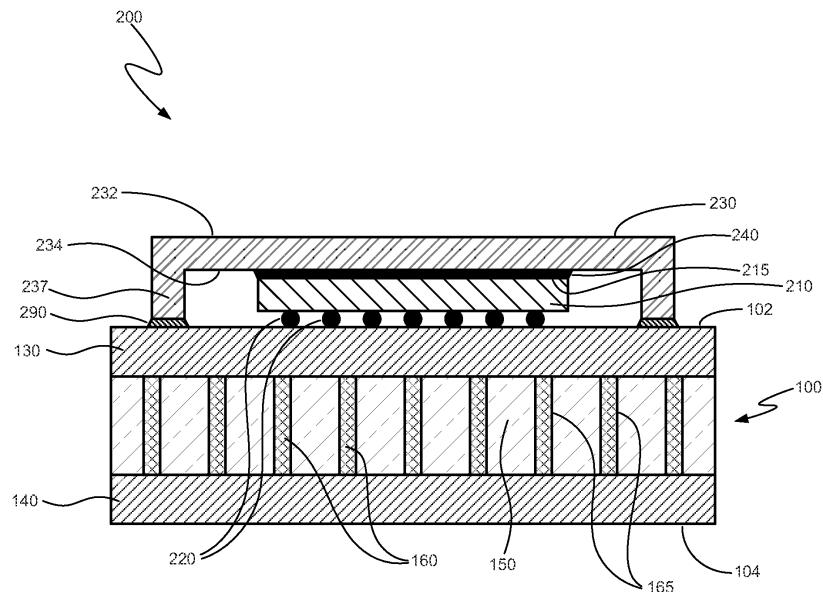

도 2는 유리 코어 기판의 실시예를 포함하는 접적 회로 어셈블리의 단면 정면도를 보여주는 개략도이다.

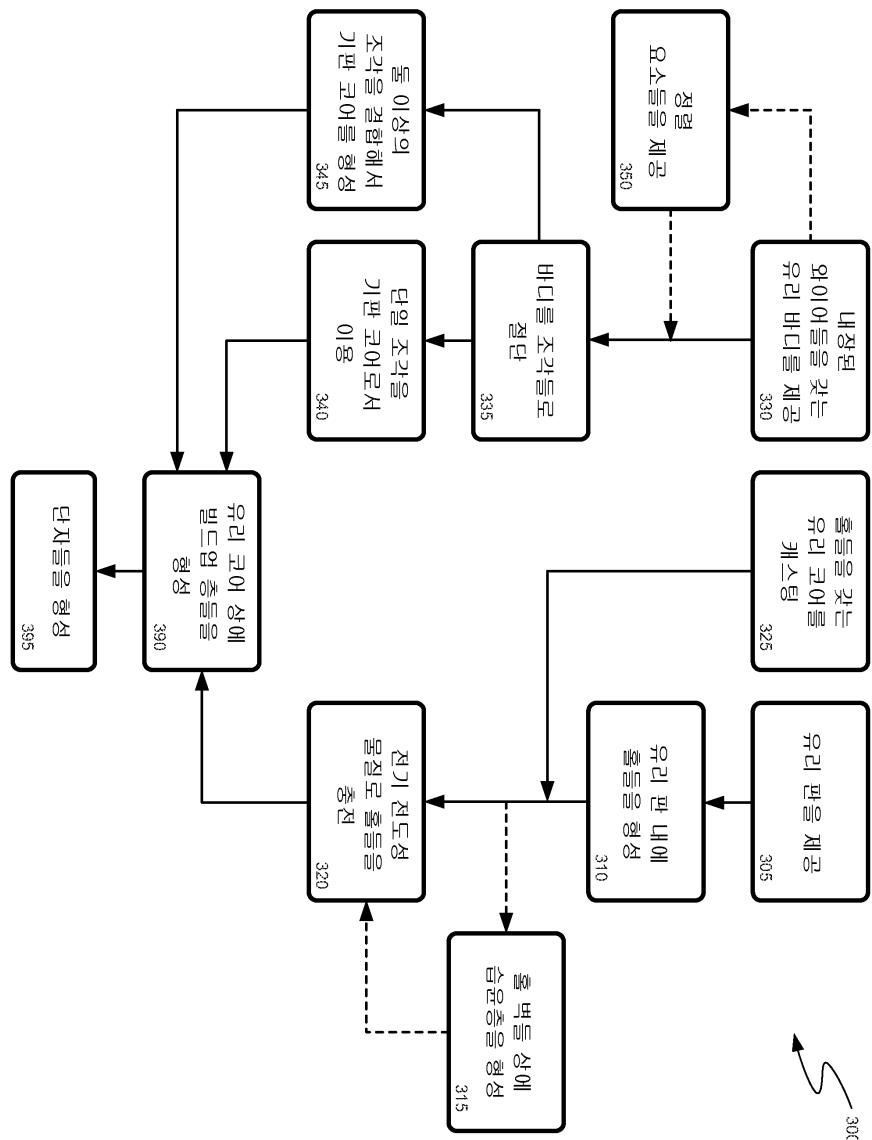

도 3은 유리 코어 기판을 형성하는 다양한 방법들의 실시예들을 도시하는 블록도이다.

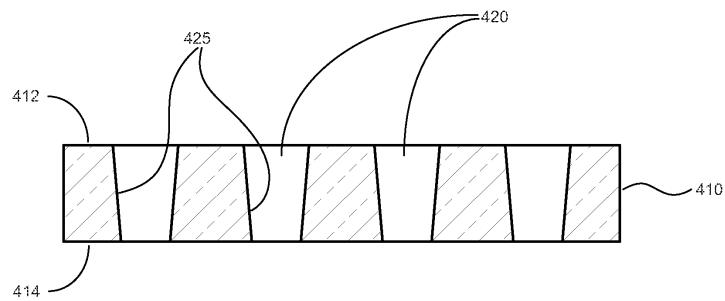

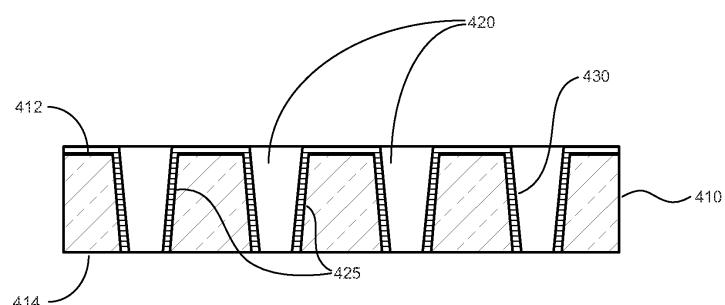

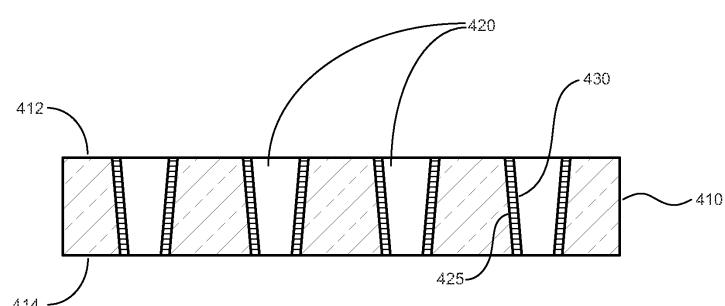

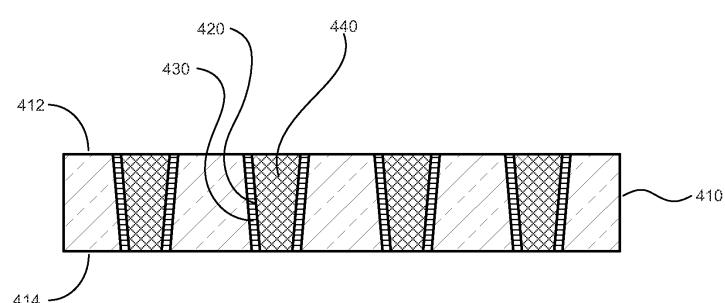

도 4a-4f는 유리 코어 내에 홀들을 형성하는 방법의 실시예들을 도시하는 개략도이다.

도 5a-5c는 유리 코어 내에 홀들을 형성하는 대안적인 방법의 실시예들을 도시하는 개략도이다.

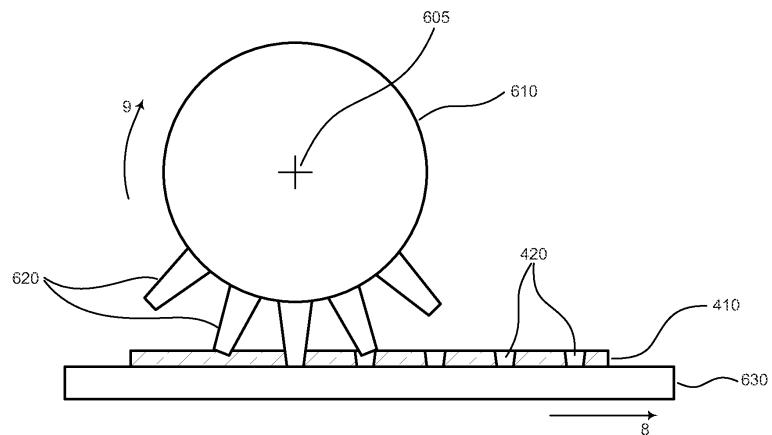

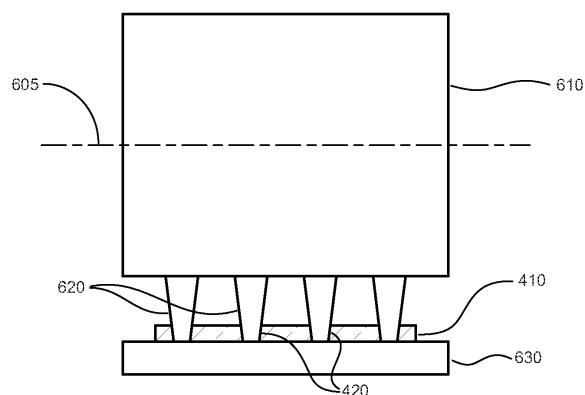

도 6a-6b는 유리 코어 내에 홀들을 형성하는 추가의 대안적인 방법의 실시예들을 도시하는 개략도이다.

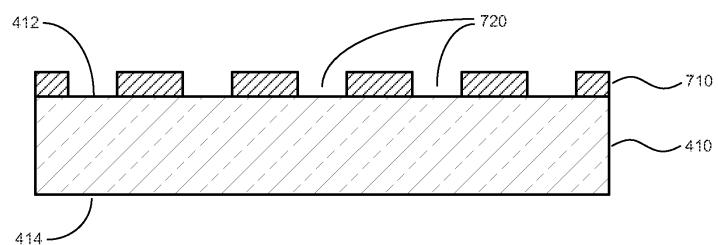

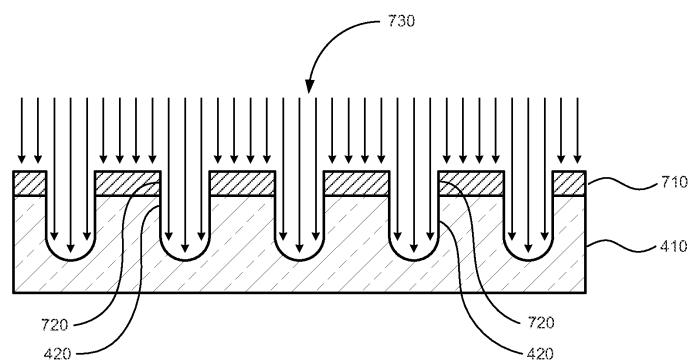

도 7a-7c는 유리 코어 내에 홀들을 형성하는 또 다른 대안적인 방법의 실시예들을 도시하는 개략도이다.

도 8a-8c는 유리 코어 내에 홀들을 형성하는 또 다른 대안적인 방법의 실시예들을 도시하는 개략도이다.

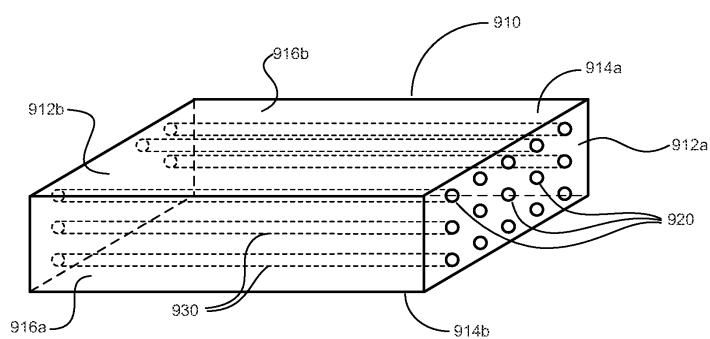

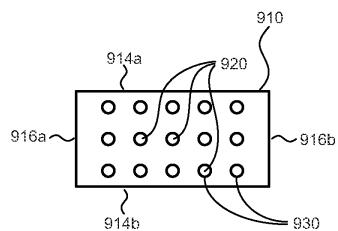

도 9a는 내장된 금속 와이어들을 갖는 유리 바디의 실시예의 사시도를 보여주는 개략도이다.

도 9b는 도 9a에 도시된 내장된 금속 와이어들을 갖는 유리 바디의 측면 정면도를 보여주는 개략도이다.

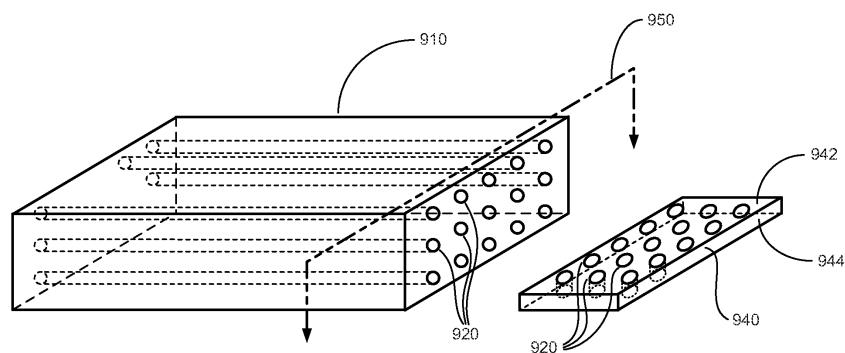

도 9c는 도 9a-9b의 유리 바디로부터 조각을 절단하는 것의 사시도를 보여주는 개략도이다.

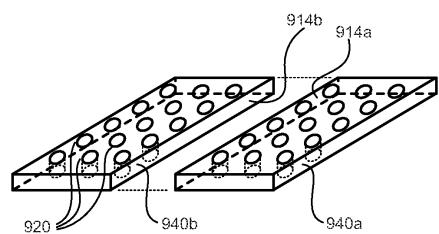

도 10a-10c는 도 9a-9b의 유리 바디로부터의 둘 이상의 조각을 결합하는 것의 실시예들을 도시하는 개략도이다.

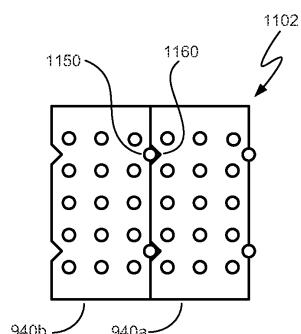

도 11a는 내장된 금속 와이어들과 정렬 요소들을 갖는 유리 바디의 다른 실시예의 사시도를 보여주는 개략도이다.

도 11b는 도 11a에 도시된 것과 같은 내장된 금속 와이어들과 정렬 요소들을 갖는 유리 바디의 측면 정면도를 보여주는 개략도이다.

도 11c-11d는 도 11a-11b의 유리 바디로부터의 둘 이상의 조각을 결합하는 것의 실시예들을 도시한 개략도이다.

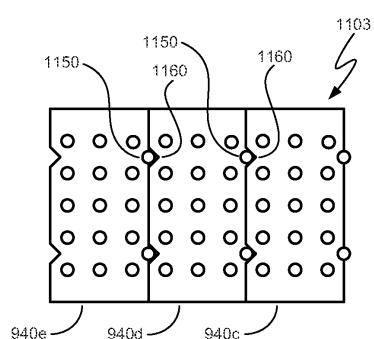

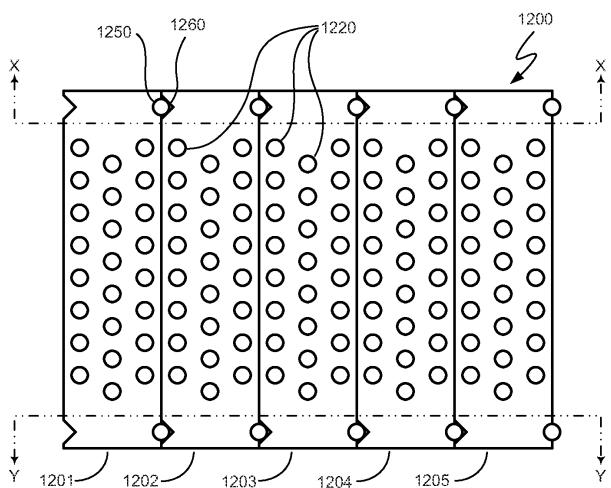

도 12는 내장된 금속 와이어들 및 정렬 요소들을 갖는 유리 바디로부터 절단된 부분들을 결합하는 것의 다른 실시예를 도시한 개략도이다.

도 13은 내장된 금속 와이어들 및 정렬 요소들을 갖는 유리 바디로부터 절단된 부분들을 결합하는 것의 다른 실시예를 도시한 개략도이다.

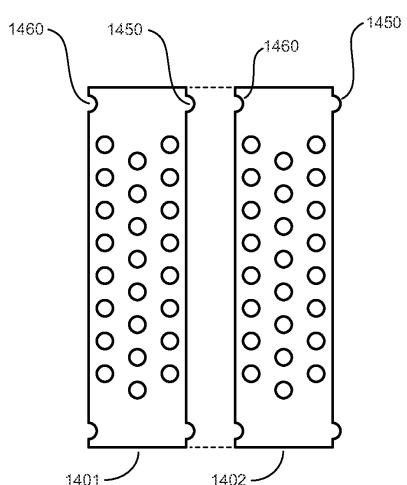

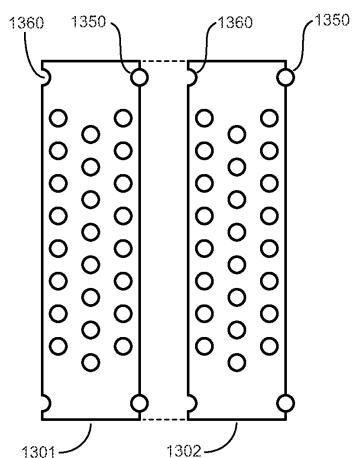

도 14는 내장된 금속 와이어들 및 정렬 요소들을 갖는 유리 바디로부터 절단된 부분들을 결합하는 것의 또 다른 실시예를 도시한 개략도이다.

### 빌명을 실시하기 위한 구체적인 내용

[0005]

유리 코어를 갖는 기판의 실시예들이 개시된다. 유리 코어의 각 면에 하나 이상의 빌드업(buildup) 층이 배치될 수 있으며, 전기 도전체들은 유리 코어를 관통하여 연장된다. 유리 코어는 단 하나의 유리 단편을 포함할 수 있거나, 다른 실시예들에서는 유리 코어가 함께 결합된 둘 이상의 유리 부분을 포함한다. 유리 코어의 두께를 관통하여 연장하는 도전체들을 갖는 유리 코어 기판을 형성하는 방법들의 실시예들이 이하에 설명된다. 또

한, 유리 코어 기판 상에 배치되고 상호접속부들의 세트에 의해 기판에 연결된 접적 회로 다이를 포함하는 어셈블리의 실시예들도 개시된다.

[0006] 위에서 언급된 바와 같이, 개시된 실시예들은 유리로 구성된 코어를 갖는 기판을 포괄한다. 일 실시예에 따르면, "유리(glass)"라는 용어는 비결정질 고체를 지칭한다. 설명되는 실시예들에서 이용될 수 있는 유리 재료들의 예는 순수 이산화규소(예를 들어 약 100% SiO<sub>2</sub>), 소다 석회 유리, 봉규산염 유리 및 알루미노 규산염 유리(alumino-silicate glass)를 포함한다. 그러나, 개시된 실시예들은 규소계 유리 조성들로만 한정되지 않고, 대안적인 기저 재료를 갖는 유리들(예를 들어 플루오르 유리, 인산 유리, 칼코겐 유리 등)도 개시된 실시예들과 함께 이용될 수 있다. 또한, 소기의 물리적 속성들을 갖는 유리를 형성하기 위해, 다른 재료들 및 첨가제들의 임의의 조합이 이산화규소(또는 다른 기저 재료)와 조합될 수 있다. 이러한 첨가제들의 예는 위에서 언급된 탄산칼슘(예를 들어 석회) 및 탄산나트륨(예를 들어 소다)뿐만 아니라, 마그네슘, 칼슘, 망간, 알루미늄, 납, 붕소, 철, 크롬, 칼륨, 황 및 안티몬과, 이러한 원소들 및 다른 원소들의 탄산염 및/또는 산화물을 포함한다. 위에서 언급된 유리들 및 첨가제들은 개시된 실시예들과 함께 적용될 수 있는 많은 유형의 재료들 및 재료 조합들 중의 몇몇 예에 지나지 않는다. 또한, 유리 바디(glass body)는 강도 및/또는 내구성을 개선하기 위한 표면 처리 및/또는 코팅을 포함할 수 있으며, 유리 바디는 또한 내적 응력(internal stresses)을 저하시키기 위해 어닐링될 수 있다.

[0007] 일반적으로, 여기에서 이용될 때의 "유리"라는 용어는 고체 형태에서 비결정질일 수 있는 유기 고분자 재료는 지칭하지 않는다. 그러나, 일부 실시예들에 따른 유리는 재료의 구성성분 중 하나로서 탄소를 포함할 수 있음을 이해해야 한다. 예를 들어, 소다 석회 유리는 물론, 이러한 유리 유형의 복수의 변형들도 탄소를 포함한다.

[0008] 일단 고체 바디로 형성되고 난 유리는 연화될 수 있고, 아마도 액체 형태로 다시 용융될 수 있다. 유리 재료의 "유리 전이 온도"는 그 온도 아래에서는 유리의 물리적 속성들이 고체의 속성들과 유사하고 그 온도 위에서는 유리 재료가 액체처럼 행동하는 온도이다. 유리가 유리 전이 온도보다 충분히 아래에 있는 경우, 유리의 분자들은 상대적 이동도를 거의 갖지 않을 수 있다. 유리가 유리 전이 온도에 근접함에 따라, 유리는 연화하기 시작할 수 있고, 온도가 증가하면 유리는 궁극적으로 액체 상태로 용융될 것이다. 따라서, 유리 바디는 바디의 형상의 조작을 가능하게 하기에 충분한 범위까지 연화될 수 있어서, 유리 바디 내에서의 홀들 또는 다른 특징 형상들의 형성을 허용한다.

[0009] 일 실시예에 따르면, 유리의 "연화 온도(softening temperature)"는 유리가 개시된 실시예들이 수행될 수 있게 하기에 충분한 범위로까지 연화되는 온도이다. 예를 들어, 일 실시예에서 유리의 연화 온도는 유리가 (이하에 더 상세하게 설명될) 임프린팅 기법에 의해 유리 내에 홀들 또는 다른 특징 형상들을 형성하는 것을 허용하기에 충분하도록 연화되는 온도이다. 둘 이상의 상이한 유리 재료가 유사한 유리 전이 및/또는 연화 온도를 가질 수 있긴 하지만, 유리 전이 및 연화 온도는 유리의 고유한 속성들이다. 또한, 특정 유리의 유리 전이 온도 및 연화 온도가 반드시 동일한 값은 아닐 수도 있음에 유의해야 한다.

[0010] 이제 도 1a 및 도 1b를 보면, 유리로 구성된 코어(150)를 갖는 기판(100)의 실시예들이 도시되어 있다. 유리 코어 기판(100)의 평면도가 도 1a에 도시되어 있는 반면, 도 1a의 선 B-B를 따라 절취된 기판의 단면 정면도는 도 1b에 도시되어 있다. 또한, 유리 코어 기판(100)의 다양한 대안적인 실시예들이 도 1c 내지 도 1e 각각에 도시되어 있으며, 도 1c 내지 도 1e 각각은 도 1b의 참조 번호 5에 의해 개괄적으로 식별된 기판(100)의 부분을 확대도로 도시하고 있다.

[0011] 도 1a 및 도 1b를 참조하면, 기판(100)은 유리로 구성된 코어(150)를 포함한다. 기판(100)은 제1 면(102), 및 대체적으로 제1 면(102)에 평행한 대향하는 제2 면(104)을 포함한다. 기판(100)의 외연(periphery)(108)은 제1 면(102)과 제2 면(104) 사이에서 연장된다. 일부 실시예들에 따르면, 기판(100)의 외연(108)은 대체적으로 직사각형이며, 일 실시예에서는 외연(108)의 네 변 전부가 실질적으로 동일하여, 외연이 정사각형을 형성한다. 그러나, 직사각형이 아닌 외연을 갖는 기판도 개시된 실시예들의 범위 내에 든다는 점에 유의해야 한다. 일 실시예에서, 기판(100)은 0.2mm와 1mm 사이의 두께를 갖는다.

[0012] 유리 코어(150)는 제1 표면(152) 및 대향하는 제2 표면(154)을 갖는다. 일 실시예에서, 제1 및 제2 표면(152, 154)은 대체적으로 서로에 평행하다. 유리 코어(150)의 외연(158)은 제1 표면(152)과 제2 표면(154) 사이에서 연장되며, 일부 실시예들에서는 유리 코어의 외연(158)이 대체적으로 기판의 외연(108)에 대응한다. 일 실시예에 따르면, 유리 코어(150)는 0.1mm 내지 0.8mm의 두께를 가질 수 있다. 일 실시예에서, 유리 코어(150)는 전적으로 (아래에 설명되는 것과 같이 도전체들(160)이 아닌) 유리로 구성된다. 다른 실시예에서, (비록 코어가 도전체들(160)을 위한 홀들을 포함하긴 하지만) 유리 코어(150)는 단 한 개의 고체 유리를 포함한다. 다른 실

시예들에서, 유리 코어(150)는 함께 결합된 복수 개의 유리 또는 유리 부분을 포함할 수 있다.

[0013] 복수의 도전체(160)가 유리 코어(150)를 관통하여 연장된다. 각각의 도전체(160)는 홀 또는 비아(165) 내에 배치되며, 각각의 도전체(160)는 제1 표면(152)으로부터 제2 표면(154)까지 연장될 수 있다. 그러나, 다른 실시 예들에서, 도전체들 중 하나 이상은 코어의 두께를 부분적으로만 관통하여 연장된다. 일 실시예에 따르면, 도전체(160)는 전기 전도성 물질로 채워진 유리 코어(150)를 관통하여 형성된 홀 또는 비아(165)를 포함한다. 다른 실시예에서, 도전체(160)는 캐스팅 공정 동안 유리 코어 내에 형성된 홀(165)을 포함하며, 이 홀은 전기 전도성 물질로 채워진다. 다른 실시예에서, 도전체(160)는 유리 코어(150) 내에 삽입된 금속 와이어를 포함한다.

[0014] 도전체들(160)은 금속, 합성 재료 및 전기 전도성 중합체를 포함하는 임의의 적절한 전기 전도성 물질을 포함할 수 있다. 적절한 금속들은 구리, 주석, 은, 금, 니켈, 알루미늄 및 텉스텐, 및 이러한 금속들 및/또는 다른 금속들의 합금들을 포함한다. 홀 또는 비아(165)를 형성하기 위해 이용될 수 있는 공정들은 예를 들어 임프린팅, 샌드 블라스팅, 캐스팅, 레이저 드릴링 및 에칭을 포함한다. 전기 전도성 물질은 예를 들어 스크린 인쇄 기법, 도금 기법(전기 도금 또는 무전해 도금), CVD(chemical vapor deposition) 및 PVD(physical vapor deposition)와 같은 임의의 적절한 공정에 의해 도전체들(160)을 형성하기 위해 홀들 또는 비아들(165) 내에 퇴적될 수 있다.

[0015] 기판(100)의 제1 면(102) 상에는 제1 세트의 전기 전도성 단자들(120)이 배치된다(도 1a 참조). 일 실시예에 따르면, 제1 세트의 단자들(120)은 집적 회로(IC) 다이 상에 배치된 대응하는 단자 어레이와 짹을 이루는 패턴으로 배열된다. IC 다이는 도 1a-1b에 도시되어 있지 않지만, 다이 영역(110)은 도 1a에 도시되어 있고, 단자들(120)은 이 다이 영역(때로는 다이 음영 영역이라고 지칭됨) 내에 놓여진다. 단자들(120)은 각각 IC 다이의 단자와의 전기 접속을 형성할 수 있는 임의의 적절한 유형의 구조물을 각각 포함할 수 있다. 예를 들어, 단자(120)는 임의의 적절한 금속 또는 금속들의 조합(예를 들어 알루미늄, 구리, 니켈 등)으로 형성된 패드, 필러 또는 스터드 범프를 포함할 수 있고, 솔더 범프가 각각의 단자(120) 상에 (및/또는 IC 다이의 단자들 상에) 배치될 수 있다. 일 실시예에서, IC 다이는 플립칩 방식으로 기판(100) 상에 배치될 수 있고, 다이 상의 단자들은 솔더 리플로우 공정에 의해 기판(100) 상의 단자들(120)에 연결될 수 있다. 다른 실시예에 따르면, IC 다이는 접착제 층에 의해 기판(100)에 연결될 수 있으며, 다이 상의 단자들은 와이어본드 공정에 의해 기판 상의 대응하는 단자들에 전기 연결된다(본 실시예에서, 단자들(120)은 다이 영역(110)의 밖에 놓일 것이다).

[0016] 기판(100)의 제2 면(104) 상에는 제2 세트의 전기 전도성 단자들(125)이 배치된다(설명의 편의 및 명확성을 위해 도 1a에는 일부분만이 도시되어 있음). 일 실시예에 따르면, 제2 세트의 단자들(125)은 메인보드, 마더보드 또는 다른 회로 보드(도면들에는 도시되지 않음)와 같은 다음 레벨 컴포넌트 상에 배치된 대응하는 단자 어레이와 짹을 이루는 패턴으로 배열된다. 단자들(125)은 각각 다음 레벨 컴포넌트의 단자와 전기 접속을 형성할 수 있는 임의의 적절한 유형의 구조를 포함할 수 있다. 예로서, 단자(125)는 패드, 랜드, 솔더 범프 또는 다른 금속 범프, 또는 핀을 포함할 수 있다. 다음 레벨 컴포넌트는 LGA(Land Grid Array) 소켓 또는 PGA(Pin Grid Array) 소켓과 같이, 기판(100) 및 단자들(125)을 수용하기 위한 소켓(및 리텐션 기구)을 포함할 수 있다. 대안적으로, 단자들(125)은 솔더 리플로우 공정에 의해 다음 레벨 컴포넌트 상의 단자들에 연결될 수 있다.

[0017] 유리 코어(150)의 제1 표면(152) 상에는 제1 빌드업(build-up) 구조물(130)이 배치되고, 코어의 제2 표면(154)에는 제2 빌드업 구조물(140)이 배치된다. 제1 빌드업 구조물은 유전체 재료 및 금속의 하나 이상의 교대하는 층을 포함하고, 단자들(120)은 제1 빌드업 구조물(130) 상에 배치된다 (제1 기판 면(102)은 대체적으로 제1 빌드업 구조물(130)의 외측 표면에 대응함). 유리 코어(150) 내의 도전체들(160) 중 적어도 하나는 제1 빌드업 구조물(130)의 적어도 하나의 금속층에 전기 연결되고, 일 실시예에서 유리 코어(150)에 가장 가까운 제1 빌드업 구조물의 금속층은 적어도 하나의 도전체(160)와 연결된다. 마찬가지로, 제2 빌드업 구조물(140)은 유전체 재료 및 금속의 하나 이상의 교대하는 층을 포함하고, 단자들(125)은 제2 빌드업 구조물(140) 상에 배치된다 (제2 기판 면(104)은 대체적으로 제2 빌드업 구조물(140)의 외측 표면에 대응함). 유리 코어(150) 내의 도전체들(160) 중 적어도 하나는 제2 빌드업 구조물(140)의 적어도 하나의 금속층에 전기 연결되며, 일 실시예에서 유리 코어(150)에 가장 가까운 제2 빌드업 구조물의 금속층은 적어도 하나의 도전체(160)와 연결된다. 제1 및 제2 빌드업 구조물(130, 140)은 제1 세트의 단자들(120)과 제2 세트의 단자들(125) 사이에서 전력과 입력/출력(I/O) 신호들을 라우팅한다(그러므로, 기판(100) 상에 장착된 IC 다이와 다음 레벨 컴포넌트 사이의 시그널링 및 전력 전달을 용이하게 함). 빌드업 구조물들(130, 140)은 이하에 더 상세하게 설명된다.

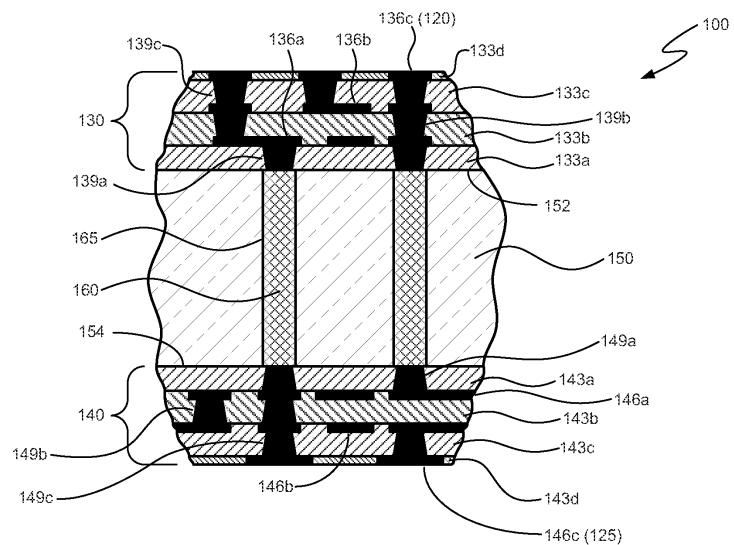

[0018] 도 1c를 참조하면, 유리 코어 기판(100)의 실시예가 더 상세하게 도시되어 있다. 앞에서 설명된 바와 같이, 기판은 각각 코어의 제1 표면(152)과 제2 표면(154) 사이에서 연장되는 도전체들(160)을 갖는 유리 코어(150)를

포함한다. 도전체들(160) 각각은 유리 코어(150)를 관통하여 연장되는 홀 또는 비아(165) 내에 배치될 수 있다. 제1 빌드업 구조물(130)은 코어(150)의 제1 면(152) 상에 배치되며, 제2 빌드업 구조물(140)은 코어의 대향하는 제2 면(154) 상에 배치된다.

[0019] 일 실시예에 따르면, 제1 빌드업 구조물(130)은 복수의 유전체 재료층(133a, 133b, 133c, 133d) 및 복수의 금속 층(136a, 136b, 136c)을 포함한다. 유전체층들(133a-d)은 임의의 적절한 유전체 재료(예를 들어 고분자 재료 등)을 포함할 수 있고, 임의의 적절한 기법에 의해(예를 들어 퇴적, 적층 등에 의해) 형성될 수 있다. 금속층들(136a-c)은 임의의 적절한 전기 전도성 금속(예를 들어 구리, 알루미늄, 은 등)을 포함할 수 있고, 임의의 적절한 기법(예를 들어 전기 도금 및 비전해 도금과 같은 도금 공정)에 의해 퇴적될 수 있다. 또한, 금속층들(136a-c)은 전력 및 I/O 신호들의 라우팅을 용이하게 하기 위해, 임의의 적절한 개수 및 구성의 트레이스, 전력 평면, 접지 평면 및 다른 도전체들을 형성하도록 각각 패턴화될 수 있다.

[0020] 유전체층들(133a-d) 중 하나는 임의의 2개의 인접하는 금속층(136a-c) 사이에 배치되고 (예를 들어 금속층들(136a 및 136b)은 유전체층(133b)에 의해 분리되는 등), 유전체층(133a)은 유리 코어(150)에 인접하여 놓여지고, 금속층(136a)을 코어로부터 분리한다. 일 실시예에 따르면, 유전체층(133a)은 유리 코어의 제1 표면(152)에 바로 인접하여 놓여진다. 금속으로 도금되거나 채워지는 비아들(139a, 139b, 139c)은 각각 유전체층들(133a, 133b, 133c)을 통해 연장되며, 인접하는 금속층들을 상호접속한다(예를 들어 비아들(139b)이 금속층들(136a 및 136b)을 상호접속하는 것 등). 또한, 유리 코어(150)에 가장 가까운 금속층(136a)은 유전체층(133a) 내에 배치된 비아들(139a)에 의해 도전체들(160) 중 하나 이상과 연결된다. 일 실시예에서, 유리 코어(150)의 제1 표면(152)은 빌드업 구조물(130)의 유전체 재료와의 접착(adhesion)을 증가시키기 위해 표면 처리 또는 코팅을 포함할 수 있다. 또한, 일부 실시예들에서, 최외측 유전체층(133d)은 레지스트층 및/또는 패시베이션 층을 포함할 수 있다. 또한, 일 실시예에 따르면, 단자들(120)은 최외측 금속층(136c)에 의해 형성되거나 그 위에 형성된다.

[0021] 일 실시예에서, 제2 빌드업 구조물(140)은 복수의 유전체 재료층(143a, 143b, 143c, 143d) 및 복수의 금속층(146a, 146b, 146c)을 포함한다. 유전체층들(143a-d)은 임의의 적절한 유전체 재료(예를 들어 고분자 재료 등)를 포함할 수 있고, 임의의 적절한 기법에 의해(예를 들어 퇴적, 적층 등에 의해) 형성될 수 있다. 금속층들(146a-c)은 임의의 적절한 전기 전도성 금속(예를 들어 구리, 알루미늄, 은 등)을 포함할 수 있고, 임의의 적절한 기법(예를 들어 전기 도금 및 비전해 도금과 같은 도금 공정)에 의해 퇴적될 수 있다. 또한, 금속층들(146a-c)은 전력 및 I/O 신호들의 라우팅을 용이하게 하기 위해, 임의의 적절한 개수 및 구성의 트레이스, 전력 평면, 접지 평면 및 다른 도전체들을 형성하도록 각각 패턴화될 수 있다.

[0022] 유전체층들(143a-d) 중 하나는 임의의 2개의 인접하는 금속층(146a-c) 사이에 배치되고 (예를 들어 금속층들(146a 및 146b)은 유전체층(143b)에 의해 분리되는 등), 유전체층(143a)은 유리 코어(150)에 인접하여 놓여지고, 금속층(146a)을 코어로부터 분리한다. 일 실시예에 따르면, 유전체층(143a)은 유리 코어의 제2 표면(154)에 바로 인접하여 놓여진다. 금속으로 도금되거나 채워지는 비아들(149a, 149b, 149c)은 각각 유전체층들(143a, 143b, 143c)을 통해 연장하며, 인접하는 금속층들을 상호접속한다(예를 들어, 비아들(149b)이 금속층들(146a 및 146b)을 상호접속하는 것 등). 또한, 유리 코어(150)에 가장 가까운 금속층(146a)은 유전체층(143a) 내에 배치된 비아들(149a)에 의해 도전체들(160) 중 하나 이상과 연결된다. 일 실시예에서, 유리 코어(150)의 제2 표면(154)은 빌드업 구조물(140)의 유전체 재료와의 접착을 증가시키기 위해 표면 처리 또는 코팅을 포함할 수 있다. 또한, 일부 실시예들에서, 최외측 유전체층(143d)은 레지스트층 및/또는 패시베이션 층을 포함할 수 있다. 또한, 일 실시예에서, 단자들(125)은 최외측 금속층(146c)에 의해 형성되거나 그 위에 형성된다.

[0023] 도 1c의 실시예(그리고, 도 1d 및 도 1e에 각각 도시된 실시예들)에서, 제1 및 제2 빌드업 구조물은 동일한 개수의 유전체 및 금속층을 포함하고, 또한 대체적으로 등가의 두께를 갖는다. 그러나, 개시된 실시예들은 그와 같이 한정되지 않으며, 다른 실시예들에서는 제1 및 제2 빌드업 구조물들이 상이한 두께를 및/또는 상이한 개수의 유전체 및 금속층을 가질 수 있다. 다른 실시예에 따르면, 빌드업 구조는 유리 코어(150)의 단 한 면 상에만 배치된다. 또한, 일부 실시예들에서, 제1 및 제2 빌드업 구조물들은 동일한 유전체 재료 및 금속으로 구성된다. 그러나, 다른 실시예들에서, 제1 및 제2 빌드업 구조물은 상이한 재료를 가질 수 있다.

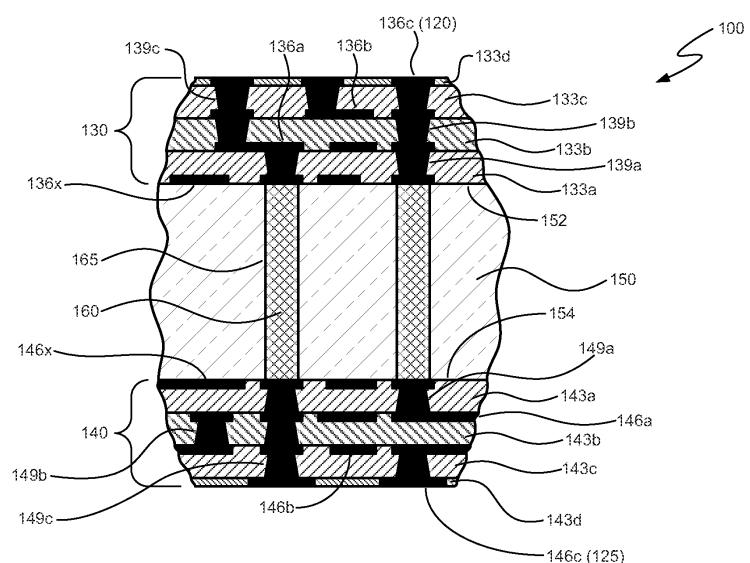

[0024] 도 1c의 실시예에서, 유전체층들(133a 및 143a)은 유리 코어(150)에 인접하게 배치되고, 코어에 가장 가까운 금속층들(즉, 금속층들(136a 및 146a))은 이러한 유전체층들에 의해 코어로부터 분리된다. 대안적인 실시예에서는, 도 1d에 도시된 바와 같이 금속층이 유리 코어(150)에 인접하게 놓여질 수 있다. 유리 코어(150)의 한 면 또는 두 면에 인접한 금속층을 포함시키는 것은 때때로 "코어층 라우팅"이라고 지칭된다.

[0025] 도 1d를 참조하면, 기판(100)의 실시예는 대체적으로 도 1c에 도시된 것과 유사하다(그리고, 유사한 특징들은 동일한 참조 번호에 의해 식별됨). 그러나, 도 1d의 실시예에서, 제1 빌드업 구조물(130)은 유리 코어(150)에 인접한 금속층(136x)을 포함하고, 일 실시예에 따르면 금속층(136x)은 유리 코어의 제1 표면(152)에 바로 인접한다. 유전체층(133a)은 금속층(136x)(및 유리 코어의 노출된 부분들) 위에 가로놓이고, 이 금속층(136x)은 이제 코어에 가장 가까운 금속층이 되며, 도전체들(160) 중 적어도 하나가 금속층(136x)과 연결된다. 또한, 다른 실시예에서, 유리 코어(150)의 제1 표면(152)은 금속층(136x)(및 아마도 유전체층(133a)의 부분들)과의 접착을 증가시키기 위한 표면 처리 또는 코팅을 포함할 수 있다.

[0026] 제1 빌드업 구조물(130)과 마찬가지로, 도 1d의 제2 빌드업 구조물(140)은 유리 코어(150)에 인접한 금속층(146x)을 포함하고, 일 실시예에 따르면 금속층(146x)은 유리 코어의 제2 표면(154)에 바로 인접한다. 유전체층(143a)은 금속층(146x)(및 유리 코어의 노출된 부분들) 위에 가로놓이고, 이 금속층(146x)은 이제 코어에 가장 가까운 금속층이 되며, 도전체들(160) 중 적어도 하나가 금속층(146x)과 연결된다. 또한, 다른 실시예에서, 유리 코어(150)의 제2 표면(154)은 금속층(146x)(및 아마도 유전체층(143a)의 부분들)과의 접착을 증가시키기 위한 표면 처리 또는 코팅을 포함할 수 있다. 일부 실시예들에서, 유리 코어의 표면들(152, 154) 중 단 하나만이 인접 금속층을 갖는다 (예를 들어, 제1 및 제2 빌드업 구조물(130, 140) 내의 금속층들(136x, 146x) 중 어느 하나가 각각 생략될 수 있음).

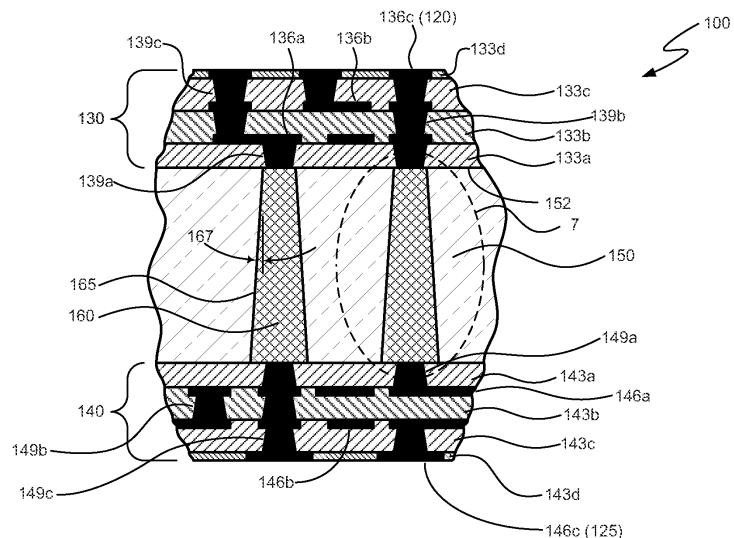

[0027] 이제 도 1e를 참조하면, 유리 코어 기판(100)의 다른 실시예가 도시되어 있다. 도 1e에 도시된 기판(100)의 실시예는 도 1c에 도시된 것과 대체적으로 유사하다(그리고, 유사한 특징들은 동일한 참조 번호들에 의해 식별됨). 그러나, 도 1e의 실시예에서, 각각의 도전체(160)가 배치되는 홀 또는 비아(165)는 테이퍼져 있는 벽을 갖는다. 일 실시예에서, 홀 또는 비아(165)의 테이퍼져 있는 벽은 홀의 중심선에 대하여 0도 내지 30도의 각도(167)를 갖는다. 홀(165)의 테이퍼져 있는 벽은 유리 코어(150)를 관통하여 홀을 형성하기 위해 이용된 공정의 결과일 수 있다. 위에서 언급된 바와 같이, 홀 또는 비아(165)를 형성하기 위해 이용될 수 있는 공정들은 예를 들어 임프린팅, 샌드 블라스팅, 캐스팅, 레이저 드릴링 및 에칭을 포함한다. 처리 조건들에 따라, 위에서 언급된 기법들 중 임의의 것이 테이퍼져 있는 벽을 갖는 홀(165)을 형성할 수 있다.

[0028] 다음으로 도 1f를 보면, 유리 코어 기판(100)의 다른 실시예가 도시되어 있다. 도 1e에서 참조 번호 7에 의해 개괄적으로 표기된 기판(100)의 부분이 도 1f에서 확대도로 도시되어 있다(유사한 특징들은 동일한 참조 번호에 의해 식별됨). 도 1f의 실시예에서, 습윤층(wetting layer)(또는 접착층)(170)이 홀(160)의 벽(165) 위에 배치되어 있다. 습윤층(170)의 기능은 전기 전도성 물질(160)과 코어(150)의 유리 재료 사이의 접착을 증가시키는 것이며, 습윤층(170)은 이를 두 재료 사이의 접착을 증가시킬 수 있는 임의의 적절한 재료를 포함할 수 있다. 일 실시예에서, 습윤층(170)은 예를 들어 티타늄, 크롬, 니켈 및 바나듐과 같은 금속과, 이를 및 다른 금속들의 합금들도 포함한다. 또한, 습윤층(170)은 도금 기법(전기 도금 또는 비전해 도금), CVD 또는 PVD와 같은 임의의 적절한 공정을 이용하여 퇴적 또는 형성될 수 있다.

[0029] 도 2에는 유리 코어 기판(100)을 포함하는 어셈블리(200)의 실시예가 도시되어 있다. 도 2를 참조하면, 어셈블리(200)는 유리 코어(150)와, 제1 면(102) 및 대향하는 제2 면(104)을 갖는 기판(100)을 포함한다. 기판의 제1 면(102) 상에는 접적 회로(IC) 다이(102)가 배치되어 있다. IC 다이(210)는 복수의 상호접속부(220)에 의해 기판(100)과 전기적으로 (그리고 기계적으로) 연결된다. 기판의 제2 면(104) 상의 단자들(125)(도 1a 참조)(예를 들어 랜드, 핀, 솔더 범프 등)은 마더보드, 메인보드 또는 다른 회로 보드와 같은 다음 레벨 컴포넌트와의 전기 접속을 형성하기 위해 이용될 수 있다. 제1 표면(232) 및 다이의 뒷면(215)을 향하는 대향하는 제2 표면(234)을 갖는 열 확산기 또는 덮개(230)는 다이(210) 위에 배치되고, 열 계면 재료의 층(240)에 의해 다이의 뒷면(215)에 열적으로 (그리고 아마도 기계적으로) 연결된다. 열 확산기(230)를 유리 코어 기판(100)의 제1 표면(102)에 고정시키기 위해 접착제 또는 밀폐제(290)가 이용될 수 있다. 도 2에는 도시되어 있지 않지만, 다른 실시예에서는 히트 싱크(또는 다른 냉각 장치)가 열 확산기(230)에 열적으로 연결될 수 있고, 열 계면 재료의 다른 층이 열 확산기의 제1 표면(232)과 히트 싱크(또는 다른 장치) 사이에 배치될 수 있다.

[0030] IC 다이(210)는 임의의 유형의 반도체 장치를 포함할 수 있다. 일 실시예에서, IC 다이(210)는 처리 시스템 또는 장치를 포함한다. 예를 들어, IC 다이(210)는 마이크로프로세서 또는 그래픽 프로세서를 포함할 수 있다. IC 다이(210)는 임의의 개수의 명령어 포맷을 갖는 임의의 개수의 프로세서 아키텍처로부터의 명령어들을 수행할 수 있다. 일 실시예에서, 명령어는 인텔사에 의해 이용되는 것과 같은 "x86" 명령어이다. 그러나, 다른 실시예들에서는 프로세서가 다른 아키텍처들 또는 다른 프로세서 설계자들로부터의 명령어들을 수행할 수 있다. 다른 실시예에서, IC 다이(210)는 메모리 장치를 포함한다. 추가의 실시예에 따르면, IC 다이(210)는 SoC(system-on-chip)를 포함한다. 또 다른 실시예에서, IC 다이(210)는 디지털 회로망, 아날로그 회로망, 또는

아날로그 및 디지털 회로망 둘 다의 조합을 포함할 수 있다.

[0031]

상호접속부들(220)은 기판의 제1 표면(102) 상의 단자들(120)(도 1a 참조)을 예를 들어 솔더 리플로우 공정에 의해 IC 다이(210) 상의 단자들과 연결함으로써 형성된다. 앞에서 설명된 바와 같이, 기판 단자들(120)은 각각 임의의 적절한 금속 또는 금속들의 조합(예를 들어 구리, 니켈, 알루미늄 등)으로 형성된 패드, 필러 또는 스터드 범프를 포함할 수 있으며, 다이 단자들은 또한 임의의 적절한 금속 또는 금속들의 조합으로 형성된 패드, 필러 또는 스터드 범프를 포함할 수 있다. (예를 들어 볼들 또는 범프들의 형태로 된) 솔더는 기판 및/또는 다이 단자들 상에 배치될 수 있으며, 이러한 단자들은 다음으로 솔더 리플로우 공정을 이용하여 결합될 수 있다. 앞에서 언급된 상호접속부들은 기판(100)과 IC 다이(210) 사이에 형성될 수 있는 상호접속부들의 유형의 일례에 지나지 않으며, 또한 임의의 다른 적절한 유형의 상호접속부가 이용될 수 있음을 이해하여야 한다. 또한, 언더필 재료의 층(도 2에는 도시되지 않음)이 상호접속부들(220) 주위, 및 IC 다이(210)와 기판의 제1 면(102) 사이에 배치될 수 있다.

[0032]

열 확산기(230)는 임의의 적절한 열 전도성 물질로 구성될 수 있고, 임의의 적절한 형상 또는 구조를 가질 수 있다. 일 실시예에 따르면, 열 확산기(230)는 기판의 제1 면(102)을 향해 연장하는 측벽(또는 벽들)(237)을 갖는 덮개를 포함하며, 이 벽(또는 벽들)은 접착제(290)에 의해 기판 표면(102)에 고정된다. 위에서 설명된 덮개는 때때로 IHS(integrated heat spreader)라고 지칭된다. 열 확산기(230)를 구성하기 위해 이용될 수 있는 재료들은 금속(예를 들어 구리 및 그것의 합금), 열 전도성 복합 재료, 및 열 전도성 중합체를 포함한다.

[0033]

도 2에 도시된 실시예에서, 어셈블리(200)는 단일 IC 다이(210)를 포함한다. 그러나, 다른 실시예들에서는 어셈블리(200)가 멀티칩 패키지를 포함할 수 있다. 예를 들어, 하나 이상의 다른 집적 회로 다이(예를 들어 메모리 장치, 전압 조정기 등)가 기판(100) 상에 배치될 수 있다. 또한, 커패시터 및 인덕터들과 같은 수동 장치들이 유리 코어 기판(100) 상에 배치될 수 있거나, 대안적으로는 기판의 빌드업 구조물들(130, 140)에 통합될 수 있다. 예로서, 어레이 커패시터 또는 박막 커패시터가 기판(100)의 빌드업 구조물들(130, 140)에 통합될 수 있다. 다른 실시예에서, 안테나 또는 RF 설드와 같은 무선 컴포넌트가 유리 코어 기판(100) 상에 배치되거나, 이 기판의 빌드업 구조물들(130, 140) 내에 통합될 수 있다. IC 다이이든, 수동 장치이든 다른 컴포넌트이든 간에, 이러한 추가의 장치들은 유리 코어 기판(100)의 어느 한 면(102, 104)에 배치될 수 있다.

[0034]

어셈블리(200)는 임의의 유형의 컴퓨팅 장치의 일부를 형성할 수 있다. 일 실시예에 따르면, 어셈블리(200)는 서버 또는 데스크탑 컴퓨터의 일부를 형성할 수 있다. 다른 실시예에서, 어셈블리(200)는 랩톱 컴퓨터 또는 유사한 모바일 컴퓨팅 장치(예를 들어 넷탑 컴퓨터)의 일부를 형성한다. 추가의 실시예에서, 어셈블리(200)는 셀폰, 스마트폰 또는 MID(mobile internet device)와 같은 핸드헬드형 컴퓨팅 장치의 일부를 포함한다. 또 다른 실시예에서, 어셈블리(200)는 내장된 컴퓨팅 장치의 일부를 형성한다.

[0035]

도 3에는 유리 코어 기판을 제조하는 다양한 방법들의 실시예들이 도시되어 있다. 이러한 다양한 방법들 및 그들의 실시예들이 도 4a-4f, 도 5a-5c, 도 6a-6c, 도 7a-7c, 도 8a-8c, 도 9a-9c, 도 10a-10c, 도 11a-11d, 도 12, 도 13 및 도 14에 더 도시되어 있고, 이하의 본문에서 요청되는 대로 이들 도면들이 참조되어야 한다.

[0036]

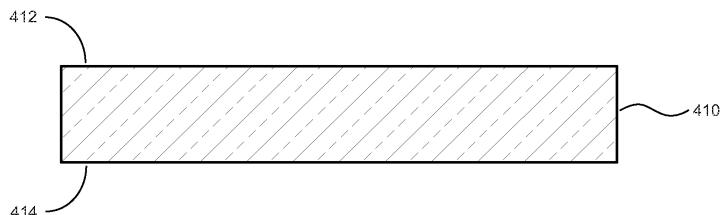

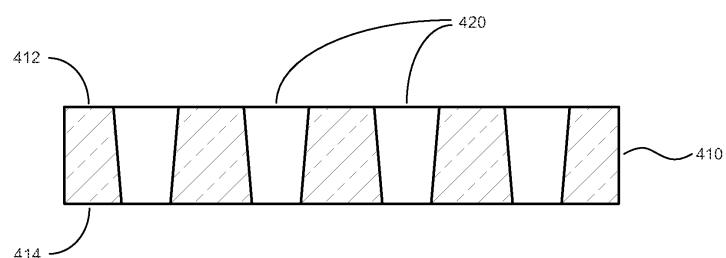

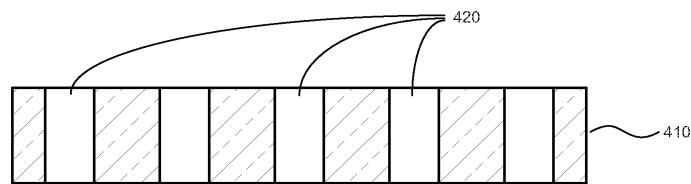

도 3의 블록(305)을 참조하면, 일 실시예에서 유리판이 제공된다. 이것은 유리판(410)이 도시된 도 4a에 도시되어 있다. 유리판은 제1 표면(412), 및 제1 표면(412)과 대체로 평행한 대향하는 제2 표면(414)을 포함한다. 유리판(410)은 응용 및/또는 소기의 특성에 따라 임의의 적절한 유형의 유리를 포함하고 임의의 적절한 두께를 가질 수 있다(위의 논의를 참조). 일 실시예에 따르면, 유리판(410)은 단일 기판의 형성을 가능하게 하는 크기 및 구성을 갖는다. 추가의 실시예에서, 유리판(410)은 둘 이상의 기판의 형성을 가능하게 하는 크기 및 구성을 갖는다(예를 들어 유리판(410)은 그로부터 둘 이상의 기판이 절단될 패널을 포함함). 판(410)은 이러한 판을 포함하는 유리 재료에 관련된 연화 온도를 가질 것이다.

[0037]

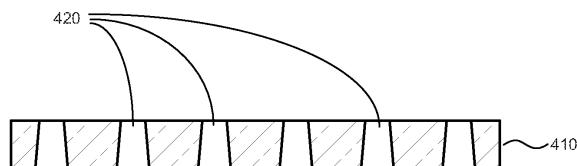

도 3의 블록(310)에 제시되어 있는 바와 같이, 유리판 내에 홀들 또는 비아들이 형성된다. 이것은 도 4b에 더 도시되어 있는데, 거기에서 홀들(420)이 유리판(410) 내에 형성되어 있고, 각각의 홀은 제1 표면(412)으로부터 판의 제2 표면(414)으로 연장된다. 다른 실시예들에서, 홀들 또는 비아들(420) 중 하나 이상은 유리판(410)의 두께를 완전히 관통하여 연장되지 않을 수 있다. 홀들(420)을 형성하기 위해 다양한 방법들이 구현될 수 있다. 일 실시예에서, 홀들은 평면 임프린팅 기법에 의해 형성된다(도 5a-5c 참조). 다른 실시예에서, 홀들은 룰러 임프린팅 기법에 의해 형성된다(도 6a-6b 참조). 추가의 실시예에서, 홀들은 샌드 블라스팅(또는 파워 블라스팅 또는 입자 블라스팅) 기법에 의해 형성된다(도 7a-7c 참조). 홀들(420)을 형성하기 위한 이러한 실시예들 각각이 이제 더 상세하게 설명될 것이다. 그러나, 개시된 실시예들은 도 5a 내지 도 7c에서 설명된 홀 형성 기법으로 한정되지 않으며, 또한 유리판 내에 홀들을 형성하기 위해 다른 방법들(예를 들어 레이저 드릴링, 에칭

등)이 이용될 수 있음을 이해해야 한다.

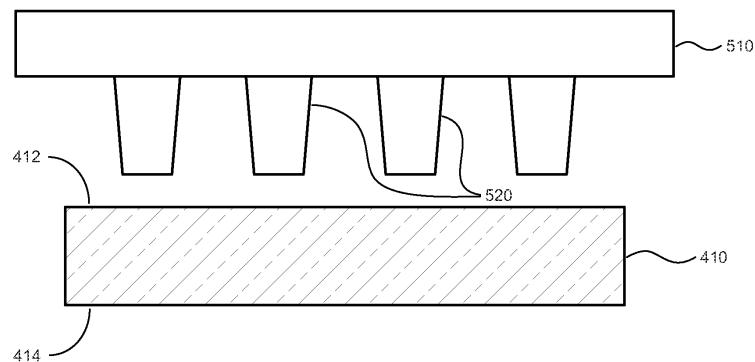

[0038] 도 5a를 보면, 임프린팅 도구(510)가 유리판(410)과 함께 도시되어 있다. 복수의 돌출부(520)가 임프린팅 도구(510)로부터 연장되며, 이러한 돌출부들 각각은 유리판(410) 내에 홀들 또는 비아들(420) 중 하나를 생성하도록 크기가 정해지고 배향되고 위치된다. 임프린팅 도구(510)는 판(410)의 유리 재료 내에 홀들을 형성할 수 있고 관련된 처리 온도를 견딜 수 있는 임의의 적절한 재료를 포함할 수 있다. 일 실시예에서, 임프린팅 도구(510) 및 돌출부들(520)의 표면들은 (예를 들어 도구와 유리가 들러붙는 것을 방지하기 위해) 유리 재료와의 접착을 최소화하기 위한 코팅 또는 표면 처리를 포함할 수 있다.

[0039] 도 5b를 참조하면, 유리판(410)은 연화 온도로 상승되고, 임프린팅 도구(510)의 돌출부들(520)이 유리판(410)에 밀어 넣어진다. 돌출부들(520)은 연화된 유리판(410) 내에 홀들(420)을 형성할 것이다. 유리판(410)을 연화 온도까지 가열하는 데에 요구되는 시간과, 유리판이 임프린팅 도구(510)와 체결되어 있으면서 그 온도로 유지되는 시간량은 예를 들어 판(410)을 구성하는 유리 재료, 최종 유리 코어의 소기의 특성, 및 이용되는 처리 장비에 의존한다.

[0040] 다음으로 도 5c를 참조하면, 임프린팅 도구(510)가 제거되었으며, 판(410)은 유리 재료를 고체 상태로 복귀시키도록 냉각되었다. 홀들(420)은 임프린팅 도구(510)의 돌출부들(520)에 대응하는 위치들에서 유리판(410) 내에 남아있게 된다. 일 실시예에서, 임프린팅 후에, 유리판(410) 내의 내적 응력을 완화하기 위해 어닐링 프로세스가 수행될 수 있다.

[0041] 이제 도 6a 및 도 6b를 보면, 롤러 임프린팅 도구(roller imprinting tool)(610)가 유리판(410)과 함께 도시되어 있다. 복수의 돌출부(620)가 롤러 임프린팅 도구(610)로부터 연장되고, 이러한 돌출부들 각각은 유리판(410) 내에 홀들 또는 비아들(420) 중 하나를 생성하도록 크기가 정해지고 배향되고 위치된다. 설명의 편의 및 명확성을 위해, 도 6a-6b에는 도구(610) 상의 돌출부들(620)의 일부만이 도시되었음에 유의해야 한다 (예를 들어, 돌출부들(620)은 도구(610)의 전체 둘레에서 연장될 수 있음). 롤러 임프린팅 도구(610)는 축(605)에 관하여 회전할 수 있고, 유리판(410)은 도구(610)에 대하여 이동할 수 있는 지지판 또는 캐리어(630) 상에 놓여질 수 있다(또는 대안적으로는 도구(610)가 지지판(630)에 대하여 이동할 수 있음). 임프린팅 도구(610)는 판(410)의 유리 재료 내에 홀들을 형성할 수 있고 관련된 처리 온도를 견딜 수 있는 임의의 적절한 재료를 포함할 수 있다. 일 실시예에서, 임프린팅 도구(610) 및 돌출부들(620)의 표면들은 유리 재료와의 접착을 최소화하기 위한 코팅 또는 표면 처리를 포함할 수 있다.

[0042] 유리판(410)은 연화 온도로 상승되고, 임프린팅 도구(610)의 돌출부들(620)은 유리판(410)과 체결된다. 롤러 임프린팅 도구(610)는 도구(610)를 축(605)에 관하여 회전시키면서(화살표(9)) 유리판을 도구(610)에 대하여 이동시킴으로써(화살표(8)) 유리판(410)과 체결된다. 돌출부들(620)은 연화된 유리판(410) 내에 홀들(420)을 형성할 것이다. 유리판(410)을 연화 온도까지 가열하는 데에 요구되는 시간과, 유리판이 임프린팅 도구(610)와 체결되는 한편 그 온도로 유지되는 시간량은 예를 들어 판(410)을 구성하는 유리 재료, 최종 유리 코어의 소기의 특성, 및 이용되는 처리 장비에 의존한다. 유리판(410)이 롤러 임프린팅 도구(610)와 체결된 후, 판(410)은 유리 재료를 고체 상태로 복귀시키도록 냉각된다. 홀들(420)은 임프린팅 도구(610) 상의 돌출부들(620)에 대응하는 위치들에서 유리판 내에 남아있다. 일 실시예에서, 임프린팅 후에, 유리판(410) 내에서의 내적 응력을 완화시키기 위해 어닐링 프로세스가 수행될 수 있다.

[0043] 도 7a를 참조하면, 레지스트 재료의 층(710)이 유리판(410)의 제1 표면(412) 상에 퇴적되었고, 이 레지스트층(710)은 개구들(720)을 형성하도록 패턴화되었다. 샌드 블라스팅 공정이 유리판(410)에 대하여 수행될 것이고, 레지스트층(710)은 샌드 블라스팅 공정을 견딜 수 있는 임의의 재료를 포함할 수 있다(예를 들어, 레지스트층이 샌드 블라스팅 공정에 실질적으로 영향을 받지 않거나, 대안적으로는 레지스트층이 샌드 블라스팅 공정에 의해 유리 재료가 제거되는 것보다 더 낮은 비율로 제거됨). 레지스트층 재료는 개구들(720)의 형성을 가능하게 하기 위해 패턴화 기법(예를 들어 포토리소그래피)으로 처리할 수 있는 것이어야 한다.

[0044] 도 7b를 참조하면, 패턴화된 레지스트층(710)을 갖는 유리판(410) 상에 샌드 블라스팅 공정(파우더 블라스팅 또는 입자 블라스팅이라고도 지칭될 수 있음)이 수행된다. 임의의 적절한 샌드 또는 입자(730)를 사용하여 임의의 적절한 샌드 블라스팅 기법 및 도구가 이용될 수 있다. 사용되는 입자는 이용되는 도구, 공정 특성, 및 판(410)을 구성하는 유리 재료에 따른 것이다. 이동하는 입자들(730)은 레지스트층(710) 내의 개구들(720)에 의해 노출되는 유리판의 부분들을 제거할 것이다. 이동하는 입자들(730)은 또한 레지스트 재료(720)도 공격할 수 있지만, 그 비율이 유리 기판(410)보다 낮아서, 개구들(720)의 위치에서만 홀들(420)을 형성하는 것을 허용한다. 샌드 블라스팅은 홀들(420)이 제1 표면(412)으로부터 제2 표면(414)으로 유리판(410)을 관통하여 연

장할 때까지 계속될 수 있다 (그러나 홀들(420) 중 하나 이상이 유리판(410)을 완전히 관통하여 연장하지는 않는 것도 개시된 실시예들의 범위 내에 듦다). 도 7c에 도시된 바와 같이 샌드 블라스팅이 완료되면 레지스트 재료(720)가 제거되고, 홀들(420)이 유리판(410) 내에 형성된다.

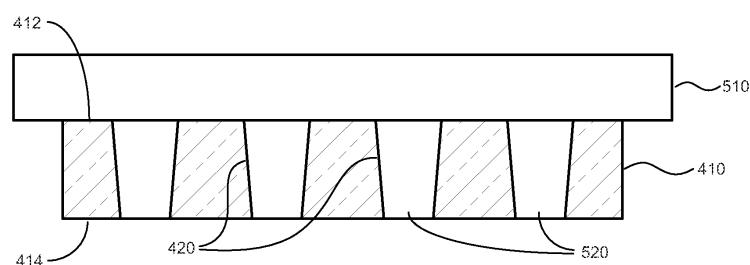

[0045] 이제 도 3, 특히 블록(315)을 보면, 일 실시예에서 습윤 또는 점착층이 비아들의 벽들 위에 형성될 수 있다. 이것은 습윤 재료의 층(430)이 홀들(420)의 벽들(425) 위는 물론, 유리 판(410)의 제1 표면(412) 위에도 배치되는 도 4c에 도시되어 있다. 도금 기법(전기 도금 또는 무전해 도금), CVD 또는 PVD와 같은 임의의 적절한 블랭킷 퇴적 공정이 습윤층(430)을 형성하는 데에 이용될 수 있다. 그 다음, 도 4d에 도시된 바와 같이 습윤 재료(430)가 비아들(420)의 벽들(425) 상에만 남아있도록 습윤 재료(430)는 유리판의 제1 표면(412)으로부터 제거된다. 과잉의 습윤 재료(430)는 예를 들어 그라인딩 공정 또는 화학기계적 연마 기법에 의해 표면(412)으로부터 제거될 수 있다.

[0046] 위에서 제시된 바와 같이, 습윤층(430)의 기능은 판(410)의 유리 재료와 홀들(420) 내에 퇴적될 전기 전도성 물질 사이의 점착을 증가시키는 것이고, 습윤층(430)은 이들 재료들 사이의 점착을 증가시킬 수 있는 임의의 적절한 재료를 포함할 수 있다. 일 실시예에서, 습윤층(430)은 예를 들어 티타늄, 크롬, 니켈 또는 바나듐과, 이러한 금속들 및/또는 다른 금속들의 합금들과 같은 금속을 포함한다. 그러나, 다른 실시예들에서, 습윤층은 유리판(410)의 비아들(420)의 표면들 상에 퇴적되지 않는다(즉, 블록(315)에 대응하는 단계는 생략될 수 있음).

[0047] 블록(320)에 제시된 바와 같이, 유리판 내의 홀들은 전기 전도성 물질로 채워져서 유리판을 관통하여 연장되는 도전체들을 형성한다. 이것은 도 4e에 도시되어 있는데, 여기에서 전기 전도성 물질(440)은 홀들(420) 내에 배치되었다. 도 4a-4f의 실시예에서는 도전 재료(440)가 습윤층(430) 상에 배치되지만, 위에서 언급된 바와 같이 다른 실시예들에서는 그러한 습윤층이 존재하지 않을 수 있다. 전기 전도성 물질(440)은 예를 들어 스크린 인쇄 기법, 도금 기법(전기 도금 또는 무전해 도금), CVD 또는 PVD와 같은 임의의 적절한 공정에 의해 비아들(420) 내에 퇴적될 수 있다. 유리판(410) 내의 도전체들을 형성하는 재료(440)는 금속, 복합 재료 및 전기 전도성 중합체를 포함하는 임의의 적절한 전기 전도성 물질을 포함할 수 있다. 적절한 금속들은 구리, 주석, 은, 금, 니켈, 알루미늄 및 텡스텐과, 이러한 금속들 및/또는 다른 금속들의 합금들을 포함한다. 일 실시예에서, 이러한 금속들 중 임의의 것은 페이스트 또는 입자 형태로 퇴적될 수 있고(예를 들어 스크린 인쇄 기법이 이용되는 경우), 페이스트 퇴적 후에는 소결 공정이 수행될 수 있다.

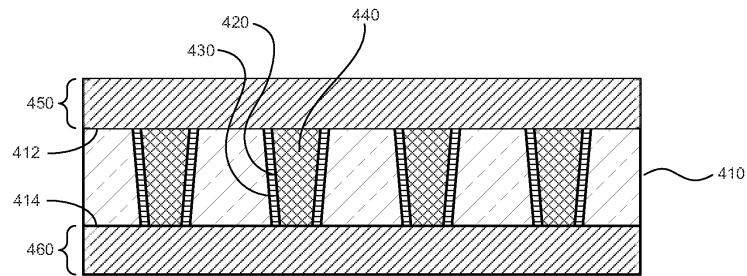

[0048] 블록(390)을 참조하면, 앞에서 설명된 바와 같이 빌드업 구조물들을 형성하기 위해 하나 이상의 빌드업 층이 유리판의 각 면에(또는 아마도 한 면에만) 퇴적된다. 이것은 제1 빌드업 구조물(450)이 유리판(410)의 제1 표면(412) 상에 형성되고 제2 빌드업 구조물(460)이 유리판의 제2 표면(414) 상에 형성된 도 4f에 도시되어 있다. 각각의 빌드업 구조물(450, 460)은 유전체 재료 및 금속의 임의의 적절한 개수의 교대하는 층을 포함할 수 있고(예를 들어 하나 이상), 그들은 임의의 적절한 기법들에 의해 형성될 수 있다. 그러한 빌드업 구조물들의 구조 및 형성은 도 1b 내지 도 1f와 상기의 수반하는 본문을 참조하여 더 상세하게 설명되어 있다. 일 실시예에서, 도전체들(440) 중 적어도 하나는 유리판(410)에 가장 가까운 제1 빌드업 구조물의 금속층에 전기 연결되고, 다른 실시예에서는 도전체들(440) 중 적어도 하나가 유리판에 가장 가까운 제2 빌드업 구조물의 금속층에 전기 연결된다.

[0049] 블록(395)을 참조하면, 전기 전도성 단자들이 유리판 상에 형성될 수 있다(도 4a-4f에는 단자들이 도시되지 않음). 제1 세트의 단자들은 제1 빌드업 구조물(450) 상에 형성될 수 있고, 제2 세트의 단자들은 제2 빌드업 구조물(460) 상에 형성될 수 있다. 그러한 단자들의 구조 및 형성은 도 1a 내지 도 1f와 상기의 수반하는 본문을 참조하여 더 상세하게 설명되어 있다.

[0050] 위에서 언급된 바와 같이, 일 실시예에서 유리판(410)은 둘 이상의 기판에 대응하는 구조물들 및 특징들을 포함한다. 본 실시예에서, 빌드업 구조물들(450, 460)을 갖는 유리판(410)은 (단자들의 형성 전에 또는 후에) 이러한 별개의 기판들로 싱크레이션될 수 있다.

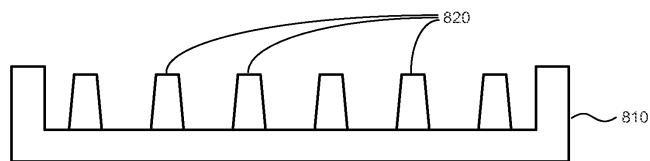

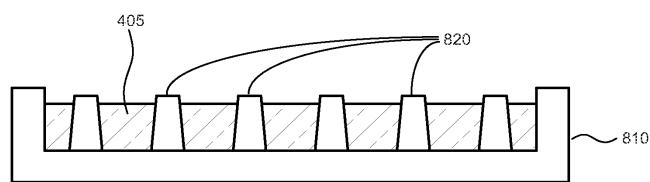

[0051] 이제 도 3의 블록(325)을 보면, 다른 실시예에서 홀들을 갖는 유리 코어는 캐스팅 공정에 의해 형성된다. 캐스팅 공정의 실시예는 도 8a-8c에 도시되어 있다. 도 8a를 참조하면, 캐스팅 몰드(810)는 복수의 돌출부(820)를 포함하고, 각각의 돌출부(820)는 몰딩된 유리판 내에 홀들 또는 비아들 중 하나를 생성하도록 크기가 정해지고 배향되고 위치된다. 캐스팅 몰드(810)는 용융된 유리에 관련된 처리 온도들을 견딜 수 있는 임의의 적절한 재료를 포함할 수 있다. 일 실시예에서, 캐스팅 몰드(810) 및 돌출부들(820)의 표면들은 (예를 들어 몰드와 유리가 들려붙는 것을 방지하기 위해) 유리 재료와의 접착을 최소화하기 위한 코팅 또는 표면 처리를 포함할 수 있다.

- [0052] 도 8b를 참조하면, 유리를 용융된 액체 상태로 변환하는 데에 충분한 시간 동안 용융 온도로 가열된 유리 재료(405)가 몰드(910) 내에 배치된다. 용융된 유리는 몰드(810) 내부 및 돌출부들(820) 주위로 흘러서, 돌출부들(820)에 대응하는 위치들에 훌들이 형성되게 될 것이다. 그 다음, 유리는 고체 상태로 냉각된 다음 몰드(820)로부터 제거되어, 도 8c에 도시된 바와 같이 훌들(420)을 갖는 캐스트 유리판(410)을 제공한다. 유리를 가열하고 냉각하는 데에 이용되는 시간 및 온도 프로파일은 이용되는 유리 재료는 물론, 최종 유리판의 소기의 특성에도 의존할 것이다. 일 실시예에서, 유리판(410) 내의 내적 응력을 완화하기 위해, 캐스팅 후에 어닐링 공정이 수행될 수 있다.

- [0053] 훌들(420)을 갖는 유리판(410)의 캐스팅 후에, 유리 코어 기판은 블록들(315, 320, 390 및 395)에 대하여 위에서 설명된 바와 같이 제조될 수 있다. 역시, 블록(315)에 도시된 것과 같은 습윤층은 일부 실시예들에서 생략될 수 있다.

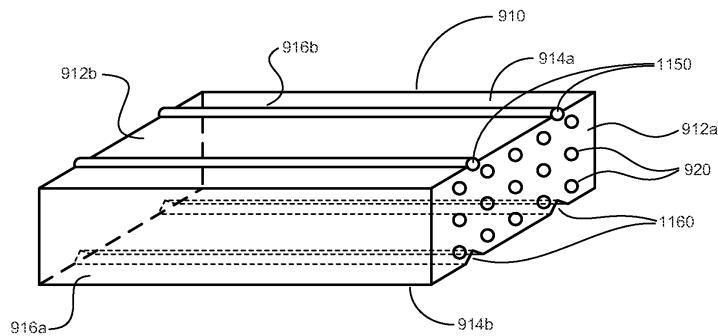

- [0054] 도 3의 블록(330)을 참조하면, 또 다른 실시예에서 유리 코어는 내장된 도전성 와이어들을 갖는 유리 바디를 제공함으로써 형성된다. 이것은 내장된 와이어들(920)을 갖는 유리 바디(910)를 도시하는 도 9a 및 도 9b에 더 도시된다. 와이어들(920)은 훌들(930) 내에 배치되는데, 여기에서 훌들(930)은 유리 바디(910) 내에 와이어들(920)을 내장하는 공정 동안 형성될 수 있다. 와이어들(920)은 임의의 적절한 전기 전도성 물질(예를 들어 구리, 알루미늄, 니켈과, 이러한 금속들 및/또는 다른 금속들의 합금들)을 포함할 수 있다. 유리 바디(910)는 임의의 적절한 유리 재료를 포함할 수 있고, 임의의 적절한 공정 또는 공정들의 조합을 이용하여 형성될 수 있다. 일 실시예에 따르면, 와이어들(920)은 유리 바디(910)가 형성되는 동일 공정 동안 내장된다. 예를 들어, (훌들(930) 내에) 내장된 와이어들(920)을 갖는 유리 바디(910)는 압출 공정을 이용하여 형성될 수 있다. 내장된 와이어들(920)을 갖는 유리 바디(910)가 유리 코어 제조에 이용되는 일 실시예에서, 비아 형성 및 금속 충전 공정은 생략될 수 있다.

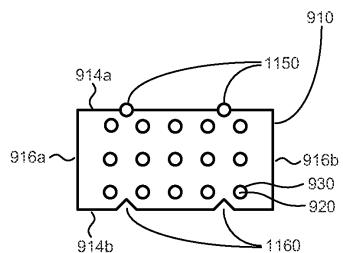

- [0055] 일 실시예에서, 유리 바디(910)는 대체적으로 직사각형인 평행 육면체 형상을 갖는다. 유리 바디는 표면(912a) 및 표면(912a)에 대체적으로 평행한 대향하는 표면(912b), 표면(914a) 및 표면(914a)에 대체적으로 평행한 대향하는 표면(914b), 및 표면(916a) 및 표면(916a)에 대체적으로 평행한 대향하는 표면(916b)을 가질 수 있다. 와이어들(920)(및 훌들(930))은 표면(912a)으로부터 유리 바디(910)를 관통하여 대향하는 표면(912b)으로 연장되고, 와이어들은 표면들(914a-b 및 916a-b)에 대체적으로 평행하다. 단면이 대체적으로 원형인 것으로 도시되어 있지만, 와이어들(920)은 임의의 다른 적절한 형상(예를 들어 타원, 정사각형, 육각형 등)을 가질 수 있다. 또한, 측면으로부터 볼 때(도 9b 참조), 유리 바디(910)는 직사각형 단면을 갖지만, 개시된 실시예들은 직사각형 또는 정사각형 단면으로 한정되지 않음을 이해해야 한다(예를 들어 유리 바디(910)는 원형 또는 타원형 단면 등을 가질 수 있음).

- [0056] 블록(335)을 참조하면, 하나 이상의 조각이 유리 바디로부터 절단된다. 이것은 조각(940)을 절단하기 위해 절단 도구 및/또는 공정(950)이 유리 바디(910)에 적용되는 도 9c에 도시되어 있다. 조각(940)은 제1 면(942), 및 제1 면(942)에 대체로 평행한 대향하는 제2 면(944)을 갖는다. 또한, 내장된 와이어들(920)의 일부분들이 조각(940) 내에 남아있고, 제1 면(942)으로부터 제2 면(944)으로 연장된다(명확함을 위하여, 조각(940)의 두께를 관통하는 와이어들(920)의 연장에 관련된 은선들(hidden lines)은 도 9c의 와이어들의 일부분에 대해서만 도시됨). 유리 바디(910)로부터 조각(940)을 절단하기 위해, 레이저 커팅 또는 기계적 소잉과 같은 임의의 적절한 절단 도구 또는 방법이 이용될 수 있다. 일 실시예에서, 유리 조각(410) 내의 내적 응력을 완화하기 위해 절단 후에 어닐링 공정이 수행될 수 있다.

- [0057] 내장된 와이어 부분들(920)을 갖는 조각(940)은 기판을 위한 유리 코어를 구성하기 위해 이용될 수 있으며, 와이어 부분들(920)은 유리 코어의 두께를 관통하는 도전체들을 제공한다. 도전체들로서 내장된 와이어들을 갖는 구조를 이용하면, 비아 형성(예를 들어 블록(310) 참조) 및 비아 금속 충전(예를 들어 블록(320 및 315) 참조)의 공정들이 제거된다. 일 실시예에서, 도 3의 블록(340)에 제시된 바와 같이, 단일 조각(940)이 기판을 위한 유리 코어로서 이용될 수 있다. 하나 이상의 빌드업 층이 코어(940)의 제1 및 제2 면(942, 944) 상에 (또는 아마도 코어의 단 한 면에만) 형성될 수 있고, 단자들도 빌드업 구조물들 상에 형성될 수 있다(블록(390 및 395)과 상기의 수반하는 본문을 참조).

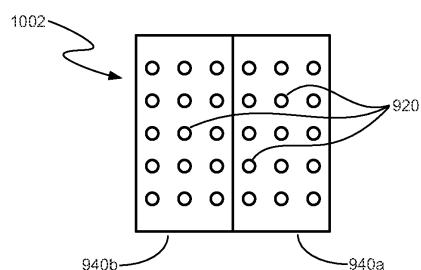

- [0058] 다른 실시예에서, 블록(345)에 제시된 바와 같이 유리 바디로부터 절단된 둘 이상의 조각이 함께 결합되어 유리 코어를 형성할 수 있다. 이것은 유리 바디(910)로부터 절단된 2개의 조각(940a 및 940b)을 보여주는 도 10a 및 도 10b에 더 도시되어 있는데, 각각의 조각은 그들 각각의 두께를 관통하여 연장하는 내장된 와이어들(920)을 갖는다(앞에서와 같이 명확성을 위하여, 와이어들(920)에 관련된 은선들은 와이어들의 일부분에 대해서만 도시

됨). 2개의 유리 조각(940a, 940b)은 각각 조각들(940a, 940b)의 2개의 마주보는 예지(914a, 914b)를 따라 함께 결합되서 도전체들(920)을 갖는 유리 코어(1002)를 형성한다. 2개의 조각(940a, 940b)을 함께 결합하거나 융합하기 위해 임의의 적절한 공정이 이용될 수 있다. 예를 들어, 조각들(940a-b)은 상승된 온도(예를 들어 연화 온도 이상) 및/또는 2개의 유리 단편을 함께 융합하기 위한 압력 하에서 결합될 수 있다. 대안적으로 조각들(940a-b)은 접착제를 이용하여 결합될 수 있다.

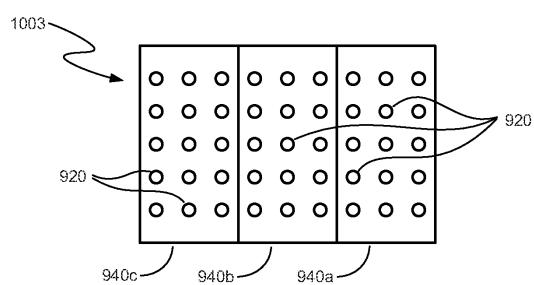

[0059] 도 10a 및 도 10b에서, 유리 바디(910)로부터 절단된 2개의 조각(940a-b)이 함께 결합되서 유리 코어를 생성한다. 그러나, 임의의 소기의 크기를 갖는 유리 코어를 생성하기 위해 임의의 적절한 개수의 조각이 결합될 수 있음을 이해해야 한다. 예로서 도 10c에 도시된 바와 같이, 3개의 조각(940c, 940d, 940e)이 함께 결합되서 유리 코어(1003)를 형성할 수 있다. 내장된 와이어들(920)은 유리 코어(1003)의 두께를 관통하여 연장된다.

[0060] 결합되는 유리 조각들의 개수에 상관없이, 조각들이 함께 융합되어 유리 코어(1002 또는 1003)로 된 후, 기판 제조 공정은 앞에서 설명된 바와 같이 계속될 수 있다. 하나 이상의 빌드업 층이 코어(1002 또는 1003)의 대향하는 면들에 (또는 아마도 그것의 한 면에만) 형성될 수 있고, 단자들도 빌드업 구조물들 상에 형성될 수 있다 (블록(390 및 395)과 상기의 수반하는 본문 참조).

[0061] 블록(350)을 참조하면, 다른 실시예에서 정렬 요소들(alignment elements)이 제공된다. 이것은 짹을 이루는 정렬 요소들(1150, 1160)이 유리 바디(910) 상에 배치된 도 11a 및 도 11b에 도시되어 있다(도 9a-9c와 도 11a-11d 사이의 유사한 특징들은 도 11a-11d에서 동일한 번호 지정을 유지함). 코어를 형성하기 위해 둘 이상의 유리 조각이 결합되고 있는 경우에서, 정렬 요소들(1150, 1160)는 결합하는 공정 동안 조각들을 서로에 대해 정렬하고 배향하기 위해 이용될 수 있다. 짹을 이루는 정렬 요소들은 하나의 유리 조각을 다른 유리 조각에 대해 정렬 및/또는 배향할 수 있는 임의의 구조들 또는 특징들을 포함할 수 있으며, 임의의 적절한 개수의 짹을 이루는 위치 조정 특징 형상들이 유리 바디(910) 상에 (따라서 유리 바디로부터 절단된 임의의 조각 상에) 배치될 수 있다. 도시된 실시예에서는 유리 바디(910)의 표면(914b)에 부분적으로 내장된 (또는 거기에 다르게 부착된) 와이어를 각각 포함하는 2개의 정렬 요소(1150)가 존재한다. 또한, 2개의 정렬 요소(1160)가 존재하며, 이들은 각각 유리 바디의 대향하는 표면(914a) 내에 형성된 노치를 포함한다. 그러나, 역시 임의의 적절한 개수의 짹을 이루는 정렬 요소(예를 들어 셋 이상의 짹을 이루는 쌍들 등)가 존재할 수 있다.

[0062] 정렬 요소들(1150, 1160)은 임의의 적절한 기법을 이용하여 유리 바디(910) 상에 형성되거나 배치될 수 있다. 일 실시예에 따르면, 정렬 요소들(1150)은 와이어들(920)이 내장되는 동일 공정 동안 유리 바디(910) 상에 배치되고, 추가의 실시예에서는 정렬 요소들(1160)이 또한 유리 바디(910)를 만드는 동일 공정 동안 형성된다 (예를 들어 와이어들(920 및 1150)은 노치들(1160)의 형성을 또한 야기하는 압출 공정 동안 유리 바디(910) 상에 퇴적될 수 있음). 그러나, 다른 실시예들에서, 정렬 요소들(1150 또는 1160) 중 어느 하나는 별개의 공정들에 의해 유리 바디(910) 상에 배치될 수 있다 (예를 들어 노치들(1160)은 압출 이후에 그라인딩 또는 절단 공정에 의해 형성될 수 있으며, 와이어들(1150)은 접착제를 이용하여 유리 바디(910) 상에 배치될 수 있는 등). 또한, 정렬 요소들은 임의의 후속 처리 온도들을 견딜 수 있는 임의의 적절한 재료를 포함할 수 있다. 도시된 실시예에서, 와이어들(1150)은 텅스텐, 몰리브덴 또는 니켈과 같은 금속, 및 이러한 금속들 및/또는 다른 금속들의 합금들도 포함할 수 있다. 일 실시예에 따르면, 와이어들(1150)은 내장된 와이어들(920)과 동일한 금속을 포함한다. 다른 실시예에 따르면, 와이어들(1150)은 바디(910)의 유리 재료와 거의 동일한 CTE를 갖는 금속을 포함한다.

[0063] 그 다음, 정렬 요소들(1150, 1160)을 갖는 유리 바디(910)는 앞에서 설명된 바와 같이 조각들로 절단된다(블록(335) 참조). 그 다음, 이러한 조각들 중 둘 이상이 결합되서 기판을 위한 유리 코어를 형성할 수 있다(블록(345) 참조). 예를 들어 도 11c에 도시된 바와 같이, 2개의 조각(940a 및 940b)이 결합되서 유리 코어(1102)를 형성하였다. 유리 조각들(940a, 940b)을 결합하는 동안, 정렬 요소들(1150, 1160)이 체결되어 이를 두 개의 단편을 서로에 대하여 정렬한다. 추가의 예로서, 도 11d에 도시된 바와 같이 3개의 부분(940c, 940d 및 940e)이 결합되서 유리 코어(1103)를 형성하였다. 역시, 3개의 부분(940c-e)의 짹을 이루는 정렬 요소들(1150, 1160)이 체결되고, 이를 3개의 단편을 서로에 대해 정렬한다.

[0064] 결합되는 유리 조각들의 개수에 무관하게, 조각들이 함께 융합되어 유리 코어(1102 또는 1103)로 된 후, 기판 제조 공정은 앞에서 설명된 바와 같이 계속될 수 있다. 하나 이상의 빌드업 층이 코어(1102 또는 1103)의 대향하는 면들에 (또는 그것의 한 면에만) 형성될 수 있고, 단자들도 빌드업 구조물들 상에 형성될 수 있다(블록(390 및 395)과 상기의 수반하는 본문을 참조).

[0065] 도 11a 내지 도 11d의 실시예들에서, 위치 조정 와이어들(1150)은 도전체들(920)의 어레이 내에 배치되었다. 일 실시예에 따르면, 위치 조정 와이어들(1150)은 유리 코어를 관통하는 도전체들로서 이용될 수 있다(예를 들

어, 위치 조정 와이어들(1150)이 도전체들(920)과 유사한 기능을 제공할 수 있음). 그러나, 다른 실시예들에서, 정렬 요소들은 도전체들의 어레이 외부에 위치될 수 있으며, 또 다른 실시예에서는 완전히 결합된 후에 정렬 요소들이 제거될 수 있다. 위에서 언급된 실시예들은 함께 결합되어서 유리 코어(1200)를 형성하는 5개의 유리 조각 또는 부분(1201, 1202, 1203, 1204 및 1205)을 보여주는 도 12에 도시되어 있다. 복수의 도전체(1220)가 유리 부분들(1201-1205) 각각을 관통하여 연장된다. 각각의 유리 조각(1201-1205)은 또한 결합하는 공정 동안 유리 부분들(1201-1205)을 정렬하기 위해 이용된 짹을 이루는 정렬 요소들(1250, 1260)을 포함한다. 정렬 요소들(1250, 1260)은 도전체들(1220)의 어레이 외부에 위치된다. 일 실시예에서, 유리가 결합되어서 코어(1200)가 생성된 후에, 정렬 요소들(1250, 1260)을 포함하는 유리 코어의 부분들이 제거될 수 있다. 예를 들어, 유리 코어(1200)는 위치 조정 특징 형상들(1250, 1260)을 제거하기 위해 선 X-X 및 Y-Y를 따라 절단될 수 있으며, 코어의 이러한 부분들을 제거하기 위해 임의의 적절한 절단 공정(예를 들어 레이저 커팅, 소잉 등)이 이용될 수 있다.

[0066] 앞에서 설명된 실시예들에서, 정렬 요소들은 라운드 와이어 및 짹을 이루는 삼각형 노치를 포함한다. 그러나, 위에서 언급된 정렬 요소들은 어떠한 적절한 형상 및 구성이라도 가질 수 있음을 이해해야 한다. 예를 들어 도 13에 도시된 바와 같이, 2개의 유리 조각(1301 및 1302)이 함께 결합되어야 하고, 각각의 조각은 위치 조정 특징 형상들(1350 및 1360)을 포함한다. 위치 조정 특징 형상들(1350)은 와이어를 포함하고, 위치 조정 특징 형상들(1360)은 와이어들(1350) 중 하나를 수용하기 위한 크기를 갖는 반원형 노치를 포함한다. 추가의 예로서, 도 14에 도시된 바와 같이 2개의 유리 부분(1401 및 1402)이 함께 결합될 것이고, 각각의 조각은 정렬 요소들(1450 및 1460)을 갖는다. 위치 조정 특징 형상들(1460)은 노치들(이 경우에서는 반원형 형상)을 포함하지만, 정렬 요소들(1450)은 유리 부분들(1401, 1402) 바로 위에 형성된 돌출부들을 포함한다(본 예에서는 돌출부도 반원형임). 도 14의 실시예에서는 별개의 위치 조정 특징 형상들(예를 들어 위치 조정 와이어들)을 부착할 필요가 없으며, 짹을 이루는 위치 조정 특징 형상들(1450, 1460) 둘 다는 그로부터 조각들(1401, 1402)이 절단되는 유리 바디(내장된 와이어들을 가짐)를 만드는 데에 이용되는 압출 공정 동안 형성될 수 있다.

[0067] 이 시점에서, 도면들은 개시된 실시예들의 이해를 돋기 위해 제공된 개략도들이며, 그 도면들은 어떠한 불필요한 한정도 시사하지 않는다는 점에 주의해야 한다. 일부 경우들에서, 설명의 편의 및 명확함을 위해 비교적 적은 수의 특징이 도시되었을 수 있다. 예를 들어, 도면들에 도시된 유리 코어(150)(또는 410, 1002, 1003, 1102, 1103, 1200)를 통해 연장되는 도전체들(60)(또는 440, 920, 1220)의 개수는 그러한 유리 코어 내에 실제로 배치될 수 있는 도전체들의 개수보다 상당히 적을 수 있다. 또한, 도면들은 비례에 맞춰서 그려지지 않을 수 있으며, 일부 경우들에서는 이해를 쉽게 하기 위해 선들(예를 들어 은선들)이 생략되었다.

[0068] CTE값은 온도 의존적이고 또한 임의의 특정한 유리 재료의 조성에 따라 달라질 것이긴 하지만, 유리 재료들은 약 3.2ppm의 CTE를 가질 수 있다. 실리콘은 약 2.6ppm의 CTE를 가질 수 있으며, 이것도 마찬가지로 온도 의존적이다. 패키지 기판 및 회로 보드의 구성에서 전형적으로 이용되는 유기 고분자계 재료들은 약 12 이상의 CTE를 가질 수 있다 (역시 온도 및 조성에 의존적인 값임). 비록 위에서 언급된 바와 같이 물질의 CTE가 온도 및 조성에 의존하지만, 실리콘 다이와 기저 기판 사이의 CTE 부정합은 유리 코어 기판을 이용하면 고분자계 기판 재료에 비교하여 상당히 감소된다. 또한, 유리는 약 75GPa의 모듈러스 E를 가질 수 있는 반면에, 흔하게 이용되는 유기 고분자계 재료는 약 25GPa의 모듈러스를 가질 수 있다(E의 값도 물질의 조성에 의존함). 따라서, 유리 코어 기판은 기판 뒤틀림에 있어서 대응하는 3배의 감소에 대한 잠재력을 제공할 수 있다. 유리의 추가의 이점은 흔한 고분자 재료들보다 더 일관된 편평도로 제조될 수 있다는 것이다.

[0069] 앞에서 설명된 CTE 부정합 및 뒤틀림에서의 감소는 다이와 패키지의 상호접속부에 대해 더 작은 피치를 이용하는 것과, 더 많은 수의 그러한 상호접속부를 이용하는 것을 가능하게 하여, I/O 능력의 증가를 제공할 수 있다. 예를 들어, 일 실시예에서 유리 코어 기판을 이용할 때 다이와 패키지의 상호접속부에 대해 50 마이크로미터 이하의 피치가 달성될 수 있다. 큰 기판 뒤틀림은 칩 부착 공정 동안 다이와 패키지의 상호접속에서 비접촉 개방 장애를 야기할 수 있고, 다이 자체 내에(예를 들어 다이의 충간 유전체층들(ILD 층들) 내에) 높은 응력을 야기 할 수 있는데, 이들 둘 다 낮은 신뢰도로 이어질 수 있다. 따라서, 개시된 유리 코어 기판은 신뢰도를 유지하거나 개선하는 동시에, 더 고도의 I/O 패키지를 구현하는 것을 가능하게 할 수 있다.

[0070] 상기의 상세한 설명 및 첨부 도면들은 예시적인 것일 뿐이고 한정적인 것은 아니다. 그들은 주로 개시된 실시예들의 명확하고 포괄적인 이해를 위해 제공되었으며, 어떠한 불필요한 한정도 그들로부터 이해되어서는 안 된다. 당업자들은 개시된 실시예들의 사상 및 첨부된 청구범위로부터 벗어나지 않고서, 여기에 설명된 실시예들에 대한 복수의 추가, 삭제 및 수정과 대안적인 구성들을 생각해낼 수 있다.

## 도면

## 도면 1a

## 도면 1b

## 도면1c

## 도면1d

## 도면1e

## 도면1f

도면2

## 도면3

## 도면4a

도면4b

도면4c

도면4d

도면4e

## 도면4f

## 도면5a

## 도면5b

## 도면5c

도면6a

도면6b

도면7a

도면7b

도면7c

도면8a

도면8b

도면8c

도면9a

도면9b

도면9c

도면10a

도면10b

도면10c

도면11a

도면11b

도면11c

도면11d

도면12

도면13

도면14