(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4853186号

(P4853186)

(45) 発行日 平成24年1月11日(2012.1.11)

(24) 登録日 平成23年11月4日(2011.11.4)

(51) Int.Cl.

F 1

H03M 1/38 (2006.01)

H03M 1/14 (2006.01)H03M 1/38

H03M 1/14

A

請求項の数 5 (全 15 頁)

(21) 出願番号 特願2006-236025 (P2006-236025)

(22) 出願日 平成18年8月31日 (2006.8.31)

(65) 公開番号 特開2008-60956 (P2008-60956A)

(43) 公開日 平成20年3月13日 (2008.3.13)

審査請求日 平成21年5月28日 (2009.5.28)

(73) 特許権者 000006220

ミツミ電機株式会社

東京都多摩市鶴牧2丁目11番地2

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 井上 文裕

東京都多摩市鶴牧2丁目11番地2 ミツ

ミ電機株式会社内

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】アナログ-デジタル変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

全差動增幅回路に信号を巡回させてアナログ信号をデジタルデータに変換するアナログ-デジタル変換回路において、

前記全差動增幅回路の接続極性を切り換える極性切換手段と、

第1巡回と第2巡回以降とで前記全差動增幅回路の接続極性が切り換わるように前記極性切換手段を制御する制御手段とを有することを特徴とするアナログ-デジタル変換回路。

## 【請求項 2】

前記全差動增幅回路を巡回させる信号をサンプルホールドするサンプルホールド回路を有し、

前記サンプルホールド回路は、同じ電位で充電され、前記全差動增幅回路の異なる位置に接続される複数のコンデンサを有し

また、前記複数のコンデンサの接続位置を切り換えるコンデンサ切換手段を有し、

前記制御手段は、前記複数のコンデンサを前記全差動增幅回路に接続するときに巡回毎にその接続位置が異なるように前記コンデンサ切換手段を制御することを特徴とする請求項1記載のアナログ-デジタル変換回路。

## 【請求項 3】

アルゴリズミックアナログ-デジタル変換回路を構成していることを特徴とする請求項1記載のアナログ-デジタル変換回路。

10

20

## 【請求項 4】

アナログ信号をデジタルデータに変換するアナログ - デジタル変換回路において、同電位で充電される複数のコンデンサを有し、信号をサンプルホールドするサンプルホールド回路と、

前記サンプルホールド回路にサンプルホールドされた信号を増幅する全差動増幅回路と、

前記サンプルホールド回路にサンプルホールドされた信号を基準電圧に応じてデジタル値に変換するアナログ - デジタル変換回路と、

前記全差動増幅回路と前記複数のコンデンサとの接続を切り換える切換回路と、

第1巡目と第2巡目以降とで前記全差動増幅回路の接続極性が切り換わるように前記切換回路を制御する制御手段とを有することを特徴とするアナログ - デジタル変換回路。 10

## 【請求項 5】

前記制御手段は、巡回毎に前記複数のコンデンサの接続位置が異なるように前記切換回路を制御することを特徴とする請求項 4 に記載のアナログ - デジタル変換回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明はアナログ - デジタル変換装置に係り、特に、全差動増幅回路に信号を巡回させてアナログ信号をデジタルデータに変換するアナログ - デジタル変換回路に関する。 20

## 【背景技術】

## 【0002】

アナログ・デジタル変換装置には、パイプライン型アナログ・デジタル変換器（例えば、特許文献 1 参照）、アルゴリズミックアナログ・デジタル変換器（例えば、特許文献 2 参照）、サイクリックアナログ・デジタル変換回路（例えば、特許文献 3 参照）などが提案されていた。

## 【0003】

このうち、アルゴリズミックアナログ・デジタル変換器及びサイクリックアナログ・デジタル変換回路は、回路規模を比較的小さくできるため、I C の小面積化に適している。 30

## 【0004】

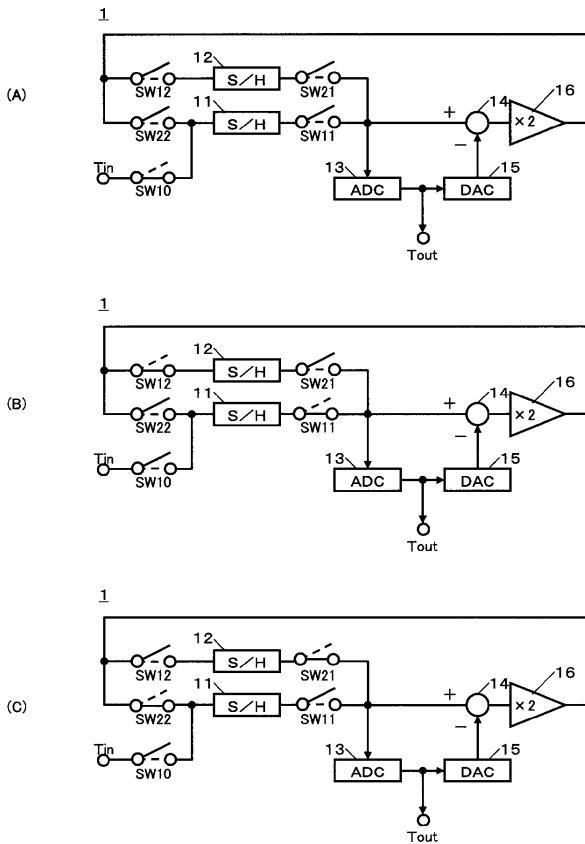

図 13 は従来のアナログ・デジタル変換器の一例のブロック構成図を示す。

## 【0005】

図 13 に示すアナログ - デジタル変換装置 1 は、アルゴリズミック A D C であり、サンプルホールド回路 11、12、1 ビット A / D 変換回路 13、減算回路 14、1 ビットデジタル - アナログ変換回路 15、増幅回路 16、スイッチ SW11、SW12、SW21、SW22 から構成されている。

## 【0006】

次にアルゴリズミック A D C の動作を説明する。

## 【0007】

まず、図 13 ( A ) に示すようにスイッチ SW10 をオン、スイッチ SW11、SW12、SW21、SW22 をオフして、サンプルホールド回路 11 で入力信号をサンプリングする。 40

## 【0008】

次に図 13 ( B ) に示すようにスイッチ SW10 をオフして、スイッチ SW11、SW12 をオン、スイッチ SW21、SW22 をオフする。これによって、サンプルホールド回路 11 にホールドされた入力信号が 1 ビット A / D 変換回路 13 に供給される。1 ビット A / D 変換回路 13 は、サンプルホールド回路 11 にサンプルホールドされた信号を 1 ビットデジタル値に変換する。これによって、最上位ビットのデジタル値を得ることができる。

## 【0009】

また、このとき、サンプルホールド回路 11 にサンプルホールドされた信号は、減算回 50

路 14 に供給されて、1 ビット A / D 変換回路 13 の 1 ビットディジタル値に応じて 1 ビットディジタル - アナログ変換回路 15 から供給される基準電圧  $V_{ref}$  が減算される。

【 0 0 1 0 】

1 ビットディジタル - アナログ変換回路 15 は、1 ビット A / D 変換回路 13 の 1 ビットディジタル値が「1」のときに基準電圧  $V_{ref}$  を減算回路 14 に供給し、1 ビット A / D 変換回路 13 の 1 ビットディジタル値が「0」のときには減算回路 14 への出力電圧を 0 とする。

【 0 0 1 1 】

減算回路 14 は、1 ビット A / D 変換回路 13 の 1 ビットディジタル値が「1」のときには基準電圧  $V_{ref}$  を減算して增幅回路 16 に供給し、1 ビット A / D 変換回路 13 の 1 ビットディジタル値が「0」のときにはサンプルホールド回路 11 にサンプルホールドされた信号をそのまま、增幅回路 16 に供給する。

【 0 0 1 2 】

增幅回路 16 は、減算回路 14 の出力を 2 倍増幅する。このとき、図 13 (B) に示すようにスイッチ SW12 がオン、スイッチ SW22 がオフされているので、增幅回路 16 で増幅された信号はサンプルホールド回路 12 にサンプルホールドされる。

【 0 0 1 3 】

サンプルホールド回路 12 に増幅回路 16 で増幅された信号がサンプルホールドされると、図 13 (C) に示すようにスイッチ SW21、SW22 がオンし、スイッチ SW11、SW12 がオフする。これによって、サンプルホールド回路 12 にサンプルホールドされた信号が 1 ビット A / D 変換される。これによって、上位 2 ビット目のディジタル値を得ることができる。

【 0 0 1 4 】

上記図 13 (B)、(C) に示すような動作を出力ディジタルデータのビット数分繰り返すことにより入力アナログ信号をディジタルデータに変換することができる。

【 0 0 1 5 】

アルゴリズミック A / D C は、上記信号を巡回して処理することによって入力アナログ信号をディジタルデータに変換している。このように、アルゴリズミック A / D C では、巡回処理によって必要最小限の回路規模で、変換動作が可能であり、回路規模を小型化できる。

【特許文献 1】特許第 3765797 号公報

【特許文献 2】特許第 3046005 号公報

【特許文献 3】特開 2004-357279 号公報

【発明の開示】

【発明が解決しようとする課題】

【 0 0 1 6 】

しかるに、従来のアルゴリズミック A / D C では、巡回処理によって、回路を最小限に留めることができる一方、増幅回路の入力換算オフセット、コンデンサの容量ばらつきなどが巡回処理によって重畠されて、増加するため、誤差が大きくなり、高精度の A / D 変換が行えないなどの問題点があった。

【 0 0 1 7 】

本発明は上記の点に鑑みてなされたもので、変換精度を向上できるアナログ - ディジタル変換装置を提供することを目的とする。

【課題を解決するための手段】

【 0 0 1 8 】

本発明は、全差動増幅回路 (113) に信号を巡回させてアナログ信号をディジタルデータに変換するアナログ - ディジタル変換回路において、全差動増幅回路 (113) の接続極性を切り換える極性切換手段 (115) と、第 1 巡目と第 2 巡目以降とで全差動増幅回路 (113) の接続極性が切り換わるように極性切換手段 (115) を制御する制御手段 (116) とを有することを特徴とする。

10

20

30

40

50

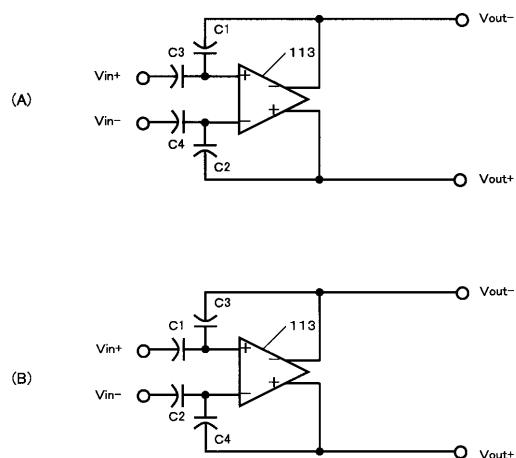

## 【0019】

本発明は、全差動増幅回路(113)を巡回させる信号をサンプルホールドするサンプルホールド回路(111, 112)を有し、サンプルホールド回路(111, 112)は同じ電位で充電され、全差動増幅回路(113)の異なる位置に接続される複数のコンデンサ(C1, C3; C2, C4; C5, C7; C6, C8)を有し、また、複数のコンデンサ(C1, C3; C2, C4; C5, C7; C6, C8)の接続位置を切り換えるコンデンサ切換手段(115)を有し、制御手段(116)は、複数のコンデンサ(C1, C3; C2, C4; C5, C7; C6, C8)を全差動増幅回路(113)に接続するときに巡回毎にその接続位置が異なるようにコンデンサ切換手段(115)を制御することを特徴とする。

10

## 【0020】

また、アルゴリズミックアナログ-ディジタル変換回路を構成していることを特徴とする。

## 【0021】

また、本発明は、アナログ信号をディジタルデータに変換するアナログ-ディジタル変換回路において、同電位で充電される複数のコンデンサ(C1, C3; C2, C4; C5, C7; C6, C8)を有し、信号をサンプルホールドするサンプルホールド回路(111, 112)と、サンプルホールド回路(111, 112)にサンプルホールドされた信号を増幅する全差動増幅回路(113)と、サンプルホールド回路(111, 112)にサンプルホールドされた信号を基準電圧に応じてディジタル値に変換するアナログ-ディジタル変換回路(114)と、全差動増幅回路(113)と複数のコンデンサ(C1, C3; C2, C4; C5, C7; C6, C8)との接続を切り換える切換回路(115)と、第1巡回と第2巡回以降とで全差動増幅回路(113)の接続極性が切り換わるように切換回路(115)を制御する制御手段(116)とを有することを特徴とする。

20

## 【0022】

制御手段(116)は、巡回毎に複数のコンデンサ(C1, C3; C2, C4; C5, C7; C6, C8)の接続位置が異なるように切換回路(115)を制御することを特徴とする。

## 【0023】

なお、上記参照符号は、あくまでも参考であり、これによって特許請求の範囲が限定されるものではない。

30

## 【発明の効果】

## 【0024】

本発明によれば、全差動増幅回路(113)に信号を巡回させてアナログ信号をディジタルデータに変換するアナログ-ディジタル変換回路において、全差動増幅回路(113)の接続極性を切り換える極性切換手段(115)と、第1巡回と第2巡回以降とで全差動増幅回路(113)の接続極性が切り換わるように極性切換手段(115)を制御する制御手段(116)とを設けることにより、信号を全差動増幅回路(113)で巡回させて増幅した場合であっても、全差動増幅回路(113)のオフセット成分を圧縮することができ、よって、誤差を低減できるため、A/D変換精度を向上させることができとなる。

40

## 【発明を実施するための最良の形態】

## 【0025】

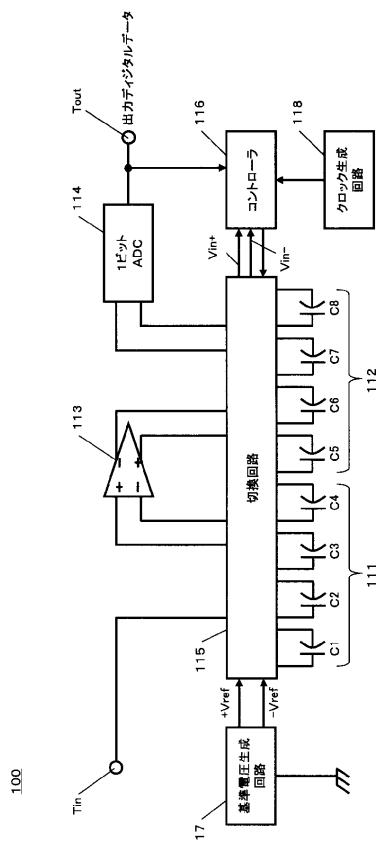

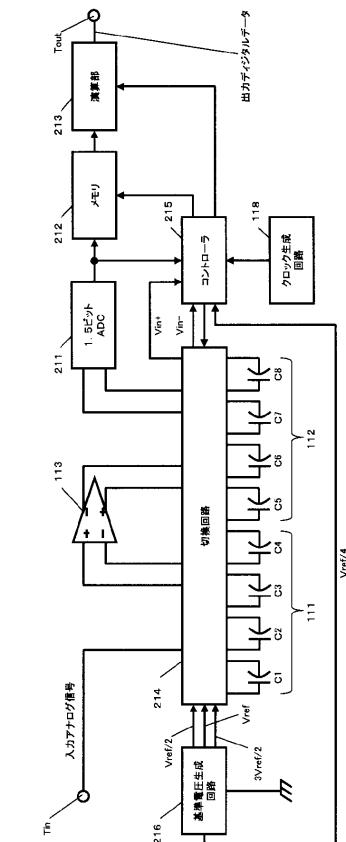

図1は本発明の一実施例のブロック構成図を示す。

## 【0026】

本実施例のアナログ-ディジタル変換装置100は、第1のサンプルホールド回路111及び第2のサンプルホールド回路112、差動増幅回路113、1ビットアナログ-ディジタル変換回路114、切換回路115、コントローラ116、基準電圧生成回路117、クロック生成回路118から構成されており、いわゆる、アルゴリズミックアナログ-ディジタル変換回路を構成している。

## 【0027】

50

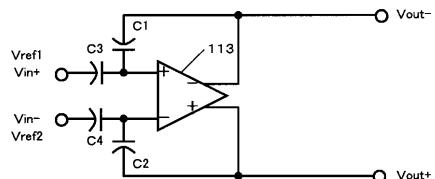

第1のサンプルホールド回路111はコンデンサC1～C4から構成されており、切換回路115に接続されている。コンデンサC1とコンデンサC3とは対をなしており、同電位で充電される。また、コンデンサC2とコンデンサC4とは対をなしており、同電位で充電される。コンデンサC1とコンデンサC3との対とコンデンサC2とコンデンサC4との対とは、同じタイミングで、互いに異なる極性で充電される。

【0028】

第2のサンプルホールド回路112は、コンデンサC5～C8から構成されており、切換回路115に接続されている。コンデンサC5とコンデンサC7とは対をなしており、同電位で充電される。また、コンデンサC6とコンデンサC8とは対をなしており、同電位で充電される。コンデンサC5とコンデンサC7との対とコンデンサC6とコンデンサC8との対とは、同じタイミングで、互いに異なる極性で充電される。

10

【0029】

差動增幅回路113は、全差動增幅回路を構成しており、反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子が切換回路115に接続されている。差動增幅回路113は、切換回路115を介してコンデンサC1～C4、C5～C8が接続され、サンプルホールドされた信号を差動增幅して、切換回路115を介して1ビットアナログ-ディジタル変換回路114に供給する。

【0030】

1ビットアナログ-ディジタル変換回路114は、切換回路115に接続されており、切換回路115から供給される第1のサンプルホールド回路111又は第2のサンプルホールド回路112にサンプルホールドされている信号を基準電圧生成回路117から供給される基準電圧Vrefと比較して、例えば、サンプルホールドされている信号が基準電圧Vrefより小さいときには出力を「0」とし、サンプルホールドされている信号が基準電圧Vrefより大きいときには出力を「1」とする。

20

【0031】

切換回路115は、コントローラ116からの切換制御信号に基づいてコンデンサC1～C4、C5～C8の接続、及び、差動增幅回路113の反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子の接続を切り換える。

【0032】

コントローラ116は、クロック生成回路118から供給されるクロックに応じたタイミングで、切換回路115を制御する切換制御信号を生成し、切換回路115に供給する。コントローラ116は、第1巡目と第2巡目以降とで差動增幅回路113の接続極性が切り換わるように切換回路115を制御するとともに、巡回毎に差動增幅回路113の入力端子側においてコンデンサC1、C2とコンデンサC3、C4又はコンデンサC5、C6とコンデンサC7、C8の接続位置が異なるように切換回路115を制御する。

30

【0033】

クロック生成回路118は、所定の周波数で発振しており、コントローラ116にクロックを供給している。コントローラ116は、クロック生成回路118からのクロックに基づいて駆動されている。

【0034】

40

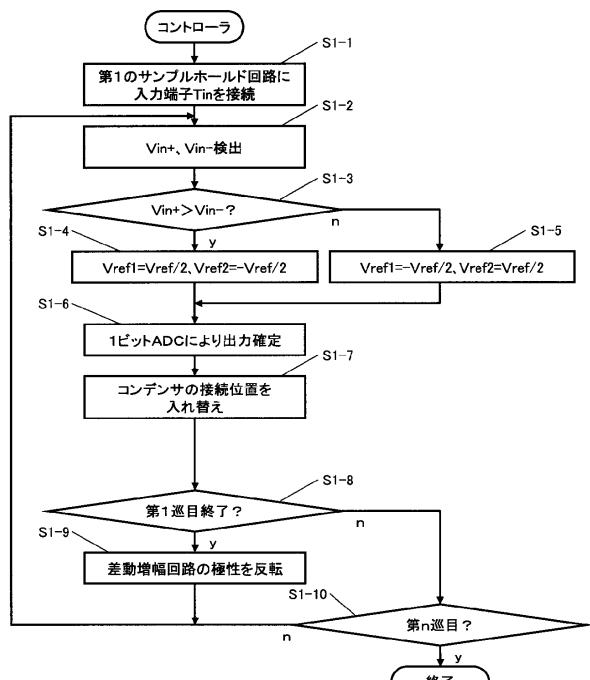

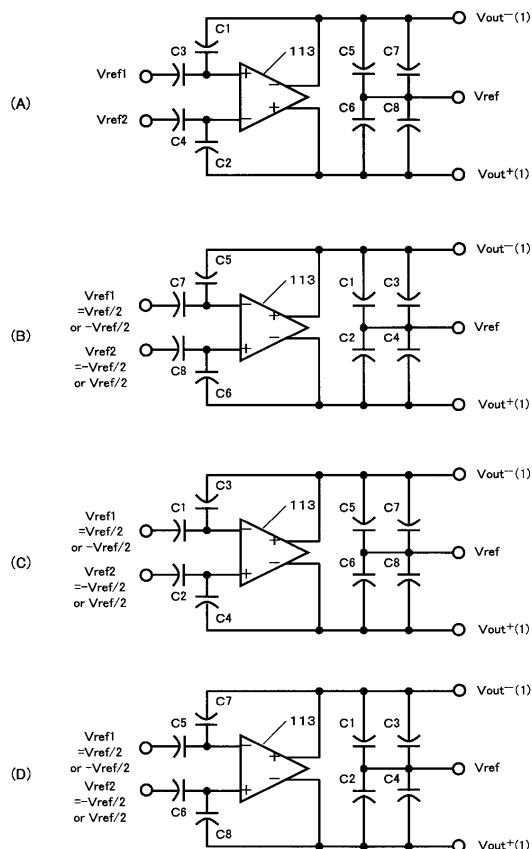

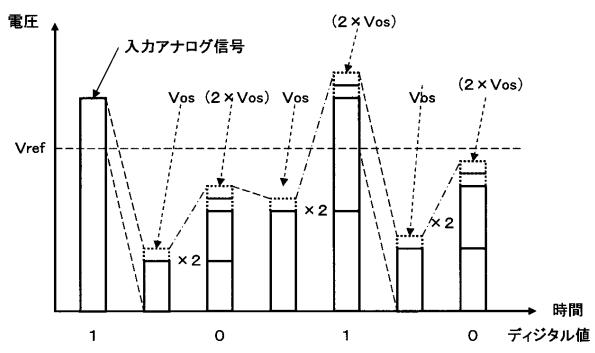

図2はコントローラ116の処理フローチャート、図3は本発明の一実施例の切換動作を説明するための図、図4は本発明の一実施例の動作説明図を示す。

【0035】

まず、コントローラ116は、ステップS1-1で入力端子Tinを第1のサンプルホールド回路111に接続し、入力端子Tinに入力される入力アナログ信号を第1のサンプルホールド回路111にサンプルホールドする。

【0036】

次にコントローラ116は、ステップS1-2で第1のサンプルホールド回路111及び第2のサンプルホールド回路112のコンデンサC1～C8を差動增幅回路113に対して図3(A)に示すように接続し、入力信号の非反転入力電圧Vin+、反転入力電圧Vi

50

$n$ -を検出し、ステップ S 1 - 3 で ( $V_{in+} > V_{in-}$ ) か否かを判定する。コントローラ 116 は、ステップ S 1 - 3 で ( $V_{in+} > V_{in-}$ ) である場合、ステップ S 1 - 4 で第 1 のサンプルホールド回路 111 への非反転入力側バイアス電圧  $V_{ref1}$  を

$$V_{ref1} = (V_{ref} / 2)$$

に設定し、反転入力側バイアス電圧  $V_{ref2}$  を

$$V_{ref2} = - (V_{ref} / 2)$$

に設定する。なお、ここで、 $V_{ref}$  は A/D 変換の中心電圧である。

#### 【0037】

次に、コントローラ 116 は、ステップ S 1 - 6 で 1 ビット ADC 114 により 1 ビット出力を確定する。1 ビット ADC 114 は、差動増幅回路 113 の出力電圧  $V_{out}$

$$V_{out} = (V_{out-} - V_{out+})$$

と  $V_{ref}$  とを比較し、

$$V_{out} < V_{ref}$$

であれば、「0」を出力し、

$$V_{out} > V_{ref}$$

であれば、「1」を出力する。

#### 【0038】

次に、コントローラ 116 は、ステップ S 1 - 7 で第 1 のサンプルホールド回路 111 及び第 2 のサンプルホールド回路 112 のコンデンサ C1 ~ C8 を差動増幅回路 113 に 10 対して図 3 (B) に示すように接続する。

#### 【0039】

また、コントローラ 116 は、ステップ S 1 - 8 で信号の差動増幅回路 113 の巡回回数が第 1 巡目か否かを判定する。

#### 【0040】

コントローラ 116 は、ステップ S 1 - 8 で第 1 巡目である場合には、ステップ S 1 - 9 で差動増幅回路 113 の極性を図 3 (A) に示す状態から図 3 (B) に示すような状態に反転させた後、ステップ S 1 - 3 に戻って処理を続ける。また、コントローラ 116 は、ステップ S 1 - 8 で第 2 巡目以降である場合には、ステップ S 1 - 9 で第  $n$  巡目か否かを判定する。なお、 $n$  は、出力ディジタルデータのビット数に応じて設定される所定の値である。

#### 【0041】

コントローラ 116 は、差動増幅回路 113 による増幅動作が  $n$  回行われるまで、ステップ S 1 - 2 ~ S 1 - 10 の処理を継続し、差動増幅回路 113 による増幅動作が  $n$  回行われると、変換動作が終了したと判断して、処理を終了する。

#### 【0042】

このとき、ステップ S 1 - 7 の処理により第 1 巡目に図 3 (A) に示すような接続が、第 2 巡目には図 3 (B) に示すように第 1 のサンプルホールド回路 111 が差動増幅回路 113 の出力側に接続され、また、第 2 のサンプルホールド回路 112 が差動増幅回路 113 の入力側に接続される。さらに、ステップ S 1 - 7 の処理によって、図 3 (A) に示す第 1 巡目と、図 3 (B) ~ (D) に示すように第 2 巡目以降とで、差動増幅回路 113 の反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子の接続関係が反転した接続となる。

#### 【0043】

図 3 (A) に示す第 1 巡目と、図 3 (B) ~ (D) に示すように第 2 巡目以降とで、差動増幅回路 113 の反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子の接続関係を反転させることにより、図 4 に示すように第 1 巡目で差動増幅回路 113 のオフセット  $V_{os}$  を含む成分が 2 倍されて出力された場合であっても、第 2 巡目で差動増幅回路 113 の反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子の接続関係が反転することによって、オフセットは  $V_{os}$  に維持される。

#### 【0044】

10

20

30

40

50

例えば、また、図4に示すように第1巡回では、差動増幅回路113のオフセットVosが増加されて2倍されることにより、オフセット成分は( $2 \times Vos$ )となる。しかし、第2巡回で差動増幅回路113の反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子の接続関係が反転するため、オフセットVosが減算され、オフセットVosは、 $(2 \times Vos) - Vos = Vos$ となり、これが2倍されてオフセット成分は( $2 \times Vos$ )となる。同様に、第2巡回以降は、オフセット成分はVosが減算されて2倍されるので、判定に用いられる信号に重畠されるオフセット成分は、差動増幅回路113を巡回しても差動増幅回路113のオフセット成分Vosだけで済む。よって、AD変換精度を向上させることができる。

【0045】

10

また、本実施例では、ステップS1-7で差動増幅回路113の入力側にコンデンサC1～C8を接続する際、図3(A)、(C)に示すようにコンデンサC1とコンデンサC3、コンデンサC2とコンデンサC4を入れ替えるとともに、図3(B)、(D)に示すようにコンデンサC5とコンデンサC7、コンデンサC6とコンデンサC8の位置を入れ替えている。

【0046】

図5、図6は本発明の一実施例の効果を説明するための図を示す。同図中、図3と同一構成部分には同一符号を付し、その説明は省略する。図5において偏差を持たせるためにコンデンサC1、C2は、 $C1 = C2 = C$ 、コンデンサC3、C4は $C3 = C4 = 1.1C$ に設定されている。

20

【0047】

図6は、図5(A)に示す状態1を繰り返した場合の増幅度と、図5(B)に示す状態2の増幅度と、図5(A)に示す状態1と図5(B)に示す状態2とを繰り返した場合の増幅度とを比較したものである。

【0048】

30

図6に示すように図5(A)に示す状態1で1回増幅すると、入力に対して出力は1.91倍となる。また、2回増幅すると、 $1.91 \times 1.91 = 3.65$ 倍となる。さらに、3回増幅すると、 $3.65 \times 1.91 = 6.97$ 倍となる。また、4回増幅すると、 $6.97 \times 1.91 = 13.31$ 倍となる。2.0倍の増幅度で4回増幅した場合、16.0倍になるのに対し、図5(A)に示す状態1で4回増幅した場合には、13.31倍にしかならず、所望の増幅度が得られずよって、AD変換精度が悪くなる。

【0049】

また、図6に示すように図5(B)に示す状態2で1回増幅すると、入力に対して出力は2.1倍となる。また、2回増幅すると、 $2.1 \times 2.1 = 4.41$ 倍となる。さらに、3回増幅すると、 $4.41 \times 2.1 = 9.26$ 倍となる。また、4回増幅すると、 $9.26 \times 2.1 = 19.45$ 倍となる。2.0倍の増幅度で4回増幅した場合、16.0倍になるのに対し、上記のように図5(B)に示す状態2で4回増幅した場合には、19.45倍になり、所望の増幅度が得られずよって、状態1と同様にAD変換精度が悪くなる。

【0050】

40

一方、図6に示すように図5(A)に示す状態1で増幅すると、入力に対して出力は1.91倍となる。次に図5(B)に示す状態2で増幅すると、 $1.91 \times 2.1 = 4.01$ 倍となる。次に、図5(A)に示す状態1で増幅すると、 $4.01 \times 1.91 = 7.66$ 倍となる。次に、図5(B)に示す状態2で増幅すると、 $7.66 \times 1.91 = 16.01$ 倍となる。2.0倍の増幅度で4回増幅した場合、16.0倍になるのに対し、上記のように図5(A)に示す状態1と図5(B)に示す状態2とを交互に4回増幅した場合には、16.01倍になり、16.0倍に極めて近い増幅度が得られる。よって、AD変換精度を向上させることができる。

【0051】

このように、コンデンサの容量の偏差を吸収でき、よって、AD変換の精度を更に向上

50

することができる。

【0052】

なお、上記実施例では、説明を簡単にするために逐次1ビットに変換出力する1ビットA D Cについて説明したが、1.5ビット以上のA D Cに適用することも可能である。

【0053】

図7は本発明の他の実施例のブロック構成図を示す。同図中、図1と同一構成部分には同一符号を付し、その説明は省略する。

【0054】

本実施例のアナログ-ディジタル変換装置200は、1.5ビットのA D Cに適用した例を示しており、1ビットアナログ-ディジタル変換回路114に代えて1.5ビットアナログ-ディジタル変換回路211、メモリ212、演算部213を設けるとともに、切換回路115に代えて切換回路214、コントローラ216に代えてコントローラ215、基準電圧生成回路117に代えて基準電圧生成回路216などを設けた構成とされている。

【0055】

基準電圧生成回路216は、基準電圧 $V_{ref}/2$ 、 $V_{ref}$ 、 $3V_{ref}/2$ を生成し、切換回路214に供給する。切換回路214は、コントローラ215からの制御信号に応じて基準電圧生成回路216からの基準電圧 $V_{ref}/2$ 、 $V_{ref}$ 、 $3V_{ref}/2$ のいずれかを基準電圧 $V_{ref1}$ 、 $V_{ref2}$ として印加する。

【0056】

ここで、コントローラ215の処理について説明する。

【0057】

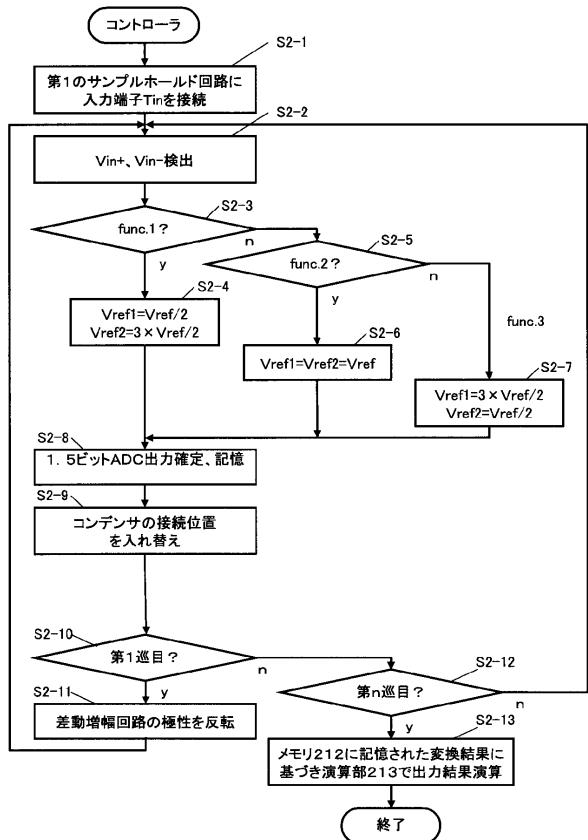

図8は、コントローラ215の処理フローチャートを示す。

【0058】

コントローラ215は、ステップS2-1で入力端子Tinを第1のサンプルホールド回路111に接続し、入力端子Tinに入力される入力アナログ信号を第1のサンプルホールド回路111にサンプルホールドする。

【0059】

次にコントローラ215は、ステップS2-2で入力アナログ信号の非反転入力側電圧 $V_{in+}$ 及び反転入力側電圧 $V_{in-}$ を検出するとともに、基準電圧生成回路117から( $V_{ref}/4$ )を入力する。

【0060】

コントローラ215は、ステップS2-3、S2-5で入力電圧 $V_{in+}$ 、 $V_{in-}$ に適用するファンクションを判定する。

【0061】

例えば、コントローラ215は、入力電圧 $V_{in+}$ 、 $V_{in-}$ と電圧( $V_{ref}/4$ )との関係が

$$V_{in+} < (V_{in-} - V_{ref}/4)$$

であれば、入力電圧 $V_{in+}$ 、 $V_{in-}$ に対してファンクションfunc.1を適用する。コントローラ215は、ステップS2-3で入力電圧 $V_{in+}$ 、 $V_{in-}$ に対してファンクションfunc.1を適用する場合、ステップS2-4で基準電圧生成回路216から第1又は第2のサンプルホールド回路111、112に印加するバイアス電圧 $V_{ref1}$ 、 $V_{ref2}$ を

$$V_{ref1} = V_{ref}/2$$

$$V_{ref2} = 3 \times V_{ref}/2$$

に設定する。

【0062】

また、コントローラ215は、入力電圧 $V_{in+}$ 、 $V_{in-}$ と電圧( $V_{ref}/4$ )との関係が $(|V_{in+} - V_{in-}|) < (V_{ref}/4)$

であれば、入力電圧 $V_{in+}$ 、 $V_{in-}$ に対してファンクションfunc.2を適用する。コントローラ215は、ステップS2-5で入力電圧 $V_{in+}$ 、 $V_{in-}$ に対してファンクションfunc.2を

10

20

30

40

50

適用する場合、ステップ S 2 - 6 で基準電圧生成回路 216 から第 1 又は第 2 のサンプルホールド回路 111, 112 に印加するバイアス電圧  $V_{ref1}$ 、 $V_{ref2}$  を

$$V_{ref1} = V_{ref2} = V_{ref}$$

とする。

#### 【0063】

さらに、コントローラ 215 は、入力電圧  $V_{in+}$ 、 $V_{in-}$  と電圧 ( $V_{ref} / 4$ ) との関係が

$$V_{in+} > (V_{in-} + V_{ref} / 4)$$

であれば、入力電圧  $V_{in+}$ 、 $V_{in-}$  に対してファンクション func.3 を適用する。コントローラ 215 は、ステップ S 2 - 5 で入力電圧  $V_{in+}$ 、 $V_{in-}$  に対してファンクション func.3 を適用する場合、ステップ S 2 - 7 で基準電圧生成回路 216 から第 1 又は第 2 のサンプルホールド回路 111, 112 に印加するバイアス電圧  $V_{ref1}$ 、 $V_{ref2}$  を

$$V_{ref1} = 3 \times V_{ref} / 2$$

$$V_{ref2} = 2 \times V_{ref} / 3$$

とする。

#### 【0064】

次に、コントローラ 215 は、ステップ S 2 - 8 で適用されたファンクション func.1、func.2、func.3 に応じて 2 ビットのデジタル値に変換する。1.5 ビット ADC 211 は、例えば、入力信号のうち非反転入力を  $V_{in+}$ 、反転入力を  $V_{in-}$  としたとき、

$$V_{in+} < (V_{in-} - V_{ref} / 4)$$

のとき、すなわち、ファンクション func.1 のときには出力デジタル値を「0、0」とする。また、1.5 ビット ADC 211 は、

$$(|V_{in+} - V_{in-}|) < (V_{ref} / 4)$$

のとき、すなわち、ファンクション func.2 のときには出力デジタル値を「0,1」とする。

#### 【0065】

さらに、1.5 ビット ADC 211 は、

$$V_{in+} > (V_{in-} + V_{ref} / 4)$$

のとき、すなわち、ファンクション func.3 のときには出力デジタル値を「1,0」とする。

#### 【0066】

1.5 ビット ADC 211 の出力デジタル値は、メモリ 212 に記憶される。

#### 【0067】

次に、コントローラ 215 は、ステップ S 2 - 9 で切換回路 214 を制御して、コンデンサ C1 ~ C8 の接続を図 3 (A) に示す状態から図 3 (B) に示すように切り換える。

また、コントローラ 215 は、ステップ S 2 - 10 で巡回回数が第 1 巡目か否かを判定する。

#### 【0068】

コントローラ 215 は、ステップ S 2 - 10 で第 1 巡目である場合には、ステップ S 2 - 11 で切換回路 214 を制御して、差動增幅回路 113 の極性を図 3 (A) に示す状態から図 3 (B) に示す状態に反転させた後、ステップ S 2 - 2 に戻って処理を続ける。このとき、ステップ S 2 - 11 の処理により第 1 巡目に図 3 (A) に示すような接続が、第 2 巡目には図 3 (B) に示すように第 1 のサンプルホールド回路 111 が差動增幅回路 113 の出力側に接続され、また、第 2 のサンプルホールド回路 112 が差動增幅回路 113 の入力側に接続される。さらに、ステップ S 2 - 11 の処理によって、図 3 (A) に示す第 1 巡目と、図 3 (B) ~ (D) に示すように第 2 巡目以降とで、差動增幅回路 113 の反転入力端子、非反転入力端子、及び、反転出力端子、非反転出力端子の接続関係が反転した接続となる。

#### 【0069】

これにより、差動增幅回路 113 のオフセットを  $V_{os}$  に維持することができる。

10

20

30

40

50

## 【0070】

また、コントローラ215は、ステップS2-10で第2巡回以降である場合には、ステップS2-12で第n巡回か否かを判定する。

## 【0071】

コントローラ215は、差動増幅回路113による増幅動作がn回行われるまで、ステップS2-2～S2-12の処理を継続し、差動増幅回路113による増幅動作がn回行われると、変換動作が終了したと判断する。コントローラ215は、ステップS2-12で第n巡回になると、1.5ビットADC211での処理は終了したと判断して、ステップS2-13でメモリ212に記憶された1.5ビットADC211での各巡回毎の変換結果を読み出して、演算部213に供給し、出力ディジタル値を決定する。

10

## 【0072】

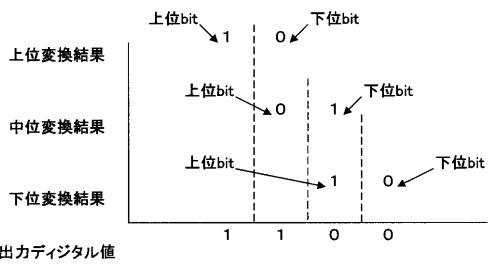

図9は演算部213の演算動作を説明するための図を示す。

## 【0073】

図9において1.5ビットADC211で最初に変換された上位変換結果を「1,0」、次に変換された中位変換結果を「0,1」、その次に変換された下位変換結果を「1,0」とする。

## 【0074】

上位変換結果の下位ビットと中位変換結果の上位ビット、中位変換結果の下位ビットと下位変換結果の上位ビットとの位を同じ位に設定して上位変換結果と中位変換結果と下位変換結果との加算を行う。図9の加算結果は「1100」となる。コントローラ215は、演算部213の演算結果を出力ディジタル値として出力する。

20

## 【0075】

なお、ここで、本実施例の動作を、数式を用いて説明する。

## 【0076】

図10は本発明の他の実施例の動作説明図を示す。

## 【0077】

図10に示すように差動増幅回路113の非反転入力をVin+、反転入力をVin-、反転出力をVout-、非反転出力をVout+、非反転入力端子のバイアス電圧をVref1、反転入力端子のバイアス電圧をVref2、コンデンサC1～C4をC1=C2=C3=C4、基準電圧をVrefとすると、差動増幅回路113の反転出力Vout-は、

30

$$V_{out-} = V_{ref1} - (V_{ref1} - V_{in+}) (1 + C3/C1) \quad \dots \quad (1)$$

非反転出力Vout+は、

$$V_{out+} = V_{ref2} - (V_{ref2} - V_{in-}) (1 + C4/C2) \quad \dots \quad (2)$$

で表せる。

## 【0078】

まず、

$$V_{in+} < V_{in-} - (V_{ref}/4) \quad \dots \quad (3)$$

のときには、

$$V_{ref1} = V_{ref}/2 \quad \dots \quad (4)$$

$$V_{ref2} = 3 \times V_{ref}/2 \quad \dots \quad (5)$$

40

とする。式(1)から非反転出力Vout+は、

$$V_{out+} = 2 \times V_{in+} - 3 \times (V_{ref}/2) \quad \dots \quad (6)$$

となり、式(2)から反転出力Vout-は、

$$V_{out-} = 2 \times V_{in-} - (V_{ref}/2) \quad \dots \quad (7)$$

となる。したがって、差動出力Vout = Vout+ - Vout-は、式(6)、(7)より、

$$V_{out} = 2 \times (V_{in+} - V_{in-}) + V_{ref} \quad \dots \quad (8)$$

となる。

## 【0079】

$$V_{out} = 2 \times (V_{in+} - V_{in-}) + V_{ref} \quad \dots \quad (9)$$

のときには、

50

$$V_{ref1} = V_{ref2} = V_{ref} \quad \dots \dots (10)$$

とする。これによって、式(1)から非反転出力  $V_{out+}$  は、

$$V_{out+} = 2 \times V_{in+} - V_{ref} \quad \dots \dots (11)$$

となり、式(2)から反転出力  $V_{out-}$  は、

$$V_{out-} = 2 \times V_{in-} - V_{ref} \quad \dots \dots (12)$$

となる。したがって、差動出力  $V_{out} = V_{out+} - V_{out-}$  は、式(11)、(12)より、

$$V_{out} = 2 \times (V_{in+} - V_{in-}) \quad \dots \dots (13)$$

となる。

#### 【0080】

$$\text{さらに、 } V_{in+} > V_{in-} + (V_{ref} / 4) \quad \dots \dots (14)$$

のときには、

$$V_{ref1} = 3 \times V_{ref} / 2 \quad \dots \dots (15)$$

$$V_{ref2} = V_{ref} / 2 \quad \dots \dots (16)$$

とする。これによって、式(1)から非反転出力  $V_{out+}$  は、

$$V_{out+} = 2 \times V_{in-} - (V_{ref} / 2) \quad \dots \dots (17)$$

となり、式(2)から反転出力  $V_{out-}$  は、

$$V_{out-} = 2 \times V_{in-} - 3 \times (V_{ref} / 2) \quad \dots \dots (18)$$

となる。したがって、差動出力  $V_{out} = V_{out+} - V_{out-}$  は、式(17)、(18)より、

$$V_{out} = 2 \times (V_{in+} - V_{in-}) - V_{ref} \quad \dots \dots (19)$$

となる。

#### 【0081】

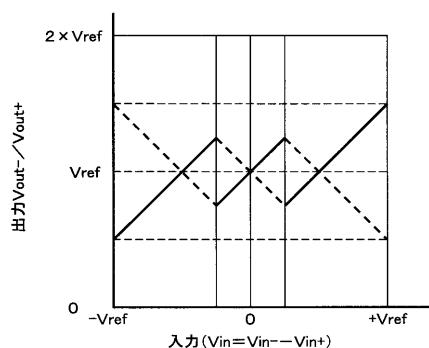

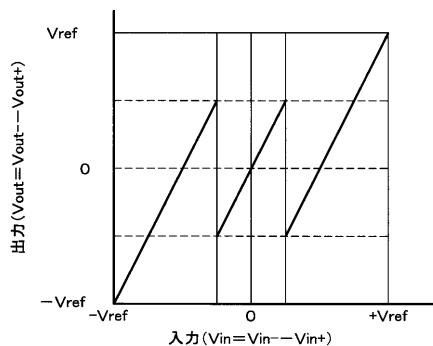

図11は入力 ( $V_{in-} - V_{out+}$ ) に対する出力  $V_{out+}$  及び出力  $V_{out-}$  の関係を示す図、図12は入力 ( $V_{out-} - V_{out+}$ ) に対する出力 ( $V_{out-} - V_{out+}$ ) の関係を示す図である。

#### 【0082】

図11において、実線は  $V_{out-}$  、破線は  $V_{out+}$  を示している。

#### 【0083】

入力 ( $V_{in-} - V_{in+}$ ) と出力  $V_{out+}$  及び出力  $V_{out-}$  並び出力 ( $V_{out-} - V_{out+}$ ) との関係は、式(6)、(7)、(8)、及び式(11)、(12)、(13)、並びに式(17)、式(18)、(19)から図11、及び、図12に示すような関係となる。

#### 【0084】

このように1.5ビットAD変換では、図12に示すように入力 ( $V_{in-} - V_{in+}$ ) に対する出力 ( $V_{out-} - V_{out+}$ ) の変位を大きくとることができ、検出精度を向上させることが可能となる。

#### 【0085】

なお、本発明は、1ビット、1.5ビットAD変換方式に限定されるものではなく、2ビット以上のAD変換方式の巡回AD変換方式においても適用可能であることは言うまでもない。

#### 【0086】

なお、本発明は上記実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変形例が考えられることは言うまでもない。

#### 【図面の簡単な説明】

#### 【0087】

【図1】本発明の一実施例のブロック構成図である。

【図2】コントローラ116の処理フローチャートである。

【図3】本発明の一実施例の切換動作を説明するための図である。

【図4】本発明の一実施例の動作説明図である。

【図5】本発明の一実施例の効果を説明するための図である。

【図6】本発明の一実施例の効果を説明するための図である。

【図7】本発明の他の実施例のブロック構成図である。

10

20

30

40

50

【図8】コントローラ212の処理フローチャートである。

【図9】演算部213の演算動作を説明するための図である。

【図10】本発明の他の実施例の動作説明図である。

【図11】入力( $V_{in-}$ - $V_{out+}$ )に対する出力 $V_{out+}$ 及び出力 $V_{out-}$ の関係を示す図である。

【図12】入力( $V_{out-}$ - $V_{out+}$ )に対する出力( $V_{out-}$ - $V_{out+}$ )の関係を示す図である。

【図13】従来のアナログ・デジタル変換器の一例のブロック構成図である。

【符号の説明】

【0088】

10

100、200 アナログ・デジタル変換回路

111 第1のサンプルホールド回路、112 第2のサンプルホールド回路

113 差動增幅回路、114 1ビットアナログ・デジタル変換器

115 切換回路、116 コントローラ、117 基準電圧生成回路

118 クロック生成回路

211 1.5ビットADC、212 メモリ、213 演算部

214 切換回路、215 コントローラ、216 基準電圧生成回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

|    |     | 増幅回数   |        |        |         |

|----|-----|--------|--------|--------|---------|

|    |     | 1回     | 2回     | 3回     | 4回      |

| 状態 | 状態1 | 1. 91倍 | 3. 65倍 | 6. 97倍 | 13. 31倍 |

|    | 状態2 | 2. 1倍  | 4. 41倍 | 9. 26倍 | 19. 45倍 |

|    | 状態3 | 1. 91倍 | 4. 01倍 | 7. 66倍 | 16. 01倍 |

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

---

フロントページの続き

(56)参考文献 特開平4-156722(JP, A)

Furuta, M.; Kawahito, S.; Inoue, T.; Nishikawa, Y.; A cyclic A/D converter with pixel noise and column-wise offset canceling for CMOS image sensors, Solid-State Circuits Conference, 2005. ESSCIRC 2005. Proceedings of the 31st European, 米国, 2005年, Pages 411-414

(58)調査した分野(Int.Cl., DB名)

H 03M 1/00 - 1/88