(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7556185号**

**(P7556185)**

(45)発行日 令和6年9月26日(2024.9.26)

(24)登録日 令和6年9月17日(2024.9.17)

(51)国際特許分類

**G 0 6 F 12/00 (2006.01)**

F I

|         |       |         |

|---------|-------|---------|

| G 0 6 F | 12/00 | 5 6 4 A |

| G 0 6 F | 12/00 | 5 5 0 B |

| G 0 6 F | 12/00 | 5 5 0 K |

請求項の数 18 外国語出願 (全14頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2019-80457(P2019-80457)   |

| (22)出願日           | 平成31年4月19日(2019.4.19)       |

| (65)公開番号          | 特開2019-212294(P2019-212294) |

|                   | A)                          |

| (43)公開日           | 令和1年12月12日(2019.12.12)      |

| 審査請求日             | 令和4年2月16日(2022.2.16)        |

| 審判番号              | 不服2023-16034(P2023-16034/J) |

|                   | 1)                          |

| 審判請求日             | 令和5年9月22日(2023.9.22)        |

| (31)優先権主張番号       | 16/001,869                  |

| (32)優先日           | 平成30年6月6日(2018.6.6)         |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

|          |                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 591003943<br>インテル・コーポレーション<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200                                                               |

| (74)代理人  | 110000877<br>弁理士法人 R Y U K A 国際特許事務所                                                                                                             |

| (72)発明者  | クリストファー・コックス<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200 インテル・コーポレーション内<br>ビル・ネイル<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ 最終頁に続く |

| (72)発明者  |                                                                                                                                                  |

(54)【発明の名称】 メモリデバイスセルフリフレッシュ中の定期的キャリブレーション

**(57)【特許請求の範囲】****【請求項1】**

メモリデバイスであって、

オンダイ終端(O D T)及びドライバの定期的なキャリブレーションを実行するためのキャリブレーション回路と、

前記メモリデバイスにより受信されるセルフリフレッシュ命令に応答して、前記メモリデバイスをセルフリフレッシュモードにするためのセルフリフレッシュ回路と、を備え、

前記O D T及びドライバの定期的なキャリブレーションは、前記メモリデバイスが前記セルフリフレッシュモードである間にリフレッシュと同時に実行される

メモリデバイス。

10

**【請求項2】**

前記メモリデバイスが前記セルフリフレッシュモードからアクティブモードへと移行するときに前記キャリブレーションは実行されない、請求項1に記載のメモリデバイス。

**【請求項3】**

メモリデバイスであって、

オンダイ終端(O D T)及びドライバの定期的なキャリブレーションを実行するためのキャリブレーション回路と、

前記メモリデバイスにより受信されるセルフリフレッシュ命令に応答して、前記メモリデバイスをセルフリフレッシュモードにするためのセルフリフレッシュ回路と、を備え、

前記O D T及びドライバの定期的なキャリブレーションは、前記メモリデバイスが前記

20

セルフリフレッシュモードである間に実行され、

前記メモリデバイスにより設定されたフラグが直近のキャリブレーションの成功を示す場合、前記メモリデバイスが前記セルフリフレッシュモードからアクティブモードへと移行するときにキャリブレーションは実行されず。

前記メモリデバイスにより設定された前記フラグが直近のキャリブレーションの成功を示さない場合、前記メモリデバイスがセルフリフレッシュ中に前記定期的なキャリブレーションを実行するよう命令されていたとしても、前記メモリデバイスが前記セルフリフレッシュモードから前記アクティブモードへと移行するときにキャリブレーションは実行される、メモリデバイス。

#### 【請求項 4】

前記メモリデバイスは、前記ODT及びドライバの定期的なキャリブレーションを可能にするためのレジスタ空間を備える

請求項1から3のいずれか一項に記載のメモリデバイス。

#### 【請求項 5】

最も直近のODT及びドライバの設定は、前記メモリデバイスがそれらをラッチするための命令を受信するまで、前記メモリデバイスによる使用のために正式にラッチされない請求項1から4のいずれか一項に記載のメモリデバイス。

#### 【請求項 6】

前記メモリデバイスは、ODT及びドライバのキャリブレーションのシーケンスの完了に応じて、前記メモリデバイスのモードレジスタ空間にフラグをセットする

請求項1から5のいずれか一項に記載のメモリデバイス。

#### 【請求項 7】

メモリデバイスであって、

オンダイ終端(ODT)及びドライバの定期的なキャリブレーションを実行するためのキャリブレーション回路と、

前記メモリデバイスにより受信されるセルフリフレッシュ命令に応答して、前記メモリデバイスをセルフリフレッシュモードにするためのセルフリフレッシュ回路と、を備え、

前記ODT及びドライバの定期的なキャリブレーションは、前記メモリデバイスが前記セルフリフレッシュモードである間に実行され、前記メモリデバイスは、ODT及びドライバのキャリブレーションのシーケンスの完了に応じて、前記メモリデバイスのモードレジスタ空間にフラグをセットする、メモリデバイス。

#### 【請求項 8】

前記メモリデバイスは、前記ODT及びドライバの定期的なキャリブレーションの定期的な時間間隔を指定するためのレジスタ空間を備える

請求項1から7のいずれか一項に記載のメモリデバイス。

#### 【請求項 9】

前記メモリデバイスは、DIMM上に配置される

請求項1から8のいずれか一項に記載のメモリデバイス。

#### 【請求項 10】

前記DIMMは、コンピュータシステムにプラグ接続される

請求項9に記載のメモリデバイス。

#### 【請求項 11】

オンダイ終端(ODT)及びドライバの定期的なキャリブレーションを実行するようにメモリデバイスに命令するための論理回路を備え、

前記論理回路は、前記メモリデバイスに対し、前記メモリデバイスがセルフリフレッシュモードである間に、前記ODT及びドライバの定期的なキャリブレーションをリフレッシュと同時に実行するように命令する、

メモリコントローラ。

#### 【請求項 12】

オンダイ終端(ODT)及びドライバの定期的なキャリブレーションを実行するように

10

20

30

40

50

メモリデバイスに命令するための論理回路を備え、

前記論理回路は、前記メモリデバイスに対し、前記メモリデバイスがセルフリフレッシュモードである間に、前記ODT及びドライバの定期的なキャリブレーションを実行するように命令し、

前記論理回路は、ODT及びドライバのキャリブレーションのシーケンスの完了に応じて、前記メモリデバイスによりセットされた前記メモリデバイスのモードレジスタ空間内のフラグを読み出して、最も直近のキャリブレーションのシーケンスが成功であるか否かを確認する、

メモリコントローラ。

**【請求項 1 3】**

オンダイ終端(ODT)及びドライバの定期的なキャリブレーションを実行するようにメモリデバイスに命令するための論理回路を備え、

前記論理回路は、前記メモリデバイスに対し、前記メモリデバイスがセルフリフレッシュモードである間に、前記ODT及びドライバの定期的なキャリブレーションを実行するように命令し、

前記論理回路は、前記メモリデバイスにより設定されたフラグが直近のキャリブレーションの成功を示すことを確認すると、前記メモリデバイスに対し、前記メモリデバイスが前記セルフリフレッシュモードからアクティブモードへと移行するときに前記キャリブレーションを実行するように命令せず、

前記論理回路は、前記メモリデバイスにより設定された前記フラグが直近のキャリブレーションの成功を示さないことを確認すると、前記論理回路は、前記メモリデバイスがセルフリフレッシュ中に前記キャリブレーションを実行するよう命令していたとしても、前記メモリデバイスに対し、前記メモリデバイスが前記セルフリフレッシュモードから前記アクティブモードへと移行するときに前記キャリブレーションを実行するように命令する、メモリコントローラ。

**【請求項 1 4】**

前記メモリコントローラは、前記メモリデバイスの最も直近のODT及びドライバのキャリブレーションの設定をラッチするように、前記メモリデバイスに命令する

請求項 1 1 から 1 3 のいずれか一項に記載のメモリコントローラ。

**【請求項 1 5】**

前記メモリコントローラは、前記メモリデバイスによりフラグがセットされることに応答して、前記メモリデバイスの最も直近のODT及びドライバのキャリブレーションの設定をラッチするように、前記メモリデバイスに命令する

請求項 1 1 または 1 3 に記載のメモリコントローラ。

**【請求項 1 6】**

前記メモリコントローラは、前記メモリデバイスのレジスタ空間に、前記ODT及びドライバの定期的なキャリブレーションの定期的な時間間隔をプログラムする

請求項 1 1 から 1 5 のいずれか一項に記載のメモリコントローラ。

**【請求項 1 7】**

前記メモリコントローラは、前記セルフリフレッシュモードに入るよう前記メモリデバイスに命令する

請求項 1 1 から 1 6 のいずれか一項に記載のメモリコントローラ。

**【請求項 1 8】**

前記メモリコントローラは、コンピュータシステム内にある

請求項 1 1 から 1 7 のいずれか一項に記載のメモリコントローラ。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

発明の分野は電子工学の技術に関する、より具体的には、メモリデバイスセルフリフレッシュ中の定期的キャリブレーションに関する。

10

20

30

40

50

**【背景技術】****【0002】**

コンピューティングシステムは、典型的には、メモリデバイスがアクティブに読み出し又は書き込み動作を実行していない期間に、セルフリフレッシュモードへと置かれ得るメモリデバイスを備える。理想的には、メモリデバイスがセルフリフレッシュモードからアクティブモードに戻るよう移行することを必要としたときに、読み出し又は書き込み命令がメモリデバイスに送信され得る前にコンピューティングシステムが長期間待たなくてもよいほど、メモリデバイスが迅速に移行できることである。

**【0003】**

本発明のより良好な理解が、以下の図面と合わせて、以下の詳細な説明から取得され得る。

10

**【図面の簡単な説明】****【0004】**

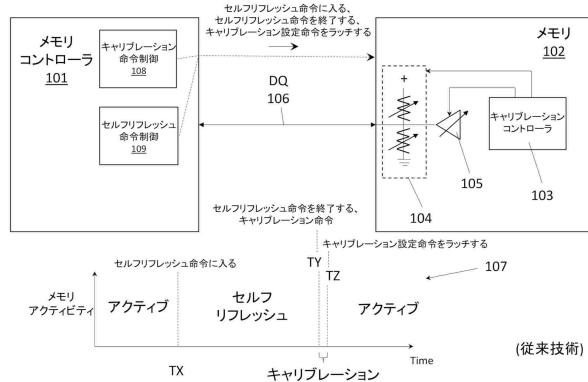

【図1】従来技術のメモリコントローラおよびメモリデバイスを示す。

**【0005】**

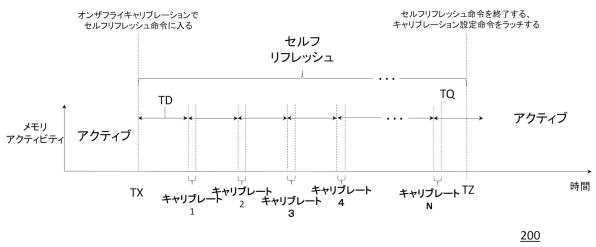

【図2】改善されたメモリデバイスのセルフリフレッシュシーケンスを示す。

**【0006】**

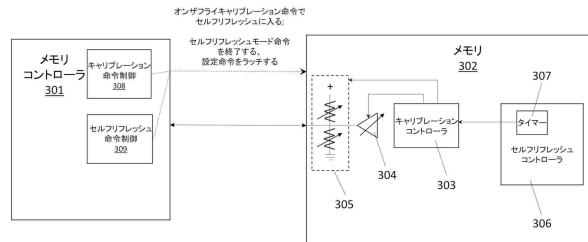

【図3】図2の改善されたメモリデバイスのセルフリフレッシュシーケンスを実装するため、改善されたメモリコントローラおよびメモリデバイスを示す。

**【0007】**

20

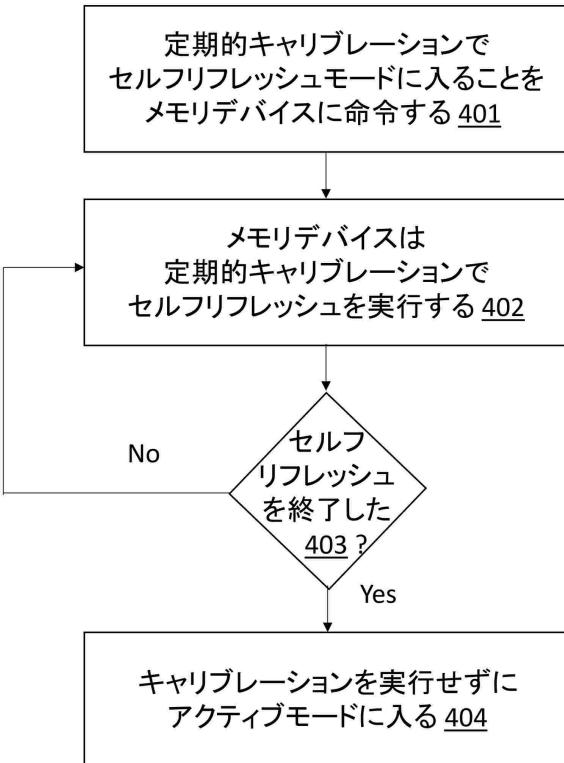

【図4】メモリデバイスセルフリフレッシュ方法を示す。

**【0008】**

【図5】コンピューティングシステムを示す。

**【発明を実施するための形態】****【0009】**

図1は、ホスト側メモリコントローラ101とメモリデバイス102とを含む、従来技術のメモリサブシステムを示している。メモリデバイス102は、(例示の簡略化のため図1に示されていない) Dual Line Memory Module (DIMM) 上に配置される多数のメモリチップのうちの一つであってもよい。DIMMは、メモリコントローラ101に結合されるメモリチャネルへとプラグ接続されてもよい。メモリチャネルは、電子デバイス技術合同協議会(JEDEC)業界標準によって定義される複数の特性を有するダブルデータレート(DDR)メモリチャネル(例えば、JEDEC DDR4メモリチャネル)であってもよい。

30

**【0010】**

メモリデバイス102は、DQワイヤ106によってメモリコントローラ101に結合される。DQワイヤ106は、書き込み動作中にメモリコントローラ101からの書き込み情報をメモリデバイス102へと転送し、読み出し動作中にメモリデバイス102からの読み出し情報をメモリコントローラ101へと転送する、双方向データワイヤである。簡単にするために、メモリコントローラ101とメモリデバイス102との間には、単一のDQワイヤ106のみが示されている。しかしながら、実際には、複数のDQワイヤが、メモリコントローラ101とメモリデバイスとの間に存在し、いくつかのビット幅を有するデータバスをエフェクトする(例えば、64個のDQワイヤが、メモリコントローラ101とメモリデバイス102との間に64ビットのデータバスを形成する)。追加的な命令および/またはアドレス指定信号のワイヤ(例えば、命令アドレス(CA)バス)もまた、メモリコントローラ101とメモリデバイス102との間に存在し、これにより、メモリコントローラは、命令およびアドレスをメモリデバイス102に送信することができる。

40

**【0011】**

メモリデバイス102内のDQワイヤ106のエンドポイントは、終端抵抗回路網104およびデータドライバ105を含む。抵抗回路網104は、書き込み動作中にメモリコ

50

ントローラ 101 からメモリデバイス 102 へと送信される書き込みデータ信号に対して、終端抵抗を DQ ワイヤ 106 のエンドに提供する。終端回路網 104 の抵抗は、理想的には、DQ ワイヤ / メモリデバイスインターフェースにおいて、書き込みデータ信号のリフレクションを防ぎ、又は他の態様では当該リフレクションを減少させる。ドライバ 105 は、理想的には、読み出し動作中にメモリコントローラ 101 によって十分に受信された読み出しデータをメモリデバイス 102 から DQ ワイヤ上へとドライブする駆動電流強度および / またはソースインピーダンスを有する。

#### 【 0012 】

終端回路網 104 の抵抗、ならびに、ドライバ 105 の駆動電流強度および / またはソースインピーダンスの両方が、可変的であるように設計され、これにより、これらは、メモリデバイスの動作中に、キャリブレーションコントローラ 103 によってキャリブレートされることができる（例えば、JEDDEC 固有の「ZQ」キャリブレーション）。ここでは、終端回路網 104 の正しい抵抗、ならびに、ドライバ 105 の正しい駆動電流強度および / またはソースインピーダンスが、温度および / または供給電圧の関数であり得る。重要なことには、これらのパラメータは、メモリデバイス 102 の動作の経過に亘って変化し得る。そのように、終端回路網 104 およびドライバ 105 のための正しい設定も同様に、メモリデバイス 102 の動作の経過に亘って変化し得る。

10

#### 【 0013 】

メモリコントローラ 101 は、メモリデバイスにとってその DQ 終端抵抗回路網および / またはその DQ ドライバをキャリブレートすることが適切であると判定する場合、キャリブレーションを実行すべくメモリデバイス 102 に命令を送信する。命令は最終的に、正しい終端回路網およびドライバ設定を判定するキャリブレーションルーチンを実行することを担当している、メモリデバイス 102 内のキャリブレーションコントローラ 103 によって受信される。しかしながら、残念なことに、キャリブレーションルーチンの実行は、メモリサブシステムの性能に影響を及ぼす、無視できない時間長を消費する。

20

#### 【 0014 】

差し込み図の 107 は、メモリサブシステム性能に対する特定の公開を示している。ここでは、メモリデバイス 102 がダイナミックランダムアクセスメモリ (DRAM) メモリデバイスである場合に、メモリデバイス 102 のストレージセルは、自己のデータを保持すべく、定期的にリフレッシュされることを必要とする。ここでは、メモリデバイス 102 (またはメモリデバイスの DIMM、もしくはメモリデバイスの DIMM がプラグ接続されるチャンネル) が長期間の（読み出し又は書き込み命令がない）非アクティビティを受けているおよび / または受けそうであることをメモリコントローラ 101 が認識する場合に、メモリコントローラ 101 は、セルフリフレッシュモードに入ることをメモリデバイス 102 に命令する。

30

#### 【 0015 】

これに応答して、メモリデバイス 102 は、自己のデータを保持するように、リフレッシュ信号を自己の内部ストレージセルに適用する。差し込み図の 107 のタイミング図に示す通り、メモリデバイスは、その時点で、進行している長期間使用されないことになる、時間 TX に至るまで、アクティブであり、メモリコントローラ 101 によってセルフリフレッシュモードへと置かれる。時間 TY で、メモリデバイスは再び使用されることを必要とする。

40

#### 【 0016 】

従って、メモリコントローラ 101 は、セルフリフレッシュモードを終了して、自己の DQ 抵抗終端回路網およびドライバのキャリブレーションを実行することをメモリデバイス 102 に命令する（なぜなら、メモリデバイス 102 が最初にセルフリフレッシュモードに入った、これ以前の時間 (TX) から、その温度と供給電圧とが変化し得ているためである）。（メモリコントローラ 101 が次に読み出す自己のモードレジスタ空間内にフラグを立てることによって）キャリブレーションが無事に実行されたことをメモリデバイス 102 が確認するときに、メモリコントローラ 101 は、新たに決定されたキャリブレ

50

ーション設定を、メモリデバイスの正式な終端回路網およびドライバ設定としてラッチすることを、メモリデバイス 102 に命令する。残念ながら、キャリブレーションを実行することによって消費される長い時間長（例えば、 $1 \sim 6 \mu s$ ）は、メモリデバイス 102 が、デバイス 102 をセルフリフレッシュモードからアクティブモードへと移行させることができ決定される瞬間（T Y）からアクティブモードに再び入ることが可能になる時間（T Z）を劇的に遅延させる。

#### 【0017】

この広大な遅延（T Z - T Y）は、メモリサブシステムを使用する様々なシステムコンポーネント（例えば、CPUコア、GPUコア、表示ドライバ、ネットワーキングインターフェース、不揮発性大容量ストレージなど）の観点から、メモリサブシステム全体の性能に悪影響を及ぼす。特に、例えば、アクティブ期間の合間の短期間（例えば、数十または数百マイクロ秒）に、好機をねらって（例えば、メモリコントローラ 101 がメモリデバイス 102 の次に来る読み出し／書き込み非アクティビティの期間を認識した場合に）メモリデバイス 102 をセルフリフレッシュモードへと入れることが可能なメモリコントローラ 101 の利点は、アクティブモードへと戻るよう移行するときにキャリブレーションを実行することによってあまりに多くの時間が消費される場合に、大幅に減少される。

10

#### 【0018】

図 2 は、DQ ワイヤを再キャリブレートする前にメモリ 202 をセルフリフレッシュモードからアクティブモードへと移行させることが肯定的に決定されるまで待つことよりもむしろ、メモリデバイス 202 が自己のセルフリフレッシュモード中に DQ 抵抗回路網およびドライバ設定を定期的に再キャリブレートする解決策を示している。図 2 にて観察されるように、メモリデバイス 202 は、TD ごとに抵抗回路網終端およびドライバ設定を再キャリブレートするように構成されている。すなわち、図 2 に観察されるように、第 1 番目のキャリブレーション 1 は、メモリデバイスが時間 TX で最初にセルフリフレッシュに入る後の TD で生じる。第 2 番目のキャリブレーション 2 は、第 1 番目のキャリブレーション 1 の後の TD で生じ、第 3 番目のキャリブレーション 3 は第 2 番目のキャリブレーション 2 の後の TD で生じ、第 4 番目のキャリブレーション 4 は第 3 番目のキャリブレーションの後の TD で生じる、などなど。

20

#### 【0019】

定期的キャリブレーションは、セルフリフレッシュモードの外へ出ることの命令をメモリデバイスがメモリコントローラから受信する（T Z）まで続く。特に、セルフリフレッシュモードの時間長に亘って N 回のキャリブレーションが実行されている。ここで、メモリサブシステムの温度および供給電圧は、第 N 番目のキャリブレーションが完了して（T Q）からあまり変化していないと推測される。そのように、セルフリフレッシュモードから出る命令が時間 TZ に受信された場合に、第 N 番目のキャリブレーションで確立された抵抗終端回路網およびドライバ設定は、存在している温度および供給電圧条件に対して十分であると推測される。

30

#### 【0020】

更に以下により詳細に説明されるように、様々な実施形態で、メモリコントローラ 201 はまた、（例えば、メモリデバイスのモードレジスタ空間内に立てられるフラグの状態を読み出すことによって）直近のキャリブレーションシーケンス（第 N 番目のシーケンス）が成功だったか否かを確認し、そうである場合、メモリデバイスの正式な抵抗回路網終端およびドライバ設定として第 N 番目のキャリブレーションシーケンスからの設定をラッチすることをメモリデバイスに命令する。その設定がラッチされた後、メモリデバイスは、アクティブモードに入り、読み出し／書き込み命令をメモリコントローラから受信することができる。そのように、メモリデバイス 202 は、キャリブレーションを実行することなく、およそ時間 TZ に、セルフリフレッシュモードからアクティブモードへと移行することが可能である。

40

#### 【0021】

図 3 は、図 2 の改善されたアプローチと共に実装することができる、改善されたメモリ

50

コントローラ 301 およびメモリデバイス 302 を示す。図 3 に観察されるように、メモリコントローラ 301 は、メモリデバイス 302 に対してセルフリフレッシュ命令を生成することが可能であり、また、メモリデバイスがセルフリフレッシュモード（オンザフライキャリブレーションでセルフリフレッシュ）中である間にメモリデバイスが定期的キャリブレーションを実行することを指定する、改善されたセルフリフレッシュ制御論理回路 309 を有する。一実施形態において、メモリデバイスのより多くのレジスタ空間が、セルフリフレッシュモード中の定期的キャリブレーションを可能にする / 不可能にするフィールドを含む。メモリデバイス 302 がセルフリフレッシュ命令を受信したときに当該フィールドが設定されている場合、メモリデバイスは、その後に続くセルフリフレッシュ中に当該定期的キャリブレーションを実行する。セルフリフレッシュモード中であるときに定期的キャリブレーションを実行することをメモリコントローラ 301 がメモリデバイス 302 に命令する場合、メモリコントローラ 301 は、セルフリフレッシュから外れる移行の一環としてキャリブレーションを実行することをメモリデバイス 302 に命令しなくてもよい、と理解する。

#### 【0022】

例えば、メモリコントローラ 301 は、セルフリフレッシュを終了することをメモリデバイス 302 に命令し、（メモリデバイスのモードレジスタを読み出すことによって）メモリデバイスの直近のキャリブレーションが有効な設定を生成したか否かを確認し、そのような確認のときに、当該設定を、メモリデバイスの次に来るアクティブモード中に使用される設定としてラッチすることをメモリデバイスに命令する。特に、メモリコントローラのキャリブレーション制御論理回路 308 は、定期的キャリブレーションを伴うセルフリフレッシュモードから、アクティブモードへの移行の一環として、キャリブレーションを実行することをメモリデバイス 302 に命令しない。

#### 【0023】

また、図 3 において観察されるように、メモリデバイス 302 は、メモリデバイス 302 が自己の終端回路網 304 およびドライバ 305 の設定を定期的に再キャリブレートするように、セルフリフレッシュ中にキャリブレーションコントローラ 303 を定期的に引き起こして動作させることを担当する、関連するタイマー回路 307 を有するセルフリフレッシュ制御回路 306 を備える。タイマー回路 307 は、様々な方法で実装ができる。第 1 の実施形態によれば、タイマー回路 307 は、メモリデバイス 302 の内部クロック（例えば、セルフリフレッシュクロック）を判定する、メモリデバイス 302 の位相同期ループ（PLL）回路または遅延同期ループ（DLL）回路に結合される。カウンタは、PLL / DLL 回路に結合され、クロック周期をカウントする（例えば、カウンタは各クロック周期でインクリメントする）。カウンタが特定の値に到達するごとに、再キャリブレーションが引き起こされ、カウンタ値がリセットされる。

#### 【0024】

第 2 実施形態によれば、セルフリフレッシュコントローラ 306 に関連するカウンタは、各再キャリブレーション動作を引き起こすのに使用される。ここで、例えば、セルフリフレッシュコントローラ 306 は、リフレッシュをカウントする 1 または複数のカウンタを含む（例えば、各々が個別に特定のメモリバンクのリフレッシュをカウントする、バンク単位のリフレッシュカウンタ、各メモリバンクがリフレッシュされた後にインクリメントするグローバルリフレッシュカウンタ、など）。タイマー回路 307 は、1 または複数のカウンタに結合され、1 または複数のカウンタが特定の 1 または複数の値に到達したときに再キャリブレーションアクティビティを引き起こす。一つの実施形態によれば、キャリブレーションは、複数の内部リフレッシュの合間に引き起こされ、キャリブレーション後に実行される任意のリフレッシュは、キャリブレーションが完了する後まで開始しない。別の実施形態によれば、キャリブレーションは、複数の内部リフレッシュの合間に引き起こされ、そして、キャリブレーションを引き起こした後に実行される複数のリフレッシュと同時に実行される。

#### 【0025】

10

20

30

40

50

更なる実施形態によれば、各セルフリフレッシュキャリプレーションシーケンス中に決定される終端回路網およびドライバ設定は、セルフリフレッシュ制御回路 306 によって内部で保持される。そのように、これらのレジスタは、セルフリフレッシュ中に実行される各々の新たなキャリプレーションで更新される。セルフリフレッシュモードからアクティブへの移行時に、制御回路のレジスタに存在する設定は、メモリコントローラ 301 による、肯定的な命令に応答して、メモリデバイスの正式な回路網およびドライバ設定制御レジスタ空間内へとラッチされ、その後、アクティブモード中のメモリデバイス 302 によって使用される。

#### 【0026】

このアプローチの更なる実施形態において、メモリデバイスは、無事にキャリプレーションを実行することに、自己のモードレジスタ空間内にフラグを立てる。メモリコントローラは次に、フラグの状態をチェックして、直近のキャリプレーションが成功したか否かを確認することが可能である。そうである場合、メモリコントローラ 301 は、キャリプレーション命令をメモリデバイス 302 に発行することなくセルフリフレッシュモードを終了することができる、と理解する。メモリデバイスが、フラグが肯定的に設定されているのを見ない場合、メモリコントローラ 301 は、セルフリフレッシュモードからアクティブモードへの移行の一環としてキャリプレーション命令を発行すべきである、と理解する。この後者のシナリオは、全てのセルフリフレッシュ期間が TD 未満である場合に可能である。

#### 【0027】

更なる実施形態において、TD 期間は、メモリデバイス内で設定可能であってもよい。例えば、メモリデバイスのモードレジスタ設定は、メモリデバイス内で、異なる TD 設定を許可してもよい。代替的に、TD パラメータは、メモリデバイス 302 内へしっかりと設計されてもよい。

#### 【0028】

様々な実施形態において、メモリデバイスは更に、上記で説明したものよりも自律的に設計されてもよく、セルフリフレッシュモードに入ることをメモリコントローラによって肯定的に命令されることを必要としなくてもよい。すなわち、メモリデバイスは、メモリコントローラによって肯定的に指令されることなくメモリデバイスをセルフリフレッシュモードへと置く、独自の内部ロジックを有してもよい。この場合、メモリデバイスのモードレジスタは、メモリデバイスが、自発的にに入るセルフリフレッシュモード中に、上記で説明した通り定期的にキャリプレーションを実行することを、メモリコントローラによって設定されてもよい。

#### 【0029】

制御回路 303、306、308、309 は、カスタム仕様のハードワイヤード論理回路（例えば、ハードワイヤードステートマシンなど）、プログラマブル論理回路（例えば、フィールドプログラマブルゲートアレイ（FPGA）、プログラマブルロジックアレイ（PLA）など）、プログラムコードの幾つかの形式を実行する論理回路（例えば、埋め込みプロセッサ、埋め込みコントローラなど）、または、これらの任意の組み合わせのような、論理回路の様々な形式で実装される得ることに留意すべきである。

#### 【0030】

図 4 は、上記で説明した方法を示す。当該方法は、定期的キャリプレーション 401 でセルフリフレッシュモードに入ることの命令をメモリデバイスに送信する段階を備える。メモリデバイスは次に、セルフリフレッシュを行い、定期的なセルフリフレッシュがセルフリフレッシュ 402 中に実行される。メモリデバイスがセルフリフレッシュから外れてアクティブモード 403 へと移行すると、メモリデバイスは、キャリプレーション 404 を実行することなく、アクティブモードに入る。

#### 【0031】

おそらく、メモリデバイスがセルフリフレッシュモード中である間にメモリデバイスによって複数のキャリプレーションが実行されるが、当該キャリプレーションは定期的に実

10

20

30

40

50

行されない（例えば、よりランダムな時間間隔で実行される）他の実施形態／実装が存在し得る。

#### 【 0 0 3 2 】

上記で説明した複数のアプローチは、J E D E C 業界標準規格のような業界標準（例えば、D D R 5 J E D E C 業界標準規格）によって指定されてもよい。

#### 【 0 0 3 3 】

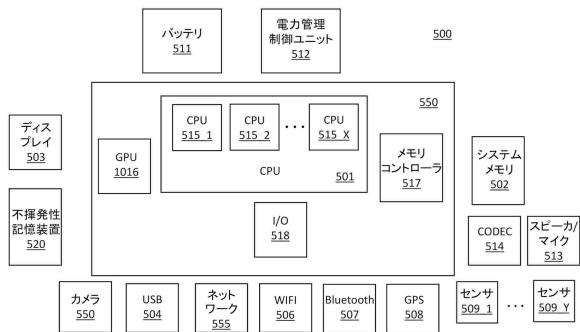

図 5 は、コンピューティングシステム 5 0 0（例えば、スマートフォン、タブレット型コンピュータ、ラップトップコンピュータ、デスクトップコンピュータ、サーバコンピュータなど）の例示的な図を提供する。図 5 において観察されるように、ベーシックコンピューティングシステム 5 0 0 は、（例えば、複数の汎用プロセッsingコア 5 1 5 \_ 1 から 5 1 5 \_ X を含み得る）中央処理装置 5 0 1 と、マルチコアプロセッサまたはアプリケーションプロセッサ上に配置されたメインメモリコントローラ 5 1 7 と、システムメモリ 5 0 2 と、ディスプレイ 5 0 3（例えば、タッチスクリーン、フラットパネル）と、ローカル有線ポイントツーポイントリンク（例えば、U S B インターフェース 5 0 4）と、様々なネットワーク I / O 機能 5 0 5（E t h e r n e t（登録商標）インターフェースおよび / またはセルラーモデムサブシステムなど）と、無線ローカルエリアネットワーク（例えば、W i F i（登録商標））インターフェース 5 0 6 と、無線ポイントツーポイントリンク（例えば、B l u e t o o t h（登録商標））インターフェース 5 0 7 と、全地球測位システムインターフェース 5 0 8 と、様々なセンサ 5 0 9 \_ 1 から 5 0 9 \_ Y と、1 または複数のカメラ 5 1 0 と、バッテリ 5 1 1 と、電力管理制御ユニット 5 1 2 と、スピーカおよびマイク 5 1 3 とオーディオコーダ / デコーダ 5 1 4 とを含み得る。

10

#### 【 0 0 3 4 】

アプリケーションプロセッサまたはマルチコアプロセッサ 5 5 0 は、そのC P U 5 0 1 内の 1 または複数の汎用プロセッsingコア 5 1 5 と、1 または複数のグラフィック処理ユニット 5 1 6 と、メモリ管理機能 5 1 7（例えば、メモリコントローラ）と、I / O 制御機能 5 1 8 とを含み得る。汎用プロセッsingコア 5 1 5 は典型的には、コンピューティングシステムのオペレーティングシステムおよびアプリケーションソフトウェアを実行する。グラフィック処理ユニット 5 1 6 は典型的には、グラフィックインテンシブ機能を実行し、例えば、ディスプレイ 5 0 3 上に表示されるグラフィック情報を生成する。メモリ管理機能 5 1 7 は、システムメモリ 5 0 2 とインターフェースで連結して、システムメモリ 5 0 2 への / からのデータの書き込み / 読み出しを行う。メモリコントローラ 5 1 7 およびシステムメモリ（または他のメモリコントローラおよびメモリ）は、上記で説明したセルフリフレッシュ中にメモリデバイスの抵抗回路網終端およびドライバ設定の定期的リフレッシュを実装してもよい。電力管理制御ユニット 5 1 2 は概して、システム 5 0 0 の電力消費を制御する。

30

#### 【 0 0 3 5 】

タッチスクリーンディスプレイ 5 0 3 、通信インターフェース 5 0 4 - 5 0 7 、G P S インターフェース 5 0 8 、センサ 5 0 9 、（複数の）カメラ 5 1 0 、およびスピーカ / マイク C O D E C 5 1 3 、5 1 4 の各々は全て、同様に、適切な場所に、統合された周辺装置（例えば、1 または複数のカメラ 5 1 0 ）を含む、全体のコンピューティングシステムに対する I / O（入力および / または出力）の様々な形式として示され得る。実装に応じて、これらの I / O コンポーネントのうちの様々なものが、アプリケーションプロセッサ / マルチコアプロセッサ 5 5 0 上で統合されてもよく、または、ダイから離れて配置され又はアプリケーションプロセッサ / マルチコアプロセッサ 5 5 0 のパッケージ外に配置されてもよい。コンピューティングシステムはまた、システムの大容量ストレージコンポーネントであり得る不揮発性記憶装置 5 2 0 を含む（例えば、ハードディスクドライブ、ソリッドステートドライブなど）。

40

#### 【 0 0 3 6 】

本発明の複数の実施形態は、上記で明らかにされた様々な処理を含んでもよい。複数の処理は、複数の機械実行可能命令に具現化されてもよい。複数の命令は、汎用または専用

50

プロセッサに特定の複数の処理を実行させるのに使用され得る。代替的に、これらの複数の処理は、複数の処理を実行するためのハードワイヤード論理回路またはプログラマブル論理回路（例えば、フィールドプログラマブルゲートアレイ（FPGA）、プログラマブルロジックデバイス（PLD））を含む特定／カスタムハードウェアコンポーネントによって実行されてもよく、または、プログラムコンピュータコンポーネントおよびカスタムハードウェアコンポーネントの任意の組み合わせによって実行されてもよい。

#### 【0037】

本発明の要素は、機械実行可能命令を保存するための機械可読媒体としてもまた提供され得る。機械可読媒体は、これらに限定はされないが、フロッピー（登録商標）ディスクケット、光ディスク、CD-ROM、磁気光ディスク、フラッシュメモリ、ROM、RAM、EPROM、EEPROM、磁気カードもしくは光カード、伝播媒体、または電子命令を保存するのに適した他のタイプの媒体／機械可読媒体を含み得る。例えば、本発明は、通信リンク（例えば、 modem 接続またはネットワーク接続）を介して、搬送波または他の伝播媒体に具現化されるデータ信号を用いて、リモートコンピュータ（例えば、サーバ）から要求しているコンピュータ（例えば、クライアント）に転送され得るコンピュータプログラムとしてダウンロードされ得る。

10

#### 【0038】

上記の明細書において、本発明は、その特定の例示的な実施形態を参照して説明されている。しかしながら、添付の請求項で明らかにされる本発明のより広い主旨および範囲から逸脱することなく、様々な修正および変更がなされ得ることは明らかであろう。従って、本明細書および図面は、限定的な意味ではなく例示的な意味のものと見做されるべきである。

20

[項目1] メモリデバイスがセルフリフレッシュモード中である間にメモリデバイスの抵抗回路網終端およびデータドライバのキャリブレーションを実行することをメモリデバイスに命令する論理回路を備える、メモリコントローラ。

[項目2] 論理回路は、メモリデバイスのモードレジスタ内に、メモリデバイスがセルフリフレッシュモード中である間にキャリブレーションの実行を可能にするフラグを立てる、

項目1に記載のメモリコントローラ。

[項目3] 論理回路は、メモリデバイスがキャリブレーションを実行することを命令されているので、セルフリフレッシュモードを終了するときに抵抗回路網終端およびデータドライバをキャリブレートする、という命令をメモリデバイスに送信しない、

30

項目1に記載のメモリコントローラ。

[項目4] 論理回路は、セルフリフレッシュモードを終了する、という第1命令と、キャリブレーションの設定をラッチする、という第2命令とをメモリデバイスに送信する、

項目3に記載のメモリコントローラ。

[項目5] 論理回路は、キャリブレーションのうち最も直近のものが無事に実行されたか否かを示す情報を含むメモリデバイスのレジスタをチェックし、

論理回路は、キャリブレーションのうち最も直近のものが無事に実行されていない場合には、たとえメモリデバイスがセルフリフレッシュモード中にキャリブレーションを実行することを命令されていたとしても、セルフリフレッシュモードから外れるメモリデバイスの移行の一環として、抵抗回路網終端およびデータドライバのキャリブレーションを実行することをメモリデバイスに命令する、

40

項目1に記載のメモリコントローラ。

[項目6] メモリデバイスであって、

メモリデバイスがセルフリフレッシュモード中である間にメモリデバイスの抵抗回路網終端およびデータドライバのキャリブレーションを実行する論理回路を備える、

メモリデバイス。

[項目7] 論理回路は、キャリブレーションが定期的に実行されるようにさせる、

項目6に記載のメモリデバイス。

50

[ 項目 8 ] 論理回路は、カウンタを備える、

項目 7 に記載のメモリデバイス。

[ 項目 9 ] カウンタは、メモリデバイスによって実行されるリフレッシュをカウントする、

項目 8 に記載のメモリデバイス。

[ 項目 10 ] カウンタは、メモリデバイスのクロックの周期をカウントする、

項目 8 に記載のメモリデバイス。

[ 項目 11 ] メモリデバイスは、セルフリフレッシュモード中にキャリブレーションを実行することをメモリデバイスに命令するメモリコントローラから、セルフリフレッシュ命令を受信する、

項目 6 に記載のメモリデバイス。

[ 項目 12 ] メモリデバイスは、モードレジスタ空間を備え、モードレジスタ空間は、設定された場合に、メモリデバイスがセルフリフレッシュ命令を受信した後で、メモリデバイスに、セルフリフレッシュモード中にキャリブレーションを実行させる、

項目 11 に記載のメモリデバイス。

[ 項目 13 ] メモリデバイスは、メモリデバイスのモードレジスタ空間内に、キャリブレーションのうち最も直近のものが無事に実行されたか否かを示すフラグを含ませる、

項目 6 に記載のメモリデバイス。

[ 項目 14 ] メモリデバイスは、Dual In-Line Memory Module (DIMM) 上に配置される、

項目 6 に記載のメモリデバイス。

[ 項目 15 ] 複数のプロセッキングコアと、

ソリッドステートドライブと、

システムメモリと、

システムメモリコントローラとを備え、

システムメモリコントローラは、複数のプロセッキングコアに結合され、メモリデバイスがセルフリフレッシュモード中である間にメモリデバイスの抵抗回路網終端およびデータドライバのキャリブレーションを実行することをメモリデバイスに命令する論理回路を有する、

コンピューティングシステム。

[ 項目 16 ] 論理回路は、メモリデバイスのモードレジスタ内に、メモリデバイスがセルフリフレッシュモード中である間にキャリブレーションの実行を可能にするフラグを立てる、

項目 15 に記載のコンピューティングシステム。

[ 項目 17 ] 論理回路は、メモリデバイスがキャリブレーションを実行することを命令されているので、セルフリフレッシュモードを終了するときに抵抗回路網終端およびデータドライバをキャリブレートする、という命令をメモリデバイスに送信しない、

項目 15 に記載のコンピューティングシステム。

[ 項目 18 ] 論理回路は、セルフリフレッシュモードを終了する、という第 1 命令と、キャリブレーションの設定をラッチする、という第 2 命令をメモリデバイスに送信する、

項目 17 に記載のコンピューティングシステム。

[ 項目 19 ] 論理回路は、キャリブレーションのうち最も直近のものが無事に実行されたか否かを示す情報を含むメモリデバイスのレジスタをチェックし、

論理回路は、キャリブレーションのうち最も直近のものが無事に実行されていない場合には、たとえメモリデバイスがセルフリフレッシュモード中にキャリブレーションを実行することを命令されていたとしても、セルフリフレッシュモードから外れるメモリデバイスの移行の一環として、抵抗回路網終端およびデータドライバのキャリブレーションを実行することをメモリデバイスに命令する、

項目 15 に記載のコンピューティングシステム。

[ 項目 20 ] メモリデバイスは、JEDEC 標準に準拠するように設計される、

10

20

30

40

50

項目 15 に記載のコンピューティングシステム。

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【図 5】

10

20

30

40

50

---

フロントページの続き

レッジ ブーレバード・2200 インテル・コーポレーション内

合議体

審判長 須田 勝巳

審判官 山崎 慎一

審判官 脇岡 剛

(56)参考文献 特開2011-187115 (JP, A)

特表2018-511108 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G06F12/00